# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114695280 A (43) 申请公布日 2022.07.01

*H01L 25/04* (2014.01) *H01L 25/10* (2006.01)

(21) 申请号 202111354488.4

(22)申请日 2021.11.15

(30) 优先权数据

17/122,061 2020.12.15 US

(71) **申请人** 英特尔公司 地址 美国加利福尼亚

(72) 发明人 S•M•利夫 J•M•斯旺

A·A·埃尔谢尔比尼 X·F·布龙

A • 阿列克索夫 F • 艾德

(74) 专利代理机构 永新专利商标代理有限公司 72002

专利代理师 林金朝

(51) Int.CI.

H01L 23/29 (2006.01)

H01L 23/42 (2006.01)

权利要求书2页 说明书22页 附图23页

### (54) 发明名称

具有直接接合的微电子组件中的部件间材 料

#### (57) 摘要

本文公开了包括通过直接接合耦合在一起的微电子部件的微电子组件以及相关的结构和技术。在一些实施例中,微电子组件可以包括中介层;第一微电子部件,具有通过第一直接接合区域耦合到中介层的第一表面和相对的第二表面;第二微电子部件,具有通过第二直接接合区域耦合到中介层的第一表面和相对的第二表面;对垫材料,在中介层的表面上且在第一微电子部件和第二微电子部件周围;无机填充材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间;以及第三微电子部件,耦合到第一微电子部件和第二微电子部件的第二表面。在一些实产的例中,对垫材料、无机填充材料和第三微电子部件的材料可以包括导热材料。

CN 114695280 A

- 1.一种微电子组件,包括:

- 中介层,具有第一表面和相对的第二表面;

- 第一微电子部件,通过第一直接接合区域耦合到所述中介层的所述第二表面;

- 第二微电子部件,通过第二直接接合区域耦合到所述中介层的所述第二表面;

衬垫材料,在所述中介层的所述第二表面上并在所述第一微电子部件和所述第二微电子部件周围;以及

无机电介质材料,在所述衬垫材料上且在所述第一微电子部件与所述第二微电子部件 之间。

- 2.根据权利要求1所述的微电子组件,其中,所述无机电介质材料包括硅和氧、或硅和 氮、或其组合。

- 3.根据权利要求1或2所述的微电子组件,其中,所述无机电介质材料的厚度在10微米与250微米之间。

- 4.根据权利要求1-3中任一项所述的微电子组件,其中,所述衬垫材料包括硅和碳和 氮、硅和氮、硅和氧和氮、或硅和碳。

- 5.根据权利要求1-4中任一项所述的微电子组件,其中,所述衬垫材料的厚度在10纳米与2000纳米之间。

- 6.根据权利要求1-5中任一项所述的微电子组件,其中,所述第一微电子部件和所述第二微电子部件的厚度小于或等于40微米。

- 7.根据权利要求1-6中任一项所述的微电子组件,其中,所述第一微电子部件和所述第二微电子部件包括耦合到所述中介层的第一表面和相对的第二表面,并且所述微电子组件进一步包括:

耦合到所述第一微电子部件和所述第二微电子部件的所述第二表面的第三微电子部 件。

8.根据权利要求7所述的微电子组件,其中,所述无机电介质材料是第一无机电介质材料,并且所述微电子组件进一步包括:

在所述第一无机电介质材料上以及在所述第一微电子部件和所述第二微电子部件的 所述第二表面上的第二无机电介质材料,其中,所述第三微电子部件通过熔融接合区域耦 合到所述第二无机电介质材料。

- 9.根据权利要求7所述的微电子组件,其中,所述第一微电子部件和所述第二微电子部件是单面管芯,其中,所述第三微电子部件是无源管芯,并且其中,所述第三微电子部件通过熔融接合区域耦合到所述第一微电子部件和所述第二微电子部件的所述第二表面。

- 10.根据权利要求9所述的微电子组件,其中,所述第三微电子部件进一步包括散热结构。

- 11.一种微电子组件,包括:

中介层,具有第一面和相对的第二面;

第一微电子部件,具有第一表面和相对的第二表面,所述第一微电子部件在所述第一 表面处通过第一直接接合区域耦合到所述中介层的所述第二面;

第二微电子部件,具有第一表面和相对的第二表面,所述第二微电子部件在所述第一 表面处通过第二直接接合区域耦合到所述中介层的所述第二面; 衬垫材料,在所述中介层的所述第二面上且在所述第一微电子部件和所述第二微电子 部件周围:

无机填充材料,在所述衬垫材料上且在所述第一微电子部件与所述第二微电子部件之间;以及

第三微电子部件,耦合到所述第一微电子部件和所述第二微电子部件的所述第二表面。

- 12.根据权利要求11所述的微电子组件,其中,所述第一微电子部件和所述第二微电子部件是双面管芯,其中,所述第三微电子部件是有源管芯,并且其中,所述第三微电子部件通过第三直接接合区域耦合到所述第一微电子部件和所述第二微电子部件的所述第二表面。

- 13.根据权利要求12所述的微电子组件,还包括:

穿衬底过孔(TSV),穿过所述无机填充材料而电耦合所述第三微电子部件和所述中介层。

- 14.根据权利要求13所述的微电子组件,其中,所述中介层包括电力输送电路,所述第一微电子部件和所述第二微电子部件包括存储器电路,并且所述第三微电子部件包括处理电路。

- 15.根据权利要求11-14中任一项所述的微电子组件,还包括:

封装衬底,耦合到所述中介层的所述第一面;以及

底部填充材料,在所述封装衬底和所述第三微电子部件之间延伸。

16.一种微电子组件,包括:

中介层:

第一微电子部件,具有第一表面和相对的第二表面,其中,所述第一微电子部件的所述 第一表面通过第一直接接合区域耦合到所述中介层;

第二微电子部件,具有第一表面和相对的第二表面,其中,所述第二微电子部件的所述 第一表面通过第二直接接合区域耦合到所述中介层;

衬垫材料,在所述中介层的表面上且在所述第一微电子部件和所述第二微电子部件周围:

无机填充材料,在所述衬垫材料上且在所述第一微电子部件与所述第二微电子部件之间:以及

第三微电子部件,耦合到所述第一微电子部件和所述第二微电子部件的所述第二表面。

- 17.根据权利要求16所述的微电子组件,其中,所述无机电介质材料包括硅和氧、或硅和氮、或其组合。

- 18.根据权利要求16或17所述的微电子组件,其中,所述衬垫材料包括硅和碳和氮、硅和氮、硅和氧和氮、或硅和碳、以及其组合。

- 19.根据权利要求16-18中任一项所述的微电子组件,其中,所述无机电介质材料的厚度在10微米与250微米之间。

- 20.根据权利要求16-19中任一项所述的微电子组件,其中,所述衬垫材料的厚度在10纳米与2000纳米之间。

# 具有直接接合的微电子组件中的部件间材料

### 背景技术

[0001] 集成电路(IC)封装通常包括引线接合或焊接到中介层的管芯、管芯与中介层之间的底部填充材料、以及设置在管芯周围的模制材料。模制材料通常对温度敏感,这限制了在半导体组装期间可以使用的制造工艺的类型。在使用中,模制材料可通过限制热量从IC封装中的热点传递出去而不利地影响处理器性能。

#### 附图说明

[0002] 根据结合附图的以下具体描述,将容易理解实施例。为了便于该描述,类似的附图标记表示类似的结构元件。在附图的各图中,通过示例而非限制的方式示出了各实施例。

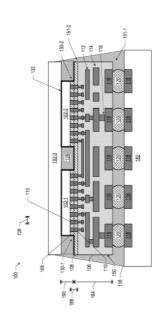

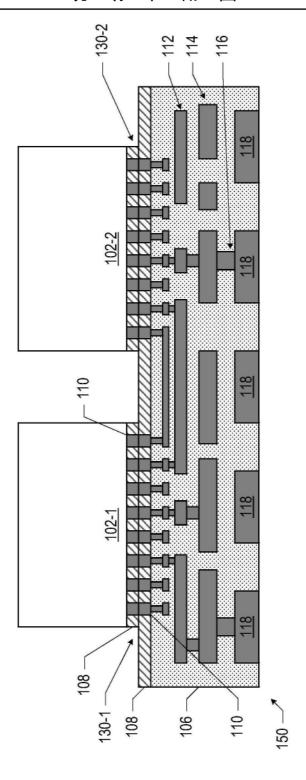

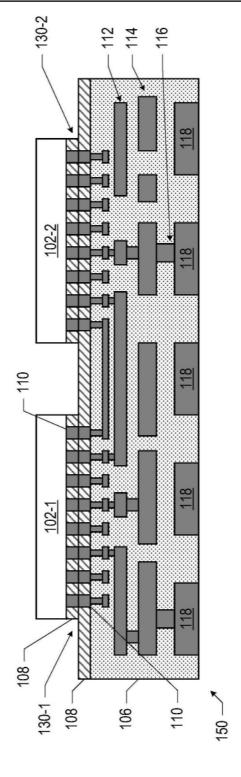

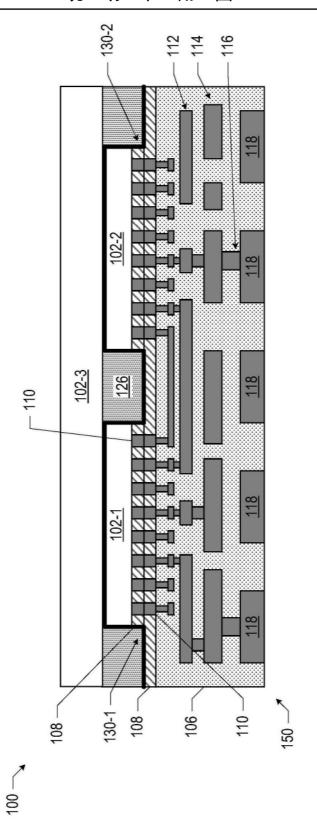

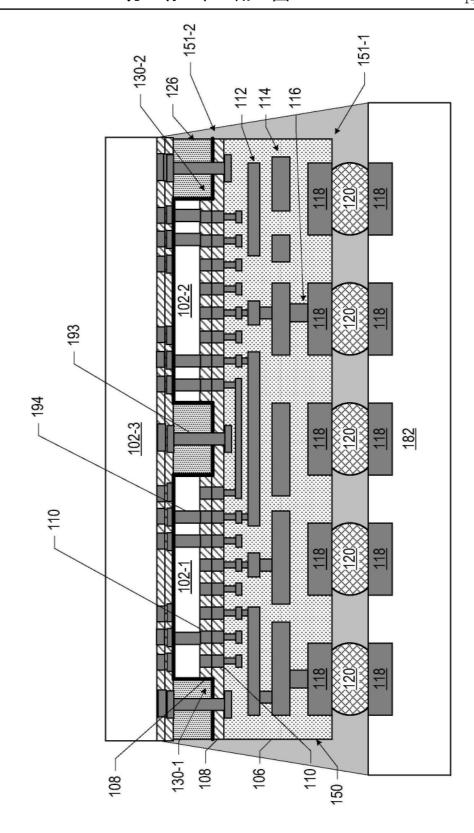

[0003] 图1是根据各种实施例的包括直接接合和部件间材料的示例微电子组件的侧视截面图。

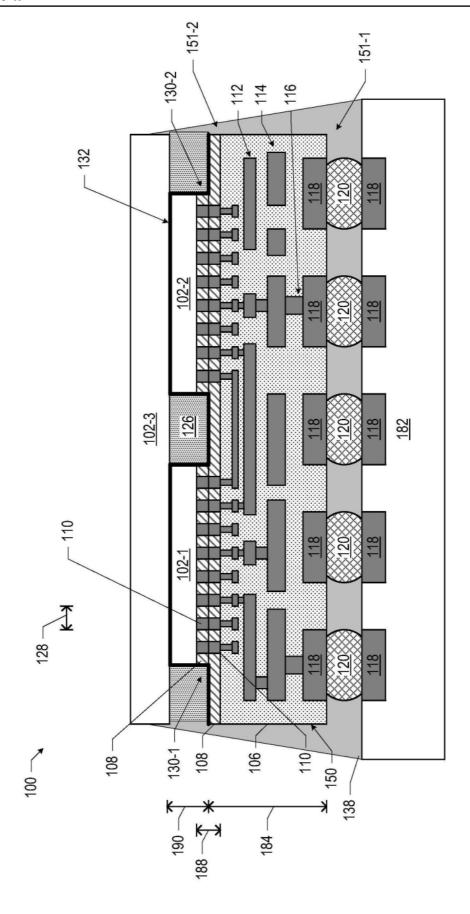

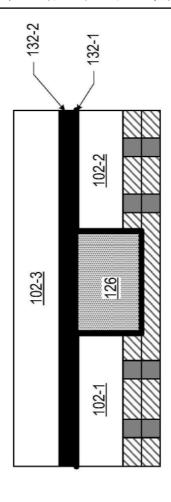

[0004] 图2是根据各种实施例的图1的微电子组件的一部分的侧视截面分解图。

[0005] 图3A-3G是根据各种实施例的图1和2的微电子组件的一部分的制造中的示例阶段的侧视截面图。

[0006] 图4A-4D是根据各种实施例的示出了示例接合界面的图3G的虚线部分的侧视截面放大图。

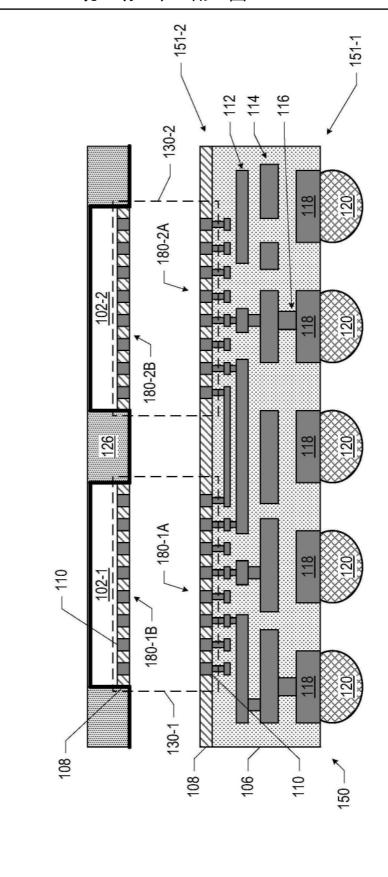

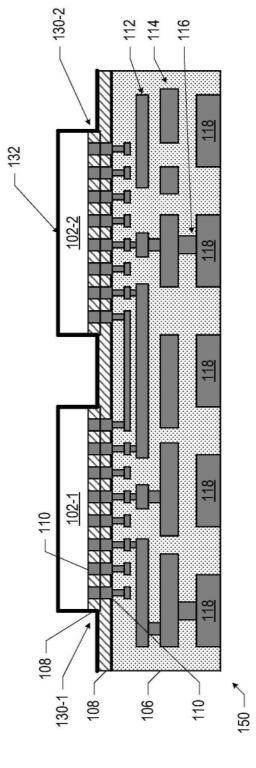

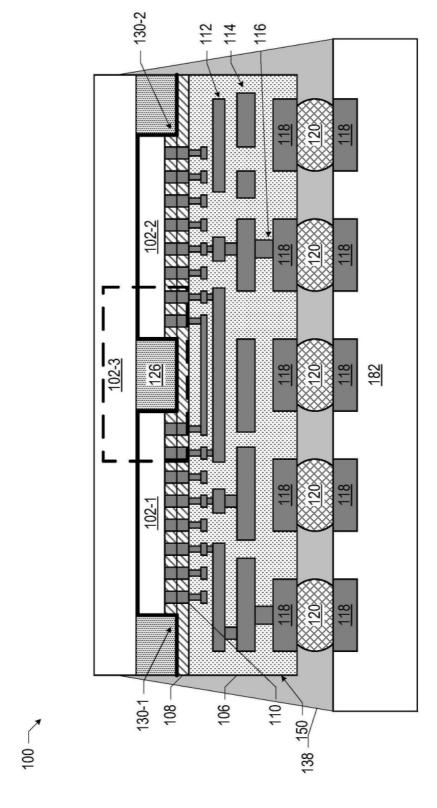

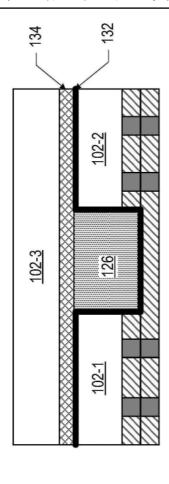

[0007] 图5是根据各种实施例的包括直接接合和部件间材料的示例微电子组件的侧视截面图。

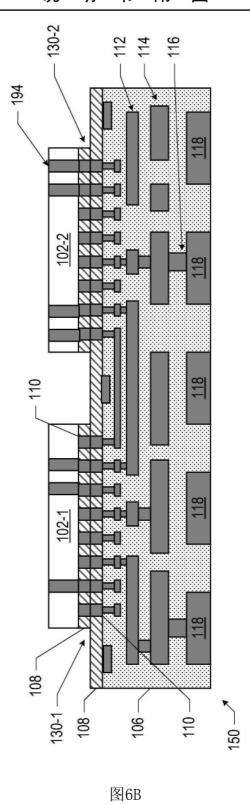

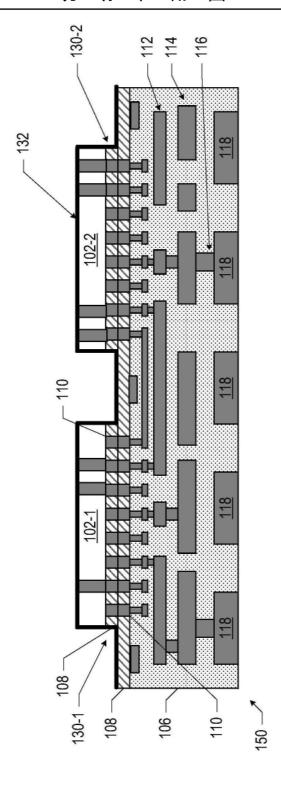

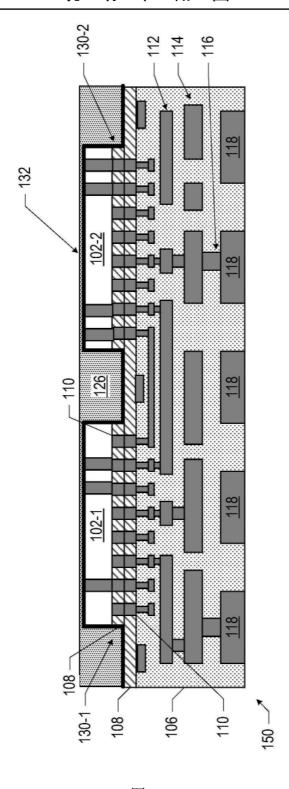

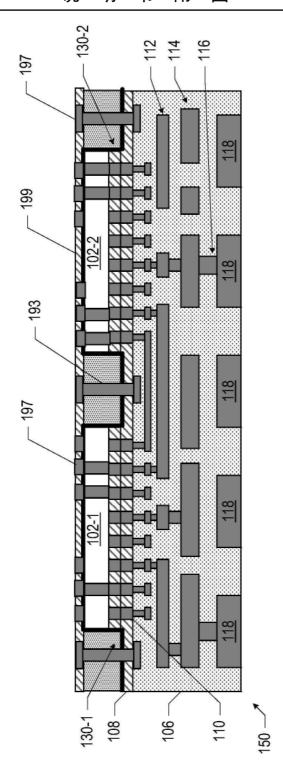

[0008] 图6A-6F是根据各种实施例的图3的微电子组件的制造中的示例阶段的侧视截面图。

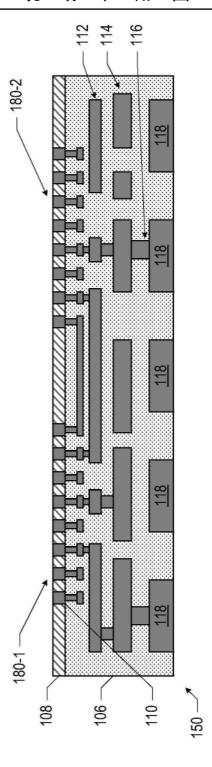

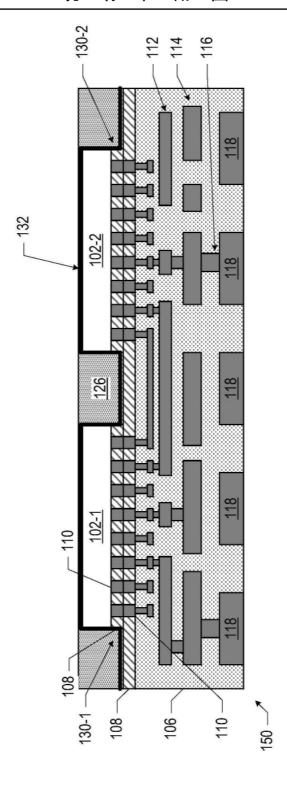

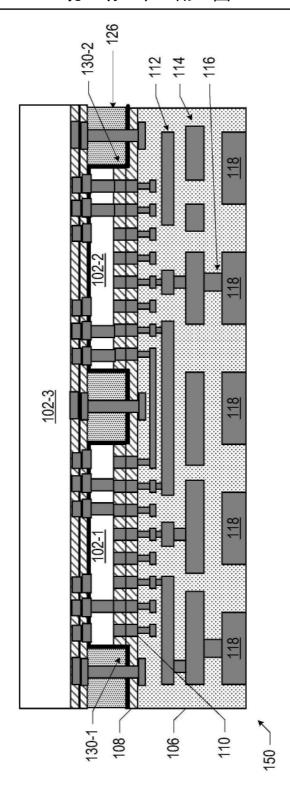

[0009] 图7是根据各种实施例的包括直接接合和部件间散热材料的示例微电子组件的侧视截面图。

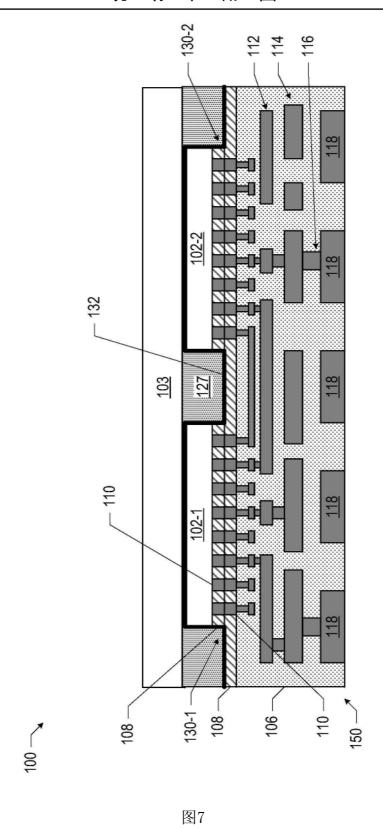

[0010] 图8是根据本文公开的任何实施例的可以包括在微电子部件中的晶圆和管芯的俯视图。

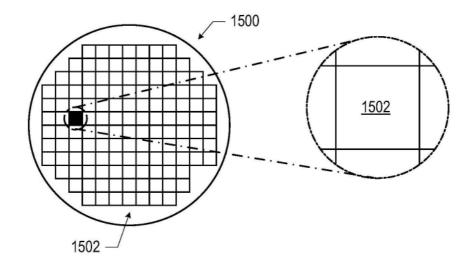

[0011] 图9是根据本文公开的任何实施例的可以包括在微电子部件中的集成电路 (IC) 器件的侧视截面图。

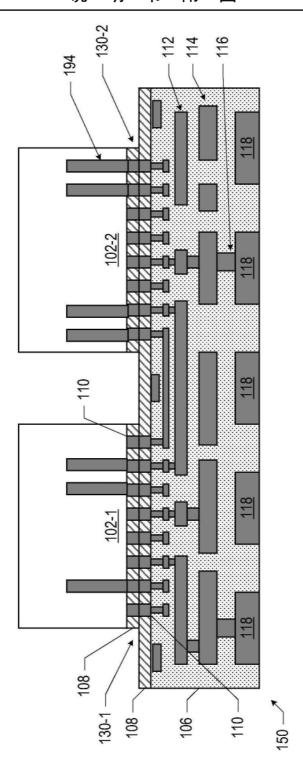

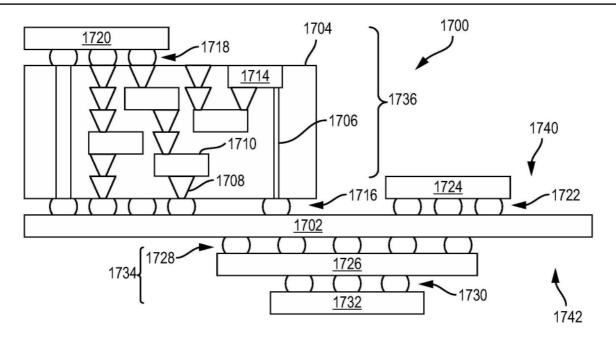

[0012] 图10是可以包括根据本文公开的任何实施例的微电子组件的IC器件组件的侧视截面图。

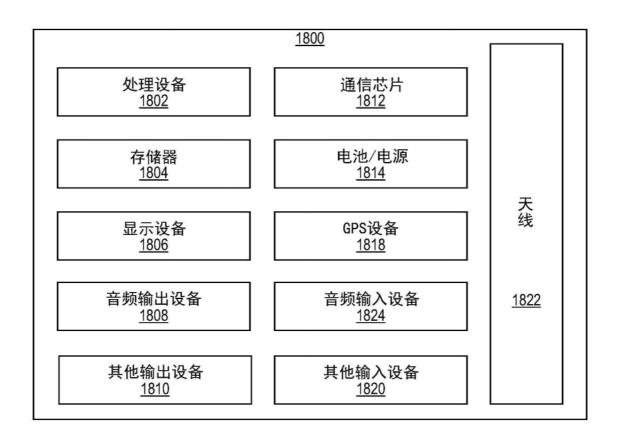

[0013] 图11是可以包括根据本文公开的任何实施例的微电子组件的示例电气设备的框图。

### 具体实施方式

[0014] 本文公开了包括通过直接接合区域耦合在一起的微电子部件的微电子组件(其中 无机电介质填充材料设置在微电子部件周围),以及相关的结构和技术。例如,在一些实施 例中,微电子组件可以包括中介层,其具有第一表面和相对的第二表面;第一微电子部件, 通过第一直接接合区域耦合到中介层的第二表面;第二微电子部件,通过第二直接接合区 域耦合到中介层的第二表面;衬垫材料,在中介层的第二表面上并在第一微电子部件和第二微电子部件周围;以及无机电介质材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间。在一些实施例中,微电子组件可包括中介层,其具有第一表面和相对的第二表面;第一微电子部件,通过第一直接接合区域耦合到中介层的第二表面;第二微电子部件,通过第二直接接合区域耦合到中介层的第二表面;对垫材料,在中介层的第二表面上并在第一微电子部件和第二微电子部件周围;以及导热填充材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间。

[0015] 在以下详细描述中,参考形成其一部分的附图,其中类似的附图标记始终表示类似的部分,并且在附图中通过说明示出了可实施的实施例。应当理解,在不脱离本公开内容的范围的情况下,可以利用其他实施例,并且可以进行结构或逻辑改变。因此,以下具体实施方式不应被理解为限制性的。

[0016] 可以以最有助于理解所要求保护的主题的方式将各种操作依次描述为多个分立的动作或操作。然而,描述的顺序不应被解释为暗示这些操作必须是顺序相关的。特别地,可以不以所呈现的顺序执行这些操作。所描述的操作可以以与所描述的实施例不同的顺序来执行。在另外的实施例中,可以执行各种另外的操作,和/或可以省略所描述的操作。

[0017] 对于本公开内容,短语"A和/或B"和"A或B"是指(A)、(B)或(A和B)。对于本公开内容,短语"A、B和/或C"和"A、B或C"是指(A)、(B)、(C)、(A和B)、(A和C)、(B和C)或(A、B和C)。附图不一定是按比例的。尽管许多附图示出了具有平坦壁和直角拐角的直线结构,但这仅仅是为了便于说明,并且使用这些技术制造的实际器件将表现出圆角、表面粗糙度和其他特征。

[0018] 本说明书使用短语"在一个实施例中"或"在实施例中",其可各自指代相同或不同实施例中的一个或多个。此外,如关于本公开内容的实施例所使用的术语"包括"、"包含"、"具有"等是同义的。当用于描述尺寸范围时,短语"在X和Y之间"表示包括X和Y的范围。术语"顶部"、"底部"等可在本文中用于解释附图的各种特征,但这些术语仅是为了便于论述,且并不暗示所要或所需的定向。尽管在本文中可能以单数形式提及某些元件,但是这样的元件可以包括多个子元件。例如,"电介质材料"可以包括一种或多种电介质材料。如本文所用,"导电触点"可指导电材料(例如,金属)的一部分,其用作不同部件之间的电接口;导电触点可以凹入元件的表面、与元件的表面齐平、或从元件的表面延伸出去,并且可以采用任何合适的形式(例如,导电焊盘或插座,或导电线或过孔的一部分)。为了便于讨论,图3A-3G的附图在本文中可被称为"图3"。

[0019] 用于不同半导体节点的管芯的异构集成以创建复合管芯的常规技术通常包括将一个管芯或多个管芯热压接合或大量回流至不同节点的晶圆,并且提供底部填充材料和/或模制材料以使得能够进行后续处理,诸如穿衬底过孔(TSV)显露(reveal)和受控塌陷芯片连接(C4)凸块形成。使用低温聚合物电介质作为底部填充和/或模制材料严格地限制了复合管芯的后续处理可以达到的温度,以避免电介质的除气、过度软化或退化,这可能导致对单独管芯和/或对管芯和晶圆之间的互连的损坏。使用低温聚合物电介质可能导致极端的晶圆弯曲(例如,弯曲大于800微米),这使得在处理期间晶圆操作(wafer handling)极具挑战性。此外,低温聚合物电介质的使用可能由于阻止热量从热源传递出去而降低性能。本文公开的微电子组件和方法提供了改进的材料和结构,其使得复合管芯能够由无机材料制

成,所述无机材料可暴露于高温下并允许更好的散热,并且在处理期间可更容易地操作,以允许相对于常规方法更简化的制造。

[0020] 图1是根据各种实施例的微电子组件100的侧视截面图。微电子组件100可包括中介层150、第一微电子部件102-1、第二微电子部件102-2、第三微电子部件102-3、衬垫材料132、部件间填充材料126、支撑部件182和底部填充材料138。中介层150包括第一表面151-1(即,底表面)和相对的第二表面151-2(即,顶表面)。

微电子组件100可包括通过直接接合(DB)区域130-1耦合到微电子部件102-1并通 过DB区域130-2耦合到微电子部件102-2的中介层150。特别地,如图2中所示,DB区域130-1 可以包括在中介层150的顶表面151-2处的DB界面180-1A,其中DB界面180-1A包括一组导电 DB触点110以及在DB界面180-1A的DB触点110周围的DB电介质108。DB区域130-1还可以包括 在微电子部件102-1的底表面处的DB界面180-1B,其中DB界面180-1B包括一组DB触点110以 及在DB界面180-1B的DB触点110周围的DB电介质108。中介层150的DB界面180-1A的DB触点 110可以与微电子部件102-1的DB界面180-1B的DB触点110对准,使得在微电子组件100中, 微电子部件102-1的DB触点110与中介层150的DB触点110接触。在图1的微电子组件100中, 可以将中介层150的DB界面180-1A与微电子部件102-1的DB界面180-1B(例如,电和机械地) 接合,以形成耦合中介层150和微电子部件102-1的DB区域130-1。如图2中进一步所示,可以 通过DB区域130-2(经由DB界面180-2A和180-2B)将微电子部件102-2耦合到中介层150。更 一般地,本文公开的DB区域130可以包括接合在一起的两个互补DB界面180;为了易于说明, 许多随后的附图可以省略DB界面180的标识以提高附图的清晰度。尽管图1和2将第一微电 子部件和第二微电子部件示出为单面的(在个体微电子部件102仅在个体微电子部件102的 单个表面上具有导电触点(例如,DB触点110)的意义上),但是微电子部件102可以是双面的 (在个体微电子部件102可以在个体微电子部件102的多个表面上具有导电触点的意义上)。 微电子组件100还可包括通过熔融接合区域和/或通过直接接合区域耦合到第一 微电子部件102-1和第二微电子部件102-2的第三微电子部件102-3,如下面参考图4所述。 在一些实施例中,如图1所示,第三微电子部件102-3可以不包括底表面上的导电结构(例 如,可以是空白的或无源的),使得第三微电子部件102-3的底表面上的电介质经由熔融接 合耦合到部件间填充材料126和单面第一微电子部件102-1与单面第二微电子部件102-2。 在这样的实施例中,第三微电子部件102-3还可以包括无源散热特征或结构,以引导和扩散 来自第一微电子部件102-1和第二微电子部件102-2的热。在一些实施例中,如图5所示,第 三微电子部件102-3可包括在底表面和/或顶表面上的导电结构(例如,可以是有源晶圆或 管芯),使得第三微电子部件102-3的底表面上的导电触点和/或电介质材料经由直接接合 耦合到双面第一微电子部件102-1和第二微电子部件102-2的顶表面上的导电触点。

[0023] 如本文所使用的,术语"直接接合"用于包括金属至金属接合技术(例如,铜至铜接合,或者其中首先使相对DB界面180的DB触点110接触、然后经受加热和/或压缩的其他技术)以及混合接合技术(例如,其中首先使相对DB界面180的DB电介质108接触、然后经受加热并且有时经受压缩的技术,或者其中基本上同时使相对DB界面180的DB触点110和DB电介质108接触、然后经受加热和压缩的技术)。在这样的技术中,使一个DB界面180处的DB触点110和DB电介质108分别与另一DB界面180处的DB触点110和DB电介质108接触,并且可以施加升高的压力和/或温度以使得接触的DB触点110和/或接触的DB电介质108接合。在一些实

施例中,可以在不使用中间焊料或各向异性导电材料的情况下实现该接合,而在一些其他实施例中,可以在DB互连中使用焊料的薄盖以适应平坦性,并且在处理期间,该焊料可以变成DB区域130中的金属间化合物(IMC)。DB互连可能能够比其他类型的互连可靠地传导更高的电流;例如,一些常规的焊料互连在电流流动时可能形成大量的易碎IMC,并且可能限制通过这样的互连提供的最大电流以减轻机械故障。如本文所用,术语"熔融接合"是指电介质-电介质接合技术(例如,其中使相对界面的电介质接触,然后经受加热并且有时经受压缩的技术)。

[0024] DB电介质108可以包括一种或多种电介质材料,诸如一种或多种无机电介质材料。例如,DB电介质108可以包括硅和氮(例如,以氮化硅的形式);硅和氧(例如,以氧化硅的形式);硅、碱和氮(例如,以碳氮化硅形式);碳和氧(例如,以碳掺杂氧化物的形式);硅、氧和氮(例如,以氮氧化硅的形式);铝和氧(例如,以氧化铝的形式);钛和氧(例如,以氧化钛的形式);铅和氧(例如,以氧化铅的形式);硅、氧、碳和氢(例如,以原硅酸四乙酯(TEOS)的形式);锆和氧(例如,以氧化锆的形式);铌和氧(例如,以氧化铌的形式);或钽和氧(例如,以氧化钽的形式);以及它们的组合。在一些实施例中,DB电介质108是与中介层150和微电子部件102的材料相同的材料,使得DB电介质108是相应中介层150或相应微电子部件102的集成部分(例如,DB电介质108可以或者可以不被沉积为单独的材料层)。在一些实施例中,DB电介质108是与中介层150和/或微电子部件102的材料不同的材料,使得DB电介质108作为单独的材料层沉积在相应的中介层150和/或相应的微电子部件102上。

[0025] 图1的微电子组件100还可包括部件间填充材料126。部件间填充材料126可以在中介层150上的一个或多个微电子部件102之间(例如,周围)延伸。在一些实施例中,部件间填充材料126可以在中介层150上的多个微电子部件102之间并且在DB区域130周围延伸。在一些实施例中,部件间填充材料126可以在中介层150(未示出)上的一个或多个微电子部件102上方延伸。部件间填充材料126可以在中介层150(未示出)上的一个或多个微电子部件102上方延伸。部件间填充材料126可以是无机电介质材料,诸如硅和氮(例如,以氮化硅的形式)或硅和氧(例如,以氧化硅的形式)以及其组合。可以使用任何合适的技术沉积部件间填充材料126,例如化学气相沉积(CVD)、原子层沉积(ALD)、等离子体增强化学气相沉积(PECVD)、旋涂或真空层压。部件间填充材料126可具有10微米和250微米之间的厚度。部件间填充材料126可以包括单层或者可以包括多层。沉积工艺可被调整以优化部件间填充材料126的机械和电气性质(例如,孔隙率和收缩率)。在一些实施例中,部件间填充材料126可以延伸到微电子部件102并且可以横向地围绕微电子部件102,并且在一些实施例中(未示出),部件间填充材料126可以覆盖微电子部件102的顶表面。如本文所用,术语"部件间填充材料"、"部件间填充材料"、"管芯间材料"、"恒隙材料"、"填充材料"和"微电子部件周围的电介质材料……"可互换使用。在一些实施例中,可以至少部分地针对其热特性来选择在微电子组件100中使用的部件间填充材料126,以促进热传递(例如,如下面参照图7所述)。

[0026] 图1的微电子组件100还可包括衬垫材料132。衬垫材料132可以设置在中介层150的DB电介质108上以及第一微电子部件102-1和第二微电子部件102-2上和周围。衬垫材料132可以用作中介层150的有源表面(例如,中介层150的第二表面151-2上的导电触点(未示出)和电介质)以及微电子部件102-1、102-2的所有刻面(facet)(例如,侧表面和顶表面)的蚀刻停止层或密封阻挡层,以限制导电触点和相邻电介质的扩散(例如,当DB触点110包括铜并且DB电介质108包括氧化硅时可能发生的铜扩散)。在一些实施例中,衬垫材料132可包

括硅、碳和氮 (例如,以硅碳氮化物的形式)、硅和氮 (例如,以氮化硅的形式)、硅、氧和氮 (例如,以氮氧化硅的形式)或硅和碳 (例如,以碳化硅的形式)以及其组合。可使用任何合适的技术 (例如,CVD、ALD或PECVD)来沉积衬垫材料132。在沉积期间,可以调整工艺的温度、压力和功率以调节膜的应力以及中介层150以及第一微电子部件102-1和第二微电子部件102-2上的后续应力。衬垫材料132可具有在10纳米与2000纳米之间的厚度。在一些实施例中,衬垫材料132的厚度可以变化 (例如,衬垫材料132可以在中介层150和微电子部件102的顶表面上较厚,而在微电子部件102的侧壁上较薄)。

[0027] 中介层150可以被称为"底部管芯"或"基底晶圆"。中介层150可包括绝缘材料106(例如,如本领域中已知的,在多个层中形成的一个或多个电介质材料)以及穿过绝缘材料106的一个或多个导电路径112(例如,包括导电线114和/或导电过孔116,如图所示)。在一些实施例中,中介层150的绝缘材料106包括无机电介质材料,诸如硅和氮(例如,以氮化硅的形式);硅和氧(例如,以氧化硅的形式);硅和碳(例如,以碳化硅的形式);硅、碳和氧(例如,以碳氧化硅的形式);硅、碳和氮(例如,以碳氮化硅的形式);碳和氧(例如,以碳掺杂氧化物的形式);战及它们的组合。在一些实施例中,中介层150的绝缘材料106包括绝缘金属氧化物,诸如铝和氧(例如,以氧化铝的形式);钛和氧(例如,以氧化钛的形式);铪和氧(例如,以氧化铅的形式);锆和氧(例如,以氧化铅的形式);铌和氧(例如,以氧化铌的形式);或但和氧(例如,以氧化铅的形式);以及它们的组合。在一些实施例中,中介层150可以是基于半导体(例如,基于硅)或基于玻璃的。在一些实施例中,中介层150是硅晶圆或管芯。在一些实施例中,中介层150可以是绝缘体上硅(S0I),并且还可以包括硅和锗(例如,以硅锗的形式)、镓和氮(例如,以氮化镓的形式)、铟和磷(例如,以磷化铟的形式)等的层。

[0028] 在一些实施例中,中介层150的绝缘材料106可以是有机材料,诸如聚酰亚胺或聚 苯并恶唑,或者可以包括具有填充材料(其可以是无机的,诸如氮化硅、氧化硅或氧化铝)的 有机聚合物基质(例如,环氧化物)。在一些这样的实施例中,中介层150可被称为"有机中介 层"。在一些实施例中,中介层150的绝缘材料106可被设置在多层有机堆积膜中。有机中介 层150可以比基于半导体或玻璃的中介层制造起来更便宜,并且由于有机绝缘材料106的低 介电常数和可以使用的更粗的线而可以具有电性能优点(允许改进的电力输送、信号传输 和潜在的热益处)。有机中介层150也可以具有比基于半导体的中介层所能实现的更大的覆 盖区域,这受到用于图案化的中间掩模(reticle)的尺寸的限制。此外,有机中介层150可以 受制于比约束基于半导体或玻璃的中介层的那些设计规则更少约束的设计规则,从而允许 使用诸如非曼哈顿布线的设计特征(例如,不限于使用一层用于水平互连,而使用另一层用 于垂直互连)以及避免诸如穿硅过孔或穿玻璃过孔的穿衬底过孔(TSV)(其可能受限于可实 现的间距,并且可能导致不太期望的功率传送和信号传输性能)。包括有机中介层的常规集 成电路封装已经被限制于基于焊料的附接技术,其可能对可实现的间距具有下限,这排除 了使用常规的基于焊料的互连来实现下一代器件所期望的精细间距。如本文所公开的,在 具有直接接合的微电子组件100中利用有机中介层150可以结合通过直接接合可实现的(并 且先前仅在使用基于半导体的中介层时可实现的)超精细间距(例如,下面讨论的间距128) 来利用有机中介层的这些优点,并且因此可以支持大且复杂的管芯复合体的设计和制造, 该管芯复合体可以实现常规方法不能实现的封装系统竞争性能和能力。

[0029] 在其他实施例中,中介层150的绝缘材料106可包括阻燃等级4材料(FR-4)、双马来 酰亚胺三嗪(BT)树脂、或低k或超低k电介质(例如,碳掺杂电介质、氟掺杂电介质、和多孔电介质)。当使用标准印刷电路板(PCB)工艺形成中介层150时,绝缘材料106可包括FR-4,并且中介层150中的导电路径112可由通过FR-4的堆积层分离的图案化铜片形成。在一些这样的实施例中,中介层150可被称为"封装衬底"或"电路板"。

[0030] 在一些实施例中,中介层150中的导电路径112中的一个或者多个可以在中介层150的顶表面处的导电触点(例如DB触点110之一)与中介层150的底表面处的导电触点118之间延伸。在一些实施例中,中介层150中的导电路径112中的一个或者多个可以在中介层150的顶表面处的不同导电触点之间(例如,在潜在地在不同DB区域130中的不同DB触点110之间,如下面进一步讨论的)延伸。在一些实施例中,中介层150中的导电路径112中的一个或多个可在中介层150的底表面处的不同导电触点118之间延伸。

[0031] 在一些实施例中,中介层150可以仅包括导电路径112,并且可以不包含有源或无源电路。在其他实施例中,中介层150可以包括有源或无源电路(例如,晶体管、二极管、电阻器、电感器和电容器等)。在一些实施例中,中介层150可以包括一个或多个器件层,所述器件层包括晶体管。

在一些实施例中,微电子部件102可以包括IC管芯(封装的或未封装的)或IC管芯 的堆叠体(例如,高带宽存储器管芯堆叠体)。在一些这样的实施例中,微电子部件102的绝 缘材料可以包括二氧化硅、氮化硅、氮氧化物、聚酰亚胺材料、玻璃增强环氧树脂基质材料、 或低k或超低k电介质(例如,碳掺杂电介质、氟掺杂电介质、多孔电介质、有机聚合物电介 质、光可成像电介质、和/或基于苯并环丁烯的聚合物)。在一些进一步的实施例中,微电子 部件102的绝缘材料可包括半导体材料,例如硅、锗或III-V族材料(例如氮化镓),以及一种 或多种附加材料。例如,微电子部件102的绝缘材料可以包括氧化硅或氮化硅。微电子部件 102中的导电路径可以包括导电线和/或导电过孔,并且可以以任何合适的方式连接微电子 部件102中的任何导电触点(例如,连接微电子部件102的相同表面上或不同表面上的多个 导电触点)。下面参照图9讨论可以包括在本文公开的微电子部件102中的示例结构。特别 地,微电子部件102可以包括有源和/或无源电路(例如,晶体管、二极管、电阻器、电感器和 电容器等)。在一些实施例中,微电子部件102可以包括一个或多个器件层,所述器件层包括 晶体管。当微电子部件102包括有源电路时,电源和/或接地信号可以通过中介层150传送, 并且通过DB区域130(并且进一步通过中间微电子部件102)往/来于微电子部件102传送。在 一些实施例中,微电子部件102可以采取本文的中介层150的任何实施例的形式。尽管图1的 微电子组件100的微电子部件102是单面部件,但是在一些实施例中,微电子部件102可以是 双面(或"多层"或"全向")部件,其中在部件的多个表面上具有导电触点。下面参考图5讨论 双面微电子部件102的特定示例。

[0033] DB触点110可以包括柱、焊盘或其他结构。尽管在附图中以相同方式在DB区域130的两个DB界面180处示出DB触点110,但是DB触点110可以在两个DB界面180处具有相同结构,或者在不同DB界面180处的DB触点110可以具有不同结构。例如,在一些实施例中,一个DB界面180中的DB触点110可以包括金属柱(例如,铜柱),并且互补DB界面180中的互补DB触点110可以包括凹陷在电介质中的金属焊盘(例如,铜焊盘)。DB触点110可以包括任何一种或多种导电材料,例如铜、锰、钛、金、银、钯、镍、铜和铝(例如,以铜铝合金的形式)、钽(例

如,钽金属、或氮化钽的形式的钽和氮)、钴、钴和铁(例如,以钴铁合金的形式)、或任何前述材料的任何合金(例如,锰化合物的形式的铜、锰和镍)。下面参照图3讨论DB触点110中的多种材料的一些特定布置。在一些实施例中,DB电介质108和DB界面180的DB触点110可以使用低温沉积技术(例如,在低于250摄氏度或低于200摄氏度的温度下进行沉积的技术),诸如低温等离子体增强化学气相沉积(PECVD)来制造。

[0034] 尽管图1示出了通过DB区域130耦合到中介层150的特定数量的微电子部件102,但是该数量和布置仅是说明性的,并且微电子组件100可以包括通过DB区域130耦合到中介层150的任何期望数量和布置的微电子部件102。尽管单个附图标记"108"用于指代多个不同DB界面180(以及不同DB区域130)的DB电介质,但是这仅是为了易于图示,不同DB界面180(甚至在单个DB区域130内)的DB电介质108可以具有不同材料和/或结构。类似地,尽管单个附图标记"110"用于指代多个不同DB界面180(以及不同DB区域130)的DB触点,但是这仅是为了易于图示,不同DB界面180(甚至在单个DB区域130内)的DB触点110可以具有不同材料和/或结构。在图1和2中,DB触点110被示出为与下面的绝缘材料106中的过孔116接触的焊盘。在其他实施例中,DB触点110本身可以是过孔。例如,在DB触点110是与绝缘材料106中的焊盘接触的过孔的实施例中,DB触点110可以比与它们接触的焊盘窄。

[0035] 微电子组件100中的不同DB区域130可以包括不同的DB电介质108。例如,在微电子组件100中,DB区域130-1包括DB电介质108-1,DB区域130-2包括不同的DB电介质108-2。DB电介质108-1和108-2可以在它们的材料成分和/或它们的结构方面不同。在一些实施例中,可以将不同DB区域130中的DB电介质108选择为具有不同的热导率,从而促进和/或限制在中介层150与微电子部件102之间的热传递。例如,DB电介质108-1可以具有比DB电介质108-2更高的热导率,从而导致在微电子部件102-1与中介层150之间的热传递大于在微电子部件102-2与中介层150之间的热传递。在一些这样的实施例中,DB电介质108-1可以包括硅和氮(例如,以氮化硅的形式),而DB电介质108-2可以包括硅和氧(例如,以氧化硅的形式);氮化硅可以具有比氧化硅更高的热导率,因此,使用氮化硅作为DB电介质108-1可以增强从微电子部件102-1到中介层150的局部热传递,而使用氧化硅作为DB电介质108-2可以减轻通过中介层150在微电子部件102-1与微电子部件102-2之间的热串扰。在图1和2的实施例中,DB电介质108延伸到DB区域130外部,覆盖中介层150的顶表面的剩余部分。在其他实施例中,可以在DB区域130外部的中介层150的顶表面处设置不同的材料(例如,与部件间填充材料126接触)。

[0036] 在一些实施例中,DB触点110的密度(即,DB界面180的接合表面的由DB触点110占据的面积的比例)可以在不同的DB区域130之间不同。在一些实施例中,该不同密度可以是由于一个DB区域130比另一DB区域130需要更少的电路径。在其他实施例中,这种不同的密度可以用于增强或抑制热传递,其中,DB触点110的较大密度(因此,较高比例的导热金属)用于增强热传递,而DB触点110的较小密度(因此,较低比例的导热金属)用于抑制热传递。例如,DB区域130-1中的DB触点110的密度可以大于DB区域130-2中的密度,以增强微电子部件102-1与中介层150之间的热传递,并且减少微电子部件102-2与中介层150之间的热传递。在一些实施例中,两个DB区域130可以具有不同密度的DB触点110,同时具有相同材料成分的DB电介质108。

[0037] 诸如表面安装电阻器、电容器和/或电感器的附加部件(未示出)可以被设置在中

介层150的顶表面或底表面上,或者被嵌入中介层150中。图1的微电子组件100还包括耦合到中介层150的支撑部件182。在图1的特定实施例中,支撑部件182包括通过中间焊料120 (例如,球栅阵列(BGA)布置中的焊球)电耦合到中介层150的互补导电触点118的导电触点118,但是可以使用任何合适的互连结构(例如,针栅阵列布置中的引脚、连接盘栅格阵列布置中的连接盘、柱、焊盘和柱等)。在本文中公开的微电子组件100中使用的焊料120可以包括任何合适的材料,例如铅/锡、锡/铋、共晶锡/银、三元锡/银/铜、共晶锡/铜、锡/镍/铜、锡/铋/铜、锡/银/铜、锡/锌/铟/铋或其他合金。在一些实施例中,中介层150与支撑部件182之间的耦合可被称为第二级互连(SLI)或多级互连(MLI)。

[0038] 在一些实施例中,支撑部件182可以是封装衬底(例如,可以使用PCB工艺制造,如上所述)。在一些实施例中,支撑部件182可以是电路板(例如,母板),并且可以具有附接到其的其他部件(未示出)。支撑部件182可以包括导电路径和其他导电触点(未示出),用于通过支撑部件182传送电源、接地和信号,如本领域已知的。在一些实施例中,支撑部件182可以包括另一IC封装、中介层或任何其他合适的部件。底部填充材料138可以设置在焊料120、中介层150、部件间填充材料126以及将包括微电子部件102的中介层150耦合到支撑部件182的微电子部件102-3的至少一部分周围。在一些实施例中,底部填充材料138可以包括环氧树脂材料。

[0039] 在一些实施例中,支撑部件182可以是较低密度部件,而中介层150和/或微电子部件102可以是较高密度部件。如本文所用,术语"较低密度"和"较高密度"是相对术语,其指示较低密度部件中的导电路径(例如,包括导电线和导电过孔)比较高密度部件中的导电路径更大和/或具有更大间距。在一些实施例中,微电子部件102可以是较高密度部件,而中介层150可以是较低密度部件。在一些实施例中,较高密度部件可以使用双镶嵌或单镶嵌工艺(例如,当较高密度部件是管芯时)来制造,而较低密度部件可以使用半加成或修改的半加成工艺(其中通过先进的激光或光刻工艺形成小的垂直互连特征)来制造(例如,当较低密度部件是封装衬底或中介层时)。在一些其他实施例中,较高密度部件可以使用半加成或者修改的半加成工艺(例如,当较高密度部件是封装衬底或者中介层时)来制造,而较低密度部件可以使用半加成或者减成工艺(使用蚀刻化学物质来去除不想要的金属的区域,并且其中通过标准激光工艺形成粗糙垂直互连特征)来制造(例如,当较低密度部件是PCB时)。

[0040] 图1的微电子组件100还可包括热界面材料(TIM)(未示出)。TIM可包括聚合物或其他接合剂中的导热材料(例如,金属颗粒)。TIM可以是热界面材料糊剂或导热环氧树脂(如本领域已知的,当施涂时可以是流体状或粘性的,并且在固化时可以硬化)。TIM也可以包含焊接材料(例如铟)。TIM可为微电子部件102所产生的热提供路径,使其容易地流到传热结构,在传热结构处可将其扩散和/或消散。

[0041] 图1的微电子组件100还可包括传热结构(未示出)。传热结构可用于将热从一个或多个微电子部件102移走(例如,使得热可更容易地消散)。传热结构可以包括任何合适的导热材料(例如,金属、适当的陶瓷等),并且可以包括任何合适的特征(例如,散热器、包括翅片的热沉、冷板等)。在一些实施例中,传热结构可以是或可以包括集成散热器(IHS)。

[0042] 微电子组件100的元件可具有任何合适的尺寸。仅附图的子集被标记有表示尺寸的附图标记,但这仅是为了图示清楚,并且本文公开的任何微电子组件100可具有本文讨论的尺寸的部件。在一些实施例中,中介层150的厚度184可以在20微米与200微米之间。在一

些实施例中,DB区域130的厚度188可以在50纳米与5微米之间。在一些实施例中,微电子部件102的厚度190可以在5微米与800微米之间。在一些实施例中,微电子部件102的厚度190可以在5微米与250微米之间。在一些实施例中,微电子部件102的厚度190可以小于40微米(例如,在5微米与40微米之间)。在一些实施例中,DB区域130中的DB触点110的间距128可以小于20微米(例如,在0.1微米与20微米之间)。

[0043] 图1中示出了包括在微电子组件100中的多个元件,但是在微电子组件100中可以不存在多个这些元件。例如,在各种实施例中,可以不包括微电子部件102-3、底部填充材料138和/或支撑部件182。此外,图1示出了为了易于图示而从随后的附图中省略的多个元件,但是这些元件可以包括在本文公开的任何微电子组件100中。这种元件的示例包括底部填充材料138和/或支撑部件182。图1的微电子组件100的许多元件包括在附图中的其他附图中;当讨论这些附图时,不再重复讨论这些元件,并且这些元件中的任何一个可以采取本文公开的任何形式。在一些实施例中,本文公开的微电子组件100中的微电子组件中的个体微电子组件可以用作系统级封装(SiP),其中包括具有不同功能的多个微电子部件102。在这样的实施例中,微电子组件100可以被称为SiP。虽然图1和2(以及其他附图)示出了中介层150中的导电路径112的特定数量和布置,但是这些仅仅是示例性的,并且可以使用任何合适的数量和布置。本文所公开的导电路径112(例如,包括线114和/或过孔116)可以由任何适当的导电材料形成,例如铜、银、镍、金、铝、其他金属或合金、或材料的组合。

[0044] 本文公开的微电子组件100可以以任何合适的方式制造。例如,图3A-3G是根据各种实施例的图1和2的微电子组件100的一部分的制造中的示例阶段的侧视截面图。尽管参考图3A-3G讨论的操作可以参考在本文中公开的微电子组件100的特定实施例来说明,但是参考图3A-3G讨论的制造方法可以用于形成任何合适的微电子组件100,在图3A-3G中,操作每次以特定顺序示出一次,但是操作可以根据需要重新排序和/或重复(例如,当同时制造多个微电子组件100时,并行执行不同的操作)。然而,任何合适的制造工艺可以用于制造本文公开的任何微电子组件100。

[0045] 图3A示出了包括两个暴露的DB界面180-1和180-2的中介层150。在一些实施例中,中介层150可以安装在载体(未示出)上。载体可以包括任何合适的材料以提供机械支撑和稳定性,例如玻璃面板。在一些实施例中,中介层可以包括半导体晶圆(例如,硅晶圆)。

[0046] 图3B示出了将微电子部件102-1和102-2直接接合到图3A的中介层150之后的组件。特别地,可以使微电子部件102的DB界面180(未标记)与中介层150的DB界面180接触,并且可以施加热和/或压力以接合接触的DB界面180,以形成DB区域130(其中DB区域130-1和130-2分别对应于DB界面180-1和180-2)。

[0047] 图3C示出了在减薄微电子部件102之后的组件。可以使用任何合适的技术,包括例如机械研磨和化学机械平坦化(CMP),来减薄和平坦化微电子部件102。在一些实施例中,微电子部件102被减薄到5微米与250微米之间的厚度。在一些实施例中,微电子部件102被减薄到小于40微米的厚度。在一些实施例中,在减薄之前,可以在微电子部件102周围沉积临时的、可去除的保护材料,以有助于减薄工艺的均匀性。在一些实施例中,减薄工艺可以包括干法等离子体蚀刻(例如SF6)或通过定时蚀刻或利用蚀刻停止层(例如氧化硅)的湿法蚀刻(例如使用氢氧化钾或四甲基氢氧化铵溶液)。在一些实施例中,减薄工艺可以包括氢注入和离子切割方法。在一些实施例中,减薄工艺还可以包括产生微裂纹以使硅中的金属迁

移最小化(例如,类似于吸杂抛光)。

[0048] 图3D示出了在图3C的组件的微电子部件102周围和中介层150的表面上提供衬垫材料132之后的组件。可使用任何合适的技术来沉积衬垫材料132,包括(例如)CVD、ALD或PECVDT艺。

[0049] 图3E示出了在衬垫材料132上提供部件间填充材料126之后的组件。可以使用任何合适的技术来沉积部件间填充材料126,包括例如PECVD工艺或旋涂以及随后的热退火工艺。在一些实施例中,部件间填充材料126可以在微电子部件102上方延伸并保持在其上方,而在其他实施例中,部件间填充材料126可以被抛光以暴露微电子部件102的顶表面上的衬垫材料132,如图所示。在一些实施例中,可以使用CMP来平坦化部件间填充材料126,并且可以执行后续半导体处理,例如镶嵌处理或半加成处理,如下面参考图5所述。

[0050] 图3F示出了在将第三微电子部件102-3耦合到部件间填充材料126以及第一微电子部件102-1和第二微电子部件102-2上之后的组件。第三微电子部件102-3可经由如下参考图4所述的熔融集合或直接接合而耦合到组件。第三微电子部件102-3可以被称为"操作管芯(handle die)"。图3F的组件本身可以是微电子组件100,如图所示。可以对图3F的微电子组件100执行进一步的制造操作以形成其他微电子组件100;例如,如图3G所示。图3F的组件可以类似于单片晶圆在机械上起作用。

[0051] 图3G示出了在导电触点118上提供焊料120之后的组件,使用焊料120将图3F的微电子组件100耦合到支撑部件182,并在焊料120周围提供底部填充材料138并延伸到第三微电子部件102-3,形成图1的微电子组件100。当使用载体时,在导电触点118上提供焊料120之前去除载体。

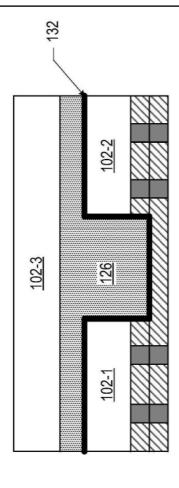

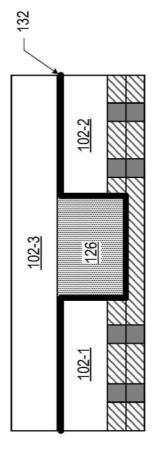

[0052] 图4A-4D是根据各种实施例的示出了示例接合界面的图3G的虚线部分的侧视截面放大图。图4A示出了第一微电子部件102-1和第二微电子部件102-2与第三微电子部件102-3之间的具有单一材料类型界面的界面的一部分。如图4A所示,部件间填充材料126围绕并覆盖第一微电子部件102-1和第二微电子部件102-2的顶表面,使得第三微电子部件102-3仅与部件间填充材料126界面连接,以产生单熔融接合界面。

[0053] 图4B示出了第一微电子部件102-1和第二微电子部件102-2与第三微电子部件102-3之间的具有混合材料型界面的界面的一部分。如图4B所示,部件间填充材料126围绕第一微电子部件102-1和第二微电子部件102-2(例如,填充第一微电子部件102-1和第二微电子部件102-2之间的空间但不覆盖其顶表面),且衬垫材料132覆盖第一微电子部件102-1和第二微电子部件102-2的顶表面,使得第三微电子部件102-3与部件间填充材料126和衬垫材料132界面连接,以产生混合熔融接合界面。

[0054] 图4C示出了第一微电子部件102-1和第二微电子部件102-2与第三微电子部件102-3之间的具有另一单一材料类型界面的界面的一部分。如图4C所示,部件间填充材料126围绕第一微电子部件102-1和第二微电子部件102-2(例如,填充第一微电子部件102-1和第二微电子部件102-2(例如,填充第一微电子部件102-1和第二微电子部件102-2以及部件间填充材料132-2)覆盖第一微电子部件102-1和第二微电子部件102-2以及部件间填充材料126的顶表面,使得第三微电子部件102-3仅与第二衬垫材料132-2界面连接,以产生单熔融接合界面。在这种界面中,沉积第一衬垫材料132-1,沉积部件间填充材料126,且接着沉积第二衬垫材料132-2。在一些实施例中,第一衬垫材料132-1和第二衬垫材料132-2为相同材

料。在一些实施例中,第一衬垫材料132-1不同于第二衬垫材料132-2。

[0055] 图4D示出了第一微电子部件102-1和第二微电子部件102-2与第三微电子部件102-3之间的具有又一单一材料类型界面的界面的一部分。如图4D所示,材料层134沉积在第一微电子部件102-1和第二微电子部件102-2周围的部件间填充材料126上以及覆盖第一微电子部件102-1和第二微电子部件102-2的顶表面的衬垫材料132上,使得第三微电子部件102-3仅与材料层134界面连接,以产生单熔融接合界面。在一些实施例中,材料层134可包括硅、碳和氮(例如,以硅碳氮化物的形式)、硅和氮(例如,以氮化硅的形式)、硅、氧和氮(例如,以氮氧化硅的形式)、硅和碳(例如,以碳化硅的形式)、硅、氧、碳和氢(例如,以原硅酸四乙酯(TEOS)的形式)等。

[0056] 微电子组件100可包括通过至少一个直接接合区域耦合的多"层"微电子部件102。 例如,图5示出了微电子组件100,其中微电子部件102-1、102-2包括在顶表面和底表面上的 导电触点(未标记),其中底表面上的导电触点直接接合到中介层150,顶表面上的导电触点 直接接合到微电子部件102-3。在微电子部件102-1、102-2在底表面上与中介层150直接接 合并且在顶表面上与微电子部件102-3直接接合的实施例中,图5的微电子组件100可被描 述为具有两层直接接合的微电子部件102。在中介层150是有源中介层(例如,有源晶圆或有 源管芯)的实施例中,图5的微电子组件100可被描述为"三层有源管芯复合物",并且顶部管 芯(例如,微电子部件102-3)可被供电并且可以是功能性的。在这样的实施例中,中介层150 可以被称为第一或底层,第一微电子部件102-1和第二微电子部件102-2可以被称为第二或 中间层,并且第三微电子部件102-3可以被称为顶层或第三层。例如,第三层可以包括较高 功率中央处理单元 (CPU) 或图形处理单元 (GPU) (例如,包括处理电路的有源管芯),第二层 可以包括存储器管芯(例如,包括存储器电路的有源管芯),并且第一层可以包括电力输送 电路并且用于对第二和第三层部件供电。在另一示例中,第三层管芯可以包括具有热电珀 耳帖冷却电路的有源热管理管芯,所述热电珀耳帖冷却电路管理热流和节流以使三层有源 管芯复合物的性能达到最大。更一般地,本文公开的任何微电子部件102可以包括一个或多 个管芯,并且可以具有不同类型的穿通导电互连,诸如铜柱和TSV(例如,穿硅过孔)。

[0057] 在一些实施例中,微电子部件102-1和102-2还可包括在其顶表面与底表面之间延伸的导电结构194,从而为到第三层中的微电子部件102-3的电源、接地和/或信号提供导电路径。在一些实施例中,这样的导电结构194可包括一个或多个TSV,包括导电材料过孔,诸如金属过孔(通过阻挡氧化物与周围的硅或其他半导体材料隔离),诸如当微电子部件102-1和102-2包括硅衬底时的穿硅过孔,或当微电子部件102-1和102-2包括玻璃衬底时的穿玻璃过孔。在一些实施例中,微电子部件102-1和102-2可以是无源的(例如,不包括晶体管)或有源的(例如,包括存储器电路和/或电力输送电路形式的晶体管)。

[0058] 如图5所示,微电子组件100还可包括导电结构193,其在中介层150的第二表面 151-2与第三微电子部件102-3的底表面之间延伸(例如,通过衬垫材料132和部件间填充材料126),从而直接为到第三层中的第三微电子部件102-3的电源、接地和/或信号提供导电路径。

[0059] 图6A示出了在将具有导电结构194的微电子部件102-1、102-2直接接合到中介层 150之后的组件。特别地,可以使微电子部件102的DB界面180(未标记)与中介层150的DB界面180接触,并且可以施加热和/或压力以接合接触的DB界面180,以形成DB区域130(其中DB

区域130-1和130-2分别对应于DB界面180-1和180-2)。

[0060] 图6B示出了在减薄微电子部件102并暴露微电子部件102的顶表面上的导电结构194之后的组件。微电子部件102可以使用任何合适的技术来减薄和平坦化,包括例如以上参考图3C描述的技术。

[0061] 图6C示出了在图6B的组件的微电子部件102周围和中介层150的表面上提供衬垫材料132之后的组件。可使用任何合适的技术(包括(例如)如所描述的技术)来沉积衬垫材料132。

[0062] 图6D示出了在衬垫材料132上提供部件间填充材料126之后的组件。可以使用任何合适的技术来沉积部件间填充材料126,包括例如如上参考图3E所述的技术。可以抛光或蚀刻部件间填充材料126以暴露微电子部件102的顶表面。在一些实施例中,例如,当衬垫材料132包括导电特性时,也去除衬垫材料132。在一些实施例中,例如,当衬垫材料132是绝缘的或帮助防止铜或其他金属的扩散时,不去除衬垫材料132。可以使用CMP来平坦化部件间填充材料126,并且可以执行后续的半导体处理。

[0063] 图6E示出了在穿过部件间填充材料126形成导电结构193以及形成导电结构197以及使用任何合适的技术(例如镶嵌处理)在部件间填充材料126和微电子部件102-1、102-2的顶表面上沉积电介质材料199之后的组件。

[0064] 图6F示出了在将第三微电子部件102-3直接接合到图6E的组件的顶表面之后的组件。图6F的组件本身可以是微电子组件100,如图所示。可以对图6F的微电子组件100执行进一步的制造操作以形成其他微电子组件100;例如,通过在导电触点118上提供焊料120,使用焊料120将图6F的微电子组件100耦合到支撑部件182,并在焊料120周围提供底部填充材料138并延伸到第三微电子部件102-3,可以进一步处理图6F的组件以形成图5的微电子组件。

[0065] 图7是根据各种实施例的微电子组件100的侧视截面图。微电子组件100可包括中 介层150、第一微电子部件102-1、第二微电子部件102-2、衬垫材料132、至少部分地根据其 热特性选择以促进热传递的导热部件间填充材料127、以及至少部分地根据其热特性选择 以促进热传递的导热块体材料103。在一些实施例中,导热部件间填充材料127可包括导热 金属、陶瓷或复合颗粒或材料,包括铜、铝、银、金刚石、石墨烯、硅和碳(例如,以碳化硅的形 式)、硼和氮(例如,以氮化硼的形式)、或铝和氮(例如,以氮化铝的形式)、以及它们的组合。 导热部件间填充材料127可为由第一微电子部件102-1和/或第二微电子部件102-2产生的 热提供扩散和/或消散的路径。导热部件间填充材料127可进一步包括溶剂或聚合物以有助 于材料的可分配性,其可在处理期间(例如,在固化或烧结部件间填充材料之后)消散或不 消散。导热部件间填充材料127可使用任何合适的技术来沉积,例如模板/丝网(stencil/ screen) 印刷、加成制造、电解镀覆、无电镀覆或如上文参照图3E所述的技术。导热部件间填 充材料127可具有10微米和250微米之间的厚度。导热部件间填充材料127可以包括单层或 者可以包括多层。沉积工艺可被调整以优化机械和电气性质(例如,孔隙率和收缩率)并防 止导热部件间填充材料127的空隙。在一些实施例中,可以优化第一微电子部件102-1和第 二微电子部件102-2的厚度以减小部件间空间的深宽比,这可以有助于沉积没有空隙的导 热部件间填充材料127。在一些实施例中,导热部件间填充材料127可以向上延伸并且可以 横向地围绕微电子部件102,并且在一些实施例中(未示出),导热部件间填充材料127可以

覆盖微电子部件102的顶表面。本文提及的任何导热部件间填充材料127可包括具有不同材料成分的一种或多种不同材料。

图7的微电子组件100还可包括至少部分地根据其热特性选择以促进热传递的衬 垫材料132。衬垫材料132可以设置在中介层150的DB电介质108上以及第一微电子部件102-1和第二微电子部件102-2上和周围。衬垫材料132可以用作中介层150的第二表面151-2和 微电子部件102-1、102-2的所有刻面(例如,侧表面和顶表面)的扩散阻挡层,以限制金属物 质的扩散(例如,当部件间填充材料127包括铜时可能发生的铜扩散)和/或作为附着促进剂 (例如,以提高DB电介质108和导热的部件间填充材料127之间、第一微电子部件102-1和第 二微电子部件102-2的顶表面和侧表面与导热部件间填充材料127之间、和/或第一微电子 部件102-1和第二微电子部件102-2的顶表面与导热块体材料103之间的机械界面连接的强 度)。在一些实施例中,衬垫材料132可包括导电材料,例如钛、钽、钒、镍、钌、钴和/或铱。可 用于衬垫材料中的导热材料的其他示例包括但不限于钛和氮(例如,以氮化钛的形式)、钽 和氮(例如,以氮化钽的形式)、钒和镍(例如,以镍钒的形式)或铱和氧(例如,以氧化铱的形 式)以及其组合。在一些实施例中,衬垫材料132可包括非导电材料,例如硅、碳和氮(例如, 以硅碳氮化物的形式)、硅和氮(例如,以氮化硅的形式)、硅和碳(例如,以碳化硅的形式)或 钛和氧(例如,以氧化钛的形式)以及其组合。可使用任何合适的技术(例如,CVD、ALD或 PECVD) 来沉积衬垫材料132。在沉积期间,可以调整工艺的温度、压力和功率以调节膜的应 力以及中介层150以及第一微电子部件102-1和第二微电子部件102-2上的后续应力。衬垫 材料132可具有在10纳米与2000纳米之间的厚度。在一些实施例中,衬垫材料132的厚度可 以变化(例如,衬垫材料132可以在中介层150和微电子部件102的顶表面上较厚,而在微电 子部件102的侧壁上较薄)。图7的微电子组件100可使用任何合适的制造工艺来制造,包括 图3A-3G中描述的工艺。

[0067] 导热块体材料103可以包括导电金属,例如铜、铝或银,或者高导电非金属,例如硅和/或碳(例如硅、碳化硅或金刚石)。在一些实施例中,导热块体材料103可以是膏的形式,其通过在部件间填充材料以及第一微电子部件102-1和第二微电子部件102-2的顶表面上进行分配,然后进行热处理来加成制造。在一些实施例中,导热块体材料103可以由导热金属或非金属颗粒(例如,来自上述材料示例)构成,所述导热金属或非金属颗粒通过在部件间填充材料以及第一微电子部件102-1和第二微电子部件102-2的顶表面上冷喷涂来加成制造。在一些实施例中,导热块体材料103可以是晶圆或管芯(例如,由硅或硅和碳制成)的形式,其使用管芯到晶圆或晶圆到晶圆接合而接合在部件间填充材料以及第一微电子部件102-1和第二微电子部件102-2的顶表面上。导热块体材料103的厚度可以在10微米和650微米之间。

[0068] 本文公开的微电子部件102和微电子组件100可以包括在任何合适的电子部件中。图8-11示出了装置的各种示例,其可以适当地包括或被包括在本文公开的微电子部件102和微电子组件100中的任何一个中。

[0069] 图8是可包括在本文公开的任何微电子部件102中的晶圆1500和管芯1502的俯视图。例如,管芯1502可以用作微电子部件102,或者可以被包括在微电子部件102中。晶圆1500可由半导体材料构成,并且可包括具有形成在晶圆1500的表面上的IC结构的一个或多个管芯1502。每个管芯1502可以是包括任何合适IC的半导体产品的重复单元。在半导体产

品的制造完成之后,晶圆1500可以经历单切工艺,其中管芯1502彼此分离以提供半导体产品的分立"芯片"。管芯1502可以包括一个或多个晶体管(例如,下面讨论的图9的晶体管1640中的一些)和/或支持电路以将电信号传送到晶体管以及任何其他IC部件。在一些实施例中,晶圆1500或管芯1502可以包括存储器器件(例如,随机存取存储器(RAM)器件,诸如静态RAM(SRAM)器件、磁性RAM(MRAM)器件、电阻RAM(RRAM)器件、导电桥接RAM(CBRAM)器件等)、逻辑器件(例如,AND、OR、NAND或NOR门)或任何其他合适的电路元件。这些器件中的多个器件可以组合在单个管芯1502上。例如,由多个存储器器件形成的存储器阵列可形成在与处理设备(例如,图11的处理设备1802)或被配置为将信息存储在存储器器件中或执行存储在存储器阵列中的指令的其他逻辑相同的管芯1502上。

[0070] 图9是可以包括在本文公开的任何微电子部件102中的IC器件1600的侧视截面图。例如,IC器件1600 (例如,作为管芯1502的一部分,如上文参考图8所讨论的)可以用作微电子部件102,或者可以被包括在微电子部件102中。IC器件1600中的一个或多个可以包括在一个或多个管芯1502 (图8)中。IC器件1600可以形成在衬底1602 (例如,图8的晶圆1500)上,并且可以包括在管芯 (例如,图8的管芯1502)中。衬底1602可以是由半导体材料系统构成的半导体衬底,该半导体材料系统包括例如n型或p型材料系统 (或两者的组合)。衬底1602可包括例如使用体硅或绝缘体上硅 (S0I)子结构形成的晶体衬底。在一些实施例中,衬底1602可使用可与硅组合或不与硅组合的替代材料形成,替代材料包括但不限于锗、锑化铟、碲化铅、砷化铟、磷化铟、砷化镓或锑化镓。分类为II-VI族、III-V族或IV族的其他材料也可用于形成衬底1602。尽管此处描述了可以形成衬底1602的材料的几个示例,但是可以使用可以用作IC器件1600的基础的任何材料。衬底1602可以是经单切管芯 (例如,图8的管芯1502)或晶圆 (例如,图8的晶圆1500)的一部分。

[0071] IC器件1600可以包括设置在衬底1602上的一个或多个器件层1604。器件层1604可以包括形成在衬底1602上的一个或多个晶体管1640(例如,金属氧化物半导体场效应晶体管(MOSFET))的特征。器件层1604可以包括例如一个或多个源极和/或漏极(S/D)区域1620、用于控制S/D区域1620之间的晶体管1640中的电流流动的栅极1622、以及用于向/从S/D区域1620传送电信号的一个或多个S/D触点1624。晶体管1640可以包括为了清楚起见而未示出的附加特征,诸如器件隔离区域、栅极触点等。晶体管1640不限于图9中所示的类型和配置,并且可以包括各种各样的其他类型和配置,例如平面晶体管、非平面晶体管或者两者的组合。平面晶体管可以包括双极结型晶体管(BJT)、异质结双极晶体管(HBT)或高电子迁移率晶体管(HEMT)。非平面晶体管可以包括FinFET晶体管,例如双栅晶体管或三栅晶体管,以及环绕或全环绕栅晶体管,例如纳米带和纳米线晶体管。

[0072] 每个晶体管1640可以包括由至少两层形成的栅极1622、栅极电介质和栅电极。栅极电介质可以包括一层或层的堆叠体。一个或多个层可以包括氧化硅、二氧化硅、碳化硅和/或高k电介质材料。高k电介质材料可以包括诸如铪、硅、氧、钛、钽、镧、铝、锆、钡、锶、钇、铅、钪、铌和锌的元素。可用于栅极电介质中的高k材料的示例包括但不限于氧化铪、铪硅氧化物、氧化镧、氧化镧铝、氧化锆、锆硅氧化物、氧化钽、氧化钛、钡锶钛氧化物、钡钛氧化物、锶钛氧化物、氧化钇、氧化铝、铅钪钽氧化物、和铌酸锌铅。在一些实施例中,当使用高k材料时,可以对栅极电介质执行退火工艺以提高其质量。

[0073] 栅电极可以形成在栅极电介质上,并且可以包括至少一个p型功函数金属或n型功

函数金属,这取决于晶体管1640是p型金属氧化物半导体 (PMOS) 晶体管还是n型金属氧化物半导体 (NMOS) 晶体管。在一些实施方式中,栅电极可由两个或更多个金属层的堆叠体组成,其中一个或多个金属层是功函数金属层且至少一个金属层是填充金属层。为了其他目的,可以包括另外的金属层,例如阻挡层。对于PMOS晶体管,可以用于栅电极的金属包括但不限于钌、钯、铂、钴、镍、导电金属氧化物 (例如,氧化钌) 以及下面参考NMOS晶体管讨论的任何金属 (例如,用于功函数调节)。对于NMOS晶体管,可以用于栅电极的金属包括但不限于铪、锆、钛、钽、铝、这些金属的合金、这些金属的碳化物 (例如,碳化铪、碳化锆、碳化钛、碳化钽和碳化铝) 以及上面参考PMOS晶体管讨论的任何金属 (例如,用于功函数调节)。

[0074] 在一些实施例中,当沿着源极-沟道-漏极方向观察晶体管1640的横截面时,栅电极可以由U形结构组成,该U形结构包括基本上平行于衬底的表面的底部部分和基本上垂直于衬底的顶表面的两个侧壁部分。在其他实施例中,形成栅电极的金属层中的至少一个可以简单地是基本上平行于衬底的顶表面的平面层,并且不包括基本上垂直于衬底的顶表面的侧壁部分。在其他实施例中,栅电极可以由U形结构和平面非U形结构的组合构成。例如,栅电极可由形成在一个或多个平面非U形层顶部的一个或多个U形金属层组成。

[0075] 在一些实施例中,一对侧壁间隔物可以形成在栅极堆叠体的相对侧上以夹置 (bracket) 栅极堆叠体。侧壁间隔物可以由诸如氮化硅、氧化硅、碳化硅、掺杂碳的氮化硅和 氮氧化硅的材料形成。形成侧壁间隔物的工艺在本领域中是公知的,并且通常包括沉积和 蚀刻工艺步骤。在一些实施例中,可以使用多对间隔物;例如,两对、三对或四对侧壁间隔物 可形成在栅极堆叠体的相对侧上。

[0076] S/D区域1620可形成在衬底1602内,邻近每个晶体管1640的栅极1622。S/D区域1620可以使用例如注入/扩散工艺或蚀刻/沉积工艺形成。在前一工艺中,可将例如硼、铝、锑、磷或砷的掺杂剂离子注入到衬底1602中以形成S/D区域1620。在离子注入工艺之后可以接着是激活掺杂剂并使它们进一步扩散到衬底1602中的退火工艺。在后一工艺中,可首先蚀刻衬底1602以在S/D区域1620的位置处形成凹槽。然后,可以执行外延沉积工艺,以用用于制造S/D区域1620的材料填充凹槽。在一些实施方式中,S/D区域1620可以使用诸如硅锗或碳化硅的硅合金来制造。在一些实施例中,外延沉积的硅合金可以用诸如硼、砷或磷的掺杂剂原位掺杂。在一些实施例中,S/D区域1620可以使用一个或多个替代半导体材料形成,例如锗或III-V族材料或合金。在进一步的实施例中,可以使用一层或多层金属和/或金属合金来形成S/D区域1620。

[0077] 可以通过设置在器件层1604上的一个或多个互连层(在图9中被示为互连层1606-1610)向和/或从器件层1604的器件(例如,晶体管1640)传送诸如功率和/或输入/输出(I/0)信号的电信号。例如,器件层1604的导电特征(例如,栅极1622和S/D触点1624)可以与互连层1606-1610的互连结构1628电耦合。一个或多个互连层1606-1610可以形成IC器件1600的金属化堆叠体(也称为"ILD堆叠体")1619。

[0078] 互连结构1628可以布置在互连层1606-1610内以根据各种设计来传送电信号(特别地,该布置不限于图9中示出的互连结构1628的特定配置)。尽管图9中示出了特定数量的互连层1606-1610,但本公开内容的实施例包括具有比所示出的更多或更少互连层的IC器件。

[0079] 在一些实施例中,互连结构1628可以包括填充有诸如金属的导电材料的线1628a

和/或过孔1628b。线1628a可被布置为在基本上平行于衬底1602的其上形成器件层1604的表面的平面的方向上传送电信号。例如,线1628a可沿从图9的角度进出纸面的方向传送电信号。过孔1628b可以被布置为在基本上垂直于衬底1602的其上形成器件层1604的表面的平面的方向上传送电信号。在一些实施例中,过孔1628b可以将不同互连层1606-1610的线1628a电耦合在一起。

[0080] 互连层1606-1610可以包括设置在互连结构1628之间的电介质材料1626,如图9所示。在一些实施例中,设置在互连层1606-1610中的不同互连层中的互连结构1628之间的电介质材料1626可具有不同的成分;在其他实施例中,不同互连层1606-1610之间的电介质材料1626的成分可以是相同的。

[0081] 第一互连层1606可以形成在器件层1604上方。在一些实施例中,第一互连层1606可以包括线1628a和/或过孔1628b,如图所示。第一互连层1606的线1628a可与器件层1604的触点(例如,S/D触点1624)耦合。

[0082] 第二互连层1608可以形成在第一互连层1606上方。在一些实施例中,第二互连层1608可以包括过孔1628b以将第二互连层1608的线1628a与第一互连层1606的线1628a耦合。尽管为了清楚起见,线1628a和过孔1628b在结构上以在每个互连层内(例如,在第二互连层1608内)的线限定,但是在一些实施例中,线1628a和过孔1628b可以在结构上和/或在材料上是连续的(例如,在双镶嵌工艺期间同时填充)。

[0083] 根据结合第二互连层1608或第一互连层1606描述的类似技术和配置,可以在第二互连层1608上接连形成第三互连层1610(以及根据需要,形成附加互连层)。在一些实施例中,IC器件1600中的金属化堆叠体1619中"较高"(即,更远离器件层1604)的互连层可以更厚。

[0084] IC器件1600可以包括阻焊材料1634 (例如聚酰亚胺或类似材料) 和形成在互连层 1606-1610上的一个或多个导电触点1636。在图9中,导电触点1636被示为采用接合焊盘的形式。导电触点1636可与互连结构1628电耦合并且被配置为将 (一个或多个) 晶体管1640的电信号传送到其他外部设备。例如,焊料接合部可以形成在一个或多个导电触点1636上,以将包括IC器件1600的芯片与另一部件 (例如,电路板) 机械和/或电耦合。IC器件1600可以包括附加的或替代的结构,以传送来自互连层1606-1610的电信号; 例如,导电触点1636可包括将电信号传送至外部部件的其他类似特征 (例如,柱)。

[0085] 图10是IC器件组件1700的侧视截面图,其可以包括本文公开的微电子部件102和/或微电子组件100中的任何一个。IC器件组件1700包括设置在电路板1702(其可以是例如母板)上的多个部件。IC器件组件1700包括设置在电路板1702的第一面1740和电路板1702的相对第二面1742上的部件;通常,部件可以设置在一个或两个面1740和1742上。下面参考IC器件组件1700讨论的任何IC封装可以包括本文公开的微电子组件100的任何实施例(例如,可以包括通过直接接合耦合在一起的多个微电子部件102)。

[0086] 在一些实施例中,电路板1702可以是包括多个金属层的PCB,所述多个金属层通过电介质材料层彼此分离并通过导电过孔互连。任何一个或多个金属层可以以期望的电路图案形成,以在耦合到电路板1702的部件之间传送电信号(可选地与其他金属层结合)。在其他实施例中,电路板1702可为非PCB衬底。

[0087] 图10中所示的IC器件组件1700包括通过耦合部件1716耦合到电路板1702的第一

面1740的中介层上封装结构1736。耦合部件1716可以将中介层上封装结构1736电和机械地耦合到电路板1702,并且可以包括焊球(如图10所示)、插座的凸出和凹入部分、粘合剂、底部填充材料和/或任何其他合适的电和/或机械耦合结构。

[0088] 中介层上封装结构1736可以包括通过耦合部件1718耦合到封装中介层1704的IC 封装1720。耦合部件1718可以采取用于应用的任何适当的形式,诸如上面参考耦合部件1716讨论的形式。尽管图10中示出了单个IC封装1720,但是多个IC封装可以耦合到封装中介层1704;实际上,附加的中介层可以耦合到封装中介层1704。封装中介层1704可提供用于桥接电路板1702和IC封装1720的中间衬底。IC封装1720可以是或者包括例如管芯(图8的管芯1502)、IC器件(例如图9的IC器件1600)或者任何其他适当的部件。通常,封装中介层1704可以将连接扩展到更宽的间距或者将连接重新布线到不同的连接。例如,封装中介层1704可以将IC封装1720(例如管芯)耦合到耦合部件1716的一组BGA导电触点,以用于耦合到电路板1702。在图10所示的实施例中,IC封装1720和电路板1702阶接到封装中介层1704的相对侧;在其他实施例中,IC封装1720和电路板1702可以附接到封装中介层1704的同一侧。在一些实施例中,三个或更多个部件可以通过封装中介层1704互连。

[0089] 在一些实施例中,封装中介层1704可以被形成为PCB,包括通过电介质材料层彼此分离并且通过导电过孔互连的多个金属层。在一些实施例中,封装中介层1704可由环氧树脂、玻璃纤维增强环氧树脂、具有无机填料的环氧树脂、陶瓷材料或诸如聚酰亚胺的聚合物材料形成。在一些实施例中,封装中介层1704可由交替的刚性或柔性材料形成,其可包括与上述用于半导体衬底的材料相同的材料,例如硅、锗和其他III-V族和IV族材料。封装中介层1704可以包括金属线1710和过孔1708,包括但不限于TSV 1706。封装中介层1704可进一步包括嵌入式器件1714,包括无源和有源器件两者。这些器件可以包括但不限于电容器、去耦电容器、电阻器、电感器、熔丝、二极管、变压器、传感器、静电放电(ESD)器件和存储器件。诸如射频器件、功率放大器、功率管理器件、天线、阵列、传感器和微机电系统(MEMS)器件之类的更复杂器件也可形成在封装中介层1704上。中介层上封装结构1736可以采用本领域已知的任何中介层上封装结构的形式。

[0090] IC器件组件1700可以包括通过耦合部件1722耦合到电路板1702的第一面1740的 IC封装1724。耦合部件1722可以采用以上参考耦合部件1716讨论的任何实施例的形式,并且IC封装1724可以采用以上参考IC封装1720讨论的任何实施例的形式。

[0091] 图10中所示的IC器件组件1700包括通过耦合部件1728耦合到电路板1702的第二面1742的堆叠式封装(package-on-package)结构1734。堆叠式封装结构1734可以包括通过耦合部件1730耦合在一起的IC封装1726和IC封装1732,使得IC封装1726被设置在电路板1702和IC封装1732之间。耦合部件1728和1730可以采用上述耦合部件1716的任何实施例的形式,并且IC封装1726和1732可以采用上述IC封装1720的任何实施例的形式。堆叠式封装结构1734可以根据本领域已知的任何堆叠式封装结构来配置。

[0092] 图11是可包括本文公开的微电子部件102和/或微电子组件100中的任一个的示例电气设备1800的框图。例如,电气设备1800的部件中的任何合适的部件可以包括本文公开的IC器件组件1700、IC器件1600或管芯1502中的一个或多个。图11中示出了包括在电气设备1800中的多个部件,但是这些部件中的任何一个或多个可以被省略或复制,以适合于应用。在一些实施例中,包括在电气设备1800中的一些或所有部件可以附接到一个或多个母

板。在一些实施例中,在单个片上系统(SoC)管芯上制造这些组件中的一些或全部。

[0093] 另外,在各种实施例中,电气设备1800可以不包括图11中所示的一个或多个部件,但是电气设备1800可以包括用于耦合到一个或多个部件的接口电路。例如,电气设备1800可以不包括显示设备1806,但可包括显示设备1806可耦合到的显示设备接口电路(例如,连接器和驱动器电路)。在另一组示例中,电气设备1800可以不包括音频输入设备1824或音频输出设备1808,但是可以包括音频输入设备1824或音频输出设备1808可以耦合到的音频输入或输出设备接口电路(例如,连接器和支持电路)。

[0094] 电气设备1800可包括处理设备1802(例如,一个或多个处理设备)。如本文所使用的,术语"处理设备"或"处理器"可以指处理来自寄存器和/或存储器的电子数据以将该电子数据转换成可以存储在寄存器和/或存储器中的其他电子数据的任何设备或设备的一部分。处理设备1802可以包括一个或多个数字信号处理器(DSP)、专用集成电路(ASIC)、CPU、GPU、密码处理器(在硬件内执行密码算法的专用处理器)、服务器处理器或任何其他合适的处理设备。电气设备1800可包括存储器1804,其本身可包括一个或多个存储器器件,诸如易失性存储器(例如,动态随机存取存储器(DRAM))、非易失性存储器(例如,只读存储器(ROM))、闪存、固态存储器、和/或硬盘驱动器。在一些实施例中,存储器1804可包括与处理设备1802共享管芯的存储器。该存储器可用作高速缓冲存储器且可包括嵌入式动态随机存取存储器(eDRAM)或自旋转移矩磁性随机存取存储器(STT-MRAM)。

[0095] 在一些实施例中,电气设备1800可以包括通信芯片1812(例如,一个或多个通信芯片)。例如,通信芯片1812可以被配置用于管理用于向和从电气设备1800传输数据的无线通信。术语"无线"及其派生词可用于描述可通过使用经调制的电磁辐射经由非固体介质来传递数据的电路、设备、系统、方法、技术、通信信道等。该术语并不意味着相关联的设备不包括任何导线,尽管在一些实施例中它们可能不包括。

[0096] 通信芯片1812可以实施多种无线标准或协议中的任何一种,包括但不限于电气和电子工程师协会(IEEE)标准,包括Wi-Fi(IEEE802.11系列)、IEEE 802.16标准(例如,IEEE 802.16-2005修订版)、长期演进(LTE)项目以及任何修订版、更新版和/或修正版(例如,高级LTE项目、超移动宽带(UMB)项目(也称为"3GPP2")等)。兼容IEEE 802.16的宽带无线接入(BWA)网络通常被称为WiMAX网络,WiMAX网络是代表微波接入全球互操作的首字母缩写词,其是通过IEEE 802.16标准的一致性和互操作性测试的产品的认证标志。通信芯片1812可以根据全球移动通信系统(GSM)、通用分组无线业务(GPRS)、通用移动电信系统(UMTS)、高速分组接入(HSPA)、演进HSPA(E-HSPA)或LTE网络来操作。通信芯片1812可以根据增强型数据GSM演进(EDGE)、GSM EDGE无线接入网(GERAN)、通用陆地无线接入网(UTRAN)或演进型UTRAN(E-UTRAN)来操作。通信芯片1812可以根据码分多址(CDMA)、时分多址(TDMA)、数字增强无绳电信(DECT)、演进数据优化(EV-DO)及其派生物、以及被指定为3G、4G、5G及之后的任何其他无线协议来操作。在其他实施例中,通信芯片1812可以根据其他无线协议进行操作。电气设备1800可以包括天线1822,以便于无线通信和/或接收其他无线通信(例如AM或FM无线电传输)。

[0097] 在一些实施例中,通信芯片1812可以管理有线通信,诸如电、光或任何其他合适的通信协议(例如,以太网)。如上所述,通信芯片1812可以包括多个通信芯片。例如,第一通信芯片1812可以专用于诸如Wi-Fi或蓝牙的较短距离无线通信,并且第二通信芯片1812可以

专用于诸如全球定位系统(GPS)、EDGE、GPRS、CDMA、WiMAX、LTE、EV-DO或其他的较长距离无线通信。在一些实施例中,第一通信芯片1812可以专用于无线通信,并且第二通信芯片1812可以专用于有线通信。

[0098] 电气设备1800可以包括电池/电源电路1814。电池/电源电路1814可以包括一个或多个能量存储设备(例如,电池或电容器)和/或用于将电气设备1800的部件耦合到与电气设备1800分离的能量源(例如,AC线路电源)的电路。

[0099] 电气设备1800可包括显示设备1806(或对应的接口电路,如上所述)。显示设备1806可包括任何视觉指示器,例如平视显示器、计算机监视器、投影仪、触摸屏显示器、液晶显示器(LCD)、发光二极管显示器或平板显示器。

[0100] 电气设备1800可以包括音频输出设备1808(或对应的接口电路,如上所述)。音频输出设备1808可以包括生成可听指示符的任何设备,诸如扬声器、耳机或耳塞。

[0101] 电气设备1800可以包括音频输入设备1824(或对应的接口电路,如上所述)。音频输入设备1824可包括产生表示声音的信号的任何设备,例如麦克风、麦克风阵列或数字乐器(例如,具有乐器数字接口(MIDI)输出的乐器)。

[0102] 电气设备1800可以包括GPS设备1818(或对应的接口电路,如上所述)。GPS设备1818可以与基于卫星的系统通信,并且可以接收电气设备1800的位置,如本领域已知的。

[0103] 电气设备1800可以包括其他输出设备1810(或对应的接口电路,如上所述)。其他输出设备1810的示例可以包括音频编解码器、视频编解码器、打印机、用于向其他设备提供信息的有线或无线发射机、或附加存储设备。

[0104] 电气设备1800可包括其他输入设备1820(或对应的接口电路,如上所述)。其他输入设备1820的示例可包括加速计、陀螺仪、罗盘、图像捕捉设备、键盘,诸如鼠标、指示笔、触摸板之类的光标控制设备,条形码读取器、快速响应(QR)码读取器、任何传感器、或射频识别(RFID)读取器。

[0105] 电气设备1800可以具有任何期望的形状因子,诸如手持式或移动电气设备(例如,蜂窝电话、智能电话、移动互联网设备、音乐播放器、平板计算机、膝上型计算机、上网本计算机、超级本计算机、个人数字助理(PDA)、超移动个人计算机等)、台式电气设备、服务器设备或其他联网计算部件、打印机、扫描仪、监视器、机顶盒、娱乐控制单元、车辆控制单元、数码相机、数字视频记录器或可穿戴电气设备。在一些实施例中,电气设备1800可以是处理数据的任何其他电子设备。

[0106] 以下段落提供了本文所公开的实施例的各种示例。

[0107] 示例1A是一种微电子组件,包括:中介层,具有第一表面和相对的第二表面;第一微电子部件,通过第一直接接合区域耦合到中介层的第二表面;第二微电子部件,通过第二直接接合区域耦合到中介层的第二表面;衬垫材料,在中介层的第二表面上并在第一微电子部件和第二微电子部件周围;以及导热填充材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间。

[0108] 示例2A可以包括示例1A的主题,并且可以进一步指定导热填充材料包括陶瓷、铜、铝、银、金刚石、石墨烯、硅和碳、硼和氮、或铝和氮、以及其组合。

[0109] 示例3A可以包括示例1A的主题,并且可以进一步指定导热填充材料的厚度在10微米与250微米之间。

[0110] 示例4A可以包括示例1A的主题,并且可以进一步指定衬垫材料包括钛、钽、钒、镍、钌、钴、铱、钛和氮、钽和氮、钒和镍、铱和氧、硅和碳和氮、硅和氮、硅和碳、或钛和氧、以及其组合。

[0111] 示例5A可以包括示例1A的主题,并且可以进一步指定衬垫材料的厚度在10纳米与2000纳米之间。

[0112] 示例6A可以包括示例1A的主题,并且可以进一步指定第一微电子部件和第二微电子部件的厚度小于或等于40微米。

[0113] 示例7A可以包括示例1A的主题,并且可以进一步指定第一微电子部件和第二微电子部件包括耦合到中介层的第一表面和相对的第二表面,并且可以进一步包括接合到第一微电子部件和第二微电子部件的第二表面的导热块体材料。

[0114] 示例8A可以包括示例7A的主题,并且可以进一步指定导热块体材料的厚度在10微米和650微米之间。

[0115] 示例9A可以包括示例1A的主题,其中,导热块体材料包括铜、铝、银、硅和碳、或金刚石、以及其组合。

[0116] 示例10A可以包括示例7A的主题,并且可以进一步包括耦合到中介层的第一表面的封装衬底;以及在封装衬底和导热块体材料之间延伸的底部填充材料。

[0117] 示例11A是一种微电子组件,包括:中介层,具有第一面和相对的第二面;第一微电子部件,具有第一表面和相对的第二表面,第一微电子部件在第一表面处通过第一直接接合区域耦合到中介层的第二面;第二微电子部件,具有第一表面和相对的第二表面,第二微电子部件在第一表面处通过第二直接接合区域耦合到中介层的第二面;衬垫材料,在中介层的第二表面上并在第一微电子部件和第二微电子部件周围;导热填充材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间;以及导热块体材料,接合到第一微电子部件和第二微电子部件的第二表面。

[0118] 示例12A可以包括示例11A的主题,并且可以进一步指定中介层包括有机电介质材料。

[0119] 示例13A可以包括示例11A的主题,并且可以进一步指定中介层包括无机电介质材料。

[0120] 示例14A可以包括示例11A的主题,并且可以进一步包括:封装衬底,耦合到中介层的第一表面;以及底部填充材料,在封装衬底和导热块体材料之间延伸。

[0121] 示例15A可以包括示例11A的主题,并且可以进一步指定第一微电子部件和第二微电子部件包括半导体管芯。

[0122] 示例16A是一种微电子组件,包括:中介层;第一微电子部件,具有第一表面和相对的第二表面,其中,第一微电子部件的第一表面通过第一直接接合区域耦合到中介层;第二微电子部件,具有第一表面和相对的第二表面,其中,第二微电子部件的第一表面通过第二直接接合区域耦合到中介层;导热填充材料,在中介层的表面上并且在第一微电子部件和第二微电子部件之间;以及导热块体材料,接合到第一微电子部件和第二微电子部件的第二表面。

[0123] 示例17A可以包括示例16A的主题,并且可以进一步指定导热填充材料包括陶瓷、铜、铝、银、金刚石、石墨烯、硅和碳、硼和氮、或铝和氮、以及其组合。

[0124] 示例18A可以包括示例16A的主题,并且可以进一步指定导热块体材料包括铜、铝、银、硅和碳、或金刚石、以及其组合。

[0125] 示例19A可以包括示例16A的主题,并且还可以包括:衬垫材料,在中介层与导热填充材料之间以及在第一微电子部件和第二微电子部件与导热填充材料之间。

[0126] 示例20A可以包括示例19A的主题,并且可以进一步指定衬垫材料包括钛、钽、钒、镍、钌、钴、铱、钛和氮、钽和氮、钒和镍、铱和氧、硅和碳和氮、硅和氮、硅和碳、或钛和氧、以及其组合。

[0127] 示例1B是一种微电子组件,包括:中介层,具有第一表面和相对的第二表面;第一微电子部件,通过第一直接接合区域耦合到中介层的第二表面;第二微电子部件,通过第二直接接合区域耦合到中介层的第二表面;衬垫材料,在中介层的第二表面上并在第一微电子部件和第二微电子部件周围;以及无机电介质材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间。

[0128] 示例2B可以包括示例1B的主题,并且可以进一步指定无机电介质材料包括硅和氧、或硅和氮、或其组合。

[0129] 示例3B可以包括示例1B的主题,并且可以进一步指定无机电介质材料的厚度在10 微米与250微米之间。

[0130] 示例4B可以包括示例1B的主题,并且可以进一步指定衬垫材料包括硅和碳和氮、硅和氮、硅和氧和氮、或硅和碳。

[0131] 示例5B可以包括示例1B的主题,并且可以进一步指定衬垫材料的厚度在10纳米与2000纳米之间。

[0132] 示例6B可以包括示例1B的主题,并且可以进一步指定第一微电子部件和第二微电子部件的厚度小于或等于40微米。

[0133] 示例7B可以包括示例1B的主题,并且可以进一步指定第一微电子部件和第二微电子部件包括耦合到中介层的第一表面和相对的第二表面,并且可以进一步包括耦合到第一微电子部件和第二微电子部件的第二表面的第三微电子部件。

[0134] 示例8B可以包括示例7B的主题,并且可以进一步指定无机电介质材料是第一无机电介质材料,并且可以进一步包括在第一无机电介质材料上以及在第一微电子部件和第二微电子部件的第二表面上的第二无机电介质材料,其中,第三微电子部件通过熔融接合区域耦合到第二无机电介质材料。

[0135] 示例9B可以包括示例7B的主题,并且可以进一步指定第一微电子部件和第二微电子部件是单面管芯,其中,第三微电子部件是无源管芯,并且其中,第三微电子部件通过熔融接合区域耦合到第一微电子部件和第二微电子部件的第二表面。

[0136] 示例10B可以包括示例9B的主题,并且可以进一步指定第三微电子部件进一步包括散热结构。

[0137] 示例11B是一种微电子组件,包括:中介层,具有第一面和相对的第二面;第一微电子部件,具有第一表面和相对的第二表面,第一微电子部件在第一表面处通过第一直接接合区域耦合到中介层的第二面;第二微电子部件,具有第一表面和相对的第二表面,第二微电子部件在第一表面处通过第二直接接合区域耦合到中介层的第二面;衬垫材料,在中介层的第二表面上且在第一微电子部件和第二微电子部件周围;无机填充材料,在衬垫材料

上且在第一微电子部件与第二微电子部件之间;以及第三微电子部件,耦合到第一微电子部件和第二微电子部件的第二表面。

[0138] 示例12B可以包括示例11B的主题,并且可以进一步指定第一微电子部件和第二微电子部件是双面管芯,其中,第三微电子部件是有源管芯,并且其中,第三微电子部件通过第三直接接合区域耦合到第一微电子部件和第二微电子部件的第二表面。

[0139] 示例13B可以包括示例12B的主题,并且还可以包括穿衬底过孔(TSV),穿过无机填充材料电耦合第三微电子部件和中介层。

[0140] 示例14B可以包括示例13B的主题,并且可以进一步指定中介层包括电力输送电路,第一微电子部件和第二微电子部件包括存储器电路,并且第三微电子部件包括处理电路。

[0141] 示例15B可以包括示例11B的主题,并且还可以包括:封装衬底,耦合到中介层的第一面;以及底部填充材料,在封装衬底和第三微电子部件之间延伸。

[0142] 示例16B是一种微电子组件,包括:中介层;第一微电子部件,具有第一表面和相对的第二表面,其中,第一微电子部件的第一表面通过第一直接接合区域耦合到中介层;第二微电子部件,具有第一表面和相对的第二表面,其中,第二微电子部件的第一表面通过第二直接接合区域耦合到中介层;衬垫材料,在中介层的表面上且在第一微电子部件和第二微电子部件周围;无机填充材料,在衬垫材料上且在第一微电子部件与第二微电子部件之间;以及第三微电子部件,耦合到第一微电子部件和第二微电子部件的第二表面。

[0143] 示例17B可以包括示例16B的主题,并且可以进一步指定无机电介质材料包括硅和氧、或硅和氮、或其组合。

[0144] 示例18B可以包括示例16B的主题,并且可以进一步指定衬垫材料包括硅和碳和氮、硅和氮、硅和氧和氮、或硅和碳、以及其组合。

[0145] 示例19B可以包括示例16B的主题,并且可以进一步指定无机电介质材料的厚度在10微米与250微米之间。

[0146] 示例20B可以包括示例16B的主题,并且可以进一步指定衬垫材料的厚度在10纳米与2000纳米之间。

图1

图2

图3A

图3B

图3C

图3D

图3E

图3F

图3G

图4A

图4B

图4C

图4D

00

图5

图6A

图6C

图6D

图6E

图6F

图8

图9

图10

图11