### (12)

# Übersetzung der europäischen Patentschrift

(97) EP 1 551 130 B1

(21) Deutsches Aktenzeichen: **60 2004 012 955.0** (96) Europäisches Aktenzeichen: **04 030 077.4**

(96) Europäischer Anmeldetag: 18.12.2004

(97) Erstveröffentlichung durch das EPA: 06.07.2005

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **09.04.2008** (47) Veröffentlichungstag im Patentblatt: **04.06.2009**

(30) Unionspriorität:

751129 31.12.2003 US

(73) Patentinhaber:

Alcatel Lucent, Paris, FR

(74) Vertreter:

Patentanwälte U. Knecht und Kollegen, 70435 Stuttgart

(51) Int CI.8: **H04L** 12/26 (2006.01)

**H04L 12/56** (2006.01) **H04L 12/46** (2006.01)

(84) Benannte Vertragsstaaten:

AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LI, LT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR

(72) Erfinder:

Narsinh, Anees, Pacific Palisades CA 90272, US; Bailey, John, Agoura Hills CA 91301, US

(54) Bezeichnung: Parallele Steuerungsvorrichtungen für den Data Link Layer mit Statistikerfassung in einer Netzwerksvermittlungseinrichtung

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

### **Beschreibung**

### ALLGEMEINER STAND DER TECHNIK

**[0001]** Die Erfindung betrifft im Allgemeinen ein Verfahren zur Verarbeitung von Frames in einer Netzwerkvermittlungseinrichtung. Insbesondere betrifft die Erfindung ein System und Verfahren zur Bereitstellung verteilter VLAN-Zuordnung, Kontrolle, Formung und Statistikerfassung in einer Vielzahl von Steuerungsvorrichtungen für den Data Link Layer der Netzwerkvermittlungseinrichtung.

### ALLGEMEINER STAND

[0002] Router in Paketvermittlungsnetzen nutzen im Allgemeinen einen oder mehr Netzwerkprozessoren, in der Regel einen anwendungsspezifischen Schaltkreis (ASIC), um verschiedene Paketverarbeitungsoperationen durchzuführen. Jeder Netzwerkprozessor ist im Allgemeinen mit einer Vielzahl von Media Access Controllern verbunden, von denen Frames empfangen werden und an die Frames gesendet werden. Historisch wurden Router entwickelt, so daß der Netzwerkprozessor gleichzeitig Verkehr von jedem zugeordneten Port empfangen konnte, der mit seiner festgelegten Leitungsgeschwindigkeit arbeitete, in der Regel 100 oder 1000 Megabit/s. Es ist jedoch ein Trend zu überbelegten Ports vorhanden, was bedeutet, daß die Bandbreite des Netzwerkprozessors oder andere Routerressourcen im Allgemeinen nicht imstande sind, jeden Port zu unterstützen, der mit Leitungsgeschwindigkeit in einem kontinuierlichen Zeitintervall arbeitet. Während die Kosteneinsparungen pro Port für ein überbelegtes System einen günstigen Kompromiß für einige Kunden bieten, können überbelegende Ports zu einem bestimmten Datenverlust als Folge dessen führen, daß der Netzwerkprozessor oder Routenprozessor nicht fähig ist, den Verkehr zu verarbeiten.

**[0003]** Um die nachteiligen Effekte der Überbelegung zu minimieren, können Router beträchtliche Pufferspeicherung beim Versuch aufwenden, Bursts des Verkehrs zu erfassen, bis die Ressourcen zur Verfügung stehen, um den Verkehr zu verarbeiten. Pausennachrichten können ebenfalls an einen oder mehr Verbindungspartner übertragen werden, um vorübergehend die empfangene Datenmenge zu verringern und dadurch die Möglichkeit des Pufferspeicherüberlaufs zu verringern. Trotz des begrenzten Erfolgs lösen beide Herangehensweisen nicht die zugrundeliegende Unfähigkeit des Netzwerkprozessors oder anderer Ressourcen, große Verkehrsmengen zu verarbeiten. Daher werden Mittel zur Bewahrung der Vorteile der überbelegten Portkonfigurationen benötigt, während der Rechenbedarf auf dem Netzwerkprozessor verringert wird.

**[0004]** Die Patentschrift WO00/10297 offenbart ein Paketverarbeitungssystem zum Empfangen und Verarbeiten eines Datenpakets. Die Verarbeitung schließt eine Vielzahl von Aufgaben ein und das System schließt einen ersten Prozessor ein, der angeordnet ist, eine erste Teilmenge von Aufgaben auf dem Datenpaket durchzuführen und einen ersten Header mit dem Paket zu verbinden. Das Paketverarbeitungssystem schließt ebenfalls einen zweiten Prozessor ein, der angeordnet ist, um eine zweite Teilmenge von Aufgaben durchzuführen, die mit dem Paket verbunden sind. Die US-Patentschrift 2002/010793 offenbart eine Vermittlungseinrichtung, die einen Netzwerkprozessor umfaßt, der mit einer Vielzahl Einrichtungen der Bitübertragungsschicht über eine Vielzahl von Netzzugangsmodulen gekoppelt ist, die Schaltungen für die Medienzugangskontrolle umfassen. Die Vermittlungseinrichtung umfaßt außerdem ein Statistikerfassungsmodul.

### KURZDARSTELLUNG

**[0005]** Die vorliegende Erfindung charakterisiert einen Data Link Lager-Prozessor zum Erfassen von Statistik integriert mit einer Vielzahl von Media Access Controllern (MACs). Beim Betrieb einer Vielzahl von Data Link Lager-Prozessoren parallel in einer Vermittlungseinrichtung verringert sich die von den Netzwerkprozessoren getragene Rechenbelastung bedeutend. Außerdem kann der Data Link Lager-Prozessor in seinen verschiedenen Ausführungsformen verwendet werden, um die Fähigkeit der Statistikerfassung in Systemen einzuführen, die Netzwerkprozessoren verwenden, die über solche Funktionalität nicht verfügen. Die Bereitstellung von Statistik auf einer VLAN-Basis zum Beispiel ist von besonderem Interesse in Anwendungen, wo Abrechnung und Gebührenerfassung vorzugsweise auf der Basis des VLAN durchgeführt werden, mit dem der Verkehr gesendet wurde.

[0006] Der Data Link Lager-Prozessor umfaßt eine Vielzahl von MACs zum Empfangen eines Frames von einem Kommunikationsnetz und ein Statistikerfassungsmodul, das funktionsfähig mit einem oder mehr MACs gekoppelt ist, zum Kompilieren der Statistik, die mit jedem der Vielzahl der MACs verbunden ist. In der bevorzugten Ausführungsform schließt die Statistik, die auf dem Eingangsfluß erzeugt wurde, kompiliert als eine Funktion des VLAN-Eintrags, die Anzahl der am Data Link Lager-Prozessor in die Warteschlange gestellten

Bytes, die Anzahl der am Data Link Lager-Prozessor in die Warteschlange gestellten Frames, die Anzahl der am Data Link Lager-Prozessor in die Warteschlange gestellten Nicht-Unicast-Bytes und die Anzahl der am Data Link Lager-Prozessor in die Warteschlange gestellten Nicht-Unicast-Frames ein. In der bevorzugten Ausführungsform sind zwei Statistiken vorhanden, die auf dem Ausgang pro VLAN-Eintrag erzeugt sind, nämlich die Anzahl der aus der Warteschlange entfernten Bytes und die Anzahl der aus der Warteschlange entfernten Frames.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0007]** Die vorliegende Erfindung ist beispielhaft und ohne Einschränkung in den Figuren der beigefügten Zeichnungen dargestellt, und in denen zeigen:

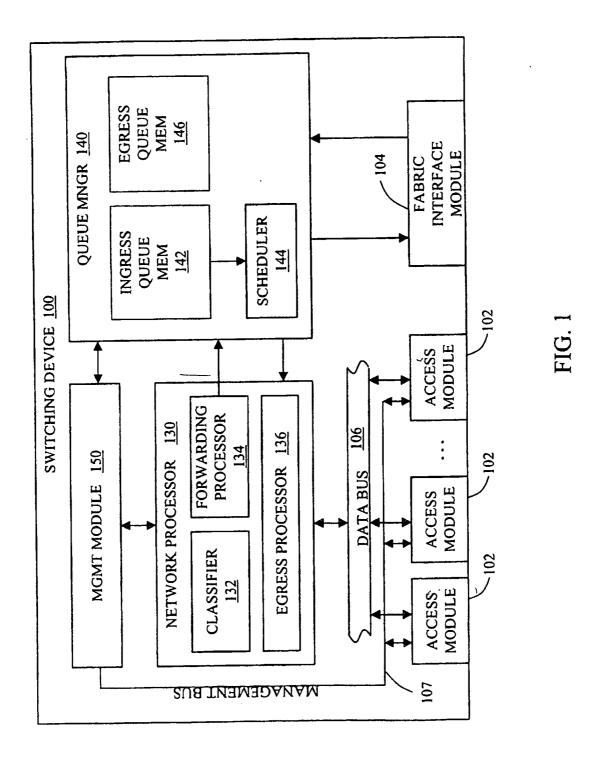

**[0008]** Fig. 1 – ein Blockschaltbild der Netzwerkvermittlungseinrichtung gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung;

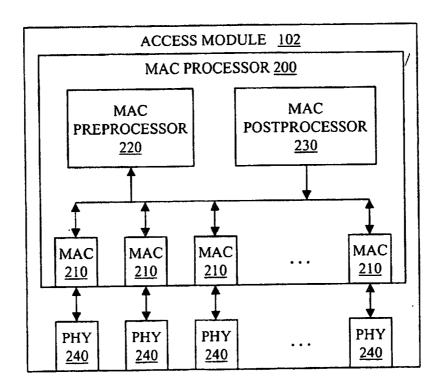

[0009] Fig. 2 – ein Blockschaltbild eines Zugangsmoduls gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung;

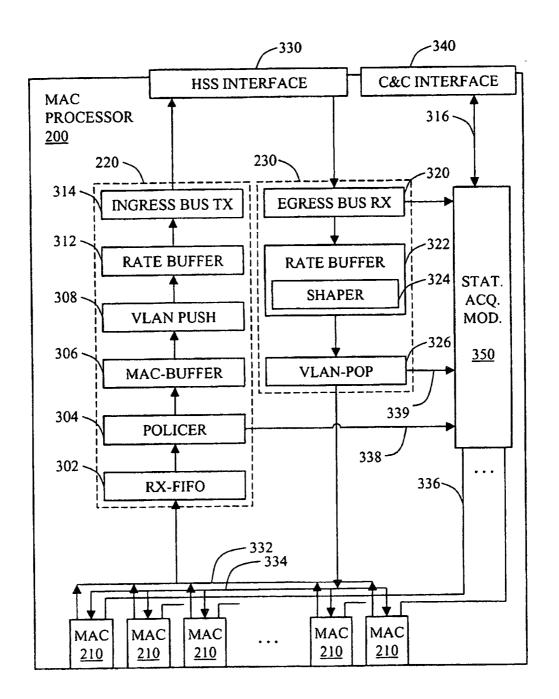

**[0010]** Fig. 3 – ein Blockschaltbild eines Data Link Layer-Prozessors gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung;

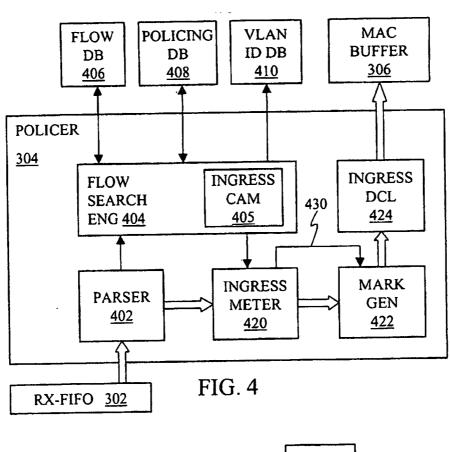

**[0011]** Fig. 4 – ein Blockschaltbild eines integralen Verkehrs-Policers, der durch den Data Link Layer-Prozessor verwendet wird, gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung

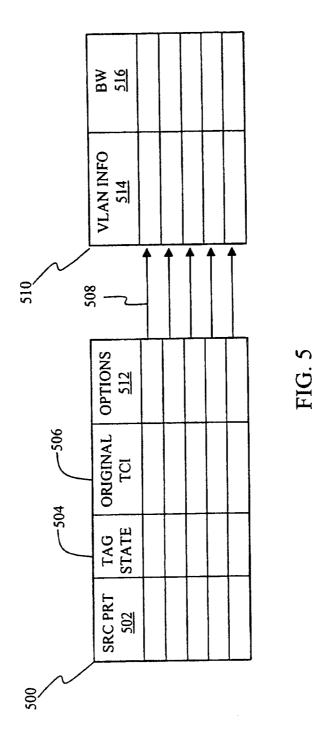

**[0012]** Fig. 5 eine schematische Darstellung der vorliegenden Flußdatenbank, die durch den Data Link Layer-Prozessor verwendet wird, gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung; und

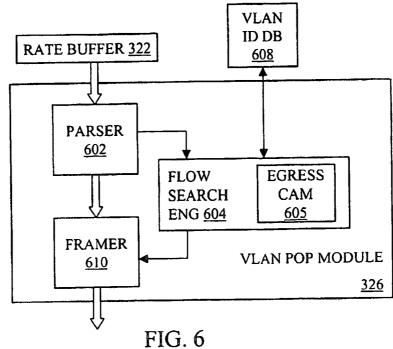

**[0013]** Fig. 6 – ein Blockschaltbild eines integralen VLAN-Pop-Moduls, das durch den Data Link Layer-Prozessor verwendet wird, gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung.

### DETAILLIERTE BESCHREIBUNG

[0014] In Fig. 1 ist ein Blockschaltbild der Netzwerksvermittlungseinrichtung dargestellt, mit der die bevorzugte Ausführungsform implementiert werden kann. Die Vermittlungseinrichtung 100 in der bevorzugten Ausführungsform ist angepaßt, um Switching- und Routingoperationen mit Protokoll-Dateneinheiten (PDUs) auf Schicht 2 (Sicherungsschicht) und Schicht 3 (Vermittlungsschicht) durchzuführen, wie im Open Systems Interconnect (OSI)-Referenzmodell definiert ist. Die Vermittlungseinrichtung 100 ist vorzugsweise eine der Vielzahl von Vermittlungseinrichtungen, die funktionsfähig miteinander über eine gemeinsame Switch Fabric (nicht gezeigt) gekoppelt sind. Die Vermittlungseinrichtungen sind ihrerseits funktionsfähig mit einer Vielzahl von Knoten in einem Datenkommunikationsnetz gekoppelt, das in einem lokalen Datennetz (LAN), Weitverkehrsnetz (WAN), Stadtbereichsnetz (MAN) oder einer Kombination davon zum Beispiel ausgeführt ist.

[0015] Die Vermittlungseinrichtung 100 der bevorzugten Ausführungsform umfaßt im Allgemeinen einen Netzwerkprozessor 130, z. B. einen Routenprozessor, einen Warteschlangen- oder Verkehrsmanager 140 und ein Verwaltungsmodul 150. Der Netzwerkprozessor 130 ist funktionsfähig mit dem Netzwerk über eine Vielzahl von Netzzugangsmodulen (AMs) 102 gekoppelt, wobei jedes der AMs 102 mindestens einen externen Port einschließt, der funktionsfähig mit einer Kommunikationsverbindung zu Zwecken des Empfangens des eingehenden Datenverkehrs und des Übertragen des ausgehenden Datenverkehrs gekoppelt ist. Wie hier verwendet, wird der Verkehr, der in die Vermittlungseinrichtung 100 an den AMs 102 eintritt, als eingehender Verkehr bezeichnet, während der Verkehr, der an einem AM 102 austritt, aus ausgehender Verkehr bezeichnet wird. Die Ports des AM 102 schließen Data Link Lager-Ports wie zum Beispiel Schnittstellen für Ethernet Medienzugangskontrolle (MAC) ein, die zum Beispiel mit dem Standard 802.3 des Institute of Electrical and Electronics Engineers (IEEE) ermöglicht sind.

[0016] Die PDUs des eingehenden und ausgehenden Verkehrs werden zwischen der Vielzahl der AMs 102 und dem Netzwerkprozessor 130 über einen oder mehr interne Datenbusse 106 transportiert. Der Netzwerkprozessor 130 der bevorzugten Ausführungsform umfaßt einen Klassifizierer 132 und einen Sendeprozessor 134 und einen Ausgangsprozessor 136. Der Klassifizierer 132 analysiert im Allgemeinen die Eingangs-PDUs; extrahiert ein oder mehr Felder der PDU, einschließlich Quell- und/oder Zieladressen, Protokolltypen und Prioritätsinformationen; und bildet die PDU auf eine Kategorie eines Satzes von Flußkategorien auf der Basis lo-

kaler Systemrichtlinien ab, die durch einen Netzwerkadministrator über das Verwaltungsmodul **150** definiert sind. Die lokalen Systemrichtlinien schreiben die Dienstklasse (class of service/(CoS) und oder Dienstgüte (quality of service/QoS) vor, die die PDU anzuwenden hat.

[0017] Der Sendeprozessor 134 bereitet dann die Eingangs-PDU zur Übertragung unter Verwendung der Adreßinformationen vor, die durch die Vermittlungseinrichtung 100 kompiliert wurden. Wenn die physikalische Zieladresse der PDU in den MAC-Adreßtabellen übereinstimmt, wird der entsprechende Ausgangsport identifiziert und der Frame wird an den Ausgangsport der entsprechenden Ausgangvermittlungseinrichtung vermittelt. Wenn jedoch die PDU eine Zielnetzadresse eines Knotens in einem anderen Netzbereich einschließt, sucht der Sendeprozessor bekannte Internet-Protokoll (IP)-Adressen und andere Flußinformationen in einer Sendetabelle, die zum Beispiel in einem zentralen Assoziativspeicher (cCAM) gehalten wird; ruft bei einer Übereinstimmung die Next-Hop-MAC-Adresse einer angrenzenden Einrichtung ab, an die das Paket zu senden ist; und kapselt das Paket in einem neuen Schicht-2-Header. Die PDUs des Eingangsflusses werden dann vom Netzwerkprozessor 130 an den Warteschlangenmanager 140 durchgelassen, wo sie vor der Übertragung an die Switch Fabric (nicht gezeigt) über das Fabric-Schnittstellenmodul 104 zwischengespeichert werden.

[0018] Außer der oben beschriebenen Eingangsverarbeitung verarbeitet der Netzwerkprozessor 130 ebenfalls ausgehenden Verkehr, der von der Switch Fabric empfangen wurde. Zur Unterstützung dieses ausgehenden Verkehrs schließt der Netzwerkprozessor 130 außerdem einen Ausgangsprozessor 136 ein, der ausgehenden Verkehr vom Ausgangswarteschlangenspeicher 146 oder Fabric-Schnittstellenmodul 104 empfängt, der vorübergehend zwischengespeichert werden kann, bevor er an den festgelegten Ausgangsport unter den AMs 102 weitergeleitet wird.

[0019] Der Warteschlangenmanager 140 umfaßt mindestens einen Eingangswarteschlangenspeicher 142 und Warteschlangenscheduler 144. Der Eingangswarteschlangenspeicher 142 schließt eine Vielzahl von Paketpufferspeichern oder Warteschlangen ein, von denen jeder/jede einer verschiedene Prioritätsebene oder einer verschiedene Ebene der QoS/CoS zugeordnet ist. Wenn Ausgangsbandbreite zur Verfügung steht, wird eine puffergespeicherte PDU durch den Scheduler 144 an die Switch Fabric über das Fabric-Schnittstellenmodul 104 gesendet.

[0020] In Fig. 2 ist ein Blockschaltbild eines AM 102 gemäß der bevorzugten Ausführungsform dargestellt. Das AM 102 umfaßt im Allgemeinen eine Vielzahl von Bitübertragungsschicht-Schnittstellen (PHY) 240 und einen MAC-Prozessor 200. Jede PHY 240, die auf Schicht 1 (Bitübertragungsschicht) arbeitet, die im OSI-Referenzmodell definiert ist, führt herkömmliche Netzschnittstellenfunktionen aus, einschließlich Empfang und Übertragung von Ethernet-Symbolströmen. Beim Empfangen eines Symbolstroms von der zugeordneten Kommunikationsverbindung werden elektrische oder optische Signale von der Kommunikationsverbindung durch die PHY 240 in einen Bytestrom umgewandelt, der anschließend an eine zugeordnete MAC-Schnittstelle 210 gesendet wird. Im Sendemodus wandelt die PHY 240 einen Bytestrom von einer zugeordneten MAC-Schnittstelle 210 in das für das Medium geeignete elektrische oder optische Signal um. Die PHY 240 entspricht dem Typ des Mediums, mit dem sie verbunden ist.

[0021] Der MAC-Prozessor 200 in der bevorzugten Ausführungsform umfaßt eine oder mehr MAC-Schnittstellen 210, die den IEEE-Standard 802.3 erfüllen, der hiermit durch Verweis aufgenommen ist. Die MAC-Schnittstellen 210, die auf Schicht 2 arbeiten, die im OSI-Referenzmodell definiert ist, führen herkömmliche Netzschnittstellenfunktionen aus, einschließlich Empfang und Übertragung von Ethernet-Frames. Im Empfangsmodus führen die MACs 210 vorzugsweise verschiedene Funktionen aus, einschließlich: (a) MAC-Frame-Parsing zum Extrahieren aus dem Ethernet-Typ-/Längenfeld des gekapselten Protokolltyps, der Framepriorität, der Benutzerpriorität der VLAN-markierten Frames und des TOS-Byte der IP-Frames mit Vorrang- oder DiffServ-Mapping; (b) Fehlerprüfung unter Verwendung des Wertes der Rahmenprüfsequenz (FCS) der empfangenen Daten sowie der Paket-Decapsulation; und (c) asymmetrische und symmetrische Flußsteuerung, einschließlich der Annahme der Flußsteuerungsframes, um die Frame-Übertragung oder Pausen-Frame-Übertragung durch einen Netzwerknachbar zum Beispiel zu unterbrechen. Frames von den MAC-Schnittstellen 210 werden dann lokal am MAC-Vorprozessor 220 verarbeitet, bevor sie an den Netzwerkprozessor 130 übertragen werden.

[0022] Im Übertragungsmodus werden Frames lokal am MAC-Postprozessor 230 verarbeitet, bevor sie an die MAC-Schnittstellen 210 übertragen werden. Übereinstimmend mit den herkömmlichen Media Access Controllern führen die MAC-Schnittstellen 210 verschiedenen Funktionen aus, einschließlich: (a) Kollisionsbearbeitung, (b) Zugriffskontrolle zum Kommunikationsmedium gemäß dem CSMA/CD-Übertragungsprotokoll, (c) Erzeugung des Wertes der Rahmenprüfsequenz (FCS), (d) Encapsulation und (e) Sendeverzögerung zum

Beispiel. In der bevorzugten Ausführungsform sind die MAC-Schnittstellen **210** angepaßt, um unabhängig entweder 10, 100 oder 1000 Megabit pro Sekunde Durchsatz unter Verwendung der Schnittstellentypen Reduced Ten-Bit Interface (RTBI) oder Reduced Gigabit Media Independent Interface (RGMII) zu unterstützen.

[0023] In Fig. 3 ist ein Blockschaltbild eines MAC-Prozessors 200 gemäß der bevorzugten Ausführungsform der vorliegenden Erfindung dargestellt. Außer einem oder mehr MACs 210 schließt der MAC-Prozessor 200 in einigen Ausführungsformen einen MAC-Vorprozessor 220 und einen MAC-Postprocessor 230 ein. Der MAC-Vorprozessor 220 schließt im Allgemeinen einen Verkehrs-Policer 304 zur selektiven Filterung von Frames, einen MAC-Pufferspeicher 306, ein VLAN-Pushmodul 308 zum Anhängen von VLAN-Tags an ausgewählte kommende Frames, einen Ratenpufferspeicher 312 und einen Eingangsbussender 314 zum Übermitteln der Frames an den Netzwerkprozessor 130 ein. Der MAC-Postprocessor 230 schließt vorzugsweise einen Ausgangsbusempfänger 320, einen Ratenpufferspeicher 322, der außerdem an die Form des ausgehenden Verkehrs 324 angepaßt ist, und ein VLAN-Pop-Modul 326 zum Entfernen von VLAN-Tags ausgewählter kommender Frames ein.

**[0024]** Eingehende Frames werden von der Vielzahl der MACs **210** an einen oder mehr Empfängerpufferspeicher über den internen Eingangsbus **332** übertragen. Ein oder mehr Empfängerpufferspeicher, die durch den First-in-First-out-Speicher (FIFO-Speicher) **302** dargestellt sind, werden verwendet, um Framesegmente zwischenzuspeichern, bevor der Frame an den Verkehrs-Policer **304** oder andere Downstream-Verarbeitungsentität übertragen wird.

[0025] Der Verkehrs-Policer 304 der bevorzugten Ausführungsform ist angepaßt, um Richtlinien des eingehenden Verkehrs und das Verwerfen von Frames lokal vor der Übertragung an den Netzwerkprozessor 130 auszuführen. In der bevorzugten Ausführungsform nutzt der Policer 304 einen Three Color Marker (TCM)-Algorithmus, um zu verwerfende Frames auf der Basis von Kriterien zu identifizieren, die am oder auf andere Weise durch den Policer 304 zugänglich sind. Das Policing lokal auf jedem der Vielzahl der AMs 102 ersetzt, verringert oder vergrößert die Zellstromkontrollfunktion, die herkömmlich im Netzwerkprozessor 130 implementiert ist.

[0026] Der Verkehrs-Policer 304, der detaillierter in Fig. 4 dargestellt ist, umfaßt vorzugsweise einen ersten Parser 402, eine Flußsuchmaschine (FSE) 404 mit Eingangs-CAM 405, ein Eingangszählmodul 420, einen Markierungsgenerator 422 und eine Eingangsverwurf-Steuerlogik 424. Ein eingehender Frame, der von einem MAC 210 über den Empfänger FIFO 302 empfangen wurde, wird durch den Parser 402 geprüft und ein oder mehr Bits oder Felder werden extrahiert, um einen Index im Eingangs-CAM 404 zu bilden, wo die Suche vorzugsweise durchgeführt wird. In der bevorzugten Ausführungsform umfaßt der CAM-Index den Quellport 502, den VLAN-Tag-Zustand 504, der die Anwesenheit oder Abwesenheit eines 802.1Q-Tags angibt, und das ursprüngliche Feld 506 der Frame-Tag-Kontrollinformationen (TCI), was schematisch in Tabellenform der Eingangs-CAM-Tabelle 500 von Fig. 5 dargestellt ist. In einigen Ausführungsformen umfaßt der Eingangs-CAM-Index außerdem ein Optionsfeld 512, um die Suche durch selektives Freigeben oder Sperren eines oder mehr CAM-Suchparameter unter Verwendung der folgenden Eigenschaften zu verfeinern:

VLAN ID-Freigabebit, um selektiv die Suche unter Verwendung des VLAN ID-Feldes des eingehenden Frames freizugeben;

TCI-Freigabebit, um selektiv die Suche unter Verwendung der Tag-Kontrollinformationen des eingehenden Frames freizugeben;

Quellport-Freigabebit, um selektiv die Suche unter Verwendung des Quellports, der dem eingehenden Frame zugeordnet ist, freizugeben;

Vertrauenswürdiges/vertrauensunwürdiges Portbit von der TCI vom äußeren VLAN-Tag des eingehenden Frames, um selektiv die Suche unter Verwendung der Priorität des eingehenden Frames freizugeben; und

Ethertype-Freigabebit, um selektiv die Suche unter Verwendung des Ethertype (VLAN Protokollkennung = x8100 oder andere) des eingehenden Frames freizugeben.

[0027] Wenn eine Übereinstimmung festgestellt wird, ruft der FSE 404 einen Flußindex 508 ab, der in die Flußdatenbank 406 zeigt, wo verschiedene Flußverarbeitungsparameter abgerufen werden. Wie schematisch durch die Tabellenform 510 der Flußdatenbank 406 dargestellt, die in Fig. 5 gezeigt ist, ruft der FSE 404 von der Flußdatenbank 406 eine oder mehr Formen der Verarbeitungsinformationen ab, einschließlich VLAN-Informationen 514, um die VLAN-Markierung und Bandbreitenparameter zu unterstützen, um Flußsteuerung zu unterstützen. Die VLAN-Informationen 514 können, aber es ist nicht eingeschränkt, einen neuen VLAN-Tag, eine neue VLAN ID für einen existierenden Tag und eine neue TCI für einen existierenden Tag einschließen. In der bevorzugten Ausführungsform schließt die Flußdatenbank 406 außerdem einen Index in der Policing-Datenbank 408 ein, der auf einen oder mehr Bandbreitenparameter zeigt, z. B. TCM-Verkehrsparameter, die notwen-

dig sind, um den eingehenden Verkehrsfluß zu überwachen.

[0028] In der bevorzugten Ausführungsform nutzt der Verkehrs-Policer 304 einen TCM-Algorithmus, um selektiv Außer-Profil-Frames zu identifizieren und zu verwerfen, vorzugsweise einen Einraten-Three Color Marking (srTCM)-Algorithmus oder den Zweiraten-Three Color Marking (trTCM)-Algorithmus. Der erste, srTCM, ist in Internet Engineering Task Force (IETF) Request for Comment (RFC) 2697, während trTCM in IETF RFC 2698 definiert ist, von denen beide hiermit durch Verweis hier aufgenommen sind. Jeder in diesen Standards beschriebene TCM-Algorithmus kann allein oder in Kombination verwendet werden, um andere entscheidungstreffende Prozesse in der Vermittlungseinrichtung 100 zu erweitern, die verantwortlich sind um zu bestimmen, ob Pakete außerhalb des Profils sind und folglich, wann Pakete zu verwerfen sind.

[0029] Wieder mit Verweis auf Fig. 4, um den srTCM-Algorithmus auszuführen, schließt der Policer 304 ein Eingangszählmodul (IMM) 420 ein, um zu messen, wieviel Daten pro vorgegebener Zeiteinheit fließen, was durch das Flußratenergebnis 430 angegeben wird, das an den Markierungsgenerator 422 übertragen wurde. Auf der Basis dieser Messung klassifiziert der Markierungsgenerator 422 den Frame in eine von drei Kategorien, die der Fachmann als "Farben" bezeichnet, nämlich grün, gelb und rot. Die einem Frame zugeordnete Farbe wird als eine Funktion der Verkehrsparameter bestimmt, die für jeden Fluß definiert sind. Die Verkehrsparameter im srTCM schließen eine garantierte Datenrate (CIR) und zwei zugeordnete Spitzenraten ein, nämlich eine garantierte Spitzenrate (CBS) und eine überschüssige Spitzenrate (EBS), die alle aus der Policing-Datenbank 408 als eine Funktion des einzelnen Flusses abgerufen wurden.

[0030] Im Allgemeinen schätzt der Markierungsgenerator 422 den Fluß gemäß dem srTCM, um zu bestimmen, welche Marke anzuwenden ist. Wenn der Frame die CBS nicht überschreitet, wird eine grüne Marke angewandt, um anzugeben, daß der Frame an den nächsten Downstream-Prozeß nach dem Policer 304 geliefert werden sollte. Ein Frame, der Teil eines Flusses ist, der sowohl den CIR als auch den EBS überschreitet, wird rot markiert und sofort verworfen. Wenn der Frame die CBS überschreitet, aber nicht die EBS, wird eine gelbe Marke dem Frame zugeordnet, um zu bezeichnen, daß der Frame solange geliefert werden kann, wie Systemressourcen oder Warteschlangenbildungsressouren dafür vorhanden sind. Der Frame kann unter Verwendung eines protokollspezifischen Feldes oder protokollunabhängiger Markierung markiert werden, falls durch das Protokoll nicht unterstützt. Obwohl ein gelber Frame in Abhängigkeit von der Verfügbarkeit von Systemressourcen verworfen werden kann, muß er immer verworfen werden, bevor ein grüner Frame verworfen wird. In der bevorzugten Ausführungsform werden Verwurfssteuerlogikeinheiten (DCL-Einheiten) 424 abwärts des Markierungsgenerators 422 verwendet, um die Marke auf jedem Frame zu prüfen und gegebenenfalls selektiv den Frame als eine Funktion der Systemressource, einschließlich Überlastung, zu verwerfen.

[0031] In der bevorzugten Ausführungsform sind die CIR und EBS als Bandbreitenzähler implementiert, die mit einem "Konform"-Bucket beziehungsweise einem "Überlauf"-Bucket verbunden sind. Die maximale Größe jedes Zählers beträgt 256 kbyte und ist durch den Netzadministrator programmierbar. Jeder Zähler wird mit einer programmierbaren Einheit von Token oder Bytes "bezahlt", die eine Quantität der Bandbreite oder der Anzahl der Frames zum Beispiel darstellen. Die Token werden durch Frames "verbraucht" durch Abziehen der Länge des Frames vom Konform-Bucket oder Überlauf-Bucket, in Abhängigkeit von der Flußrate. Insbesondere wird die Größe eines kommenden Frames mit der akkumulierten Bezahlung in jedem Zähler verglichen. Wenn die Größe größer als die Bezahlung ist, hat der Frame gegen den Zähler "verstoßen" und muß markiert werden. Ein Frame, der nicht gegen den Konform-Bucket verstößt, wird nicht markiert, und in den globalen Pufferspeicher, MAC-Pufferspeicher 306, eingereiht. Die Bezahlung gleich der Länge des Frames wird dann vom Konform-Zähler abgezogen. Ein Frame, der gegen den Konform-Bucket verstößt, wird "gelb" markiert und dann in den Pufferspeicher eingereiht. Die Bezahlung gleich der Länge des Frames wird dann vom Überlauf-Zähler abgezogen. Frames, die gegen sowohl den Konform-Bucket als auch den Überlauf-Bucket verstoßen, werden "rot" markiert und verworfen.

[0032] In einem periodischen Intervall werden der Konform-Bucket oder der Überlauf-Bucket bezahlt sein und die Token auf einen programmierbaren maximalen Wert nachgefüllt sein. In der bevorzugten Ausführungsform können die zwei Zähler mit verschiedenen Werte der Bezahlung programmiert sein, auch wenn die Zunahme zum gleichen Zeitintervall erfolgt. Der Fachmann wird verstehen, daß die Bezahlung für den Konform-Bucket immer kleiner als die Bezahlung des Überlauf-Buckets sein muß und daß der Überlauf-Bucket erst bezahlt wird, nachdem der Konform-Bucket die maximale Bezahlung hat.

[0033] Der Konform-Bucket steuert die garantierte Datenrate und der Überlauf-Bucket steuert die Spitzendatenrate. Beide Raten sind programmierbar, haben eine Granularität von 64 kbit/s und können von 64 kbit/s bis 1 Gbit/s reichen. Die rot markierten Frames werden im MAC-Vorprozessor 220 verworfen. Die gelb markierten

Frames werden vorzugsweise durch die seriellen Hochgeschwindigkeitsschnittstelle **330** zum Netzwerkprozessor **130** transportiert.

[0034] Außer den TCM-Verkehrsparametern, die verwendet werden, um das Policing zu implementieren, ruft der FSE 404 ebenfalls einen oder mehr VLAN-Kennungen ab, die auf den kommenden Frame anwendbar sind. In der bevorzugten Ausführungsform werden die eine oder mehr VLAN-Kennungen von einem Tag-Optionsfeld im VLAN-Informationsfeld 514 der Tabelle 510 der Flußdatenbank 406 abgeleitet. Wenn der anwendbare VLAN-Tag identifiziert ist, wird der VLAN-Tag in die VLAN ID-Datenbank 410 geschrieben, wo er für das VLAN-Pushmodul 308 zu Zwecken der Durchführung der 802.1Q VLAN-Markierung zu Verfügung gestellt wird.

[0035] Der Policer 304 sendet dann die vom Eingangs-DCL 424 durchgelassenen Frames an den MAC-Pufferspeicher 306. Der MAC-Pufferspeicher 306 schließt einen globalen 512-Kilobyte-Pufferspeicher ein, der durch zwölf Empfangs-MAC-Schnittstellen 210 gemeinsam genutzt wird. Der 512-Kilobyte-Pufferspeicher ist in 8192 Chunks zu 64 Bytes unterteilt. Im Allgemeinen werden die von den verschiedenen MAC-Schnittstellen 210 gelesenen Frames im Empfangspufferspeicher in ihrer Reihenfolge des Eintreffens gespeichert.

[0036] In der bevorzugten Ausführungsform kann der MAC-Vorprozessor 200 in einer überbelegten Umgebung implementiert werden, wo die Sammeleingabe des MAC-Vorprozessors 200 von der MAC-Schnittstelle 210 die Kapazität des MAC-Prozessors 200 übersteigt, um sie an den Netzwerkprozessor 130 zu senden. Als solche werden ein oder mehr Frame-Verwurf-Algorithmen verwendet, um alle kommenden Frames zu verwerfen, wenn der MAC-Pufferspeicher 306 voll ist. Die Verwurf-Algorithmen können verwendet werden, um Frames auf der Basis verschiedener Faktoren zu verwerfen, einschließlich der Priorität des kommenden Pakets wie in der US-Patentschrift Nr. 10/068,710 gelehrt wurde. Die kommenden Frames werden verworfen, wenn mindestens ein 64 Byte-Chunk des MAC-Pufferspeichers 306 nicht frei ist.

**[0037]** In der bevorzugten Ausführungsform sind die Frame-Verwurf-Algorithmen auf vier Ebenen implementiert:

- auf der Ebene des Frameparsers 402, der dem MAC-Pufferspeicher 306 vorangeht;

- am Eingang des MAC-Pufferspeichers **306** über ein Protokoll-CAM (nicht gezeigt) und Frameprioritätsdeskriptoren;

- auf der Schreibzeit des MAC-Pufferspeichers **306** unter Verwendung der Schwellenwerte Weighted Early Random Discard (WRED) oder FIFO, d. h. "Wasserzeichen", die das Verwerfen der Frames an einer Vielzahl von FIFO MAC-Pufferspeichern **306** auslösen, wobei jeder FIFO mit der Priorität für einen der zwölf Ports verbunden wird; und

- auf der Schreibzeit des MAC-Pufferspeichers **306** über einen klassenbasierten, d. h. prioritätsbasierten, FIFO-Warteschlangenausgliederungsalgorithmus.

[0038] Der Fachmann wird verstehen, daß in einer überbelegten Umgebung die Anwesenheit des Verkehrs-Policers 304 besonders wichtig ist, da er eine intelligente Möglichkeit bereitstellt, um die Frames frühzeitig zu verwerfen, und verhindert, daß Außerprofil-Frames unnötigerweise die Ressourcen und Speicher im MAC-Pufferspeicher 306 verbrauchen. Durch Eliminieren störender Frames vor der Verarbeitung und Pufferspeicherung wird der Netzwerkprozessor 130 von der Last der Verarbeitung der Frames entlastet und die Wahrscheinlichkeit des Verwerfens eines gültigen Frames aufgrund fehlenden verfügbaren Pufferspeicherplatzes und anderer Ressourcen wird minimiert.

[0039] Mit der Freigabe der Frames vom MAC-Pufferspeicher 306 werden einzelne Frames an das VLAN-Pushmodul 308 gesendet, wo ein oder mehr VLAN-Tags in ausgewählte Frames eingefügt werden. In der bevorzugten Ausführungsform ruft das VLAN-Pushmodul 308 eine oder mehr VLAN IDs und/oder andere VLAN-Informationen aus der VLAN ID-Datenbank 410 ab, die vorher dort durch den FSE 404 platziert wurden, nachdem der Frame während der Policing-Operation klassifiziert wurde. Die neuen VLAN-Tag-Informationen können an den Frame in Form eines neuen VLAN-Tags angehängt werden oder verwendet werden, um eine Tag-Information zu ersetzen, die in einem existierenden VLAN-Tag anwesend ist. Die Art und Weise, auf welche die Tags, die aus der VLAN ID-Datenbank 410 abgerufen wurden, zu verwenden sind, wird durch die Tag-Optionsbits aus dem VLAN-Informationsfeld 514 der Tabelle 510 bestimmt. Das Feld für Rahmenprüfsequenz (FCS) wird ebenfalls modifiziert, um die Länge des Frames mit dem neuen Tag zu berücksichtigen.

**[0040]** In einigen alternativen Ausführungsformen schließt das VLAN-Pushmodul **308** einen VLAN-CAM ein, der angepaßt ist, um die entsprechende VLAN ID auf der Basis einer Übereinstimmung eines oder mehr Framefelder, einschließlich Quellport und kommendes VLAN-Tag, zum Beispiel zu identifizieren. Der überein-

stimmende Eintrag im VLAN-CAM zeigt dann auf einen neuen Tag, der dann auf das Paket gelegt oder verwendet wird, um einen existierenden Tag zu ersetzen.

[0041] Das Merkmal des VLAN-Pushing, das ein Merkmal des VLAN-Stacking einschließt, ist angepaßt, um soviel wie möglich 128 QoS-Regeln/VLAN-Einträge zu speichern und zu nutzen, obgleich mehr als möglich. In der bevorzugten Ausführungsform stellen ungefähr 128 VLAN-Einträge, die auf dem MAC-Prozessor 210 im Allgemeinen gehalten werden, eine Teilmenge aller QoS-Regeln/VLANs dar, die durch die Vermittlungseinrichtung 100 unterstützt werden. Die Teilmenge der QoS-Regeln/VLANs, die durch einen gegebenen MAC-Prozessor 200 unterstützt wird, stellt die minimale Menge der QoS-Regeln/VLANs dar, die mit dem Verkehr auf der lokalen MAC-Schnittstelle 210 verbunden sind, während QoS-Regeln ausgeschlossen werden, die für den einzelnen MAC-Prozessor nicht relevant sind. Das bietet mindestens zwei Vorteile. Erstens, die Tiefe des CAM, die notwendig ist, um nach dem anwendbaren VLAN zu suchen, ist kleiner und, zweitens, entlastet die lokale VLAN-Verarbeitung den Netzwerkprozessor von der Verantwortung, die VLAN-Markierung und Stacking durchzuführen.

[0042] Vom VLAN-Pushmodul 308 gehen die Frames an einen Eingangsratenpufferspeicher 312, der für das Übertragen der Frames mit einer relativ gleichmäßigen Rate an die Hochgeschwindigkeitsschnittstelle (HSS-Schnittstelle) 316 über einen Eingangsdatenbussender 314 verantwortlich ist. Die Hochgeschwindigkeitsschnittstelle (HSS-Schnittstelle) 316 koppelt funktionsfähig den MAC-Vorprozessor 220 mit dem Netzwerkprozessor 130 mittels eines Paket-Streamingbusses, der dem Fachmann weithin bekannt ist. Der Paket-Streamingbus kann auch den Netzwerkprozessor 130 mit jedem der Vielzahl der MAC-Prozessoren 200 funktionsfähig koppeln.

[0043] Außer dem eingehenden Sendeverkehr empfängt jeder der Vielzahl der MAC-Prozessoren 200 ebenfalls ausgehenden Verkehr vom Netzwerkprozessor 130. Der ausgehende Verkehr, der für den Port einer lokalen PHY-Schnittstelle 240 bestimmt ist, wird durch den MAC-Postprocessor 230 am Ausgangsbusempfänger 320 über die HSS-Schnittstelle 200 empfangen. Die ausgehenden Frames werden vorübergehend auf dem Ausgangsratenpufferspeicher 322 zwischengespeichert und anschließend mit einer relativ gleichmäßigen Rate an das VLAN-Pop-Modul 326 übertragen.

[0044] In einigen Ausführungsformen schließt der Ratenpufferspeicher 322 außerdem einen Verkehrsformer 324 ein, der angepaßt ist, um bandbreitenbasierte Flußsteuerung für den ausgehenden Verkehr durchzuführen, der durch den MAC-Prozessor 200 empfangen wurde. Der Verkehrsformer 324 in der bevorzugten Ausführungsform regelt die Ausgangsbandbreite des MAC-Postprozessors 230 unter Verwendung eines einzelnen Token-Bucket-Algorithmus zusammen mit einem oder mehr Buckets, wobei jeder Bucket einer Flußklasse zugeordnet wird. Token, die jedem Bucket zugeordnet wurden, der unter Verwendung eines "Konform-Zählers" überwacht wird, stellen die Kapazität für jede Flußklasse dar. Jedesmal beim Übertragen eines Frames vom Ratenpufferspeicher 322 werden mehrere Token, die die Länge des Frames darstellen, vom zugeordneten Konform-Zähler abgezogen. Wenn nicht ausreichend Token vorhanden sind, um den Frame zu übertragen, wird die Übertragung des Frames vom Ratenpufferspeicher ausgesetzt, bis die Token anschließend aufgefüllt sind. Obgleich der Former 324 im Allgemeinen keine Frames verwirft, kann das vorübergehende Sperren des Buckets für ein längeres Zeitintervall zur Verstärkung der Switch Fabric (nicht gezeigt) und/oder Verwerfen der Frames an einer Eingangsvermittlungseinrichtung führen.

**[0045]** Frames, die einer Flußklasse zugeordnet sind, werden noch einmal übertragen, nachdem die Token aufgefüllt sind. In der bevorzugten Ausführungsform werden die Konform-Zähler mit einer maximalen Anzahl von Token in einem regulären Zeitintervall bezahlt, das programmierbar durch den Netzadministrator festgelegt wird. In der bevorzugten Ausführungsform kann die Formung auf Port, VLAN und Priorität oder jeder Kombination davon basieren.

[0046] Das VLAN-Pop-Modul 326 angepaßt ist, um einen existierenden Tag auf einem ausgehenden Frame zu entfernen oder um VLAN-Taginformationen in einem existierenden Tag oder einen Tag, der vorher auf dem VLAN-Pushmodul 308 der Eingangsvermittlungseinrichtung eingefügt wurde, zu ersetzen. Das VLAN-Pop-Modul 326 der bevorzugten Ausführungsform, die in Fig. 6 dargestellt ist, umfaßt einen zweiten Parser 602 zum Extrahieren eines oder mehr Bits oder Felder aus dem ausgehenden Frame und eine Ausgangsfluß-Suchmaschine 604 zum Erzeugen eines Schlüssels in einem Ausgangs-CAM 605, der bei Übereinstimmung einen Zeiger auf die VLAN-Kennungsdatenbank 606 ergibt. In der VLAN-Kennungsdatenbank 606 eingeschlossen sind die VLAN-Zuordnungsregeln, die in Optionsbits ausgeführt sind, die Anweisungen bereitstellen, um eine oder mehr existierende VLAN-Tags, falls anwendbar, zu entfernen oder zu ersetzen. Die VLAN-Tag-Verarbeitungsanweisungen werden an den Framer 610 übertragen, der für die Änderung des Fra-

mes vor der Übertragung an die entsprechende MAC-Schnittstelle **210** über den Ausgangsbus **334** verantwortlich ist. Falls anwendbar, wird ein neues CRC-Feld an den Frame angehängt, bevor er im Netzwerk ausgesendet wird.

[0047] Der MAC-Postprocessor 230 der bevorzugten Ausführungsform schließt außerdem ein Statistikerfassungsmodul (SAM) 350 zum Kompilieren der Flußstatistik von jeder MAC-Schnittstelle 210 ein. In der bevorzugten Ausführungsform wird die Statistik pro Port oder pro VLAN erfaßt. Nach der Kompilierung wird die Statistik durch den SAM 350 an eine zentrale Verwaltungsentität gesendet, die im Verwaltungsmodul 150 oder an einem anderen Ort vorhanden ist, der für jeden der einen oder mehr Vermittlungseinrichtungen 100 zugänglich ist. Wenn der SAM 350 mit einem einfachen Simple Network Management (SNMP) Client freigegeben ist, kann die zentrale Verwaltungsentität periodisch die Statistik unter Verwendung der SNMP-Nachrichten, die über die Befehls- und Bedienschnittstelle 340 transportiert werden, herunterladen.

[0048] Die in der bevorzugten Ausführungsform erfaßte Statistik schließt die Gesamtmenge der Statistik der Remote Monitoring (RMON) und Managed Information Base (MIB)-II von jeder der Vielzahl der MACs 210 über den ersten Statistikkanal 336 ein. RMON ist in einer Vielzahl von Request For Comment (RFC) dargelegt, die dem Fachmann bekannt sind, während MIB-II in RFC 1213 dargelegt ist, mit dem Titel "Management Information Base for Network Management of TCP/IP-based internets". In der bevorzugten Ausführungsform erfaßt SAM 350 außerdem Statistik, die notwendig ist, um QoS-Merkmale wie zum Beispiel VLAN-Statistik und Statistik, die relevant für Übereinstimmung des Switch Monitoring (SMON) ist, zu implementieren; die SMON-Anforderungen sind in der Internet Engineering Task Force (IETF) Request For Comment (RFC) 2613 mit dem Titel "Remote Network Monitoring MIB Extensions for Switched Networks" dargelegt, hiermit durch Verweis hier aufgenommen.

[0049] Die VLAN-Statistik wird vorzugsweise pro VLAN-Eintrag für den eingehenden Stream durch die Eingangs-FSE 404 und für den ausgehenden Stream durch die Ausgangs-FSE 604 erfaßt, wie durch den Eingangsstatistikkanal 338 beziehungsweise den Ausgangsstatistikkanal 339 dargestellt ist. Bezüglich des eingehenden Verkehrs erfaßt der SAM 350 die folgende Statistik pro VLAN-Eintrag, der durch den MAC-Vorprozessor 220 unterstützt wird:

Anzahl der am MAC-Pufferspeicher 306 eingereihten Bytes;

Anzahl der am MAC-Pufferspeicher 306 eingereihten Pakete;

Anzahl der durch den Verkehrs-Policer 304 verworfenen Bytes;

Anzahl der durch den Verkehrs-Policer 304 verworfenen Pakete;

Anzahl der am MAC-Pufferspeicher 306 eingereihten Nicht-Unicast-Bytes;

Anzahl der am MAC-Pufferspeicher 306 eingereihten Nicht-Unicast-Pakete;

Anzahl der durch den Verkehrs-Policer 304 verworfen Nicht-Unicast-Bytes; und

Anzahl der durch den Verkehrs-Policer 304 verworfen Nicht-Unicast-Pakete.

**[0050]** Bezüglich des ausgehenden Verkehrs erfaßt und kompiliert der SAM **350** vorzugsweise Statistiken pro Port und pro VLAN-Eintrag. Die erfaßte Statistik wird in die Anzahl der aus der Warteschlange entfernten Bytes und die Anzahl der aus der Warteschlange entfernten Pakete zum Beispiel unterteilt. Wenn der Frame eine Vielzahl von VLAN-Tags einschließt, wird die Statistik auf dem äußeren Tag akkumuliert.

**[0051]** Die folgenden Merkmale und die folgende Einrichtung, separat oder in Kombination, bilden ebenfalls die vorteilhaften Ausführungsformen der beanspruchten und/oder beschriebenen Erfindung:

- Die beanspruchte und/oder beschriebene Vermittlungseinrichtung, in welcher Ausgangsframestatistik als eine Funktion der Bitübertragungsschicht-Schnittstelle kompiliert wird;

- Die beanspruchte und/oder beschriebene Vermittlungseinrichtung, in welcher die Ausgangsframestatistik außerdem als eine Funktion des VLAN-Eintrags kompiliert wird;

- Die beanspruchte und/oder beschriebene Vermittlungseinrichtung, in welcher die durch das Statistikerfassungsmodul kompilierte Statistik die Ausgangsframestatistik umfaßt;

- Ein Data Link Layer-Prozessor, umfassend: einen oder mehr Media Access Controller (MACs) zum Empfangen eines Frames von einem Kommunikationsnetz; und ein Statistikerfassungsmodul, das funktionsfähig mit dem einen oder mehr MACs gekoppelt ist, zum Kompilieren der Statistik, die mit jedem der Vielzahl der MACs verbunden ist.

**[0052]** Obgleich die Beschreibung oben viele Spezifikationen enthält, sollten diese nicht als den Anwendungsbereich der Erfindung einschränkend ausgelegt werden, sondern nur als Illustrationen einiger derzeit bevorzugter Ausführungsformen dieser Erfindung bereitstellend.

**[0053]** Außerdem ist die Erfindung beispielhaft und ohne Einschränkung offenbart worden, und es sollte auf die folgenden Patentansprüche verwiesen werden, um den Anwendungsbereich der vorliegenden Erfindung zu bestimmen.

| Bezugszeichen | Englisch | Deutsch                               |

|---------------|----------|---------------------------------------|

| FIG. 1        |          |                                       |

| 107           |          | MANAGEMENTBUS                         |

| 100           |          | VERMITTLUNGSEINRICHTUNG               |

| 150           |          | VERWALUNGSMODUL                       |

| 130           |          | NETZWERKPROZESSOR                     |

| 132           |          | KLASSIFIZIERER                        |

| 134           |          | SENDEPROZESSOR                        |

| 136           |          | AUSGANGSPROZESSOR                     |

| 106           |          | DATENBUS                              |

| 102           |          | ZUGANGSMODUL                          |

| 102           |          | ZUGANGSMODUL                          |

| 102           |          | ZUGANGSMODUL                          |

| 142           |          | WARTESCHLANGENMANAGER                 |

| 104           |          | FABRIC-SCHNITTSTELLENMO-<br>DUL       |

| 144           |          | SCHEDULER                             |

| 142           |          | EINGANGSWARTESCHLAN-<br>GENMANAGER    |

| 146           |          | AUSGANGSWARTESCHLAN-<br>GENMANAGER    |

|               |          |                                       |

| FIG. 2        |          |                                       |

| 102           |          | ZUGANGSMODUL                          |

| 200           |          | MAC-Prozessor                         |

| 220           |          | MAC-VORPROZESSOR                      |

| 230           |          | MAC-POSTPROZESSOR                     |

| 210           |          | MAC                                   |

| 240           |          | PHY                                   |

|               |          |                                       |

| FIG. 3        |          |                                       |

| 200           |          | MAC-PROZESSOR                         |

| 330           |          | HSS-SCHNITTSTELLE                     |

| 340           |          | BEFEHLS- UND BEDIEN-<br>SCHNITTSTELLE |

| 220           |          | EINGANGSBUS TX                        |

| 230           |          | AUSGANGSBUS RX                        |

| 312           |          | RATENPUFFERSPEICHER                   |

| 322           |          | RATENPUFFERSPEICHER                   |

| 308           |          | VLAN-PUSH                             |

| 324           |          | FORMER                                |

| 306           |          | MAC-PUFFERSPEICHER                    |

| 326           |          | VLAN-POP                              |

| 304    | POLICER                       |

|--------|-------------------------------|

| 302    | RX-FIFO                       |

| 350    | STATISTIKERFASSUNGSMO-<br>DUL |

| 210    | MAC                           |

|        |                               |

| FIG. 4 |                               |

| 406    | FLUß-DB                       |

| 408    | POLICING-DB                   |

| 410    | VLAN ID DB                    |

| 306    | MAC-PUFFERSPEICHER            |

| 304    | POLICER                       |

| 404    | FLUßSUCHMASCHINE              |

| 405    | EINGANGS-CAM                  |

| 424    | EINGANGS-DCL                  |

| 402    | PARSER                        |

| 420    | EINGANGSZÄHLMODUL             |

| 422    | MARKIERUNGSGENERATOR          |

| 302    | RX-FIFO                       |

|        |                               |

| FIG. 5 |                               |

| 502    | SRC PRT                       |

| 504    | TAGZUSTAND                    |

| 506    | ORIGINAL-TCI                  |

| 512    | OPTIONEN                      |

| 514    | VLAN-INFO                     |

| 516    | BANDBREITE                    |

| FIG. 6 |                               |

| 322    | RATENPUFFERSPEICHER           |

| 608    | VLAN ID DB                    |

| 602    | PARSER                        |

| 610    | FRAMER                        |

| 604    | FLUßSUCHMASCHINE              |

| 605    | AUSGANGS-CAM                  |

| 326    | VLAN POP-MODUL                |

| 320    | VLAN POP-INIODOL              |

### Patentansprüche

1. Eine Vermittlungseinrichtung (100) umfassend: einen Netzwerkprozessor (130), eine Vielzahl von Bitübertragungsschicht-Schnittstellen (240), zum Empfangen eines oder mehr Frames von einem Kommunikationsnetz, wobei der Netzwerkprozessor (130) funktionsfähig mit dem Kommunikationsnetz über eine Vielzahl von Netzzugangsmodulen (102) gekoppelt ist, in welcher jedes Netzzugangsmodul (102) einen Data Link Layer-Prozessor (200) umfaßt, wobei die Vermittlungseinrichtung (100) dadurch gekennzeichnet ist, daß jeder Data Link Layer-Prozessor (200) eine Vielzahl von Media Access Controllern (210) umfaßt, die jeder funktionsfähig mit einer der Bitübertragungsschicht-Schnittstellen (240) gekoppelt sind, und ein Statistikerfassungsmodul (350), das funktionsfähig mit den Media Access Controllern (210) gekoppelt ist, zum Kompilieren von Statistiken über jeden der Vielzahl der Media Access Controller (210), und dadurch, daß der Netzwerkprozessor (130) konfiguriert ist, um ein oder mehr Frames zu routen, die von der Vielzahl der Data Link Layer-Prozesso-

ren (200) empfangen wurden.

- 2. Die Vermittlungseinrichtung (**100**) nach Anspruch 1, in welcher jeder Data Link Layer-Prozessor (**200**) außerdem eine oder mehr Flußsuchmaschinen (**404**) zum Klassifizieren eines oder mehr Frames auf der Basis einer oder mehr Eigenschaften umfaßt, die den Frames zugeordnet sind.

- 3. Die Vermittlungseinrichtung (**100**) nach Anspruch 2, in welcher eine oder mehr Eigenschaften einen Quellport, einen VLAN-Tag-Zustand, eine VLAN-Kennung und eine VLAN-Tag-Steuerinformation, TCI, Feld umfassen.

- 4. Die Vermittlungseinrichtung (**100**) nach Anspruch 2, in welcher die eine oder mehr Flußsuchmaschinen (**404**) eine oder mehr Assoziativspeicher (CAMS) umfassen.

- 5. Die Vermittlungseinrichtung (**100**) nach Anspruch 4, in welcher eine oder mehr CAMs, die jedem der Vielzahl der Data Link Layer-Prozessoren (**200**) zugeordnet sind, QoS-Regeln umfassen, die sich auf die zugeordnete Vielzahl der Bitübertragungsschicht-Schnittstellen (**240**) beziehen.

- 6. Die Vermittlungseinrichtung (**100**) nach Anspruch 1, in welcher die Data Link Layer-Prozessoren (**200**) MAC-Prozessoren (Media Access Controller-Prozessoren) sind.

- 7. Die Vermittlungseinrichtung (100) nach Anspruch 1, in welcher die Vermittlungseinrichtung (100) aus der Gruppe ausgewählt ist, bestehend aus: einem Router, einer Multilager-Vermittlungseinrichtung (100) und einem Switch-Blade.

- 8. Die Vermittlungseinrichtung (100) nach Anspruch 1, in welcher die Statistik, die durch das Statistikerfassungsmodul (350) kompiliert wurde, die Statistik eingehender Frames umfaßt.

- 9. Die Vermittlungseinrichtung (**100**) nach Anspruch 8, in welcher die Statistik eingehender Frames als eine Funktion des VLAN-Eintrags kompiliert ist.

- 10. Die Vermittlungseinrichtung (100) nach Anspruch 9, in welcher die Statistik eingehender Frames, die als eine Funktion des VLAN-Eintrags kompiliert ist, umfaßt: die Anzahl der Bytes, die am Data Link Layer-Prozessor (200) in die Warteschlange eingereiht wurden; die Anzahl der Frames, die am Data Link Layer-Prozessor (200) in die Warteschlange eingereiht wurden; die Anzahl der Nicht-Unicast-Bytes, die am Data Link Layer-Prozessor (200) in die Warteschlange eingereiht wurden; und die Anzahl der Nicht-Unicast-Frames, die am Data Link Layer-Prozessor (200) in die Warteschlange eingereiht wurden.

Es folgen 5 Blatt Zeichnungen

# Anhängende Zeichnungen

FIG. 2

FIG. 3