### (12) UK Patent Application (19) GB (11) 2 292 494 (13) A

(43) Date of A Publication 21.02.1996

(21) Application No 8600277.1

(22) Date of Filing 07.01.1986

(30) Priority Data

(31) 8500185

(32) 08.01.1985

(33) FR

(71) Applicant(s)

Thomson-CSF

(Incorporated in France)

173 Boulevard Haussmann, 75008 Paris, France

(72) Inventor(s)

Philippe Elleaume

(74) Agent and/or Address for Service

F J Cleveland & Co 40-43 Chancery Lane, LONDON, WC2A 1JQ, **United Kingdom**

(51) INT CL6 G01S 7/288

(52) UK CL (Edition O)

H4D DSPX D360 D40X D402

**H4P PDRX**

(56) Documents Cited

GB 1113431 A EP 0145056 A2 US 4224575 A MI Skolnik, "Radar Handbook", 1970, McGraw-Hill,

pages 3-30 and 20-18

Field of Search

UK CL (Edition H) H3A, H3H, H4D

INT CL4 H03D

#### (54) Process for the phase detection of a received radar signal

(57) The present invention detection relates to a process consisting in sampling the intermediate frequency signal at a sampling frequency  $f_{e}$  such that  $f_{e}$  is equal to  $\alpha$  B,  $\alpha$  being a number greater than or equal to 2 and B being the width of the pass-band, the intermediate frequency fi and the sampling frequency being in a ratio such that  $f_i = (k \pm 1/4)f_{e'}$  k being an integer. The invention is applied.

# PROCESS FOR THE PHASE AMPLITUDE DEMODULATION OF A RECEIVED RADAR SIGNAL AND DEVICE IMPLEMENTING SUCH A PROCESS

The present invention relates to devices for the phase amplitude demodulation of a received radar signal, this demodulation generally taking place after transposition of the UHF signal into intermediate frequency.

Traditionally, radars in which Doppler filtering or digital pulse compression is carried out necessitate the use of receivers including a coherent detection device. These devices which are also called demodulators give information on the amplitude and phase of the received signals. These coherent detection radar receivers therefore include, after an intermediate frequency amplifier, two phase amplitude detectors which work together in quadrature in order to carry out amplitude and phase demodulation. This demodulation consists in shifting the whole spectrum of the carrier frequency in order to bring one of the two spectra (real spectrum or image spectrum) into base band. Then, a low pass filtering is carried out in order to eliminate the image spectrum. These phase amplitude detectors are controlled by the output signal of a local reference oscillator at intermediate frequency. The video output signals are generally called I and 6.

Now, the two channels I and Q which come from the two phase amplitude detectors, are followed by two sampling and coding devices. A balance fault between these two channels I and Q can appear at the point of phase amplitude detection, which gives a slight unbalance in amplitude in these two channels and also a quadrature fault, in other words a phase shift slightly different from 90° from the local oscillator reference signal FI also gives a phase unbalance in the two channels I and Q.

These faults can be compensated for by adjustment loops associated with very powerful computation

algorithms but despite everything they remain an element limiting the performance of radar signal processing devices. In particular they cause a rising of secondary tobes at the output of the Doppler filters which is undesirable. In the same way this rising of secondary tobes also appears in digital pulse compression devices whereas it is required to reduce the secondary tobes as much as possible.

Another solution solving this problem of balance consists in using devices for the automatic balancing of the gain and the quadrature of the video signals I and Q. A description of this solution can be found in the following articles: "Radar Conference 82" IEE Conference publication number 216 p.46. "Sacrifices in radar clutter suppression due to compromises in implementation of digital Doppler filter". I.W. TAYLOR; or IEE Trans. AES 17 p. 131 "the correction of I and Q errors in a coherent processor". The implemented devices are not however always simple and sometimes complicate the production of signal processing devices.

The present invention relates to a process for the phase amplitude demodulation of a received radar signal consisting in the direct sampling of the intermediate frequency  $\mathbf{f}_i$  received signal at a frequency of  $\mathbf{f}_e$  which is lower than that intermediate frequency.

In fact, one characteristic of the process consists in sampling the  $f_i$  signal at a frequency  $f_e$  equal to  $\infty$  B, B corresponding to the reception pass band and  $\infty$  being a positive number greater than or equal to 2.

Another characteristic of the invention consists in then carrying out a sub-sampling at a frequency  $f^{\dagger}_{e}$  such that  $f^{\dagger}_{e}$  is approximately equal to B, before or after having brought the signal into baseband by demodulation.

The present invention also relates to a radar receiver implementing the process, which according to a first embodiment includes an intermediate frequency amplifier

followed by an analog-digital converter, this converter being followed by a digital processing circuit.

The present invention also relates to a radar receiver implementing the process, which according to a second embodiment includes an intermediate frequency amplifier, a demodulator which brings the intermediate frequency signal to a frequency fig, such that  $f'_i = f_{0L} - f'_e$ ,  $f_{0L}$  being the frequency of the local oscillator and f'e being the sub-sampling frequency, this demodulator being followed by an analogdigital converter.

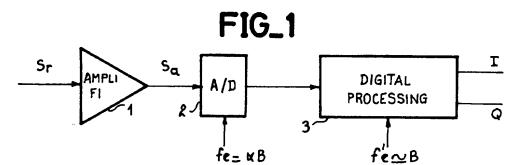

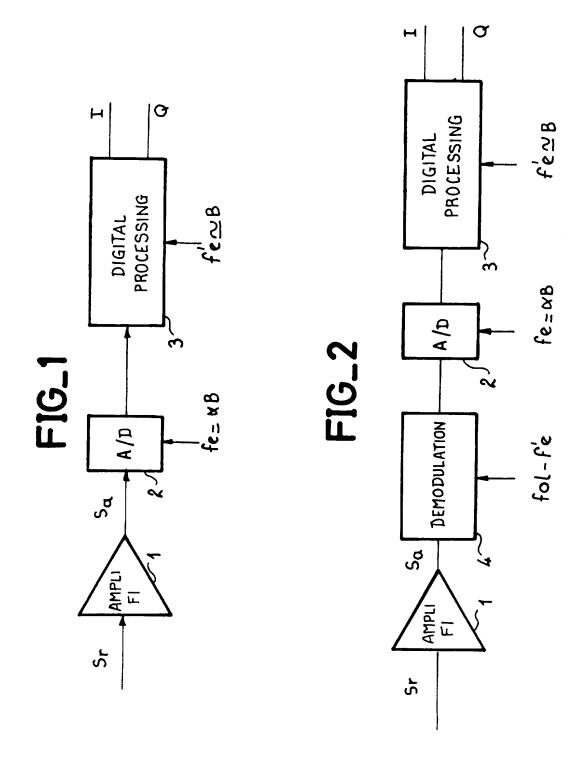

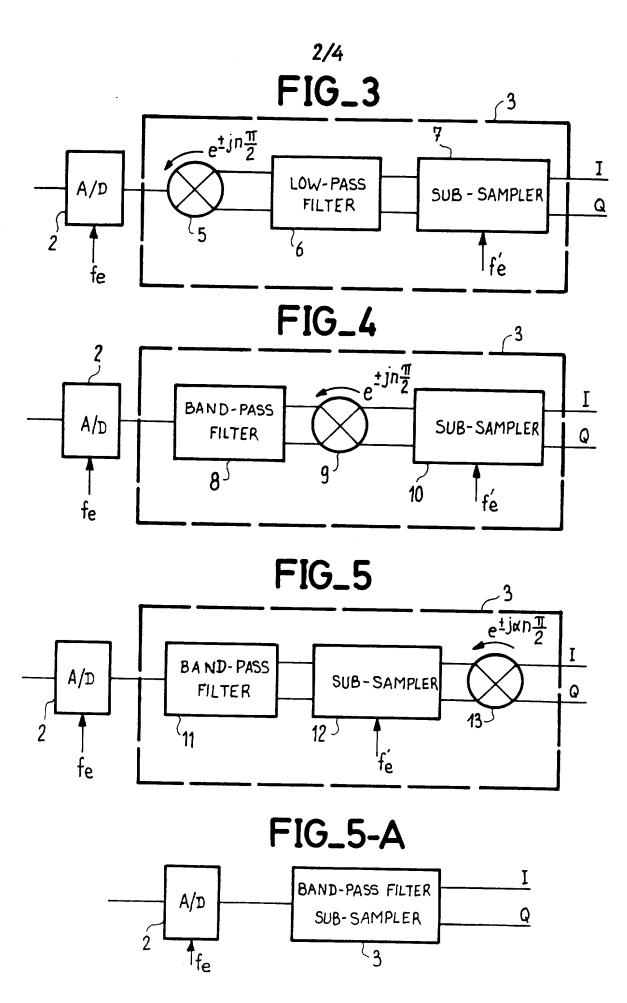

Other characteristics and advantages of the present invention will clearly appear on reading the following description given by way of non-limiting example and with reference to the appended drawing in which: - Figure 1 shows the general block diagram of a first embodiment of the device according to the invention; - Figure 2 shows the general block diagram of a second embodiment of the device according to the invention; - Figure 3 shows the basic block diagram of a first variant embodiment of the digital processing circuit; - Figure 4 shows the basic block diagram of a second variant embodiment of the digital processing circuit; - Figure 5 shows the basic block diagram of a third variant embodiment of this same circuit;

- Figure 5A shows a special case relating to Figure 5;

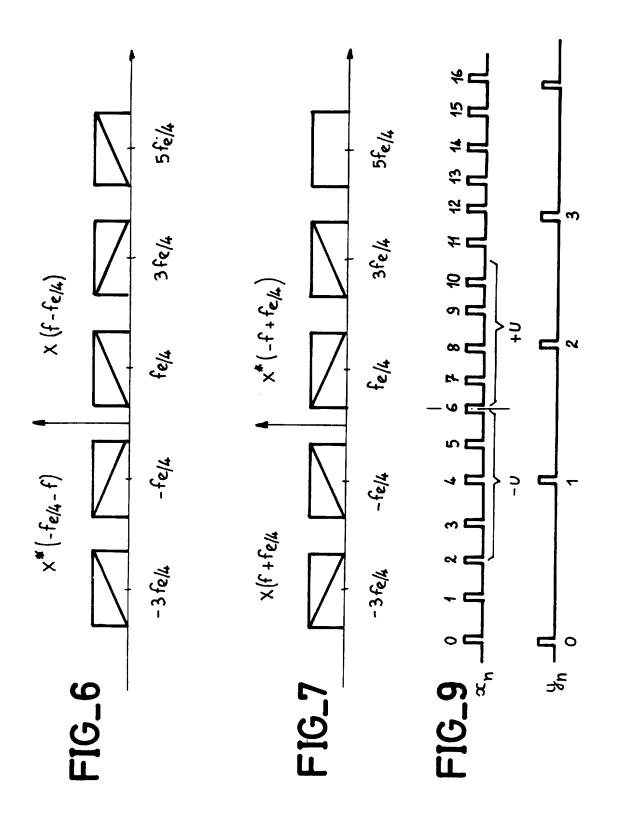

- Figures 6 and 7 show the spectra of the signal after sampling according to the first and second variant embodiments respectively;

- Figure 8 shows a particular embodiment of the digital processing circuit;

- Figure 9 shows a series of samples at frequency f. and at frequency f

The process according to the invention consists in sampling the received signal transposed into intermediate frequency. The sampling frequency fe is chosen equal to of times the reception pass band B, of being a

number greater than or equal to 2. The process then consists in carrying out a digital processing in order to provide digital signals representing the amplitude and the phase of the received signal.

Elements having the same function for the purpose of the same result are given the same references.

The general block diagram of the device implementing the process according to the invention is shown in figure 1. It is a first embodiment wherein the device includes an intermediate frequency amplifier 1, an analog-digital converter 2, and a digital processing circuit 3. The amplifier 1 receives the radar signal  $S_r$  transposed into intermediate frequency and amplifies it. The amplified signal  $S_a$  is sampled by the converter 2 at a frequency of  $f_e$  equal to  $\ll B_r$ , the sampled signal then being processed by circuit 3. This processing consists in particular in carrying out a sub-sampling at a frequency  $f_e$  such that  $f_e$  is approximately equal to  $g_e$ .

Figure 2 shows a second embodiment wherein the amplified intermediate frequency signal is demodulated by a demodulator 4 by a signal at intermediate frequency  $f^i{}_i$  such that  $f^i{}_i$  is equal to  $f_{0L}{}^-f_e/4$ ,  $f_{0L}$  being the frequency of the receiver's local oscillator. The signal coming from the demodulator 4 is sampled at frequency  $f_e$ ,  $f_e{}^- \bowtie B$ . The sampled signal is processed by the processing circuit 3.

Figures 3, 4 and 5 show the basic block diagrams of the processing circuit according to three variant embodiments.

According to the first variant the circuit 3 includes firstly a demodulator 5 which brings the useful signal into baseband, i.e. shifts the spectrum of the signal by at least plus or minus  $f_e/4(\pm f_e/4)$ . This circuit is followed by a low pass filter 6 which eliminates the conjugate image spectrum. The baseband signal is then sub-sampled at frequency  $f_e$  which is approximately equal to  $f_e$

In the second and third variants shown in figures 4 and 5 respectively the order in which the demodulation and filtering operations are carried out is changed. The solutions proposed in these two variants are equivalent to the first one. In fact, in Figure 4, a bandpass filter 8 filters the output signal of the converter 2. The filtered signal is then demodulated by the demodulator 9 and then sub-sampled at frequency field by circuit 10.

In Figure 5, there is also a band-pass filter 11 following the coder 2, a sub-sampler 12 which sub-samples at frequency f'e the signal coming from the filter 11. The demodulator 13 demodulates the output signal of the sub-sampler.

The principle of the invention therefore consists in sampling the signal on a carrier. In order to do this it is necessary that the pass-band of the intermediate frequency is matched to the useful band of the signal in order not to reduce the signal to noise ratio.

The sampling frequency chosen must satisfy the Shanonn Niquist criterion and its ratio with the intermediate frequency of the signal must enable an acceptable separation of the two bands of the signal (real and image spectra).

By choosing a sampling frequency f such that:

where ≪ ≥ 2

. .

and an intermediate frequency f; such that:

$$f_1 = (k + 1/4) f_e$$

k being an integer, the two imposed conditions are satisfied.

It is also noted that the second condition ensures not only the separation of the two bands but also the balancing of the inter-band difference. This difference is therefore:

The choice between + or - corresponds with the two possible positions of the bands with respect to the origin. The signal on carrier  $S_a$  (at the intermediate frequency) is expressed by a function of time t, namely y(t), this function y(t) having a Fourier transform Y(f) such that:

$$Y(f) = \frac{1}{2} \{X(f - f_i) + X^{H}(-f_i - f)\}$$

where X(f) represents the spectrum and  $\mathbf{X}^{\pm}$ (f) represents the image spectrum.

If  $\delta_{\tau}$  (t) is the sampling function:

$$\delta_{\tau}(t) = \sum_{n=-\infty}^{+\infty} \delta(t - n\tau)$$

$\tau = 1/f_e$

The sampled signal is therefore equal to z(t), such that:

$$z(t) = y(t)$$

.  $\delta_{\gamma}(t)$ , or:

$$z(t) = \sum_{n=-\infty}^{+-\infty} y_n \delta(t - n\tau)$$

where  $yn = y(n \tau)$ .

The spectrum of the sampled signal z(t) is expressed by its Fourier transform which is:

$$Z(f) = f e^{\int_{0}^{+\infty} y (f - nf_e)}$$

In the case in which  $f_i = (k-1/4)f_e$  is chosen, the spectrum shown in Figure 6 is obtained, namely:

$$Z(f) = \frac{1}{2} f_e \sum_{n=-\infty}^{+\infty} X(f - f_e/4 - nf_e) + X^{X} (-f - f_e/4 - nf_e)$$

The low pass filter will be passing between 0 and B/2 and attenuating between  $f_{\rm e}/2$  - B/2 and  $f_{\rm e}/2$  + B/2.

In the case in which  $f_i = (k+1/4)f_e$  is chosen, the spectrum shown in Figure 7 is obtained, namely:

$$Z(f) = \frac{1}{2} \qquad f_e \stackrel{+^{\infty}}{\Sigma} \{ X^{\Xi}(-f + f_e/4 - nf_e) + X(+f + f_e/4 + nf_e) \}$$

The band-pass filter will be passing between  $f_e/4$  - B/2 and  $f_e/4$  + B/2 and attenuating between  $3f_e/4$  - B/2 and  $3f_e/4$  + B/2.

The two solutions are of course equivalent. The processing after sampling therefore consists in restoring X(f) explicitly.

This processing therefore consists as has been described previously in bringing the useful signal into baseband, i.e. in shifting the spectrum by  $\pm$  f<sub>e</sub>/4 according to whether f<sub>i</sub> =  $(k \pm 1/4)$ f<sub>e</sub>, in eliminating the image spectrum by means of a low-pass (or band-pass) filter and in sub-sampling in order to approach a sampling frequency that satisfies the Shanonn criterion (f'  $\triangle$  B).

In the case in which the demodulation is carried out before the sub-sampling as shown in Figures 3 and 4, the following operation is carried out on each sample  $\mathbf{x}_{n}$ .

$$x_{n}^{t} = x_{n}^{t} e^{\frac{1}{2}\pi \frac{f_{e}}{4} n\tau}, \qquad \tau = 1/f_{e}$$

01:

..!

$$x'_{n} = x_{n} e^{\pm jn} \frac{\pi}{2}$$

This demodulation consists in fact in multiplying the modulo p, p=0,1,2,3 samples by the states representing  $e^{\frac{+j}{2}n\frac{\pi}{2}}$ , i.e. 1,  $\frac{+}{2}$  j, -1,  $\frac{+}{2}$  j. If  $x_0$ ,  $x_1$ ,  $x_2$  and  $x_3$  are the first four successive samples, these samples will be respectively multiplied by 1, +j, -1, -j if  $f_1 = (k+1/4)f_e$  or by (1, -j, -1, +j) if  $f_1 = (k-1/4)f_e$ .

The practical achievement of this operation is trivial for a specialist in the field as it is a matter of sign changes and exchanging of real and imaginary parts.

When the filtering takes place after the demodulation,  $x_n$  is of course real (Figure 3) and when the filtering takes place before the demodulation,  $x_n$  is complex (Figure 4).

In the case in which the demodulation is carried out after the sub-sampling as shown in Figure 5, the following operation is carried out:

$$x'_{n} = x_{n}e + j2m \frac{f_{e}}{4} \quad a\tau$$

In the special case in which  $\infty$  = 4 has been chosen, the demodulation disappears, circuit 3 carries out the band-pass filtering and the sub-sampling as shown in Figure 5A.

In other cases the following operation is carried out:

$$x'_{n} = x_{n}^{e} e^{\pm j\alpha \frac{\pi}{2}}$$

$e^{\pm jn\alpha \frac{\pi}{2}}$

Figure 8 shows a particular embodiment of the digital processing device 3 which corresponds with the case in which  $\alpha=4$ , i.e. that of Figure 5A. In this case the demodulation disappears. In addition the computing power that is used is reduced by a factor of 4 as only samples corresponding to the sub-sampling are computed.

Circuit 3 includes a processing circuit 20 which restores the real part of the signal, i.e the amplitude I. It also includes a processing circuit 40 which restores the imaginary part of the signal, i.e. the phase Q. Each of these two circuits carries out the filtering and the sub-sampling. The demodulation disappears as has been stated previously because of the particular choice of  $\alpha$ .

The series of samples  $x_n$ , n=0,1...N, is received at the input of each of the circuits 20 and 40. These two circuits carry out a digital filtering and the sub-sampling.

If  $y_n$  is the signal at the output of these circuits, the filtering and sub-sampling operation on the samples  $x_n$  is obtained by carrying out the following operations:

where  $\mathbf{h}_{\mathbf{u}}$  represents the complex coefficients of the digital filter produced.

Figure 9 shows a first line corresponding to a series of samples  $x_n$ , n=0, 1 ... N, and a second line corresponding to the series of samples at frequency  $f^*e$ . It is noted that a sample  $y_n$  corresponds with a sample  $x_{4n}$ . The filtering and sampling operation represented by equation (1) can be simplified by noting that if we consider u past samples and u future samples, the complex coefficient  $h_{-n}$  to be applied for a given sample among the u past samples is equal to the conjugate of  $h_n$ , i.e  $h^*$ , to be applied to a future sample corresponding in time. The operation therefore consists in carrying out the following function:

$$y_n = \sum_{u = -N/2}^{u = +N/2} x_{4n-u} \cdot h_u$$

or:

. . .

$$y_n = \sum_{u = -N/2}^{0} x_{4n-u} \cdot h_u + \sum_{u = 0}^{+ N/2} x_{4n+u} \cdot h_u$$

Where: h\_u = h\_u\*

In order to make understanding simpler we shall take an example in which u=0, 1, 2, 3;  $h_{u}=a_{u}+jb_{u}$  and  $h_{-u}=h_{u}^{\pm}$  from which  $h_{-u}=a_{u}-jb_{u}$

$$y_n = x_{4n-3}(a_u-jb_u)+x_{4n+3}(a_u+jb_u)$$

or:

$$y_{n} = \sum_{u=0}^{N/2} (x_{4n-u} + x_{4n+u}) (a_{u}) + (x_{4n+u} - x_{4n-u}) (b_{u})$$

which for the previous example is:

$$y_n = (x_{n-u} + x_{n+u}) \begin{pmatrix} a_3 \\ a_2 \\ a_1 \\ a_0 \end{pmatrix} + j (x_{n+u} - x_{n-u}) \begin{pmatrix} b_3 \\ b_2 \\ b_1 \\ b_0 \end{pmatrix}$$

Circuit 21 performs the function  $(x_{4n-u}+x_{4n+u})$  i.e. the summing of the samples considered as past and of the samples considered as future. Circuit 41 performs the function  $(x_{4n+u}-x_{4n-u})$  i.e. the difference between those same samples.

Circuit 22 stores the 2u real elements, i.e. it will carry out the following operation:

$$+ N/2$$

$\Sigma_0 (x_{4n-u} + x_{4n+u}) (a_u)$

Circuit 42 stores the 2u imaginary elements, i.e. it will carry out the following operation:

$$\frac{+N/2}{\Sigma} (x_{4n+u} - x_{4n-u}) (b_u)$$

The output of circuit 22 delivers a digital signal corresponding to the amplitude of the received signal and the output of circuit 42 delivers a digital signal in quadrature corresponding to the phase of the received signal.

Circuit 21 advantageously includes a FIFO (first in, first out) stack 23 which receives successively the samples  $x_n$ , these samples are stored in a Random Access Memory (RAM) 24 which will form the memory containing the future samples (+u samples at a given time). A sequential circuit 25 for example of Programmable Logic network (PAL) type addresses the memory. These samples are put into a register 26 which stores them in order to transmit them to a stack 27 of First In , First Out (FIFO) type on the one hand and to an adder 28 on the other hand.

The stack 27 successively introduces the samples which were in the memory 24 in order to re-enter them in a random acces (RAM) memory 29. Memory 29 stores the "future" samples

which become "past". A sequential circuit 30 addresses this memory 29. The data read from memory 29 are stored in a register 31 which restores them at one input of the adder 28 at the same time as register 26 restores the stored data to the other input of the adder. The adder 28 therefore successively receives at each input the future and past samples  $(x_{4n-u} \text{ and } x_{4n+u})$  in order to add them and to successively deliver the resultant samples of the sum to the output.

Circuit 22 includes a multiplier accumulator circuit 31 (MAC). This circuit 31 includes a multiplier 32 which receives the output signal of adder 28 and the data stored in a Programmable Read Only memory (PROM) 33 in which the real coefficients au of the filter are stored. This memory 33 is controlled by a PAL sequencer 34. The output of multiplier 32 is applied to an adder 35. This adder is associated with an accumulator 36 to carry out the sum of the 2u elements and deliver a sample which is stored in a register 37.

circuit 41 is formed from circuits referenced 43 to 50. Circuits 43 to 47, 49 and 50 are identical to circuits 23 to 27, 29 and 30, i.e. they perform the same function for the purpose of the same result. Only circuit 48 differs since this is a subtractor which carries out the difference between the "future" samples and the "past" samples.

Circuit 42 is formed from circuits 51 to 57. Circuits 51 to 57 are identical to circuits 31 to 37, they perform the same function for the purpose of the same result. However, the Programmable Read Only Memory 53 does not contain the real coefficients of the filter but the complex coefficients  $\mathbf{b}_{\mathbf{u}}$  of the filter. Register 57 delivers samples in quadrature with the output samples from register 37.

The present invention carries out a phase-amplitude demodulation of a signal on a carrier figure a sampling frequency to which can be very much toget

than the carrier frequency since this frequency  $f_e$  is equal to  $\propto$  B,  $\propto$  = 4 in a preferred embodiment and B being in general very small with respect to  $f_1$  (the ratio can vary from 1 to 50 for example).

#### CLAIRS

- 1. Process for the phase amplitude demodulation of a received radar signal after transposition of that signal into intermediate frequency  $f_1$ , characterized in that it consists in sampling this signal at intermediate frequency  $f_1$  at a sampling frequency  $f_2$  such that  $f_2 = \bigcirc B$ , where B is the width of the reception pass-band and  $\bigcirc A$  is a number greater than or equal to 2.

- 2. Process according to Claim 1, characterized in that the signal sampled at frequency  $f_e$  is demodulated in order to bring the useful signal into baseband, then filtered in order to eliminate the conjugate image spectrum and is sub-sampled at a frequency  $f_e$  such that  $f_e$  is approximately equal to B.

- 3. Process according to Claim 1, characterized in that the signal sampled at frequency  $f_e$  is filtered, then demodulated and then sub-sampled at a frequency  $f_e$  approximately equal to B.

- 4. Process according to Claim 1, characterized in that the signal sampled at frequency  $f_e$  is filtered then sub-sampled at a frequency  $f_e$  approximately equal to B and then demodulated.

- 5. Process according to any of Claims 1 to 4, characterized in that the intermediate frequency signal results from a first transposition of the Ultra High Frequency signal and then a demodulation of this signal at a frequency  $f_i$  such that  $f_i = f_{0L} f_e/4$ , where  $f_{0L}$  is the frequency of the receiver's local oscillator.

- 6. Process according to any of Claims 1 to 5, characterized in that the sampling frequency  $f_e$  and the intermediate frequency are in a ratio such that  $f_i = (k \pm 1/4)f_e$ , k being an integer.

- 7. Process according to Claim 2 or 3, characterized in that the demodulation consists in multiplying the modulo p samples respectively by p representative states corresponding to (1, +j, -j) if we have taken

$f_1 = (k+1/4)f_e$  or (1, -j, -1, +j) if we have taken  $f_1 = (k-1/4)f_e$ .

8. Process according to Claim 4, characterized in that the demodulation consists in carrying out the following operation on each sample  $\mathbf{x}_n,$

$$x'_n = x_n e^{\frac{1}{2}j 2\pi n} \frac{f_e}{4} \alpha \tau$$

where T is equal to 1/fe.

- 9. Process according to Claim 8, characterized in that we take 0.24, which enables the demodulation operation to be suppressed.

- 10. Phase amplitude demodulation device, characterized in that it includes an  $f_i$  amplifier (1), an analog-digital converter (2) and a digital processing circuit (3).

- 11. Device according to Claim 10, characterized in that the digital processing circuit (3) includes a filter (6, 8, 11), and a sub-sampler (7,10,12).

- 12. Device according to Claim 10 or 11, characterized in that the digital processing circuit (3) also includes a demodulator (5,9,13).

- 13. Device according to Claim 12, characterized in that, when the demodulation is carried out before the filtering, the filter is a low-pass filter (5), and when it takes place after the filtering, the filter is a band-pass filter (8,11).

- 14. Device according to any of Claims 10 to 13, characterized in that the demodulator (13) is placed after the sub-sampler (12).

- 15. Device according to Claim 11, wherein the sampling frequency  $f_e$  is equal to 4B and  $f_{\frac{1}{4}}=(k\pm\frac{1}{4})\,f_e$  ,

characterized in that the digital processing circuit (31) is formed from a first digital circuit (21) which receives the samples  $\mathbf{x}_n$ , and carries out the addition of terms having the same filtering coefficient, a second digital circuit (22) which carries out the digital filtering of these samples and delivers a digital signal I, at the sub-sampling rate  $1/f_{\rm e}$ ,

corresponding with the amplitude of the received signal, a third digital circuit (41) which receives the samples  $\mathbf{x}_{n}$  carries out the subtraction of terms having the same filtering coefficient, a fourth digital circuit (42) which carries out the digital filtering of these samples and delivers a digital signal  $\mathbf{Q}$  in quadrature with the first signal and at the same rate  $1/f_{n}^{n}$ .

16. Device according to Claim 14, characterized in that the first and third circuits (21) and (41) include respectively a first Random Access Memory (24) (44) containing the "future" samples, a second Random Access Memory (29) (49) containing the "past" samples, a FIFO stack (27) (47) for introducing the samples from the first memory into the second memory, sequencing circuits (25, 30) (45,50) sequencing the read-write operations of the memories; output registers (26,31) (46,51) for the memories; an adder (28) for the first circuit (21) and a subtractor for the third circuit (48).

17. Device according to Claim 15 or 16, characterized in that the second and fourth circuits (22) (42) respectively contain a multiplier-accumulator circuit (31) (51); a Programmable Read Only Memory (33) (53), a sequencer (34) (54) sequencing the memory read operations.

18. A phase amplitude demodulation device substantially as hereinbefore described with reference to and as illustrated in the accompanying drawings.

#### CLAIMS

1. Process for phase detection of a received radar signal by digital processing after transposition of that signal into intermediate frequency fi, and sampling of that signal at a sampling frequency fe such that  $fe = \alpha B$ , where B is the width of the reception pass-band and  $\alpha$  is a number greater than or equal to 2, characterised in that the sampling frequency fe and the intermediate frequency fi are in a ratio such that  $fi = (k + \frac{1}{4})$  fe, k being an integer, in that a frequency in order to bring the useful signal into baseband is realised simultaneously with phase detection by carrying out the following operation on each input sample  $x_n : x'_{n=x_n} = \frac{e^+ j 2\pi n}{4} \frac{fe}{\alpha \tau}$ , and in that said process further comprises a filtering in order to eliminate the conjugate image spectrum and a sub-sampling at a frequency  $f'_e$  such that  $f'_e$  is approximately equal to B.

15

5

10

2. Process according to claim 1, characterised in that the signal sampled at frequency  $f_e$  is first shifted in frequency and phase detected, then filtered in order to eliminate the conjugate image spectrum, and then subsampled at a frequency  $f_e$  such that  $f_e$  is approximately equal to B.

20

3. Process according to claim 1, characterised in that the signal sampled at frequency  $f_e$  is first filtered, then frequency shifted and phase-detected, then sub-sampled at a frequency  $f_e$  approximately equal to B.

25

4. Process according to claim 1, characterised in that the signal sampled at frequency  $f_e$  is first filtered, then sub-sampled at a frequency  $f'_e$  approximately equal to B and then frequency shifted and phase detected.

- 5. Process according to claim 4, characterised in that  $\alpha$  is equal to 4, which enables the frequency shifting and phase detection operation to be suppressed.

- 6. Process according to any of claims 1 to 5, characterised in that a frequency conversion is carried out before sampling.

5

15

20

25

- 7. Phase detection device for implementing said process according to any of claims 1 to 6, characterised in that it includes an  $\mathbf{f}_i$  amplifier , an analog-digital converter and a digital processing circuit .

- 8. Device according to claim 7, characterised in that the digital processing circuit includes a filter, and a sub-sampler.

- 9. Device according to claim 7 or 8, characterised in that the digital processing circuit also includes a frequency shifter and phase detector.

- 10. Device according to claim 9, characterised in that, when the frequency shifting and phase detection is carried out before the filtering, the filter is a low-pass filter, and when it takes place after the filtering, the filter is a band-pass filter.

- 11. Device according to any of-claims 7 to 10, characterized in that the frequency shifter and phase detector is placed after the sub-sampler.

- 12. Device according to claim 8, wherein the sampling frequency  $f_e$  is equal to 4B and  $f_i = (k + \frac{1}{4}) f_e$ , characterised in that the digital processing circuit is formed from a first digital circuit which receives the samples  $x_n$ , and carries out the addition of terms having the same filtering coefficient, a second

digital circuit which carries out the digital filtering of these samples and delivers a digital signal I, at the sub-sampling rate  $1/f_e$ , corresponding with the amplitude of the received signal, a third digital circuit which receives the samples  $x_n$  carries out the subtraction of terms having the same filtering coefficient, a fourth digital circuit which carries out the digital filtering of these samples and delivers a digital signal Q in quadrature with the first signal and at the same rate  $1/f_{e^{i}}$ .

10

5

13. Device according to claim 11, characterised in that the first and third circuits include respectively a first Random Access Memory containing the "future" samples, a second Random Access Memory containing the "past" samples, a FIFO stack for introducing the samples from the first memory into the second memory, sequencing circuits

15

sequencing the read-write operations of the memories; output registers

-for the memories; an adder for the first circuit and a subtractor for the third circuit.

20

14. Device according to claim 12 or 13, characterized in that the second and fourth circuits respectively contain a multiplier-accumulator circuit; a Programmable Read Only Memory and a sequencer sequencing the memory read operations.

15. A phase amplitude demodulation device substantially as hereinbefore described with reference to and as illustrated in the accompanying drawings.

25

7

## PATENTS ACT 1977 EXAMINER'S REPORT TO THE COMPTROLLER UNDER SECTION 17(5) (The Search Report)

Application No.

8600277

FIELD OF SEARCH: The search has been conducted through the relevant published UK patent specifications and applications, and applications published under the European Patent Convention and the Patent Co-operation Treaty (and such other documents as may be mentioned below) in the following subject-matter areas:-

**UK Classification**

H3A (AD and part B)

H3H (HAL)

(Collections other than UK, EP & PCT:) Selected US specifications in HO3D 1/00 to 5/00

DOCUMENTS IDENTIFIED BY THE EXAMINER (NB In accordance with Section 17(5), the list of documents below may include only those considered by the examiner to be the most relevant of those lying within the field (and extent) of search)

| Category | Identity of document and relevant passages                               | Relevant to claim(s) |

|----------|--------------------------------------------------------------------------|----------------------|

| x        | GB 1113431 (EMI) - whole document, noting page 2 lines 7-8               | 1, 10                |

| X,P      | EP+A2-0145056 (Hollandse) - see page 3 line 29 to page 4 line 4          | 1, 10                |

| Y        | US 4224575 (Mosley) - whole document                                     | 1                    |

| Y        | M I Skolnik, "Radar Handbook", McGraw-Hill 1970:<br>pages 3-30 and 20-18 | 1                    |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

|          |                                                                          |                      |

#### CATEGORY OF CITED DOCUMENTS

relevant if taken alone relevant if combined with another cited document document published on or after the declared priority date but before the filing date of the present application patent document published on or after, but with priority date

Search examiner

P HAYWARD

Date of search

1 July 1986