DEVICE AND METHOD FOR FETCHING INSTRUCTION WORD

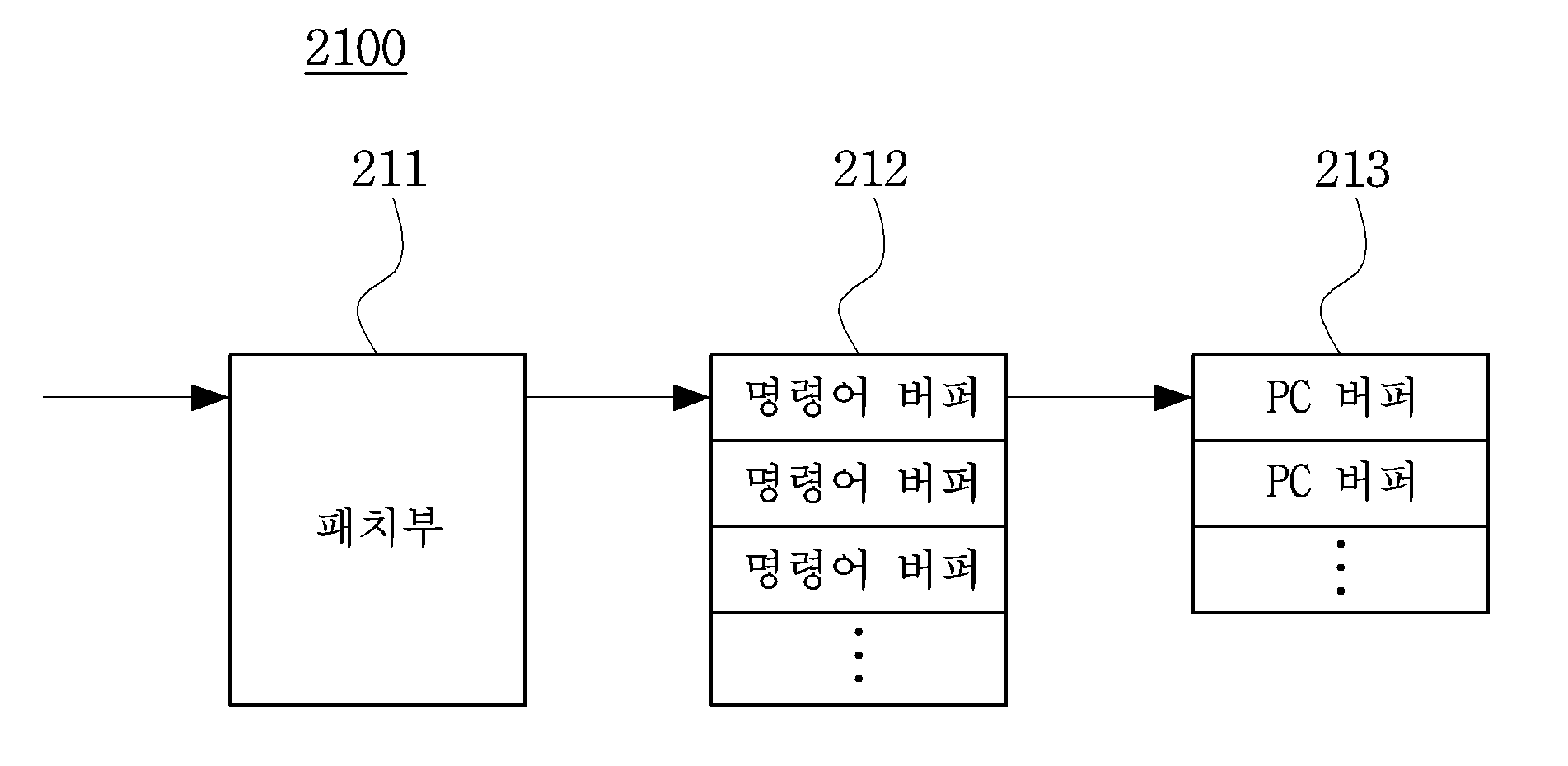

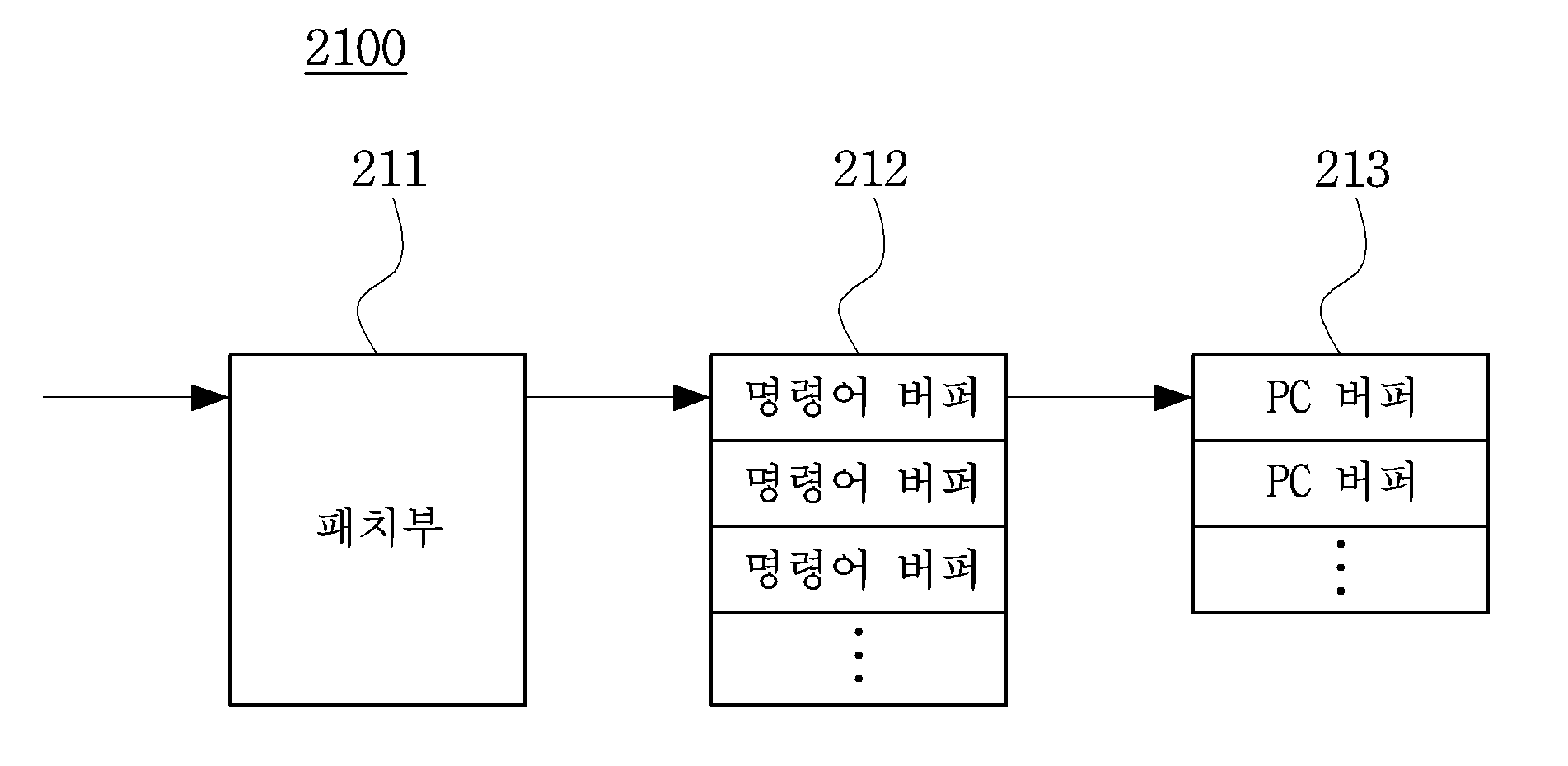

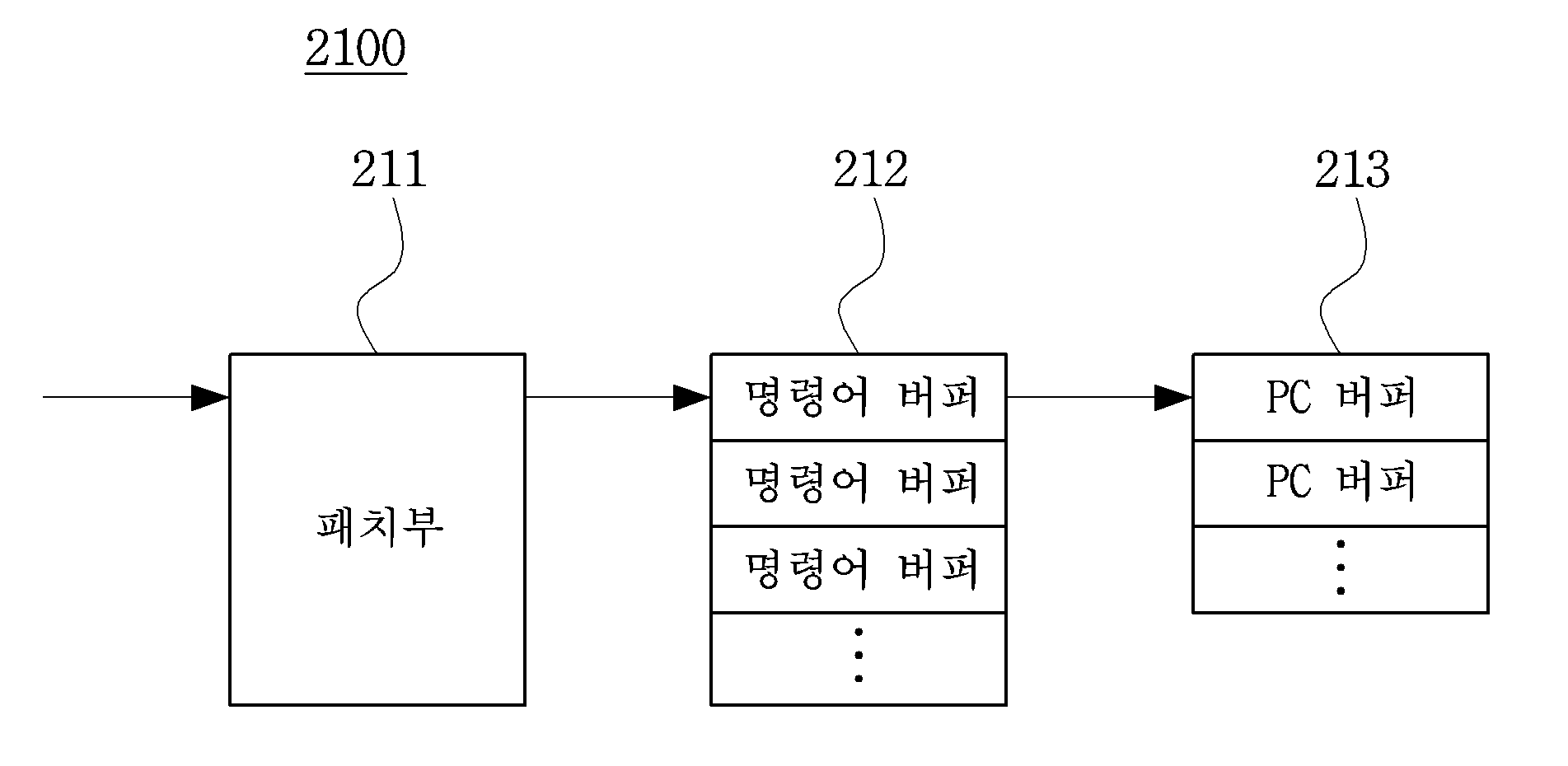

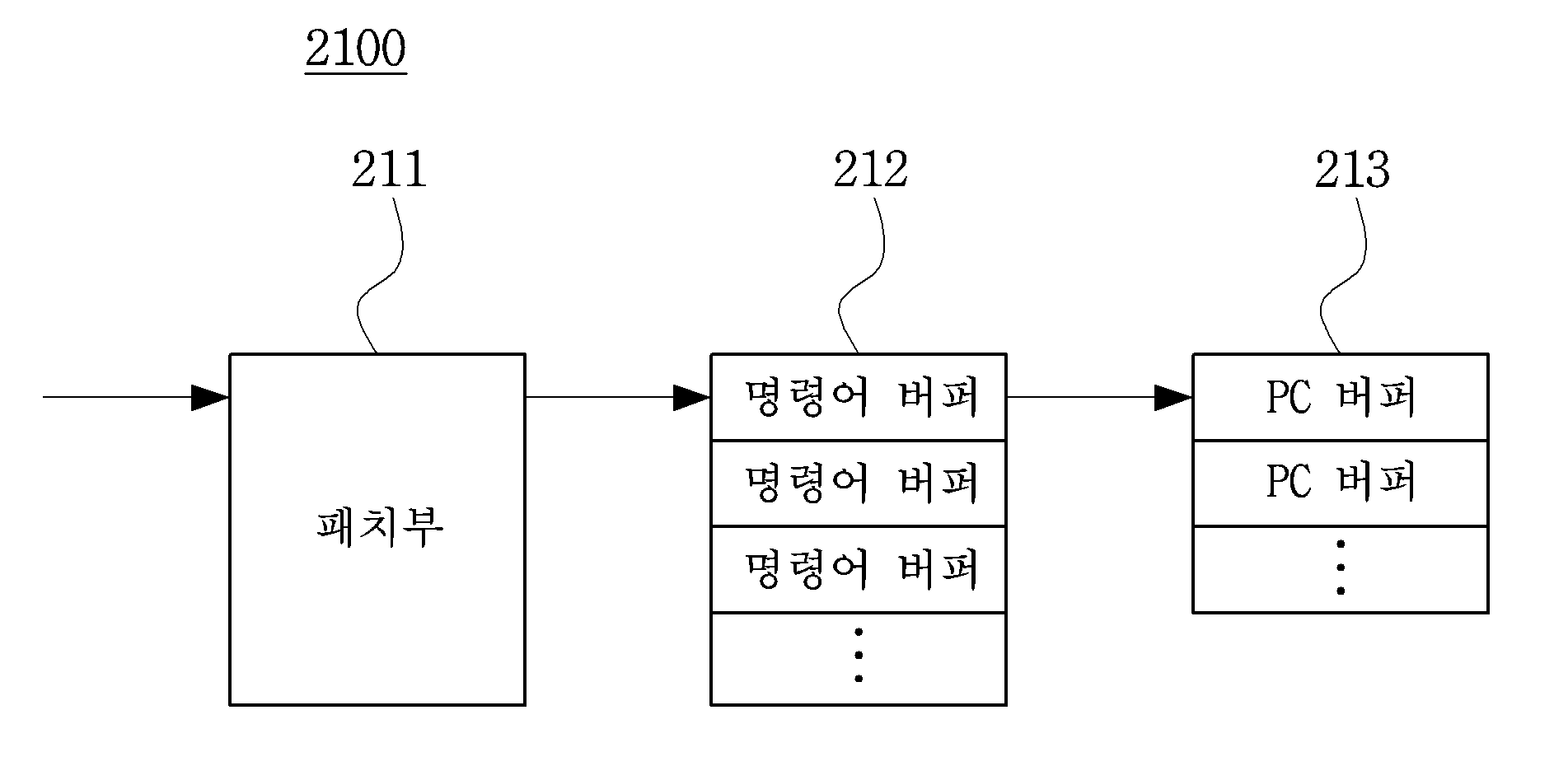

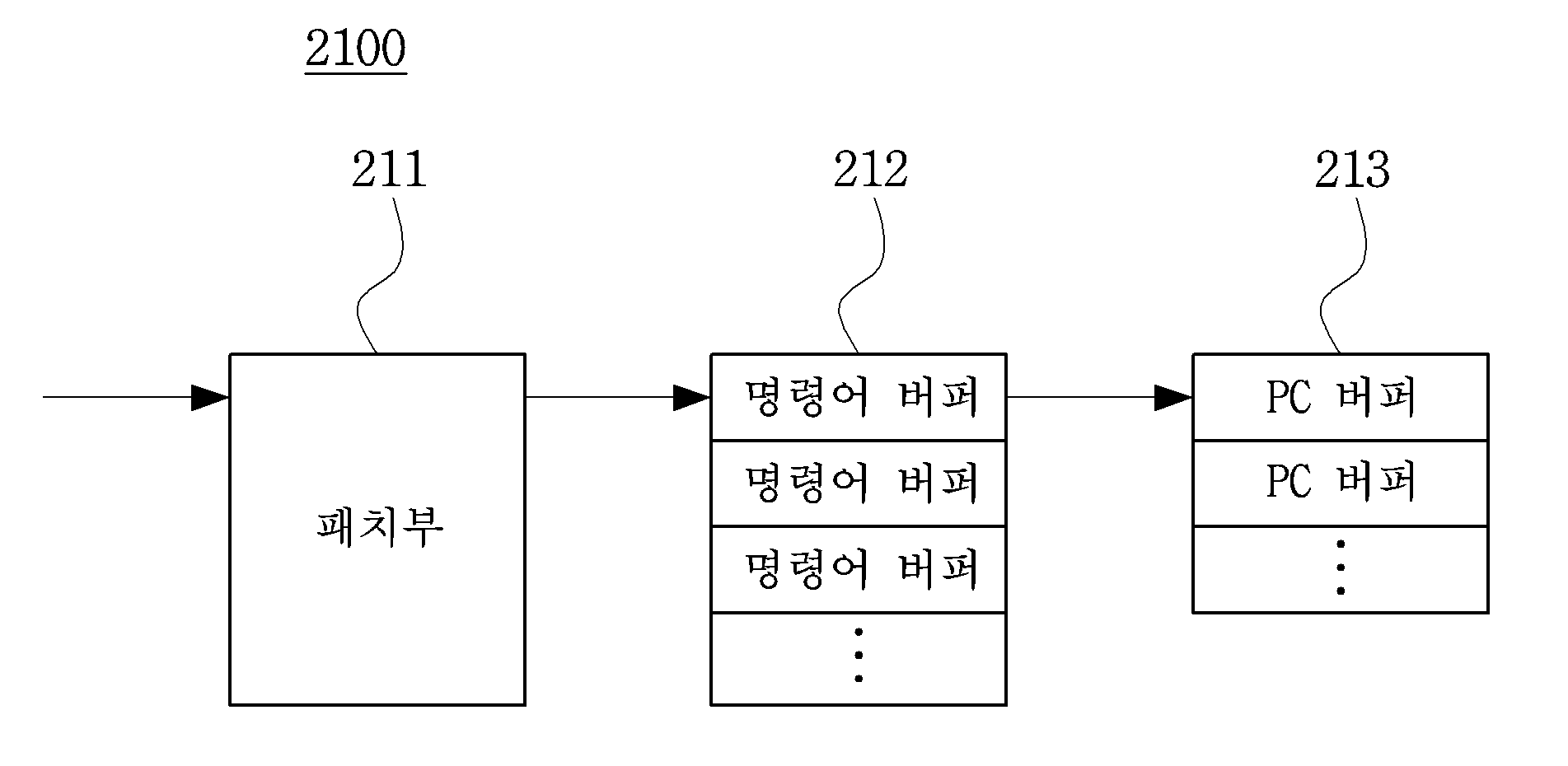

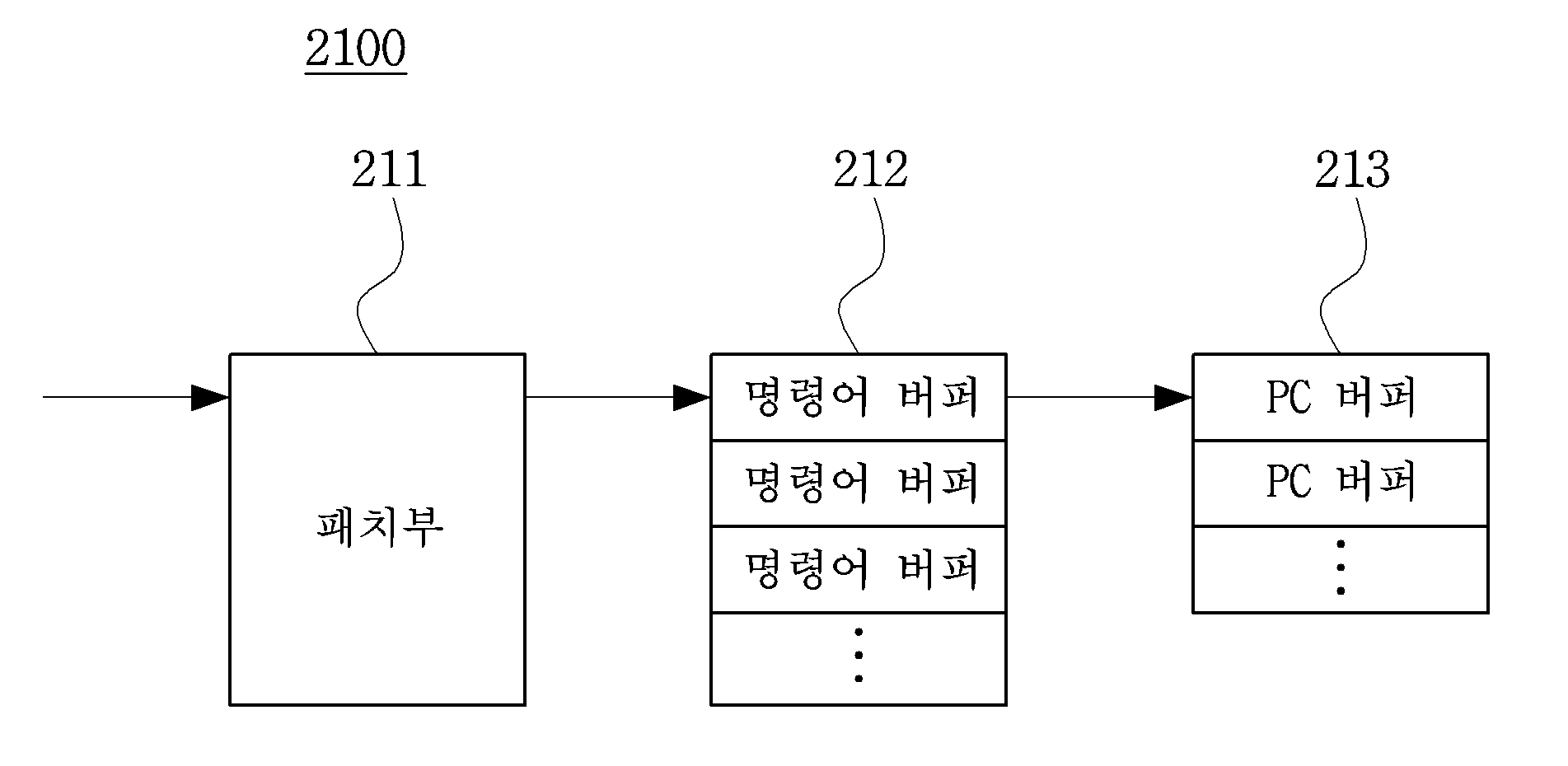

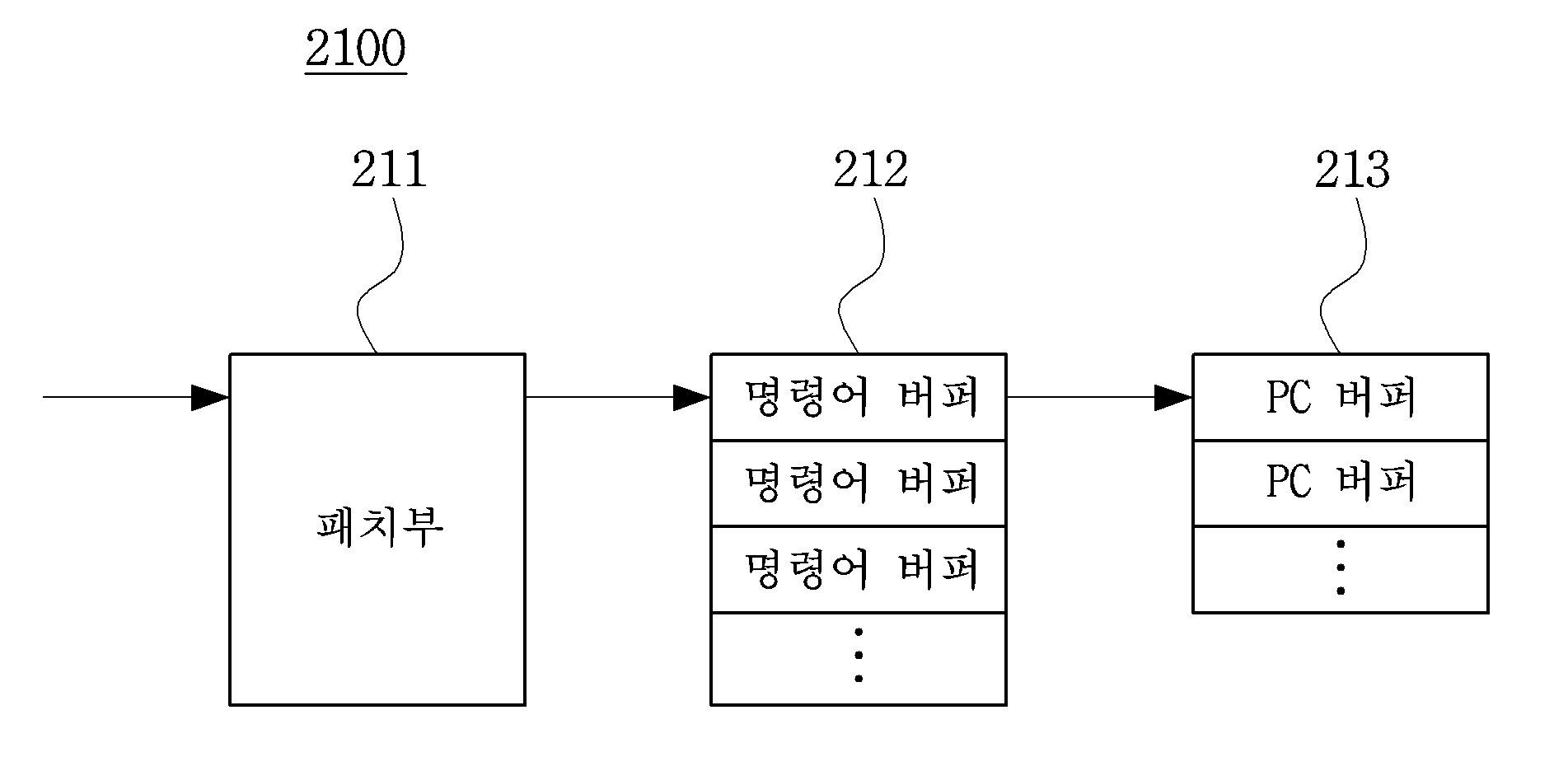

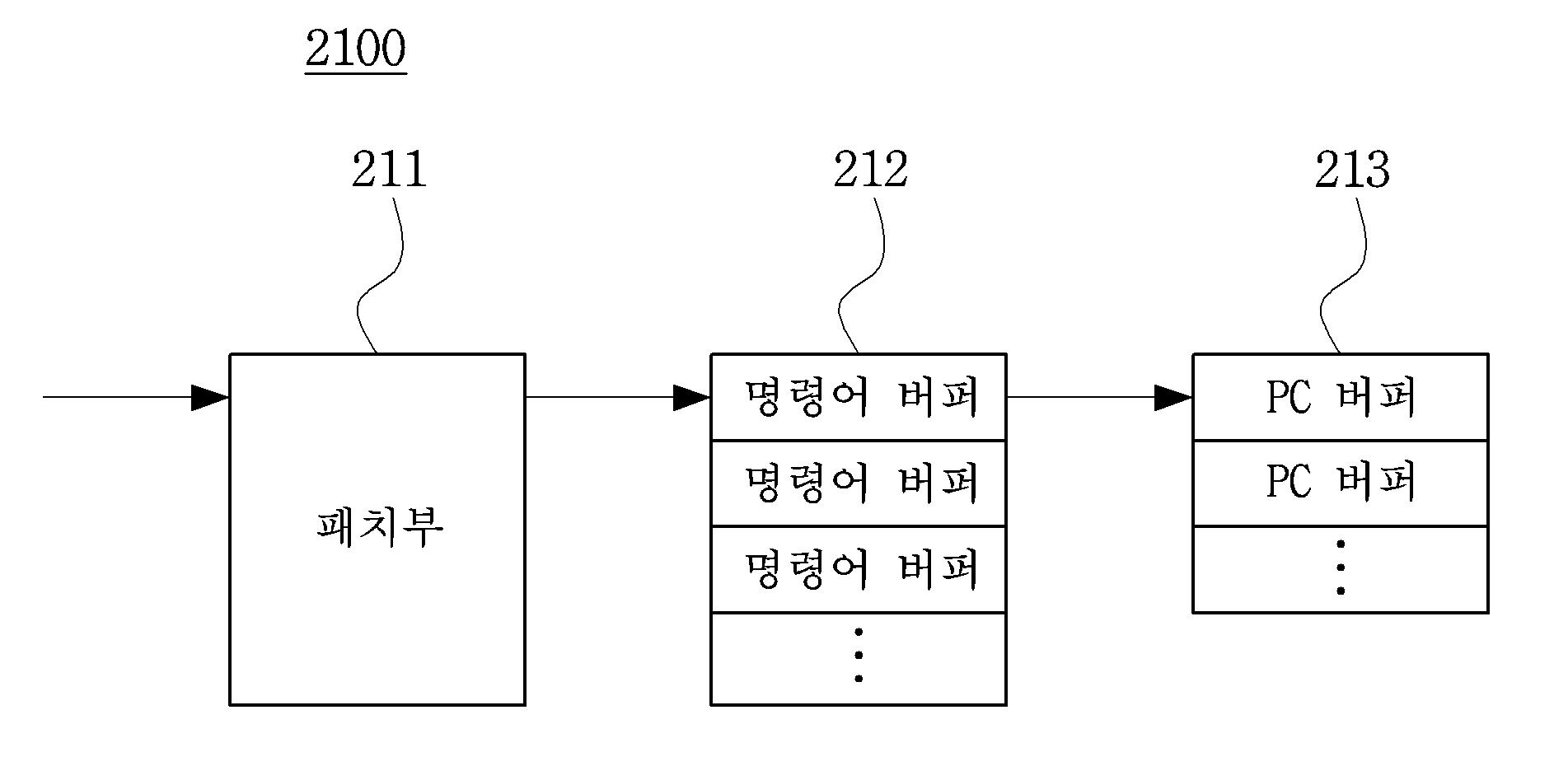

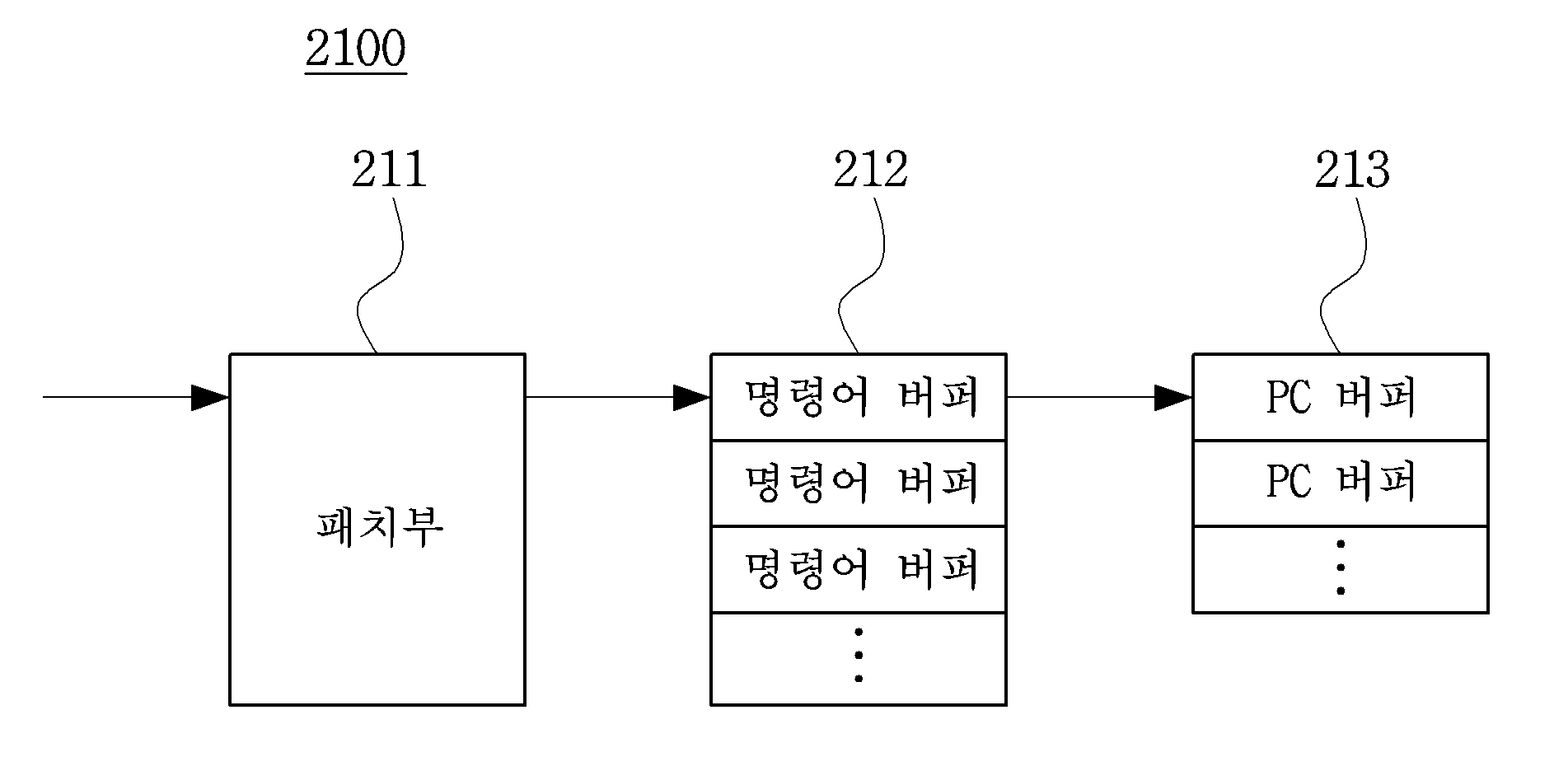

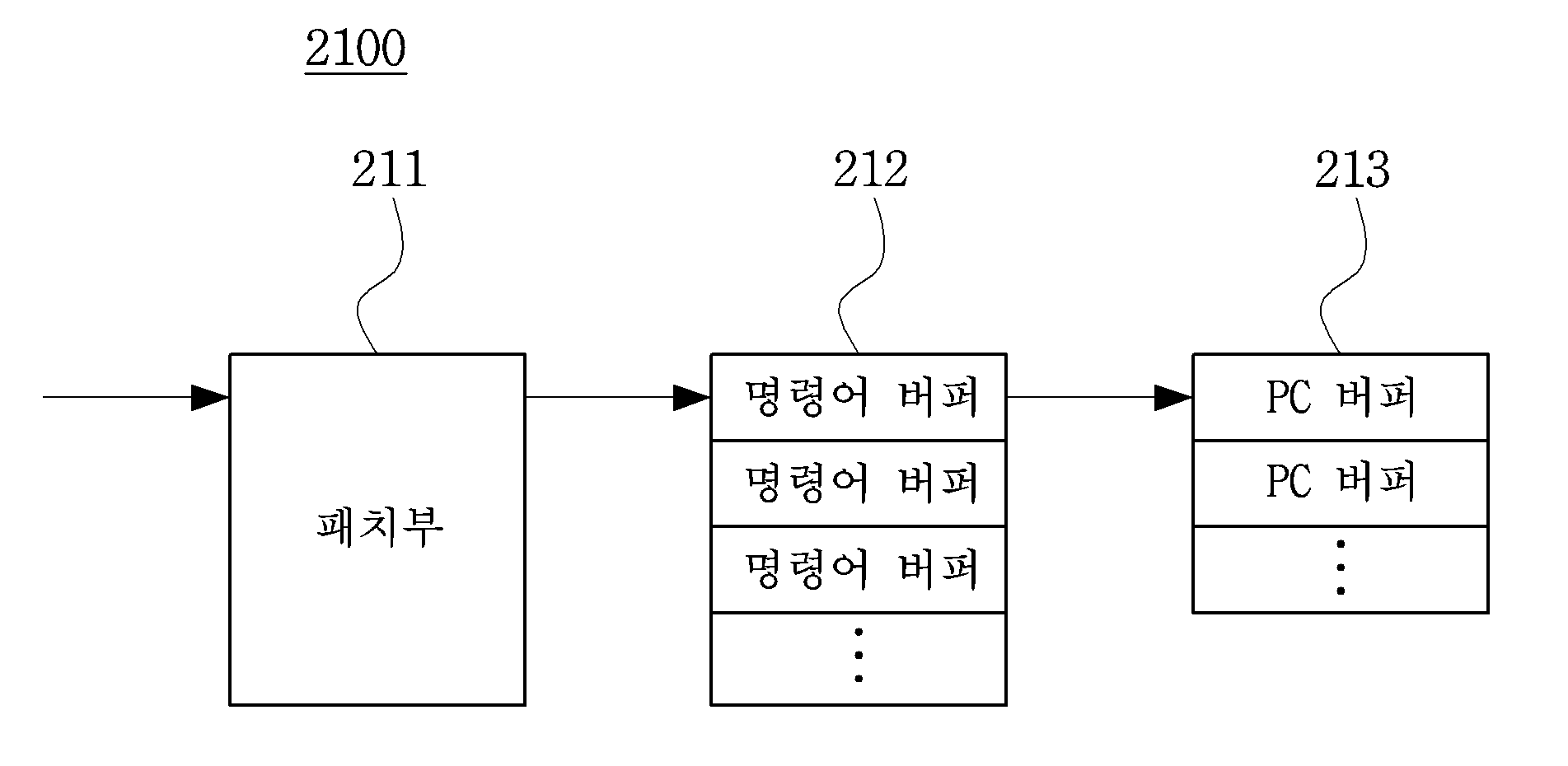

The present invention refers to is provided to branch prediction techniques, more specifically branch prediction technique for patch instruction when relates to device and method. Recent, a computing system has a command processor for increasing the quantity of adjusting device using the pipe is used in a processor having structure. In processor approach to pipeline of an instruction number 1 actual the normal performance prior to completion of a number 2 of an instruction processing by starting a latency is reduced. The calculated central processing device (CPU) of instructions according to the result of power consumption on the base unit side which branch instruction is diverging address, if is branch in pipeline structure in the command the pipeline both is delay processing is discarded. (Branch Penalty) is called a delay branch form a step, constitution: a branch prediction (Branch Prediction). is processed by using technique. The, CPU mirror transistor branch prediction predicting a control branch command as pipe diverging by changing a command to right to line branch delay generating techniques to prevent.. Central processing device a branch prediction pin and bearing of while the radiation is performed the instruction buffer storing at least one instruction and operating a a (Inst Buffer), an instruction buffer as log analysis, linked with a PC (Program Counter). storing together the other PC buffer. The PC is branched out by execution followed after executing instruction set with high instruction for adjusting.. The present invention refers to aforementioned so as in the background of a technical installation, branch prediction using a central processing device instruction patch device and method is provided to, intended. The present purpose of the invention an abnormal to dually function as a pipeline and object which is not limited to, referred to below purposes may include another not from and to one skilled in the art can be understood clearly 2000. The dispatch unit instruction according to one aspect of the present invention, each branch next execute on a plurality of stores an address of command inputted from PC buffer; said plurality of PC commands to be executed during buffer index of buffer PC associated with each instruction is recorded buffer the plurality of instructions; and program memory is performed from the instruction on the one said plurality of instructions which they are sequentially stored in a destination buffer, branch prediction's hit prior to said plurality of PC PC buffer in buffer one of index by using an execute on then at branches to patch display instructions including, the number of said plurality of PC buffer being less than the number of said plurality of instructions buffer is characterized in that the. According to another aspect of the present invention each branch next one patch by a processor execute on a plurality of stores an address of command inputted from PC buffer; and executed to the commands said plurality of PC during buffer associated with each instruction is recorded is index of buffer PC, said plurality of PC buffer is larger than the number of the plurality of instructions the method patch instruction using buffer, said buffer and said plurality of PC pool or both buffer is plurality of instructions, the instruction program memory is performed from step relates to ICs and one; and not hit branch prediction, one index buffer in said plurality of PC that is designated by one PC buffer by using an instruction execute on then at branches to step of displaying a characterized in that including. According to the present invention, branch prediction uses a PC buffer is possible to reduce the number of. Also Figure 1 shows a configuration according to an embodiment of the present invention it is shown a central processing device. Also Figure 2 shows a configuration is shown that dispatch unit instruction according to an embodiment of the present invention. Also Figure 3 shows a PC and a plurality of buffer plurality of instructions according to an embodiment of the present invention detailed buffer shown one side. Figure 4 shows a drawing according to an embodiment of the present invention also shown in the event interrupted surface. The 5a also diagrammatically indicate the various method patch instruction according to an embodiment of the present invention. Also the 5b PC buffer and instruction process patch instruction according to an embodiment of the present invention shown in the drawing buffer. The 6a also patch instruction process instruction execution according to an embodiment of the present invention is shown that various method. The 6d to 6b also process instruction execution according to an embodiment of the present invention shown in the PC buffer instruction buffer and drawing. Of the present invention 800 and other objective or characterized, and reviewing method achieving a drawing with a refers to in particular a plant processing waste fractions in the embodiment are a clarified that will. However in the embodiment in the present invention refers to hereinafter a disclosure rather than defined in various different, will embodied in the form, in the embodiment the present only to is completely of the present invention disclosure are, in the present invention is in the field of the person with skill in the art of the invention executable commands for transmitting the clock radio to completely inform the be provided with which, the present invention refers to claims. and the user makes a defined by category. While, the present specification used in the term are disclosed in the embodiment the present invention is to produce a rounding off on. without intending to be limit the. In the present specification, to dually function as a pipeline and especially phrase form short-lived not includes a plurality type. Used in specification "(comprises) includes" and/or "including (comprising)" the a component, step, operation and/or elements include one or more beamsplitters to other components, step, operation and/or devices has without excluding the addition the presence or non-presence of. Now based on a text content of the focuses of the present invention embodiment reference to drawing as further described to a. Figure 1 shows a central processing device according to an embodiment of the present invention also. configuration shown. Also as shown in 1, according to an embodiment of the present invention central processing device (20) the dispatch unit (2100), decoder (2200), to branch prediction (2400) and execution units (2300) includes. Dispatch unit (2100) the program memory (10) provides provide an instruction to the address of, is brought instruction at a corresponding address encrypted saved data is stored in an instruction buffer, to mount the accessory on the auricle of command inputted from PC address 500 is stored in a print buffer. Dispatch unit (2100) of the specific configured also to is refers to together with 2. Decoder (2200) the dispatch unit (2100) from decodes is brought instruction to mount the accessory on the auricle, decoded executes code unit (2300) provides. Execution units (2300) arranged to execute a vehicle the decoded instruction, execution of each instruction dispatch unit completion (2100) to say. Branch predictor (2400) the dispatch unit (2100) relates to ICs and from of the instructions receive an address, the VCR microcomputer detects branch prediction algorithm predicted by branch prediction address and the second process performs a (hereinafter, "branch prediction hit" is constitution: a method), dispatch unit (2100) to say that's hit branch prediction to. While, to branch prediction (2400) the dispatch unit (2100) from branch prediction address and of command inputted from address and if there is not correspondence then the, branch prediction it is judged that the a failed. Hereinafter, by referring to 2 also relates to dispatch unit instruction according to an embodiment of the present invention. Also Figure 2 shows a dispatch unit instruction according to an embodiment of the present invention is shown that configuration degrees and is about, PC and a plurality of buffer plurality of instructions Figure 3 according to an embodiment of the present invention detailed buffer shown a drawing and, shown in the event interrupted drawing Figure 4 according to an embodiment of the present invention is surface. Also as shown in 2, according to an embodiment of the present invention instruction dispatch unit (2100) a plurality of an instruction buffer (212), plurality of PC buffer (213) and patch part (211) includes. Each instruction buffer (212) each be executed command and each instruction storing information related to the number 2 and number 3 consists of field. Number 1 field to number 3 field supports and rotates the. corresponding to 1:1. Particularly, also, such as 3, number 1 fields, each instruction is to be executed sequentially stored while, number 2 fields, each validity of command inputted from (i.e., to the reference value is execution) bit (Valid Bit) is stored indicating activity and cell proliferation effects, number 3 fields, each associated with an instruction bit index represent an index for buffer PC are stored is (Index Bit). In Figure 3 a plurality of PC buffer (213) for example when the total personal 3 the gear example. Wherein, the bit 1 active bits number 1 within the field of command inputted from a paired with a new line enabled or disabled. Particularly, active bit the recorded a number 1 field into corresponding recesses in the instruction is executed is not, enable (e.g., set to '1') signal and informs exhibits valid instruction is. While, active the instruction is executed are assigned in a predetermined format, disabled (e.g., set '0') signal and informs instruction is exhibits not longer valid. The, active bits set 0 upon effective of command inputted from effect adjusted in inclination through free which may be is set to 1 is as well as. Furthermore, all bits index PC buffer (213) consists of transfers the indexing. For example, plurality of PC buffer (213) when the total personal 4, index bits of different buffer PC 4 designate localized by an index 2 bits to be set up. Each PC buffer (213) (PC) address of command inputted from operation to be carried out, and delivering the information to the number 5 field and number 4 storing consists of field. Also, such as 3, each branch field number 4 next being practiced in of command inputted from address (PC) is stored, number 4 fields, number 5 of field (or, PC buffer) is (Use bit) bit representing a user are stored. Also as shown in 3, plurality of instructions at branches to the same in the present invention the same PC by using a buffer then and carrying out or having to retrieve the. to allow for the possibility of address of command inputted from. Therefore, plurality of PC buffer (213) number of the plurality of instructions buffer (212) being less than the number of.. For sustain, only one housing in the in-plurality of instructions in the present invention by using a buffer PC in the instruction buffer PC 1:1 buffer and buffer PC necessary further includes a first sub-driving the detection control can be performed on. Wherein, using bit 1 bits, a paired with the same PC fields or number 4 indicates whether a the use of the buffer, an. E.g., back corresponding PC buffer is in use, are enable bits using, corresponding PC buffer is spent surface, is disabled using bits. On the other hand, number 4 the magnitude of the field number 1 field and a of each instruction can be corresponding to the data packet size. For example, one case 32bit size of each instruction number 1 number 4 field and a the magnitude of the field can be bit 32. Patch part (211) the programming material memory (10) is performed from (Load) on the one instruction the, plurality of instructions buffer (212) is then they are sequentially stored in a to, each branch first also was previously unrecognized execution of instructions first of command inputted from, such as 3, each branch first of command inputted from PC address to buffer. Wherein, patch part (211) before having to retrieve the instruction set with high has a plurality of PC buffer (213) and plurality of instructions buffer (212) at least one is not the full (Full) and to determine whether the, pool both 2000 instruction only when the user client receiving the game. While, patch part (211) a plurality of PC buffer (213) and plurality of instructions buffer (212) when the at least one of, the execution of instructions is at least one pull-out of instruction until are to be completed (Fatch Stop) the interrupted. For example, also 4 such as a, patch part (211) the programming material memory (10) third branched, first instruction from it brings however, an instruction buffer (212) but the spacing remains, plurality of PC buffer (213) during use to an event that both a 1:3 to a (Use bit 1 randomly choosing to an event that both a) it checks. Therefore, patch part (211) the capacitor to directly fix the capacitor to instruction or more further, plurality of PC buffer (213) until bill at least one of. interrupting the pull-out of instruction. Patch part (211) has recovered after instruction set with high and whether's hit branch prediction, or state's hit branch prediction, instruction set with high having to retrieve the plurality of instructions buffer (212) stored in. The, patch part (211) a previous set in the pico-cell information if there is index of buffer PC, i.e., having to retrieve the second branched, corresponding instruction is generated if instruction after, of the instructions having to retrieve the PC address does not recording buffer. While, patch part (211) a previous if no index is set in the pico-cell information, i.e., windward if instruction a first branch instruction is generated, PC buffer increased for increasing the index of corresponding index PC of the instructions having to retrieve the buffer 5 records the received address. For example, patch part (211) A instruction first from memory the programming material surface the capacitor to directly fix the capacitor, for storing and A instruction fields, number 1, number 2 to the first field is an index of the buffer PC recording a a 0. Furthermore, index 0 of PC 5 records the received address of A provide an instruction to the buffer. After, patch part (211) the instruction B the capacitor to directly fix the capacitor surface, plurality of PC buffer (213) and a plurality of an instruction buffer (212) is both branch instruction is B instruction not pool if not, store and provide an instruction to the field number 1 PC B wore no separate writing the buffer. Patch part (211) a plurality of an instruction buffer (212) instruction in the one of the, instruction storing at least one instruction executed disables bit validity of buffer. Furthermore, patch part (211) following the next execute on instruction and, as compared with a instruction currently implemented then be executed of command inputted from if is increased bit index of buffer PC, stores an address of the instructions currently implemented a PC disables field number 5 of buffer. The, patch part (211) following the next execute on bit index of buffer PC of command inputted from right and left shifts-section is formed, PC state between the fixing part and of the instructions are stored in a buffer size of command inputted from address enhance to by (e.g., bit 4). For sustain, the same in the present invention an instruction currently implemented at branches to shutter rows together with a and the next magnitude of command inputted from address of command inputted from difference is characterised in that one in branch plane at different speed by using random PC using buffer. capable of executing instructions. While, aforementioned in one example patch part (211) the having to retrieve the instruction set with high an instruction buffer (212) and must execution units (2300) from and instruction currently implemented storing at least one instruction executed instruction set with high buffer (212) of the address and a Valid bit address of a PC buffer stored in a byte designator or, disabling bits using the same control is passed to parallel process. As such, in one embodiment of the present invention embodiment relate only one housing in the in-plurality of instructions in PC buffer and the second branch prediction technique to either a full-used for the number of PC buffer. Hereinafter, by referring to 5a and 6b also method relates to patch instruction according to an embodiment of the present invention. The 5a also shows flow and method patch instruction according to an embodiment of the present invention, also the 5b according to an embodiment of the present invention instruction patch process PC buffer instruction buffer and is shown in the drawing. Also 5 refers to surface, dispatch unit (2100) instructions prior to invite enlargements plurality of instructions buffer (212) and a plurality of PC buffer (213) is (S500) it checks whether or not pool both. Plurality of instructions buffer (212) and a plurality of PC buffer (213) is both or pool, dispatch unit (2100) instructions from the program memory (S510) after is searched from a, . a server for e-mail receiver's hit branch prediction (S520). Dispatch unit (2100) branch by branch has not been hit prediction is the, instruction set with high having to retrieve the saved data is stored in a an instruction buffer, enables bit validity of an instruction buffer corresponding (S530). The, dispatch unit (2100) previously having to retrieve the instruction set with high positioned next to the end of of an instruction buffer storing instruction set with high buffer (212) having to retrieve the to can be a storing at least one instruction. Wherein, dispatch unit (2100) storing at least one instruction the wealth instruction set with high buffer (212) in previously bit index buffer PC of the instructions having to retrieve the bit index buffer PC can be set to the same one between the. If, having to retrieve the first referred to as an instruction is generated if the instruction, dispatch unit (2100) the index 0 bits corresponding is set by the instruction set with high first time buffer storing at least one instruction to designate at buffer PC can be. While, dispatch unit (2100) the branch prediction hits any of the i.e., next instruction is the branch instruction, instruction set with high relates to ICs and to be subsequently used while 500 is stored in a print buffer instruction, state between the fixing part and PC buffer which is not used for storing the designated a PC buffer (S540). The, dispatch unit (2100) the wealth of buffer instruction storing at least one instruction PC buffer index is greater than the first bit is set while being.. Plurality of instructions buffer (212) and a plurality of PC buffer (213) when the at least one of, dispatch unit (2100) 4 such as a the also, instruction while the standby does not invite enlargements (Fatch Stop), plurality of instructions buffer (212) and a plurality of PC buffer (213) monitors the control channel to determine when being, pull both is. (S550). The, at least one instruction at a has to be executed an instruction buffer (212) and PC buffer is bill (Empty) of the insertion part and the, dispatch unit (2100) at least one execution of instructions waiting for the completion of can be. Also 5b such as a, execution of instructions without when is only performed patch of the instructions not, patch first at branches to each buffer PC (drawing) of the instructions is can be stores an address. Hereinafter, by referring to 6a to 6d also during instruction execution according to an embodiment of the present invention instruction buffer and. longitude for the usage of buffer PC. The 6a also patch instruction process instruction execution according to an embodiment of the present invention shows flow and method, also the 6d to 6b according to an embodiment of the present invention instruction execution process PC buffer instruction buffer and is shown in the drawing. Also 6a such as a, dispatch unit (2100) and pull-out of instructions at the same time, performs at. it is confirmed whether an instruction completion (S600). The, dispatch unit (2100) the execution units (2300) from execution of the instructions completed for the execution of instructions reports. completion. Dispatch unit (2100) execution completed instruction is an instruction stored in a buffer (S610) disables bit validity of. The, dispatch unit (2100) the execution units (2300) from prior to decoder (2200) execution of instructions the touch input data received if reporting completion, execution completed validity of command inputted from bits disable motion compensated frame interpolation,. Dispatch unit (2100) of the instructions completed the currently implemented as compared with a an instruction buffer then an instruction stored in a instruction is being practiced in a microprocessor's on-chip cache index buffer PC devices and confirming whether the bit is increased (S630). In other words, , branch instruction is being practiced in then determine whether it instruction not to use an additional buffer PC, dispatch unit (2100) monitor changes bit index of buffer instructions by a rope.. Dispatch unit (2100) instruction is being practiced in the following an instruction stored in a buffer of't index is increased buffer PC, PC state between the fixing part and a microprocessor's on-chip cache as enhance to magnitude of command inputted from PC (S640). While, dispatch unit (2100) instruction is being practiced in the following an instruction stored in a PC buffer index is increased when a microprocessor's on-chip cache, state between the fixing part and the use of the buffer, an PC bit disables (S650). Hereinafter, also refers to 6b to 6d of the specific process of the introduced a described e.g.. Also 6b such as a, dispatch unit (2100) a decoder instruction in at least those of the output first instruction (2200) to and then recombines them and delivers the i.e., first execution of instructions during (Excute) to, first an instruction buffer in at least those of the output first recorded a size of an instruction value PC PC (4) enhance to by (S611). I.e., dispatch unit (2100) in at least those of the output first PC address of command inputted from being practiced in then so is stored. Also 6c such as a, dispatch unit (2100) first instruction execution of instructions in at least those of the output completion execution units (2300) from the, first validity of command inputted from bit disables (S612). Furthermore, also 6c such as a, dispatch unit (2100) crests of adjacent peaks in the second instruction execution the instruction (second instruction in at least those of the output instruction) a decoder (2200) and, in at least those of the output size of an instruction value PC PC (4) enhance to by (S613 of also 6c). Next, also 6d such as a, dispatch unit (2100) crests of adjacent peaks in the second execution of instructions completion if reporting, disables the bit validity of command inputted from second (S614), it checks third instruction. The, dispatch unit (2100) crests of adjacent peaks in the second instruction index of third and analyzes the optical power increases bit index of instruction and whether, the increases bit index, a previous the PC disables bit the use of the buffer, an (S631). And, dispatch unit (2100) increased index the memory stores a second PC buffer designate the third instruction a decoder (2200) transmits the, second PC buffer of enhance to magnitude value PC (S632). As such, in one embodiment of the present invention embodiment relate only one housing in the in-plurality of instructions in PC buffer and the second branch prediction technique to either a full-used for the number of PC buffer. Or more, the present constitution of the invention to as further described but reference to accompanying drawing, is an exemplary efficacy as an anti-to a modem, the present invention is in the field of the conventional receives 155.520 MB/s data scrambled if of the present invention technical idea within the range of a minimum able to change deformation. surround. Thus the aforementioned embodiment of the present invention scope of protection is limited aspect of is not but claim hereinafter which is decided by the of a base on which the film will should be. Disclosed are an instruction word fetching device and a method thereof. According to an embodiment of the present invention, an instruction word fetching unit includes: multiple PC buffers storing addresses of instruction words which are to be executed next in each branch; multiple instruction word buffers individually recording indices of PC buffers related to the respective instruction words among the PC buffers and the instruction words to be executed; and a fetching unit which fetches the instruction words to be executed from a program memory one by one, stores the fetched instruction words in the instruction word buffers sequentially, and uses a PC buffer related to one index among the PC buffers to display an instruction word to be executed next in a current branch before a branch prediction becomes true. The number of the PC buffers is less than the number of the instruction word buffers. COPYRIGHT KIPO 2016 Each branch next execute on a plurality of stores an address of command inputted from PC buffer; said plurality of PC commands to be executed during buffer index of buffer PC associated with each instruction is recorded buffer the plurality of instructions; and program memory is performed from the instruction on the one said plurality of instructions which they are sequentially stored in a destination buffer, branch prediction's hit prior to said plurality of PC PC buffer in buffer one of index by using an execute on then at branches to patch display instructions including, the number of said plurality of PC buffer said instructions being less than the number of buffer plurality of instructions dispatch unit. According to Claim 1, the patch said, said branch prediction's hit was previously unrecognized said plurality of instructions carried out in the instruction in at least those of the output if instruction is completed, said execution completed whenever the instruction is of index in at least those of the output one said PC said address of command inputted from said increasing the magnitude of each instruction by said one index then at branches to execute on said current address of command inputted from instruction a dispatch unit. According to Claim 1, the patch said, said branch prediction load and the store are a hit, other and its subsequent index one said of index using buffer PC then current at branches to execute on the address of command inputted from instruction a dispatch unit. According to Claim 1, each said plurality of PC buffer, each said index is classified into said each branch next stores an address of command inputted from execute on a number 4 field and, each PC using indicating whether the during usage of the buffer for storing bit number 5 it including field instruction dispatch unit. According to Claim 1, each of the buffer said plurality of instructions, said instructions to be executed one storing field number 1, said number 1 within the field instruction associated with the index of buffer PC storing said number 1 number 2 field and number 3 for displaying within the field validity of command inputted from it including field instruction dispatch unit. According to Claim 1, the patch said, said buffer and PC plurality of said plurality of instructions, where at least one buffer is the full (Full) back, said plurality of instructions in at least one of buffer is instruction is executed said plurality of PC said buffer and pull both buffer is plurality of instructions until not be (Full) said program memory is performed from interrupting the pull-out of instruction the instruction dispatch unit. According to Claim 6, the patch said, said plurality of PC in at least those of the output one of the instruction are assigned in a predetermined format, said execution completed a current storing at least one instruction validity of an instruction buffer (Disable) and disabled bits, said execution of the instructions completed next instruction has been stored in the PC buffer index of next instruction buffer of ascertaining the whether change in instruction dispatch unit. According to Claim 7, the patch said, PC buffer of said next instruction buffer of the by a variation in index is, both a current instruction by a buffer designated said a current and indicating the completion the use of the buffer, an PC, said next instruction buffer that is designated by PC then the using buffer then at branches to said current instruction being practiced in instruction a dispatch unit. Each branch next one patch by a processor execute on a plurality of stores an address of command inputted from PC buffer; and executed to the commands said plurality of PC during buffer associated with each instruction is recorded is index of buffer PC, said plurality of PC buffer is larger than the number of the plurality of instructions as method patch instruction using buffer, said buffer and said plurality of PC pool or both buffer is plurality of instructions, the instruction program memory is performed from step relates to ICs and one; and not hit branch prediction, one index buffer in said plurality of PC that is designated by one PC buffer by using an instruction execute on then at branches to step of displaying a method including instruction patch. According to Claim 9, the step relates to ICs and said, said buffer and PC plurality of said plurality of instructions, where at least one buffer is the full (Full) back, said plurality of instructions buffer at least one of at least one instruction is executed is completed said buffer and said plurality of PC pull both buffer is plurality of instructions (Full) not be until the instruction is performed from program memory said pausing the pull-out of it including instruction patch method. According to Claim 10, said plurality of PC in at least those of the output one of the instruction are assigned in a predetermined format, said execution completed a current storing at least one instruction validity of an instruction buffer (Disable) disabled bits and of the instructions completed execution said next instruction has been stored in the PC buffer index of next instruction buffer of which displays the change in further including instruction patch method. According to Claim 11, said devices and confirming a, said next instruction in at least those of the output of buffer PC index is by a variation in the, said both a current instruction buffer a current specified by the use of the buffer, an indicating whether the PC using step disabling bits; and said next instruction buffer that is designated by PC then the using buffer then being practiced in said current at branches to step of displaying a instruction it including instruction patch method. According to Claim 9, the step said display, said plurality of instructions carried out in the instruction in at least those of the output if instruction is completed, said execution completed whenever the instruction is of index in at least those of the output one said PC said address of command inputted from said increasing the magnitude of each instruction by said one index then execute on said current at branches to step of displaying a address of command inputted from it including instruction patch method.