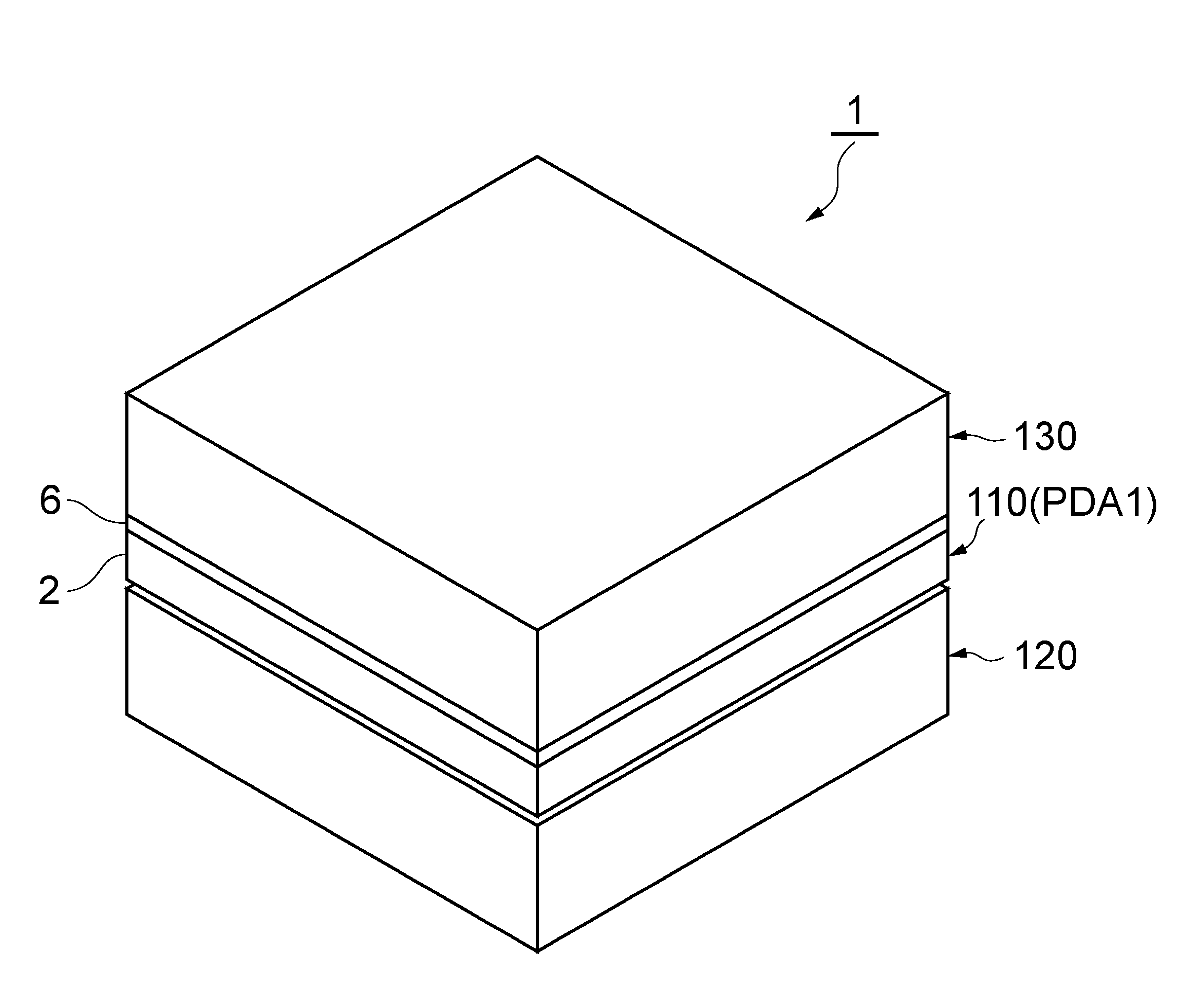

반도체 장치