Delay circuit with current steering output symmetry and supply voltage insensitivity

[0001] 1. Technical Field of the Invention [0002] The present invention relates generally to the field of integrated circuits and, more particularly, to oscillator delay cells. [0003] 2. Description of Related Art [0004] Controlled ring oscillators are common building blocks in most communication systems, especially in applications such as phase locked loops, clock generations and clock distributions. The frequency of operation, jitter or phase noise, tuning range and frequency stability with temperature, supply voltage variation are typical characteristics which must be considered when designing oscillators. Differential ring oscillators, in particular, offer a key advantage of being integratable on a chip without external components, which becomes very important for applications where space is very limited. LC oscillator or crystal oscillators generally provide low jitter or phase noise, but also generally require external chip components. Some disadvantages of typical CMOS differential ring oscillators include a relatively lower phase noise performance and the increased sensitivity to supply voltage change when compared to LC oscillator or a crystal oscillator. [0005] In general, a differential ring oscillator is comprised of several cascaded stages of identical differential delay cells connected in such a manner as to provide an effective phase inversion allowing oscillation. Typically, these stages are used to provide the instability and feedback necessary for oscillation. The amount of jitter or phase noise in a ring oscillator is determined by the nature of the differential delay cells and the biasing tail currents, particularly in a low power application. To reduce the overall jitter and phase noise of a ring oscillator, care must be taken to ensure that each differential delay cell contributes minimal noise. Furthermore, the device noise of each tail current transistor is also a considerable source of jitter, particularly, in extra low power applications. [0006] Therefore, there is a need for a differential delay cell which reduces or eliminates phase, jitter, and/or flicker noise for use in ring oscillators, PLL, DLL, and other communication systems, in low power applications. [0007] The present invention achieves technical advantages as a circuit for providing a symmetrical signal to a communication system which can be integrated in oscillator type circuits, for example. In one embodiment, the circuit includes a pair of half circuits having respective inputs for receiving a differential signal pair, and a pair of symmetry circuits coupled to the half circuits and advantageously configured to provide an output signal exhibiting a symmetrical waveform in response to the received differential input signal. The circuit further enables current steering to each half circuit to advantageously reduce voltage variation on a common node, hence, reducing current fluctuation from a current source. [0008] For a more complete understanding of the present invention, reference is made to the following detailed description taken in conjunction with the accompanying drawings wherein: [0009] [0010] [0011] [0012] The numerous innovative teachings of the present application will be described with particular reference to the presently preferred exemplary embodiments. However, it should be understood that this class of embodiments provides only a few examples of the many advantageous uses and innovative teachings herein. In general, statements made in the specification of the present application do not necessarily delimit any of the various claimed inventions. Moreover, some statements may apply to some inventive features, but not to others. [0013] Oscillators may occur in many forms. The simplest form of an oscillator is an amplifier with positive feedback. This type of oscillator is one which generates a signal where the output voltage oscillates, meaning that it swings up and down in a regular pattern or wave such as a sine wave, for example. A ring type oscillator generally includes a plurality of stages or differential delay cells connected in a ring configuration as is known in the art. In operation, the outputs of the first differential delay cell act as inputs to the next delay cell, and so on. [0014] By studying the impulse response of an oscillator it can be seen that upconversion of 1/f noise can be managed by designing a differential cell which operates to give a symmetrical rising and falling waveform on the outputs of the individual delay cells. For a more detailed discussion of noise in oscillators, reference can be made to, A. Hajimiri and T. H. Lee, “A general theory of phase noise in electrical oscillators,” IEEE JSSC, 33(2): 179-194, 1998 and A. Hajimir, S. Limatyrakis, and T. H. Lee, “Jitter and phase noise in ring oscillator,” IEEE JSSC, 34(6): 790-804, 1999, the descriptions of which are incorporated herein by reference. [0015] Referring now to [0016] A typical technique for noise reduction is to increase the supply current, however, low power designs simply cannot supply the larger noise reduction currents necessary for this method of noise reduction. The symmetry cell 110 can operate to reduce noise in low power designs for a given supply current. [0017] The symmetry cell 110 is electrically coupled to the inverting delay cell 120 forming an integrated pair of circuits connected at a common mode node. The circuit pair includes an input for receiving a differential input signal (input1 and input2) and an output for outputting a delayed differential signal (output1 and output2) responsive to the input signal. The symmetry cell 110 is configured to provide symmetry to the rising and falling edges of the differential output signal (output1 and output2) waveform produced by the delay cell 120. A symmetrical waveform advantageously reduces or eliminates the low-frequency-noise (1/f) upconversion in a time-varying phase-noise model. [0018] Additionally, the symmetry cell 110 is configured to advantageously steer the current into the circuit pair to reduce the voltage variation on the common mode node. Reduced voltage variation on the common mode node consequently reduces kickback which operates to reduce or eliminate noise (i.e., current variance) from a transistor type current source. [0019] Referring now to [0020] Regarding input circuit 22, the source of transistor MP1 is connected at common mode node N1 which is a shared node of current source Is. The gate of MP1 is connected to differential input Vinpand the drain of transistor MP1 is connected to the drain of transistor MN1 at node N2. The source of MN1 is connected to ground (or power supply) and its gate is coupled to differential input Vinp. For input circuit 24, the source of transistor MP3 is also connected at N1. The gate of MP3 is connected to differential input Vinmand the drain of transistor MP3 is connected to the drain of transistor MN3 at node N3. The source of MN3 is connected to ground and its gate is coupled to differential input Vinm. [0021] The parallel symmetry output circuits 205 and 210 are connected to the common mode node N1. More specially, for symmetry output circuit 205, the source of transistor MP2 is connected to node N1. The drain and gate of MP2 are connected to node N2. The drain and gate of MN2 are also connected to node N2 and its source is connected to ground. One of the symmetrical differential output signals (Voutm) is provided at node N2. [0022] For symmetry output circuit 210, the source of transistor MP4 is connected to common mode N1. The drain and gate of MP4 are connected to node N3. The drain and gate of transistor MN4 are also connected to node N3 and its source is connected to ground. The other symmetrical differential output signal (Voutp) is provided at node N3. There is a propagation delay time between the input signals Vinpand Vinmand the corresponding responsive output signals Voutmand Voutp. In at least one embodiment, transistors MP1, MP2, MP3, MP4, MN1, MN2, MN3, and MN4 are metal-oxide semiconductor (MOS) transistors. Further, in at least one embodiment, MP1, MP2, MP3 and MP4 are p-channel MOS transistors and MN1, MN2, MN3, and MN4 are n-channel MOS transistors all of which can be integrated as a complementary MOS device. [0023] Jitter and/or phase noise caused by the up-conversion of the low frequency component of the noise is reduced or eliminated by sizing the transistors to enable output signals Voutm, and Voutpwith respective waveforms exhibiting symmetrical rising and falling edges. The rising and falling edge on each of the outputs can be symmetrically shaped by choosing equal sizes for the corresponding transistors. [0024] In operation when the input signal level is between a minimum (min) and a midpoint [(max−min)/2+min], the transistors MP1 and MN2 are conducting and the gain is determined approximately by gmp1/gmn2 (gmp1 is the transconductance of MP1 and gmn2 is the transconductance of MN2). When the signal level is between the midpoint and maximum (max), transistors MN1 and MP2 are conducting and the gain is determined approximately by gmn1/gmp2 (gmn1 is the transconductance of MN1 and gmp2 is the transconductance of MP2). The size of the transistors are advantageously selected so that these two gains are similar, therefore, the rising and falling edges of the output signal are approximately symmetrical. The same explanation holds for the other half of the circuit (MN3, MN4, MP3 and MP4). Note, for example, that when MN1 and MP1 are sized to have approximately the same transconductance, and MN2 and MP2 are sized to have approximately the same transconductance, then gmn1/gmp2≈gmp1/gmn2. The gain is, in some embodiments, selected to be as low as possible while guaranteeing the oscillation. [0025] The output voltage swing, of the differential current steering delay cell, is advantageously limited, enabling a limited oscillation magnitude which also enables an oscillation frequency that is insensitive to supply voltage variations. By applying the diode-connected transistors (MN2 and MP2; MN4 and MP4) the output magnitude is limited to the gate-to-source voltage, Vgs, of the transistors which are not supply dependent. Therefore, the output magnitude and the oscillation frequency are insensitive to the supply voltage. For example, in an operating voltage range of approximately 1.1 to approximately 1.5, simulation results show that for a voltage variation of 10 mV, the oscillation magnitude and oscillation frequency exhibit little or no variations. [0026] Additionally, transistors MP2 and MP4 (which are connected to the common mode node N1) advantageously steer current into each half circuit of the differential delay cell, reducing the voltage variation on N1 and, thereby, reducing the kickback from the delay cell to the current source Is. Consequently, current source fluctuation or noise is reduced. [0027] Kickback from the delay cell causes a modulation of the drain-source voltage (Vds) of a transistor current source which, thereby, modulates the current supplied to the delay cell. Delay cells which enable a more constant supply current throughout the period of oscillation further improves the phase-noise characteristics of, for example, an oscillator or clock generator employing the differential delay cell. [0028] In accordance with the present invention, when the input signal level (Vinp) is between the minimum and midpoint, the transistor MP1 and MN2 conduct on one side and MN3 and MP4 conduct on the other side (since this is a differential circuit, the other input (Vinm) will be between the midpoint and maximum). During this phase, transistors MN1, MP2, MP3, and MN4 are off. When signal level Vinpis between the midpoint and maximum, transistor MN1 and MP2 conduct on one side and MP3 and MN4 conduct on the other side, and transistors MP1, MN2, MN3, and MP4 are off during this phase. [0029] To further illustrate, suppose MP2 and MP4 are not used, during the transition from MP1 conducting (MP3 off) to MP3 conducting (MP1 off), the circuit is not fully conducting. Since there is no flow path for the full tail current, the tail current is reduced by modulating the Vdswhich in turn disadvantageously modulates the voltage on N1. By adding MP2 and MP4, even during the signal voltage transition, the current can flow through either MP2 or MP4 depending on the transition direction, thus advantageously reducing the tail current variation and hence the voltage on N1. For example, during the transition when MP1 is off and MP3 starts to conduct, the current can flow through MP2. So MP2 and MP4 act to steer the current into each half circuit and make the transition smoother to reduce the voltage variation on N1. [0030] [0031] Although a preferred embodiment of the method and system of the present invention has been illustrated in the accompanied drawings and described in the foregoing Detailed Description, it is understood that the invention is not limited to the embodiments disclosed, but is capable of numerous rearrangements, modifications, and substitutions without departing from the spirit of the invention as set forth and defined by the following claims. A circuit for providing a symmetrical output signal to a communication system. The circuit includes an input circuit (22 and 24) for receiving an input signal and a symmetry circuits (205 and 210) advantageously configured to provide an output signal exhibiting a symmetrical rising and falling edge waveform in response to the received input signal. An integrated power source (Is) provides current to a common node (N1) in which current is advantageously steered to each half circuit (22, 205 and 24, 210) to reduce voltage variation on the common node during voltage transition of the input signal, hence, reducing current fluctuation from the current source. 1. An apparatus for providing an output signal waveform responsive to an input signal waveform, comprising:

an input adapted to receive said input signal waveform; an output adapted to output said output signal waveform; a delay circuit coupled between said input and said output; and a symmetry circuit coupled to said delay circuit and cooperable therewith to produce a gain characteristic between said input and said output that provides said output signal waveform with approximately symmetrical rising and falling edges. 2. The apparatus of 3. The apparatus of 4. The apparatus of 5. The apparatus of 6. The apparatus of 7. The apparatus of 8. The apparatus of 9. The apparatus of 10. The apparatus of 11. An apparatus for providing a differential output signal responsive to a differential input signal, comprising:

first and second inputs respectively adapted to receive first and second waveform portions of said differential input signal; first and second outputs respectively adapted to output first and second waveform portions of said differential output signal; a first delay circuit coupled between said first input and said first output; a second delay circuit coupled between said second input and said second output; a first symmetry circuit coupled to said first delay circuit and cooperable therewith to produce a gain characteristic between said first input and said first output that provides said differential output signal first waveform portion with approximately symmetrical rising and falling edges; and a second symmetry circuit coupled to said second delay circuit and cooperable therewith to produce a gain characteristic between said second input and said second output that provides said differential output signal second waveform portion with approximately symmetrical rising and falling edges. 12. The apparatus of 13. The apparatus of 14. The apparatus of 15. The apparatus of 16. An apparatus for providing a differential output signal responsive to a differential input signal, comprising:

first and second inputs respectively adapted to receive first and second waveform portions of said differential input signal; first and second outputs respectively adapted to output first and second waveform portions of said differential output signal; a first delay half circuit coupled between said first input and said first output and adapted to produces a first gain characteristic between said first input and said first output; a second delay half circuit coupled between said second input and said second output and adapted to produces a second gain characteristic between said second input and said second output, and wherein said delay half circuits are coupled at a common node; first and second current steering circuits coupled to said common node and cooperable to steer current from said common node to said delay half circuits. 17. The apparatus of 18. The apparatus of 19. The apparatus of 20. The apparatus of BACKGROUND OF THE INVENTION

SUMMARY OF THE INVENTION

BRIEF DESCRIPTION OF THE DRAWINGS

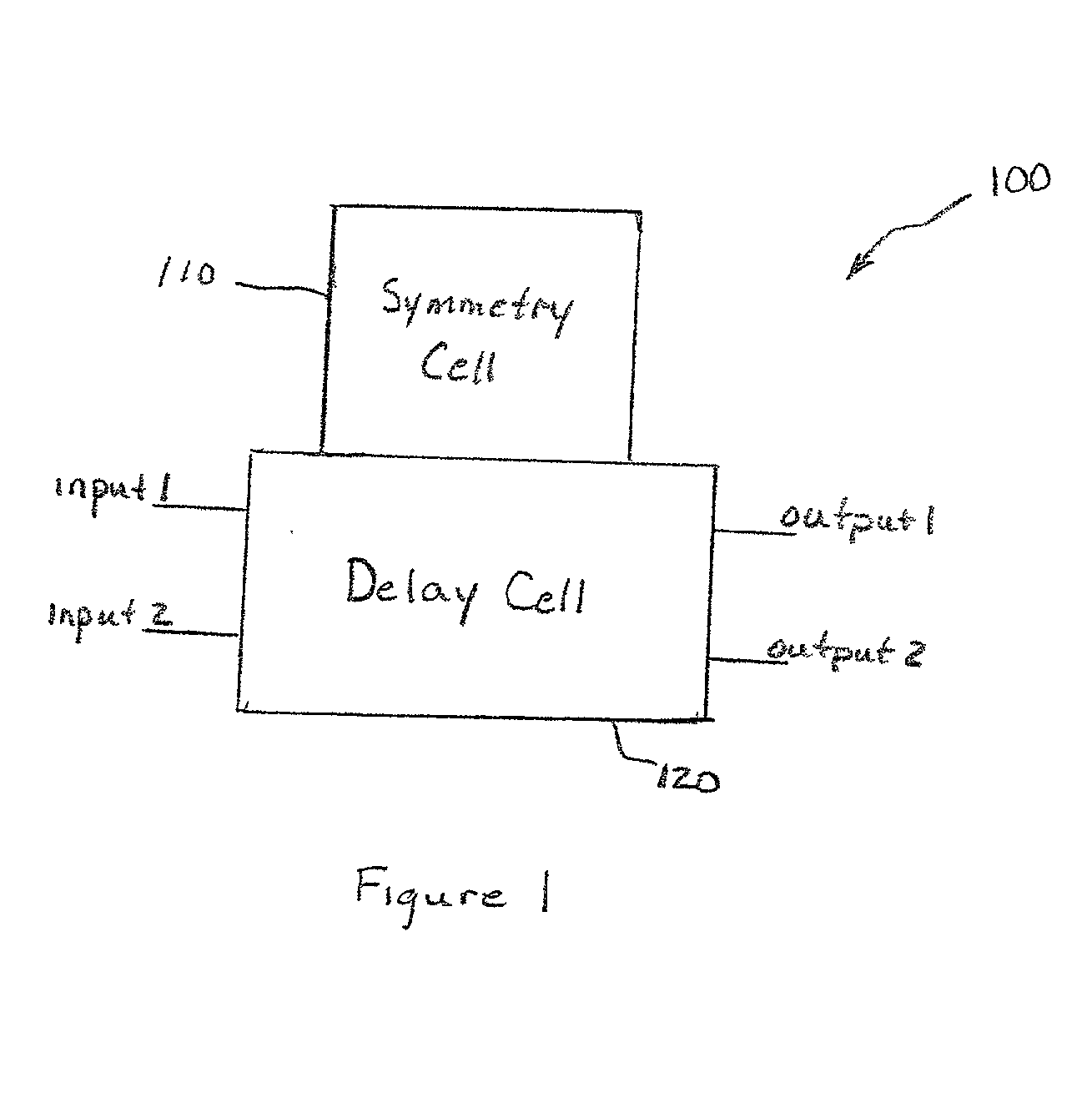

DETAILED DESCRIPTION OF THE INVENTION