US 20160173115A1

### (19) United States

# (12) Patent Application Publication OKUDA et al.

### (10) Pub. No.: US 2016/0173115 A1

(43) **Pub. Date: Jun. 16, 2016**

## (54) PASSIVE AMPLIFICATION CIRCUIT AND ANALOG-DIGITAL CONVERTOR

## (71) Applicant: RENESAS ELECTRONICS CORPORATION, Tokyo (JP)

(72) Inventors: **Yuichi OKUDA**, Tokyo (JP); **Hideo NAKANE**, Tokyo (JP); **Takaya**

YAMAMOTO, Tokyo (JP); Keisuke KIMURA, Tokyo (JP); Takashi OSHIMA, Tokyo (JP); Tatsuji MATSUURA, Tokyo (JP)

(21) Appl. No.: 15/051,193

(22) Filed: Feb. 23, 2016

#### Related U.S. Application Data

(63) Continuation of application No. 14/692,374, filed on Apr. 21, 2015, now Pat. No. 9,294,115, which is a continuation of application No. 14/159,511, filed on Jan. 21, 2014, now Pat. No. 9,054,726.

#### (30) Foreign Application Priority Data

| Jan. 23, 2013 | (JP) | 2013-010218 |

|---------------|------|-------------|

| Dec. 17, 2013 | (JP) | 2013-259954 |

#### **Publication Classification**

| (51) | Int. Cl.  |           |

|------|-----------|-----------|

|      | H03M 1/10 | (2006.01) |

|      | H03F 1/32 | (2006.01) |

|      | H03F 3/00 | (2006.01) |

|      | H03F 1/02 | (2006.01) |

|      | H03M 1/00 | (2006.01) |

|      | H03M 1/38 | (2006.01) |

(52) U.S. Cl.

#### (57) ABSTRACT

A differential signal is amplified by passive amplification which does not a reference of a common-mode voltage. At this time, the voltage of the differential signal is passive-amplified twice before carrying out a successive approximation type analog-digital conversion operation. The passive amplification is attained by providing a plurality of capacitances which carry out a sampling operation, and switching these connection relation by using switches. Without being accompanied by the increase of the consumed power and the chip size, an influence by the noise of s comparator is reduced to a half so that the effective resolution can be increased for one bit.

FIG. 1A RELATED ART

FIG. 1B RELATED ART

FIG. 2A

FIG. 2B RELATED ART

FIG.3A

FIG.3B

RELATED ART

## FIG. 4A

FIG.4B

$FIG.\,5\,A$

FIG.5B

WH WH ADC DC

FIG. 6

SN, ADC, ~VHbSW4 VHa ŠW3 VHbSW2

FIG. 8A

FIG. 8B

FIG. 8C

FIG. 8D

AĎC ΡÀ Š, エ

FIG. 9

ADC BCTSW6 BCTSW2 BC1SW1-BC1SW3/ Ŗ, -- BC1SW4 VHbC3

FIG. 11A

FIG. 11B

FIG. 11C

FIG. 12A

FIG. 12B

FIG. 12C

FIG 13

FIG. 14

IB S H ADC

FIG. 15

~VHaSW4 VHbSW7 VHaC3 VHaSW1 VHbc3\_

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 1

FIG. 20

## PASSIVE AMPLIFICATION CIRCUIT AND ANALOG-DIGITAL CONVERTOR

#### CROSS REFERENCE

[0001] This application is a continuation of U.S. patent application Ser. No. 14/692,374, filed Apr. 21, 2015 which is a continuation of U.S. patent application Ser. No. 14/159,511, filed Jan. 1, 2014, now U.S. Pat. No. 9,054,726, issued Jun. 9, 2015, which claims priorities on convention based on Japanese Patent Application Nos. JP 2013-010218 and JP 2013-259954. The disclosure thereof is incorporated herein by reference.

#### TECHNICAL FIELD

[0002] The present invention is related to a passive amplification circuit and an analog-digital convertor, and more particularly, to a passive amplification circuit having the voltage gain of 1 to 2 times, and an analog-digital convertor suitable for a charge share type successive approximation type analog-digital convertor.

#### **BACKGROUND ART**

[0003] Conventionally, a configuration is generally used in which correct signal amplification is carried out by using a closed amplifier for a circuit which contains an amplification stage thereinside, such as a pipeline ADC (Analog-Digital Converter).

[0004] However, although the closed amplifier can realize amplification in a high precision, it causes the increase of the consumed power in a high-speed operation. As a result, it is tended to increase the the consumed power of the ADC. Therefore, the approach is proposed in which the consumed power is suppressed by employing an open loop amplifier, a dynamic amplifier such as a comparator, and a passive amplifier by a passive device.

[0005] However, while these schemes can realize the high-speed operation and the low consumed power operation, it is difficult to realize linearity and a gain in a high precision independently. Thus, a usage method in which a calibration technique is combined is adopted.

[0006] Not only an inter-stage amplifier of the pipeline ADC but also an ADC which carries out a sampling operation are effective for these schemes in which signal amplification is carried out without the closed amplifier. If an amplification stage is provided after the sampling stage, an input conversion noise after sampling stage can be reduced and the noise request can be eased.

[0007] A technique which relates to the above technique is reported in Non-Patent Literature 1 and Patent Literature 1. In Non-Patent Literature 1, a method of simply realizing signal amplification by using a capacitance is described. In Patent Literature 1, a method of carrying out the amplification of only a differential signal by using a common mode reference voltage is proposed.

[0008] Also, a next generation mobile phone terminal requires that it is possible to handle various methods of LTE (Long Term Evolution) and LTE Advanced in addition to a conventional GSM (Global System for Mobile communication) method and the WCDMA (Wideband Code Division Multiple Access) method. For a signal received in each of these methods of one analog-digital convertor, the conversion

rate as high-speed as about 40 MS/s (mega sample per second) and the high effective resolution of 11 bits or more are required.

[0009] Also, in the mobile terminal, a very small consumed power of the analog-digital convertor is required. Due to the miniaturization of the semiconductor manufacture process, an error factor of an analog circuit of the analog-digital convertor is corrected with a digital circuit, to improve the effective resolution. As the analog-digital convertor with low consumed power, an analog-digital convertor of a successive approximation type is suitable to carry out a digital correction. Moreover, as the analog-digital convertor of the successive approximation type which carries out a high-speed operation, the analog-digital convertor with a charge share-type successive approximation type according to the following Non-Patent Literature 2 more than the analog-digital convertor of a charge share type successive approximation type's being suits.

**[0010]** In the microcomputer of the next generation, as the multi-function develops, the analog-digital convertor of the high speed and high resolution is required. As the analog-digital convertor mounted on a microcomputer, the effective resolution of 11 bits or more is often required.

[0011] Also, in case of the microcomputer, especially, it is required that chip size of the analog-digital convertor is small. Therefore, the analog-digital convertor of the successive approximation type which carries out the digital correction is more suitable than the analog-digital convertor of a pipeline type which carries out the digital correction. Moreover, because the high-speed operation of tens of MS/s or higher is required in many cases, the analog-digital convertor of a charge share-type successive approximation type is suitable.

[0012] The analog-digital convertor of the charge share-type and successive approximation type which carries out a digital correction has one feature that a high resolution can be realized in the small chip size and consumed power in the conversion rate of about 100 MS/s or below. Therefore, the wide application such as SoC (System on a Chip) technique is thought of in addition to the above convertor.

[0013] A comparator for the analog-digital convertor is disclosed in Patent Literatures 2 and 3.

[0014] Non-Patent Literature 3 discloses an approach which improves an effective resolution, by setting an input full scale range to Rail-to-Rail, in the analog-digital convertor of the charge redistribution-type and the successive approximation type which carries out the digital correction. That is, by using from the power supply voltage VDD to the grounding voltage completely, a signal component is maximized in SNR (Signal to Noise Ratio).

[0015] Also, many conventional analog-digital convertor of the successive approximation type disclose the approaches which improve an effective resolution by fundamentally reducing a quantity of noise generated by a comparator known as a dominant noise source of the analog-digital convertor. The noise voltage level of the comparator is inversely proportion to a square root of the capacitance. Therefore, by increasing a capacitance value to 4 times, the noise can be reduced to a half. When the capacitance is increased to 4 times, it needs to maintain a conversion rate by increasing the consumed power of the comparator to 4 times to maintain a response speed.

[0016] Non-Patent Literature 4 discloses an analog-digital convertor of a charge redistribution-type and a successive approximation type which carries out the determination of

each of bits in a first half from the MSB (Most Significant Bit). Next, a conversion residual after the conversion of the first half is amplified by an intermediate amplifier and the analog-digital conversion is carried out to the amplified residual. Thus, each of bits of the second half to the LSB (Least Significant Bit) is determined. In this way, because the noise level which is required for the comparator can be eased for the gain of the above-mentioned intermediate amplifier, the influence by the noise of the comparator can be substantively made small.

[0017] Non-Patent Literature 5 discloses a sigma-delta analog-digital convertor which is known to be possible to output a high resolution.

#### CITATION LIST

[0018] [Patent Literature 1] US 2010/0237710A1

[0019] [Patent Literature 2] JP 560-51901A

[0020] [Patent Literature 3] JP 2000-269792A

[0021] [Non-Patent Literature 1] I. Ahmed et al., "A 50 MS/s 9.9 mW Pipelined ADC with 58 dB SNDR in 0.18 µm CMOS Using Capacitive Charge-Pumps", ISSCC Dig. Tech. Papers, pp. 164-165, 2009.

[0022] [Non-Patent Literature 2] Jan Craninckx and Geert Van der Plas, "A 65fJ/Conversion-Step 0-to-50 MS/s 0-to-0.7 mW 9 b Charge-Sharing SAR ADC in 90 nm Digital CMOS," International Solid-State Circuits Conference, Digest of Technical Papers, pp. 246-247, February 2007.

[0023] [Non-Patent Literature 3] Wenbo Liu, Pingli Huang and Yun Chiu, "A 12 b 22.5/45 MS/s 3.0 mW 0.059 mm2 CMOS SAR ADC achieving over 90 dB SFDR", International Solid-State Circuits Conference, Digest of Technical Papers, pp. 380-381, February 2010.

[0024] [Non-Patent Literature 4] Christopher Peter Hurrell, Colin Lynden, David Laing, Derek Hummerston and Mark Vickery, "An 18 b 12.5 MHz ADC with 93 dB SNR", International Solid-State Circuits Conference, Digest of Technical Papers, pp. 378-379, February 2012.

[0025] [Non-patent literature 5] Yun-Shiang Shu, Bang-Sup Song and Kantilal Bacrania, "A 65 nm CMOS CTΔΣ modulator with 81 dB DR and 8 MHz BW auto-tuned by pulse injection", International Solid-State Circuits Conference, Digest of Technical Papers, pp. 500-501, February 2008.

#### SUMMARY OF THE INVENTION

[0026] When a differential signal is amplified by a passive amplifier, only the differential signal is amplified without needing a reference of a common-mode voltage. Also, an error efficient of an analog circuit which is a cause to degrade the effective resolution of the analog-digital converter, contains a non-linear error, a DC offset, a comparator noise and so on. It is possible to improve the effective resolution by carrying out the digital correction for the non-linear error and the DC offset. However, because the comparator noise is a random noise, it is difficult to carry out a systematic correction such as the digital correction. One object of the present invention is to improve the effective resolution of the analog-digital convertor which carries out the digital correction. Other objects and a new feature would become clear from the description of this Specification and the attached drawings.

[0027] According to an embodiment, a differential signal is passive-amplified by a passive amplifier which does not use a reference of a common-mode voltage, and before carrying

out an analog-digital conversion operation, the voltage of the differential signal is passive-amplified to twice.

[0028] According to the embodiment, it becomes possible to avoid a high-speed charging and discharging operation because the reference of the common-mode voltage is not used for the passive amplifier. Also, without being accompanied by the increase of the consumed power and the chip size, an influence of the noise of the comparator can be reduced to a half so that the effective resolution can be increased for one bit

#### BRIEF DESCRIPTION OF THE DRAWINGS

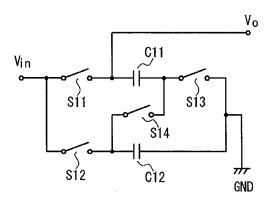

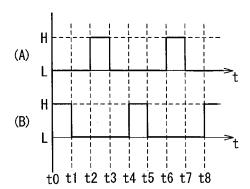

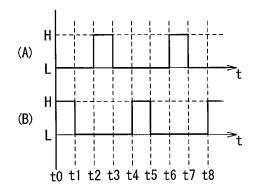

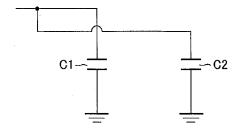

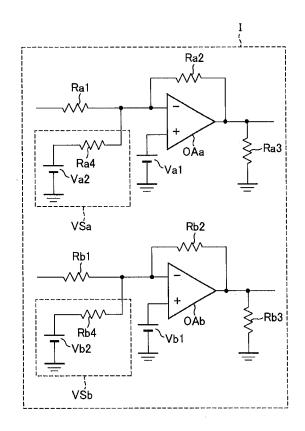

**[0029]** FIG. 1A is a diagram schematically showing a configuration example of a passive amplification circuit according to a conventional example 1;

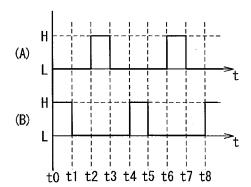

[0030] FIG. 1B is a time chart showing an example of a control signal to control each switch group shown in FIG. 1A; [0031] FIG. 2A is a diagram schematically showing a configuration example of the passive amplification circuit according to the conventional example 2;

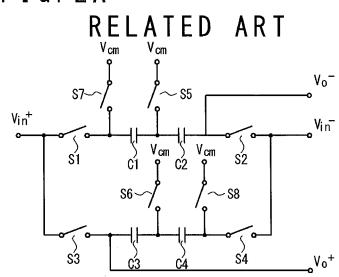

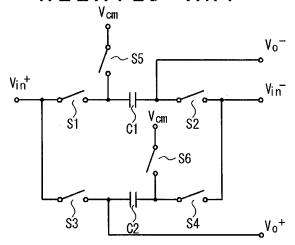

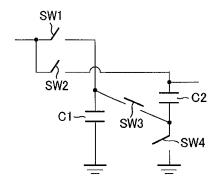

[0032] FIG. 2B is a time chart showing an example of the control signal to control each switch group shown in FIG. 2A; [0033] FIG. 3A is a diagram schematically showing a configuration example of the passive amplification circuit according to the conventional example 3;

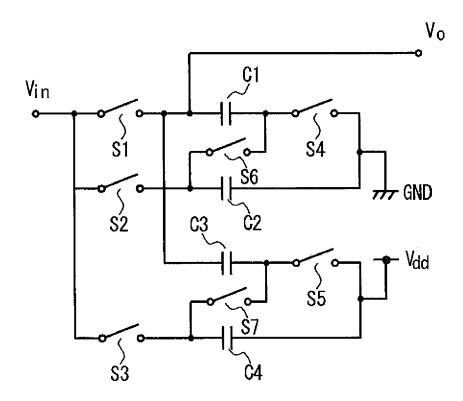

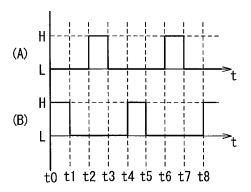

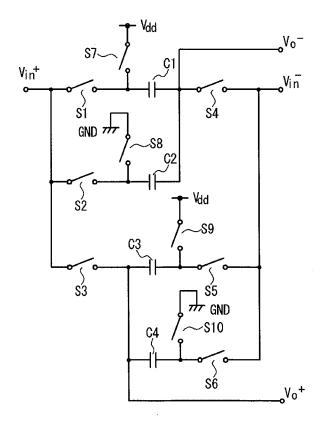

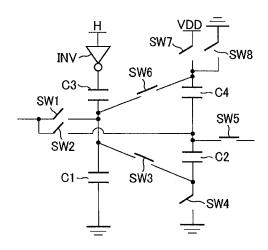

[0034] FIG. 3B is a time chart showing an example of the control signal to control each switch group shown in FIG. 2A; [0035] FIG. 4A is a diagram schematically showing the configuration example of the passive amplification circuit in a first embodiment of the present invention;

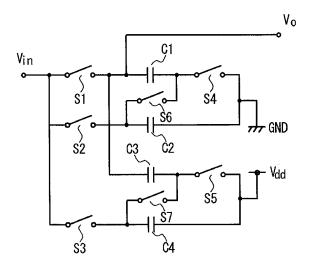

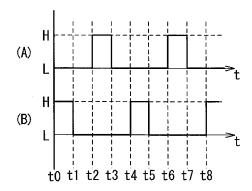

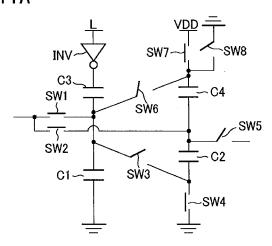

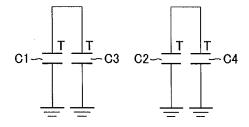

[0036] FIG. 4B is a time chart showing an example of the control signal to control each switch group shown in FIG. 4A; [0037] FIG. 5A is a diagram schematically showing the configuration example of the passive amplification circuit in a second embodiment;

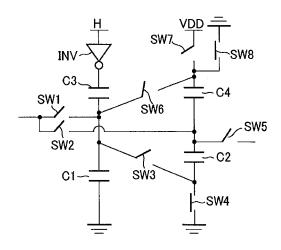

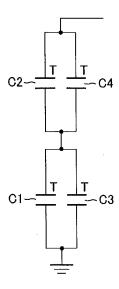

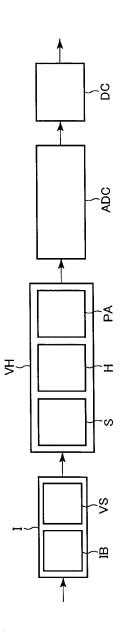

[0038] FIG. 5B is a time chart showing an example of the control signal to control each switch group shown in FIG. 5A; [0039] FIG. 6 is a functional block diagram showing the configuration of an analog-digital convertor in a third embodiment;

[0040] FIG. 7 is a diagram schematically showing the configuration of a voltage holding circuit section and the analog-digital converting circuit section in the third embodiment;

[0041] FIG. 8A is a diagram schematically showing a first state in each of a positive phase side voltage holding circuit section and a negative phase side voltage holding circuit section in the third embodiment;

[0042] FIG. 8B is an equivalent circuit diagram corresponding to the first state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the third embodiment;

[0043] FIG. 8C is a diagram schematically showing a second state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the third embodiment:

[0044] FIG. 8D is an equivalent circuit diagram corresponding to the second state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the third embodiment;

[0045] FIG. 9 is a functional block diagram showing the configuration of the analog-digital convertor in a fourth embodiment;

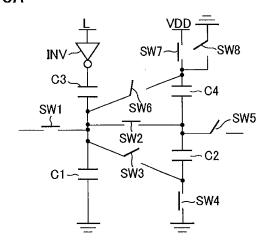

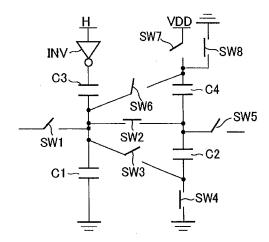

[0046] FIG. 10 is a diagram schematically showing the configuration of a voltage holding circuit section VH and the analog-digital converting circuit section in the fourth embodiment:

[0047] FIG. 11A is a diagram schematically showing the first state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment;

[0048] FIG. 11B is a diagram schematically showing the second state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment;

[0049] FIG. 11C is a diagram schematically showing a third state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment;

[0050] FIG. 12A is an equivalent circuit diagram showing the first state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment shown in FIG. 11A;

[0051] FIG. 12B is an equivalent circuit diagram showing the second state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment shown in FIG. 11B;

[0052] FIG. 12C is an equivalent circuit diagram showing the third state which is common to the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the fourth embodiment shown in FIG. 11C;

[0053] FIG. 13 is a functional block diagram showing the configuration of the analog-digital convertor in a fifth embodiment;

[0054] FIG. 14 is a diagram schematically showing the configuration of an input circuit section in the fifth embodiment.

[0055] FIG. 15 is a functional block diagram showing the configuration of the analog-digital convertor in a sixth embodiment:

[0056] FIG. 16 is a diagram schematically showing the configuration of a voltage holding circuit section and the analog-digital converting circuit section in a seventh embodiment;

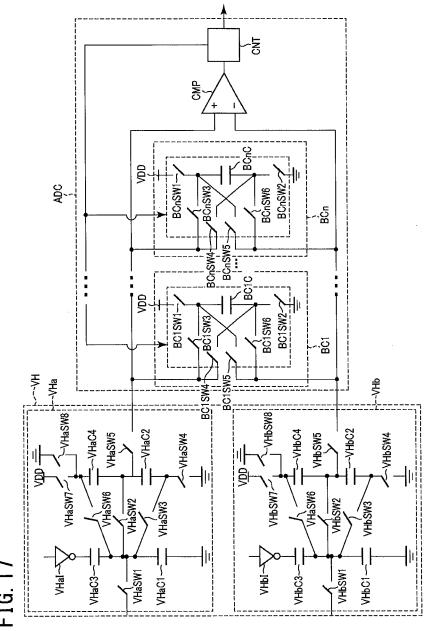

[0057] FIG. 17 is a diagram schematically showing the configuration of the voltage holding circuit section and the analog-digital converting circuit section in an eighth embodiment:

[0058] FIG. 18A is a diagram schematically showing the first state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the eighth embodiment;

[0059] FIG. 18B is a diagram schematically showing the second state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the eighth embodiment;

[0060] FIG. 18C is a diagram schematically showing the third state in each of the positive phase side voltage holding circuit section and the negative phase side voltage holding circuit section in the eighth embodiment;

[0061] FIG. 19 is a diagram schematically showing the configuration of the analog-digital converting circuit section in a ninth embodiment;

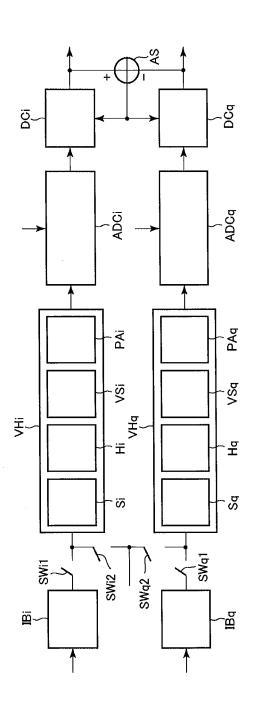

[0062] FIG. 20 is a functional block diagram showing the configuration of the analog-digital convertor in which the two analog-digital converting circuit sections are combined in a tenth embodiment;

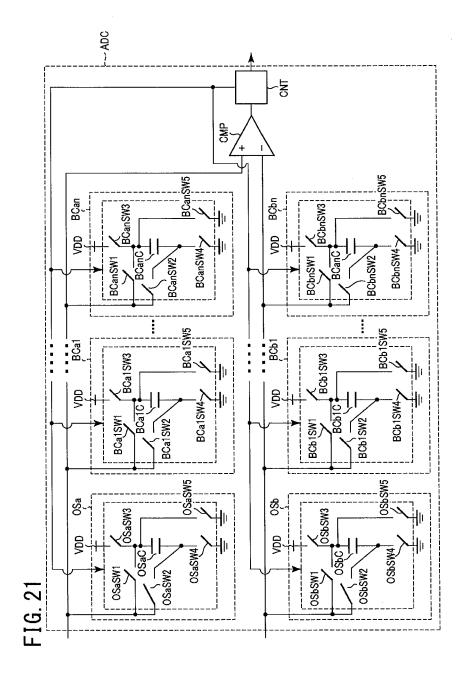

[0063] FIG. 21 is a diagram schematically showing the configuration of the analog-digital converting circuit section in an eleventh embodiment;

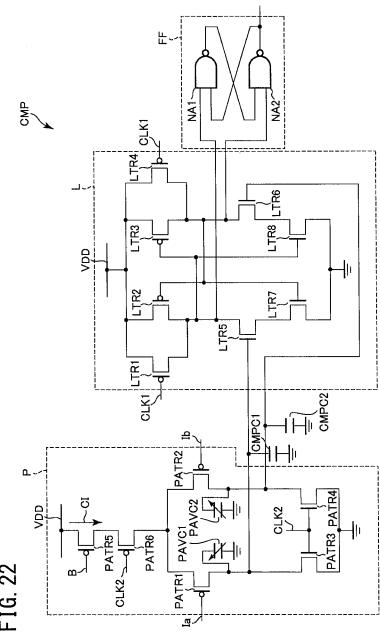

[0064] FIG. 22 is a diagram schematically showing the configuration of a comparator in a twelfth embodiment;

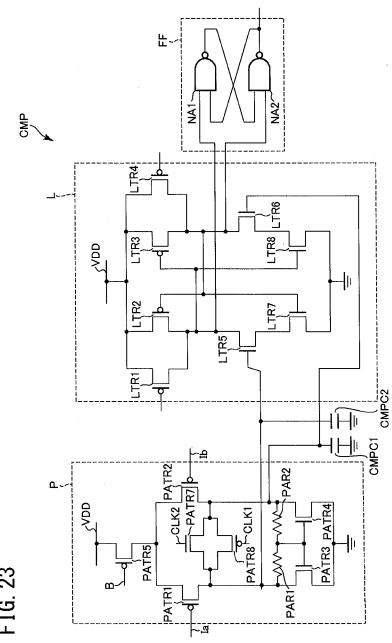

[0065] FIG. 23 is a diagram schematically showing the configuration of the comparator in a thirteenth embodiment; and

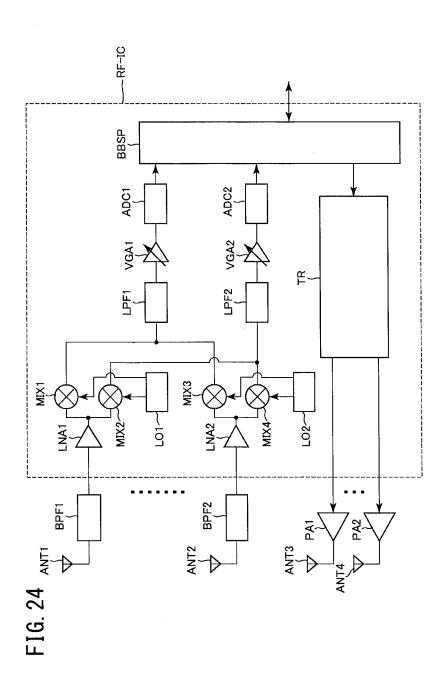

[0066] FIG. 24 is a diagram schematically showing the configuration of an RF-IC for a mobile terminal in a four-teenth embodiment and the components of a peripheral circuit.

#### DESCRIPTION OF EMBODIMENTS

[0067] Hereinafter, embodiments will be described.

[0068] At first, problems in a the conventional passive amplification circuit will be described as the conventional examples 1 to 3 in order to facilitate the understanding of technical meaning.

#### CONVENTIONAL EXAMPLE 1

[0069] In Non-Patent Literature 1, a method of simply realizing signal amplification by using a capacitance has been described. In this method, capacitances connected in parallel are stacked in serial upon sampling a signal so as to obtain a voltage with the magnitude of about twice.

[0070] FIG. 1A is a diagram schematically showing a configuration example of the passive amplification circuit according to the conventional example 1.

[0071] The components of the passive amplification circuit shown in FIG. 1A will be described. The passive amplification circuit shown in FIG. 1A has a first capacitance C11, a second capacitance C12, an input terminal  $V_{in}$ , an output terminal Vo, the ground voltage GND, and a first switch S11 to a fourth switch S14. Here, the first capacitance C1 and the second capacitance C2 have a same capacitive amount or capacitance.

[0072] The connection relation of the respective components shown in FIG. 1A will be described. The input terminal Vin is connected in common with one of the ends of a first switch S11 and one of the ends of the second switch S12. The output terminal Vo is connected in common with the other end of the first switch S11 and one of the ends of the first capacitance C11. The other end of the second switch S12 is connected in common with one of the ends of the second capacitance C12 and one of the ends of the fourth switch S14. The other end of the first capacitance C11 is connected in common with one of the ends of the third switch S13 and the other end of the fourth switch S14. The ground voltage GND is connected in common with the other end with the second capacitance C12 and the other end of third switch S13.

[0073] An operation of the passive amplification circuit shown in FIG. 1A will be described. The first switch S11 to the third switch S13 are controlled simultaneously as a first switch group to switch between a block-off (isolation) state and a conductive state. The fourth switch S14 is controlled as a second switch group independently from the first switch group, to switch the block-off state and the conductive state.

[0074] The control of the first switch group and the second switch group is carried out in response to a first control signal and a second control signal which are generated by a control circuit (not shown).

[0075] FIG. 1B is a time chart showing an example of the control signal to control each of the switch groups shown in FIG. 1A. FIG. 1B contains a first graph (A) and a second graph (B).

[0076] The first graph (A) in FIG. 1B shows an example of the first control signal. The second graph (B) in FIG. 1B shows an example of the second control signal. In each of the first and second graphs (A) and the second graphs (B) shown in FIG. 1B, the horizontal axis shows a time and the vertical axis shows the logic state of the control signal. In this case, when each control signal is in the low state in each graph, the switch is set to the block-off state, and when being in the high state, the switch is set to the conductive state.

[0077] In an example of a time chart shown in FIG. 1B, in the time periods t0 to t1, t4 to t5, and t8 and the subsequent, the first switch S11 to the third switch S13 are in the block-off state and the fourth switch S14 is in the conductive state. At this time, in the circuit of FIG. 1A, the first capacitance C11 and the second capacitance C12 are connected between the input terminal Vin and the ground voltage GND in parallel. This state of the passive amplification circuit shown in FIG. 1A is called a parallel connection state.

[0078] In the same way, in the time periods of t2 to t3 and t6 to t7, the first capacitance C11 and the second capacitance C12 are connected in serial between the output terminal Vo and the ground voltage GND in this order. This state of the passive amplification circuit shown in FIG. 1A is called a serial connection state.

[0079] Besides, in time periods t1 to t2, t3 to t4, t5 to t6 and t7 to t8, all switches are in the block-off state. At this time, in the circuit of FIG. 1A, each of the terminals of the first capacitance C11 and the second capacitance C12 is insulated from all of the input terminals Vin, the output terminals Vo and the ground voltage GND. This state of the passive amplification circuit shown in FIG. 1A is called the block-off state.

[0080] The passive amplification circuit shown in FIG. 1A repeats the above-mentioned parallel connection state and the serial connection state through the block-off state. Thus, the sampling operation of a signal supplied from the input terminal Vin is carried out in the parallel connection state, and the voltages are stacked in serial to produce a voltage of approximately twice in the serial connection state outputted from the output terminal Vo.

[0081] When amplifying a differential signal by the passive amplification circuit shown in FIG. 1A, it is desired to amplify only a differential component of the differential signal. That is, when the voltage of the differential signal is expressed as Vcmi±Vin and an amplification gain is expressed as G, the desired output signal is Vcmo±GVin.

[0082] However, because common mode components of the differential signal is also amplified by the passive amplification circuit shown in FIG. 1A, GVcmi±GVin is actually obtained as the output signal. As a result, there is a problem that a level shift circuit is newly necessary, in order to take a consistence with an input range of the rear stage whose output dynamic range is limited.

[0083] As an approach to solve these problems, methods of amplifying only a differential signal by using the common mode reference is proposed in Non-Patent Literature 1 and

Patent Literature 1. These methods will be described as the conventional example 2 and the conventional example 3.

#### **CONVENTIONAL EXAMPLE 2**

[0084] FIG. 2A is a diagram schematically showing a configuration example of the passive amplification circuit according to the conventional example 2.

[0085] The components of the passive amplification circuit shown in FIG. 2A will be described. The passive amplification circuit shown in FIG. 2A has the first capacitance C1 to the fourth capacitance C4, the positive side input terminal of Vin+, the negative side input terminal Vin-, the positive side output terminal Vo+, the negative side output terminal Vo-, a reference voltage supply end Vcm, a first switch S1 to an eighth switch S8. Here, the first capacitance C1 to the fourth capacitance C4 have a same capacitance. The positive side input terminal Vin+ and the negative side input terminal Vinrespectively input a positive side voltage and a negative side voltage of an input signal. The positive side output terminal Vo+ and the negative side output terminal Vo- respectively output a positive side voltage and a negative side voltage of an output signal. The reference voltage supply end Vcm supplies a common mode component of the differential signal as a reference voltage.

[0086] The connection relation of the respective components shown in FIG. 2A will be described. The positive side input terminal Vin+ is connected with one of the ends of the first switch S1 and one of the ends of the third switch S3. The positive side output terminal Vo+ is connected in common with the other end of the third switch S3 and one of the ends of the third capacitance C3. The reference voltage supply end Vcm is connected with one of the ends of the fifth switch S5, one of the ends of the sixth switch S6, one of the ends of the seventh switch S7 and one of the ends of the eighth switch S8. One of the ends of the first capacitance C1 is connected in common with the other end of the first switch S1 and the other end of the seventh switch S7. The other end of the first capacitance C1 is connected with the other end of the fifth switch S5 and one of the ends of the second capacitance C2. The negative side output terminal Vo- is connected with the other end of the second capacitance C2 and one of the ends of the second switch S2. The other end of the third capacitance C3 is connected in common with the other end of the sixth switch C6 and one of the ends of the fourth capacitance C4. The other end of the fourth capacitance C4 is connected in common with the other end of the seventh switch S7 and one of the ends of the fourth switch S4. The negative side input terminal Vin- is connected in common with the other end of the second switch S2 and the other end of the fourth switch S4.

[0087] An operation of the passive amplification circuit shown in FIG. 2A will be described. The first switch S1 to the sixth switch C6 are controlled as the first switch group to carry out the switching between the block-off state and the conductive state at the same time. The seventh switch S7 to the eighth switch S8 are controlled as the second switch group to carry out the switching between the block-off state and the conductive state at the same time, independently from the first switch group.

[0088] The control of the first switch group and the second switch group is carried out in response to the first control signal and the second control signal which are generated by a control circuit (not shown).

[0089] FIG. 2B is a time chart showing an example of the control signals which controls each of the switch groups shown in FIG. 2A. The time chart in FIG. 2B is the same as the time chart shown in FIG. 1B. Also, because the relation between the control signals, the graphs and the above two switch groups shown in FIG. 2B is same as that of FIG. 1B, further detailed description is omitted.

[0090] The passive amplification circuit shown in FIG. 2A carries out a sampling operation in each of time periods of t0 to t1, t4 to t5 and t8 and the subsequent. At this time, the first capacitance C1 and the second capacitance C2 are connected in serial between the positive side input terminal Vin+ and the negative side input terminal Vin-, and moreover the reference voltage is applied to a node between the two capacitances. In the same way, the third capacitance C3 and the fourth capacitance C4 are connected in serial between the positive side input terminal Vin+ and the negative side input terminal Vin- and moreover a reference voltage is applied to a node between the two capacitances. Note that at this time, a set of the first capacitance C1 and the second capacitance C2 and a set of the third capacitance C3 and the fourth capacitance C4 are connected in parallel.

[0091] The reference voltage is equal to the common mode component of the differential signal Vcmi±Vin which is supplied between the positive side input terminal Vin+ and the negative side input terminal Vin-. Therefore, at the time of sampling, only a differential component of the differential signal is applied to the first capacitance C1 to the fourth capacitance C4.

[0092] Also, the passive amplification circuit shown in FIG. 2A amplification-operates in the time periods t2 to t3 and t6 to t7. At this time, the first capacitance C1 and the second capacitance C2 are connected in serial between the reference voltage supply end Vcm and the negative side output terminal Vo-. In the same way, the third capacitance C3 and the fourth capacitance C4 are connected in serial between the reference voltage supply end Vcm and the positive side output terminal Vo+. Therefore, a signal in which only a differential component of the differential signal is amplified approximately twice is obtained to the output terminals.

#### **CONVENTIONAL EXAMPLE 3**

[0093] FIG. 3A is a diagram schematically showing a configuration example of the passive amplification circuit according to the conventional example 3.

[0094] The component of the passive amplification circuit shown in FIG. 3A will be described. The passive amplification circuit shown in FIG. 3A has the first capacitance C1, the second capacitance C2, the positive side input terminal Vin+, the negative side input terminal Vin-, the positive side output terminal Vo+, the negative side output terminal Vo-, the reference voltage supply end Vcm, the first switch S1 to the sixth switch S6. Here, the first capacitance C1 and the second capacitance C2 have completely the same capacitance. The positive side input terminal Vin+ and the negative side input terminal Vin- input the positive side voltage and the negative side voltage of the input signal, respectively. The positive side output terminal Vo+ and the negative side output terminal output the positive side voltage and the negative side voltage of the output signal, respectively. The common mode component of the differential signal is supplied to the reference voltage supply end Vcm as the reference voltage.

[0095] The connection relation of the respective components shown in FIG. 3A will be described. The positive side

input terminal Vin+ is connected in common with one of the ends of the first switch S1 and one of the ends of the third switch S3. The reference voltage supply end Vcm is connected with one of the ends of the fifth switch S5 and one of the ends of the sixth switch S6. One of the ends of the first capacitance C1 is connected in common with the other end of the first switch S1 and the other end of the fifth switch S5. The negative side output terminal is connected in common with the other end of the first capacitance C1 and one of the ends of the second switch S2. The positive side output terminal Vo+ is connected in common with the other end of the third switch S3 and one of the ends of the second capacitance C2. The other end of the second capacitance C2 is connected in common with one of the ends of the fourth switch S4 and the other end of the sixth switch S6. The negative side input terminal Vin-is connected in common with the other end of the second switch S2 and the other end of the fourth switch S4.

[0096] An operation of the passive amplification circuit shown in FIG. 3A will be described. The first switch S1 to the fourth switch S4 are controlled as the first switch group to carry out the switching between the block-off state and the conductive state simultaneously. A fifth switch S5 and a sixth switch C6 are controlled as the second switch group to carry out the switching between the block-off state and the conductive state simultaneously and independently from the first switch group.

[0097] The control of the first switch group and the second switch group is carried out in response to the first control signal and the second control signal generated by a control circuit (not shown), respectively.

[0098] FIG. 3B is a time chart showing an example of the control signal which controls each switch group shown in FIG. 3A. The time chart shown in FIG. 3B is the same as the time chart shown in FIG. 1B. Also, because the relation between the respective graphs shown in FIG. 3B, the two control signal and the two switch groups is same as that of FIG. 1B, further detailed description is omitted.

[0099] The passive amplification circuit shown in FIG. 3A carries out the sampling operation in each of the time period t0 to t1, t4 to t5 and t8 and the subsequent. At this time, the first capacitance C1 and the second capacitance C2 are in the parallel connection state between the positive side input terminal Vin+ and the negative side input terminal Vin-.

[0100] Also, the passive amplification circuit shown in FIG. 3A carries out an amplification in the time periods t2 to t3 and t6 to t7. At this time, the first capacitance C1 is connected between the reference voltage supply end Vcm and the negative side output terminal Vo-. In the same way, the first capacitance C1 is connected between the positive side output terminal Vo+ and the reference voltage supply end Vcm.

[0101] The reference voltage which is applied from the reference voltage supply end Vcm is equal to the common mode component of the differential signal Vcmi±Vin which is supplied between the positive side input terminal Vin+ and the negative side input terminal Vin-. Therefore, in the passive amplification circuit shown in FIG. 3A, in amplification operation, the differential signal is obtained in which only a differential component is amplified by subtracting the reference voltage which is equivalent to the common mode component before the amplification from the differential signal amplified approximately twice.

[0102] Comparing with the case of the conventional example 2, there is a merit that can reduce a total capacitance area can be reduced in the passive amplification circuit

according to the conventional example 3. Also, comparing KT/C noise (thermal noise) per signal under a predetermined state, because a required capacitance in the conventional example 3 is only ½ of that of the conventional example 2, there is further advantage with respect to the area.

[0103] In this way, the high-speed charging and discharging operation in an about sampling frequency is carried out to a common mode reference in the conventional example 2 and the conventional example 3. Because a lack in convergence of the reference voltage causes degradation in the signal precision after the amplification, it is required to prepare a reference voltage source having a sufficient current supply performance and the high speed response performance. This leads to addition a new circuit such as a Low Drop Out (LDO) regulator and many pins, resulting in the cost increases.

[0104] In addition, there is another problem in a recent semiconductor circuit manufactured with a miniaturization process and driven with a low power supply voltage of about 1 V. In the miniaturization process, a MOS threshold value is comparatively high to the power supply voltage. Therefore, it is difficult to reduce the ON resistance of a switch which bypasses a voltage level (about 0.4 to 0.6 V in case of the power supply voltage of 1 V) which is selected as a common mode. For example, the seventh switch S7 and the eighth switch S8 in the conventional example 2 and the fifth switch S5 and the sixth switch C6 in the conventional example 3 are in the ON state in the amplification operation. However, it is difficult to reduce the ON resistance in case of using a realistic switch size, which causes reduction of the convergence speed and the degradation of the noise characteristic which is caused by the heat noise and so on.

[0105] Of the above-mentioned problem, the former problem of the reference voltage is called a first problem from now. Also, the latter problem of the ON resistance is called a second problem. In a first embodiment, a technique to solve the first problem is proposed. Also, in a second embodiment, a technique to solve the first problem and the second problem is proposed.

[0106] The passive amplification circuit according to an embodiment of the present invention will be described below with refers to the attached drawings.

[0107] Through a switching operation using a capacitance, a scheme of amplifying an input differential voltage signal to G times is proposed. Here, G is a gain and the value is contained in the range of 1<G<2.

[0108] Only two kinds of the power supply voltage and the ground voltage are required as the reference voltage and another reference voltage is not required. In the miniaturization process in recent years, for the improvement of robust property, the power supply voltage is generally supplied from LDO of an IC chip, and it is not a big problem to use the reference voltage of the power supply voltage level.

#### First Embodiment

[0109] FIG. 4A is a diagram schematically showing a configuration example of the passive amplification circuit according to a first embodiment. In this circuit configuration, as described above, only a differential signal component of an input signal is amplified without requiring a common mode reference which needs high-speed charging and discharging operation. The passive amplifier shown in FIG. 4A is used as a voltage holding circuit section VH of an analog-digital converter shown in FIG. 9. A signal of a single end in this case is exemplified, but two passive amplification circuits are used

according to a need, when a differential signal is supplied to the analog-digital converting circuit section ADC.

[0110] The component of the passive amplification circuit shown in FIG. 4A will be described. The passive amplification circuit shown in FIG. 4A has a first capacitance C1 to a fourth capacitance C4, and a first switch S1 to a seventh switch S7, an input terminal Vin, an output terminal Vo, a power supply voltage Vdd and the ground voltage GND. Here, the input terminal Vin receives an input signal. The output terminal Vo outputs an output signal to the analog-digital converting circuit section ADC. The power supply voltage Vdd supplies a power supply voltage. The ground voltage GND supplies the ground voltage.

[0111] The connection relation of each component shown in FIG. 4A will be described. The input terminal Vin is connected in common with one of the ends of the first switch S1, one of the ends of the second switch S2 and one of the ends of the third switch S3. The output terminal Vo is connected in common with the other end of the first switch S1, one of the ends of the first capacitance C1 and one of the ends of the third capacitance C3. The other end of the second switch S2 is connected in common with one of the ends of the sixth switch C6 and one of the ends of the second capacitance C2. The other end of the third switch S3 is connected in common with one of the ends of the seventh switch S7 and one of the ends of the fourth capacitance C4. The other end of the first capacitance C1 is connected in common with one of the ends of the fourth switch S4 and the other end of the sixth switch S6. The other end of the second capacitance C2 is connected in common with the other end of the fourth switch S4 and the ground voltage GND. The other end of the third capacitance C3 is connected in common with one of the ends of the fifth switch S5 and the other end of the seventh switch S7. The other end of the fourth capacitance C4 is connected in common with the other end of the fifth switch S5 and power Vdd.

[0112] The operation of the passive amplification circuit shown in FIG. 4A will be described. The first switch S1 to the fifth switch S5 are controlled so as to simultaneously carry out the switching between a block-off state and a conductive state all together as a first switch group. The sixth switch C6 and the seventh switch S7 are controlled so as to simultaneously carry out the switching between the block-off state and the conductive state all together as a second switch group, and so as to be independent from the first switch group.

[0113] The control of the first switch group and the second switch group is carried out in response to a first control signal and a second control signal which are generated by a control circuit (not shown).

[0114] FIG. 4B is a time chart showing an example of the control signal which controls each switch group shown in FIG. 4A. The time chart shown in FIG. 4B is the same as the time chart shown in FIG. 1B. Also, because the relation among the graphs shown in FIG. 4B, the above two control signals, and the above two switch groups is also same as that of FIG. 1B. Therefore, further detailed description is omitted. [0115] In the passive amplification circuit shown in FIG. 4A, a sampling action of the input signal supplied to the input terminal Vin is carried out in each range of time periods to to t1, t4 to t5 and t8 and the subsequent. At this time, the first capacitance C1 and the second capacitance C2 are connected in parallel between the input terminal Vin and the ground voltage GND. Also, the third capacitance C3 and the fourth capacitance C4 are connected in parallel between the input terminal Vin and power Vdd.

[0116] Also, in the passive amplification circuit shown in FIG. 4A, the amplifying operation is carried out in the range of the time periods t2 to t3 and t6 to t7. At this time, the first capacitance C1 and the second capacitance C2 are connected in serial between the output terminal Vo and the ground voltage GND. Also, the third capacitance C3 and the fourth capacitance C4 are connected in serial between power Vdd and the output terminal Vo.

[0117] It is supposed that a capacitance value of each of the first capacitance C1 and the second capacitance C2 is Ca and a capacitance value of each of the third capacitance C3 and the fourth capacitance C4 is Cb. Moreover, calculating a charge quantity to have been charged in the first capacitance C1 to the fourth capacitance C4 in case of the sampling operation and a charge quantity to have been charged in case of the amplifying operation, it is described from a conservation rule of a total electric charge quantity that the voltage of the output terminal Vo in the amplifying operation is equal to 2(Vin+Vdd×Ca/(Ca+Cb)).

[0118] That is, by appropriately selecting the capacitance values Ca and Cb, it is possible to design the common mode voltage of the output signal. Thus, a function of an in-phase voltage shift circuit section VS can be realized. Moreover, it is possible to design an amplifying circuit having a voltage gain in a range of one or two times by connecting a capacitance not having an amplification function in parallel with a set of the capacitances which have such an amplification function.

## Second Embodiment

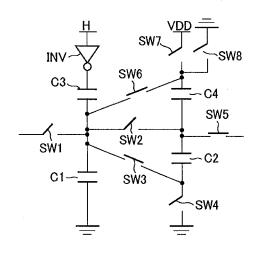

[0119] FIG. 5A is a diagram schematically showing a configuration example of the passive amplification circuit according to a second embodiment. This configuration solves the problem of an ON resistance as the second problem in addition to the first problem solved in the first embodiment, and also does not require the common mode reference voltage. The passive amplifier shown in FIG. 5A is used as the voltage holding circuit section VH of the analog-digital converter shown in FIG. 9.

[0120] The components of the passive amplification circuit shown in FIG. 5A will be described. The passive amplification circuit shown in FIG. 5A has the first capacitance C1 to the fourth capacitance C4, the first switch S1T to a tenth switch S10, a positive side input terminal Vin+, a negative side input terminal Vin-, a positive side output terminal Vo+ and a negative side output terminal Vo-, the power supply voltage Vdd and the ground voltage GND. Here, the positive side input terminal Vin+ and the negative side input terminal Vin- receive the positive side voltage and the negative side voltage of the input signal, respectively. The positive side output terminal Vo+ and the negative side output terminal Vooutput the positive side voltage and the negative side voltage of the output signal to the analog-digital converting circuit section ADC. The power supply voltage Vdd supplies a power supply voltage. The ground voltage GND supplies the ground voltage.

[0121] The connection relation of the respective components shown in FIG. 5A will be described. The positive side input terminal Vin+ is connected in common with one of the ends of the first switch S1, one of the ends of the second switch S2 and one of the ends of the third switch S3. The power supply voltage Vdd is connected with one of the ends of the seventh switch S7 and one of the ends of the ninth switch S9. The ground voltage GND is connected with one of the ends of the eighth switch S8 and one of the ends of the

tenth switch S10. One of the ends of the first capacitance C1 are connected with the other end of the first switch S1 and the other end of the seventh switch S7. One of the ends of the second capacitance C2 is connected with the other end of the second switch S2 and the other end of the eighth switch S8. The positive side output terminal Vo+ is connected in common with the other end of the third switch S3, one of the ends of the third capacitance C3 and one of the ends of the fourth capacitance C4. The negative side output terminal Vo- is connected in common with the other end of the first capacitance C1, the other end of the second capacitance C2 and one of the ends of the fourth switch S4. The other end of the third capacitance C3 is connected in common with one of the ends of the fifth switch S5 and the other end of the ninth switch S9. The other end of the fourth capacitance C4 is connected in common with one of the ends of the sixth switch C6 and the other end of the tenth switch S10. The negative side input terminal Vin- is connected in common with the other end of the fourth switch S4, the other end of the fifth switch S5 and the other end of the sixth switch S6.

[0122] The operation of the passive amplification circuit shown in FIG. 5A will be described. The first switch S1 to the sixth switch C6 are controlled so as to simultaneously carry out the switching between the block-off state and the conductive state all together as the first switch group. The seventh switch S7 to the tenth switch S10 are connected so as to simultaneously carry out the switching between the block-off state and the conductive state all together as the second switch group, while being independent from the first switch group.

[0123] The control of the first switch group and the second switch group is carried out in response to the first control signal and the second control signal generated by the control circuit (not shown).

[0124] FIG. 5B is a time chart showing an example of the control signal which controls each switch group shown in FIG. 5A. The time chart shown in FIG. 5B is the same as the time chart shown in FIG. 1B. Also, because the relation between each graph shown in FIG. 5B, the above two control signals, and the above two switch groups is same as the case of FIG. 1B. Therefore, further detailed description is omitted.

[0125] The passive amplification circuit shown in FIG. 5A carries out the sampling operation of the input signal received from the input terminal Vin in the range of time periods t0 to t1, t4 to t5, and t8 and the subsequent. At this time, the first capacitance C1 to the fourth capacitance C4 are connected in parallel between the positive side input terminal Vin+ and the negative side input terminal Vin-.

[0126] Here, in order to carry out the sampling operation of a high-speed input signal in high precision, it is general to use a boost switch. However, in order to generate the boosted voltage, it is required to dispose a sufficiently larger capacitance than a parasitic capacitance of a sampling switch in a boosting block. Therefore, the boost switch requires a large area cost. In the present embodiment, too, in order to carry out the sampling operation of a high-speed signal in a high precision, the boost switches have to be used as the first switch S1 to the sixth switch S6. However, the boosting block of the boost switch that has a same connection destination can be used in common. Therefore, an overhead of a larger area is not required, compared with a sampling block having no amplification mechanism.

[0127] Also, the passive amplification circuit shown in FIG. 5A carries out the amplifying operation in the range of the time periods t2 to t3 and t6 to t7. At this time, the power

supply voltage Vdd, the first capacitance C1, the negative side output terminal Vo-, the second capacitance C2 and the ground voltage GND are connected in serial in this order. Also, the power supply voltage Vdd, the third capacitance C3, the positive side output terminal Vo+, the fourth capacitance C4 and the ground voltage GND are connected in serial in this order.

[0128] At this time, the voltages of the positive side output terminal Vo+ and the negative side output terminal Vo- are the voltage obtained by amplifying an input differential signal.

[0129] Here, it is supposed that a capacitance value of each of the first capacitance C1 and the third capacitance C3 is an identical Ca and a capacitance value of each of the second capacitance C2 and the fourth capacitance C4 is an identical Cb. Moreover, calculating the electric charge quantities to have been charged in the first capacitance C1 to the fourth capacitance C4 in case of the sampling operation and the electric charge quantities charged in case of the amplifying operation, it is described from the conservation rule of a total electric charge quantity that the voltage at the output terminal Vo in the amplifying operation is 2 (±Vin+Vdd×Ca/(Ca+Cb)).

[0130] Therefore, in that the present embodiment, it is possible to design the common mode voltage of the output signal by appropriately selecting the capacitance values Ca and Cb, like the first embodiment. Thus, it is possible to have a function of the in-phase voltage shift circuit section V. Moreover, it is possible to design the voltage gain as the amplification circuit by connecting capacitance which does not have an amplification function in parallel to a set of the capacitances which have such an amplification function and by appropriately selecting the capacitance values of them.

[0131] Next, embodiments of the analog-digital converter will be described. The passive amplification circuit proposed in the first and second embodiments may be combined with these embodiments of the analog-digital converter.

[0132] The analog-digital converter according to the embodiments of the present invention will be described below with reference to the attached drawings.

## Third Embodiment

[0133] FIG. 6 is a functional block diagram showing a configuration of the analog-digital converter according to a third embodiment. The components of the analog-digital converter shown in FIG. 6 will be described.

[0134] The analog-digital converter shown in FIG. 6 contains an input buffer circuit section IB, a voltage holding circuit section VH, an analog-digital converting circuit section ADC and a digital correcting circuit section DC. The voltage holding circuit section VH contains a sampling circuit section S, a holding circuit section H and a passive amplification circuit section PA. Here, the sampling circuit section S, the holding circuit section H and the passive amplification circuit section PA cannot always separated clearly, and a part or all of the sections may be shared.

[0135] The connection relation of the components of the analog-digital converter shown in FIG. 6 will be described. The voltage holding circuit section VH is connected as the rear stage of the input buffer circuit section IB. The analog-digital converting circuit section ADC is connected as the rear stage of the voltage holding circuit section VH. The digital correcting circuit section DC is connected as the rear stage of the analog-digital converting circuit section ADC.

[0136] The operation of the components of the analogdigital converter shown in FIG. 6 will be described. The input buffer circuit section IB carries out a buffering operation of the input signal to drive a sampling capacitance of the voltage holding circuit section VH at a high speed and in a high precision. However, in the present embodiment, the input buffer circuit section IB is not an essential component and may be omitted. The voltage holding circuit section VH holds a voltage value of the input signal and a corresponding electric charge value effectively. More specifically, in the voltage holding circuit section VH, the sampling circuit section S carries out the sampling operation of the input signal, the holding circuit section H holds the voltage value of the sampled input signal and the corresponding electric charge value effectively, and the passive amplification circuit section PA carries out the passive amplification of the held input signal voltage. The analog-digital converting circuit section ADC carries out a digital change in an electric charge sharetype successive approximation type analog-digital conversion to convert the analog signal into a digital signal. The digital correcting circuit section DC corrects a warp of the digital signal which is brought about based on a deviation of capacitance values in the analog-digital converting circuit section ADC when a high-effective resolution is required.

[0137] FIG. 7 is a diagram schematically showing the configuration of the voltage holding circuit section VH and the analog-digital converting circuit section ADC according to a third embodiment. The components shown in FIG. 7 will be described. The voltage holding circuit section VH contains a positive phase side voltage holding circuit section VHa and a negative phase side voltage holding circuit section VHb.

[0138] The components of the positive phase side voltage holding circuit section VHa will be described. The positive phase side voltage holding circuit section VHa contains first and second positive phase side capacitances VHaC1 and VHaC2 and first to fifth positive phase side switches VHaSW1 to VHaSW5. The negative phase side voltage holding circuit section VHb contains first and second negative phase side capacitances VHbC1 and VHbC2 and first to fifth negative phase side switches VHbSW1 to VHbSW5.

**[0139]** The analog-digital converting circuit section ADC contains first to  $n^{th}$  bit comparison circuit sections BC1 to BCn, a comparator CMP and a control circuit section CNT. Here, "n" is an integer showing the number of digits of the digital value after the conversion.

[0140] The components of the first bit comparison circuit section B C1 will be described. The first bit comparison circuit section BC1 contains the capacitance BC1C and first to sixth switches BC1SW1 to BC1SW6. Note that the components of the first to n<sup>th</sup> bit comparison circuit sections are all same although the capacitance values of the capacitances BC1C to BCnC and the switch sizes for the bits are different. That is, when the first to n<sup>th</sup> bit digits is shown by "i", the capacitance value of the capacitance BCiC is an about half of that of the capacitance BC(i-1)C. Further detailed explanation of the bit comparison circuit section BCi for bits except the first bit is omitted.

[0141] The connection relation of the components of the voltage holding circuit section VH and the analog-digital converting circuit section ADC shown in FIG. 7 will be described.

[0142] At first, the connection relation of the components of the positive phase side voltage holding circuit section VHa will be described. An input section of the positive phase side

voltage holding circuit section VHa is connected in common with one of the ends of the first positive phase side switch VHaSW1 and one of the ends of the second positive phase side switch VHaSW2. The other end of the first positive phase side switch VHaSW1 is connected in common with one of the ends of the third positive phase side switch VHaSW3 and one of the ends of the first positive phase side capacitance VHaC1. The other end of the third positive phase side switch VHaSW3 is connected in common with one of the ends of the fourth positive phase side switch VHaSW4 and one of the ends of the second positive phase side capacitance VHaC2. The other end of the first positive phase side capacitance VHaC1 is grounded. The other end of the fourth positive phase side switch VHaSW4 is grounded. The other end of the second positive phase side switch VHaSW2 and the other end of the second positive phase side capacitance VHaC2 are connected in common with one of the ends of the fifth positive phase side switch VHaSW5. The other end of the fifth positive phase side switch VHaSW5 is connected with the output section of the positive phase side voltage holding circuit section VHa.

[0143] Because the connection relation of the components of the negative phase side voltage holding circuit section VHb are same as those of the positive phase side voltage holding circuit section VHa, further detailed description is omitted.

[0144] Next, the connection relation of the analog-digital converting circuit section ADC will be described. An output section of the positive phase side voltage holding circuit section VHa is connected in common with a non-inversion side input section in each of the first to the n<sup>th</sup> bit comparison circuit sections and a non-inversion side input section of the comparator CMP. An output section of the negative phase side voltage holding circuit section VHb is connected in common with an inversion side input section of each of first to n<sup>th</sup> bit comparison circuit sections and an inversion side input section of the comparator CMP is connected with the input section of the control circuit section CNT. An output section of the control circuit section CNT is connected with the output section of the analog-digital converting circuit section ADC.

[0145] The connection relation of the components of the first bit comparison circuit section BC1 will be described. One of the ends of the first switch BC1SW1 is connected with the power supply voltage VDD. One of the ends of the second switch BC1SW2 is grounded. One of the ends of each of the third switch BC1SW3 and the fourth switch BC1SW4 is connected with the output section of the positive phase side voltage holding circuit section VHa. One of the ends of each of the fifth switch BC1SW5 and the sixth switch BC1SW6 is connected with the output section of the negative phase side voltage holding circuit section VHb. The other end of each of the first switch BC1SW1, the third switch BC1SW3 and the fifth switch BC1SW5 is connected with one of the ends of the capacitance BC1C. The other end of each of the second switch BC1SW2, the fourth switch BC1SW4 and the sixth switch BC1SW6 is connected with the other end of the capacitance BC1C.

[0146] Because the connection relation of the components of the first to n<sup>th</sup> bit comparison circuit sections BC1 to BCn is same, further detailed description is omitted.

[0147] The operation of the analog-digital converter according to the third embodiment will be described. At first, the input buffer circuit section IB receives and buffers an analog signal. The input buffer circuit section IB outputs a

voltage corresponding to an analog value of the received analog signal for the voltage holding circuit section VH.

[0148] The operation of the voltage holding circuit section VH according to the third embodiment will be described. The voltage holding circuit section VH carries out the sampling operation of the analog input signal by the sampling circuit section S, the holding circuit section H carries out the holding operation of the sampled voltage and the passive amplification circuit section PA carries out the passive amplification of the held voltage. More specifically, the voltage holding circuit section VH carries out the sampling operation, the voltage holding and the passive amplification by alternately changing the first state shown in FIG. 8A and FIG. 8B and the second state shown in FIG. 8C and FIG. 8D.

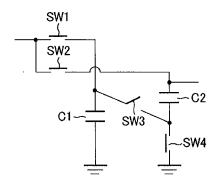

[0149] FIG. 8A is a diagram schematically showing a the first state in each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb according to the third embodiment. A circuit diagram shown in FIG. 8A contains the input section, the first capacitance C1, the second capacitance C2, the first to fourth switches SW1 to SW4 and the output section. Here, the input section and the output section shown in FIG. 8A correspond to the input section and the output section in each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb shown in FIG. 7, respectively. The first capacitance C1 shown in FIG. 8A and the second capacitance C2 correspond to the first positive phase side capacitance VHaC1 shown in FIG. 7, the first negative phase side capacitance VHbC1, the second positive phase side capacitance VHaC2 of the and the negative phase side capacitance VHbC2 of the second respectively. The first to fourth switches SW1 to SW4 shown in FIG. 8A corresponds to the first to fourth positive phase side switches VHaSW1 to VHaSW4 shown in FIG. 7 and the first to the fourth negative phase side switches VHbSW1 to VHbSW4, respectively.

[0150] In the first state schematically shown in FIG. 8A, the first switch SW1, the second switch SW2 and the fourth switch SW4 are in the conductive state, and the third switch SW3 is in the block-off state. At this time, note that it is desirable that the fifth positive phase side switch VHaSW5 and the fifth negative phase side switch VHbSW5 shown in FIG. 7 are in the block-off state.

[0151] FIG. 8B is an equivalent circuit diagram corresponding to the first state in each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb according to the third embodiment. The equivalent circuit diagram shown in FIG. 8B contains the input section, the first capacitance C1 and the second capacitance C2. In this case, like the case shown in FIG. 8A, the input section, the first capacitance C1 and the second capacitance C2 shown in FIG. 8B correspond to the input section of each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb, the first positive phase side capacitance VHaC1 and the first negative phase side capacitance VHbC1, and the first positive phase side capacitance VHaC2 and the second negative phase side capacitance VHbC2, respectively. It should be noted that because the fifth positive phase side switch VHaSW5 and the fifth negative phase side switch VHbSW5 of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb are in the block-off state in the first state, the output section is omitted in FIG. 8B.

[0152] In the first state shown in FIG. 8A and FIG. 8B, in the two of the capacitances C1 and C2, one of the ends is connected with the input section and the other end is grounded. In other words, at the first state shown in FIG. 8A and FIG. 8B, the two capacitances C1 and C2 are connected in parallel between the input section and the ground voltage. [0153] FIG. 8C is a diagram schematically showing the second state in each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb according to the third embodiment. The circuit diagram schematically shown in FIG. 8C contains the first capacitance C1, the second capacitance C2 and the first to the fourth switches SW1 to SW4. In this case, the first capacitance C1 and the second capacitance C2 shown in FIG. 8C correspond to the first positive phase side capacitance VHaC1 and the first negative phase side capacitance VHbC1, and the second positive phase side capacitance VHaC2 and the second negative phase side capacitance VHbC2 shown in FIG. 7, respectively. The first to fourth switches SW1 to SW4 shown in FIG. 8C correspond to the first to fourth positive phase side switches VHaSW1 to VHaSW4, and the first to fourth negative phase side switches VHbSW1 to VHbSW4, shown in FIG. 7, respectively.

[0154] In the first state schematically shown in FIG. 8C, the first switch SW1, the second switch SW2 and the fourth switch SW4 are in the block-off state, and the third switch SW3 is in the conductive state. It should be noted that the fifth positive phase side switch VHaSW5 and the fifth negative phase side switch VHbSW5 shown in FIG. 7 are set to the conductive state at the time of the analog-digital conversion processing.

[0155] FIG. 8D is an equivalent circuit diagram corresponding to the second state in each of the positive phase side voltage holding circuit section VHa and the negative phase side voltage holding circuit section VHb according to the third embodiment. The equivalent circuit diagram shown in FIG. 8D contains the first capacitance C1 and the second capacitance C2. In this case, like the case of FIG. 8C, the first capacitance C1 and the second capacitance C2 correspond to the first positive phase side capacitance VHaC1 and the first negative phase side capacitance VHbC1, and the second negative phase side capacitance VHbC2 and the second positive phase side capacitance VHaC2, respectively.

[0156] In the second state shown in FIG. 8C and FIG. 8D, one of the ends of the first capacitance C1 is grounded, and the other end of the first capacitance C1 is connected with one of the ends of the second capacitance C2. The other end of the second capacitance C2 is connected with the output section. In other words, in the second state shown in FIG. 8C and FIG. 8D, the two of the capacitances C1 and C2 are connected in serial between the output section and the ground voltage.

[0157] In this case, the passive amplification in a case where the capacitance values of the first and second capacitances C1 and C2 are equal to each other, the power supply voltage VDD is 1.2 V and the voltage of the input signal changes in a range of 0 to 0.6 V will be described as an example.

[0158] At first, in the first state, the first capacitance C1 and the second capacitance C2 are charged in parallel when the voltage of an analog signal outputted from the input buffer circuit section IB shown in FIG. 6 is applied. At this time, the first capacitance C1 and the second capacitance C2 which are connected in parallel are charged with the sampling voltage which is contained in the range of 0 to 0.6 V.

[0159] Next, in the second state, the first switch SW1 and the second switch SW2 are blocked off or isolated from each other, to finish the charging operation of the first capacitance C1 and the second capacitance C2, i.e. to complete the sampling operation. Also, the states of the third switch SW3 and the fourth switch SW4 are switched so that the connection relation of the first capacitance C1 and the second capacitance C2 is switched from the serial connection to the parallel connection. At this time, the voltage between both ends of the first and second capacitances C1 and C2 serially-connected is fallen in the range of 0 to 1.2 V, i.e. the passive amplification has been carried out. Moreover, the state of the fifth switch SW5 is switched, and the voltage after the passive amplification is effectively held and is applied to the analog-digital converting circuit section of the rear stage.

[0160] In this way, before analog-digital change operation, in the voltage amplitude of vibration of the input signal, by being amplified beforehand, the input change value of the noise which the comparator CMP generates can be reduced by half by twice. As a result, the effective resolution increases in the degree for 1 bit, i.e. the precision of the analog-digital change becomes by twice. Because the passive amplification can be realized only by the nexus exchange by the capacitance, it isn't accompanied by the increase of the consumption electric current and the chip size.

[0161] It should be noted that a ratio of the passive amplification is determined based on a ratio of the capacitance values of the first and second capacitances C1 and C2. As mentioned above, if the two capacitance values are equal to each other, the ratio of the passive amplification is about twice. It is possible to change the ratio of the passive amplification freely by suitability controlling the ratio of the two capacitance values.

[0162] The analog-digital converting circuit section ADC according to the present embodiment shown in FIG. 7 operates in the same way as a general electric charge share-type successive approximation type analog-digital converting circuit. At this time, when the comparator CMP compares the voltage between its ends of the capacitance in the successive approximation from the MSB corresponding to the first bit comparison circuit section BC1 to the LSB corresponding to the n<sup>th</sup> bit comparison circuit section BCn, the control circuit section CNT suitability switches each switch between the conductive state and the block-off state.

[0163] In the third embodiment, the capacitance value of the first capacitance C1 is the same as that of the second capacitance C2. Therefore, the voltage obtained after the passive amplification is about twice of the voltage before the passive amplification. By amplifying the voltage showing an analog value twice before the analog-digital conversion by the analog-digital converting circuit section ADC, a input conversion value of noise which is generated through the comparing operation by the comparator CMP can be suppressed to a half. As a result, because the precision of the analog-digital conversion becomes twice, the effective resolution increases by about 1 bit.

[0164] Also, because the passive amplification can be realized only by switching the connection of the capacitances, it does not require the increase of the consumption power and the chip size. It should be noted that the control of the switch group whose states are switched in the passive amplification may be carried out by the control circuit section CNT which is contained in the analog-digital converting circuit section ADC and another control circuit section which is not shown.

#### Fourth Embodiment

[0165] FIG. 9 is a functional block diagram showing the configuration of the analog-digital converter according to the fourth embodiment. The analog-digital converter in the present embodiment shown in FIG. 9 is the same as a circuit obtained by adding the in-phase voltage shift circuit section VS to the analog-digital converter according to the third embodiment shown in FIG. 6. Here, the in-phase voltage shift circuit section VS in the present embodiment is contained in the voltage holding circuit section VH. Because the other configuration of the analog-digital converter in the present embodiment shown in FIG. 9 is the same as that of the third embodiment shown in FIG. 6, further detailed description is omitted.

[0166] FIG. 10 is a diagram schematically showing the configuration of the voltage holding circuit section VH and the analog-digital converting circuit section ADC according to the fourth embodiment. The voltage holding circuit section VH in the present embodiment shown in FIG. 9 is the same as a circuit obtained by adding the following changes to the voltage holding circuit section VH of the third embodiment shown in FIG. 7.

[0167] That is, the positive phase side voltage holding circuit section VHa of the voltage holding circuit section VH in the present embodiment is obtained by adding the positive phase side inverter VHaI, a third positive phase side capacitance VHaC3, a fourth positive phase side capacitance VHaC4, and the sixth to the eighth positive phase side switches VHaSW6 to VHaSW8 to the positive phase side voltage holding circuit section VHa in the third embodiment shown in FIG. 7.

[0168] Here, the input section of the positive phase side inverter VHaI is connected with a control signal generating section (not shown). The output section of the positive phase side inverter VHaI is connected with one of the ends of the third positive phase side capacitance VHaC3. The other end of the third positive phase side capacitance VHaC3 and one of the ends of the sixth positive phase side switch VHaSW6 are connected in common with one of the ends of the first positive phase side capacitance VHaC1, the other end of the first positive phase side switch VHaSW1 and one of the ends of the third positive phase side switch VHaSW3. One of the ends of the seventh positive phase side switch VHaSW7 is connected with the power supply voltage VDD. One of the ends of the eighth positive phase side switch VHaSW8 is grounded. The other end of the sixth positive phase side switch VHaSW6, the other end of the seventh positive phase side switch VHaSW7 and the other end of the eighth positive phase side switch VHaSW8 are connected in common with one of the ends of the fourth positive phase side capacitance VHaC4. The other end of the fourth positive phase side capacitance VHaC4 is connected in common with one of the ends of the second positive phase side capacitance VHaC2, the other end of the second positive phase side switch VHaSW2 and one of the ends of the fifth positive phase side switch VHaSW5.

[0169] Also, the negative phase side voltage holding circuit section VHb of the voltage holding circuit section VH in the present embodiment is obtained by adding the negative phase side inverter VHbI, the third negative phase side capacitance VHbC3, the fourth negative phase side capacitance VHbC4, and the sixth to eighth negative phase side switches VHbSW6 to VHbSW8 to the negative phase side voltage holding circuit section VHb in the third embodiment shown in FIG. 7.

[0170] Here, the input section of the negative phase side inverter VHbI is connected with the control signal generating section (not shown). The output section of the negative phase side inverter VHbI is connected with one of the ends of the third negative phase side capacitance VHbC3. The other end of the third negative phase side capacitance VHbC3 and one of the ends of the sixth negative phase side switch VHbSW6 are connected in common with one of the ends of the first negative phase side capacitance VHbC1, the other end of the first negative phase side switch VHbSW1 and one of the ends of the third negative phase side switch VHbSW3. One of the ends of the seventh negative phase side switch VHbSW7 is connected with the power supply voltage VDD. One of the ends of the eighth negative phase side switch VHbSW8 is grounded. The other end of the sixth negative phase side switch VHbSW6, the other end of the seventh negative phase side switch VHbSW7 and the other end of the eighth negative phase side switch VHbSW8 are connected in common with one of the ends of the fourth negative phase side capacitance VHbC4. The other end of the fourth negative phase side capacitance VHbC4 is connected in common with one of the ends of the second negative phase side capacitance VHbC2, the other end of the second negative phase side switch VHbSW2 and one of the ends of the fifth negative phase side switch VHbSW5.

[0171] It should be noted that because the other configuration of the voltage holding circuit section VH in the present embodiment is the same as that of the third embodiment shown in FIG. 7, further detailed description is omitted.

[0172] It will be described that the voltage holding circuit section VH in the present embodiment has a function as the in-phase voltage shift circuit section VS by adding the above changes.