ELECTRODE SURFACE-COATED BY POLYMER FILM, METHOD FOR PRODUCING SAME, AND SECONDARY BATTERY COMPRISING SAME

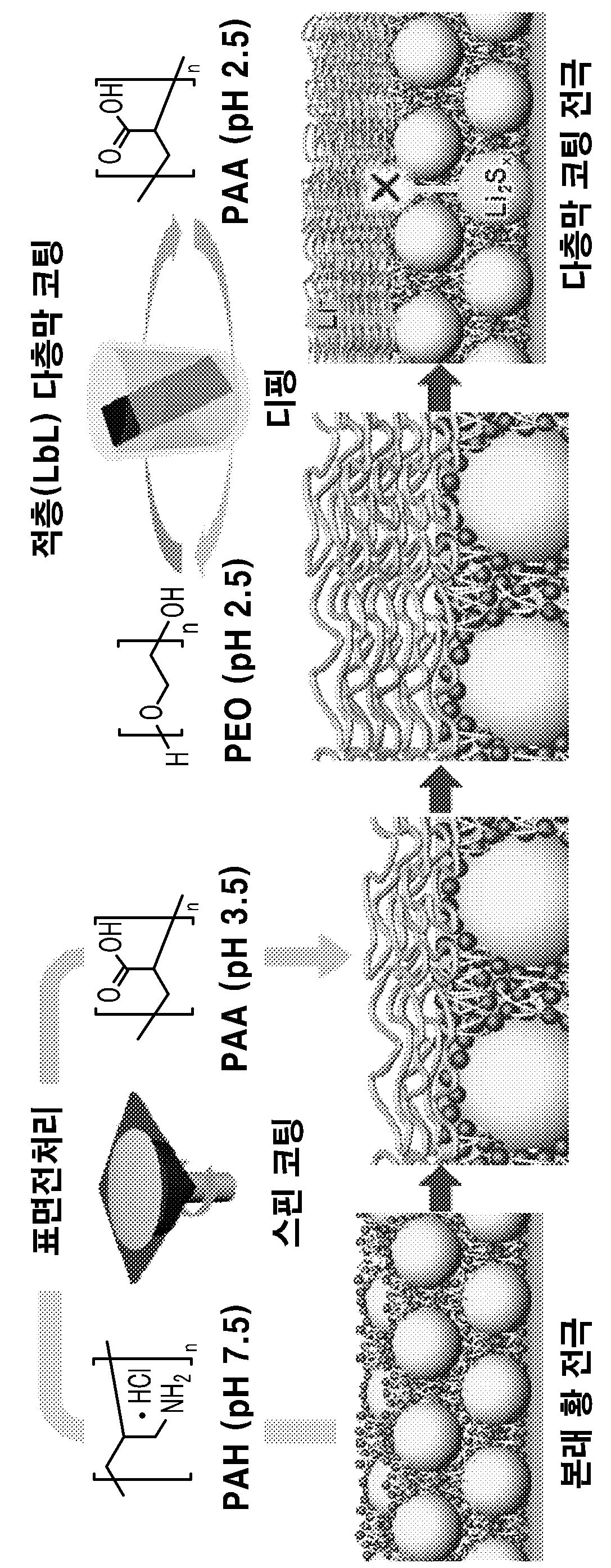

본원은, 고분자 막에 의하여 표면-코팅된 전극, 상기 고분자 막에 의하여 표면-코팅된 전극의 제조 방법, 및 상기 고분자 막에 의하여 표면-코팅된 전극을 포함하는 이차 전지에 관한 것이다. 리튬-황(Li-S) 전지는 황 캐소드(cathode)의 높은 이론적 비정전용량(specific capacity)으로 인하여(1,675 mAhg-1) 차세대 에너지 저장 시스템을 위한 가장 유망한 후보 중 하나로서 간주된다. 그러나, 반복되는 충전/방전 사이클 동안 상기 캐소드에서 활성 황 종의 비가역적 용출로 인하여 이것의 이론적 용량을 달성하는 것은 여전히 벅찬 과제로서 간주된다. 고차 충전/방전 생성물인, Sn2-(n = 4, 6, 및 8)인 폴리설파이드는, 전해질 매질 내에서 잘 용해되며, 따라서 그들은 전지 동작 동안 상기 캐소드로부터 계속적으로 용출된다. 상기 전해질에서 전기적으로 단리된 상기 폴리설파이드는 Li 애노드(anode) 상으로 이동하며, Li 금속의 표면 상에 비활성 침적물(inactive deposits)을 형성하고, 이것은 용량의 심각한 손실 및 불량한 쿨롱 효율(coulombic efficiency)을 야기한다. 이러한 중요한 문제들을 해결하기 위해, 상당한 노력들이 활성 황 종의 모폴로지 또는 분자 구조를 설계하는 것에 특별히 집중되었다. 이러한 개선들은 탄소질 물질에 의해 포집된 나노-사이즈의 황의 사용에 의해 이루어지며, 여기서 폴리설파이드는 밀접한 전기적 컨택을 가지며 캐소드 측 부근 내에 보존된다. 최근, 원소 황(S8, octasulfur)의 공중합 물질로의 화학적 개질이 보고되었으며, 여기서 유기 공단량체(comonomer)는 리튬화된 황 생성물과 탈리튬화된 황 생성물 사이의 중간상(interphase)을 안정화하는 분자 바인더로서 작용한다. 황 캐소드의 거시적인 관점으로부터, 상기 용해된 폴리설파이드는 상기 캐소드와 세퍼레이터(separator) 사이에 중간층을 추가함으로써, 벌크 캐소드 부분 내에 남아 있을 수 있다. 주로, 탄소질 물질 또는 고분자 전해질의 층은 황 캐소드에 대향하여 추가적인 층으로서 세퍼레이터 상에 증착된다. 상기 폴리설파이드의 비가역적인 손실을 최소화하기 위해, 상기 황 캐소드 및 상기 중간층 사이의 컨포멀 컨택이 선호되고, 따라서 상기 캐소드 표면 상에 중합 층의 직접 코팅 전략이 또한 최근에 도입되었다. 그러나, 상기 황 캐소드 상의 컨포멀 코팅 층은, 전해질과 캐소드 표면 사이에서 리튬 이온의 확산을 지연시킬 수 있어, Li-S 전지의 증가된 저항을 야기한다. 또한, 더 두꺼워진 중합 층 코팅은 Li-S 전지의 비활성 질량을 증가시켜, 황 로딩의 주어진 양에서 상기 전지의 비에너지(specific energy)를 감소시킨다. 따라서 전체 전지 성능을 최적화하기 위한 상기 코팅 층 두께의 정확한 제어가 요구되며, 이는 상세히 연구된 적이 거의 없다. 한편, 다중층막(layer-by-layer, LbL) 증착은 다양한 기재 상에 컨포멀 코팅 층을 형성하는 효과적인 기술로서 알려졌다. 다중층막 증착을 위한 기능성 물질의 많은 옵션들이 존재하며, 상기 코팅 층의 두께는, LbL 증착 단계로부터 다중층의 수에 의하여, 나노미터(nm) 스케일로 쉽게 조정된다. 폴리에틸렌 옥사이드(PEO)는 이온 전도성 멤브레인을 위한 수소-결합된 PEO/PAA 다중층막을 형성하기 위해 폴리아크릴산(PAA)와 조합되어 흔히 사용되며, 폴리알릴아민 하이드로클로라이드(PAH) 또는 폴리에틸렌이민(PEI)과 같은 양이온성 고분자 전해질을 이용하는 정전 다중층막과 비교하여 우수한 리튬 이온 확산 특성을 나타낸다. 그러나, 이러한 고분자의 LbL 증착은 황 캐소드 상의 보호 코팅 층을 위해 이용되지 않고 있으며, 이는 최근 연구에서 노력 중이다. 대한민국 공개특허 제2012-0074646호는, 리튬 설퍼 전지용 세퍼레이터와 이의 제조 방법에 대해 개시하고 있다. 본원은, 고분자 막에 의하여 표면-코팅된 전극, 상기 고분자 막에 의하여 표면-코팅된 전극의 제조 방법, 및 상기 고분자 막에 의하여 표면-코팅된 전극을 포함하는 이차 전지를 제공하고자 한다. 그러나, 본원이 해결하고자 하는 과제는 이상에서 언급한 과제로 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다. 본원의 제 1 측면은, 전극 상에 형성된 프라이밍 층(priming layer); 및 상기 프라이밍 층 상에 형성되며, 제 1 고분자 층 및 제 2 고분자 층이 순차적으로 적층된 고분자 다중층을 포함하는, 고분자 막에 의하여 표면-코팅된 전극을 제공한다. 본원의 제 2 측면은, 전극 상에 프라이밍 층을 형성하는 단계; 및 상기 프라이밍 층 상에 제 1 고분자 층과 제 2 고분자 층을 순차적으로 적층하여 고분자 다중층을 형성하는 단계를 포함하는, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법을 제공한다. 본원의 제 3 측면은, 본원의 제 1 측면에 따른 고분자 막에 의하여 표면-코팅된 전극을 포함하는, 이차 전지를 제공한다. 본원의 일 구현예에 따르면, 전극 상에 프라이밍 층을 형성한 후, 제 1 고분자 층 및 제 2 고분자 층을 다중층막 증착에 의하여 순차적으로 적층하여 고분자 다중층을 형성함으로써, 고분자 막에 의하여 표면-코팅된 전극을 제조할 수 있다. 본원의 일 구현예에 따른 상기 표면-코팅된 전극은, 나노미터 규모의 두께 제어가 가능하며, 고분자 다중층의 제 1 고분자와 제 2 고분자 사이의 정전기적 결합(예: 폴리아릴아민 하이드로클로라이드와 폴리아크릴산) 또는 수소결합(예: 폴리에틸렌옥사이드와 폴리아크릴산)을 이용하여 적층하기 때문에, 형성된 고분자 막 내부의 양이온 및 음이온의 이동이 용이하여 전기화학적 디바이스의 다양한 용도로 사용될 수 있다. 또한, 본원의 일 구현예에 따른 상기 표면-코팅된 전극은, 리튬 이온 확산을 용이하게 하는 한편, 황의 확산을 물리적 또는 정전기적으로 배척함으로써 전극 내부의 활물질 감소 및 전극 표면에서의 비가역적인 석출을 제한할 수 있다. 따라서, 이차 전지에 적용 시 리튬-황 이차 전지의 충전/방전 용량 감소 문제를 해결하고, 전지의 수명 및 전지의 전반적인 성능을 향상시킬 수 있다는 효과를 갖는다. 도 1은, 본원의 일 구현예에 있어서, 프라이밍 층의 증착 및 황 캐소드 상의 (PEO/PAA) 다중층막을 나타내는 개략도이다. 도 2a는, 본원의 일 실시예에 있어서, 황, 탄소+바인더, 및 황+탄소+바인더(즉, 황 캐소드)의 기재 상에서 흡착된 고분자 층의 함수로서의 접촉 각 변화를 나타낸 그래프이다. 도 2b의 (a) 내지 (f)는, 본원의 일 실시예에 있어서, 본래 황 캐소드의 SEM 이미지 및 본래 황 캐소드 상의 물 액적의 광학 이미지(a), 5 회 다중층-코팅된 캐소드의 SEM 이미지 및 5 회 다중층-코팅된 캐소드 상의 물 액적의 광학 이미지(b), 5 회 다중층-코팅된 캐소드의 단면 SEM 이미지(c), 본래 황 캐소드의 고 배율 단면 SEM 이미지(d), 5 회 다중층-코팅된 캐소드의 고 배율 단면 SEM 이미지(e), 및 도 2b의 (d)에서 5 회 다중층-코팅된 캐소드의 단면 SEM 이미지에서 수득된 산소(주황색)의 EDS 원소 맵을 나타낸 이미지(f)이다. 도 3은, 본원의 일 실시예에 있어서, Si 웨이퍼 기재 상에서 PAH/PAA/(PEO/PAA)n 다중층의 LbL 증착 동안 다중층 수의 함수로서의 다중층 두께 성장을 나타낸 그래프이다. 도 4의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 탄소+바인더 기재(a), 5 회 다중층-코팅된 탄소+바인더 기재(b), 순수(bare) 황 기재(c), 및 5 회 다중층-코팅된 황 기재(d)의 SEM 이미지이다. 도 5는, 본원의 일 실시예에 있어서, 황, 탄소+바인더, 및 상기 캐소드 기재 상에서 흡착된 고분자 층의 함수로서 접촉각에서의 점진적인 감소를 나타내는 물 접촉각 측정의 광학 이미지이다. 도 6은, 본원의 일 실시예에 있어서, (PAH/PAA)의 프라이밍 층과, 또는 이것 없이, (PEO/PAA)n, n=1, 3, 및 5 회 증착 동안 형태학적 변화를 나타내는 황 캐소드의 이미지이다. 도 7의 (a) 및 (b)는, 본원의 일 실시예에 있어서, 본래 황 캐소드 및 (PEO/PAA) 5 회 다중층-코팅된 황 캐소드의 XPS 스펙트럼이다. 도 8은, 본원의 일 실시예에 있어서, 본래 황 캐소드 및 (PEO/PAA) 5 회 다중층-코팅된 황 캐소드에 대한 원소 맵 및 EDS 스펙트럼이다. 도 9의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 초기 10 사이클 동안 0.5 C에서의 충전/방전 전압 프로파일로서, 본래 황 캐소드(a), 1 회 다중층-코팅된 황 캐소드(b), 3 회 다중층-코팅된 황 캐소드(c), 및 5 회 다중층-코팅된 황 캐소드(d)를 나타낸 것이며, 도 9의 (e) 및 (f)는, 본원의 일 실시예에 있어서, 본래 황 캐소드와 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 0.5 C 에서의 사이클링 성능(e), 및 본래 황 캐소드와 (PEO/PAA) 1, 3, 및 5 회 다중층-코팅된 황 캐소드들의 C-속도 특성을 나타낸 그래프(f)이다. 도 10은, 본원의 일 실시예에 있어서, (PAH/PAA) 1, 4, 6 회 다중층-코팅된 황 캐소드와 비교하여, 본래 황 캐소드 및 (PEO/PAA) 1, 4, 및 6 회 다중층-코팅된 황 캐소드의 0.1 C에서의 사이클 성능을 나타낸 그래프이다. 도 11의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 본래 황 캐소드(a), 1 회 다중층-코팅된 캐소드(b), 3 회 다중층-코팅된 캐소드(c), 및 5 회 다중층-코팅된 캐소드(d)의 10 사이클 이후, 분해된 Li 애노드의 광학 이미지이다. 도 12는, 본원의 일 실시예에 있어서, 1.5 V에서의 정전압을 본래 황 전극 및 5 회 다중층-코팅된 캐소드와 조립된 비커 전지(beaker cells)로 인가한 후, 5 분에서의 전해질 용액의 UV-Vis 스펙트럼 및 광학 이미지를 나타낸 것이다. 도 13은, 본원의 일 실시예에 있어서, 사이클 이전에 측정된 본래 황 전극 및 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 전기화학적 임피던스 분광 분석(EIS) 데이터이다. 도 14의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 처음 1 사이클 및 10 사이클 이후 측정된 본래 황 전극(a) 및 1(b), 3(c), 및 5 회(d) 다중층-코팅된 황 캐소드의 EIS 데이터이다. 도 15는, 본원의 일 실시예에 있어서, 전해질 중 LiNO3 없이 본래 황 전극 및 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 0.5 C에서의 사이클 성능 및 쿨롱 효율(쿨롱 효율=충전/방전 용량)을 나타낸 그래프이다. 도 16의 (a) 및 (b)는, 본원의 일 실시예에 있어서, 10 사이클 이후 본래 황 캐소드(a) 및 5 회 다중층-코팅된 황 캐소드(b)의 SEM 이미지이다. 아래에서는 첨부한 도면을 참조하여 본원이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 본원의 실시예를 상세히 설명한다. 그러나 본원은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다. 그리고 도면에서 본원을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략하였으며, 명세서 전체를 통하여 유사한 부분에 대해서는 유사한 도면 부호를 붙였다. 본원 명세서 전체에서, 어떤 부분이 다른 부분과 “연결”되어 있다고 할 때, 이는 “직접적으로 연결”되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 “전기적으로 연결”되어 있는 경우도 포함한다. 본원 명세서 전체에서, 어떤 부재가 다른 부재 “상에” 위치하고 있다고 할 때, 이는 어떤 부재가 다른 부재에 접해 있는 경우뿐 아니라 두 부재 사이에 또 다른 부재가 존재하는 경우도 포함한다. 본원 명세서 전체에서, 어떤 부분이 어떤 구성 요소를 “포함” 한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성 요소를 제외하는 것이 아니라 다른 구성 요소를 더 포함할 수 있는 것을 의미한다. 본원 명세서 전체에서 사용되는 정도의 용어 “약”, “실질적으로” 등은 언급된 의미에 고유한 제조 및 물질 허용오차가 제시될 때 그 수치에서 또는 그 수치에 근접한 의미로 사용되고, 본원의 이해를 돕기 위해 정확하거나 절대적인 수치가 언급된 개시 내용을 비양심적인 침해자가 부당하게 이용하는 것을 방지하기 위해 사용된다. 본원 명세서 전체에서 사용되는 정도의 용어 “~(하는) 단계” 또는 “~의 단계”는 “~ 를 위한 단계”를 의미하지 않는다. 본원 명세서 전체에서, 마쿠시 형식의 표현에 포함된 “이들의 조합(들)”의 용어는 마쿠시 형식의 표현에 기재된 구성 요소들로 이루어진 군에서 선택되는 하나 이상의 혼합 또는 조합을 의미하는 것으로서, 상기 구성 요소들로 이루어진 군에서 선택되는 하나 이상을 포함하는 것을 의미한다. 본원 명세서 전체에서, “A 및/또는 B”의 기재는 “A 또는 B, 또는 A 및 B”를 의미한다. 본원 명세서 전체에서, "그래핀(graphene)"이라는 용어는 복수개의 탄소 원자들이 서로 공유 결합으로 연결되어 폴리시클릭 방향족 분자를 형성한 것을 의미하는 것으로서, 상기 공유 결합으로 연결된 탄소 원자들은 기본 반복 단위로서 6 원환을 형성하나, 5 원환 및/또는 7 원환을 더 포함하는 것도 가능하다. 따라서, 상기 그래핀이 형성하는 시트는 서로 공유 결합된 탄소 원자들의 단일층으로서 보일 수 있으나, 이에 제한되는 것은 아니다. 상기 그래핀이 형성하는 시트는 다양한 구조를 가질 수 있으며, 이와 같은 구조는 그래핀 내에 포함될 수 있는 5 원환 및/또는 7 원환의 함량에 따라 달라질 수 있다. 또한, 상기 그래핀이 형성하는 시트가 단일층으로 이루어진 경우, 이들이 서로 적층되어 복수층을 형성할 수 있으며, 상기 그래핀 시트의 측면 말단부는 수소 원자로 포화될 수 있으나, 이에 제한되는 것은 아니다. 본원 명세서 전체에서, "그래핀 옥사이드(graphene oxide)"이라는 용어는 그래핀 산화물이라고도 불리우고, "GO"로 약칭될 수 있다. 단일층 그래핀 상에 카르복실기, 히드록시기, 또는 에폭시기 등의 산소를 함유하는 작용기가 결합된 구조를 포함할 수 있으나, 이에 제한되는 것은 아니다. 본원 명세서 전체에서, "환원된 그래핀 산화물" 또는 "환원 그래핀 옥사이드(reduced graphene oxide)"이라는 용어는 환원 과정을 거쳐 산소 비율이 줄어든 그래핀 산화물을 의미하는 것으로서, "rGO"로 약칭될 수 있으나, 이에 제한되는 것은 아니다. 이하, 첨부된 도면을 참조하여 본원의 구현예 및 실시예를 상세히 설명한다. 그러나, 본원이 이러한 구현예 및 실시예와 도면에 제한되지 않을 수 있다. 본원의 제 1 측면은, 전극 상에 형성된 프라이밍 층(priming layer); 및 상기 프라이밍 층 상에 형성되며, 제 1 고분자 층 및 제 2 고분자 층이 순차적으로 적층된 고분자 다중층을 포함하는, 고분자 막에 의하여 표면-코팅된 전극을 제공한다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은, 폴리에틸렌 옥사이드(PEO), 폴리아릴아민 하이드로클로라이드(PAH), 폴리에틸렌이민(PEI), 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것이고, 상기 제 2 고분자 층은, 폴리아크릴산, 폴리메타크릴산, 폴리비닐 알코올, 그래핀 옥사이드, 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층은, 폴리아릴아민 하이드로클로라이드, 폴리아크릴산, 폴리에틸렌이민, 폴리메타크릴산, 및 이들의 조합들로 이루어진 군으로부터 선택되는 하나 이상의 고분자를 포함하는 것일 수 있으며, 상기 제 1 고분자 층 및 상기 제 2 고분자 층을 이루는 고분자와 동일하거나 또는 상이할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층을 이루는 고분자는, 상기 제 2 고분자 층을 이루는 고분자를 포함하는 것일 수 있다. 상기 프라이밍 층의 형성 목적은 상기 고분자 다중층의 제 1 고분자 층이 잘 형성되도록 하기 위한 것이다. 따라서, 상기 제 1 고분자와 상기 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 서로 잘 결합될 수 있기 때문에, 상기 프라이밍 층을 이루는 고분자는 프라이밍 층 상에 형성될 제 1 고분자와 잘 결합되는 성질을 가지는 제 2 고분자를 포함하는 것일 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층 상에 형성될 상기 제 1 고분자와 잘 결합되는 성질을 가지는 고분자를 프라이밍 층으로서 이용할 경우, 하나의 고분자만으로도 프라이밍 층을 구성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 및 상기 제 2 고분자는 서로 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이룰 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 제 1 고분자 및 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이루며, 상기 고분자 상이 상기 프라이밍 층 상에 교대로 적층되어 고분자 다중층을 형성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은 상기 프라이밍 층에 용이하게 결합되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 프라이밍 층에 의하여 상기 제 1 고분자가 상기 전극 상의 프라이밍 층에 균일하게 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층에 의하여 상기 전극의 표면이 균일하게 커버되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층은 스핀-코팅에 의하여 상기 전극 상에 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 스핀-코팅에 의하여 코팅된 상기 프라이밍 층은 침지법(dipping method)에 의하여 코팅된 것보다 더 얇고 균일한 표면을 생성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 전극은 황 전극일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층 및 상기 제 2 고분자 층은 침지법에 의하여 상기 황 전극 상에 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 다중층막 증착(layer-by-layer deposition, LbL)법에 의하여 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 다중층막 증착법에 의하여 상기 고분자 다중층이 나노미터 규모로 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층의 두께에 따라 상기 폴리설파이드의 음이온의 용출 및 리튬 이온의 이동 속도가 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 다중층의 두께가 두꺼워질수록 상기 폴리설파이드 음이온의 용출이 방지되는 한편, 리튬 이온의 이동속도가 감소하여 전하 용량이 감소될 수 있으므로, 상기 다중층막 증착법을 통하여 상기 고분자 다중층의 두께를 조절할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 전해질로의 용출을 방지하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 비가역적인 석출을 방지할 수 있으나, 이에 제한되지 않을 수 있다. 황 전극의 작동 시, 폴리설파이드 음이온의 용출 및 비가역적인 석출은, 반복된 사이클 동안 탄소 골격과 황 생성물 사이의 전기적 컨택의 점진적 분해를 야기하며, 활성 황의 이용을 제한되도록 만든다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 용출 및 비가역적인 석출을 방지함으로써, 상기 황 전극의 캐소드 활물질의 급격한 감소를 방지할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 전극은 리튬염을 추가 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 리튬염은 LiTFSI, LiNO3, LiBOB, LiCl, LiClO4, 및 이들의 조합들로 이루어진 군으로부터 선택되는 것을 하나 이상 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 구체적으로 상기 리튬염은 리튬-황 이차 전지 구동 시 우수한 성능을 보이는 LiTFSI 및 LiNO3의 조합을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 리튬염에 의하여 상기 프라이밍 층 및 상기 제 1 고분자 층과 상기 제 2 고분자 층 사이의 결합이 유도되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 막에 의하여 표면-코팅된 전극 제조 시, 상기 리튬염의 추가로 인하여 상기 제 1 고분자 및 제 2 고분자를 포함하는 용액의 이온 강도(ionic strength)가 증가되어, 상기 제 1 고분자 및 상기 제 2 고분자의 효과적인 흡착 또는 흡착된 상기 제 1 고분자 및 제 2 고분자가 다시 상기 용액에 녹아나가는 것을 방지할 수 있으나, 이에 제한되지 않을 수 있다. 전극 제조 시 사용되는 염은 리튬염 외에 어떠한 물질이라도 사용될 수 있지만, 이차 전지를 제조하기 위한 목적으로는 전해질에 포함되는 리튬염을 사용하는 것이 바람직하다. 본원의 일 구현예에 있어서, 상기 리튬염의 농도는 약 0.05 M 이상인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 리튬염은 약 0.05 M 이상, 약 0.05 M 내지 약 0.5 M, 약 0.05 M 내지 약 0.4 M, 약 0.05 M 내지 약 0.2 M, 약 0.05 M 내지 약 0.1 M, 약 0.1 M 내지 약 0.5 M, 약 0.1 M 내지 약 0.4 M, 약 0.1 M 내지 약 0.2 M, 약 0.2 M 내지 약 0.5 M, 또는 약 0.2 M 내지 약 0.4 M의 농도로 추가되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 막에 의하여 표면-코팅된 전극은, 이차 전지용 전극으로서 사용되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 이차 전지는 리튬-황 이차 전지일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 제 2 측면은, 전극 상에 프라이밍 층을 형성하는 단계; 및 상기 프라이밍 층 상에 제 1 고분자 층과 제 2 고분자 층을 순차적으로 적층하여 고분자 다중층을 형성하는 단계를 포함하는, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법을 제공한다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은, 폴리에틸렌 옥사이드, 폴리아릴아민 하이드로클로라이드, 폴리에틸렌이민, 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것이고, 상기 제 2 고분자 층은, 폴리아크릴산, 폴리메타크릴산, 폴리비닐 알코올, 그래핀 옥사이드, 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층은, 폴리아릴아민 하이드로클로라이드, 폴리아크릴산, 폴리에틸렌이민, 폴리메타크릴산, 및 이들의 조합들로 이루어진 군으로부터 선택되는 하나 이상의 고분자를 포함하는 것일 수 있으며, 상기 제 1 고분자 층 및 상기 제 2 고분자 층을 이루는 고분자와 동일하거나 또는 상이할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층을 이루는 고분자는, 상기 제 2 고분자 층을 이루는 고분자를 포함하는 것일 수 있다. 상기 프라이밍 층의 형성 목적은 상기 고분자 다중층의 제 1 고분자 층이 잘 형성되도록 하기 위한 것이다. 따라서, 상기 제 1 고분자와 상기 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 서로 잘 결합될 수 있기 때문에, 상기 프라이밍 층을 이루는 고분자는 프라이밍 층 상에 형성될 제 1 고분자와 잘 결합되는 성질을 가지는 제 2 고분자를 포함하는 것일 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층 상에 형성될 상기 제 1 고분자와 잘 결합되는 성질을 가지는 고분자를 프라이밍 층으로서 이용할 경우, 하나의 고분자만으로도 프라이밍 층을 구성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 전극은 황 전극일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 및 상기 제 2 고분자는 서로 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이룰 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 제 1 고분자 및 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이루며, 상기 고분자 상이 상기 프라이밍 층 상에 교대로 적층되어 고분자 다중층을 형성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은 상기 프라이밍 층에 용이하게 결합되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 프라이밍 층에 의하여 상기 제 1 고분자가 상기 전극 상의 프라이밍 층에 균일하게 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층에 의하여 상기 전극의 표면이 균일하게 커버되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층은 스핀-코팅에 의하여 상기 전극 상에 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 스핀-코팅에 의하여 코팅된 상기 프라이밍 층은 침지법(dipping method)에 의하여 코팅된 것보다 더 얇고 균일한 표면을 생성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층 및 상기 제 2 고분자 층은 침지법에 의하여 상기 황 전극 상에 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 다중층막 증착(layer-by-layer deposition, LbL)법에 의하여 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 다중층막 증착법에 의하여 상기 고분자 다중층이 나노미터 규모로 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층의 두께에 따라 상기 폴리설파이드의 음이온의 용출 및 리튬 이온의 이동 속도가 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 다중층의 두께가 두꺼워질수록 상기 폴리설파이드 음이온의 용출이 방지되는 한편, 리튬 이온의 이동속도가 감소하여 전하 용량이 감소될 수 있으므로, 상기 다중층막 증착법을 통하여 상기 고분자 다중층의 두께를 조절할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 전해질로의 용출을 방지하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 비가역적인 석출을 방지할 수 있으나, 이에 제한되지 않을 수 있다. 황 전극의 작동 시, 폴리설파이드 음이온의 용출 및 비가역적인 석출은, 반복된 사이클 동안 탄소 골격과 황 생성물 사이의 전기적 컨택의 점진적 분해를 야기하며, 활성 황의 이용을 제한되도록 만든다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 용출 및 비가역적인 석출을 방지함으로써, 상기 황 전극의 캐소드 활물질의 급격한 감소를 방지할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제조 방법은 리튬염을 첨가하는 단계를 추가 포함할 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 리튬염은 LiTFSI, LiNO3, LiCl, LiClO4, 및 이들의 조합들로 이루어진 군으로부터 선택되는 것을 하나 이상 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 구체적으로 상기 리튬염은 리튬-황 이차 전지 구동 시 우수한 성능을 보이는 LiTFSI 및 LiNO3의 조합을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 리튬염에 의하여 상기 프라이밍 층 상기 제 1 고분자 층과 상기 제 2 고분자 층 사이의 수소 결합이 유도되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 막에 의하여 표면-코팅된 전극 제조 시, 상기 리튬염의 추가로 인하여 상기 제 1 고분자 및 제 2 고분자를 포함하는 용액의 이온 강도(ionic strength)가 증가되어, 상기 제 1 고분자 및 상기 제 2 고분자의 효과적인 흡착 또는 흡착된 상기 제 1 고분자 및 제 2 고분자가 다시 상기 용액에 녹아나가는 것을 방지할 수 있으나, 이에 제한되지 않을 수 있다. 전극 제조 시 사용되는 염은 리튬염 외에 어떠한 물질이라도 사용될 수 있지만, 이차 전지를 제조하기 위한 목적으로는 전해질에 포함되는 리튬염을 사용하는 것이 바람직하다. 본원의 일 구현예에 있어서, 상기 리튬염의 농도는 약 0.05 M 이상인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 리튬염은 약 0.05 M 이상, 약 0.05 M 내지 약 0.5 M, 약 0.05 M 내지 약 0.4 M, 약 0.05 M 내지 약 0.2 M, 약 0.05 M 내지 약 0.1 M, 약 0.1 M 내지 약 0.5 M, 약 0.1 M 내지 약 0.4 M, 약 0.1 M 내지 약 0.2 M, 약 0.2 M 내지 약 0.5 M, 또는 약 0.2 M 내지 약 0.4 M의 농도로 추가되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층을 형성하는 단계는 pH 약 2 내지 pH 약 8.5에서 수행되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 다중층을 형성하는 단계는, pH 약 2 내지 pH 약 8.5, pH 약 2 내지 pH 약 7, pH 약 2 내지 pH 약 6, pH 약 2 내지 pH 약 5, pH 약 5 내지 pH 약 8.5, pH 약 5 내지 pH 약 7, pH 약 5 내지 pH 약 6, pH 약 6 내지 pH 약 8.5, pH 약 6 내지 pH 약 7, 또는 pH 약 7 내지 pH 약 8에서 수행되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 막에 의하여 표면-코팅된 전극은, 이차 전지용 전극으로서 사용되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 이차 전지는 리튬-황 이차 전지일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 제 3 측면은 상기 본원의 제 1 측면에 따른 고분자 막에 의하여 표면-코팅된 전극을 포함하는, 이차 전지를 제공한다. 본원의 제 3 측면에 따른 이차 전지에 대하여, 본원의 제 1 측면과 중복되는 부분들에 대해서는 상세한 설명을 생략하였으나, 그 설명이 생략되었더라도 본원의 제 1 측면에 기재된 내용은 본원의 제 3 측면에 동일하게 적용될 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 막에 의하여 표면-코팅된 전극은 전극 상에 형성된 프라이밍 층(priming layer); 및 상기 프라이밍 층 상에 형성되며, 제 1 고분자 층 및 제 2 고분자 층이 순차적으로 적층된 고분자 다중층을 포함을 포함할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은, 폴리에틸렌 옥사이드, 폴리아릴아민 하이드로클로라이드, 폴리에틸렌이민, 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것이고, 상기 제 2 고분자 층은, 폴리아크릴산, 폴리메타크릴산, 폴리비닐 알코올, 그래핀 옥사이드, 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층은, 폴리아릴아민 하이드로클로라이드, 폴리아크릴산, 폴리에틸렌이민, 폴리메타크릴산, 및 이들의 조합들로 이루어진 군으로부터 선택되는 하나 이상의 고분자를 포함하는 것일 수 있으며, 상기 제 1 고분자 층 및 상기 제 2 고분자 층을 이루는 고분자와 동일하거나 또는 상이할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층을 이루는 고분자는, 상기 제 2 고분자 층을 이루는 고분자를 포함하는 것일 수 있다. 상기 프라이밍 층의 형성 목적은 상기 고분자 다중층의 제 1 고분자 층이 잘 형성되도록 하기 위한 것이다. 따라서, 상기 제 1 고분자와 상기 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 서로 잘 결합될 수 있기 때문에, 상기 프라이밍 층을 이루는 고분자는 프라이밍 층 상에 형성될 제 1 고분자와 잘 결합되는 성질을 가지는 제 2 고분자를 포함하는 것일 수 있다. 본원의 일 구현예에 있어서, 상기 프라이밍 층 상에 형성될 상기 제 1 고분자와 잘 결합되는 성질을 가지는 고분자를 프라이밍 층으로서 이용할 경우, 하나의 고분자만으로도 프라이밍 층을 구성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 및 상기 제 2 고분자는 서로 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이룰 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 제 1 고분자 및 제 2 고분자는 정전기적 결합 및/또는 수소 결합이 가능하여 고분자 쌍을 이루며, 상기 고분자 상이 상기 프라이밍 층 상에 교대로 적층되어 고분자 다중층을 형성할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 제 1 고분자 층은 상기 프라이밍 층에 용이하게 결합되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 프라이밍 층에 의하여 상기 상기 제 1 고분자가 상기 전극 상의 프라이밍 층에 균일하게 코팅되는것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 전극은 황 전극일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 다중층막 증착(layer-by-layer deposition, LbL)법에 의하여 코팅되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 다중층막 증착법에 의하여 상기 고분자 다중층이 나노미터 규모로 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층의 두께에 따라 상기 폴리설파이드의 음이온의 용출 및 리튬 이온의 이동 속도가 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 다중층의 두께가 두꺼워질수록 상기 폴리설파이드 음이온의 용출이 방지되는 한편, 리튬 이온의 이동속도가 감소하여 전하 용량이 감소될 수 있으므로, 상기 다중층막 증착법을 통하여 상기 고분자 다중층의 두께를 조절할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 전해질로의 용출을 방지하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 비가역적인 석출을 방지할 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 용출 및 비가역적인 석출을 방지함으로써, 캐소드 활물질의 급격한 감소를 방지할 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 이차 전지는 리튬-황 이차 전지일 수 있으나, 이에 제한되지 않을 수 있다. 본원의 일 구현예에 있어서, 상기 황 전극의 작동 시 폴리설파이드 음이온의 용출 및 비가역적인 석출을 방지함으로써, 용출된 폴리설파이드 음이온이 애노드 표면에 흡착되어 반응하는 셔틀효과로 인한 전하 효율 및 에너지 용량 감소를 방지할 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 전극의 상기 전하 효율 및 에너지 용량 감소를 방지함으로써, 상기 리튬-황 이차 전지의 에너지 저장 용량 및/또는 충전/방전 용량을 향상시킬 수 있으나, 이에 제한되지 않을 수 있다. 본원에서, 황 캐소드 상에 직접 다중층막(LbL) 증착을 수행함으로써, PAH/PAA/(PEO/PAA)n (n = 1, 3, 및 5) 다중층막의 컨포멀 코팅을 가능하게 하는, 신규한 전략을 입증한다. 본원은, 상기 캐소드 상의 다중층막이 Li+ 이온 전도를 제공하면서 폴리설파이드 음이온의 비가역적인 손실을 효과적으로 예방한다는 것을 나타냈다. Li-S 전지의 사이클 성능은 상기 LbL 코팅 층의 다중층 수를 조정함으로써 최적화될 수 있었다. 이러한 진보는 이것의 체적의 무시할만한 증가와 함께 Li-S 전지의 성능을 향상시키는 비싸지 않은 방법론을 제공한다. 이하, 본원의 실시예를 통하여 본 발명을 더욱 상세하게 설명하고자 하나, 하기의 실시예는 본원의 이해를 돕기 위하여 예시하는 것 일뿐, 본원의 내용이 하기 실시예에 한정되는 것은 아니다. [실시예] 재료 폴리알릴아민 하이드로클로라이드(polyallylamine hydrochloride, PAH, Mw = 15 000 g mol-1), 폴리아크릴산(PAA, Mw = 50,000 g mol-1), 폴리에틸렌 옥사이드(polyethylene oxide, PEO, Mw = 300,000 g mol-1), 리튬 나이트레이트(LiNO3), 및 비스(트리플루오로메탄)설폰아마이드 리튬 염[bis(trifluoromethane)sulfonamide lithium salt, LiTFSI]은 Sigma-Aldrich로부터 구입되었다. 황 분말(325 메쉬)는 Alfa Aesar로부터 구입되었다. Super P 탄소 및 폴리비닐리덴 플루오라이드(polyvinylidene fluoride, pvdf)는 SK 이노베이션으로부터 제공되었다. 디옥솔란(dioxolane, DOL) 및 다이메틸 에테르(DME)는 PanaxEtec로부터 구입되었다. 기재의 제조 슬러리 혼합물이 황(60 wt%), super P(20 wt%), 및 pvdf(20 wt%)의 모르타르(mortar) 혼합에 의해 제조되었으며, 닥터블레이트법(doctor blade method)을 이용하여 알루미늄 포일 상에 캐스팅되었고, 이어서 12 시간 동안 진공 오븐에서 건조되었다. 탄소+바인더 기재는 상기 황 캐소드에 대하여 상기 기재된 것과 동일한 절차에 의하 제조되었으나, 황 분말을 포함하지 않았다. 황 기재는 금(gold) 기재 상에서 탄소 다이설파이드 용액 중 황의 스핀-코팅에 의해 제조되었다. 다중층막(layer-by-layer, LbL) 증착 다중층막 증착을 위한 고분자 용액은 18M Milli-Q wtater(1 mg mL-1) 중 고분자를 용해시킴으로써 제조되었으며, 각 용액의 pH는 0.1 M의 HCl 및 NaOH를 이용하여 조정되었다. 동일한 pH를 갖는 각 고분자 용액과 대응하는 세정 용액은 Milli-Q water로 제조되었다. LiTFSI(0.1 M)는 모든 고분자 및 세정 용액에 추가되었다. 프라이밍 층의 증착을 위해, 황 캐소드를 처음에 5 분 동안 PAH(pH = 7.5) 용액에 침지한 뒤 이어서 30 초 동안 상기 PAH 용액으로 1,500 rpm에서 스핀-코팅하였고, 그 후 동일한 rpm에서 동일한 pH의 Milli-Q water로 세정되었다. 동일한 조건으로 PAA(pH = 3.5) 용액을 이용하여 스핀-코팅하였으며, 그 후 동일한 pH의 상기 세정 용액으로 세척하였다. 상기 준비된 프라이밍 층 상에 PEO(pH = 2.5) 및 PAA(pH = 2.5) 고분자 용액에서 각각 5 분 동안, 세정 용액에서 1 분 동안 각각 침지함으로써 다중층막 증착을 수행하였다. 사이클은 요구되는 다중층의 수에 따라 반복되었다. 증착 이후, 상기 캐소드는 50℃에서 진공 오븐에서 밤새 건조되었다. 형태학적 특성 분석 물 접촉각은 DE/DSA100 접촉각 측정기(Fruss Inc.)를 이용하여 측정되었다. 주사 전자 현미경(SEM) 이미지는 JSM-6701F(JEOL)로 수득되었다. X-선 광전자 분광 분석(XPS)은 15 KV 및 10 mA에서 Mg/Al 듀얼 애노드를 구비한 Axis-HSi(Kratos)를 이용하여 수행되었다. 전기화학적 특성 분석 모든 캐소드들은 원형 디스크(직경: ~11 mm)로 구멍이 뚫린 2032 타입 코인 전지로 조립되었다. 전해질은 DOL과 DME의 1:1 부피비 혼합물 중 LiTFSI(1.0 M)과 LiNO3(0.33 M), 또는 LiNO3(0.33 M) 없이 제조되었다. 전기화학적 특성은 WBC300 cycler(Won-A Tech, Korea)로 측정되었다. 포텐셜 윈도우(potential window)는 Li+/Li에 대하여 1.7 V-2.8 V로 고정되었다. 전기화학적 임피던스 분광 분석(EIS)은 10 mV의 변동을 갖는 100 kHz 내지 100 mHz 사이의 개방-회로 전압에서 수행되었다. 일반적으로, 처음 부착 층은 LbL 다중층막의 안정한 성장을 가능하게 하는 중요한 단계이다. 특히, 상기 황 캐소드 상의 (PEO/PAA)n 다중층막의 직접 LbL 증착은 상기 캐소드 표면의 균일성의 부족 및 소수성으로 인하여 어려움을 겪는다. 따라서, 상기 LbL 증착 이전에, PAH/PAA 프라이밍 층은 PAH(pH 7.5) 및 PAA(pH 3.5)의 수성 용액과 염이 첨가된 LiTFSI을 이용하여 1 차 스핀-코팅되었다. 상기 캐소드 상에서 PAH/PAA 층의 초기 프라이밍의 분자적 인과관계는, 장거리 정전기적 반발력을 충분히 차단하고 그것에 의하여 상기 캐소드 표면으로 흡착된 사슬의 소수성 인력을 향상시키는 상기 고분자 용액의 약한 양/음 전하 및 높은 이온 세기에 기인된다. 따라서, 상기 기재의 스피닝(spinning)이 흡착 고분자 사슬에 전단력(shear forces)을 가하여 그들이 상기 표면을 조밀하게 커버하기 때문에, 상기 스핀-이용 고분자 전해질 흡착은 침지법(dipping method)으로 형성된 것과 비교하여 더 얇고 균일한 표면을 생성한다. 상기 캐소드 상의 프라이밍 층(PAH/PAA)의 증착 이후, PEO/PAA 다중층막이 PEO 및 PAA 용액을 이용한 침지법에 의하여 교대로 흡착되었으며, 두 용액 모두 PEO의 에테르 산소와 PAA의 양성자화된 카복실산 사이의 수소 결합을 유도하기 위해 LiTFSI(0.1 M)를 첨가하고 용액 pH를 2.5로 조정함으로써 제조되었다. 상기 황 캐소드의 비균질 표면 상의 균일한 고분자 층을 확인하기 위해, 상기 캐소드 구성 요소 각각에 대하여 LbL 다중층막 증착이 수행되었다. 황 캐소드의 표면은 일반적으로 3 가지 상이한 물질인, 황 분말(60 wt%), 카본 블랙(20 wt%), 및 폴리비닐리덴 플루오라이드(polyvinylidene fluoride, pvdf) 바인더(20 wt%)로 구성되어있으며, 이는 상기 표면 상에 무작위로 분포되었다. 상기 캐소드 구성 요소는, 2 가지 상이한 기재, 황 기재 및 탄소+바인더 기재로 분리되었으며, 상기에서 기재된 다중층막 증착 절차가 수행되었다. 상이한 기재 상의 고분자 흡착 경향은 접촉각 측정기(contact angle measurements)에 의하여 조사되었다(도 2a). 테스트된 상기 모든 기재는 황, 탄소+바인더, 및 황+탄소+바인더 기재(즉, 황 캐소드)에 대하여 초기에 소수성이었지만(104.1°, 164.9°, 및 144.4°), PEO/PAA 5 회 다중층까지 다중층막의 순차적인 증착 동안, 3 가지 상이한 초기 기재의 접촉각은 각각, 24.7°, 13.4°, 및 16.2°로 유의하게 감소하였다. 황 기재만 비교하였을 때, 탄소+바인더 기재와 상기 캐소드의 매우 낮은 물 접촉은, 그들의 더욱 다공성인 거친 표면 모폴로지에 의하여 부분적으로 설명될 수 있었다. 본래(pristine) 황 캐소드의 표면 및 단면 SEM 이미지는, 다공성의 거친 표면 모폴로지를 확인하며, 여기에서 약 50 nm의 직경을 갖는 카본 블랙 입자가 상기 캐소드 표면을 대부분 덮고 있다[도 2b의 (a) 및 도 2b의 (d)]. 상기 PEO/PAA 5 회 다중층 증착 이후, SEM 이미지들[도 2b의 (c) 및 도 2b의 (f)]에 나타낸 바와 같이 상기 표면은 상기 고분자 다중층막에 의하여 컨포멀하게(conformally) 부동태화되었으며, 도 2b의 (c) 및 도 2b의 (f)에서 산소의 EDS 원소 맵으로부터 입증된 바와 같이, 상기 고분자들은 동공을 통하여 상기 캐소드 내부로 깊숙하게 침투될 수 있었다. 그러나, PAH/PAA 프라이밍 층의 부재 하에서 증착된 상기 PEO/PAA의 LbL 코팅은, 격렬한 형태학적 변화를 나타내지 않았을 뿐만 아니라, 막 두께의 균일한 증가 또한 나타내지 않았다(도 3 내지 도 8 참조). 도 3은, 본원의 일 실시예에 있어서, Si 웨이퍼 기재 상에서 PAH/PAA/(PEO/PAA)n 다중층막의 LbL 증착 동안 다중층 수의 함수로서의 다중층막 두께 성장을 나타낸 그래프이다. 도 4의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 탄소+바인더 기재(a), 5 회 다중층-코팅된 탄소+바인더 기재(b), 순수(bare) 황 기재(c), 및 5 회 다중층-코팅된 황 기재(d)의 SEM 이미지이다. 도 5는, 본원의 일 실시예에 있어서, 황, 탄소+바인더, 및 상기 캐소드 기재 상에서 흡착된 고분자 층의 함수로서 접촉각에서의 점진적인 감소를 나타내는 물 접촉각 측정의 광학 이미지이다. 도 6은, 본원의 일 실시예에 있어서, (PAH/PAA)의 프라이밍 층과, 또는 이것 없이, (PEO/PAA)n, n=1, 3, 및 5 회 증착 동안 형태학적 변화를 나타내는 황 캐소드의 이미지이다. 도 7의 (a) 및 (b)는, 본원의 일 실시예에 있어서, 본래 황 캐소드 및 (PEO/PAA) 5 회 다중층-코팅된 황 캐소드의 XPS 스펙트럼이다. 도 8은, 본원의 일 실시예에 있어서, 본래 황 캐소드 및 (PEO/PAA) 5 회 다중층-코팅된 황 캐소드에 대한 원소 맵 및 EDS 스펙트럼이다. 상기 다중층막-코팅된 캐소드의 전기화학적 성능은 2032 코인 전지 Li-S 전지 내부로의 통합에 의해 조사되었으며, 그 후에 이러한 디바이스들의 정전류 사이클링 연구(galvanostatic cycling studies)가 이어졌다. 이러한 연구들에서 사용된 전해질 시스템은 디옥솔란(dioxolane, DOL)/다이메틸 에테르(DME) 중의 LiTFSI(1.0 M) 및 LiNO3(0.33 M) 이었다. 0.5 C 속도(1 C = 1,675 mAg-1)에서 상이한 다중층 수를 갖는 상기 황 캐소드의 충전/방전 전압 프로파일은 도 9에 도시되었다. 상기 방전 프로파일에서 ~2.4 V의 상부 정체기(plateau)의 영역은 용해 반응으로부터 기원된 것으로 여겨지며, 여기서 고체 황은 리튬화(lithiation)에 따라 수용성 폴리설파이드(S8 to Sn2-, n=8-4)로 감소된다. 이러한 영역에서, 초기 10 사이클 동안 비정전용량(specific capacity)의 감소는 "ΔQ"로서 나타내어지며, 이는 수용성 폴리설파이드의 형성으로 인하여 활성 황의 비가역적인 손실을 야기하고, 따라서 ΔQ는 상기 황 캐소드의 특성을 표면 특성 보호와 직접적으로 관련된다. 표면 패시베이션 없이 본래 캐소드의 ΔQ 값은 가장 크며(164 mAhg-1) 이러한 ΔQ 값은 상기 황 캐소드 상의 표면 코팅의 1, 3, 및 5 회 다중층 코팅과 함께 106, 92, 및 81 mAhg-1로 감소한다. 다중층의 수의 함수로서 상기 ΔQ 값에서의 이러한 감소는 상기 (PEO/PAA)n 다중층막 코팅으로 인한 전해질로의 폴리설파이드 확산의 효과적인 억제를 나타낸다. 사이클링 이후 Li 애노드의 표면은 또한 상기 캐소드 상의 다중층막 코팅이 상기 애노드 측으로 폴리설파이드 이동을 방지하는 것을 확인하였다(도 10 내지 도 15 참조). 한편, 도 9의 (d)에서, 충전 및 방전 전압 사이의 더욱 강한 분극(polarization)(ΔV = 0.141 V), 및 더욱 경사진 2.1 V 이하로 전압 강하가 방전의 종료 시 본래 캐소드보다 5 회 다중층-코팅된 캐소드에서 발견되었다. 이것은 상기 캐소드에 증착된 더 두꺼운 다중층막을 통한 Li+ 확산 속도에서의 감소에 기인하는 것으로 여겨진다. 이러한 관점에서, 이것은 느린 Li+ 확산으로 인한 ΔQ 및 전압 강하 사이의 상충점(trade-off point)이며, 곧 간략하게 논의될 바와 같이, 효과적인 표면 패시베이션을 위한 최적의 다중층 수가 있다는 것을 시사한다. 도 10은, 본원의 일 실시예에 있어서, (PAH/PAA) 1, 4, 6 회 다중층-코팅된 황 캐소드와 비교하여, 본래 황 캐소드 및 (PEO/PAA) 1, 4, 및 6 회 다중층-코팅된 황 캐소드의 0.1 C에서의 사이클 성능을 나타낸 그래프이다. 도 11의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 본래 황 캐소드(a), 1 회 다중층-코팅된 캐소드(b), 3 회 다중층-코팅된 캐소드(c), 및 5 회 다중층-코팅된 캐소드(d)의 10 사이클 이후, 분해된 Li 애노드의 광학 이미지이다. 도 12는, 본원의 일 실시예에 있어서, 1.5 V에서의 정전압을 본래 황 전극 및 5 회 다중층-코팅된 캐소드와 조립된 비커 전지(beaker cells)로 인가한 후, 5 분에서의 전해질 용액의 UV-Vis 스펙트럼 및 광학 이미지를 나타낸 것이다. 도 13은, 본원의 일 실시예에 있어서, 사이클 이전에 측정된 본래 황 전극 및 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 전기화학적 임피던스 분광 분석(EIS) 데이터이다. 도 14의 (a) 내지 (d)는, 본원의 일 실시예에 있어서, 처음 1 사이클 및 10 사이클 이후 측정된 본래 황 전극 및 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 EIS 데이터이다. 도 15는, 본원의 일 실시예에 있어서, 전해질 중 LiNO3 없이 본래 황 전극 및 1, 3, 및 5 회 다중층-코팅된 황 캐소드의 0.5 C에서의 사이클 성능 및 쿨롱 효율(쿨롱 효율=충전/방전 용량)을 나타낸 그래프이다. 0.5 C 에서 상이한 수의 (PEO/PAA)n 다중층을 갖는 황 캐소드의 사이클링 성능은 도 15에서 나타내었다. 상기 본래 황 캐소드가 처음 10 사이클 이후에서 조차 급속한 용량 변화(fading)를 나타내는 반면, 상기 다중층막-코팅된 캐소드는 100 사이클까지 매우 높은 비정전용량을 유지하였다. 상기 3 회 다중층-코팅된 캐소드는 100 사이클 이후 가장 높은 용량 유지율(806 mAhg-1)을 나타냈으며, 5 회 다중층-코팅된 캐소드에 대해 수득된 728 mAhg-1의 용량보다 더 높았다. 그 이유는, 전술한 바와 같이, 상기 비가역적인 폴리설파이드 손실로부터 보호의 더 나은 능력에도 불구하고, 5 회 다중층-코팅된 캐소드의 심각한 전압 강하가 이것의 용량의 손실에 우세하게 영향을 미치기 때문이다. 상기 다중층막-코팅된 캐소드의 용량 유지율 경향에서 C 속도(각각 10 사이클, 0.1 C 내지 2.0 C)의 영향이 또한 조사되었다. 낮은 C 속도에서, 상기 캐소드들로부터 폴리설파이드의 용출은 상기 다중층막을 통한 Li+ 확산의 임피던스(impedance)보다, 전체 용량 손실에 대하여 더욱 지배적인 요소였으며, 따라서 0.1 C에서 시작한, 5 회 다중층-코팅된 상기 캐소드의 용량은 3 회 다중층의 것보다 약간 높다. C 속도의 증가에 따라, 두 캐소드 사이의 성능에서의 차이는 ΔQ와 상기 전압 강하 사이의 절충으로 인하여 미미해진다. 한편, 상기 용량들에서의 급격한 감소는 상기 본래 캐소드에서 1.0 C 이상이며, 1 회 다중층-코팅된 캐소드에서 2.0 C인 것으로 관찰되었다. 이러한 캐소드의 표면 상의 불충분한 보호를 갖는 상기 폴리설파이드 확산은 반복된 사이클 동안 상기 탄소 골격과 황 생성물 사이의 전기적 컨택의 점진적 분해를 야기하며, 특히, 높은 C 속도에서, 활성 황의 제한된 이용으로 이끈다. 한편, 3 및 5 회 다중층-코팅된 캐소드는 2 C에서조차 그들의 높은 용량을 유지하며, 이것은 상기 캐소드 상의 충분한 다중층막 코팅으로 인한 상기 폴리설파이드 확산으로부터 효과적인 보호의 명백한 증거이다. 0.5 C에서 충전/방전의 10 사이클 이후 상기 다중층막-코팅된 캐소드의 구조적 안정성은 도 16의 (a) 및 도 16의 (b)에서 SEM을 이용하여 본래 황 캐소드와 비교하여 확인되었다. 상기 본래 황 전극 상에 상기 탄소 골격으로부터 전기적으로 단리된, 다수의 황 종이 있으며, 한편, 상기 다중층-코팅된 캐소드가 본래의 모폴로지를 유지하며, 이것은 컨포멀하게 패시베이션된 중합 층을 나타내는 것임을 발견하였다. 결론적으로, 상기 LbL 증착에 의하여 황 전극 상에 증착된 (PEO/PAA) 다중층막은 전해질로의 폴리설파이드 확산을 성공적으로 방지하며 사이클 동안 안정한 캐소드 구조를 유지함으로써, Li-S 전지의 용량 유지율을 효과적으로 향상시킨다. 또한, 다양한 C 속도에 따른 상기 전지 성능은 상기 다중층막 증착 단계 동안 상기 다중층의 수를 조정함으로써 최적화될 것으로 예상된다. 전술한 본원의 설명은 예시를 위한 것이며, 본원이 속하는 기술분야의 통상의 지식을 가진 자는 본원의 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 쉽게 변형이 가능하다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다. 예를 들어, 단일형으로 설명되어 있는 각 구성 요소는 분산되어 실시될 수도 있으며, 마찬가지로 분산된 것으로 설명되어 있는 구성 요소들도 결합된 형태로 실시될 수 있다. 본원의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 균등 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본원의 범위에 포함되는 것으로 해석되어야 한다. Disclosed are an electrode surface-coated by a polymer film, a method for producing the electrode surface-coated by a polymer film, and a secondary battery comprising the electrode surface-coated by a polymer film. 전극 상에 형성된 프라이밍 층(priming layer); 및 상기 프라이밍 층 상에 형성되며, 제 1 고분자 층 및 제 2 고분자 층이 순차적으로 적층된 고분자 다중층 을 포함하는, 고분자 막에 의하여 표면-코팅된 전극. 제 1 항에 있어서, 상기 제 1 고분자 층은, 폴리에틸렌 옥사이드, 폴리아릴아민 하이드로클로라이드, 폴리에틸렌이민, 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것이고, 상기 제 2 고분자 층은, 폴리아크릴산, 폴리메타크릴산, 폴리비닐 알코올, 그래핀 옥사이드, 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것인, 고분자 막에 의하여 표면-코팅된 전극. 제 1 항에 있어서, 상기 프라이밍 층은, 폴리아릴아민 하이드로클로라이드, 폴리아크릴산, 폴리에틸렌이민, 폴리메타크릴산, 및 이들의 조합들로 이루어진 군으로부터 선택되는 하나 이상의 고분자를 포함하는 것인, 고분자 막에 의하여 표면-코팅된 전극. 제 1 항에 있어서, 상기 전극은 황 전극인 것인, 고분자 막에 의하여 표면-코팅된 전극. 제 1 항에 있어서, 이차 전지용 전극으로서 사용되는, 고분자 막에 의하여 표면-코팅된 전극. 제 4 항에 있어서, 상기 고분자 다중층은 상기 황 전극의 작동 시 폴리설파이드 음이온의 전해질로의 용출을 방지하는 것인, 고분자 막에 의하여 표면-코팅된 전극. 제 1 항에 있어서, 상기 전극은 리튬염을 추가 포함하는, 고분자 막에 의하여 표면-코팅된 전극. 전극 상에 프라이밍 층을 형성하는 단계; 및 상기 프라이밍 층 상에 제 1 고분자 층과 제 2 고분자 층을 순차적으로 적층하여 고분자 다중층을 형성하는 단계 를 포함하는, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 8 항에 있어서, 상기 제 1 고분자 층은, 폴리에틸렌 옥사이드, 폴리아릴아민 하이드로클로라이드, 폴리에틸렌이민, 및 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것이고, 상기 제 2 고분자 층은, 폴리아크릴산, 폴리메타크릴산, 폴리비닐 알코올, 그래핀 옥사이드, 이들의 조합들로 이루어진 군으로부터 선택되는 고분자를 포함하는 것인, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 8 항에 있어서, 상기 프라이밍 층은 폴리아릴아민 하이드로클로라이드, 폴리아크릴산, 폴리에틸렌이민, 폴리메타크릴산, 및 이들의 조합들로 이루어진 군으로부터 선택되는 하나 이상의 고분자를 포함하는 것인, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 8 항에 있어서, 상기 전극은 황 전극인 것인, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 8 항에 있어서, 상기 제 1 고분자 층 및 상기 제 2 고분자 층은 리튬염을 추가로 포함하는 것인, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 8 항에 있어서, 상기 고분자 다중층을 형성하는 단계는 pH 2 내지 pH 8.5에서 수행되는 것인, 고분자 막에 의하여 표면-코팅된 전극의 제조 방법. 제 1 항 내지 제 7 항 중 어느 한 항에 따른 고분자 막에 의하여 표면-코팅된 전극을 포함하는, 이차 전지. 제 14 항에 있어서, 상기 이차 전지는 리튬-황 이차 전지인, 이차 전지.