IMAGE PROCESSING DEVICE AND METHOD

本開示は、画像処理装置および方法に関し、特に、符号化効率の低減を抑制することができるようにした画像処理装置および方法に関する。

従来、TU単位毎に、水平方向のプライマリ変換PThor(プライマリ水平変換とも称する)および垂直方向のプライマリ変換PTver(プライマリ垂直変換とも称する)毎に、適応的に複数の異なる直交変換から、プライマリ変換を選択する適応プライマリ変換(AMT: Adaptive Multiple Core Transforms)が開示されている(例えば、非特許文献1参照)。

なお、非特許文献1には、水平方向(x方向)および垂直方向(y方向)毎に、プライマリ変換の候補となる直交変換を含む変換セットTransformSetが、モード情報と変換セットの対応表(イントラ予測モード情報)に基づいて、(一意に)決定(選択)されることも開示されている。そして、変換セットの定義が、変換ブロックサイズとモード情報に基づいて定まることも開示されている(例えば、非特許文献2参照)。

しかしながら、従来の方法では、1次元変換スキップが特定の変換ブロックサイズ、およびイントラ予測モード番号のときにしか選択できないとう制限があった。従って、レート歪の観点から、2次元直交変換をするよりも、水平もしくは垂直方向の直交変換をスキップする1次元変換スキップを選択する方が良い場合、エンコーダ側において1次元変換スキップを選択することが出来ないため、符号化効率が低減するおそれがあった。

本開示は、このような状況に鑑みてなされたものであり、符号化効率の低減を抑制することができるようにするものである。

本技術の第1の側面の画像処理装置は、符号化データを復号する復号部と、前記復号部により前記符号化データが復号されて得られた変換スキップ識別子の値に基づいて、画像データが変換された変換係数データに対する垂直方向の逆プライマリ変換である逆プライマリ垂直変換の実行を制御する逆プライマリ垂直変換制御部と、前記変換スキップ識別子の値に基づいて、画像データが変換された係数データに対する水平方向の逆プライマリ変換である逆プライマリ水平変換の実行を制御する逆プライマリ水平変換制御部とを備える画像処理装置である。

前記逆プライマリ垂直変換制御部は、前記変換スキップ識別子が垂直方向の1次元変換をスキップしないことを示す場合、前記変換係数データに対する前記逆プライマリ垂直変換を実行させ、前記変換スキップ識別子が垂直方向の1次元変換をスキップすることを示す場合、前記変換係数データに対する前記逆プライマリ垂直変換を省略させることができる。

前記逆プライマリ水平変換制御部は、前記変換スキップ識別子が水平方向の1次元変換をスキップしないことを示す場合、前記変換係数データに対する前記逆プライマリ水平変換を実行させ、前記変換スキップ識別子が水平方向の1次元変換をスキップすることを示す場合、前記変換係数データに対する前記逆プライマリ水平変換を省略させることができる。

前記逆プライマリ垂直変換および前記逆プライマリ水平変換に適用する直交変換を選択する選択部をさらに備えるようにすることができる。

前記選択部は、前記復号部により前記符号化データが復号されて得られた垂直変換セット識別子とプライマリ垂直変換指定フラグに基づいて、前記逆プライマリ垂直変換として適用する直交変換を選択し、前記復号部により前記符号化データが復号されて得られた水平変換セット識別子とプライマリ水平変換指定フラグに基づいて、前記逆プライマリ水平変換として適用する直交変換を選択することができる。

前記復号部は、前記変換スキップ識別子の値に応じて、プライマリ変換識別子から前記プライマリ垂直変換指定フラグおよび前記プライマリ水平変換指定フラグを導出することができる。

前記復号部は、前記変換スキップ識別子が2次元変換をスキップしないことを示す場合、前記プライマリ変換識別子を2ビットのbin列として処理して前記プライマリ垂直変換指定フラグおよび前記プライマリ水平変換指定フラグを導出し、前記変換スキップ識別子が垂直方向または水平方向の1次元変換をスキップしないことを示す場合、前記プライマリ変換識別子を1ビットのbin列として処理して前記プライマリ垂直変換指定フラグまたは前記プライマリ水平変換指定フラグを導出することができる。

前記復号部は、前記符号化データに含まれる前記プライマリ垂直変換指定フラグおよび前記プライマリ水平変換指定フラグを復号することができる。

前記復号部は、前記変換スキップ識別子が、垂直方向若しくは水平方向の1次元変換または2次元変換をスキップしないことを示す場合、セカンダリ変換識別子の復号を省略し、前記セカンダリ変換識別子を、セカンダリ変換をしないことを示す値に設定することができる。

本技術の第1の側面の画像処理方法は、符号化データを復号し、前記符号化データが復号されて得られた変換スキップ識別子の値に基づいて、画像データが変換された変換係数データに対する垂直方向の逆プライマリ変換である逆プライマリ垂直変換の実行を制御し、前記変換スキップ識別子の値に基づいて、画像データが変換された係数データに対する水平方向の逆プライマリ変換である逆プライマリ水平変換の実行を制御する画像処理方法である。

本技術の第2の側面の画像処理装置は、変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する水平方向のプライマリ変換であるプライマリ水平変換の実行を制御するプライマリ水平変換制御部と、前記変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する垂直方向のプライマリ変換であるプライマリ垂直変換の実行を制御するプライマリ垂直変換制御部と、前記変換スキップ識別子を符号化する符号化部とを備える画像処理装置である。

前記プライマリ水平変換制御部は、前記変換スキップ識別子が水平方向の1次元変換をスキップしないことを示す場合、前記残差データに対する前記プライマリ水平変換を実行させ、前記変換スキップ識別子が水平方向の1次元変換をスキップすることを示す場合、前記残差データに対する前記プライマリ水平変換を省略させることができる。

前記プライマリ垂直変換制御部は、前記変換スキップ識別子が垂直方向の1次元変換をスキップしないことを示す場合、前記残差データに対する前記プライマリ垂直変換を実行させ、前記変換スキップ識別子が垂直方向の1次元変換をスキップすることを示す場合、前記残差データに対する前記プライマリ垂直変換を省略させることができる。

前記プライマリ水平変換および前記プライマリ垂直変換に適用する直交変換を選択する選択部をさらに備えるようにすることができる。

前記選択部は、水平変換セット識別子とプライマリ水平変換指定フラグに基づいて、前記プライマリ水平変換として適用する直交変換を選択し、垂直変換セット識別子とプライマリ垂直変換指定フラグに基づいて、前記プライマリ垂直変換として適用する直交変換を選択することができる。

前記符号化部は、前記変換スキップ識別子の値に応じて、前記プライマリ水平変換指定フラグおよび前記プライマリ垂直変換指定フラグからプライマリ変換識別子を導出することができる。

前記符号化部は、前記変換スキップ識別子が2次元変換をスキップしないことを示す場合、前記プライマリ水平変換指定フラグおよび前記プライマリ垂直変換指定フラグを用いて、2ビットのbin列の前記プライマリ変換識別子を導出し、前記変換スキップ識別子が水平方向または垂直方向の1次元変換をスキップしないことを示す場合、前記プライマリ水平変換指定フラグまたは前記プライマリ垂直変換指定フラグを用いて、1ビットのbin列の前記プライマリ変換識別子を導出することができる。

前記符号化部は、前記プライマリ水平変換指定フラグおよび前記プライマリ垂直変換指定フラグを符号化することができる。

前記符号化部は、前記変換スキップ識別子が、水平方向若しくは垂直方向の1次元変換または2次元変換をスキップしないことを示す場合、セカンダリ変換識別子の符号化を省略することができる。

本技術の第2の側面の画像処理方法は、変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する水平方向のプライマリ変換であるプライマリ水平変換の実行を制御し、前記変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する垂直方向のプライマリ変換であるプライマリ垂直変換の実行を制御し、前記変換スキップ識別子を符号化する画像処理方法である。

本技術の第1の側面の画像処理装置および方法においては、符号化データが復号され、その符号化データが復号されて得られた変換スキップ識別子の値に基づいて、画像データが変換された変換係数データに対する垂直方向の逆プライマリ変換である逆プライマリ垂直変換の実行が制御され、また、その変換スキップ識別子の値に基づいて、画像データが変換された係数データに対する水平方向の逆プライマリ変換である逆プライマリ水平変換の実行が制御される。

本技術の第2の側面の画像処理装置および方法においては、変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する水平方向のプライマリ変換であるプライマリ水平変換の実行が制御され、また、その変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する垂直方向のプライマリ変換であるプライマリ垂直変換の実行が制御され、その変換スキップ識別子が符号化される。

本開示によれば、画像を処理することができる。特に、符号化効率の低減を抑制することができる。

以下、本開示を実施するための形態(以下実施の形態とする)について説明する。なお、説明は以下の順序で行う。

<1.第1の実施の形態>

また、JEM3では、TU単位毎に、水平方向のプライマリ変換PThor(プライマリ水平変換とも称する)および垂直方向のプライマリ変換PTver(プライマリ垂直変換とも称する)毎に、適応的に複数の異なる直交変換から、プライマリ変換を選択する適応プライマリ変換(AMT(Adaptive Multiple Core Transforms))が開示されている。

より具体的には、例えばTU単位で、適応プライマリ変換を実施するか否かを示す適応プライマリ変換フラグapt_flag(amt_flag、cu_pt_flag、またはemt_flagとも称する)が0(偽)の場合、プライマリ変換として、 DCT-IIまたはDST-VIIがモード情報によって(一意に)決定される。

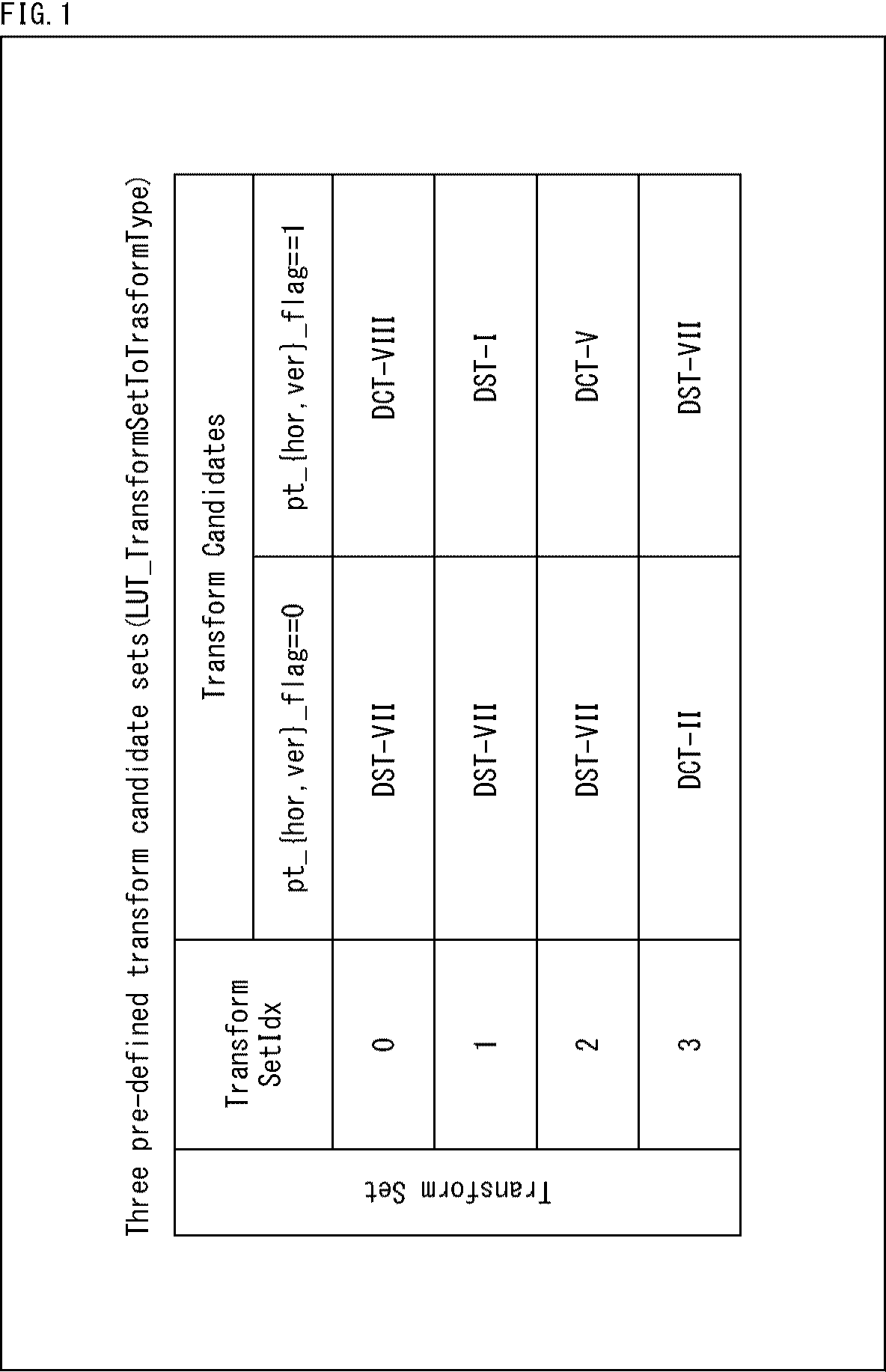

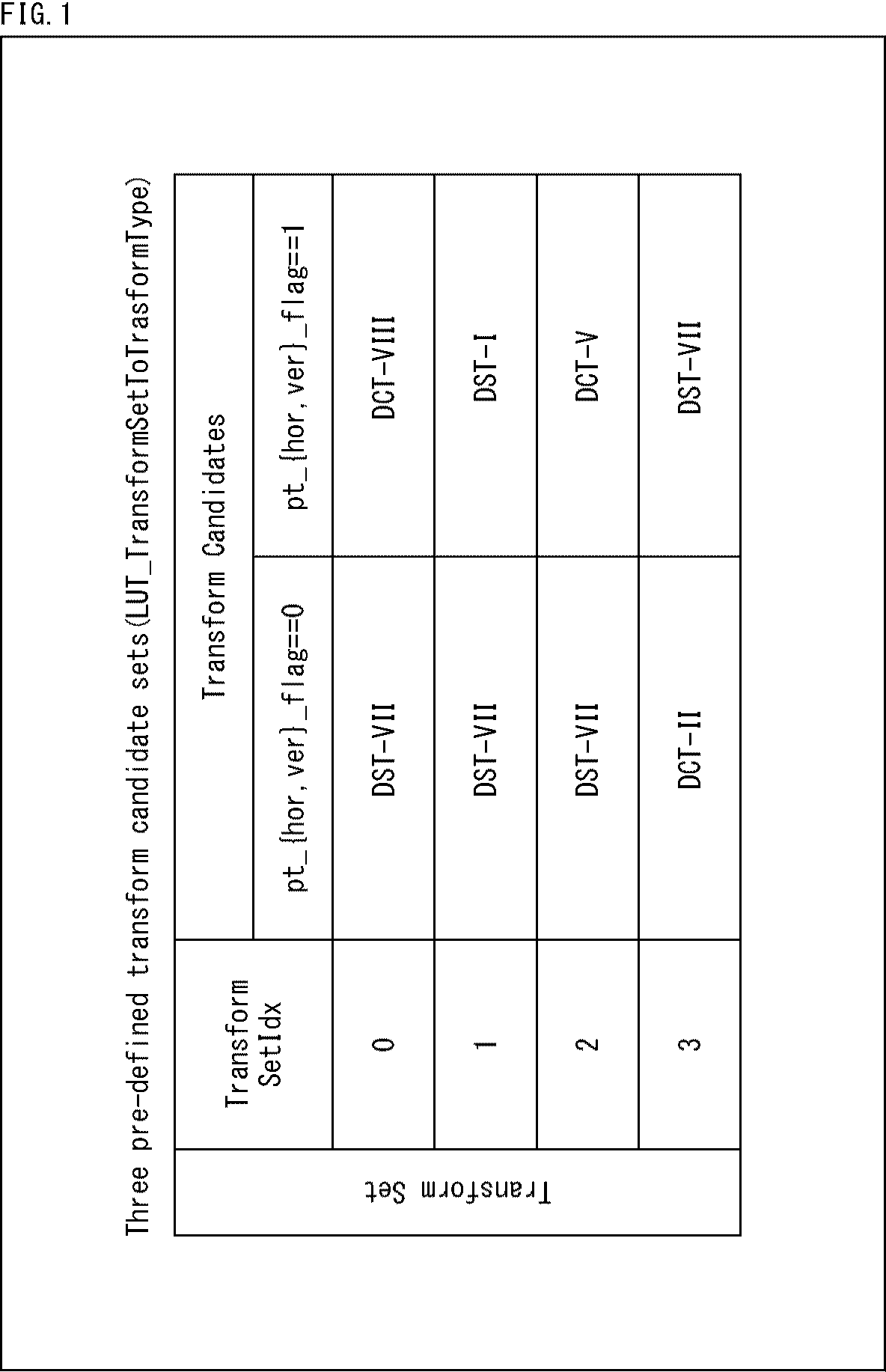

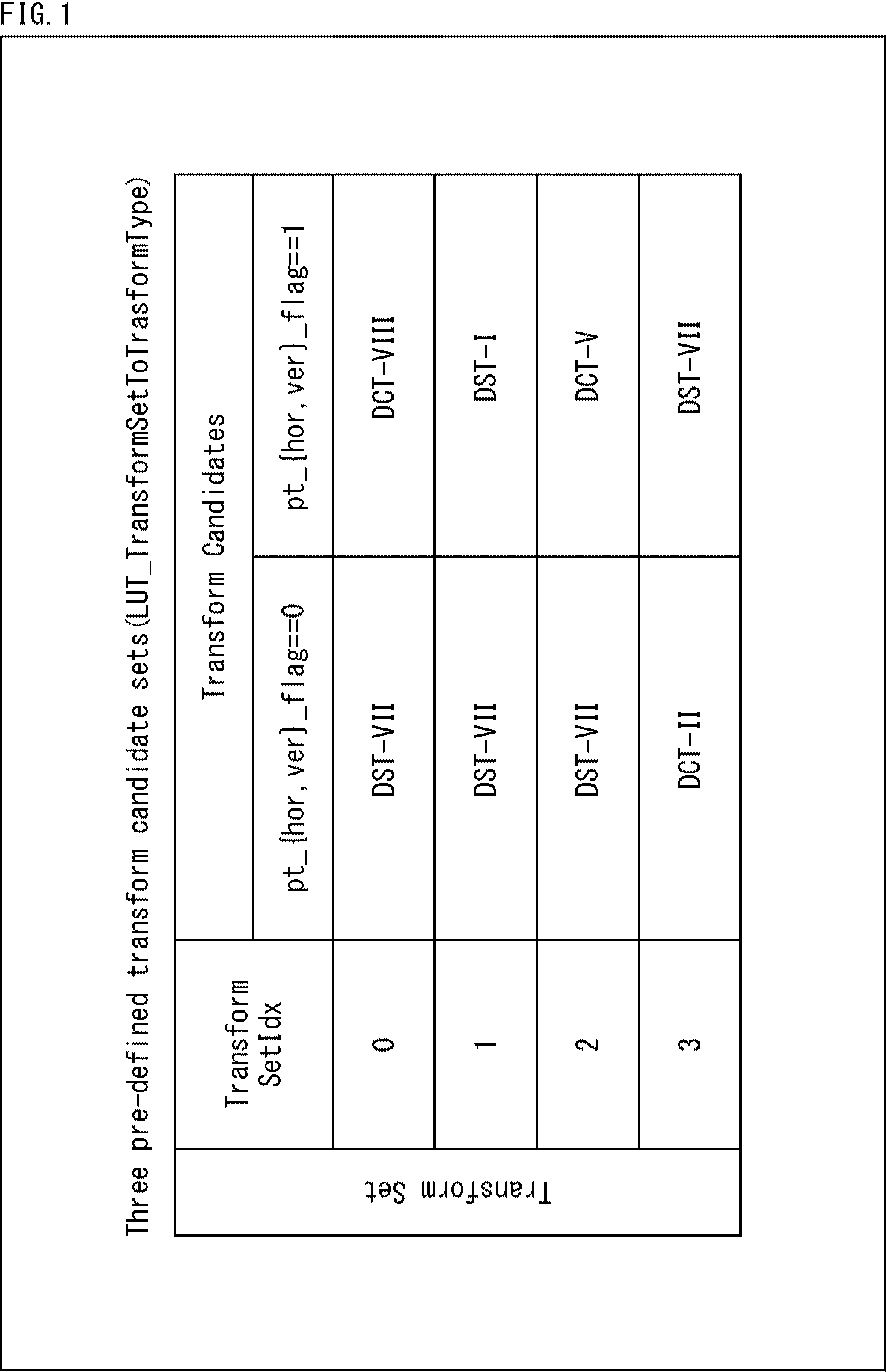

これに対して、例えば、適応プライマリ変換フラグapt_flagが1(真)の場合、図1に示される表のように、水平方向(x方向)と垂直方向(y方向)のそれぞれについてのプライマリ変換の候補となる直交変換を含む変換セットTransformSetが、3つの候補(Transform SetIdx = 0乃至2)の中から選択される。図1に示されるDST(Discrete Sine Transform)-VIIやDCT(Discrete Cosine Transform)-VIII等は、直交変換のタイプを示しており、それぞれ、図2に示される表のような関数が用いられる。

変換セットTransformSetの選択(決定)は、図3に示される表のように、イントラ予測モード(Intra Mode)に基づいて行われる。例えば、以下の式(1)および式(2)のように、各変換セットTransformSet{H,V}に対して、対応する変換セットTransformSetを指定する変換セット識別子TransformSetIdxを設定するように実施される。

TransformSetH = LUT_IntraModeToTransformSet [ IntraMode ] [ H(=0) ]

ここで、TransformSetHは、プライマリ水平変換PThorの変換セットを示し、TransormSetVは、プライマリ垂直変換PTverの変換セットを示し、ルックアップテーブルLUT_IntraModeToTransformSetは、図3の対応表を示している。ルックアップテーブルLUT_IntraModeToTransformSet[][]の1番目の配列は、イントラ予測モードIntraModeを引数とし、2番目の配列は、{H=0, V=1}を引数とする。

例えば、イントラ予測モード番号9(IntraMode==9)の場合、プライマリ水平変換PThorの変換セットTransformSetH(プライマリ水平変換セットとも称する)として、図1の表に示される変換セット識別子TransformSetIdx=0の変換セットが選択され、プライマリ垂直変換PTverの変換セットTransformSetV(プライマリ垂直変換セットとも称する)として、図1の表に示される変換セット識別子TransformSetIdx=2の変換セットが選択される。

さらに、選択された変換セットTransformSetのうちのどの直交変換をプライマリ水平変換に適用するかが、プライマリ水平変換指定フラグpt_hor_flagによって選択される。また、選択された変換セットTransformSetのうちのどの直交変換をプライマリ垂直変換に適用するかが、プライマリ垂直変換指定フラグpt_ver_flagによって選択される。例えば、以下の式(3)および式(4)のように、プライマリ{水平, 垂直}変換セットTransformSet{H,V}、とプライマリ{水平, 垂直}変換指定フラグpt_{hor,ver}_flagを引数として、図1に示される変換セットの定義表(LUT_TransformSetToTransformType)から導出される。

PThor = LUT_TransformSetToTransformType [ TransformSetH ] [ pt_hor_flag ]

例えば、イントラ予測モード番号9(IntraMode==9)の場合、プライマリ水平変換セットTransformSetHの変換セット識別子の値は0であるため、図1の変換セット定義表LUT_TransformSetToTransformType上で変換セット識別子TransformSetIdx==0である変換セットからプライマリ水平変換が選択(指定)される。すなわち、プライマリ水平変換指定フラグpt_hor_flagが0の場合、プライマリ水平変換PThorとして、DST-VIIが選択され、プライマリ水平変換指定フラグpt_hor_flagが1の場合、プライマリ水平変換PThorとして、DCT-VIIIが選択される。

また、プライマリ水平指定フラグpt_hor_flagおよびプライマリ垂直変換指定フラグpt_ver_flagからプライマリ変換識別子pt_idxが、以下の式(5)に基づいて導出される。

pt_idx = (pt_ver_flag << 1) + pt_hor_flag

すなわち、プライマリ変換識別子pt_idxの上位1bitは、プライマリ垂直変換指定フラグの値に対応し、下位1bitは、プライマリ水平変換指定フラグの値に対応する。導出されたプライマリ変換識別子pt_idxのbin列に対して、算術符号化を適用して、ビット列を生成することで、符号化が実施される。

非特許文献2では、プライマリ変換の変換セットを構成する直交変換として、非特許文献1の直交変換の候補{DST-VII, DST-I, DCT-V, DCT-VIII}に加えて、DST-IV及び1次元直交変換をスキップし、係数のスケーリングのみを行うIdentity Transform(IDTまたは1次元変換スキップ(1D Transform Skip)とも称する)を導入することが開示されている。また、非特許文献2においては、図1に新たな変換セット(変換セット識別子TransformSetIdx==3)が追加されている。

また、非特許文献2の場合、変換セットの定義は、変換ブロックサイズとモード情報に基づいて定まる。イントラ予測モード番号が9の場合の、4x4/8x8/16x16/32x32変換における変換セットの定義の一例を図4の表に示す。例えば、図4に示される表において、変換ブロックサイズ4x4の場合、変換セット識別子TrasnformSetIdx=2の変換セットでは、プライマリ水平変換PThorとして、IDTが選択され、プライマリ垂直変換PTverとして、DST-VIIが選択される。具体的には、以下の式(6)および式(7)のように、ルックアップテーブルLUT_TransformSetから、1番目の配列はイントラ予測モードIntraModeを引数とし、2番目の配列は変換ブロックサイズの対数値 - 2 の値を引数とし、3番目の配列は、変換セット識別子TransformSetIdxを引数とし、4番目の配列は、水平方向H(=0)または垂直方向V(=1)を引数として、プライマリ水平変換PThorおよびプライマリ垂直変換PTverの直交変換が選択される。

PThor = LUT_TransfomSet[ IntraMode(=9) ] [ log2TBSize - 2 (=0) ] [ TransformSetIdx(=2) ] [ H(=0) ] = IDT

なお、非特許文献2では、以下の式(8)のように、プライマリ変換識別子pt_idxが、変換セット識別子TransfromSetIdxに対応する。

pt_idx = TransformSetIdx

非特許文献2では、1次元変換スキップが特定の変換ブロックサイズおよびイントラ予測モード番号のときにしか選択できないとう制限がある。従って、レート歪の観点から、2次元直交変換をするよりも、水平もしくは垂直方向の直交変換をスキップする1次元変換スキップを選択する方が良い場合、エンコーダ側において1次元変換スキップを選択することが出来きないため、符号化効率が低減するおそれがあった。

そこで、符号化側において、変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する水平方向のプライマリ変換であるプライマリ水平変換の実行を制御し、またその変換スキップ識別子の値に基づいて、画像と予測画像の残差データに対する垂直方向のプライマリ変換であるプライマリ垂直変換の実行を制御し、その変換スキップ識別子を符号化するようにする。また、復号側において、符号化データを復号し、その符号化データが復号されて得られた変換スキップ識別子の値に基づいて、画像データが変換された変換係数データに対する垂直方向の逆プライマリ変換である逆プライマリ垂直変換の実行を制御し、またその変換スキップ識別子の値に基づいて、画像データが変換された係数データに対する水平方向の逆プライマリ変換である逆プライマリ水平変換の実行を制御するようにする。

このようにすることにより、水平方向または垂直方向の1次元変換をスキップすることが望ましい場合に、(逆)プライマリ変換の処理量の低減およびエナジーコンパクションの低下を抑制し、符号化効率を向上させることができる。

<ブロック分割>

このように、可変的なサイズを有するCUが採用される結果、HEVCでは、画像の内容に応じて画質及び符号化効率を適応的に調整することが可能である。予測符号化のための予測処理は、PU(Prediction Unit)と呼ばれる処理単位(予測単位)で実行される。PUは、CUをいくつかの分割パタンのうちの1つで分割することにより形成される。また、PUは、輝度(Y)及び色差(Cb,Cr)毎のPB(Prediction Block)と呼ばれる処理単位(予測ブロック)から構成される。さらに、直交変換処理は、TU(Transform Unit)と呼ばれる処理単位(変換単位)で実行される。TUは、CU又はPUをある深さまで分割することにより形成される。また、TUは、輝度(Y)及び色差(Cb,Cr)毎のTB(Transform Block)と呼ばれる処理単位(変換ブロック)から構成される。

<再帰的なブロックの分割>

図6の上部には、一例として、64x64画素のサイズを有するCUであるC01が示されている。C01の分割の深さは、ゼロに等しい。これは、C01がCTUのルートでありLCUに相当することを意味する。LCUサイズは、SPS(Sequence Parameter Set)又はPPS(Picture Parameter Set)において符号化されるパラメータにより指定され得る。CUであるC02は、C01から分割される4つのCUのうちの1つであり、32x32画素のサイズを有する。C02の分割の深さは、1に等しい。CUであるC03は、C02から分割される4つのCUのうちの1つであり、16x16画素のサイズを有する。C03の分割の深さは、2に等しい。CUであるC04は、C03から分割される4つのCUのうちの1つであり、8x8画素のサイズを有する。C04の分割の深さは、3に等しい。このように、CUは、符号化される画像を再帰的に分割することにより形成される。分割の深さは、可変的である。例えば、青空のような平坦な画像領域には、より大きいサイズの(即ち、深さが小さい)CUが設定され得る。一方、多くのエッジを含む急峻な画像領域には、より小さいサイズの(即ち、深さが大きい)CUが設定され得る。そして、設定されたCUの各々が、符号化処理の処理単位となる。

<CUへのPUの設定>

<CUへのTUの設定>

上述したCU、PU及びTUといったブロックを画像に設定するためにどのようなブロック分割を行うかは、典型的には、符号化効率を左右するコストの比較に基づいて決定される。エンコーダは、例えば1つの2Mx2M画素のCUと、4つのMxM画素のCUとの間でコストを比較し、4つのMxM画素のCUを設定した方が符号化効率が高いならば、2Mx2M画素のCUを4つのMxM画素のCUへと分割することを決定する。

<CUとPUの走査順>

以下においては、画像(ピクチャ)の部分領域や処理単位として「ブロック」を用いて説明する場合がある(処理部のブロックではない)。この場合の「ブロック」は、ピクチャ内の任意の部分領域を示し、その大きさ、形状、および特性等は限定されない。つまり、この場合の「ブロック」には、例えば、TB、TU、PB、PU、SCU、CU、LCU(CTB)、サブブロック、マクロブロック、タイル、またはスライス等、任意の部分領域(処理単位)が含まれるものとする。

<画像復号装置>

図10において、画像復号装置100は、復号部111、逆量子化部112、逆変換部113、演算部114、フレームメモリ115、および予測部116を備えている。なお、予測部116は、不図示のイントラ予測部、およびインター予測部を備えている。画像復号装置100は、符号化データ#1(bitstream)を復号することによって、動画像#2を生成するための装置である。

復号部111は、符号化データ#1を入力とし、シンタックステーブルの定義に沿って、符号化データ#1のビット列から、各シンタックス要素のシンタックス値を可変長復号する。さらに、シンタックス要素には、ヘッダ情報Hinfo、予測モード情報Pinfo、変換情報Tinfo、残差情報Rinfoなどの情報が含まれる。

VPS/SPS/PPS/スライスヘッダSHなどのヘッダ情報Hinfoには、画像サイズ(横幅PicWidth、縦幅PicHeight)、ビット深度(輝度bitDepthY, 色差bitDepthC)、CUサイズの最大値MaxCUSize/最小値MinCUSize、4分木分割(Quad-tree分割ともいう)の最大深度MaxQTDepth/最小深度MinQTDepth、2分木分割(Binary-tree分割)の最大深度MaxBTDepth/最小深度MinBTDepth、変換スキップブロックの最大値MaxTSSize(最大変換スキップブロックサイズともいう)、各符号化ツールのオンオフフラグ(有効フラグともいう)などを規定する情報が含まれる。

例えば、ヘッダ情報Hinfoに含まれる符号化ツールのオンオフフラグとしては、以下に示す変換、量子化処理に関わるオンオフフラグがある。なお、符号化ツールのオンオフフラグは、該符号化ツールに関わるシンタックスが符号化データ中に存在するか否かを示すフラグとも解釈することができる。また、オンオフフラグの値が1(真)の場合、該符号化ツールが使用可能であることを示し、オンオフフラグの値が0(偽)の場合、該符号化ツールが使用不可であることを示す。なお、フラグ値の解釈は逆であってもよい。

適応プライマリ変換有効フラグapt_enabled_flag(adaptive_primary_transform_enabled_flag、adaptive_pt_enabled_flag、またはamt_enabled_flagとも称する)は、変換処理及びその逆処理の1つとして、適応的なプライマリ変換の選択が可能な符号化ツール(適応プライマリ変換ともいう)が使用可能か示すフラグである。

セカンダリ変換有効フラグst_enabled_flagは、変換処理およびその逆処理の1つとして、セカンダリ変換/逆セカンダリ変換をする符号化ツールが使用可能か否かを示すフラグである。

変換量子化バイパス有効フラグtransquant_bypass_enabled_flagは、変換・量子化、およびその逆処理の1つとして、変換と量子化/逆量子化と逆変換をスキップする符号化ツールが使用可能か否かを示すフラグである。

変換スキップフラグ有効フラグts_enabled_flagは、変換処理およびその逆処理の1つとして、2次元変換スキップや1次元変換スキップが使用可能か否かを示すフラグである。その2次元変換スキップは、プライマリ変換とセカンダリ変換を含む直交変換およびその逆処理(逆直交変換)をスキップする符号化ツールである。また、1次元変換スキップは、プライマリ変換のうち、水平方向または垂直方向のプライマリ変換、および、それに対応する逆変換(逆プライマリ変換)、並びに、セカンダリ変換とその逆セカンダリ変換をスキップする符号化ツールである。

予測モード情報Pinfoには、さらに、処理対象PUのPUサイズ(予測ブロックサイズ)PUSize、イントラ予測モード情報IPinfo(例えば、JCTVC-W1005, 7.3.8.5 Coding Unit syntax中のprev_intra_luma_pred_flag, mpm_idx, rem_intra_pred_mode)、動き予測情報MVinfo(例えば、JCTVC-W1005, 7.3.8.6 Prediction Unit Syntaxを参照, merge_idx, merge_flag, inter_pred_idc, ref_idx_LX, mvp_lX_flag, X={0,1}, mvd)等が含まれる。

また、変換情報Tinfoには、例えば、処理対象変換ブロックの横幅サイズTBWidthおよび縦幅TBHeight、(逆)変換および(逆)量子化の処理をスキップするか否かを示す変換量子化バイパスフラグtransquant_bypass_flag、2次元変換スキップや1次元変換スキップなどの各種変換スキップモードを指定する変換スキップ識別子ts_idx、対象TUにおいて適応プライマリ変換を適用するかを示す適応プライマリ変換フラグapt_flag、垂直方向および水平方向の(逆)プライマリ変換にどの(逆)プライマリ変換を適用するかを示すプライマリ変換識別子pt_idx、どの(逆)セカンダリ変換を適用するかを示すセカンダリ変換識別子st_idx(dnsst_idx、nsst_idx、またはrot_idxとも称する)、スキャン識別子scanIdx、量子化パラメータqp、量子化マトリックスscaling_matrix等のシンタックスが含まれる。なお、処理対象変換ブロックの横幅サイズTBWidthおよび縦幅TBHeightの代わりに、2を底とする各TBWidth、TBHeightの対数値log2TBWidth、log2TBHeightが含まれるようにしてもよい。

残差情報Rinfoには、例えば、ラスト非ゼロ係数X座標(last_sig_coeff_x_pos)、ラスト非ゼロ係数Y座標(last_sig_coeff_y_pos)、サブブロック非ゼロ係数有無フラグ(coded_sub_block_flag)、非ゼロ係数有無フラグ(sig_coeff_flag)、非ゼロ係数のレベルが1より大きいかを示すフラグ(gr1_flag)(GR1フラグとも称する)、非ゼロ係数のレベルが2より大きいかを示すフラグ(gr2_flag)(GR2フラグとも称する)、非ゼロ係数の正負を示す符号(sign_flag)(サイン符号とも称する)、並びに、非ゼロ係数の残余レベル(coeff_abs_level_remaining)(非ゼロ係数残余レベルとも称する)等が含まれるようにしてもよい。

復号部111は、残差情報Rinfoを参照して、各変換ブロック内の各係数位置の量子化変換係数レベルlevelを導出する。復号部111は、復号して得た予測モード情報Pinfo、量子化変換係数レベルlevel、変換情報Tinfoを各ブロックへ供給する。例えば、復号部111は、予測モード情報Pinfoを予測部24に供給し、量子化変換係数レベルlevelを、逆量子化部22に供給し、変換情報Tinfoを、逆変換部113および逆量子化部112に供給する。

逆量子化部112は、変換情報Tinfo、及び量子化変換係数レベルlevelを入力とし、変換情報Tinfoに基づいて、量子化変換係数レベルlevelの値をスケーリング(逆量子化)し、逆量子化後の変換係数Coeff_IQを逆変換部113へ出力する。

逆変換部113は、変換係数Coeff_IQおよび変換情報Tinfoを入力とし、変換情報Tinfoに基づいて、変換係数Coeff_IQに対して、逆変換を適用し、予測残差D'を導出し、それを演算部114へ出力する。逆変換部113の詳細については、後述する。

演算部114は、予測残差D'と、予測部116より供給される予測画像Pとを入力とし、以下の式(9)に示すように予測残差D'と予測残差D'に対応する予測画像P(予測信号)とを加算し、局所復号画像Recを導出し、それをフレームメモリ115または画像復号装置100の外部に供給する。

Rec = D' + P

フレームメモリ115は、演算部114より供給される局所復号画像Recを入力とし、ピクチャ単位毎の復号画像を再構築して、フレームメモリ115内のバッファへ格納する。フレームメモリ115は、予測部116の予測モード情報Pinfoによって指定される復号画像を参照画像としてバッファより読み出し、予測部116へ供給する。また、フレームメモリ115は、復号画像の生成に係るヘッダ情報Hinfo、予測モード情報Pinfo、変換情報Tinfoなどをフレームメモリ内のバッファへ格納するようにしても良い。

予測部116は、予測モード情報Pinfoを入力とし、予測モード情報Pinfoによって指定される予測方法により、予測モード情報PInfoによって指定される、フレームメモリ115に格納された復号画像を参照画像として予測画像Pを生成し、演算部114へ出力する。

図11は、図10の画像復号装置100が備える逆変換部113の主な構成例を示すブロック図である。図11に示されるように、逆変換部113は、スイッチ121、逆セカンダリ変換部122、および逆プライマリ変換部123から構成される。

スイッチ121は、変換係数Coeff_IQ、及び変換スキップ識別子ts_idxを入力とする。変換スキップ識別子ts_idxの値がNO_TS(=0)、または、1D_H_TS(=2)、または、1D_V_TS(=3)の場合(変換スキップを適用しない、あるいは、水平・垂直方向のいずれか一方に対して1次元変換スキップを適用することを示す場合)、逆セカンダリ変換部122へ変換係数Coeff_IQを出力する。また、変換スキップフラグts_idxの値が2D_TS(=1)の場合(2次元変換スキップを適用することを示す場合)、逆セカンダリ変換部122、及び逆プライマリ変換部123をスキップし、変換係数Coeff_IQを予測残差D'として出力する。

例えば、変換スキップ識別子ts_idxが2D_TS(=1)であって、逆変換部113へ入力する変換係数Coeff_IQが、4x4行列Coeff_IQ = [[255, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0]]である場合、スイッチ121は、変換係数Coeff_IQを、予測残差D'として出力する。すなわち、予測残差D'=[[255, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0]]となる。従って、逆セカンダリ変換、及び逆プライマリ変換をスキップすることができる。特に、2次元変換スキップを適用するのが望ましい非ゼロ係数の数が少ない疎な残差信号に対して、逆変換の処理量の低減、及び符号化効率の向上した逆変換処理を行うことができる。

逆セカンダリ変換部122は、セカンダリ変換識別子st_idx、変換係数のスキャン方法を示すスキャン識別子scanIdx、及び変換係数Coeff_IQを入力とし、逆セカンダリ変換後の変換係数Coeff_IS(プライマリ変換係数ともいう)を導出し、逆プライマリ変換部123に供給する。より具体的には、セカンダリ変換識別子st_idxが、逆セカンダリ変換を適用することを示す場合(st_idx>0)、逆セカンダリ変換部122は、変換係数Coeff_IQに対して、セカンダリ変換識別子st_idxに対応する逆セカンダリ変換の処理を実行し、逆セカンダリ変換後の変換係数Coeff_ISを出力する。セカンダリ変換識別子st_idxが、逆セカンダリ変換を適用しないことを示す場合(st_idx==0)、逆セカンダリ変換をスキップし、変換係数Coeff_IQを逆セカンダリ変換後の変換係数Coeff_ISとして出力する。

逆プライマリ変換部123は、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、変換スキップ識別子ts_idx及び逆セカンダリ変換後の変換係数Coeff_ISを入力とする。逆プライマリ変換部123は、予測モード情報PInfo、変換スキップ識別子及び各プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flagで指定される逆プライマリ水平変換の行列IPThor(=PThorT)、及び逆プライマリ垂直変換の行列IPTver(=PTverT)を選択し、逆セカンダリ後の変換係数Coeff_IS(プライマリ変換係数Coeff_Pとも称する)に対して、選択された各方向の逆プライマリ変換の行列により、逆プライマリ水平変換、及び逆プライマリ垂直変換をして、逆プライマリ変換後の予測残差D'を導出し、出力する。

図11に示されるように、逆プライマリ変換部123は、逆プライマリ変換選択部131、スイッチ132、逆プライマリ垂直変換部133、スイッチ134、および逆プライマリ水平変換部135を有する。

逆プライマリ変換選択部131は、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、及び変換スキップ識別子ts_idxを入力とし、予測モード情報PInfo、変換スキップ識別子ts_idx、プライマリ水平変換指定フラグpt_hor_flag及びプライマリ垂直変換指定フラグpt_ver_flagで指定される逆プライマリ水平変換の行列IPThor(=PThorT)、及び逆プライマリ垂直変換の行列IPTver(=PTverT)を、逆プライマリ変換選択部131の内部メモリ(不図示)より読み出し、それぞれ、逆プライマリ水平変換部135、逆プライマリ垂直変換部133に供給する。

より具体的には、適応プライマリ変換フラグapt_flag(CUプライマリ変換フラグcu_pt_flagとも呼ぶ)が1(真)の場合、逆プライマリ変換選択部131は、例えば、図1の表に示される変換セット識別子TransfromSetIdx=0...2の3つの変換セットTransformSetから、水平方向及び垂直方向のそれぞれについて、プライマリ変換の候補となる直交変換を含む変換セットTransformSetを、図3に示されるモード情報と変換セットの対応表(イントラ予測モード情報)に基づいて選択する。なお、図3において、イントラ予測モード番号35をインター予測(Inter)、あるいはイントラブロックコピー(IBC;Intra Block Copy)を示すモードとして扱ってもよい。

例えば、以下の条件式(10)のように、各変換セットTransformSet{H,V}に対して、対応する変換セットTransformSetを指定する変換セット識別子TransformSetIdxを設定するように実施される。

if (apt_flag)

ここで、TransformSetHは、プライマリ水平変換PThorの変換セットを示し、TransormSetVは、プライマリ垂直変換PTverの変換セットを示し、ルックアップテーブルLUT_IntraModeToTransformSetは、図3の対応表である。ルックアップテーブルLUT_IntraModeToTransformSet[][]の1番目の配列は、イントラ予測モードIntraModeを引数とし、2番目の配列は、{H=0, V=1}を引数とする。例えば、イントラ予測モード番号9 (IntraMode==9)の場合、プライマリ水平変換PThorの変換セットTransformSetH (プライマリ水平変換セットとも呼ぶ)として、図1の表に示される変換セット識別子TransformSetIdx=0の変換セットが選択され、プライマリ垂直変換PTverの変換セットTransformSetV(プライマリ垂直変換セットとも呼ぶ)として、図1に示される変換セット識別子TransformSetIdx=2の変換セットが選択される。また、適応プライマリ変換フラグamt_flagが0(偽)の場合、逆プライマリ変換選択部131は、図1の表に示される変換セット識別子TransfromSetIdx=3(所定値)の変換セットTransformSetを、プライマリ変換の候補となる直交変換を含む変換セットとして選択する。

さらに、逆プライマリ変換選択部131は、各水平/垂直方向毎に、選択された変換セットTransformSetから、逆プライマリ変換に用いる直交変換を、おのおの、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagによって選択する。

例えば、以下の条件式(11)のように、プライマリ水平変換指定フラグpt_hor_flagが-1の場合、1次元変換スキップに対応する行列IDTを選択し、プライマリ水平変換指定フラグpt_hor_flagが-1以外の場合、プライマリ水平変換セットTransformSetHとプライマリ水平変換指定フラグpt_hor_flagを引数として、図1に示される変換セットの定義表(LUT_TransformSetToTransformType)から導出する。

if ( pt_hor_flag!=-1)

例えば、イントラ予測モード番号9(IntraMode==9)の場合の、逆プライマリ水平変換を例にすると、プライマリ水平変換セットTransformSetHの変換セット識別子の値は0であるため、図1の変換セット定義表LUT_TransformSetToTransformType上で変換セット識別子TransformSetIdx==0である変換セットから逆プライマリ水平変換が選択される。すなわち、プライマリ水平変換指定フラグpt_hor_flag==-1の場合、逆プライマリ水平変換IPThorとしてIDTが選択され、プライマリ水平変換指定フラグpt_hor_flag==0の場合、逆プライマリ水平変換IPThorとして、DST-VIIが選択され、プライマリ水平変換指定フラグpt_hor_flagが1の場合、逆プライマリ水平変換IPThorとして、DCT-VIIIが選択される。

同様にして、逆プライマリ垂直変換についても、以下の条件式(12)のように、プライマリ垂直変換指定フラグpt_ver_flagが-1の場合、1次元変換スキップに対応する行列IDT(単位行列)を選択し、プライマリ垂直変換指定フラグpt_ver_flagが-1以外の場合、プライマリ垂直変換セットTransformSetVとプライマリ垂直変換指定フラグpt_ver_flagを引数として、図1に示される変換セットの定義表(LUT_TransformSetToTransformType)から導出する。

if ( pt_ver_flag!=-1)

なお、上述の式(11)および式(12)では、pt_{hor,ver}_flag==-1の場合、条件分岐によりIDTを設定しているが、ルックアップテーブルLUT_TransformSetToTransformType[][]を参照して設定するようにしてもよい。この場合、ルックアップテーブルLUT_TransformSetToTransformType[ 0...3 ][ - 1]の要素の値をIDTとすればよい。なお、この例では、pt_{hor, ver}_flag==-1は1次元変換スキップを表す値としているが、値は実施可能な範囲で自由に変更可能である。また、図1の変換セット識別子とpt_{hor,ver}_flagの値の組み合わせは、実施可能な範囲で自由に変更してよい。例えば、pt_{hor,ver}_flag==1の場合に、変換セット識別子の値によらず、DST-VIIを設定し、pt_{hor,ver}_flag==0の場合に、変換セット識別子0…3の順に、それぞれ、DCT-VIII,DST-I, DCT-V, DST-VIIを設定してもよい。また、変換セット識別子0…2の順は、実施可能な範囲で自由に入れ替えてもよい。また、逆プライマリ変換選択部131は、イントラ予測モード情報IPinfoの代わりに、動き予測情報MVinfoとプライマリ水平変換指定フラグpt_hor_flagとプライマリ垂直変換指定フラグpt_ver_flagに応じて、逆プライマリ水平変換IPThor、及び逆プライマリ垂直変換IPTverを選択してもよい。

その後、逆プライマリ変換選択部131は、逆プライマリ水平変換IPThor、及び逆プライマリ垂直変換IPTverに対応する直交変換の行列を、逆プライマリ変換部123が保持するバッファ(不図示)より読み出し、逆プライマリ垂直変換、逆プライマリ水平変換へ対応する行列を供給する。

スイッチ132は、逆セカンダリ変換後の変換係数Coeff_IS(プライマリ変換係数Coeff_Pとも表記する)、及び変換スキップ識別子ts_idxを入力とする。変換スキップ識別子ts_idxの値が1D_V_TS(=3)、すなわち、垂直方向の1次元変換をスキップすること(ts_idx==1D_V_TS)((逆)プライマリ垂直変換をスキップすること)を示す場合、スイッチ132は、逆プライマリ垂直変換部133の処理をスキップし、プライマリ変換係数Coeff_ISを逆プライマリ垂直変換後の変換係数Coeff_IPverとして外部へ出力する。また、変換スキップ識別子ts_idxの値が1D_V_TS(=3)以外の場合(ts_idx!=1D_V_TS)((逆)プライマリ垂直変換をスキップしないことを示す場合)、スイッチ132はプライマリ変換係数Coeff_ISを外部へ出力する。

逆プライマリ垂直変換部133は、変換ブロック毎に、逆セカンダリ変換後の変換係数Coeff_ISと逆プライマリ垂直変換IPTverの行列を入力とし、以下の式(13)に示す通り行列演算を行い、その結果を逆プライマリ垂直変換後の変換係数Coeff_IPverとして出力する。なお、逆プライマリ垂直変換IPTverは、変換基底を列ベクトルとして有するプライマリ垂直変換PTverの逆変換であり、前記プライマリ垂直変換PTverを転置した行列PTverTで表される。

Coeff_IPver = (IPTver・Coeff_IS) >> s1

ここで、演算子"・"は行列積(inner product)を表し、演算子"T"は、転置行列の操作を表し、演算子">>"は要素毎に右シフト演算を行う操作を表す。式(13)によれば、変換係数Coeff_IPverの各値は、変換係数Coeff_ISとプライマリ垂直変換の転置行列PTverT(=IPTver)との行列積の要素毎に対して、所定のスケーリングパラメータs1によって右シフト演算することで得られる。なお、スケーリングパラメータs1は、IPTver・Coeff_ISの行列演算結果を、中間バッファのビット深度に収まるよう正規化するために用いる。スケーリングパラメータs1の値は、例えば、以下の式(14)に示すように中間バッファのビット深度BitDepthbuffと、IPTver・Coeff_ISの行列演算のビット深度のワーストケースMaxBitDepth(IPTver・Coeff_IS)から定まる。

s1 = max(0, MaxBitDepth(IPTver・Coeff_IS) - BitDpethbuff)

例えば、IPTver・Coeff_ISの値域が、-2**22乃至2**22 - 1である場合、すなわち、MaxBitDepth(IPTver・Coeff_IS)のビット深度が23bitであって、中間バッファに格納可能な値の値域が、-2**15乃至2**15 - 1である場合、すなわち中間バッファのビット深度が16bitの場合、スケーリングパラメータs1は、s1 = 7bit( = max(0, 23-16) = max(0, 7))となる。

また、MaxBitDepth(IPTver・Coeff_IS)のビット深度が23bitであって、中間バッファに格納可能な値の値域が、-2**31乃至2**31 - 1である場合、すなわち、中間バッファのビット深度が32bitの場合、スケーリングパラメータs1は、s1 = 0bit(=max(0, 23-32)=max(0,-9))となる。スケーリングパラメータs1が0であるということは、中間バッファのビット深度の値が十分に大きいため、IPTver・Coeff_ISの行列積の各要素値を正規化せずとも、中間バッファにオーバフローせずに格納することが出来ることを表す。なお、スケーリングパラメータs1は、IPTver・Coeff_ISの値域が既知であると仮定して、予め定めた固定値としてもよい。

また、上述の式(13)において、右シフト演算によるクリップ誤差を小さくするために、行列積の後、所定のオフセット値o1を要素毎に加算するようにしてもよい。このとき、オフセット値o1は、スケーリングパラメータs1を用いて、以下の式(15)により表される。

o1 = ( s1>0 ? 1<<(s1-1) : 0 )

スイッチ134は、逆プライマリ垂直変換後の変換係数Coeff_IPver、及び変換スキップ識別子ts_idxを入力とする。変換スキップ識別子ts_idxの値が1D_H_TS(=2)、すなわち、水平方向の1次元変換をスキップすること(ts_idx==1D_H_TS)((逆)プライマリ水平変換をスキップすること)を示す場合、スイッチ134は、逆プライマリ水平変換部135をスキップし、逆プライマリ垂直変換後の変換係数Coeff_IPverを予測残差D'として外部へ出力する。また、変換スキップ識別子ts_idxの値が1D_H_TS(=2)以外の場合(ts_idx!=1D_H_TS)((逆)プライマリ水平変換をスキップしないことを示す場合)、スイッチ134は、逆プライマリ垂直変換後の変換係数Coeff_IPverを逆プライマリ水平変換部135へ出力する。

逆プライマリ水平変換部135は、変換ブロック毎に、逆プライマリ垂直変換後の変換係数Coeff_IPverと逆プライマリ水平変換IPThorの行列を入力とし、以下の式(16)に示す通り行列演算を行い、その結果を予測残差D'として出力する。なお、逆プライマリ水平変換IPThorは、変換基底を行ベクトルとして有するプライマリ水平変換PThorの逆変換であり、前記プライマリ水平変換PThorを転置した行列PThorTで表される。

D' = (Coeff_IPver・IPThor) >> s2

ここで、演算子"・"は行列積(inner product)を表し、演算子"T"は、転置行列の操作を表し、演算子">>"は要素毎に右シフト演算を行う操作を表す。この式(16)によれば、予測残差D'の各値は、変換係数Coeff_IPverとプライマリ水平変換の転置行列PThorT(=IPTver)との行列積の要素毎に対して、所定のスケーリングパラメータs2によって右シフト演算することで得られる。なお、スケーリングパラメータs2は、Coeff_IPver・IPThorの行列演算結果を、所望のビット深度に収まるよう正規化するために用いる。スケーリングパラメータs2の値は、所望のビット深度BitDepthoutと、Coeff_IPver・IPThorの行列演算のビット深度のワーストケースMaxBitDepth(Coeff_IPver・IPThor)から、以下の式(17)により定まる。

s2 = max(0, MaxBitDepth(Coeff_IPver・IPThor) - BitDpethout)

例えば、Coeff_IPver・IPThorの値域が、-2**22 乃至 2**22 - 1である場合、すなわち、MaxBitDepth(Coeff_IPver・IPThor)のビット深度が23bitであって、所望ビット深度のとき取りえる値の値域が、-2**15乃至2**15 - 1である場合、すなわち所望ビット深度が16bitの場合、スケーリングパラメータs2は、s2 = 7bit( = max(0, 23-16) = max(0, 7))となる。

また、MaxBitDepth(Coeff_IPver・IPThor)のビット深度が23bitであって、所望ビット深度のとき取りえる値の値域が、-2**31乃至2**31 - 1である場合、すなわち、所望ビット深度が32bitの場合、スケーリングパラメータs2は、s2 = 0bit(=max(0, 23-32)=max(0,-9))となる。スケーリングパラメータs2が0であるということは、所望ビット深度の値が十分に大きいため、Coeff_IPver・IPThorの行列積の各要素値が正規化せずとも、所望ビット深度内に収まることを表す。

なお、式(16)において、右シフト演算によるクリップ誤差を小さくするために、行列積の後、所定のオフセット値o2を要素毎に加算するようにしてもよい。このとき、オフセット値o2は、スケーリングパラメータs2を用いて、以下の式(18)により表される。

O2 = ( s2>0 ? 1<<(s2-1) : 0 )

以上のように、逆プライマリ変換部123は、水平方向、または垂直方向の1次元変換をスキップことが望ましい残差信号に対して、逆プライマリ変換の処理量の低減、及びエナジーコンパクションの低下を防止し、符号化効率の向上した逆プライマリ変換処理を行うことができる。

特に、水平方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、水平方向の1次元変換をスキップし、垂直方向に1次元変換をすることで、2次元直交変換をする場合と比較して、垂直方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率の向上を実現させることができる。

同様に、垂直方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、垂直方向の1次元変換をスキップし、水平方向に1次元変換をすることで、2次元直交変換をする場合と比較して、水平方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率の向上を実現させることができる。

<画像復号処理の流れ>

画像復号処理が開始されると、ステップS101において、復号部111は、画像復号装置100に供給されるビットストリーム(符号化データ)を復号し、ヘッダ情報Hinfo、予測モード情報Pinfo、変換情報Tinfo、残差情報Rinfo、量子化変換係数レベルlevel等の情報を得る。

ステップS102において、逆量子化部112は、ステップS101の処理により得られた量子化変換係数レベルlevelを逆量子化して変換係数Coeff_IQを導出する。この逆量子化は、後述する画像符号化処理において行われる量子化の逆処理であり、その画像符号化処理において行われる逆量子化と同様の処理である。

ステップS103において、逆変換部113は、ステップS102の処理により得られた変換係数Coeff_IQを逆変換し、予測残差D'を導出する。この逆変換は、後述する画像符号化処理において行われる変換処理の逆処理であり、その画像符号化処理において行われる逆変換と同様の処理である。

ステップS104において、予測部116は、予測モード情報PInfoに基づいて、符号化の際の予測と同一の予測モードで予測を行い、予測画像生成する。

ステップS105において、演算部114は、ステップS103の処理により得られた予測残差D'に、ステップS104の処理により得られた予測画像を加算し、復号画像を得る。

ステップS106において、演算部114は、ステップS105の処理により得られた復号画像を画像復号装置100の外部に出力する。

ステップS107において、フレームメモリ115は、ステップS105の処理により得られた復号画像を記憶する。

ステップS107の処理が終了すると、画像復号処理が終了される。

<逆変換の処理の流れ>

また、ステップS121において、変換スキップ識別子ts_idxが2D_TSでない(2次元変換スキップ以外のモード)、かつ、変換量子化バイパスフラグが0(偽)であると判定された場合、スイッチ121により変換係数Coeff_IQが逆セカンダリ変換部122に供給され、処理はステップS122に進む。

ステップS122において、逆セカンダリ変換部122は、入力された変換係数Coeff_IQ'に対して、セカンダリ変換識別子st_idxに基づいて、逆セカンダリ変換を行い、プライマリ変換係数Coeff_ISを導出し、出力する。

ステップS123において、逆プライマリ変換選択部131は、逆プライマリ変換選択処理を行い、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、及び変換スキップ識別子ts_idxを参照して、逆プライマリ水平変換IPThor、及び逆プライマリ垂直変換IPTverを選択する。

ステップS124において、スイッチ132は、変換スキップ識別子ts_idxが1D_V_TS(垂直方向の1次元変換スキップのモード)であるか否か(ts_idx==1D_V_TS)を判定する。変換スキップ識別子ts_idxが1D_V_TSでない場合、処理はステップS125に進む。

ステップS125において、逆プライマリ垂直変換部133は、変換ブロック毎に、逆セカンダリ変換後の変換係数Coeff_ISと逆プライマリ垂直変換IPTverの行列を入力とし、行列演算を行い、その結果を逆プライマリ垂直変換後の変換係数Coeff_IPverとして出力する。ステップS125の処理が終了すると処理はステップS126に進む。

また、ステップS124において、変換スキップ識別子ts_idxが1D_V_TSの場合、ステップS125の処理が省略され、処理はステップS126に進む。

ステップS126において、スイッチ134は、変換スキップ識別子ts_idxが1D_H_TS(水平方向の1次元変換スキップのモード)であるか否か(ts_idx==1D_H_TS)を判定する。変換スキップ識別子ts_idxが1D_H_TSでないと判定された場合、処理はステップS127に進む。

ステップS127において、逆プライマリ水平変換部135は、変換ブロック毎に、逆プライマリ垂直変換後の変換係数Coeff_IPverと逆プライマリ水平変換IPThorの行列を入力とし、行列演算を行い、その結果を予測残差D'として出力する。ステップS127の処理が終了すると逆変換処理が終了し、処理は図12に戻る。

また、ステップS126において、変換スキップ識別子ts_idxが1D_H_TSであると判定された場合、ステップS127の処理が省略され、逆変換処理が終了し、処理は図12に戻る。

以上において、逆プライマリ変換部123の処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。例えば、ステップS124およびステップS126の処理を省略し、ステップS123において変換スキップ識別子ts_idxが1D_V_TS(垂直方向の1次元変換スキップ)であるか否かを判定するようにしてもよい。そして、ステップS123において変換スキップ識別子ts_idxが1D_V_TSであると判定された場合、単位行列を逆プライマリ垂直変換IPTverとして選択し、ステップS125の処理が実行されるようにしてもよい。また、ステップS123において変換スキップ識別子ts_idxが1D_H_TSであると判定された場合、単位行列を逆プライマリ水平変換IPThorとして選択し、ステップS127の処理が実行されるようにしてもよい。

<逆プライマリ変換選択処理の流れ>

逆プライマリ変換選択処理が開始されると、ステップS141において、逆プライマリ変換選択部131は、適応プライマリ変換フラグapt_flagが1(真)であるか否かを判定する。適応プライマリ変換フラグapt_flagが1(真)であると判定された場合、処理はステップS142に進む。ステップS142において、逆プライマリ変換選択部131は、予測モード情報PInfoに基づいて、逆プライマリ垂直変換および逆プライマリ水平変換のそれぞれについて、上述の式(10)に従って変換セットを選択する。ステップS142の処理が終了すると、処理はステップS144に進む。

また、ステップS141において、適応プライマリ変換フラグapt_flagが0(偽)であると判定された場合、処理はステップS143に進む。ステップS143において、逆プライマリ変換選択部131は、所定の変換セットを選択する。ステップS143の処理が終了すると、処理はステップS144に進む。

ステップS144において、逆プライマリ変換選択部131は、水平変換セット識別子TransformSetH、及びプライマリ水平変換指定フラグpt_hor_flagを参照して、上述の式(11)に従って、逆プライマリ水平変換IPThorとして適用する直交変換を選択する。

ステップS145において、逆プライマリ変換選択部131は、垂直変換セット識別子TransformSetV、及びプライマリ垂直変換指定フラグpt_ver_flagを参照して、上述の式(12)に従って、逆プライマリ垂直変換IPTverとして適用する直交変換を選択する。

ステップS145の処理が終了すると、逆プライマリ変換選択処理が終了し、処理は図13に戻る。

なお、この逆プライマリ変換選択処理は、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。例えば、ステップS144の処理において、変換スキップ識別子ts_idx==TS_1D_H_TSの場合(水平方向の1次元変換をスキップする場合)、明示的に1次元変換スキップを示す直交変換IDT(単位行列)が選択されないようにしてもよい。同様にして、ステップS145の処理において、変換スキップ識別子ts_idx==TS_1D_V_TSの場合(垂直方向の1次元変換をスキップする場合)、明示的に1次元変換スキップを示す直交変換IDT(単位行列)が選択されないようにしてもよい。

以上のように各処理を実行することにより、画像復号装置100は、変換スキップを適用するのが望ましい残差信号に対して、逆変換の処理量の低減、及びエナジーコンパクションの低下を抑制することができ、符号化効率の向上を実現することができる。

より具体的には、逆変換部113は、水平方向または垂直方向の1次元変換をスキップすることが望ましい残差信号に対して、逆プライマリ変換の処理量の低減やエナジーコンパクションの低下を抑制することができ、符号化効率の向上を実現することができる。特に、水平方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、水平方向の1次元変換をスキップし、垂直方向に1次元変換をすることで、2次元直交変換をする場合と比較して、垂直方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率の向上を実現させることができる。同様に、垂直方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、垂直方向の1次元変換をスキップし、水平方向に1次元変換をすることで、2次元直交変換をする場合と比較して、水平方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率の向上を実現させることができる。

<2.第2の実施の形態>

pt_hor_flag = pt_idx & 0x01

すなわち、プライマリ変換識別子pt_idxは、2ビットの値をとり、上位1ビットがプライマリ垂直変換指定フラグpt_ver_flagに相当し、下位1ビットがプライマリ水平変換指定フラグpt_hor_flagに相当する。なお、符号化側においては、このプライマリ変換識別子pt_idxの導出は、以下の式(20)のように行われる。

pt_idx = ((pt_ver_flag)<<1) + pt_hor_flag

従って、従来技術JEM3に対して、第1の実施の形態において説明した通り下記(1)乃至(3)の変更を加えた場合、変換ブロック単位で復号された変換スキップ識別子ts_idxが、1D_H_TSの場合、プライマリ水平変換指定フラグpt_hor_flagは使用されないため、この情報を符号化/復号するのは冗長である。また、変換スキップ識別子ts_idxが1D_V_TSを示す場合、プライマリ垂直変換指定フラグpt_ver_flagは使用されないため、この情報を符号化/復号するのは冗長である。

(1)変換スキップフラグts_flagを変換スキップ識別子ts_idxへ拡張する。

従って、プライマリ変換識別子pt_idxを効率良く符号化/復号するために、下記のような変更を加えるようにしてもよい。

(1)変換スキップ識別子ts_idx = NO_TSの場合、復号側では、上述の式(19)の通り、プライマリ変換識別子pt_idxから、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagを導出するようにする。符号化側では、式(20)の通り、プライマリ水平変換指定フラグpt_hor_flag及びプライマリ垂直変換指定フラグpt_ver_flagよりプライマリ変換識別子pt_idxを導出するようにする。

(2)変換スキップ識別子ts_idxが1D_H_TSの時、復号側では、以下の式(21)の通り、プライマリ垂直変換指定フラグpt_ver_flag = pt_idx、プライマリ水平変換指定フラグpt_hor_flag = - 1(所定値)として導出するようにする。符号化側では、以下の式(22)の通り、プライマリ変換識別子pt_idx = pt_ver_flagとして導出するようにする。

pt_ver_flag = pt_idx

(3)変換スキップ識別子ts_idxが1D_V_TSの時、復号側では、以下の式(23)の通り、プライマリ水平変換指定フラグpt_hor_flag = pt_idx、プライマリ垂直変換指定フラグpt_ver_flag = - 1(所定値)として導出するようにする。符号化側では、以下の式(24)の通り、プライマリ変換識別子pt_idx = pt_hor_flagとして導出するようにする。

pt_hor_flag = pt_idx

(4)変換スキップ識別子ts_idxが2D_TSの時、復号側では、以下の式(25)の通り、プライマリ水平変換指定フラグpt_hor_flag=-1(所定値)、及びプライマリ垂直変換指定フラグpt_ver_flag=-1(所定値)として設定されるようにする。符号化側では、プライマリ変換識別子pt_idxの符号化は省略されるようにする。

上記の変更をすることで、変換スキップ識別子ts_idxが1D_H_TS、または1D_V_TSの場合、プライマリ変換識別子pt_idxは、1ビットのbin列として、算術復号/算術符号化されるため、2ビットのbin列として算術復号/算術符号化する場合より、復号/符号化対象となるbin列を削減することができる。従って、符号量の増大を抑制することでき、符号化効率の向上を実現することができる。

また、セカンダリ変換に関して、セカンダリ変換は、2次元直交変換が適用された変換係数のエナジーコンパクションを向上させるために設計された変換である。従って、2次元変換スキップや1次元変換スキップが適用された変換係数に対して、セカンダリ変換を適用することは逆に符号化効率を低下させる可能性がある。そこで、変換スキップ識別子ts_idxが2D_TS、1D_H_TS、または1D_V_TSの場合、逆セカンダリ変換をスキップするように変更する。この場合、(逆)セカンダリ変換の制御パラメータであるセカンダリ変換識別子st_idxを符号化/復号するのは冗長である。

そこで、変換スキップ識別子ts_idxが2D_TS、1D_H_TS、または1D_V_TSの場合、セカンダリ変換識別子st_idxの復号を省略し、かつ、セカンダリ変換識別子st_idxの値を、セカンダリ変換をしないことを示す値(0)へ推定するように変更してもよい。このようにすることで、セカンダリ変換識別子st_idxの復号に係る処理量の増大を抑制することができる。また、2次元変換スキップ、または1次元変換スキップが適用された変換係数に対して、セカンダリ変換を適用しないようにするため、符号化効率の低下を防止することができる。

<変換スキップ識別子ts_idxの復号>

変換スキップ有効フラグ復号部151は、変換スキップ有効フラグts_enabled_flagの復号に関する処理を行う。最大変換スキップブロックサイズ復号部152は、最大変換スキップブロックサイズMaxTSSizeの復号に関する処理を行う。変換量子化バイパスフラグ復号部153は、変換量子化バイパスフラグtransquant_bypass_flagの復号に関する処理を行う。変換スキップ識別子復号部154は、変換スキップ識別子ts_idxの復号に関する処理を行う。

このような復号部111により図12のステップS101において実行される、変換スキップ識別子ts_idxに関する復号処理の流れの例を、図16のフローチャートを参照して説明する。

復号処理が開始されると、変換スキップ有効フラグ復号部151は、ステップS161において、符号化データ#1のビット列から変換スキップ有効フラグts_enabled_flagを復号し、ヘッダ情報Hinfoの一部として出力する。

ステップS162において、最大変換スキップブロックサイズ復号部152は、ヘッダ情報Hinfoに含まれる変換スキップ有効フラグts_enabled_flagが、1(真)であるか否かを判定する。変換スキップ有効フラグts_enabled_flagが1であると判定された場合、処理はステップS163に進む。

ステップS163において、最大変換スキップブロックサイズ復号部152は、符号化データ#1のビット列から最大変換スキップブロックサイズMaxTSSize (あるいは、2を底とする対数値log2MaxTSSize)を復号する。ステップS163の処理が終了すると、処理はステップS164に進む。また、ステップS162において、変換スキップ有効フラグts_enabled_flagが0と判定された場合、ステップS163の処理が省略され、処理はステップS164に進む。

ステップS164において、変換量子化バイパスフラグ復号部153は、符号化データ#1のビット列から変換量子化バイパスフラグtransquant_bypass_flagを復号し、変換情報Tinfoの一部として出力する。

ステップS165において、変換スキップ識別子復号部154は、変換情報Tinfoに含まれる変換量子化バイパスフラグtransquant_bypass_flagが1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1であると判定された場合、処理はステップS169に進む。また、ステップS165において、変換量子化バイパスフラグtransquant_bypass_flagが0であると判定された場合、処理はステップS166に進む。

ステップS166において、変換スキップ識別子復号部154は、ヘッダ情報HInfoに含まれる変換スキップ有効フラグts_enabled_flagが1(真)であるか否かを判定する。変換スキップ有効フラグts_enabled_flagが0であると判定された場合、処理はステップS169に進む。また、ステップS166において、変換スキップ有効フラグts_enabled_flagが1であると判定された場合、処理はステップS167に進む。

ステップS167において、変換スキップ識別子復号部154は、処理対象の変換ブロックのサイズTBSizeが最大変換スキップブロックサイズMaxTSSize以下であるか否か(条件式(TBSize<=MaxTSSize)の論理値が1(真)であるか否か)を判定する。なお、条件式(TBSize<=MaxTSSize)において、TBSizeは、以下の式(26)により導出する。式(26)の場合、変換ブロックの縦サイズTBHSize、横サイズTBWSizeのうち大きい値をTBSizeとする。

TBSize = max(TBWSize, TBHSize)

式(26)の代わりに、以下の式(27)を用いるようにしてもよい。式(27)の場合、変換ブロックの縦サイズTBHSizeと横サイズTBWSizeの乗算した値をTBSizeとする。

TBSize = TBWSize * TBHSize

式(26)および式(27)において、TBSize、TBWSize、TBHSizeを、2を底とする対数値log2TBSize、log2TBWSize、log2TBHSizeに置き換えてもよい。この場合、式(26)は以下の式(28)に置き換え、式(27)は以下の式(29)へ置き換える。なお、対数値を用いる場合は、上述の条件式(TBSize<=MaxTSSize)のTBSizeおよび最大変換スキップブロックサイズMaxTSSizeは、それぞれ対応する対数値log2TBSize、log2MaxTSSizeへ置き換えるものとする。

log2TBSize = max(log2TBWSize, log2TBHSize)

ステップS167において、処理対象の変換ブロックのサイズTBSizeが最大変換スキップブロックサイズMaxTSSizeより大きい(条件式(TBSize<=MaxTSSize)の論理値が0(偽)である)と判定された場合、処理はステップS169に進む。また、ステップS167において、処理対象の変換ブロックのサイズTBSizeが最大変換スキップブロックサイズMaxTSSize以下である(条件式(TBSize<=MaxTSSize)の論理値が1(真)である)と判定された場合、処理はステップS168に進む。

ステップS168において、変換スキップ識別子復号部154は、符号化データ#1のビット列から変換スキップ識別子ts_idxを復号し、変換情報Tinfoの一部として出力する。ステップS168の処理が終了すると、変換スキップ識別子に関する復号処理が終了し、処理は図12に戻る。

また、ステップS169において、変換スキップ識別子復号部154は、変換スキップ識別子ts_idxの復号を省略し、ts_idxの値がNO_TS(=0)である推定し、その値をts_idxへ設定する。すなわち、ts_idx = NO_TSとなる。ステップS169の処理が終了すると、変換スキップ識別子に関する復号処理が終了し、処理は図12に戻る。

ステップS165乃至ステップS169の各処理の疑似コードを記載したシンタックステーブルを図17に示す。図17において符号SYN11を付したif文の条件式(上から2行目)は、下記の条件式(30)のように表すことができ、これはすなわち、図16を参照して説明したステップS165乃至ステップS167の分岐判定と等価である。また、図16のステップS168の処理は、図17において符号SYN12を付したシンタックスts_flagの復号(符号化)処理と対応する。

論理値 = ( ts_enabled_flag &&

以上において、変換スキップ識別子ts_idxの復号に係る処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。また、条件式(30)は、実施可能な範囲で演算を変更可能である。

以上のように各処理を行うことにより、JEM3の場合と比較して、復号側において、変換ブロック単位で2次元変換スキップ、水平方向または垂直方向の1次元変換スキップを適応的に選択することができる。従って、従来よりも1次元変換スキップが有効な残差信号に対して、1次元変換スキップのモードにより復号することができるため、符号化効率の向上を実現することができる。

<プライマリ変換識別子pt_idxの復号について>

プライマリ変換有効フラグ復号部161は、プライマリ変換有効フラグpt_enabled_flagの復号に関する処理を行う。適応プライマリ変換フラグ復号部162は、プライマリ変換フラグpt_enabled_flagの復号に関する処理を行う。プライマリ変換識別子復号部163は、プライマリ変換識別子pt_idxの復号に関する処理を行う。

このような復号部111により図12のステップS101において実行される、プライマリ変換識別子pt_idxに関する復号処理の流れの例を、図19のフローチャートを参照して説明する。

復号処理が開始されると、プライマリ変換有効フラグ復号部161は、ステップS181において、符号化データ#1のビット列からプライマリ変換有効フラグpt_enabled_flagを復号し、ヘッダ情報Hinfoの一部として出力する。

ステップS182において、適応プライマリ変換フラグ復号部162は、ヘッダ情報Hinfoに含まれるプライマリ変換有効フラグpt_enabled_flagが1(真)であるか否かを判定する。プライマリ変換有効フラグpt_enabled_flagが0(偽)であると判定された場合、処理はステップS183に進む。

ステップS183において、適応プライマリ変換フラグ復号部162は、適応プライマリ変換フラグapt_flagの符号化を省略し、このフラグの値が0であると推定する。ステップS183の処理が終了すると、処理はステップS193に進む。

また、ステップS182において、プライマリ変換有効フラグpt_enabled_flagが1(真)であると判定された場合、処理はステップS184に進む。ステップS184において、適応プライマリ変換フラグ復号部162は、符号化データ#1のビット列から適応プライマリ変換フラグapt_flagを復号する。

ステップS185において、プライマリ変換識別子復号部163は、適応プライマリ変換フラグapt_flagが1(真)であるか否かを判定する。適応プライマリ変換フラグapt_flagが0(偽)であると判定された場合、処理はステップS193に進む。また、ステップS185において、適応プライマリ変換フラグapt_flagが1(真)であると判定された場合、処理はステップS186に進む。

ステップS186において、プライマリ変換識別子復号部163は、変換量子化バイパスフラグtransquant_bypass_flagが1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1(真)であると判定された場合、処理はステップS193に進む。また、ステップS186において、変換量子化バイパスフラグtransquant_bypass_flagが0(偽)であると判定された場合、処理はステップS187に進む。

ステップS187において、プライマリ変換識別子復号部163は、変換スキップ識別子ts_idxが2D_TS(2次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが2D_TSであると判定された場合、処理はステップS193に進む。また、ステップS187において、変換スキップ識別子ts_idxが2D_TS以外であると判定された場合、処理はステップS188に進む。

ステップS188において、プライマリ変換識別子復号部163は、変換ブロックの縦サイズ(TBHSize)および横サイズ(TBWSize)がいずれも最大適応プライマリ変換ブロックサイズMaxPTSize以下(max(TBHSize, TBWSize)<=MaxPTSize)であるか否かを判定する。変換ブロックの縦サイズおよび横サイズの内の少なくともいずれか一方が、最大適応プライマリ変換ブロックサイズMaxPTSizeより大きいと判定された場合、処理はステップS193に進む。また、ステップS188において、変換ブロックの縦サイズおよび横サイズが最大適応プライマリ変換ブロックサイズMaxPTSize以下であると判定された場合、処理はステップS189に進む。

ステップS189において、プライマリ変換識別子復号部163は、復号対象の変換ブロックが輝度成分であるか否かを判定する。輝度成分ではないと判定された場合、処理はステップS193に進む。また、ステップS189において、復号対象の変換ブロックが輝度成分であると判定された場合、処理はステップS190に進む。

ステップS190において、プライマリ変換識別子復号部163は、残差情報Rinfoを参照して、変換ブロック内に存在する非ゼロ変換係数の総数numSig(sig_coeff_flag==1の総数)を導出する。

ステップS191において、プライマリ変換識別子復号部163は、非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTH以上であるか否か(numSig>=ptNumSigTH)を判定する。非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTHより少ないと判定された場合、処理はステップS193に進む。また、ステップS191において、非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTH以上である(numSig>=ptNumSigTHを満たす)と判定された場合、処理はステップS192に進む。

ステップS192において、プライマリ変換識別子復号部163は、符号化データ#1のビット列からプライマリ変換識別子pt_idxを復号する。ステップS192の処理が終了すると処理はステップS193に進む。

ステップS193において、プライマリ変換識別子復号部163は、変換スキップ識別子ts_idx、及び復号済のプライマリ変換識別子pt_idxを参照して、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagを導出する。ステップS193の処理が終了すると、復号処理が終了し、処理は図12に戻る。

以上に説明したステップS185乃至ステップS192の各処理の疑似コードを記載したシンタックステーブルを図17に示す。図17において符号SYN13を付したif文の条件式(以下の条件式(31))は、ステップS185乃至ステップS192の分岐判定と等価である。ステップS192は、図17において符号SYN14を付したシンタックスpt_idxの復号処理と対応する。なお、式(31)では、ステップS188の条件は省略されている。ステップS188の条件を含む式は、式(32)で表される。

論理値 = ( apt_flag

以上において、プライマリ変換識別子pt_idxの復号に係る処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。

次に、図19のステップS193において実行される、プライマリ水平変換指定フラグpt_hor_flagと、プライマリ垂直変換指定フラグpt_ver_flagとの導出に関する処理(プライマリ垂直水平変換指定フラグ導出処理)について、図20のフローチャートを参照して説明する。

プライマリ垂直水平変換指定フラグ導出処理が開始されると、プライマリ変換識別子復号部163は、ステップS211において、変換スキップ識別子ts_idxがNO_TS (変換スキップでない)であるか否かを判定する。変換スキップ識別子ts_idxがNO_TSであると判定された場合、処理はステップS212に進む。

ステップS212において、プライマリ変換識別子復号部163は、上述の式(19)により、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換フラグpt_ver_flagを導出する。つまり、プライマリ変換識別子pt_idxが2ビットのbin列として処理され、その2ビットからプライマリ水平変換指定フラグpt_hor_flagおよびプライマリ垂直変換フラグpt_ver_flagが導出される。ステップS212の処理が終了すると、プライマリ垂直水平変換指定フラグ導出処理が終了し、処理は図19に戻る。

ステップS212において、変換スキップ識別子ts_idxがNO_TS以外であると判定された場合、処理はステップS213に進む。ステップS213において、プライマリ変換識別子復号部163は、変換スキップ識別子ts_idxが2D_ TS(2次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが2D_TSであると判定された場合、処理はステップS214に進む。

ステップS214において、プライマリ変換識別子復号部163は、上述の式(25)により、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換フラグpt_ver_flagを導出する。つまり、プライマリ変換識別子pt_idxの復号が省略され、プライマリ水平変換指定フラグpt_hor_flagおよびプライマリ垂直変換フラグpt_ver_flagが所定値にセットされる。ステップS214の処理が終了すると、プライマリ垂直水平変換指定フラグ導出処理が終了し、処理は図19に戻る。

ステップS213において、変換スキップ識別子ts_idxが2D_TS以外であると判定された場合、処理はステップS215に進む。ステップS215において、プライマリ変換識別子復号部163は、変換スキップ識別子ts_idxが1D_H_TS(水平方向の1次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが1D_H_TSであると判定された場合、処理はステップS216に進む。

ステップS216において、プライマリ変換識別子復号部163は、上述の式(21)により、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換フラグpt_ver_flagを導出する。つまり、プライマリ変換識別子pt_idxが1ビットのbin列として処理され、プライマリ水平変換指定フラグpt_hor_flagが所定値にセットされ、プライマリ垂直変換フラグpt_ver_flagがプライマリ変換識別子pt_idxの値にセットされる。ステップS216の処理が終了すると、プライマリ垂直水平変換指定フラグ導出処理が終了し、処理は図19に戻る。

ステップS215において、変換スキップ識別子ts_idxが1D_H_TS以外であると判定された場合、処理はステップS217に進む。ステップS217において、プライマリ変換識別子復号部163は、上述の式(23)により、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換フラグpt_ver_flagを導出する。つまり、プライマリ変換識別子pt_idxが1ビットのbin列として処理され、プライマリ水平変換指定フラグpt_hor_flagがプライマリ変換識別子pt_idxの値にセットされ、プライマリ垂直変換フラグpt_ver_flagが所定値にセットされる。ステップS217の処理が終了すると、プライマリ垂直水平変換指定フラグ導出処理が終了し、処理は図19に戻る。

以上においては、プライマリ水平変換指定フラグpt_hor_ flag、及びプライマリ垂直変換指定フラグpt_ver_ flagの導出に係る処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。

以上のように、変換スキップ識別子ts_idxが1D_H_TS、または1D_V_TSの場合、プライマリ変換識別子pt_idxを1ビットのbin列として、算術復号することができるため、2ビットのbin列として算術復号する場合より、復号対象となるbin列を削減することができる。従って、プライマリ変換識別子pt_idxの復号に係る処理量を低減することができる。また、符号量を削減することできるので、符号化効率の向上も実現することができる。

<セカンダリ変換識別子st_idxの復号>

セカンダリ変換有効フラグ復号部171は、セカンダリ変換有効フラグst_enabled_flagの復号に関する処理を行う。セカンダリ変換識別子復号部172は、セカンダリ変換識別子st_idxの復号に関する処理を行う。

このような復号部111により図12のステップS101において実行される、セカンダリ変換識別子st_idxに関する復号処理の流れの例を、図22のフローチャートを参照して説明する。

復号処理が開始されると、セカンダリ変換有効フラグ復号部171は、ステップS231において、符号化データ#1のビット列からセカンダリ変換有効フラグst_enabled_flagを復号し、ヘッダ情報Hinfoの一部として出力する。

ステップS232において、セカンダリ変換識別子復号部172は、ヘッダ情報Hinfoに含まれるセカンダリ変換有効フラグst_enabled_flagが、1(真)であるか否かを判定する。セカンダリ変換有効フラグst_enabled_flagが0(偽)であると判定された場合、処理はステップS238に進む。また、ステップS232において、セカンダリ変換有効フラグst_enabled_flagが1(真)であると判定された場合、処理はステップS233に進む。

ステップS233において、セカンダリ変換識別子復号部172は、変換量子化バイパスフラグtransquant_bypass_flagが、1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1(真)であると判定された場合、処理はステップS238に進む。また、ステップS233において、変換量子化バイパスフラグtransquant_bypass_flagが0(偽)であると判定された場合、処理はステップS234に進む。

ステップS234において、セカンダリ変換識別子復号部172は、変換スキップ識別子ts_idxが、NO_TS(変換スキップをしない)であるか否かを判定する。変換スキップ識別子ts_idxがNO_TS以外であると判定された場合、処理はステップS238に進む。また、ステップS234において、変換スキップ識別子ts_idxがNO_TSであると判定された場合、処理はステップS235に進む。

ステップS235において、セカンダリ変換識別子復号部172は、残差情報Rinfoを参照して、変換ブロック内に存在する非ゼロ変換係数の総数numSig(sig_coeff_flag==1の総数)を導出する。ステップS235の処理が終了すると、処理はステップS236に進む。

ステップS236において、セカンダリ変換識別子復号部172は、非ゼロ変換係数の総数numSigが所定の閾値TH以上であるか否か(numSig>=stNumSigTH)を判定する。非ゼロ変換係数の総数numSigが所定の閾値THより少ない(すなわち、numSig<stNumSigTHを満たす)と判定された場合、処理はステップS238に進む。

また、ステップS236において、非ゼロ変換係数の総数numSigが所定の閾値TH以降である(すなわち、numSig>=stNumSigTHを満たす)と判定された場合、処理はステップS237に進む。

ステップS237において、セカンダリ変換識別子復号部172は、符号化データ#1のビット列からセカンダリ変換識別子st_idxを復号する。ステップS237の処理が終了すると、復号処理が終了し、処理は図12に戻る。

また、ステップS238において、セカンダリ変換識別子復号部172は、セカンダリ変換識別子st_idxの復号を省略し、セカンダリ変換識別子st_idxの値が0であると推定し、その値をst_idxへ設定する。すなわち、st_idx = 0となる。ステップS238の処理が終了すると、復号処理が終了し、処理は図12に戻る。

ステップS232乃至ステップS238(ステップS235およびステップS237を除く)の疑似コードを記載したシンタックステーブルを図23に示す。図23において符号SYN19を付したif文の条件式(以下の条件式(33))は、ステップS232乃至ステップS238の分岐判定と等価である。また、図23において符号SYN20を付したシンタックスは、図22のステップS237の処理に対応する。

論理値 = ( st_enabled_flag &&

以上においては、セカンダリ変換識別子st_idxの復号に係る処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。また、条件式(33)は、実施可能な範囲で演算を変更可能である。なお、上記では、セカンダリ変換の制御パラメータを、セカンダリ変換識別子st_idxとしたが、セカンダリ変換フラグst_flagであってもよい。

以上のように本技術を適用することにより、従来技術と比較して、変換ブロック単位でセカンダリ変換識別子を復号する場合において、2次元変換スキップ、または1次元変換スキップを適用する場合(ts_idx!=NO_TSの場合)、セカンダリ変換識別子の復号処理を省略することができる。すなわち、セカンダリ変換識別子の復号に係る処理量を低減することができる。

<3.第3の実施の形態>

図24は、復号部111の、プライマリ水平変換指定フラグpt_hor_flagおよびプライマリ垂直変換指定フラグpt_ver_flagの復号に関する主な構成例を示すブロック図である。図24に示されるように、この場合の復号部111は、プライマリ変換有効フラグ復号部161、適応プライマリ変換フラグ復号部162、プライマリ水平変換指定フラグ復号部181、およびプライマリ垂直変換指定フラグ復号部182を有する。

プライマリ水平変換指定フラグ復号部181は、プライマリ水平変換指定フラグpt_hor_flagの復号に関する処理を行う。プライマリ垂直変換指定フラグ復号部182は、プライマリ垂直変換指定フラグpt_ver_flagの復号に関する処理を行う。

プライマリ水平変換指定フラグ復号部181は、図25に示されるシンタクスにおいて、符号SYN15を付したif文の条件を満たす場合、すなわち、変換スキップ識別子ts_idxがNO_TSまたは1D_V_TSであって(ts_idx==NO_TS||ts_idx==1D_V_TS)、変換量子化バイパスフラグが0(偽)であって(transquant_bypass_flag==0)、輝度成分であって(cIdx==0)、適応プライマリ変換フラグapt_flagが1(真)であって(apt_flag==1)、かつ、変換ブロック内の非ゼロ変換係数の総数numSigが閾値ptNumSigTH以上である(numSig>=ptNumSigTH)場合、符号化データ#1のビット列からプライマリ水平変換指定フラグpt_hor_flagを復号する。それ以外の場合、プライマリ水平変換指定フラグ復号部181は、プライマリ水平変換指定フラグpt_hor_flagの値を-1(所定値)に設定する(推定する)。

同様に、プライマリ垂直変換指定フラグ復号部182は、図25に示されるシンタクスにおいて、符号SYN17を付したif文の条件を満たす場合、すなわち、変換スキップ識別子ts_idxがNO_TSまたは1D_H_TSであって(ts_idx==NO_TS||ts_idx==1D_H_TS)、変換量子化バイパスフラグが0(偽)であって(transquant_bypass_flag==0)、輝度成分であって(cIdx==0)、適応プライマリ変換フラグapt_flagが1(真)であって(apt_flag==1)、かつ、変換ブロック内の非ゼロ変換係数の総数numSigが閾値ptNumSigTH以上である(numSig>=ptNumSigTH)場合、符号化データ#1のビット列からプライマリ垂直変換指定フラグpt_ver_flagを復号する。それ以外の場合、プライマリ垂直変換指定フラグ復号部182は、プライマリ垂直変換指定フラグpt_ver_flagの値を-1(所定値)に設定する(推定する)。

以上のようにすることにより、変換スキップ識別子ts_idxが1D_H_TSの場合、プライマリ水平変換指定フラグpt_hor_flagの復号を省略することができる。同様に、変換スキップ識別子ts_idxが1D_V_TSの場合、プライマリ垂直変換指定フラグpt_ver_flagの復号を省略することができる。従って、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagの復号に係る処理量を低減することができる。また、符号量の増大を抑制することできるので、符号化効率の向上も実現することができる。

<4.第4の実施の形態>

図26は、その場合の逆変換部113の主な構成例を示すブロック図である。図26に示されるように、逆変換部113は、この場合も、図11の場合と基本的に同様の構成を有する。ただし、この場合、逆プライマリ変換部123は、スケーリング部191およびスケーリング部192を有する。

スイッチ132は、逆プライマリ垂直変換をスキップする場合、プライマリ変換係数Coeff_ISをスケーリング部191に供給する。スケーリング部191は、スイッチ132から供給されるプライマリ変換係数Coeff_IS(逆プライマリ垂直変換後の変換係数Coeff_IPver)に対してスケーリングを行う。例えば、スケーリング部191は、供給された変換係数に対して、逆プライマリ垂直変換を実施した場合と同一のノルムになるように正規化するためのN(Nは自然数)ビットのビットシフト演算を行う。スケーリング部191は、スケーリングした変換係数をスイッチ134に供給する。

スイッチ134は、逆プライマリ水平変換をスキップする場合、逆プライマリ垂直変換後の変換係数Coeff_IPverを予測残差D'としてスケーリング部192に供給する。スケーリング部192は、スケーリング部191の場合と同様に、スイッチ134から供給される逆プライマリ垂直変換後の変換係数Coeff_IPver(予測残差D')に対してスケーリングを行う。例えば、スケーリング部192は、供給された変換係数に対して、逆プライマリ水平変換を実施した場合と同一のノルムになるように正規化するためのN(Nは自然数)ビットのビットシフト演算を行う。スケーリング部192は、スケーリングした予測残差D'を外部に出力する。

このようにすることにより、変換係数のダイナミックレンジ幅を所定の範囲内に抑えることができるので、復号の負荷の増大を抑制することができる。

<5.第5の実施の形態>

なお、図27においては、処理部やデータの流れ等の主なものを示しており、図27に示されるものが全てとは限らない。つまり、画像符号化装置300において、図27においてブロックとして示されていない処理部が存在したり、図27において矢印等として示されていない処理やデータの流れが存在したりしてもよい。

図27に示されるように画像符号化装置300は、制御部311、演算部312、変換部313、量子化部314、符号化部315、逆量子化部316、逆変換部317、演算部318、フレームメモリ319、および予測部320を有する。

制御部311は、外部、または予め指定された処理単位のブロックサイズに基づいて、動画像#2を処理単位のブロック(CU, PU, 変換ブロックなど)へ分割し、分割されたブロックに対応する画像Iを演算部312へ入力する。また、制御部311は、各ブロックへ供給する符号化パラメータ(ヘッダ情報Hinfo、予測モード情報Pinfo, 変換情報Tinfoなど)を、例えば、RDO(Rate-Distortion Optimization)に基づいて、決定する。決定された符号化パラメータは、各ブロックへ供給される。具体的には、以下の通りである。

ヘッダ情報Hinfoは、各ブロックに供給される。予測モード情報Pinfoは、符号化部315および予測部320に供給される。変換情報Tinfoは、符号化部315、変換部313、量子化部314、逆量子化部316、および逆変換部317に供給される。

演算部312は、処理単位のブロックに対応する画像Iと、予測部320より供給される予測画像Pを入力とし、画像Iから予測画像Pを式(34)に示すように減算して、予測残差Dを導出し、変換部313に供給する。

D = I - P

変換部313は、逆変換部317の逆処理であり、予測残差Dおよび変換情報Tinfoを入力とし、変換情報Tinfoに基づいて、予測残差Dに対して、変換を適用し、変換係数Coeffを導出し、それを量子化部314に供給する。

量子化部314は、逆量子化部316の逆処理であり、変換情報Tinfoおよび変換係数Coeffを入力とし、変換情報Tinfoに基づいて、変換係数Coeffをスケーリング(量子化)し、量子化後の変換係数、すなわち量子化変換係数レベルlevelを符号化部315に供給する。

符号化部315は、復号部111(図10)の逆処理であり、シンタックステーブルの定義に沿って、制御部311から供給される符号化パラメータ(ヘッダ情報、予測モード情報Pinfo、変換情報Tinfo)、及び量子化部314より供給される量子化変換係数レベルlevelを、各シンタックス要素のシンタックス値へ変換し、各シンタックス値を可変長符号化(例えば、算術符号)し、ビット列を生成する。

なお、符号化部315は、量子化変換係数レベルlevelから残差情報RInfoを導出し、残差情報RInfoを可変長符号化し、ビット列を生成する。また、符号化部315は、可変長符号化された各シンタックス要素のビット列を多重化し、符号化データ#1を生成して出力する。

逆量子化部316は、逆量子化部112(図10)と同様の処理部であり、画像符号化装置300において、逆量子化部112と同様の処理を行う。逆変換部317は、逆変換部113(図10)と同様の処理部であり、画像符号化装置300において、逆変換部113と同様の処理を行う。フレームメモリ319は、フレームメモリ115(図10)と同様の処理部であり、画像符号化装置300において、フレームメモリ115と同様の処理を行う。予測部320は、予測部116(図10)と同様の処理部であり、画像符号化装置300において、予測部116と同様の処理を行う。

<変換部>

スイッチ331は、予測残差Dおよび変換スキップ識別子ts_idxを入力とし、変換スキップ識別子ts_idxの値がNO_TS(=0)、または、1D_H_TS(=2)、または、1D_V_TS(=3)の場合(変換スキップを適用しない、または、水平・垂直方向のいずれか一方に対して1次元変換スキップを適用することを示す場合)、プライマリ変換部332に予測残差Dを供給する。また、変換スキップ識別子ts_idxの値が2D_TS(=1)の場合(2次元変換スキップを適用することを示す場合)、プライマリ変換部332およびセカンダリ変換部333をスキップし、予測残差Dを変換係数Coeffとして変換部313の外部(量子化部314)に出力する。

例えば、変換スキップフラグts_idxが2D_TS(=1)であって、変換部313へ入力する予測残差Dが、4x4行列の予測残差D = [[255, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0], [0,0,0,0]]である場合、スイッチ331は、予測残差Dを、変換係数Coeffとして出力する。すなわち、変換係数Coeff = [[255, 0, 0, 0], [0, 0, 0, 0], [0, 0, 0, 0], [0,0,0,0]]となる。従って、プライマリ変換およびセカンダリ変換をスキップすることができる。特に、2次元変換スキップを適用するのが望ましい非ゼロ係数の数が少ない疎な残差信号に対して、変換の処理量の低減やエナジーコンパクションの低減を抑制することができ、符号化効率の向上した変換処理を行うことができる。

プライマリ変換部332は、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、変換スキップ識別子ts_idx、及び予測残差Dを入力とする。プライマリ変換部332は、予測モード情報PInfo、変換スキップ識別子、プライマリ水平変換指定フラグpt_hor_flagで指定されるプライマリ水平変換の行列PThor、プライマリ垂直変換指定フラグpt_ver_flagで指定されるプライマリ垂直変換の行列PTverを選択し、予測残差Dに対して、選択された各方向のプライマリ変換の行列により、プライマリ水平変換及びプライマリ垂直変換をして、プライマリ変換後の予測残差D'を導出し、出力する。

セカンダリ変換部333は、セカンダリ変換識別子st_idx、変換係数のスキャン方法を示すスキャン識別子scanIdx、及びプライマリ変換後の変換係数Coeff_Pを入力とし、セカンダリ変換後の変換係数Co eff(セカンダリ変換係数Coeff_Sともいう)を導出し、出力する。

より具体的には、セカンダリ変換識別子st_idxがセカンダリ変換を適用することを示す場合(st_idx>0)、セカンダリ変換部333は、プライマリ変換係数Coeff_Pに対して、セカンダリ変換識別子st_idxに対応するセカンダリ変換の処理を実行し、セカンダリ変換後の変換係数Coeff_Sを出力する。また、セカンダリ変換識別子st_idxがセカンダリ変換を適用しないことを示す場合(st_idx==0)、セカンダリ変換部333は、セカンダリ変換をスキップし、プライマリ変換後の変換係数Coeff_Pをセカンダリ変換後の変換係数Coeff_Sとして出力する。

図28に示されるように、プライマリ変換部332は、プライマリ変換選択部341、スイッチ342、プライマリ水平変換部343、スイッチ344、およびプライマリ垂直変換部345を有する。

プライマリ変換選択部341は、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、および変換スキップ識別子ts_idxを入力とし、予測モード情報PInfo、変換スキップ識別子ts_idx、プライマリ水平変換指定フラグpt_hor_flagで指定されるプライマリ水平変換の行列PThor、およびプライマリ垂直変換指定フラグpt_ver_flagで指定されるプライマリ垂直変換の行列PTverを、プライマリ変換選択部341の内部メモリ(不図示)より読み出し、それぞれを、プライマリ水平変換部343、プライマリ垂直変換部345へ出力する。

プライマリ変換選択部341は、逆プライマリ変換選択部131の場合と同様に、水平方向および垂直方向のそれぞれについて、プライマリ変換の候補となる直交変換を含む変換セットTransformSetを選択する。なお、この処理は逆プライマリ変換選択部131の処理と同一であるため、説明を省略する。

逆プライマリ変換選択部131における逆プライマリ水平変換IPThor、プライマリ垂直変換IPTverの選択処理と同様にして、プライマリ変換選択部341は、選択された変換セットTransformSetから、水平方向のプライマリ変換に用いる直交変換をプライマリ水平変換指定フラグpt_hor_flagによって選択し、垂直方向のプライマリ変換に用いる直交変換をプライマリ垂直変換指定フラグpt_ver_flagによって選択する。具体的な処理は、逆プライマリ変換選択部131における逆プライマリ水平変換IPThor及びプライマリ垂直変換IPTverの選択処理において、以下の読み替えを行い、解釈するものとする。

スイッチ342は、予測残差D及び変換スキップ識別子ts_idxを入力とする。変換スキップ識別子ts_idxの値が1D_H_TS(=2)、すなわち、水平方向の1次元変換をスキップすること(ts_idx==1D_H_TS)(プライマリ水平変換をスキップすること)を示す場合、スイッチ342は、プライマリ水平変換部343をスキップし、予測残差Dをプライマリ水平変換後の変換係数Coeff_Phorとしてスイッチ344へ出力する。また、変換スキップ識別子ts_idxの値が1D_H_TS(=2)以外の場合(ts_idx!=1D_H_TS)(プライマリ水平変換をスキップしないことを示す場合)、スイッチ342は予測残差Dをプライマリ水平変換部343へ出力する。

プライマリ水平変換部343は、変換ブロック毎に、予測残差Dとプライマリ水平変換PThorの行列を入力とし、以下の式(35)に示される通りに行列演算を行い、その結果をプライマリ水平変換後の変換係数Coeff_Phorとして出力する。なお、プライマリ水平変換PThorは、変換基底を列ベクトルとして有する行列である。

Coeff_Phor = (D・PThor) >> s3

ここで、演算子"・"は行列積(inner product)を表し、演算子">>"は要素毎に右シフト演算を行う操作を表す。式(35)によれば、変換係数Coeff_Phorの各値は、予測残差Dとプライマリ水平変換PThorとの行列積の要素毎に対して、所定のスケーリングパラメータs3によって右シフト演算することで得られる。なお、スケーリングパラメータs3は、D・PThorの行列演算結果を、中間バッファのビット深度に収まるよう正規化するために用いる。スケーリングパラメータs3の値は、例えば、以下の式(36)に示されるように中間バッファのビット深度BitDepthbuffと、D・PThorの行列演算のビット深度のワーストケースMaxBitDepth(D・PThor)から定まる。

s3 = max(0, MaxBitDepth(D・PThor) - BitDpethbuff)

例えば、D・PThorの値域が、-2**22乃至2**22 - 1である場合、すなわち、MaxBitDepth(D・PThor)のビット深度が23bitであって、中間バッファに格納可能な値の値域が、-2**15乃至2**15 - 1である場合、すなわち中間バッファのビット深度が16bitの場合、スケーリングパラメータs3は、s3 = 7bit( = max(0, 23-16) = max(0, 7))となる。また、MaxBitDepth(D・PThor)のビット深度が23bitであって、中間バッファに格納可能な値の値域が、-2**31乃至2**31 - 1である場合、すなわち、中間バッファのビット深度が32bitの場合、スケーリングパラメータs3は、s3 = 0bit(=max(0, 23-32)=max(0,-9))となる。スケーリングパラメータs3が0であるということは、中間バッファのビット深度の値が十分に大きいため、D・PThorの行列積の各要素値を正規化せずとも、中間バッファにオーバフローせずに格納することが出来ることを表す。

なお、スケーリングパラメータs3は、D・PThorの値域が既知であると仮定して、予め定めた固定値としてもよい。また、上述の式(36)において、右シフト演算によるクリップ誤差を小さくするために、行列積の後、所定のオフセット値o3を要素毎に加算するようにしてもよい。このとき、オフセット値o3は、スケーリングパラメータs3を用いて、以下の式(37)により表される。

o3 = ( s3>0 ? 1<<(s3-1) : 0 )

スイッチ344は、プライマリ水平変換後の変換係数Coeff_Phorおよび変換スキップ識別子ts_idxを入力とする。変換スキップ識別子ts_idxの値が1D_V_TS(=3)、すなわち、垂直方向の1次元変換をスキップすること(ts_idx==1D_V_TS)(プライマリ垂直変換をスキップすること)を示す場合、スイッチ344は、プライマリ垂直変換部345をスキップし、プライマリ水平変換後の変換係数Coeff_Phorをプライマリ変換後の変換係数Coeff_Pとして外部(セカンダリ変換部333)へ出力する。また、変換スキップ識別子ts_idxの値が1D_V_TS(=2)以外の場合(ts_idx!=1D_V_TS)(プライマリ垂直変換をスキップしないことを示す場合)、スイッチ344はプライマリ水平変換後の変換係数Coeff_Phorをプライマリ垂直変換部345へ出力する。

プライマリ垂直変換部345は、変換ブロック毎に、プライマリ水平変換後の変換係数Coeff_Phorとプライマリ垂直変換PTverの行列を入力とし、以下の式(38)に示す通り行列演算を行い、その結果をプライマリ変換後の変換係数Coeff_Pとして出力する。なお、プライマリ垂直変換PTverは、変換基底を行ベクトルとして有する行列である。

Coeff_P = (PTver・Coeff_Phor) >> s3

ここで、演算子"・"は行列積(inner product)を表し、演算子">>"は要素毎に右シフト演算を行う操作を表す。式(38)によれば、変換係数Coeff_Pの各値は、プライマリ水平変換後の変換係数Coeff_Phorとプライマリ垂直変換の行列PTverとの行列積の要素毎に対して、所定のスケーリングパラメータs3によって右シフト演算することで得られる。なお、スケーリングパラメータs4は、PTver・Coeff_Phorの行列演算結果を、所望のビット深度に収まるよう正規化するために用いる。スケーリングパラメータs4の値は、所望のビット深度BitDepthoutと、PTver・Coeff_Phorの行列演算のビット深度のワーストケースMaxBitDepth(PTver・Coeff_Phor)から、以下の式(39)により定まる。

s4 = max(0, MaxBitDepth(PTver・Coeff_Phor) - BitDpethout)

例えば、PTver・Coeff_Phorの値域が、-2**22乃至2**22 - 1である場合、すなわち、MaxBitDepth(PTver・Coeff_Phor)のビット深度が23bitであって、所望ビット深度のとき取りえる値の値域が、-2**15乃至2**15 - 1である場合、すなわち所望ビット深度が16bitの場合、スケーリングパラメータs4は、s4 = 7bit( = max(0, 23-16) = max(0, 7))となる。また、MaxBitDepth(PTver・Coeff_Phor)のビット深度が23bitであって、所望ビット深度のとき取りえる値の値域が、-2**31乃至2**31 - 1である場合、すなわち、所望ビット深度が32bitの場合、スケーリングパラメータs4は、s4 = 0bit(=max(0, 23-32)=max(0,-9))となる。スケーリングパラメータs4が0であるということは、所望ビット深度の値が十分に大きいため、PTver・Coeff_Phorの行列積の各要素値が正規化せずとも、所望ビット深度内に収まることを表す。

なお、上述の式(38)において、右シフト演算によるクリップ誤差を小さくするために、行列積の後、所定のオフセット値o4を要素毎に加算するようにしてもよい。このとき、オフセット値o3は、スケーリングパラメータs4を用いて、以下の式(40)により表される。

o4 = ( s4>0 ? 1<<(s4-1) : 0 )

以上、プライマリ変換部332は、水平方向、または垂直方向の1次元変換をスキップことが望ましい残差信号に対して、プライマリ変換の処理量の低減、及びエナジーコンパクションの低下を防止し、符号化効率の向上したプライマリ変換処理を行うことができる。特に、水平方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、水平方向の1次元変換をスキップし、垂直方向に1次元変換をすることで、2次元直交変換をする場合と比較して、垂直方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率を向上させることができる。同様に、垂直方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、垂直方向の1次元変換をスキップし、水平方向に1次元変換をすることで、2次元直交変換をする場合と比較して、水平方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率を向上させることができる。

<画像符号化処理の流れ>

画像符号化処理が開始されると、ステップS301において、制御部311は、符号化制御処理を行い、ブロック分割や符号化パラメータの設定等を行う。

ステップS302において、予測部320は、予測処理を行い、最適な予測モードの予測画像等を生成する。例えば、この予測処理において、予測部320は、イントラ予測を行って最適なイントラ予測モードの予測画像等を生成し、インター予測を行って最適なインター予測モードの予測画像等を生成し、それらの中から、コスト関数値等に基づいて最適な予測モードを選択する。

ステップS303において、演算部312は、入力画像と、ステップS302の予測処理により選択された最適なモードの予測画像との差分を演算する。つまり、演算部312は、入力画像と予測画像との予測残差Dを生成する。このようにして求められた予測残差Dは、元の画像データに比べてデータ量が低減される。したがって、画像をそのまま符号化する場合に比べて、データ量を圧縮することができる。

ステップS304において、変換部313は、ステップS303の処理により生成された予測残差Dに対して変換処理を行い、変換係数Coeffを導出する。なお、この変換処理は、ステップS307の逆変換処理の逆処理であり、上述した画像復号処理において実行される逆変換処理の逆処理である。ステップS304の処理の詳細については後述する。

ステップS305において、量子化部314は、制御部311により算出された量子化パラメータを用いる等して、ステップS304の処理により得られた変換係数Coeffを量子化し、量子化変換係数レベルlevelを導出する。

ステップS306において、逆量子化部316は、ステップS305の処理により生成された量子化変換係数レベルlevelを、そのステップS305の量子化の特性に対応する特性で逆量子化し、変換係数Coeff_IQを導出する。

ステップS307において、逆変換部317は、ステップS306の処理により得られた変換係数Coeff_IQを、ステップS304の変換処理に対応する方法で逆変換し、予測残差D’を導出する。なお、この逆変換処理は、上述した画像復号処理において実行される逆変換処理と同様に実行される。

ステップS308において、演算部318は、ステップS307の処理により導出された予測残差D’に、ステップS302の予測処理により得られた予測画像を加算することにより、局所的に復号された復号画像を生成する。

ステップS309において、フレームメモリ319は、ステップS308の処理により得られた、局所的に復号された復号画像を記憶する。

ステップS310において、符号化部315は、ステップS305の処理により得られた量子化変換係数レベルlevelを符号化する。例えば、符号化部315は、画像に関する情報である量子化変換係数レベルlevelを、算術符号化等により符号化し、符号化データを生成する。また、このとき、符号化部315は、各種符号化パラメータ(ヘッダ情報Hinfo、予測モード情報Pinfo、変換情報Tinfo)を符号化する。さらに、符号化部315は、量子化変換係数レベルlevelから残差情報RInfoを導出し、その残差情報RInfoを符号化する。

ステップS311において、符号化部315は、このように生成した各種情報の符号化データをまとめて、ビットストリームとして画像符号化装置300の外部に出力する。このビットストリームは、例えば、伝送路や記録媒体を介して復号側に伝送される。ステップS311の処理が終了すると、画像符号化処理が終了する。

なお、これらの各処理の処理単位は任意であり、互いに同一でなくてもよい。したがって、各ステップの処理は、適宜、他のステップの処理等と並行して、または、処理順を入れ替えて実行することもできる。

<変換処理の流れ>

また、ステップS331において、変換スキップ識別子ts_idxが2D_TSでない(2次元変換スキップ以外のモード)、かつ変換量子化バイパスフラグが0(偽)であると判定された場合、スイッチ331は、予測残差Dをプライマリ変換部332へ出力する。つまり、処理はステップS332に進む。

ステップS332において、プライマリ変換選択部341は、プライマリ水平変換指定フラグpt_hor_flag、プライマリ垂直変換指定フラグpt_ver_flag、予測モード情報PInfo、および変換スキップ識別子ts_idxを参照して、プライマリ水平変換PThorおよびプライマリ垂直変換PTverを選択し、それぞれ、プライマリ水平変換部343、プライマリ垂直変換部345に供給する。

ステップS333において、スイッチ342は、変換スキップ識別子ts_idxが1D_H_TS(水平方向の1次元変換スキップのモード)であるか否か(ts_idx==1D_H_TS)を判定する。変換スキップ識別子ts_idxが1D_H_TSでないと判定された場合、処理はステップS334に進む。ステップS334において、プライマリ水平変換部343は、変換ブロック毎に、予測残差Dとプライマリ水平変換PThorの行列を入力とし、行列演算を行い、その結果をプライマリ水平変換後の変換係数Coeff_Phorとして出力する。ステップS334の処理が終了すると、処理はステップS335に進む。

また、ステップS333において、変換スキップ識別子ts_idxが1D_H_TSであると判定された場合、スイッチ342は、予測残差Dを、プライマリ水平変換部343をスキップして、プライマリ水平変換後の変換係数Coeff_Phorとして、スイッチ344に供給する。つまり、ステップS334の処理が省略され、処理はステップS335に進む。

ステップS335において、スイッチ344は、変換スキップ識別子ts_idxが1D_V_TS(垂直方向の1次元変換スキップのモード)であるか否か(ts_idx==1D_V_TS)を判定する。変換スキップ識別子ts_idxが1D_V_TSでないと判定された場合、処理はステップS336に進む。ステップS336において、プライマリ垂直変換部345は、プライマリ垂直変換を行う。すなわち、プライマリ垂直変換部345は、変換ブロック毎に、プライマリ水平変換後の変換係数Coeff_Phorとプライマリ垂直変換PTverの行列を入力とし、行列演算を行い、その結果をプライマリ変換後の変換係数Coeff_Pとして出力する。ステップS336の処理が終了すると、処理はステップS337に進む。

また、ステップS335において、変換スキップ識別子ts_idxが1D_V_TSであると判定された場合、スイッチ344は、プライマリ水平変換後の変換係数Coeff_Phorを、プライマリ垂直変換部345への入力をスキップして、プライマリ変換後の変換係数Coeff_Pとして出力するよう制御する。すなわち、ステップS336の処理が省略され、処理はステップS337に進む。

ステップS337において、セカンダリ変換部333は、入力されたプライマリ変換係数Coeff_Pに対して、セカンダリ変換識別子st_idxに基づいて、セカンダリ変換を行い、変換係数Coeffを導出し出力する。ステップS337の処理が終了すると、変換処理が終了し、処理は図29に戻る。

<プライマリ変換選択処理の流れ>

プライマリ変換選択処理が開始されると、プライマリ変換選択部341は、ステップS351において、適応プライマリ変換フラグapt_flagが1(真)であるか否かを判定する。適応プライマリ変換フラグapt_flagが1(真)であると判定された場合、処理はステップS352に進む。ステップS352において、プライマリ変換選択部341は、予測モード情報PInfoに基づいて、プライマリ垂直変換およびプライマリ水平変換のそれぞれについて変換セットを選択する。ステップS352の処理が終了すると、処理はステップS354に進む。

また、ステップS351において、適応プライマリ変換フラグapt_flagが0(偽)であると判定された場合、処理はステップS353に進む。ステップS353において、プライマリ変換選択部341は、所定の変換セットを選択する。ステップS353の処理が終了すると、処理はステップS354に進む。

ステップS354において、プライマリ変換選択部341は、水平変換セット識別子TransformSetH、及びプライマリ水平変換指定フラグpt_hor_flagを参照して、プライマリ水平変換PThorとして適用する直交変換を選択する。

ステップS355おいて、逆プライマリ変換選択部341は、垂直変換セット識別子TransformSetV、及びプライマリ垂直変換指定フラグpt_ver_flagを参照して、プライマリ垂直変換PTverとして適用する直交変換を選択する。

ステップS355の処理が終了すると、プライマリ変換選択処理が終了し、処理は図30に戻る。

なお上述の処理も、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。例えば、ステップS333およびステップS335の処理を省略し、ステップS331において、変換スキップ識別子ts_idxが1D_H_TS(水平方向の1次元変換スキップ)の場合、単位行列をプライマリ水平変換PThorとして選択し、ステップS334の処理を実行するようにしてもよい。また、ステップS331において、変換スキップ識別子ts_idxが1D_V_TS(垂直方向の1次元変換スキップ)の場合、単位行列をプライマリ垂直変換PTverとして選択し、ステップS336の処理を実行するようにしてもよい。

以上のようにすることにより、画像符号化装置300が備える変換部313は、変換スキップを適用するのが望ましい残差信号に対して、変換の処理量の低減、及びエナジーコンパクションの低下を抑制することができ、符号化効率の向上した逆変換処理を行うことができる。より具体的には、変換部313は、水平方向、または垂直方向の1次元変換をスキップことが望ましい残差信号に対して、プライマリ変換の処理量の低減、及びエナジーコンパクションの低下を抑制することができ、符号化効率の向上した逆プライマリ変換処理を行うことができる。

特に、水平方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、水平方向の1次元変換をスキップし、垂直方向に1次元変換をすることで、2次元直交変換をする場合と比較して、垂直方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができるため、符号化効率を向上させることができる。

同様に、垂直方向に信号の連続性が急激に変化するステップエッジの特性を持つ残差信号に対しては、垂直方向の1次元変換をスキップし、水平方向に1次元変換をすることで、2次元直交変換をする場合と比較して、水平方向の周波数成分の低域に非ゼロ係数を効率よく集中させることができる。すなわち、エナジーコンパクションを高めることができ、符号化効率を向上させることができる。

<6.第6の実施の形態>

この場合、変換ブロック単位で符号化された変換スキップ識別子ts_idxが、1D_H_TSの場合、プライマリ水平変換指定フラグpt_hor_flagは使用されないため、この情報を符号化するのは冗長である。また、変換スキップ識別子ts_idxが1D_V_TSを示す場合、プライマリ垂直変換指定フラグpt_ver_flagは使用されないため、この情報を符号化するのは冗長である。従って、プライマリ変換識別子pt_idxを効率良く符号化するために、下記の変更を加える。

このようにすることで、変換スキップ識別子ts_idxが1D_H_TS、または1D_V_TSの場合、プライマリ変換識別子pt_idxは、1ビットのbin列として、算術符号化されるため、2ビットのbin列として算術符号化する場合より、符号化対象となるbin列を削減することができる。従って、符号量の増大を抑制することでき、符号化効率を向上させることができる。

また、セカンダリ変換に関して、変換スキップ識別子ts_idxが2D_TS、または1D_H_TS、または、1D_V_TSの場合、セカンダリ変換をスキップするため、セカンダリ変換の制御パラメータであるセカンダリ変換識別子st_idxを符号化するのは冗長である。そこで、変換スキップ識別子ts_idxが2D_TS、または1D_H_TS、または1D_V_TSの場合には、セカンダリ変換識別子st_idxの符号化が省略されるように変更することで、セカンダリ変換識別子st_idxの符号化に係る処理量の増大を抑制することができる。

<変換スキップ識別子ts_idxの符号化>

変換スキップ有効フラグ符号化部361は、変換スキップ有効フラグts_enabled_flagの符号化に関する処理を行う。最大変換スキップブロックサイズ符号化部362は、最大変換スキップブロックサイズMaxTSSizeの符号化に関する処理を行う。変換量子化バイパスフラグ符号化部363は、変換量子化バイパスフラグtransquant_bypass_flagの符号化に関する処理を行う。変換スキップ識別子符号化部364は、変換スキップ識別子ts_idxの符号化に関する処理を行う。

このような符号化部315により図29のステップS310において実行される、変換スキップ識別子ts_idxに関する符号化処理の流れの例を、図33のフローチャートを参照して説明する。

符号化処理が開始されると、変換スキップ有効フラグ符号化部361は、ステップS371において、ヘッダ情報HInfoに含まれる変換スキップ有効フラグts_enabled_flagを可変長符号化し、ビット列を生成し出力する。

ステップS372において、最大変換スキップブロックサイズ符号化部362は、ヘッダ情報Hinfoに含まれる変換スキップ有効フラグts_enabled_flagが、1(真)であるか否かを判定する。変換スキップ有効フラグts_enabled_flagが1(真)であると判定された場合、処理はステップS373に進む。

ステップS373において、最大変換スキップブロックサイズ符号化部362は、ヘッダ情報HInfoに含まれる最大変換スキップブロックサイズMaxTSSize (あるいは、2を底とする対数値log2MaxTSSize)を可変長符号化し、ビット列を生成し出力する。ステップS373の処理が終了すると、処理はステップS374に進む。また、ステップS372において、変換スキップ有効フラグts_enabled_flagが0(偽)であると判定された場合、ステップS373の処理が省略され、処理はステップS374に進む。

ステップS374において、変換量子化バイパスフラグ符号化部363は、ヘッダ情報HInfoに含まれる変換量子化バイパスフラグtransquant_bypass_flagを可変長符号化し、ビット列を生成して出力する。

ステップS375において、変換スキップ識別子符号化部364は、変換情報Tinfoに含まれる変換量子化バイパスフラグtransquant_bypass_flagが1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1(真)であると判定された場合、変換スキップ識別子ts_idxの符号化が省略され、符号化処理が終了し、処理は図29に戻る。また、ステップS375において、変換量子化バイパスフラグtransquant_bypass_flagが0(偽)であると判定された場合、処理はステップS376に進む。

ステップS376において、変換スキップ識別子符号化部364は、ヘッダ情報HInfoに含まれる変換スキップ有効フラグts_enabled_flagが1(真)であるか否かを判定する。変換スキップ有効フラグts_enabled_flagが0(偽)であると判定された場合、変換スキップ識別子ts_idxの符号化が省略され、符号化処理が終了し、処理は図29に戻る。また、変換スキップ有効フラグts_enabled_flagが1(真)であると判定された場合、処理はステップS377に進む。

ステップS377において、変換スキップ識別子符号化部364は、処理対象の変換ブロックのサイズTBSizeが最大変換スキップブロックサイズMaxTSSize以下であるか否か、言い換えれば、条件式(TBSize<=MaxTSSize)の論理値が1(真)であるか否かを判定する。

なお、条件式(TBSize<=MaxTSSize)において、TBSizeは、上述の式(26)または式(27)により導出する。また、式(26)及び式(27)において、TBSize、TBWSize、TBHSizeを、2を底とする対数値log2TBSize、log2TBWSize、log2TBHSizeに置き換えてもよい。この場合、式(26)は上述の式(28)に置き換え、式(27)は上述の式(29)へ置き換える。なお、対数値を用いる場合は、上述の条件式(TBSize<=MaxTSSize)のTBSizeおよび最大変換スキップブロックサイズMaxTSSizeは、それぞれ対応する対数値log2TBSize、log2MaxTSSizeへ置き換えるものとする。

TBSizeが最大変換スキップブロックサイズMaxTSSizeより大きい、すなわち、条件式の論理値が0であると判定された場合、変換スキップ識別子ts_idxの符号化が省略され、符号化処理が終了し、処理は図29に戻る。また、TBSizeが最大変換スキップブロックサイズMaxTSSize以下である、すなわち、条件式の論理値が1であると判定された場合、処理はステップS378に進む。

ステップS378において、変換スキップ識別子符号化部364は、ヘッダ情報HInfoに含まれる変換スキップ識別子ts_idxを可変長符号化し、ビット列を生成し出力する。ステップS378の処理が終了すると、符号化処理が終了し、処理は図29に戻る。

以上において、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。

このように各処理を実行することにより、JEM3と比較して、符号化側において、変換ブロック単位で2次元変換スキップ、水平方向または垂直方向の1次元変換スキップを適応的に選択することができる。従って、従来よりも1次元変換スキップが有効な残差信号に対して、1次元変換スキップのモードにより符号化することができるため、符号化効率を向上させることができる。

<プライマリ変換識別子pt_idxの符号化>

プライマリ変換有効フラグ符号化部371は、プライマリ変換有効フラグpt_enabled_flagの符号化に関する処理を行う。適応プライマリ変換フラグ符号化部372は、プライマリ変換フラグpt_enabled_flagの符号化に関する処理を行う。プライマリ変換識別子符号化部373は、プライマリ変換識別子pt_idxの符号化に関する処理を行う。

このような符号化部315により図29のステップS310において実行される、プライマリ変換識別子pt_idxに関する符号化処理の流れの例を、図35のフローチャートを参照して説明する。

符号化処理が開始されると、プライマリ変換有効フラグ符号化部371は、ステップS391において、ヘッダ情報HInfoに含まれるプライマリ変換有効フラグpt_enabled_flagを可変長符号化し、ビット列を生成し出力する。

ステップS392において、適応プライマリ変換フラグ符号化部372は、ヘッダ情報Hinfoに含まれるプライマリ変換有効フラグpt_enabled_flagが、1(真)であるか否かを判定する。プライマリ変換有効フラグpt_enabled_flagが0であると判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、プライマリ変換有効フラグpt_enabled_flagが1であると判定された場合、処理はステップS393に進む。

ステップS393において、適応プライマリ変換フラグ符号化部372は、ヘッダ情報HInfoに含まれる適応プライマリ変換フラグapt_flagを可変長符号化し、ビット列を生成し出力する。

ステップS394において、適応プライマリ変換フラグ符号化部372は、適応プライマリ変換フラグapt_flagが、1(真)であるか否かを判定する。適応プライマリ変換フラグapt_flagが0(偽)であると判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、適応プライマリ変換フラグapt_flagが1(真)であると判定された場合、処理はステップS395に進む。

ステップS395において、プライマリ変換識別子符号化部373は、変換量子化バイパスフラグtransquant_bypass_flagが、1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1(真)であると判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、変換量子化バイパスフラグtransquant_bypass_flagが0(偽)であると判定された場合、処理はステップS396に進む。

ステップS396において、プライマリ変換識別子符号化部373は、変換スキップ識別子ts_idxが2D_TS(2次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが2D_TSであると判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、変換スキップ識別子ts_idxが2D_TS以外であると判定された場合、処理はステップS397に進む。

ステップS397において、プライマリ変換識別子符号化部373は、変換ブロックの縦サイズまたは横サイズの少なくとも一方が最大適応プライマリ変換ブロックサイズMaxPTSize以下(max(TBHSize, TBWSize)<=MaxPTSize)であるか否かを判定する。変換ブロックの縦サイズまたは横サイズの少なくとも一方が最大適応プライマリ変換ブロックサイズMaxPTSizeより大きいと判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、変換スキップ識別子ts_idxが2D_TS以外であると判定された場合、処理はステップS397に進む。変換ブロックの縦サイズおよび横サイズの両方ともが最大適応プライマリ変換ブロックサイズMaxPTSize以下であると判定された場合、処理はステップS398に進む。

ステップS398において、プライマリ変換識別子符号化部398は、符号化対象の変換ブロックが輝度成分であるか否かを判定する。輝度成分でないと判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、輝度成分であると判定された場合、処理はステップS399に進む。

ステップS399において、プライマリ変換識別子符号化部398は、残差情報Rinfoを参照して、変換ブロック内に存在する非ゼロ変換係数の総数numSig(sig_coeff_flag==1の総数)を導出する。ステップS399の処理が終了すると、処理はステップS400に進む。

ステップS400において、プライマリ変換識別子符号化部398は、非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTH以上であるか否か(numSig>=ptNumSigTH)を判定する。非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTHより少ないと判定された場合、プライマリ変換識別子pt_idxの導出や符号化に関する処理が省略され、符号化処理が終了し、処理は図29に戻る。また、非ゼロ変換係数の総数numSigが所定の閾値ptNumSigTH以上であると判定された場合、処理はステップS401に進む。

ステップS401において、プライマリ変換識別子符号化部373は、変換スキップ識別子ts_idx、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagを参照して、プライマリ変換識別子pt_idxを導出する。なお、プライマリ変換識別子pt_idxの詳細の導出については後述する。

ステップS402において、プライマリ変換識別子符号化部373は、ヘッダ情報HInfoに含まれるプライマリ変換識別子pt_idxを可変長符号化し、ビット列を生成し出力する。ステップS402の処理が終了すると、符号化処理が終了し、処理は図29に戻る。

以上においては、プライマリ変換識別子pt_idxの符号化に係る処理について説明したが、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。

以上、変換スキップ識別子ts_idxが1D_H_TS、または1D_V_TSの場合、プライマリ変換識別子pt_idxを1ビットのbin列として、算術符号化することができるため、2ビットのbin列として算術符号化する場合より、符号化対象となるbin列を削減することができる。従って、プライマリ変換識別子pt_idxの符号化に係る処理量を低減することができる。また、符号量を削減することできるので、符号化効率を向上させることができる。

次に図36のフローチャートを参照して、符号化部315により図35のステップS401において実行される、プライマリ変換識別子pt_idxのの導出処理の流れの例を説明する。

プライマリ変換識別子導出処理が開始されると、ステップS421において、プライマリ変換識別子符号化部373は、変換スキップ識別子ts_idxがNO_TS (変換スキップでない)であるか否かを判定する。変換スキップ識別子ts_idxがNO_TSであると判定された場合、処理はステップS422に進む。

ステップS422において、プライマリ変換識別子符号化部373は、上述の式(20)により、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換フラグpt_ver_flagからプライマリ変換識別子pt_idxを導出する。ステップS422の処理が終了すると、プライマリ変換識別子導出処理が終了し、処理は図35に戻る。

また、ステップS421において、変換スキップ識別子ts_idxがNO_TS以外であると判定された場合、処理はステップS423に進む。

ステップS423において、プライマリ変換識別子符号化部373は、変換スキップ識別子ts_idxが2D_TS (2次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが2D_TSであると判定された場合、プライマリ変換識別子導出処理が終了し、処理は図35に戻る。

また、ステップS423において、変換スキップ識別子ts_idxが2D_TS以外であると判定された場合、処理はステップS424に進む。

ステップS424において、プライマリ変換識別子符号化部373は、変換スキップ識別子ts_idxが1D_H_TS(水平方向の1次元変換スキップ)であるか否かを判定する。変換スキップ識別子ts_idxが1D_H_TSであると判定された場合、処理はステップS425に進む。

ステップS425において、プライマリ変換識別子符号化部373は、上述の式(22)に基づいて、プライマリ変換識別子pt_idx = pt_ver_flagとして導出する。ステップS425の処理が終了すると、プライマリ変換識別子導出処理が終了し、処理は図35に戻る。

また、ステップS424において、変換スキップ識別子ts_idxが1D_H_TS以外であると判定された場合、処理はステップS426に進む。

ステップS426において、プライマリ変換識別子符号化部373は、上述の式(24)に基づいて、プライマリ変換識別子pt_idx = pt_hor_flagとして導出する。ステップS426の処理が終了すると、プライマリ変換識別子導出処理が終了し、処理は図35に戻る。

もちろん、この処理も、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。

<セカンダリ変換識別子st_idxの復号>

セカンダリ変換有効フラグ符号化部381は、セカンダリ変換有効フラグst_enabled_flagの符号化に関する処理を行う。セカンダリ変換識別子符号化部382は、セカンダリ変換識別子st_idxの符号化に関する処理を行う。

このような符号化部315により図29のステップS310において実行される、セカンダリ変換識別子st_idxに関する復号処理の流れの例を、図38のフローチャートを参照して説明する。

符号化処理が開始されると、セカンダリ変換有効フラグ符号化部381は、ステップS441において、ヘッダ情報HInfoに含まれるセカンダリ変換有効フラグst_enabled_flagを可変長符号化し、ビット列を生成し出力する。

ステップS442において、セカンダリ変換識別子符号化部382は、ヘッダ情報Hinfoに含まれるセカンダリ変換有効フラグst_enabled_flagが、1(真)であるか否かを判定する。セカンダリ変換有効フラグst_enabled_flagが0(偽)であると判定された場合、符号化処理が終了し、処理は図29に戻る。

また、ステップS442において、セカンダリ変換有効フラグst_enabled_flagが1(真)であると判定された場合、処理はステップS443に進む。

ステップS443において、セカンダリ変換識別子符号化部382は、変換量子化バイパスフラグtransquant_bypass_flagが、1(真)であるか否かを判定する。変換量子化バイパスフラグtransquant_bypass_flagが1(真)であると判定された場合、符号化処理が終了し、処理は図29に戻る。また、変換量子化バイパスフラグtransquant_bypass_flagが0(偽)であると判定された場合、処理はステップS444に進む。

ステップS444において、セカンダリ変換識別子符号化部382は、変換スキップ識別子ts_idxが、NO_TS(変換スキップをしない)であるか否かを判定する。変換スキップ識別子ts_idxがNO_TS以外であると判定された場合、符号化処理が終了し、処理は図29に戻る。また、変換スキップ識別子ts_idxがNO_TSであると判定された場合、処理はステップS445に進む。

ステップS445において、セカンダリ変換識別子符号化部382は、残差情報Rinfoを参照して、変換ブロック内に存在する非ゼロ変換係数の総数numSig(sig_coeff_flag==1の総数)を導出する。

ステップS446において、セカンダリ変換識別子符号化部382は、非ゼロ変換係数の総数numSigが所定の閾値TH以上であるか否か(numSig>=stNumSigTH)を判定する。非ゼロ変換係数の総数numSigが所定の閾値THより少ない(numSig<stNumSigTH)、すなわち、条件式の論理値が0(偽)であると判定された場合、セカンダリ変換識別子符号化部382は、符号化処理が終了し、処理は図29に戻る。また、非ゼロ変換係数の総数numSigが所定の閾値TH以上である(numSig>=stNumSigTH)、すなわち、条件式の論理値が1(真)であると判定された場合、処理はステップS447に進む。

ステップS447において、セカンダリ変換識別子符号化部382は、ヘッダ情報HInfoに含まれるセカンダリ変換識別子st_idxを可変長符号化し、ビット列を生成し出力する。

ステップS447の処理が終了すると、符号化処理が終了し、処理は図29に戻る。

この処理も、実施可能な範囲で、各ステップの処理順の入れ替えや、処理の内容を変更してよい。また、以上においてはセカンダリ変換の制御パラメータを、セカンダリ変換識別子st_idxとしたが、セカンダリ変換フラグst_flagであってもよい。

以上のようにすることにより、従来技術と比較して、変換ブロック単位でセカンダリ変換識別子を符号化する場合において、2次元変換スキップ、または1次元変換スキップを適用する場合(ts_idx!=NO_TS)の場合、セカンダリ変換識別子の符号化処理を省略することができる。すなわち、セカンダリ変換識別子の符号化に係る処理量、及び符号量を低減させることができる。

<7.第7の実施の形態>

図39は、符号化部315の、プライマリ水平変換指定フラグpt_hor_flagおよびプライマリ垂直変換指定フラグpt_ver_flagの符号化に関する主な構成例を示すブロック図である。図39に示されるように、この場合の符号化部315は、プライマリ変換有効フラグ符号化部371、適応プライマリ変換フラグ符号化部372、プライマリ水平変換指定フラグ符号化部391、およびプライマリ垂直変換指定フラグ符号化部392を有する。

プライマリ水平変換指定フラグ符号化部391は、プライマリ水平変換指定フラグpt_hor_flagの符号化に関する処理を行う。プライマリ垂直変換指定フラグ符号化部392は、プライマリ垂直変換指定フラグpt_ver_flagの符号化に関する処理を行う。

プライマリ水平変換指定フラグ符号化部391は、図25に示されるシンタクスにおいて、符号SYN15を付したif文の条件を満たす場合、すなわち、変換スキップ識別子ts_idxがNO_TSまたは1D_V_TSであって(ts_idx==NO_TS||ts_idx==1D_V_TS)、変換量子化バイパスフラグが0(偽)であって(transquant_bypass_flag==0)、輝度成分であって(cIdx==0)、適応プライマリ変換フラグapt_flagが1(真)であって(apt_flag==1)、かつ、変換ブロック内の非ゼロ変換係数の総数numSigが閾値ptNumSigTH以上(numSig>=ptNumSigTH)である場合に、符号化データ#1のビット列からプライマリ水平変換指定フラグpt_hor_flagを可変長符号化し、ビット列を生成する。それ以外の場合、プライマリ水平変換指定フラグ符号化部391は、プライマリ水平変換指定フラグpt_hor_flagの符号化を省略する。

同様に、プライマリ垂直変換指定フラグ符号化部392は、図25に示されるシンタクスにおいて、符号SYN17を付したif文の条件を満たす場合、すなわち、変換スキップ識別子ts_idxがNO_TSまたは1D_H_TSであって(ts_idx==NO_TS||ts_idx==1D_H_TS)、変換量子化バイパスフラグが0(偽)であって(transquant_bypass_flag==0)、輝度成分であって(cIdx==0)、適応プライマリ変換フラグapt_flagが1(真)であって(apt_flag==1)、かつ、変換ブロック内の非ゼロ変換係数の総数numSigが閾値ptNumSigTH以上(numSig>=ptNumSigTH)である場合に、プライマリ垂直変換指定フラグpt_ver_flagを可変長符号化し、ビット列を生成する。それ以外の場合、プライマリ垂直変換指定フラグ符号化部392は、プライマリ垂直変換指定フラグpt_ver_flagの符号化を省略する。

以上のようにすることにより、変換スキップ識別子ts_idxが1D_H_TSの場合、プライマリ水平変換指定フラグpt_hor_flagの符号化を省略することができる。同様に、変換スキップ識別子ts_idxが1D_V_TSの場合、プライマリ垂直変換指定フラグpt_ver_flagの符号化を省略することができる。従って、プライマリ水平変換指定フラグpt_hor_flag、及びプライマリ垂直変換指定フラグpt_ver_flagの符号化に係る処理量を低減することができる。また、符号量の増大を抑制することができるので、符号化効率を向上させることができる。

<8.第8の実施の形態>

図40は、その場合の変換部313の主な構成例を示すブロック図である。図40に示されるように、変換部313は、この場合も、図28の場合と基本的に同様の構成を有する。ただし、この場合、プライマリ変換部332は、スケーリング部401およびスケーリング部402を有する。

スイッチ342は、プライマリ水平変換をスキップする場合、変換係数Dをスケーリング部401に供給する。スケーリング部401は、スイッチ342から供給される変換係数Dに対してスケーリングを行う。例えば、スケーリング部401は、供給された変換係数に対して、プライマリ水平変換を実施した場合と同一のノルムになるように正規化するためのN(Nは自然数)ビットのビットシフト演算を行う。スケーリング部401は、スケーリングした変換係数をスイッチ344に供給する。

スイッチ344は、プライマリ垂直変換をスキップする場合、プライマリ水平変換後の変換係数Coeff_Phorを予測残差D'としてスケーリング部402に供給する。スケーリング部402は、スケーリング部401の場合と同様に、スイッチ344から供給されるプライマリ水平変換後の変換係数Coeff_Phorに対してスケーリングを行う。例えば、スケーリング部402は、供給された変換係数に対して、プライマリ垂直変換を実施した場合と同一のノルムになるように正規化するためのN(Nは自然数)ビットのビットシフト演算を行う。スケーリング部402は、スケーリングした予測残差D'を外部に出力する。

このようにすることにより、変換係数のダイナミックレンジ幅を所定の範囲内に抑えることができるので、復号の負荷の増大を抑制することができる。

<9.第9の実施の形態>

<制御情報>

<符号化・復号>

<本技術の適用分野>

例えば、本技術は、鑑賞の用に供される画像を伝送するシステムやデバイスにも適用することができる。また、例えば、本技術は、交通の用に供されるシステムやデバイスにも適用することができる。さらに、例えば、本技術は、セキュリティの用に供されるシステムやデバイスにも適用することができる。また、例えば、本技術は、スポーツの用に供されるシステムやデバイスにも適用することができる。さらに、例えば、本技術は、農業の用に供されるシステムやデバイスにも適用することができる。また、例えば、本技術は、畜産業の用に供されるシステムやデバイスにも適用することができる。さらに、本技術は、例えば火山、森林、海洋等の自然の状態を監視するシステムやデバイスにも適用することができる。また、本技術は、例えば天気、気温、湿度、風速、日照時間等を観測する気象観測システムや気象観測装置に適用することができる。さらに、本技術は、例えば鳥類、魚類、ハ虫類、両生類、哺乳類、昆虫、植物等の野生生物の生態を観測するシステムやデバイス等にも適用することができる。

<多視点画像符号化・復号システムへの適用>

<階層画像符号化・復号システムへの適用>

<コンピュータ>

図41は、上述した一連の処理をプログラムにより実行するコンピュータのハードウエアの構成例を示すブロック図である。

図41に示されるコンピュータ800において、CPU(Central Processing Unit)801、ROM(Read Only Memory)802、RAM(Random Access Memory)803は、バス804を介して相互に接続されている。

バス804にはまた、入出力インタフェース810も接続されている。入出力インタフェース810には、入力部811、出力部812、記憶部813、通信部814、およびドライブ815が接続されている。

入力部811は、例えば、キーボード、マウス、マイクロホン、タッチパネル、入力端子などよりなる。出力部812は、例えば、ディスプレイ、スピーカ、出力端子などよりなる。記憶部813は、例えば、ハードディスク、RAMディスク、不揮発性のメモリなどよりなる。通信部814は、例えば、ネットワークインタフェースよりなる。ドライブ815は、磁気ディスク、光ディスク、光磁気ディスク、または半導体メモリなどのリムーバブルメディア821を駆動する。

以上のように構成されるコンピュータでは、CPU801が、例えば、記憶部813に記憶されているプログラムを、入出力インタフェース810およびバス804を介して、RAM803にロードして実行することにより、上述した一連の処理が行われる。RAM803にはまた、CPU801が各種の処理を実行する上において必要なデータなども適宜記憶される。

コンピュータ(CPU801)が実行するプログラムは、例えば、パッケージメディア等としてのリムーバブルメディア821に記録して適用することができる。その場合、プログラムは、リムーバブルメディア821をドライブ815に装着することにより、入出力インタフェース810を介して、記憶部813にインストールすることができる。

また、このプログラムは、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の伝送媒体を介して提供することもできる。その場合、プログラムは、通信部814で受信し、記憶部813にインストールすることができる。

その他、このプログラムは、ROM802や記憶部813に、あらかじめインストールしておくこともできる。

<本技術の応用>

<第1の応用例:テレビジョン受像機>

チューナ902は、アンテナ901を介して受信される放送信号から所望のチャンネルの信号を抽出し、抽出した信号を復調する。そして、チューナ902は、復調により得られた符号化ビットストリームをデマルチプレクサ903へ出力する。即ち、チューナ902は、画像が符号化されている符号化ストリームを受信する、テレビジョン装置900における伝送部としての役割を有する。

デマルチプレクサ903は、符号化ビットストリームから視聴対象の番組の映像ストリーム及び音声ストリームを分離し、分離した各ストリームをデコーダ904へ出力する。また、デマルチプレクサ903は、符号化ビットストリームからEPG(Electronic Program Guide)などの補助的なデータを抽出し、抽出したデータを制御部910に供給する。なお、デマルチプレクサ903は、符号化ビットストリームがスクランブルされている場合には、デスクランブルを行ってもよい。

デコーダ904は、デマルチプレクサ903から入力される映像ストリーム及び音声ストリームを復号する。そして、デコーダ904は、復号処理により生成される映像データを映像信号処理部905へ出力する。また、デコーダ904は、復号処理により生成される音声データを音声信号処理部907へ出力する。

映像信号処理部905は、デコーダ904から入力される映像データを再生し、表示部906に映像を表示させる。また、映像信号処理部905は、ネットワークを介して供給されるアプリケーション画面を表示部906に表示させてもよい。また、映像信号処理部905は、映像データについて、設定に応じて、例えばノイズ除去などの追加的な処理を行ってもよい。さらに、映像信号処理部905は、例えばメニュー、ボタン又はカーソルなどのGUI(Graphical User Interface)の画像を生成し、生成した画像を出力画像に重畳してもよい。

表示部906は、映像信号処理部905から供給される駆動信号により駆動され、表示デバイス(例えば、液晶ディスプレイ、プラズマディスプレイ又はOELD(Organic ElectroLuminescence Display)(有機ELディスプレイ)など)の映像面上に映像又は画像を表示する。

音声信号処理部907は、デコーダ904から入力される音声データについてD/A変換及び増幅などの再生処理を行い、スピーカ908から音声を出力させる。また、音声信号処理部907は、音声データについてノイズ除去などの追加的な処理を行ってもよい。

外部インタフェース部909は、テレビジョン装置900と外部機器又はネットワークとを接続するためのインタフェースである。例えば、外部インタフェース部909を介して受信される映像ストリーム又は音声ストリームが、デコーダ904により復号されてもよい。即ち、外部インタフェース部909もまた、画像が符号化されている符号化ストリームを受信する、テレビジョン装置900における伝送部としての役割を有する。

制御部910は、CPUなどのプロセッサ、並びにRAM及びROMなどのメモリを有する。メモリは、CPUにより実行されるプログラム、プログラムデータ、EPGデータ、及びネットワークを介して取得されるデータなどを記憶する。メモリにより記憶されるプログラムは、例えば、テレビジョン装置900の起動時にCPUにより読み込まれ、実行される。CPUは、プログラムを実行することにより、例えばユーザインタフェース部911から入力される操作信号に応じて、テレビジョン装置900の動作を制御する。

ユーザインタフェース部911は、制御部910と接続される。ユーザインタフェース部911は、例えば、ユーザがテレビジョン装置900を操作するためのボタン及びスイッチ、並びに遠隔制御信号の受信部などを有する。ユーザインタフェース部911は、これら構成要素を介してユーザによる操作を検出して操作信号を生成し、生成した操作信号を制御部910へ出力する。

バス912は、チューナ902、デマルチプレクサ903、デコーダ904、映像信号処理部905、音声信号処理部907、外部インタフェース部909及び制御部910を相互に接続する。

このように構成されたテレビジョン装置900において、デコーダ904が、上述した画像復号装置100の機能を有するようにしてもよい。つまり、デコーダ904が、符号化データを、以上の各実施の形態において説明した方法で復号するようにしてもよい。このようにすることにより、テレビジョン装置900は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

また、このように構成されたテレビジョン装置900において、映像信号処理部905が、例えば、デコーダ904から供給される画像データを符号化し、得られた符号化データを、外部インタフェース部909を介してテレビジョン装置900の外部に出力させることができるようにしてもよい。そして、その映像信号処理部905が、上述した画像符号化装置300の機能を有するようにしてもよい。つまり、映像信号処理部905が、デコーダ904から供給される画像データを、以上の各実施の形態において説明した方法で符号化するようにしてもよい。このようにすることにより、テレビジョン装置900は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

<第2の応用例:携帯電話機>

アンテナ921は、通信部922に接続される。スピーカ924及びマイクロホン925は、音声コーデック923に接続される。操作部932は、制御部931に接続される。バス933は、通信部922、音声コーデック923、カメラ部926、画像処理部927、多重分離部928、記録再生部929、表示部930、及び制御部931を相互に接続する。

携帯電話機920は、音声通話モード、データ通信モード、撮影モード及びテレビ電話モードを含む様々な動作モードで、音声信号の送受信、電子メール又は画像データの送受信、画像の撮像、及びデータの記録などの動作を行う。

音声通話モードにおいて、マイクロホン925により生成されるアナログ音声信号は、音声コーデック923に供給される。音声コーデック923は、アナログ音声信号を音声データへ変換し、変換された音声データをA/D変換し圧縮する。そして、音声コーデック923は、圧縮後の音声データを通信部922へ出力する。通信部922は、音声データを符号化及び変調し、送信信号を生成する。そして、通信部922は、生成した送信信号を、アンテナ921を介して基地局(図示せず)へ送信する。また、通信部922は、アンテナ921を介して受信される無線信号を増幅し及び周波数変換し、受信信号を取得する。そして、通信部922は、受信信号を復調及び復号して音声データを生成し、生成した音声データを音声コーデック923へ出力する。音声コーデック923は、音声データを伸張し及びD/A変換し、アナログ音声信号を生成する。そして、音声コーデック923は、生成した音声信号をスピーカ924に供給して音声を出力させる。

また、データ通信モードにおいて、例えば、制御部931は、操作部932を介するユーザによる操作に応じて、電子メールを構成する文字データを生成する。また、制御部931は、文字を表示部930に表示させる。また、制御部931は、操作部932を介するユーザからの送信指示に応じて電子メールデータを生成し、生成した電子メールデータを通信部922へ出力する。通信部922は、電子メールデータを符号化及び変調し、送信信号を生成する。そして、通信部922は、生成した送信信号を、アンテナ921を介して基地局(図示せず)へ送信する。また、通信部922は、アンテナ921を介して受信される無線信号を増幅し及び周波数変換し、受信信号を取得する。そして、通信部922は、受信信号を復調及び復号して電子メールデータを復元し、復元した電子メールデータを制御部931へ出力する。制御部931は、表示部930に電子メールの内容を表示させると共に、電子メールデータを記録再生部929に供給し、その記憶媒体に書き込ませる。

記録再生部929は、読み書き可能な任意の記憶媒体を有する。例えば、記憶媒体は、RAM又はフラッシュメモリなどの内蔵型の記憶媒体であってもよく、ハードディスク、磁気ディスク、光磁気ディスク、光ディスク、USB(Universal Serial Bus)メモリ、又はメモリカードなどの外部装着型の記憶媒体であってもよい。

また、撮影モードにおいて、例えば、カメラ部926は、被写体を撮像して画像データを生成し、生成した画像データを画像処理部927へ出力する。画像処理部927は、カメラ部926から入力される画像データを符号化し、符号化ストリームを記録再生部929に供給し、その記憶媒体に書き込ませる。

さらに、画像表示モードにおいて、記録再生部929は、記憶媒体に記録されている符号化ストリームを読み出して画像処理部927へ出力する。画像処理部927は、記録再生部929から入力される符号化ストリームを復号し、画像データを表示部930に供給し、その画像を表示させる。

また、テレビ電話モードにおいて、例えば、多重分離部928は、画像処理部927により符号化された映像ストリームと、音声コーデック923から入力される音声ストリームとを多重化し、多重化したストリームを通信部922へ出力する。通信部922は、ストリームを符号化及び変調し、送信信号を生成する。そして、通信部922は、生成した送信信号を、アンテナ921を介して基地局(図示せず)へ送信する。また、通信部922は、アンテナ921を介して受信される無線信号を増幅し及び周波数変換し、受信信号を取得する。これら送信信号及び受信信号には、符号化ビットストリームが含まれ得る。そして、通信部922は、受信信号を復調及び復号してストリームを復元し、復元したストリームを多重分離部928へ出力する。多重分離部928は、入力されるストリームから映像ストリーム及び音声ストリームを分離し、映像ストリームを画像処理部927、音声ストリームを音声コーデック923へ出力する。画像処理部927は、映像ストリームを復号し、映像データを生成する。映像データは、表示部930に供給され、表示部930により一連の画像が表示される。音声コーデック923は、音声ストリームを伸張し及びD/A変換し、アナログ音声信号を生成する。そして、音声コーデック923は、生成した音声信号をスピーカ924に供給して音声を出力させる。

このように構成された携帯電話機920において、例えば画像処理部927が、上述した画像符号化装置300の機能を有するようにしてもよい。つまり、画像処理部927が、画像データを、以上の各実施の形態において説明した方法で符号化するようにしてもよい。このようにすることにより、携帯電話機920は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

また、このように構成された携帯電話機920において、例えば画像処理部927が、上述した画像復号装置100の機能を有するようにしてもよい。つまり、画像処理部927が、符号化データを、以上の各実施の形態において説明した方法で復号するようにしてもよい。このようにすることにより、携帯電話機920は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

<第3の応用例:記録再生装置>

記録再生装置940は、チューナ941、外部インタフェース(I/F)部942、エンコーダ943、HDD(Hard Disk Drive)部944、ディスクドライブ945、セレクタ946、デコーダ947、OSD(On-Screen Display)部948、制御部949、およびユーザインタフェース(I/F)部950を備える。

チューナ941は、アンテナ(図示せず)を介して受信される放送信号から所望のチャンネルの信号を抽出し、抽出した信号を復調する。そして、チューナ941は、復調により得られた符号化ビットストリームをセレクタ946へ出力する。即ち、チューナ941は、記録再生装置940における伝送部としての役割を有する。

外部インタフェース部942は、記録再生装置940と外部機器又はネットワークとを接続するためのインタフェースである。外部インタフェース部942は、例えば、IEEE(Institute of Electrical and Electronic Engineers)1394インタフェース、ネットワークインタフェース、USBインタフェース、又はフラッシュメモリインタフェースなどであってよい。例えば、外部インタフェース部942を介して受信される映像データおよび音声データは、エンコーダ943へ入力される。即ち、外部インタフェース部942は、記録再生装置940における伝送部としての役割を有する。

エンコーダ943は、外部インタフェース部942から入力される映像データおよび音声データが符号化されていない場合に、映像データおよび音声データを符号化する。そして、エンコーダ943は、符号化ビットストリームをセレクタ946へ出力する。

HDD部944は、映像および音声などのコンテンツデータが圧縮された符号化ビットストリーム、各種プログラムおよびその他のデータを内部のハードディスクに記録する。また、HDD部944は、映像および音声の再生時に、これらデータをハードディスクから読み出す。

ディスクドライブ945は、装着されている記録媒体へのデータの記録および読み出しを行う。ディスクドライブ945に装着される記録媒体は、例えばDVD(Digital Versatile Disc)ディスク(DVD-Video、DVD-RAM(DVD - Random Access Memory)、DVD-R(DVD - Recordable)、DVD-RW(DVD - Rewritable)、DVD+R(DVD + Recordable)、DVD+RW(DVD + Rewritable)等)又はBlu-ray(登録商標)ディスクなどであってよい。

セレクタ946は、映像および音声の記録時には、チューナ941又はエンコーダ943から入力される符号化ビットストリームを選択し、選択した符号化ビットストリームをHDD944又はディスクドライブ945へ出力する。また、セレクタ946は、映像及び音声の再生時には、HDD944又はディスクドライブ945から入力される符号化ビットストリームをデコーダ947へ出力する。

デコーダ947は、符号化ビットストリームを復号し、映像データ及び音声データを生成する。そして、デコーダ947は、生成した映像データをOSD部948へ出力する。また、デコーダ947は、生成した音声データを外部のスピーカへ出力する。

OSD部948は、デコーダ947から入力される映像データを再生し、映像を表示する。また、OSD部948は、表示する映像に、例えばメニュー、ボタン又はカーソルなどのGUIの画像を重畳してもよい。

制御部949は、CPUなどのプロセッサ、並びにRAM及びROMなどのメモリを有する。メモリは、CPUにより実行されるプログラム、及びプログラムデータなどを記憶する。メモリにより記憶されるプログラムは、例えば、記録再生装置940の起動時にCPUにより読み込まれ、実行される。CPUは、プログラムを実行することにより、例えばユーザインタフェース部950から入力される操作信号に応じて、記録再生装置940の動作を制御する。

ユーザインタフェース部950は、制御部949と接続される。ユーザインタフェース部950は、例えば、ユーザが記録再生装置940を操作するためのボタンおよびスイッチ、並びに遠隔制御信号の受信部などを有する。ユーザインタフェース部950は、これら構成要素を介してユーザによる操作を検出して操作信号を生成し、生成した操作信号を制御部949へ出力する。

このように構成された記録再生装置940において、例えばエンコーダ943が、上述した画像符号化装置300の機能を有するようにしてもよい。つまり、エンコーダ943が、画像データを、以上の各実施の形態において説明方法で符号化するようにしてもよい。このようにすることにより、記録再生装置940は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

また、このように構成された記録再生装置940において、例えばデコーダ947が、上述した画像復号装置100の機能を有するようにしてもよい。つまり、デコーダ947が、符号化データを、以上の各実施の形態において説明した方法で復号するようにしてもよい。このようにすることにより、記録再生装置940は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

<第4の応用例:撮像装置>

撮像装置960は、光学ブロック961、撮像部962、信号処理部963、画像処理部964、表示部965、外部インタフェース(I/F)部966、メモリ部967、メディアドライブ968、OSD部969、制御部970、ユーザインタフェース(I/F)部971、およびバス972を備える。

光学ブロック961は、撮像部962に接続される。撮像部962は、信号処理部963に接続される。表示部965は、画像処理部964に接続される。ユーザインタフェース部971は、制御部970に接続される。バス972は、画像処理部964、外部インタフェース部966、メモリ部967、メディアドライブ968、OSD部969、および制御部970を相互に接続する。

光学ブロック961は、フォーカスレンズ及び絞り機構などを有する。光学ブロック961は、被写体の光学像を撮像部962の撮像面に結像させる。撮像部962は、CCD(Charge Coupled Device)又はCMOS(Complementary Metal Oxide Semiconductor)などのイメージセンサを有し、撮像面に結像した光学像を光電変換によって電気信号としての画像信号に変換する。そして、撮像部962は、画像信号を信号処理部963へ出力する。

信号処理部963は、撮像部962から入力される画像信号に対してニー補正、ガンマ補正、色補正などの種々のカメラ信号処理を行う。信号処理部963は、カメラ信号処理後の画像データを画像処理部964へ出力する。

画像処理部964は、信号処理部963から入力される画像データを符号化し、符号化データを生成する。そして、画像処理部964は、生成した符号化データを外部インタフェース部966またはメディアドライブ968へ出力する。また、画像処理部964は、外部インタフェース部966またはメディアドライブ968から入力される符号化データを復号し、画像データを生成する。そして、画像処理部964は、生成した画像データを表示部965へ出力する。また、画像処理部964は、信号処理部963から入力される画像データを表示部965へ出力して画像を表示させてもよい。また、画像処理部964は、OSD部969から取得される表示用データを、表示部965へ出力する画像に重畳してもよい。

OSD部969は、例えばメニュー、ボタン又はカーソルなどのGUIの画像を生成して、生成した画像を画像処理部964へ出力する。

外部インタフェース部966は、例えばUSB入出力端子として構成される。外部インタフェース部966は、例えば、画像の印刷時に、撮像装置960とプリンタとを接続する。また、外部インタフェース部966には、必要に応じてドライブが接続される。ドライブには、例えば、磁気ディスク又は光ディスクなどのリムーバブルメディアが装着され、リムーバブルメディアから読み出されるプログラムが、撮像装置960にインストールされ得る。さらに、外部インタフェース部966は、LAN又はインターネットなどのネットワークに接続されるネットワークインタフェースとして構成されてもよい。即ち、外部インタフェース部966は、撮像装置960における伝送部としての役割を有する。

メディアドライブ968に装着される記録媒体は、例えば、磁気ディスク、光磁気ディスク、光ディスク、又は半導体メモリなどの、読み書き可能な任意のリムーバブルメディアであってよい。また、メディアドライブ968に記録媒体が固定的に装着され、例えば、内蔵型ハードディスクドライブ又はSSD(Solid State Drive)のような非可搬性の記憶部が構成されてもよい。

制御部970は、CPUなどのプロセッサ、並びにRAM及びROMなどのメモリを有する。メモリは、CPUにより実行されるプログラム、及びプログラムデータなどを記憶する。メモリにより記憶されるプログラムは、例えば、撮像装置960の起動時にCPUにより読み込まれ、実行される。CPUは、プログラムを実行することにより、例えばユーザインタフェース部971から入力される操作信号に応じて、撮像装置960の動作を制御する。

ユーザインタフェース部971は、制御部970と接続される。ユーザインタフェース部971は、例えば、ユーザが撮像装置960を操作するためのボタン及びスイッチなどを有する。ユーザインタフェース部971は、これら構成要素を介してユーザによる操作を検出して操作信号を生成し、生成した操作信号を制御部970へ出力する。

このように構成された撮像装置960において、例えば画像処理部964が、上述した画像符号化装置300の機能を有するようにしてもよい。つまり、画像処理部964が、画像データを、以上の各実施の形態において説明した方法で符号化するようにしてもよい。このようにすることにより、撮像装置960は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

また、このように構成された撮像装置960において、例えば画像処理部964が、上述した画像復号装置100の機能を有するようにしてもよい。つまり、画像処理部964が、符号化データを、以上の各実施の形態において説明した方法で復号するようにしてもよい。このようにすることにより、撮像装置960は、図1乃至図40を参照して上述した各実施の形態と同様の効果を得ることができる。

<第5の応用例:ビデオセット>

近年、電子機器の多機能化が進んでおり、その開発や製造において、その一部の構成を販売や提供等として実施する場合、1機能を有する構成として実施を行う場合だけでなく、関連する機能を有する複数の構成を組み合わせ、複数の機能を有する1セットとして実施を行う場合も多く見られるようになってきた。

図46に示されるビデオセット1300は、このような多機能化された構成であり、画像の符号化や復号(いずれか一方でもよいし、両方でも良い)に関する機能を有するデバイスに、その機能に関連するその他の機能を有するデバイスを組み合わせたものである。

図46に示されるように、ビデオセット1300は、ビデオモジュール1311、外部メモリ1312、パワーマネージメントモジュール1313、およびフロントエンドモジュール1314等のモジュール群と、コネクティビティ1321、カメラ1322、およびセンサ1323等の関連する機能を有するデバイスとを有する。

モジュールは、互いに関連するいくつかの部品的機能をまとめ、まとまりのある機能を持った部品としたものである。具体的な物理的構成は任意であるが、例えば、それぞれ機能を有する複数のプロセッサ、抵抗やコンデンサ等の電子回路素子、その他のデバイス等を配線基板等に配置して一体化したものが考えられる。また、モジュールに他のモジュールやプロセッサ等を組み合わせて新たなモジュールとすることも考えられる。

図46の例の場合、ビデオモジュール1311は、画像処理に関する機能を有する構成を組み合わせたものであり、アプリケーションプロセッサ、ビデオプロセッサ、ブロードバンドモデム1333、およびRFモジュール1334を有する。

プロセッサは、所定の機能を有する構成をSoC(System On a Chip)により半導体チップに集積したものであり、例えばシステムLSI(Large Scale Integration)等と称されるものもある。この所定の機能を有する構成は、論理回路(ハードウエア構成)であってもよいし、CPU、ROM、RAM等と、それらを用いて実行されるプログラム(ソフトウエア構成)であってもよいし、その両方を組み合わせたものであってもよい。例えば、プロセッサが、論理回路とCPU、ROM、RAM等とを有し、機能の一部を論理回路(ハードウエア構成)により実現し、その他の機能をCPUにおいて実行されるプログラム(ソフトウエア構成)により実現するようにしてもよい。

図46のアプリケーションプロセッサ1331は、画像処理に関するアプリケーションを実行するプロセッサである。このアプリケーションプロセッサ1331において実行されるアプリケーションは、所定の機能を実現するために、演算処理を行うだけでなく、例えばビデオプロセッサ1332等、ビデオモジュール1311内外の構成を必要に応じて制御することもできる。

ビデオプロセッサ1332は、画像の符号化・復号(その一方または両方)に関する機能を有するプロセッサである。