US 20220115291A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2022/0115291 A1

### KIM et al.

### (54) INSULATING SUBSTRATE AND DUAL-SIDE **COOLED POWER MODULE USING THE** SAME

- (71) Applicants: HYUNDAI MOTOR COMPANY, Seoul (KR); KIA CORPORATION, Seoul (KR)

- (72) Inventors: Hyeon Uk KIM, Hwaseong-si (KR); Jun Hee PARK, Hwaseong-si (KR); Sung Won PARK, Incheon (KR)

- (73) Assignees: HYUNDAI MOTOR COMPANY, Seoul (KR); KIA CORPORATION, Seoul (KR)

- (21) Appl. No.: 17/409,348

- (22)Filed: Aug. 23, 2021

- (30)**Foreign Application Priority Data**

Oct. 13, 2020 (KR) ..... 10-2020-0132097

### Apr. 14, 2022 (43) **Pub. Date:**

### **Publication Classification**

- (51) Int. Cl. H01L 23/373 (2006.01)H01L 23/367 (2006.01)

- (52) U.S. Cl. CPC ..... H01L 23/3735 (2013.01); H01L 23/3675 (2013.01)

#### (57) ABSTRACT

An insulating substrate provided between the semiconductor chip and a cooler in the dual-side cooled power module includes: an inner metal layer configured to face the semiconductor chip; an outer metal layer configured to face the cooler; and an insulating layer interposed between the inner metal layer and the outer metal layer, wherein at least one inner thermal diffusion inductor of a plurality of inner thermal diffusion inductors is inserted into the inner metal layer.

100(110,120,130) 200(210,220,230)

100(110,120,130) 200(210,220,230)

FIG. 2

## FIG. 3

### FIG. 4A

FIG. 4C

FIG. 5A

# MAXIMUM TEMPERATURE 93.04°C

FIG. 5B

## MAXIMUM TEMPERATURE 139.8℃

US 2022/0115291 A1

FIG. 5C

# MAXIMUM TEMPERATURE 91.4°C

### INSULATING SUBSTRATE AND DUAL-SIDE COOLED POWER MODULE USING THE SAME

### CROSS REFERENCE TO RELATED APPLICATION

**[0001]** The present application claims priority to and the benefit of Korean Patent Application No. 10-2020-0132097, filed Oct. 13, 2020, the entire contents of which is incorporated herein for all purposes by this reference.

### TECHNICAL FIELD

**[0002]** The present disclosure relates to an insulating substrate and a dual-side cooled power module using the same.

#### BACKGROUND

**[0003]** In order to drive a hybrid vehicle or an electric vehicle, it is essential to apply an electrically powered motor. Such a motor is controlled by a power module to regulate an operating time point and an output.

**[0004]** Since high-power electricity is continuously applied to the power module, a lot of heat is generated. In order to cool the power module, many methods have been considered. Among them, a dual-side cooled power module has a structure in which substrates are provided on both sides of a semiconductor chip, which is a core component, and coolers are provided on the respective substrates to cool the semiconductor chip from both sides of the semiconductor chip.

**[0005]** Meanwhile, the semiconductor chip is generally bonded to a signal lead by a wire to transmit an operation signal to the semiconductor chip.

**[0006]** Due to the nature of the wire bonding, a surface of the wire is inevitably curved. Thus, a spacer is installed between the substrate and the semiconductor chip to prevent a contact between the wire and the substrate.

**[0007]** Then, in order to effectively dissipate heat generated from the semiconductor chip, substrates are disposed and mounted on both sides of the semiconductor chip. In this case, the substrate needs to not only secure a heat diffusion path for dissipating heat but also secure a path through which an electrical signal is transmitted. For this reason, an insulating substrate in which an insulating material is interposed between conductive materials has been applied.

**[0008]** The contents described as the related art have been provided only to assist in understanding the background of the present disclosure and should not be considered as corresponding to the related art known to those having ordinary skill in the art.

#### SUMMARY

**[0009]** The present disclosure provides an insulating substrate capable of securing a path for diffusing heat generated from a semiconductor chip to improve heat dissipation efficiency, and a dual-side cooled power module using the same.

**[0010]** According to an embodiment of the present disclosure, an insulating substrate provided between a semiconductor chip and a cooler in a dual-side cooled power module includes: an inner metal layer disposed to face the semiconductor chip; an outer metal layer disposed to face the cooler; and an insulating layer interposed between the inner metal layer and the outer metal layer, wherein at least one inner thermal diffusion inductor is inserted into the inner metal layer.

**[0011]** The inner metal layer may be formed as an inner metal plate that is formed of a copper (Cu) material in a plate shape, and the inner thermal diffusion inductor may be formed of a material including at least graphite, and formed in a graphene to be disposed parallel to a surface facing the semiconductor chip among surfaces of the inner metal plate.

**[0012]** The inner thermal diffusion inductor may be disposed on a virtual surface where the inner thermal diffusion inductor is disposed inside the inner metal plate, excluding at least a virtual area transferred vertically from an area in which the semiconductor chip is disposed, along a periphery of the virtual area.

**[0013]** The inner thermal diffusion inductor may be disposed on a virtual surface where the inner thermal diffusion inductor is disposed inside the inner metal plate, including at least an edge of a virtual area transferred vertically from an area in which the semiconductor chip is disposed, along a periphery of the virtual area.

**[0014]** The inner thermal diffusion inductor may be disposed parallel to a center point of the inner metal plate based on a thickness direction.

**[0015]** At least one outer thermal diffusion inductor may be inserted into the outer metal layer.

**[0016]** The outer metal layer may be formed as an outer metal plate that is formed of a copper (Cu) material in a plate shape, and the outer thermal diffusion inductor may be formed of a material including at least graphite, and formed in a graphene to be disposed parallel to a surface facing the semiconductor chip among surfaces of the outer metal plate. **[0017]** According to another embodiment of the present disclosure, a dual-side cooled power module in which a semiconductor chip is provided between a pair of coolers includes: a pair of insulating substrates provided between

the semiconductor chip and the pair of coolers, respectively, each of the insulating substrates including: an inner metal layer disposed to face the semiconductor chip and having at least one inner thermal diffusion inductor inserted therein; an outer metal layer disposed to face a corresponding one of the coolers; and an insulating layer interposed between the inner metal layer and the outer metal layer.

**[0018]** The dual-side cooled power module may further include: a signal lead transmitting and receiving a signal to and from the semiconductor chip; a wire connecting the semiconductor chip and the signal lead to each other; and a spacer disposed between the semiconductor chip and any one of the pair of insulating substrates.

**[0019]** The inner metal layer may be formed as an inner metal plate that is formed of a copper (Cu) material in a plate shape, and the inner thermal diffusion inductor may be formed of a material including at least graphite, and formed in a graphene to be disposed parallel to a surface facing the semiconductor chip among surfaces of the inner metal plate. **[0020]** At least one outer thermal diffusion inductor may be inserted into the outer metal layer.

**[0021]** The outer metal layer may be formed as an outer metal plate that is formed of a copper (Cu) material in a plate shape, and the outer thermal diffusion inductor may be formed of a material including at least graphite, and formed in a graphene to be disposed parallel to a surface facing the semiconductor chip among surfaces of the outer metal plate.

### DRAWINGS

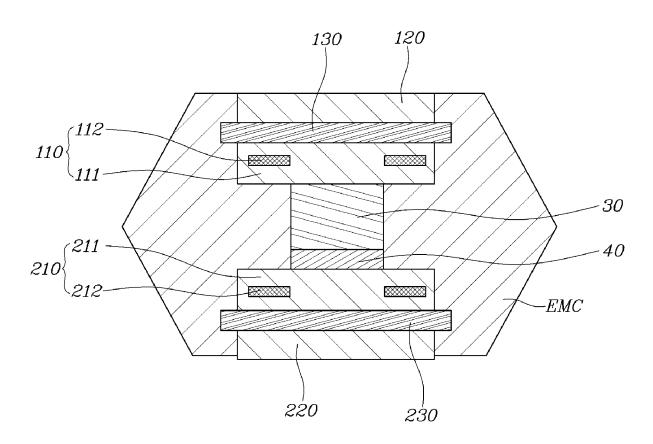

**[0022]** FIG. **1** is a cross-sectional view illustrating a general power module.

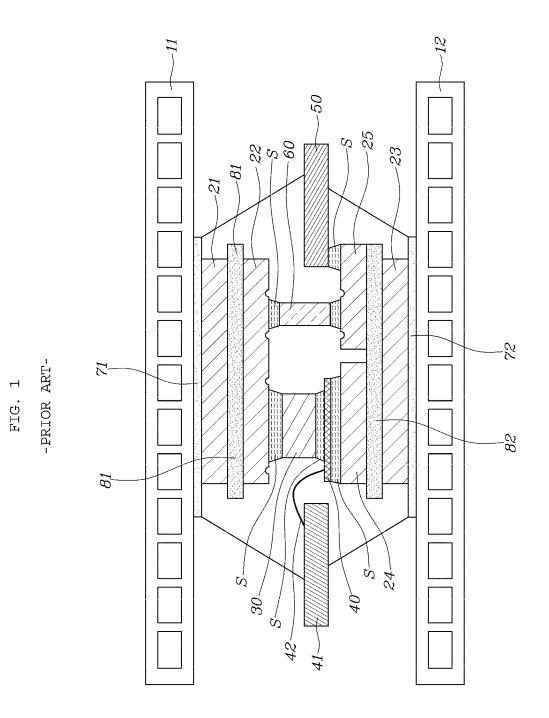

**[0023]** FIG. **2** is a cross-sectional view illustrating an insulating substrate according to an embodiment of the present disclosure.

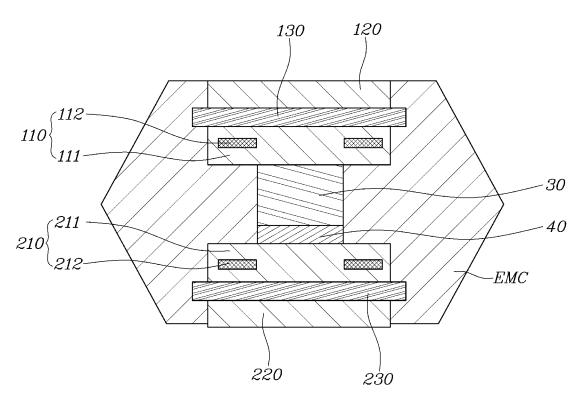

**[0024]** FIG. **3** is a cross-sectional view illustrating an insulating substrate according to another embodiment of the present disclosure.

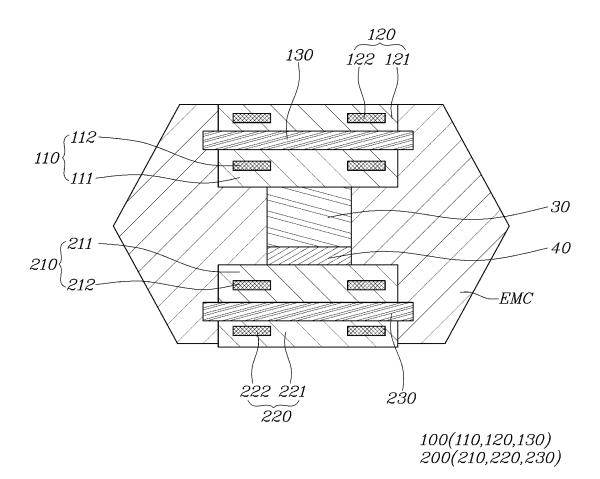

**[0025]** FIGS. **4**A to **4**C are views illustrating heat conduction paths of insulating substrates in an example and comparative examples.

**[0026]** FIGS. **5**A to **5**C are views illustrating degrees of heat diffusion of the insulating substrates in the example and the comparative examples.

#### DETAILED DESCRIPTION

**[0027]** Hereinafter, embodiments of the present disclosure will be described in more detail with reference to the accompanying drawings. However, the present disclosure is not limited to the embodiments to be disclosed below, and may be implemented in various different forms. The embodiments are provided so that the present disclosure will be thorough and complete and will fully convey the scope of the disclosure to those skilled in the art. Like reference numerals in the drawings refer to like elements.

**[0028]** FIG. **1** is a cross-sectional view illustrating a general power module.

[0029] As illustrated in FIG. 1, the general power module includes an upper cooler 11 and a lower cooler 12, with a semiconductor chip 40 disposed between the upper cooler 11 and the lower cooler 12. In this case, insulating substrates are disposed on both sides of the semiconductor chip 40, respectively, between the upper cooler 11 and the lower cooler 12, the insulating substrates including metal layers 21 to 25 formed of a metal material and insulating layers 81 and 82 formed of an insulating material, and the metal layers 21 and 23 are bonded to the upper cooler 11 and the lower cooler 12 by thermal interface materials (TIMs) 71 and 72, respectively.

[0030] In addition, the semiconductor chip 40 is connected to a signal lead 41 via a wire 42. Further, a power lead 50 connected to the semiconductor chip 40 via the metal layer 22 or 25 may be provided, a spacer 30 may be provided to maintain a distance between the metal layer 22 and the semiconductor chip 40, and a via spacer 60 may be provided to maintain a distance between the metal layer 22 and the metal layer 25.

[0031] In addition, by soldering S, the metal layer 22 is bonded to the spacer 30 and the spacer 30 is bonded to the semiconductor chip 40.

[0032] Meanwhile, in order to increase the heat dissipation effect of the insulating substrates, copper (Cu) having good thermal conductivity has been used for the metal layers 22 to 25, and a ceramic material has been used for the insulating layers 81 and 82. However, such a general structure has a problem in that the ceramic material may be damaged during operation due to a difference in thermal expansion coefficient between the copper (Cu) forming the metal layers 81 and 82. Thus, the thickness of the insulating layers 81 and

**82** needs to be secured to some extent. For this reason, there has been a limit in increasing the thickness of the metal layers **22** to **25**.

**[0033]** Recently, an insulating substrate implemented with the insulating layers **81** and **82** formed of an organicinorganic composite material instead of the ceramic material has been used. However, although the insulating substrate to which the organic-inorganic composite material is applied has slightly thicker metal layers **22** to **25** than the insulating substrate to which the ceramic material is applied, the thickness of the metal layers **22** to **25** cannot be increased indefinitely. Thus, there has been a limit in improving the heat dissipation effect.

**[0034]** Meanwhile, attempts have recently been made to improve diffusion of heat emitted from the semiconductor chip 40 through the insulating substrates by placing graphite sheets between the insulating substrates and the coolers 11 and 12, respectively. However, the graphite sheet has low thermal conductivity in a vertical direction, while having good thermal conductivity in a horizontal direction. Thus, it has not been helpful in the dissipation of the heat generated from the semiconductor chip 40 to place the graphite sheets between the insulating substrates and the coolers 11 and 12, respectively.

**[0035]** FIG. **2** is a cross-sectional view illustrating an insulating substrate in some forms of the present disclosure, and FIG. **3** is a cross-sectional view illustrating an insulating substrate in some forms of the present disclosure.

**[0036]** Like the insulating substrates illustrated in FIG. 1, a pair of insulating substrates 100 and 200 are provided between an upper cooler 11 and a semiconductor chip 40 and between the semiconductor chip 40 and a lower cooler 12, respectively, according to an embodiment of the present disclosure.

[0037] In this case, a dual-side cooled power module including the insulating substrates 100 and 200 includes: a signal lead 41 transmitting and receiving a signal to and from the semiconductor chip 40; a wire 42 connecting the semiconductor chip 40 and the signal lead 41 to each other; and a spacer 30 disposed between the semiconductor chip 40 and any one of the pair of insulating substrates 100 and 200. [0038] The components constituting the dual-side cooled power module other than the insulating substrates 100 and 200, and the positions and the bonding method of the insulating substrates 100 and 200 are the same as those in the general power module illustrated in FIG. 1. Thus, overlapping descriptions will be omitted.

**[0039]** Meanwhile, in the present embodiment, the insulating substrates **100** and **200** each have at least one thermal diffusion inductor **112**, **122**, **212**, or **222** inserted thereinto to additionally secure a thermal diffusion path therein.

[0040] More specifically, as illustrated in FIG. 2, the insulating substrates 100 and 200 are divided into a first insulating substrate 100 disposed between the upper cooler 11 and the semiconductor chip 40 and a second insulating substrate 200 disposed between the semiconductor chip 40 and the lower cooler 12. In this case, the first insulating substrate 100 and the second insulating substrate 200 are preferably symmetric to each other with respect to the semiconductor chip 40. Therefore, overlapping descriptions will be described based on the second insulating substrate 200 below.

[0041] Each of the first insulating substrate 100 and the second insulating substrate 200 includes an inner metal layer

110 or 210 disposed to face the semiconductor chip 40; an outer metal layer 120 or 220 disposed to face the cooler 11 or 12; and an insulating layer 130 or 230 interposed between the inner metal layer 110 or 210 and the outer metal layer 120 or 220.

[0042] In this case, the inner metal layer 110 of the first insulating substrate 100 is in indirect contact with the semiconductor chip 40 via the spacer 30. In addition, the inner metal layer 210 of the second insulating substrate 200 is in direct contact with the semiconductor chip 40.

[0043] Each of the inner metal layers 110 and 210 of the first insulating substrate 100 and the second insulating substrate 200 is formed as an inner metal plate 111 or 211 that is formed of a metal material, and at least one inner thermal diffusion inductor 112 or 212 is inserted into the inner metal plate 111 or 211.

**[0044]** The inner metal plates **111** and **211**, which serve to not only dissipate heat generated from the semiconductor chip **40** but also transmit an operation signal or power to the semiconductor chip **40**, are formed of a material that is excellent is thermal conductivity and electrical conductivity. For example, the inner metal plates **111** and **211** are formed of a copper (Cu) material in a plate shape.

**[0045]** In addition, the outer metal layers **120** and **220**, which serve to dissipate heat generated from the semiconductor chip **40**, are formed of a material that is excellent in thermal conductivity. For example, like the inner metal plates **111** and **211**, the outer metal layers **120** and **220** are also formed of a copper (Cu) material in a plate shape.

[0046] On the other hand, the insulating layers 130 and 230 interposed between the inner metal plates 111 and 211 and the outer metal layers 120 and 220, which need to electrically insulate the inner metal plates 111 and 211 and the outer metal layers 120 and 220, respectively, are formed of an insulating material. For example, the insulating layers 130 and 230 are formed of an organic-inorganic composite material in a sheet shape. Of course, the material of the insulating layers 130 and 230 is not limited to the organic-inorganic composite material, and a ceramic material may be applied thereto.

[0047] In addition, the inner thermal diffusion inductors 112 and 212 are formed of a material including at least graphite, preferably a graphite material, each being preferably formed in a graphene to be disposed parallel to a surface facing the semiconductor chip 40 among surfaces of the inner metal plate 111 or 211. In particular, each of the inner thermal diffusion inductors 112 and 212 is preferably disposed parallel to a center point of the inner metal plate 111 or 211 based on a thickness direction. In this case, the center point based on the thickness direction refers to a place around the  $\frac{1}{2}$  point rather than the exact  $\frac{1}{2}$  point based on the thickness direction.

**[0048]** The reason for forming the inner thermal diffusion inductors **112** and **212** in the graphene and disposing the inner thermal diffusion inductors **112** and **212** parallel to the respective surfaces of the inner metal plates **111** and **211**, is that the graphene forming the inner thermal diffusion inductors **112** and **212** has better thermal conductivity in a horizontal direction than in a vertical direction.

**[0049]** Meanwhile, each of the inner thermal diffusion inductors **112** and **212** is preferably disposed on a virtual surface where the inner thermal diffusion inductor **112** or **212** is disposed inside the inner metal plate **111** or **211**, excluding at least a virtual area transferred vertically from

an area in which the semiconductor chip 40 is disposed, along a periphery of the virtual area. For example, as can be seen from FIG. 2, each of the inner thermal diffusion inductors 112 and 212 is inserted into the inner metal plate 111 or 211 at a position slightly out of the virtual area transferred vertically from the area where the semiconductor chip 40 is disposed. In this case, one inner thermal diffusion inductor 112 and one inner thermal diffusion inductor 212 may be inserted into the inner metal plates 111 and 211, respectively, along a periphery of the semiconductor chip 40in a form of a closed curve, or multiple inner thermal diffusion inductors 112 and multiple inner thermal diffusion inductors 212 may be inserted into the inner metal plates 111 and 211, respectively, along the periphery of the semiconductor chip 40, while being spaced apart from each other at a predetermined distance.

**[0050]** This is because, if each of the inner thermal diffusion inductors **112** and **212** is inserted into the virtual area transferred vertically from the area where the semiconductor chip **40** is disposed, the inner thermal diffusion inductors **112** and **212** may rather block heat diffusion paths through which heat generated from the semiconductor chip **40** is transmitted in the vertical direction, thereby reducing heat dissipation efficiency.

[0051] In addition, each of the inner thermal diffusion inductors 112 and 212 may be disposed on the virtual surface where the inner thermal diffusion inductor 112 or 212 is disposed inside the inner metal plate 111 or 211, including an edge of the virtual area transferred vertically from the area in which the semiconductor chip 40 is disposed, along the periphery of the virtual area. For example, as can be seen from FIG. 3, each of the inner thermal diffusion inductors 112 and 212 is inserted into the inner metal plate 111 or 211 at a position slightly including the edge of the virtual area transferred vertically from the area where the semiconductor chip 40 is disposed. In this case as well, one inner thermal diffusion inductor 112 and one inner thermal diffusion inductor 212 may be inserted into the inner metal plates 111 and 211, respectively, along a periphery of the semiconductor chip 40 in a form of a closed curve, or multiple inner thermal diffusion inductors 112 and multiple inner thermal diffusion inductors 212 may be inserted into the inner metal plates 111 and 211, respectively, along the periphery of the semiconductor chip 40, while being spaced apart from each other at a predetermined distance.

[0052] In addition, in the present disclosure, in order to further improve the heat dissipation efficiency of the insulating substrates 100 and 200, thermal diffusion inductors 122 and 222 may also be inserted into the outer metal layers 120 and 220 constituting the insulating substrates 100 and 200, respectively.

[0053] As illustrated in FIG. 3, the insulating substrates 100 and 200 according to another embodiment of the present disclosure include inner metal layers 110 and 210 formed of inner metal plates 111 and 211 and inner thermal diffusion inductors 112 and 212, insulating layers 130 and 230, and outer metal layers 120 and 220, respectively.

[0054] In this case, like the inner metal layers 110 and 210, each of the outer metal layers 120 and 220 is formed as an outer metal plate 121 or 221 that is formed of a metal material, and at least one outer thermal diffusion inductor 122 or 222 is inserted into the outer metal plate 121 or 221. [0055] In addition, the outer metal plates 121 and 221 are formed of a material that is excellent in thermal conductivity

to dissipate heat generated from the semiconductor chip 40. For example, the outer metal plates 121 and 221 are formed of a copper (Cu) material in a plate shape.

[0056] In addition, the outer thermal diffusion inductors 122 and 222 are formed of a material including at least graphite, preferably a graphite material, each being preferably formed in a graphene to be disposed parallel to a surface facing the semiconductor chip 40 among surfaces of the outer metal plate 121 or 221.

[0057] In this case, the outer thermal diffusion inductors 122 and 222 are preferably inserted to be symmetric to the inner thermal diffusion inductors 112 and 212 with respect to the insulating layers 130 and 230, respectively.

**[0058]** Next, heat diffusion characteristics of the insulating substrate according to the present disclosure will be described through an example and comparative examples.

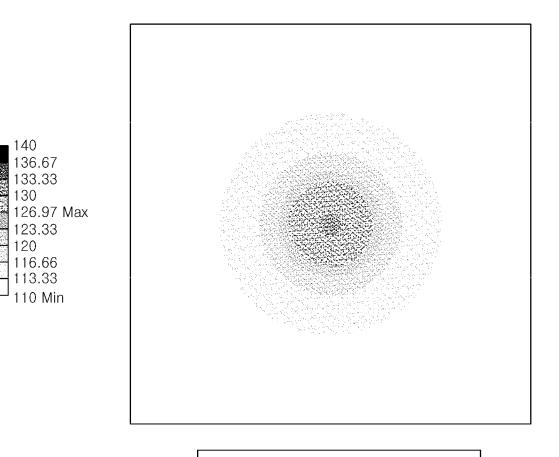

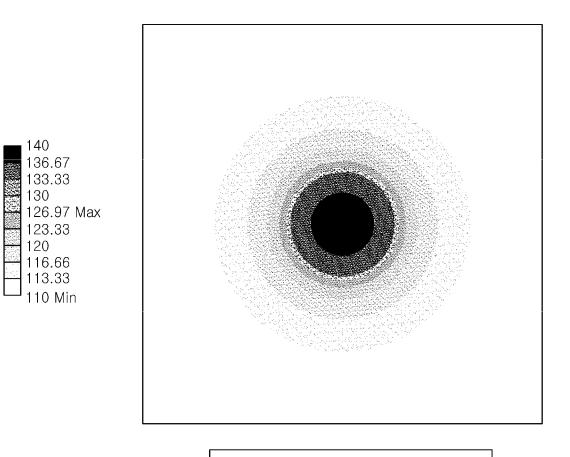

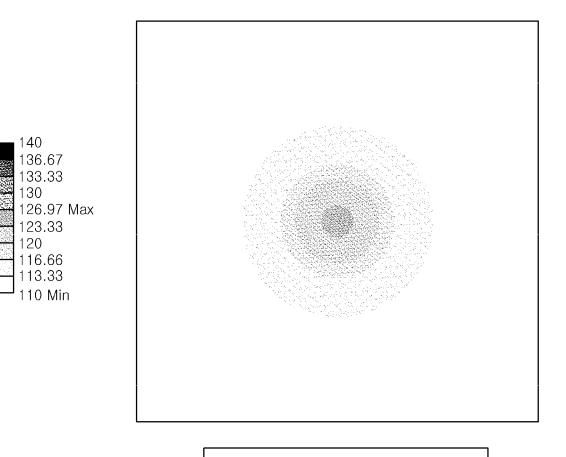

**[0059]** FIGS. **4**A to **4**C are views illustrating heat conduction paths of insulating substrates in an example and comparative examples, and FIGS. **5**A to **5**C are views illustrating degrees of heat diffusion of the insulating substrates in the example and the comparative examples.

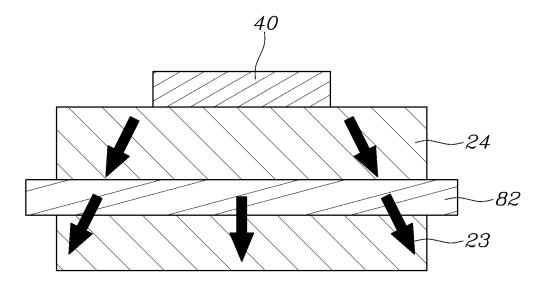

**[0060]** FIG. **4**A illustrates a conventional general insulating substrate as Comparative Example 1. In this insulating substrate, an insulating layer **82** formed of an organic-inorganic composite material is interposed between a pair of metal layers **23** and **24** formed of copper (Cu). A semiconductor chip **40** is mounted on the metal layer **24** for operation.

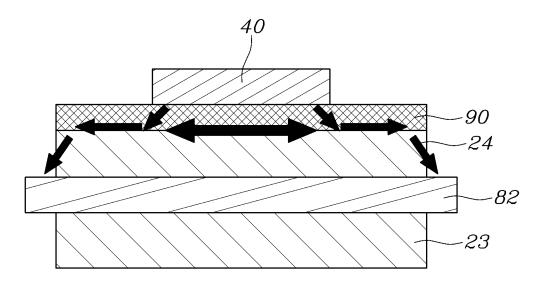

[0061] FIG. 4B illustrates an insulating substrate to which a graphite sheet is applied as Comparative Example 2. In this insulating substrate, an insulating layer 82 formed of an organic-inorganic composite material is interposed between a pair of metal layers 23 and 24 formed of copper (Cu) as in Comparative Example 1. A graphite sheet 90 is interposed between the metal layer 24 and a semiconductor chip 40.

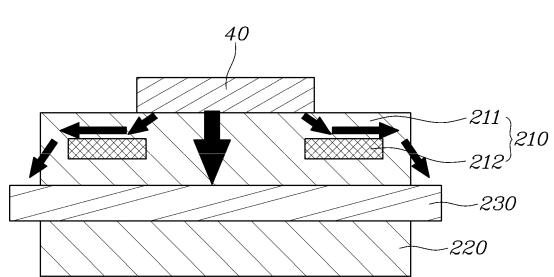

**[0062]** FIG. 4C illustrates an insulating substrate according to an embodiment of the present disclosure as Example. In this insulating substrate, the insulating layer 230 formed of an organic-inorganic composite material is interposed between the inner metal layer 210 and the outer metal layer 220. The semiconductor chip 40 is mounted on the inner metal layer 210 for operation. In this case, the inner metal layer 210 is formed of the inner metal plate 211 that is formed of copper (Cu), and the inner thermal diffusion inductor 212 formed of a graphite material is inserted into the inner metal plate 211. In addition, the outer metal layer 220 is formed of copper (Cu).

**[0063]** In each of Comparative Examples 1 and 2 and Example as illustrated in FIGS. 4A to 4C, in order to check a maximum temperature and a heat distribution state, the semiconductor chip mounted on the insulating substrate was activated until the insulating substrate reached the maximum temperature. The results are as shown in FIGS. 5A to 5C.

[0064] FIG. 5A shows a result of Comparative Example 1, FIG. 5B shows a result of Comparative Example 2, and FIG. 5C is a result of Example. Arrows in FIGS. 5A to 5C indicate heat diffusion paths.

**[0065]** As can be seen from FIGS. **5**A to **5**C, it was confirmed that the maximum temperature was lowest in Example according to the present disclosure, as compared with those in Comparative Examples 1 and 2.

**[0066]** Particularly, when Example was compared with Comparative Example 2 in which the graphite sheet was used, it was confirmed that, although both used a thermal

diffusion means formed of graphite for thermal diffusion, the results were significantly different in terms of the maximum temperature depending on the position of the thermal diffusion means. In addition, in terms of heat distribution, it was also confirmed that heat dissipation was better in Example than in Comparative Example 2.

**[0067]** Therefore, it was confirmed that the heat generated from the semiconductor chip could be effectively dissipated by inserting the thermal diffusion inductor formed of a graphite material in a graphene into the metal plate and disposing the thermal diffusion inductor parallel to the surface of the metal plate as suggested by the present disclosure.

**[0068]** In some forms of the present disclosure, the heat dissipation efficiency of the power module can be improved by inserting the heat diffusion inductor, which is capable of additionally securing a heat diffusion path, into the metal layer constituting the insulating substrate.

**[0069]** In particular, the heat diffusion path can be expanded by forming the heat diffusion inductor with a graphene, which has better thermal conductivity in the horizontal direction than in the vertical direction, and inserting the heat diffusion inductor into the metal layer to be parallel to the surface of the metal layer. Accordingly, an improvement in the heat dissipation efficiency of the power module can be expected.

**[0070]** Although the present disclosure has been shown and described with respect to specific embodiments, it will be apparent to those having ordinary skill in the art that the present disclosure may be variously modified and altered without departing from the spirit and scope of the present disclosure as defined by the following claims.

What is claimed is:

1. An insulating substrate provided between a semiconductor chip and a cooler in a dual-side cooled power module, the insulating substrate comprising:

- an inner metal layer configured to face the semiconductor chip;

- an outer metal layer configured to face the cooler; and

- an insulating layer interposed between the inner metal layer and the outer metal layer,

- wherein at least one inner thermal diffusion inductor of a plurality of inner thermal diffusion inductors is inserted into the inner metal layer.

2. The insulating substrate of claim 1, wherein the inner metal layer is formed as an inner metal plate that is formed of a copper (Cu) material in a plate shape, and

the inner thermal diffusion inductor is formed of a material including at least graphite, and disposed parallel to a surface facing the semiconductor chip among surfaces of the inner metal plate.

**3**. The insulating substrate of claim **2**, wherein the inner thermal diffusion inductor is formed of a graphene.

4. The insulating substrate of claim 2, wherein the inner thermal diffusion inductor is disposed on a virtual surface where the inner thermal diffusion inductor is disposed inside the inner metal plate, excluding at least a virtual area transferred vertically from an area in which the semiconductor chip is disposed, along a periphery of the virtual area.

**5**. The insulating substrate of claim **2**, wherein the inner thermal diffusion inductor is disposed on a virtual surface where the inner thermal diffusion inductor is disposed inside the inner metal plate, including at least an edge of a virtual

6. The insulating substrate of claim 2, wherein the inner thermal diffusion inductor is disposed parallel to a center point of the inner metal plate corresponding to a thickness direction.

7. The insulating substrate of claim 1, wherein at least one outer thermal diffusion inductor of a plurality of outer thermal diffusion inductors is inserted into the outer metal layer.

8. The insulating substrate of claim 7, wherein the outer metal layer is formed as an outer metal plate that is formed of a copper (Cu) material in a plate shape, and

the outer thermal diffusion inductor is formed of a material including at least graphite, and disposed parallel to a surface facing the semiconductor chip among surfaces of the outer metal plate.

9. The insulating substrate of claim 8, wherein the outer thermal diffusion inductor is formed of a graphene.

**10**. A dual-side cooled power module in which a semiconductor chip is provided between a pair of coolers, the dual-side cooled power module comprising:

a pair of insulating substrates provided between the semiconductor chip and the pair of coolers, respectively,

each of the insulating substrates including:

- an inner metal layer configured to face the semiconductor chip and having at least one inner thermal diffusion inductor inserted into the inner metal layer; an outer metal layer configured to face a corresponding cooler; and

- an insulating layer interposed between the inner metal layer and the outer metal layer.

11. The dual-side cooled power module of claim 10, further comprising:

- a signal lead configured to transmit and receive a signal to and from the semiconductor chip;

- a wire connecting the semiconductor chip and the signal lead; and

- a spacer disposed between the semiconductor chip and the pair of insulating substrates.

12. The dual-side cooled power module of claim 10, wherein the inner metal layer is formed as an inner metal plate that is formed of a copper (Cu) material in a plate shape, and

the inner thermal diffusion inductor is formed of a material including at least graphite, and disposed parallel to a surface facing the semiconductor chip among surfaces of the inner metal plate.

**13**. The insulating substrate of claim **12**, wherein the inner thermal diffusion inductor is formed of a graphene.

14. The dual-side cooled power module of claim 10, wherein at least one outer thermal diffusion inductor of a plurality of outer thermal diffusion inductors is inserted into the outer metal layer.

**15**. The dual-side cooled power module of claim **14**, wherein the outer metal layer is formed as an outer metal plate that is formed of a copper (Cu) material in a plate shape, and

the outer thermal diffusion inductor is formed of a material including at least graphite, and disposed parallel to a surface facing the semiconductor chip among surfaces of the outer metal plate.

**16**. The insulating substrate of claim **15**, wherein the outer thermal diffusion inductor is formed of a graphene.

\* \* \* \* \*