2019년10월16일

# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.) G11C 7/10 (2015.01)

(52) CPC특허분류 *G11C 7/1018* (2013.01) G11C 7/1072 (2013.01)

(21) 출원번호 10-2018-0040203

(22) 출워일자 2018년04월06일 심사청구일자 없음

(11) 공개번호 10-2019-0117104

(71) 출원인

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

(43) 공개일자

윤영준

경기도 이천시 증신로291번길 105, 105동 301호( 송정동)

김현숭

경기도 이천시 증신로 278, 102동 1702호 ( 송정동, 풍산아파트)

(74) 대리인

특허법인신성

전체 청구항 수 : 총 16 항

(54) 발명의 명칭 반도체 메모리 장치 및 그의 동작 방법

#### (57) 요 약

본 발명은 제1 및 제2 리드 제어 신호에 기초하여, 앞에 입력된 버스트 순서 정보 신호와 뒤에 입력된 상기 버스 트 순서 정보 신호를 2번 이상 번갈아가며 리드 스케쥴링 신호로서 출력하기 위한 스케쥴러; 복수의 메모리 블록 을 포함하며, 상기 제1 및 제2 리드 제어 신호와 리드 어드레스 신호에 기초하여 상기 복수의 메모리 블록 중 제 1 및 제2 메모리 블록으로부터 제1 및 제2 리드 데이터들을 생성하기 위한 메모리 영역; 및 모드 신호에 기초하 여 상기 제1 리드 데이터들 중 일부와 상기 제2 리드 데이터들의 일부를 2번 이상 번갈아가며 데이터 패드로 출 력하되, 상기 리드 스케쥴링 신호에 기초하여 상기 제1 리드 데이터들을 제1 버스트 순서(burst sequence)에 따 라 상기 데이터 패드로 출력하고 상기 제2 리드 데이터들을 제2 버스트 순서에 따라 상기 데이터 패드로 출력하 기 위한 출력 드라이버을 포함하는 반도체 메모리 장치를 제공한다.

### 대표도

#### 명 세 서

#### 청구범위

#### 청구항 1

제1 및 제2 리드 제어 신호에 기초하여, 앞에 입력된 버스트 순서 정보 신호와 뒤에 입력된 상기 버스트 순서 정보 신호를 2번 이상 번갈아가며 리드 스케쥴링 신호로서 출력하기 위한 스케쥴러;

복수의 메모리 블록을 포함하며, 상기 제1 및 제2 리드 제어 신호와 리드 어드레스 신호에 기초하여 상기 복수의 메모리 블록 중 제1 및 제2 메모리 블록으로부터 제1 및 제2 리드 데이터들을 생성하기 위한 메모리 영역; 및

모드 신호에 기초하여 상기 제1 리드 데이터들 중 일부와 상기 제2 리드 데이터들의 일부를 2번 이상 번갈아가며 데이터 패드로 출력하되, 상기 리드 스케쥴링 신호에 기초하여 상기 제1 리드 데이터들을 제1 버스트 순서 (burst sequence)에 따라 상기 데이터 패드로 출력하고 상기 제2 리드 데이터들을 제2 버스트 순서에 따라 상기데이터 패드로 출력하기 위한 출력 드라이버

를 포함하는 반도체 메모리 장치.

#### 청구항 2

제1항에 있어서.

앞에 입력된 상기 버스트 순서 정보 신호는 상기 제1 버스트 순서를 나타내는 어드레스 신호를 포함하고,

뒤에 입력된 상기 버스트 순서 정보 신호는 상기 제2 버스트 순서를 나타내는 어드레스 신호를 포함하는 반도체 메모리 장치.

#### 청구항 3

제1항에 있어서,

상기 스케쥴러는,

상기 제1 및 제2 리드 제어 신호에 기초하여, 2번 이상 활성화되는 제1 출력 제어 신호와 2번 이상 활성화되는 제2 출력 제어 신호를 생성하기 위한 출력 제어 회로;

제1 및 제2 리드 카운트 신호에 기초하여, 상기 버스트 순서 정보 신호를 입력 순서에 따라 제1 및 제2 정보 신호로서 순차적으로 래치하기 위한 래치 회로; 및

상기 제1 및 제2 출력 제어 신호에 기초하여 상기 제1 및 제2 정보 신호를 교대로 2번 이상 선택하고 그 선택된 정보 신호를 상기 리드 스케쥴링 신호로서 출력하기 위한 출력 회로를 포함하는 반도체 메모리 장치.

#### 청구항 4

제3항에 있어서.

상기 출력 제어 회로는,

상기 제1 리드 제어 신호에 기초하여 상기 제1 및 제2 리드 카운트 신호를 생성하기 위한 제1 카운팅부;

상기 제2 리드 제어 신호에 기초하여 제3 및 제4 리드 카운트 신호를 생성하기 위한 제2 카운팅부; 및

상기 제1 내지 제4 리드 카운트 신호에 기초하여 상기 제1 및 제2 출력 제어 신호를 생성하기 위한 신호 처리부 를 포함하는 반도체 메모리 장치.

#### 청구항 5

제3항에 있어서,

상기 래치 회로는,

상기 제1 리드 카운트 신호에 기초하여 앞서 입력된 상기 버스트 순서 정보 신호를 상기 제1 정보 신호로서 래치하기 위한 제1 래치부; 및

상기 제2 리드 카운트 신호에 기초하여 뒤에 입력된 상기 버스트 순서 정보 신호를 상기 제2 정보 신호로서 래치하기 위한 제2 래치부를 포함하는 반도체 메모리 장치.

#### 청구항 6

제3항에 있어서,

상기 출력 회로는,

상기 제1 출력 제어 신호에 기초하여 상기 제1 정보 신호를 출력 정보 신호로서 2번 이상 출력하기 위한 제1 출력부;

상기 제2 출력 제어 신호에 기초하여 상기 제2 정보 신호를 상기 출력 정보 신호로서 2번 이상 출력하기 위한 제2 출력부; 및

상기 출력 정보 신호를 래치하고 상기 리드 스케쥴링 신호로서 출력하기 위한 래치부를 포함하는 반도체 메모리 장치.

#### 청구항 7

제1항에 있어서,

커맨드 신호에 기초하여 상기 제1 및 제2 리드 제어 신호를 생성하기 위한 상기 커맨드 디코더를 더 포함하고, 상기 커맨드 디코더는 커맨드 신호에 대응하는 상기 제1 리드 제어 신호를 생성하고, 상기 제1 리드 제어 신호 의 토글링 시점보다 예정된 시간 이후에 토글링되는 상기 제2 리드 제어 신호를 생성하는 반도체 메모리 장치.

#### 청구항 8

제1항에 있어서,

상기 메모리 영역은 제1 및 제2 리드 데이터들을 각각 제3 버스트 순서에 따라 생성하고,

상기 제1 내지 제3 버스트 순서는 서로 같거나 또는 서로 다른 반도체 메모리 장치.

#### 청구항 9

제1항에 있어서.

상기 출력 드라이버는 제1 리드 구간 동안 상기 제1 리드 데이터들 중 일부를 상기 데이터 패드를 통해 출력하고, 제2 리드 구간 동안 상기 제2 리드 데이터들 중 일부를 상기 데이터 패드를 통해 출력하고, 제3 리드 구간 동안 상기 제1 리드 데이터들 중 나머지를 상기 데이터 패드를 통해 출력하고, 제4 리드 구간 동안 상기 제2 리드 데이터들 중 나머지를 상기 데이터 패드를 통해 출력하는 반도체 메모리 장치.

#### 청구항 10

제9항에 있어서,

상기 제1 내지 제4 리드 구간은 공백없이 연속되는 반도체 메모리 장치.

#### 청구항 11

제9항에 있어서,

상기 제1 리드 데이터들 중 일부와 상기 제1 리드 데이터들 중 나머지와 상기 제2 리드 데이터들 중 일부와 상기 제2 리드 데이터들 중 나머지는 동일한 버스트 길이(burst length)를 가지는 반도체 메모리 장치.

#### 청구항 12

제1 및 제2 리드 제어 신호에 기초하여, 제1 메모리 블록에 대응하는 버스트 순서 정보 신호와 제2 메모리 블록에 대응하는 버스트 순서 정보 신호를 2번 번갈아가며 리드 스케쥴링 신호로서 출력하는 단계;

상기 리드 스케쥴링 신호에 기초하여, 상기 제1 메모리 블록으로부터 생성된 제1 리드 데이터들 중 제1 버스트 길이(burst length)를 가지는 제1 리드 데이터들을 제1 리드 구간 동안 데이터 패드로 출력하는 단계;

상기 리드 스케쥴링 신호에 기초하여, 상기 제2 메모리 블록으로부터 생성된 제2 리드 데이터들 중 제2 버스트 길이를 가지는 제2 리드 데이터들을 제2 리드 구간 동안 상기 데이터 패드로 출력하는 단계;

상기 리드 스케쥴링 신호에 기초하여, 상기 제1 메모리 블록으로부터 생성된 제1 리드 데이터들 중 제3 버스트 길이를 가지는 제1 리드 데이터들을 제3 리드 구간 동안 상기 데이터 패드로 출력하는 단계; 및

상기 리드 스케쥴링 신호에 기초하여, 상기 제2 메모리 블록으로부터 생성된 제2 리드 데이터들 중 제4 버스트 길이를 가지는 제2 리드 데이터들을 제4 리드 구간 동안 상기 데이터 패드로 출력하는 단계

를 포함하는 반도체 메모리 장치의 동작 방법.

#### 청구항 13

제12항에 있어서.

상기 제1 리드 데이터들은 제1 버스트 순서(burst sequence)에 따라 상기 데이터 패드로 출력되고,

상기 제2 리드 데이터들은 상기 제1 버스트 순서와 같거나 또는 다른 제2 버스트 순서에 따라 상기 데이터 패드로 출력되는 반도체 메모리 장치의 동작 방법.

#### 청구항 14

제12항에 있어서,

상기 제1 내지 제4 버스트 길이는 서로 같은 반도체 메모리 장치의 동작 방법.

### 청구항 15

제12항에 있어서,

상기 제1 내지 제4 리드 구간은 공백없이 연속되는 반도체 메모리 장치.

#### 청구항 16

제12항에 있어서,

상기 리드 스케쥴링 신호로서 출력하는 단계는,

제1 및 제2 리드 제어 신호에 기초하여, 2번 활성화되는 제1 출력 제어 신호를 생성하고 상기 제1 출력 제어 신호와 예정된 시간 간격을 두고 2번 활성화되는 제2 출력 제어 신호를 생성하는 단계;

제1 및 제2 리드 카운트 신호에 기초하여, 상기 버스트 순서 정보 신호를 입력 순서에 따라 제1 및 제2 정보 신호로서 순차적으로 래치하는 단계; 및

상기 제1 및 제2 출력 제어 신호에 기초하여 상기 제1 및 제2 정보 신호를 교대로 2번 선택하고 그 선택된 정보 신호를 상기 리드 스케쥴링 신호로서 출력하는 단계를 포함하는 반도체 메모리 장치의 동작 방법.

#### 발명의 설명

#### 기 술 분 야

[0001] 본 발명은 반도체 설계 기술에 관한 것으로, 더욱 상세하게는 반도체 메모리 장치 및 그의 동작 방법에 관한 것이다.

#### 배경기술

[0003] 반도체 메모리 장치는 모드에 따라 다양한 방식으로 데이터를 입출력할 수 있다. 예컨대, 상기 반도체 메모리 장치는 뱅크 그룹 모드시 서로 다른 뱅크 그룹에 대응하는 리드 제어 신호가 공백없이 입력되는 경우 상기 서로 다른 뱅크 그룹으로부터 공백없이 리드 데이터 신호를 교대로 출력할 수 있다.

## 발명의 내용

#### 해결하려는 과제

[0005] 본 발명의 실시예는 서로 다른 뱅크 그룹으로부터 교대로 리드 데이터를 출력할 때 뱅크 그룹별 리드 버스트 순 서(read burst sequence) 정보가 정상적으로 반영되도록 한 반도체 메모리 장치 및 그의 동작 방법을 제공한다.

#### 과제의 해결 수단

[0006] 본 발명의 일 측면에 따르면, 반도체 메모리 장치는, 제1 및 제2 리드 제어 신호에 기초하여, 앞에 입력된 버스트 순서 정보 신호와 뒤에 입력된 상기 버스트 순서 정보 신호를 2번 이상 번갈아가며 리드 스케쥴링 신호로서 출력하기 위한 스케쥴러; 복수의 메모리 블록을 포함하며, 상기 제1 및 제2 리드 제어 신호와 리드 어드레스 신호에 기초하여 상기 복수의 메모리 블록 중 제1 및 제2 메모리 블록으로부터 제1 및 제2 리드 데이터들을 생성하기 위한 메모리 영역; 및 모드 신호에 기초하여 상기 제1 리드 데이터들 중 일부와 상기 제2 리드 데이터들의 일부를 2번 이상 번갈아가며 데이터 패드로 출력하되, 상기 리드 스케쥴링 신호에 기초하여 상기 제1 리드 데이터들을 제1 버스트 순서(burst sequence)에 따라 상기 데이터 패드로 출력하고 상기 제2 리드 데이터들을 제2 버스트 순서에 따라 상기 데이터 패드로 출력하기 위한 출력 드라이버를 포함할 수 있다.

[0007] 본 발명의 다른 측면에 따르면, 반도체 메모리 장치의 동작 방법은, 제1 및 제2 리드 제어 신호에 기초하여, 제 1 메모리 블록에 대응하는 버스트 순서 정보 신호와 제2 메모리 블록에 대응하는 버스트 순서 정보 신호를 2번 번갈아가며 리드 스케쥴링 신호로서 출력하는 단계; 상기 리드 스케쥴링 신호에 기초하여, 상기 제1 메모리 블록으로부터 생성된 제1 리드 데이터들 중 제1 버스트 길이(burst length)를 가지는 제1 리드 데이터들을 제1 리드 구간 동안 데이터 패드로 출력하는 단계; 상기 리드 스케쥴링 신호에 기초하여, 상기 제2 메모리 블록으로부터 생성된 제2 리드 데이터들 중 제2 버스트 길이를 가지는 제2 리드 데이터들을 제2 리드 구간 동안 상기 데이터 패드로 출력하는 단계; 상기 리드 스케쥴링 신호에 기초하여, 상기 제1 메모리 블록으로부터 생성된 제1 리드 데이터들 중 제3 버스트 길이를 가지는 제1 리드 데이터들을 제3 리드 구간 동안 상기 데이터 패드로 출력하는 단계; 및 상기 리드 스케쥴링 신호에 기초하여, 상기 제2 메모리 블록으로부터 생성된 제2 리드 데이터들 중

제4 버스트 길이를 가지는 제2 리드 데이터들을 제4 리드 구간 동안 상기 데이터 패드로 출력하는 단계를 포함할 수 있다.

#### 발명의 효과

[0009] 본 발명의 실시예는 서로 다른 메모리 블록 - 각각 뱅크 그룹을 포함함 - 으로부터 리드 데이터가 교대로 출력 될 때 리드 버스트 순서(read burst sequence) 정보가 정상적으로 반영되도록 함으로써 반도체 메모리 장치의 동작 신뢰성을 향상시킬 수 있는 효과가 있다.

#### 도면의 간단한 설명

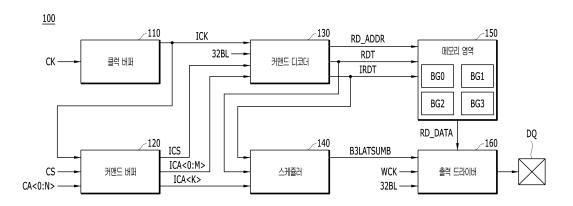

[0011] 도 1은 본 발명의 실시예에 따른 반도체 메모리 장치의 블록 구성도이다.

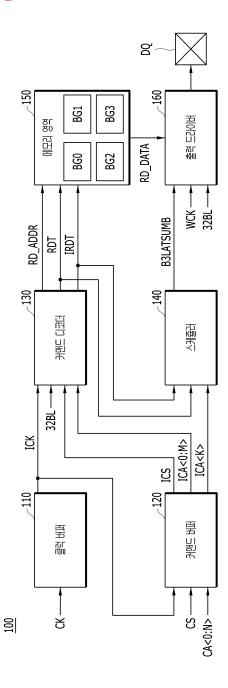

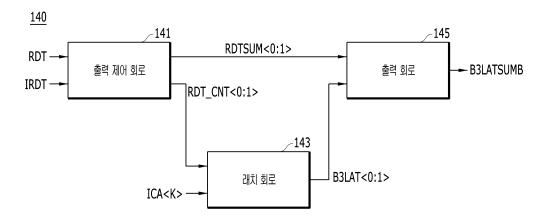

도 2는 도 1에 도시된 스케쥴러의 블록 구성도이다.

도 3은 도 2에 도시된 출력 제어 회로의 블록 구성도이다.

도 4는 도 2에 도시된 래치 회로의 블록 구성도이다.

도 5는 도 2에 도시된 출력 회로의 블록 구성도이다.

도 6은 도 1에 도시된 반도체 메모리 장치의 동작을 설명하기 위한 타이밍도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0012] 이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 실시예를 첨부 도면을 참조하여 설명하기로 한다.

- [0013] 도 1에는 본 발명의 실시예에 따른 반도체 메모리 장치가 블록 구성도로 도시되어 있다.

- [0014] 도 1을 참조하면, 반도체 메모리 장치(100)는 클럭 버퍼(110), 커맨드 버퍼(120), 커맨드 디코더(130), 스케쥴러(140), 및 메모리 영역(150)을 포함할 수 있다.

- [0015] 클럭 버퍼(110)는 클럭 신호(CK)에 기초하여 내부 클럭 신호(ICK)를 생성할 수 있다.

- [0016] 커맨드 버퍼(120)는 커맨드 신호들(CS, CA<0:N>)에 기초하여 내부 커맨드 신호들(ICS, ICA<0:M>)을 생성할 수 있다. 이하에서는 내부 커맨드 신호들(ICS, ICA<0:M>) 중 리드 버스트 순서(read burst sequence)를 나타내는 어드레스 신호를 버스트 순서 정보 신호(ICA<K>)라 칭하여 설명한다.

- [0017] 커맨드 디코더(130)는 내부 클럭 신호(ICK)와 모드 신호(32BL)와 내부 커맨드 신호들(ICS, ICA<0:M>)에 기초하여 리드 어드레스 신호(RD\_ADDR)와 제1 및 제2 리드 제어 신호(RDT, IRDT)를 생성할 수 있다. 특히, 커맨드 디코더(130)는 모드 신호(32BL)에 따라 제1 리드 제어 신호(RDT)를 활성화하고 예정된 시간 이후에 제2 리드 제어 신호(IRDT)를 활성화할 수 있다. 상기 예정된 시간은 아래에서 설명되는 최소의 시간(tCCD\_S)를 포함할 수 있다.

- [0018] 참고로, 모드 신호(32BL)는 모드 레지스터 라이트(mode register write) 회로(도면에 미도시)에 기설정된 신호일 수 있다. 모드 신호(32BL)는 뱅크 그룹 모드에서 지원하는 버스트 랭쓰(burst length) 32 동작 및 버스트 랭쓰 16 동작 중 상기 버스트 랭쓰 32 동작을 나타낼 수 있다.

- [0019] 스케쥴러(140)는 제1 및 제2 리드 제어 신호(RDT, IRDT)와 버스트 순서 정보 신호(ICA<K>)에 기초하여 리드 스케쥴링 신호(B3LATSUMB)를 출력할 수 있다. 예컨대, 스케쥴러(140)는 앞서 입력된 버스트 순서 정보 신호(ICA<K>)와 뒤에 입력된 버스트 순서 정보 신호(ICA<K>)를 2번 번갈아가며 리드 스케쥴링 신호(B3LATSUMB)로서 출력할 수 있다.

- [0020] 메모리 영역(150)은 제1 내지 제4 메모리 블록(BGO ~ BG3)을 포함할 수 있다. 제1 내지 제4 메모리 블록(BGO ~ BG3)은 각각 복수의 뱅크(bank)를 포함하는 뱅크 그룹을 포함할 수 있다. 이하에서는 제1 내지 제4 메모리 블록(BGO ~ BG3)을 제1 내지 제4 뱅크 그룹이라 칭하여 설명한다.

- [0021] 메모리 영역(150)은 리드 어드레스 신호(RD\_ADDR)와 제1 및 제2 리드 제어 신호(RDT, IRDT)에 기초하여 리드 데이터 신호(RD\_DATA)를 생성할 수 있다. 예컨대, 메모리 영역(150)은 리드 어드레스 신호(RD\_ADDR)에 기초하여 제1 내지 제4 뱅크 그룹(BGO ~ BG3) 중 어느 하나의 뱅그 그룹을 선택할 수 있고, 제1 리드 제어 신호(RDT)에 기초하여 그 선택된 뱅크 그룹으로부터 32비트의 리드 데이터(RD\_DATA) 중 16비트의 리드 데이터를 생성할 수 있고, 제2 리드 제어 신호(IRDT)에 기초하여 그 선택된 뱅크 그룹으로부터 상기 32비트의 리드 데이터(RD\_DATA) 중 나머지 16비트의 리드 데이터를 생성할 수 있다. 이하에서는 리드 어드레스 신호(RD\_ADDR)가 연속으로 2번입력되는 경우, 앞서 입력된 리드 어드레스 신호(RD\_ADDR)에 의해 선택된 뱅크 그룹을 제1 뱅크 그룹이라 칭하여설명하고, 뒤에 입력된 리드 어드레스 신호(RD\_ADDR)에 의해 선택된 뱅크 그룹을 제2 뱅크 그룹이라 칭하여설명한다. 아울러, 상기 제1 랭크 그룹으로부터 생성되는 32비트의 리드 데이터(RD\_DATA) 제1 리드 데이터라 칭하여설명하고, 상기 제1 리드 데이터 중 16비트의 리드 데이터를 제1-1 리드 데이터라 칭하여설명하고, 상기 제2 랜크 그룹으로부터 생성되는 32비트의 리드 데이터라 칭하여설명하고, 상기 제2 밴크 그룹으로부터 생성되는 32비트의 리드 데이터를 제2-1 리드 데이터라 칭하여설명하고, 상기 제2 리드 데이터를 제2-2 리드 데이터라 칭하여설명하다.

- [0022] 출력 드라이버(160)는 리드 스케쥴링 신호(B3LATSUMB)와 모드 신호(32BL)와 라이트 클럭 신호(WCK)에 기초하여 제1-1 리드 데이터들과 제1-2 리드 데이터들과 제2-1 리드 데이터들과 제2-2 리드 데이터들을 번갈아가며 데이터 패드로 출력할 수 있다. 예컨대, 출력 드라이버(160)는 앞서 입력된 버스트 순서 정보 신호(ICA<K>)에 포함된 제1 버스트 순서(burst sequence)에 따라 제1 리드 구간 동안 상기 제1-1 및 제1-2 리드 데이터 중 어느 하나를 제1 출력 데이터로서 데이터 패드(DQ)로 출력할 수 있고, 뒤에 입력된 버스트 순서 정보 신호(ICA<K>)에 포함된 제2 버스트 순서에 따라 제2 리드 구간 동안 상기 제2-1 및 제2-2 리드 데이터 중 어느 하나를 제2 출력 데이터로서 데이터 패드(DQ)로 출력할 수 있고, 상기 제1 버스트 순서에 따라 제3 리드 구간 동안 상기 제1-1 및 제1-2 리드 데이터 중 나머지 하나를 제3 출력 데이터로서 데이터 패드(DQ)로 출력할 수 있고, 상기 제2 버스트 순서에 따라 제4 리드 구간 동안 상기 제2-1 및 제2-2 리드 데이터 중 나머지 하나를 제4 출력 데이터로서 데이터 패드(DQ)로 출력할 수 있다.

- [0023] 여기서, 상기 제1 및 제2 버스트 순서는 같거나 또는 다를 수 있다. 상기 제1 내지 제4 리드 구간은 공백없이 연속될 수 있다. 상기 제1 내지 제4 출력 데이터는 각각 16비트에 대응하는 버스트 길이(burst length)를 가질 수 있다.

- [0024] 도 2에는 도 1에 도시된 스케쥴러(140)의 일예를 보인 블록 구성도가 도시되어 있다.

- [0025] 도 2를 참조하면, 스케쥴러(140)는 출력 제어 회로(141), 래치 회로(143), 및 출력 회로(145)를 포함할 수 있다.

- [0026] 출력 제어 회로(141)는 제1 및 제2 리드 제어 신호(RDT, IRDT)에 기초하여, 앞서 입력된 내부 커맨드 신호들 (ICS, ICA<0:M>)에 대응하여 2번 활성화되는 제1 출력 제어 신호(RDTSUM<0>)와 뒤에 입력된 내부 커맨드 신호들 (ICS, ICA<0:M>)에 대응하여 2번 활성화되는 제2 출력 제어 신호(RDTSUM<1>)를 생성할 수 있다.

- [0027] 래치 회로(143)는 제1 및 제2 리드 카운트 신호(RDT\_CNT<0:1>)에 기초하여 버스트 순서 정보 신호(ICA<K>)를 입력 순서에 따라 제1 및 제2 정보 신호(B3LAT<0:1>)로서 순차적으로 래치할 수 있다. 제1 및 제2 리드 카운트 신호(RDT\_CNT<0:1>)는 출력 제어 회로(141)로부터 생성될 수 있으며, 이는 아래에서 자세하게 설명하기로 한다.

- [0028] 출력 회로(145)는 제1 및 제2 출력 제어 신호(RDTSUM<0:1>)에 기초하여 제1 및 제2 정보 신호(B3LAT<0:1>)를 교대로 2번 선택하고 그 선택된 정보 신호를 리드 스케쥴링 신호(B3LATSUMB)로서 출력할 수 있다.

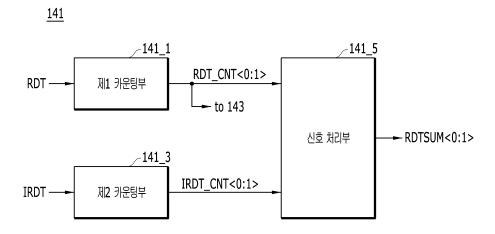

- [0029] 도 3에는 도 2에 도시된 출력 제어 회로(141)의 일예를 보인 블록 구성도가 도시되어 있다.

- [0030] 도 3을 참조하면, 출력 제어 회로(141)는 제1 카운팅부(141\_1), 제2 카운팅부(141\_3), 및 신호 처리부(141\_5)를 포함할 수 있다.

- [0031] 제1 카운팅부(141\_1)는 제1 리드 제어 신호(RDT)에 기초하여 제1 및 제2 리드 카운트 신호(RDT\_CNT<0:1>)를 생성할 수 있다. 예컨대, 제1 카운팅부(141\_1)는 제1 리드 제어 신호(RDT)가 첫 번째 활성화될 때 제1 리드 카운트 신호(RDT\_CNT<0>)를 활성화할 수 있고, 제1 리드 제어 신호(RDT)가 두 번째 활성화될 때 제2 리드 카운트 신호(RDT\_CNT<1>)를 활성화할 수 있다.

- [0032] 제2 카운팅부(141\_3)는 제2 리드 제어 신호(IRDT)에 기초하여 제3 및 제4 리드 카운트 신호(IRDT\_CNT<0:1>)를

생성할 수 있다. 예컨대, 제2 카운팅부(141\_3)는 제2 리드 제어 신호(IRDT)가 첫 번째 활성화될 때 제3 리드 카운트 신호(IRDT\_CNT<0>)를 활성화할 수 있고, 제2 리드 제어 신호(IRDT)가 두 번째 활성화될 때 제4 리드 카운트 신호(IRDT\_CNT<1>)를 활성화할 수 있다.

- [0033] 신호 처리부(141\_5)는 제1 내지 제4 리드 카운트 신호(RDT\_CNT<0:1>, IRDT\_CNT<0:1>)에 기초하여 제1 및 제2 출력 제어 신호(RDTSUM<0:1>)를 생성할 수 있다. 예컨대, 신호 처리부(141\_5)는 제1 및 제3 리드 카운트 신호 (RDT\_CNT<0>, IRDT\_CNT<0>)를 합산(예:논리 합 연산)하여 제1 출력 제어 신호(RDTSUM<0>)를 생성할 수 있고, 제2 및 제4 리드 카운트 신호(RDT\_CNT<1>, IRDT\_CNT<1>)를 합산(예:논리 합 연산)하여 제2 출력 제어 신호 (RDTSUM<1>)를 생성할 수 있다.

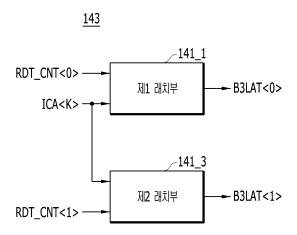

- [0034] 도 4에는 도 2에 도시된 래치 회로(143)의 일예를 보인 블록 구성도가 도시되어 있다.

- [0035] 도 4를 참조하면, 래치 회로(143)는 제1 래치부(143\_1), 및 제2 래치부(143\_3)를 포함할 수 있다.

- [0036] 제1 래치부(143\_1)는 제1 리드 카운트 신호(RDT\_CNT<0>)에 기초하여 앞서 입력된 버스트 순서 정보 신호 (ICA<K>)를 제1 정보 신호(B3LAT<0>)로서 래치할 수 있다.

- [0037] 제2 래치부(143\_3)는 제2 리드 카운트 신호(RDT\_CNT<1>)에 기초하여 뒤에 입력된 버스트 순서 정보 신호 (ICA<K>)를 제2 정보 신호(B3LAT<1>)로서 래치할 수 있다.

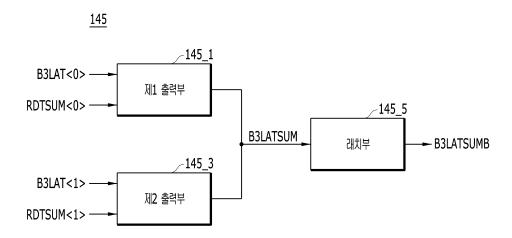

- [0038] 도 5에는 도 2에 도시된 출력 회로(145)의 일예를 보인 블록 구성도가 도시되어 있다.

- [0039] 도 5를 참조하면, 출력 회로(145)는 제1 출력부(145\_1), 제2 출력부(145\_3), 및 래치부(145\_5)를 포함할 수 있다.

- [0040] 제1 출력부(145\_1)는 제1 출력 제어 신호(RDTSUM<0>)에 기초하여 제1 정보 신호(B3LAT<0>)를 출력 정보 신호 (B3LATSUM)로서 2번 출력할 수 있다.

- [0041] 제2 출력부(145\_3)는 제2 출력 제어 신호(RDTSUM<1>)에 기초하여 제2 정보 신호(B3LAT<1>)를 출력 정보 신호 (B3LATSUM)로서 2번 출력할 수 있다.

- [0042] 래치부(145\_5)는 출력 정보 신호(B3LATSUM)를 래치할 수 있고 리드 스케쥴링 신호(B3LATSUMB)로서 출력할 수 있다.

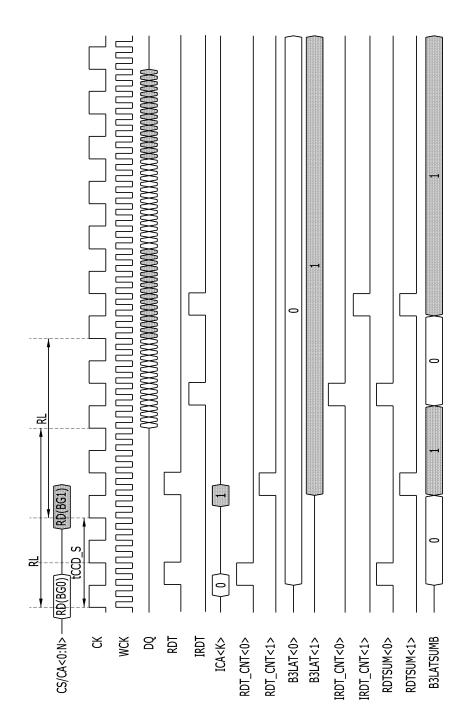

- [0043] 이하, 상기와 같은 구성을 가지는 본 발명의 실시예에 따른 반도체 메모리 장치의 동작을 도 6을 참조하여 설명한다.

- [0044] 도 6에는 본 발명의 실시예에 따른 반도체 메모리 장치(100)의 동작을 설명하기 위한 타이밍도가 도시되어 있다.

- [0045] 도 6을 참조하면, 클럭 버퍼(110)는 클럭 신호(CK)를 버퍼링하여 내부 클럭 신호(ICK)를 생성할 수 있고, 커맨드 버퍼(120)는 커맨드 신호들(CS, CA<0:N>)을 버퍼링하여 내부 커맨드 신호들(ICS, ICA<0:M>)을 생성할 수 있다. 이때, 상기 제1 뱅크 그룹에 대응하는 내부 커맨드 신호들(ICS, ICA<0:M>) 및 버스트 순서 정보 신호 (ICA<K>)가 입력된 다음 상기 제2 뱅크 그룹에 대응하는 내부 커맨드 신호들(ICS, ICA<0:M>) 및 버스트 순서 정보 신호(ICA<K>)가 공백없이 입력될 수 있다. 여기서, 공백없이 입력된다는 것은 서로 다른 뱅크 그룹을 액세스 (access)하기 위한 최소한의 시간(tCCD\_S) 간격으로 입력됨을 의미할 수 있다.

- [0046] 커맨드 디코더(130)는 내부 커맨드 신호들(ICS, ICA<0:M>)에 기초하여 상기 제1 및 제2 뱅크 그룹에 대응하여 상기 최소한의 시간(tCCD\_S) 간격으로 2번 활성화되는 제1 리드 제어 신호(RDT)를 생성할 수 있다. 그리고, 커맨드 디코더(130)는 제1 리드 제어 신호(RDT)를 예정된 시간만큼 지연시킨 제2 리드 제어 신호(IRDT)를 생성할 수 있다. 상기 예정된 시간은 상기 최소한의 시간(tCCD\_S)의 2배에 대응할 수 있다. 또한, 커맨드 디코더(130)는 상기 제1 및 제2 뱅크 그룹에 대응하는 각각의 리드 어드레스 신호(RD\_ADDR)를 순차적으로 생성할 수 있다.

- [0047] 메모리 영역(150)은 리드 어드레스 신호(RD\_ADDR)와 제1 리드 제어 신호(RDT)와 제2 리드 제어 신호(IRDT)에 기초하여 상기 제1 뱅크 그룹으로부터 상기 제1 리드 데이터를 생성하고 상기 제2 뱅크 그룹으로부터 상기 제2 리드 데이터를 생성할 수 있다.

- [0048] 스케쥴러(140)는 제1 리드 제어 신호(RDT)가 첫 번째 활성화될 때 제1 리드 카운트 신호(RDT\_CNT<0>)를 활성화할 수 있고, 제1 리드 제어 신호(RDT)가 두 번째 활성화될 때 제2 리드 카운트 신호(IRDT\_CNT<1>)를 활성화할 수 있고, 제2 리드 제어 신호(IRDT)가 첫 번째 활성화될 때 제3 리드 카운트 신호(IRDT\_CNT<0>)를 활성화할 수

있으며, 제2 리드 제어 신호(IRDT)가 두 번째 활성화될 때 제4 리드 카운트 신호(IRDT\_CNT<1>)를 활성화할 수 있다. 그리고, 스케쥴러(140)는 제1 및 제3 리드 카운트 신호(RDT\_CNT<0>, IRDT\_CNT<0>)를 합산하여 상기 최소한의 시간(tCCD\_S)의 2배에 대응하는 시간 간격으로 2번 활성화되는 제1 출력 제어 신호(RDT\_SUM<0>)를 생성할 수 있고, 제2 및 제4 리드 카운트 신호(RDT\_CNT<1>, IRDT\_CNT<1>)를 합산하여 상기 최소한의 시간(tCCD\_S)의 2배에 대응하는 시간 간격으로 2번 활성화되는 제2 출력 제어 신호(RDT\_SUM<1>)를 생성할 수 있다.

- [0049] 스케쥴러(140)는 제1 및 제2 출력 제어 신호(RDT\_SUM<0:1>)에 기초하여 상기 제1 뱅크 그룹에 대응하는 버스트 순서 정보 신호(ICA<K>)와 상기 제2 뱅크 그룹에 대응하는 버스트 순서 정보 신호(ICA<K>)를 교대로 선택하고 리드 스케쥴링 신호(B3LATSUMB)로서 출력할 수 있다.

- [0050] 출력 드라이버(160)는 리드 스케쥴링 신호(B3LATSUMB)와 모드 신호(32BL)와 라이트 클럭 신호(WCK)에 기초하여 동일한 버스트 길이를 가지는 제1-1 리드 데이터와 제1-2 리드 데이터와 제2-1 리드 데이터와 제2-2 리드 데이터 터를 번갈아가며 데이터 패드(DQ)로 출력할 수 있다.

- [0051] 이때, 상기 제1-1 및 제1-2 리드 데이터는 상기 제1 버스트 순서에 따라 데이터 패드(DQ)로 출력될 수 있고, 상기 제2-1 및 제2-2 리드 데이터는 상기 제2 버스트 순서에 따라 데이터 패드(DQ)로 출력될 수 있다. 여기서, 상기 제1 및 제2 버스트 순서는 같거나 또는 다를 수 있다. 상기 제1 및 제2 버스트 순서는 각각 다음의 표 1 또는 표 2와 같이 정의될 수 있다.

丑 1

| Burst<br>Length | ICA     |   |   |   |   |   |   |   |     |   |    | В  | ırst C | Cycle | Nur | nber | and | Bur | st Ad | dres | s Se | quen     | ce |    |    |    |    |    |    |    |    |    |    |

|-----------------|---------|---|---|---|---|---|---|---|-----|---|----|----|--------|-------|-----|------|-----|-----|-------|------|------|----------|----|----|----|----|----|----|----|----|----|----|----|

| Length          | <k></k> | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8   | 9 | 10 | 11 | 12     | 13    | 14  | 15   | 16  | 17  | 18    | 19   | 20   | 21       | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

| 20              | 0       | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7   | 8 | 9  | Α  | В      | С     | ٥   | Е    | F   | 10  | 11    | 12   | 13   | 14       | 15 | 16 | 17 | 18 | 19 | 1A | 18 | 1C | 1D | 1E | 1F |

| 32              | 1       | 8 | 9 | Α | В | C | ۵ | E | IL. | 0 | 1  | 2  | 3      | 4     | 5   | 6    | 7   | 18  | 19    | 1A   | 18   | 14<br>1C | 1D | 1E | 1F | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

[0053] 표 1과 같이, 버스트 순서 정보 신호(ICA<K>)가 논리 로우 레벨(즉, '0')을 가지면, 32비트의 리드 데이터는 디폴트 값으로 정의된 순서에 따라 순차적으로 출력될 수 있다. 반면, 버스트 순서 정보 신호(ICA<K>)가 논리 하이 레벨(즉, '1')을 가지면, 32비트의 리드 데이터는 상기 디폴트 값에 비하여 8비트 단위로 변경된 순서에 따라 순차적으로 출력될 수 있다.

丑 2

| Burst  | ICA     |    |    |    |    |    |         |    |    |    |    | В  | ırst ( | ycle | Nur | nber | and | Bur | t Ad | dres | s Se | quen | ce |    |    |    |    |    |    |    |    |    |    |

|--------|---------|----|----|----|----|----|---------|----|----|----|----|----|--------|------|-----|------|-----|-----|------|------|------|------|----|----|----|----|----|----|----|----|----|----|----|

| Length | <k></k> | 1  | 2  | 3  | 4  | 5  | 6       | 7  | 8  | 9  | 10 | 11 | 12     | 13   | 14  | 15   | 16  | 17  | 18   | 19   | 20   | 21   | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 |

| 22     | 0       | 0  | 1  | 2  | 3  | 4  | 5<br>15 | 6  | 7  | 8  | 9  | Α  | В      | С    | D   | Е    | F   | 10  | 11   | 12   | 13   | 14   | 15 | 16 | 17 | 18 | 19 | 1A | 18 | 1C | 1D | 1E | 1F |

| 32     | 1       | 10 | 11 | 12 | 13 | 14 | 15      | 16 | 17 | 18 | 19 | 1A | 18     | 10   | 1D  | 1E   | 1F  | 0   | 1    | 2    | 3    | 4    | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F  |

[0055] 표 2와 같이, 버스트 순서 정보 신호(ICA<K>)가 논리 로우 레벨(즉, '0')을 가지면, 32비트의 리드 데이터는 디폴트 값으로 정의된 순서에 따라 순차적으로 출력될 수 있다. 반면, 버스트 순서 정보 신호(ICA<K>)가 논리 하이 레벨(즉, '1')을 가지면, 32비트의 리드 데이터는 상기 디폴트 값에 비하여 16비트 단위로 변경된 순서에 따라 순차적으로 출력될 수 있다.

[0056] 참고로, 본 발명의 실시예에서는 하나의 버스트 순서 정보 신호(ICA<%>)를 이용하는 것을 예로 들어 설명하고 있지만, 반드시 이에 한정되는 것은 아니며, 두 개의 버스트 순서 정보 신호들(ICA<%>, ICA<%'>)를 이용할 수도 있다. 이러한 경우, 다음의 표 3과 같이, 4가지 경우의 버스트 순서를 적용할 수 있을 것이다.

丑 3

| Burst  | ICA       | ICA<br><k></k> |    |    |    |    |    |    |    |    |    |    | В  | ırst ( | Cycle | Nur | nber | and | Burs | t Ad | dres | s Se | quen | ce |    |    |    |    |    |    |    |    |    |   |

|--------|-----------|----------------|----|----|----|----|----|----|----|----|----|----|----|--------|-------|-----|------|-----|------|------|------|------|------|----|----|----|----|----|----|----|----|----|----|---|

| Length | <k'></k'> |                | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12     | 13    | 14  | 15   | 16  | 17   | 18   | 19   | 20   | 21   | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 3 |

| 32     | 0         | 0              | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В      | С     | D   | Ε    | F   | 10   | 11   | 12   | 13   | 14   | 15 | 16 | 17 | 18 | 19 | 1A | 18 | 1C | 1D | 1E | 1 |

|        | 0         | 1              | 8  | 9  | Α  | В  | С  | D  | E  | F  | 0  | 1  | 2  | 3      | 4     | 5   | 6    | 7   | 18   | 19   | 1A   | 18   | 1C   | 1D | 1E | 1F | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 1 |

|        | 1         | 0              | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B     | 10    | 1D  | 1E   | 1F  | 0    | 1    | 2    | 3    | 4    | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | Г |

|        | 1         | 1              | 18 | 19 | 1A | 1B | 1C | 1D | 1E | 1F | 10 | 11 | 12 | 13     | 14    | 15  | 16   | 17  | 8    | 9    | A    | В    | C    | D  | E  | F  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | Г |

[0057]

[0052]

[0054]

- [0058] 요약하면, 반도체 메모리 장치(100)의 동작 방법은, 제1 및 제2 리드 제어 신호(RDT, IRDT)에 기초하여 상기 제 1 뱅크 그룹에 대응하는 버스트 순서 정보 신호(ICA<K>)와 상기 제2 뱅크 그룹에 대응하는 버스트 순서 정보 신호(ICA<K>)와 상기 제2 뱅크 그룹에 대응하는 버스트 순서 정보 신호(ICA<K>)를 2번 번갈아가며 리드 스케쥴링 신호(B3LATSUMB)로서 출력하는 단계와, 리드 스케쥴링 신호(B3LATSUMB)에 기초하여 상기 제1 뱅크 그룹으로부터 생성된 상기 제1-1 리드 데이터를 제1 리드 구간 동안 데이터 패드(DQ)로 출력하는 단계와, 리드 스케쥴링 신호(B3LATSUMB)에 기초하여 상기 제2 뱅크 그룹으로부터 생성된 상기 제2-1 리드 데이터를 제2 리드 구간 동안 데이터 패드(DQ)로 출력하는 단계와, 리드 스케쥴링 신호(B3LATSUMB)에 기초하여 상기 제3 리드 구간 동안 데이터 패드(DQ)로 출력하는 단계와, 리드 스케쥴링 신호(B3LATSUMB)에 기초하여 상기 제2 뱅크 그룹으로부터 생성된 상기 제2-2 리드 데이터를 제4 리드 구간 동안 데이터 패드(DQ)로 출력하는 단계를 포함할 수 있다.

- [0059] 이와 같은 본 발명의 실시예에 따르면, 서로 다른 뱅크 그룹으로부터 리드 데이터를 교대로 출력할 때 각각의 뱅크 그룹에 할당된 리드 버스트 순서 정보 신호를 잃어버리지 않고 정확하게 반영할 수 있는 이점이 있다.

- [0060] 본 발명의 기술 사상은 상기 실시예에 따라 구체적으로 기술되었으나, 이상에서 설명한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 전문가라면 본 발명의 기술 사상의 범위 내에서 여러 가지 치환, 변형 및 변경으로 다양한 실시예가 가능함을 이해할 수 있을 것이다.

#### 부호의 설명

[0062] 100 : 반도체 메모리 장치 110 : 클럭 버퍼

120 : 커맨드 버퍼 130 : 커맨드 디코더

140 : 스케쥴러 150 : 메모리 영역

## 도면3