# (12) UK Patent Application (19) GB (11)

# 2 067 352 A

- (21) Application No 8001060

- (22) Date of filing 11 Jan 1980

- (43) Application published 22 Jul 1981

- (51) INT CL<sup>3</sup> H01L 27/10

- (52) Domestic classification **H1K** 11A3 11C1A 11C1B 11D1 11D 1CA 1FE 1FF 4C11 4C14 9E 9R2 GAB

- (56) Documents cited

GB 1558205

GB 1535615

GB 1516005

IEEE Transactions on

Electron Devices Vol Ed.

26 No. 6, June 1979

Pages 839-852- (in

particular section III J

on page 846)

and pages 853-860- (in

particular section IV B on

page 855)

- (58) Field of search H1K

- (71) Applicants

Mostek Corporation,

1215 West Crosby Road,

Carrollton,

Texas 75006,

United States of America.

- (72) Inventors

Tsiu Chiu Chan

- (74) Agents

Kilburn & Strode,

30 John Street,

London, WC1N 2DD.

# (54) One transistor - one capacitor memory cell

(57) An integrated circuit memory cell pair has its data lines insulated with

respect to the semiconductor substrate at all points other than the point of electrical contact to the transistors of each memory cell. The semiconductor substrate has drain and source regions about the transmission channel of the field effect transistor and has a first capacitor electrode integral with one terminal of the transistor. A first polysilicon layer insulatively disposed relative to the substrate provides a conductive layer 82 for a second capacitor electrode for each memory cell. A second insulatively disposed polysilicon layer provides the gate regions 16,26 of the transistors and the data lines 30,32. The data lines make electrical contact through a self-aligned embedded contact 62. Using this construction, a highly dense memory cell array is achieved without sacrificing capacitor area.

GB 2 067 352 /

# 1/2

FIG. 1

fig. 2

FIG. 3

FIG. 4

FIG. 5

1 GB 2 067 352 A 1

### **SPECIFICATION**

### One transistor-one capacitor memory cell

# 5 Background of the invention Field of the invention

The present invention relates to the field of dynamic memory cells utilized in integrated circuitry. More particularly, the present invention relates to 10 a very high-density integrated circuit memory utilizing a single transistor and a single capacitor for each storage cell.

# Description of the prior art

Memories based on the use of metal oxide silicon field effect transistors (MOSFETs) commonly use a single device per bit. The memory package is typically organized as a two dimensional matrix of rows and columns. The gates of a multiplicity of the

20 MOSFETs of the cells are connected to form a row.

Similarly, a column is formed by coupling the source

or drain regions of the MOSFET in the memory cells.

Any number of rows and columns may be constructed in this manner. Depending upon whether

25 the source or drain is connected to the column line, the source or drain remaining is capacitively coupled to ground. As the column or, as it is often called, the data line and the source or drain region, are constructed of the same material, in the prior art

30 they are constructed as one and the same. In a like sense, one of the capacitor plates also serves as the drain or source of the MOSFET in each memory cell. It is to be particularly noted that the performance of this storage device depends to a large part on the

35 ratio of the capacitance of the storage device to the stray capacitance of the data line. Various prior art methods exist to increase this ratio and are discussed in United States Patent No. 4,012,757.

In the art of memory construction, there is a

40 continuing effort to reduce the substrate area required for the memory cells. The memory cell area occupies a substantial portion of a memory circuit and consitutes a limitation on the reduction of size to be achieved. It is desirable to reduce the size of the

45 memory cells in view of economical considerations, among other reasons. However, as the overall cell size is decreased, the ratio of cell capacitance to data line capacitance also significantly decreases, thereby affecting the performance of the device. Thus, the

50 minimum size of a memory cell is limited by the minimum acceptable memory cell capacitance ratio.

This size limitation, however, is not acceptable because the memory cells now in use in 16K bit

RAMs cannot be used in a 64K bit RAM and still

55 maintain the same package size. See, U.S. Patent 4,012,757 for a memory cell commonly used in 16K bit Random Access Memories.

In a memory cell, the cell area is occupied by four elements. These four elements include the channel area of the transistor, the electrode of the capacitor, the field area isolating the cell from the other cells, and the data line. This is the structure as disclosed in U.S. Patent 4,012,757. A general object of the invention is to remove one of these elements from the substrate level and thereby provide decreased

cell area requirements, without impairing the operation of the device, such as by decreasing the capacitance ratio.

### 70 Summary of the invention

Accordingly the present invention provides an integrated circuit memory formed in a semiconductor substrate having a multiplicity of memory cell pairs, each memory cell pair being coupled to one of a plurality of word select lines of said memory cell pairs which comprises:

a first region including a first transmission channel disposed in said semiconductor substrate of said memory cell pair;

80 a first data line electrically coupled to the first region and insulatively disposed from said semiconductor substrate except at the point of electrical coupling;

a second region including a second transmission 85 channel disposed in said semiconductor substrate of said memory cell pair;

a second data line electrically coupled to said second region and insulatively disposed from said semiconductor substrate except at the point of 90 electrical coupling;

conductive gate means for controlling electrical current flowing in said first and second transmission channels, said gate means being insulatively disposed with respect to the first and second transmission channels in said first and second regions, respectively, said gate means having an electrical contact region for connection to a word select line, said first transmission channel constituting a portion of and being electrically coupled to said first region, and said second transmission channel constituting a portion of and being electrically coupled to said second region; and,

conductive capactive means insulatively disposed with respect to said first and second regions,

105 respectively, said conductive capacitive means defining first and second capacitor regions operable for storing electrical charge, said first capacitor region constituting a portion of said first region and electrically coupled to said first transmission channel, and

110 said second capacitor region constituting a portion of said second region and electrically coupled to said second transmission channel.

## Brief description of the drawings

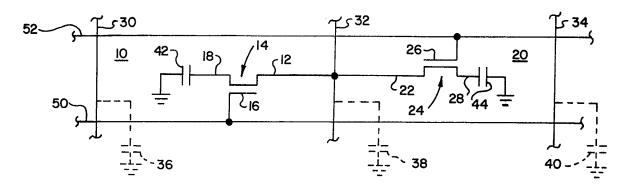

115 Figure 1 is a schematic diagram of two one transistor-one capicitor memory cells.

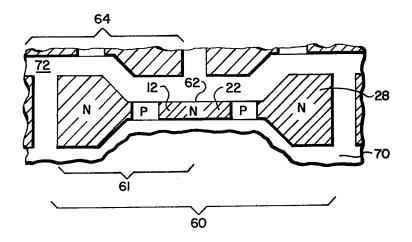

Figure 2 is a top view of the conductive regions forming a first region in the substrate, including a drain, source, capacitor area, and a transmission thannel.

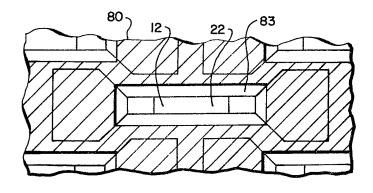

Figure 3 is a top view showing the conductive capacitive means formed by a first polysilicon area.

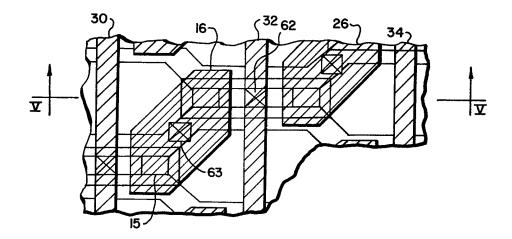

Figure 4 is a top view showing data lines and conductive gates extending between two transmission channels of the transistors in a memory cell pair, the data lines and conductive capacitive means being formed by a second polysilicon layer.

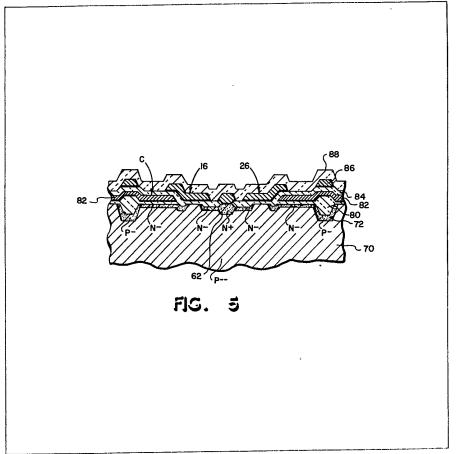

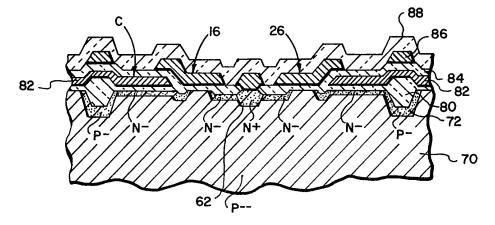

Figure 5 is a cross-section of two memory cells of adjacent memory cell pairs.

130

ľ

Description of the preferred embodiments

The present invention is a one transistor-one capacitor memory cell structure used in integrated memory circuits to store a single information bit. 5 The memory cell is a field effect transistor coupled to a capacitor which is similarly coupled to ground or other reference potential. One terminal of the field effect transistor and a first electrode of the capacitor are an integral unit. This capacitor electrode is 10 physically formed in the substrate and not dependent upon inducement of an inversion field in a first polysilicon layer which may be a continuous layer throughout the memory array with exposure at the transmission channels of the field effect transistors 15 and the point of contact between the data line and a terminal of the field effect transistor. The gate of each field effect transistor is formed in a second polysilicon layer, in which layer the data line is also formed. The data line is electrically isolated from the 20 substrate layer except at the points in which it drops to make contact to the field effect transistor in a memory cell. By placing the data line in an upper layer of polysilicon, more substrate area is provided, thereby providing higher density while maintaining 25 a desired ratio of memory cell capacitance of the data line stray capacitance. Further, the stray capacitance of the data line is decoupled from the substrate potential by the first polysilicon layer, and the problems of a changing substrate potential are 30 avoided in this construction.

It should be clearly understood that the operation of the device is not dependent upon whether the device begins with a P-type or N-type substrate. This in turn effects whether a transistor terminal connected at a particular point is a source or a drain, as it also effects the polarity of the applied potential.

Also, the term "semiconductor substrate" generally means a thick monocrystalline layer of silicon, an epitaxial layer of silicon grown in a supporting base, or a monocrystalline layer grown on an oxide layer which in turn is supported by a thick spinel or sapphire base.

Referring now to the drawings, Figure 1 illustrates a portion of the memory array using a memory cell to store a single bit. This equivalent circuit includes two memory cells 10 and 20. Data lines 30, 32 and 34 have stray capacitances 36, 38 and 40. A source terminal 12 of a transistor 14 is connected to the data line 32 and a source terminal 22 of a transistor 24 of the memory cell 20 is connected to the data line 32. The gate 16 of the transistor 14 is connected to a word line 50, while the gate 26 of the transistor 24 is connected to a word line 52.

The drain terminal 18 of the transistor 12 is also connected to a first electrode of a capacitor 42 whose second electrode is connected to ground. Similarly, the drain terminal 28 of the transistor 24 is connected to the first electrode of a capacitor 44, whose second electrode is connected to ground. In practice, if the capacitor 42 stores a bit of information as a charge on the capacitor 42, a signal applied to the word line 50 causes the transistor 14 to become conductive. When the transistor 14 becomes conductive, the capacitor 42 then discharges to the data line 32 on which the bit of information may be read.

Appropriate circuitry then carries the information to an output and may recharge the capacitor.

The strength of the signal on the data line 32 is in great part dependent on the ratio of the capacitance 70 of capacitor 42 to the stray capacitance 38. However as cell density increases, the area allowable for a large capacitor 42 decreases. In order to achieve a much greater available area for the capacitors of the memory cell, the data line is constructed in a first 75 polysilicon layer separate from the substrate and a second separate polysilicon layer is used for a second electrode of the capacitor of the memory cell. This achieves a substantial increase in available area. In this manner capacitance is not decreased, 80 while much greater memory storage in the same area becomes available. Further, because of the process steps involved in constructing two layers of polysilicon, the first polysilicon layer constituting a second electrode of the capacitor 42 may be grounded. This avoids the fluctuations inherent in any power supply, and further increases the operational effectiveness of the device. The uniqueness of these features can be seen with reference to the

following figures. 90 Figure 2 shows a region 60 comprised of N-type areas and P-type transmissions channels. This region 60 is disposed in a P-type substrate 70. In this region 60, the drains, sources, and channels of two field effect transistors for two memory cells are formed along with the two first electrodes of the two capacitors in the memory cells. The terminals 22 and 12 will also form a point of contact 62 for the data line 32 (see Figure 4). As can be seen, the terminals 12, 22, and the point of contact 62 are a common 100 doped region. It should also be noted that only a portion of the full pattern of regions such as region 60 in a memory array is shown in Figure 2. The region 72 between the region 60 and a similar region such as 64 is a P-type doped region beneath a thick 105 field oxide layer 80 to electrically isolate one region from the other. The left half of a region 60 is designated as a first region disposed in the semiconductor substrate. An arbitrarily designated "memory cell pair" includes the right half of a different region 60 (belonging to the memory cell immediately below the cell which contains the first region) and is designated as a second region disposed in the semiconductor substrate.

In Figure 3, a first continuous layer of polysilicon

115 82 is grown. A window 83 is exposed to allow

contact to be made to the transistor terminals 12 and

22. The transmission channels of the transistors are

also exposed to allow a later process step to grow a

gate region. The continuous layer 82 forms the top

120 electrode of the capacitors 42 and 44 and every other

capacitor in the memory array. This capacitive layer

may then be grounded to provide a common

reference potential for all cells in the memory array.

An oxide layer 84 covers this layer of polysilicon.

A second layer 86 of polysilicon is grown as shown in Figure 4. This layer includes the data lines 30, 32 and 34 and the gates 16 and 26 of the transistors 14 and 24 respectively. As illustrated, the gates are common with another gate region of another mem ory cell extending from a different data line. Thus,

GB 2 067 352 A

for example, the gate 16 of the transistor 14 which is connected to data line 32 is in common with the gate of another transistor in the memory cell which is connected to data line 30. The "X's" within rectang-5 les or contacts 63 in Figure 4 represent contact points. Although not shown in Figure 4, a word line 50 is routed horizontally and is electrically coupled to these gates via contact 63 and will act to turn on the transistors. However, the outputs will be sensed on 10 different data lines. In this manner, a memory matrix is provided. Further memory cell pairs will also be coupled to the same word line.

The data line 32 is embedded in the second polysilicon layer 86 and is insulated at all points 15 other than where it makes contact with transistor pairs such as 14 and 24. At this contact point the oxide has been removed to allow an embedded contact such as contact 62 to be made. Because the embedded contact 62 involves transistor terminals 20 already incorporated in the substrate and a thick oxide has been grown around the contact region through succeeding steps, a self-aligning contact results. This overcomes requirements of greater contact area to insure proper contact and achieves 25 greater density due to the lesser area requirements. Further, with the data lines at a different level in the memory circuit above the substrate, the capacitors and transistors of the memory cells can be more closely packed, achieving greater cell density with-30 out compromising the desired capacitance ratio.

A cross-section taken through the lines 5-5 in Figure 4 is shown in Figure 5. The substrate 70 is P-doped and transistors 14 and 24 are implemented in the surface. The terminals 12, 18, 22 and 28 are 35 N-type, along with the first electrode of the capacitors 42 and 44. A buffer area 72 is P-type. The thick field oxide layer 80 is grown over the substrate with a contact 62 to be formed in successive steps. The first polysilicon layer 82 forms the top electrode of 40 the capacitors 42 and 44. This electrode is preferably grounded. The second polysilicon layer 86 forms the data lines 30, 32 and 34, and the gates 16 and 26 over the channels of the transistors. As seen, the data line 32 forms a contact 62 at the transistors while data 45 lines 30 and 34 are stacked over the first polysilicon capacitive layer 82. The entire circuit is then coated with an insulating oxide 88. Finally, the circuit is

50 as is well known in the art.

Therefore, using the inventive concepts herein disclosed, a memory cell array with much greater density than heretofore available may be achieved

\* without sacrificing capacitor area. Further, using this construction, better memory cell performance is obtained through a more effective capacitor. It is to be understood that further modifications and alterations may be made without departing from the spirit and scope of the present invention.

supplied with appropriate contacts, metal interconnects for the word lines and a protective oxide layer,

#### **CLAIMS**

60

In an integrated circuit memory formed in a semiconductor substrate having a multiplicity of 65 memory cell pairs, each memory cell pair being coupled to one of a plurality of word select lines of said memory and each memory cell pair being coupled to two of a plurality of data lines of said memory, the improvement in each of said memory 70 cell pairs which comprises:

a first region including a first transmission channel disposed in said semiconductor substrate of said memory cell pair;

a first data line electrically coupled to the first

75 region and insulatively disposed from said semiconductor substrate except at the point of electrical

coupling;

a second region including a second transmission channel disposed in said semiconductor substrate of 80 said memory cell pair;

a second data line electrically coupled to said second region and insulatively disposed from said semiconductor substrate except at the point of electrical coupling;

conductive gate means for controlling electrical current flowing in said first and second transmission channels, said gate means being insulatively disposed with respect to the first and second transmission channels in said first and second regions,

90 respectively, said gate means having an electrical contact region for connection to a word select line, said first transmission channel constituting a portion of and being electrically coupled to said first region, and said second transmission channel constituting a

95 portion of and being electrically coupled to said second region; and,

conductive capacitive means insulatively disposed with respect to said first and second regions, respectively, said conductive capacitive means de100 fining first and second capacitor regions operable for storing electrical charge, said first capacitor region constituting a portion of said first region and electrically coupled to said first transmission channel, and said second capacitor region constituting a portion

105 of said second region and electrically coupled to said second transmission channel.

- The integrated circuit memory as set forth in Claim 1 wherein said first and second capacitor regions are diffusion regions disposed in said semi-110 conductor substrate.

- The integrated circuit memory as set forth in any preceding Claim wherein said conductive capacitive means is a continuous layer over at least a section of the integrated circuit memory and exposed at said first and second tranmission channels and at points of electrical coupling of said first and second data lines and said first and second regions,

- 4. The integrated circuit memory as set forth in 120 any preceding Claim wherein said first and second data lines are electrically isolated from said semiconductor substrate at all points other than at the points of electrical coupling of said first and second data lines and said first and second regions, respectively.

respectively.

5. The integrated circuit memory as set forth in any preceding Claim wherein said conductive capacitive means is electrically isolated from and disposed between said semiconductor substrate and said first and second data lines, whereby electrical signals in the first and second data lines are

decoupled from said semiconductor substrate.

- The integrated circuit memory as set forth in any preceding Claim wherein each point of electrical coupling of said first and second data lines and said

first and second regions, respectively, is an embedded contact, self-aligned to said first and second regions.

- The integrated circuit memory as set forth in any preceding Claim wherein said semiconductor

substrate is of P-type doped monocrystalline semiconductor.

Printed for Her Majesty's Stationery Office by Croydon Printing Company Limited, Croydon, Surrey, 1981. Published by The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained. .

j,