### RÉPUBLIQUE FRANÇAISE

#### **INSTITUT NATIONAL** DE LA PROPRIÈTÉ INDUSTRIELLE

**PARIS**

(11) No de publication :

(à n'utiliser que pour les commandes de reproduction)

(21) Nº d'enregistrement national :

97 15159

2 762 930

(51) Int Cl<sup>6</sup>: **H 01 L 29/43,** H 01 L 27/088, 21/8234

#### DEMANDE DE BREVET D'INVENTION

Α1

- (22) **Date de dépôt** : 02.12.97.

- (71) Demandeur(s) : MITSUBISHI DENKI KABUSHIKI KAISHA KABÚSHIKI KAISHA — JP.

- Date de mise à la disposition du public de la demande : 06.11.98 Bulletin 98/45.

- (56) Liste des documents cités dans le rapport de recherche préliminaire : Ce dernier n'à pas été établi à la date de publication de la demande.

- 60 Références à d'autres documents nationaux apparentés :

- Inventeur(s): UENO SHUICHI, OKUMURA YOSHINORÍ, MAEDA SHIGENOBU et MAEGAWA SHI-GETO.

- (73) Titulaire(s) :

- (74) **Mandataire(s)**: CABINET PLASSERAUD.

## DISPOSITIF A SEMICONDUCTEURS AYANT UNE STRUCTURE DE GRILLE DU TYPE SILICIUM POLYCRISTALLIN/SILICIURE ET PROCEDE DE FABRICATION.

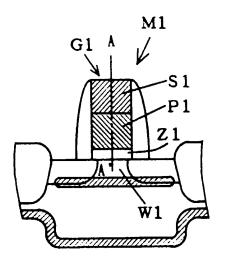

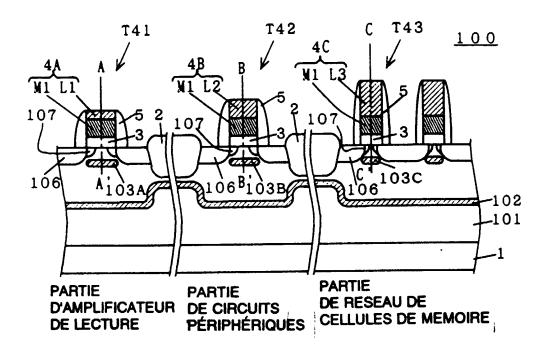

Dans un dispositif conforme à l'invention, des transistors (T41, T42, T43) formés sur un même substrat qui doivent avoir des caractéristiques mutuellement différentes, ont des électrodes de grille (4A, 4B et 4C) qui comprennent respectivement une couche de silicium polycristallin (M1) et une couche de siliciure de tungstène (L1, L2, L3) superposées dans cet ordre sur une pellicule d'oxyde de grille (3). Le rapport entre l'épaisseur de la couche de silicium polycristallin et l'épaisseur de la pellicule de siliciure de tungsténe est fixée en fonction des caractéristiques désirées pour chaque transistor et il modifie l'épaisseur effective de l'isolant de grille en modifiant la distribution d'impuretés dans la couche de silicium polycristallin.

# DISPOSITIF A SEMICONDUCTEURS AYANT UNE STRUCTURE DE GRILLE DU TYPE SILICIUM POLYCRISTALLIN/SILICIURE ET PROCEDE DE FABRICATION

La présente invention concerne un dispositif à semiconducteurs et un procédé de fabrication de celui-ci, et elle concerne plus particulièrement un dispositif à semiconducteurs dans lequel plusieurs types de transistors sont formés dans une seule puce, ainsi qu'un procédé de fabrication d'un tel dispositif à semiconducteurs.

On décrira les quatre exemples classiques suivants, à titre de dispositif à semiconducteurs dans lequel plusieurs types de transistors (par exemple des transistors ayant des spécifications imposées mutuellement différentes) sont formés dans une seule puce.

Premier exemple classique

5

10

15

20

25

Structure d'ensemble d'une mémoire vive dynamique

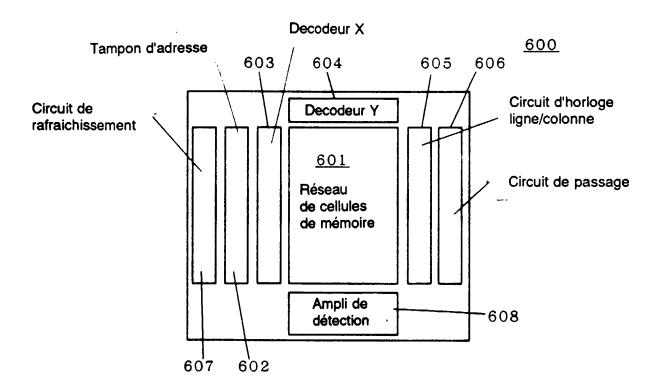

On décrira tout d'abord, à titre de premier exemple classique, une structure d'une mémoire vive dynamique (ou DRAM) 600 dans laquelle plusieurs types de transistors sont formés, ainsi qu'un procédé de fabrication de celle-ci. La structure de la mémoire DRAM 600 (c'est-à-dire la structure de cellule) est représentée sur la figure 76.

La mémoire DRAM 600 comprend non seulement une partie de réseau de cellules de mémoire 601 pour enregistrer des données, mais également une partie de circuits périphériques (c'est-à-dire un tampon d'adresse 602, un décodeur X 603, un décodeur Y 604, une partie d'horloge de ligne/colonne 605, une partie de transmission d'entrée/sortie 606, une partie de régénération 607), une partie d'amplificateur de lecture 608, etc.

Bien que toutes ces parties soient formées par des transistors, les caractéristiques exigées pour ces parties sont mutuellement différentes. Par exemple, la partie de réseau de cellules de mémoire 601 ne tolère qu'un faible courant de fuite, afin d'éviter une disparition de données à cause d'un courant de fuite. D'autre part, un niveau de courant élevé est exigé dans la partie de circuits périphériques, de façon à permettre des opérations à vitesse élevée. En outre, pour distinguer un niveau haut d'un niveau bas, la partie d'amplificateur de lecture 608 doit fonctionner à une tension qui est par exemple la moitié de celle du niveau haut. Dans ce but, un transistor qui est utilisé pour la partie d'amplificateur de lecture 608 doit fonctionner à une tension basse. En résumé, plusieurs types de transistors qui ont des caractéristiques mutuellement différentes sont nécessaires dans la mémoire DRAM qui est fabriquée sous la forme d'une seule puce.

Si l'on compare par exemple des valeurs de seuil, on note qu'une valeur de seuil pour un transistor de la partie de réseau de cellules de mémoire est d'environ 1 V et qu'une valeur de seuil pour des transistors des parties de circuits périphériques est d'environ 0,8 V, tandis qu'une valeur de seuil pour le transistor de la partie d'amplificateur de lecture doit être réduite à une valeur aussi faible que 0,4 V.

Structures des transistors respectifs

5

10

15

20

25

30

35

Une technique classique pour former dans une seule puce ces transistors qui ont des caractéristiques mutuellement différentes, consiste à changer un profil d'impureté d'une couche dopée de canal conformément à un transistor. Dans ce qui suit, on décrira un exemple dans lequel une concentration d'impureté d'une couche dopée de canal est changée conformément à un transistor.

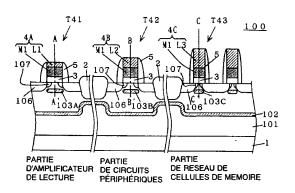

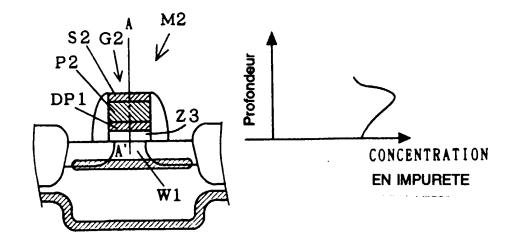

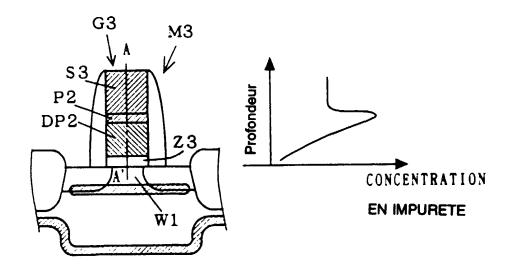

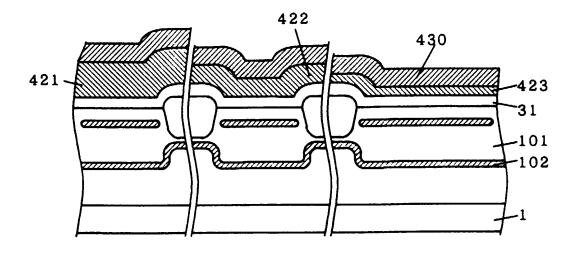

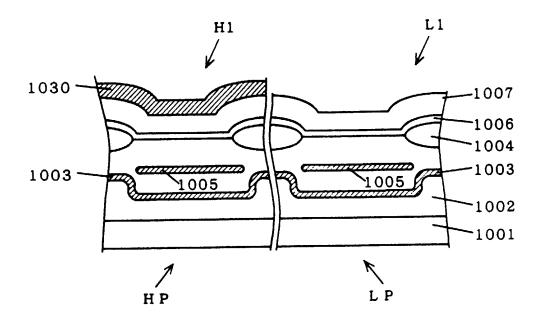

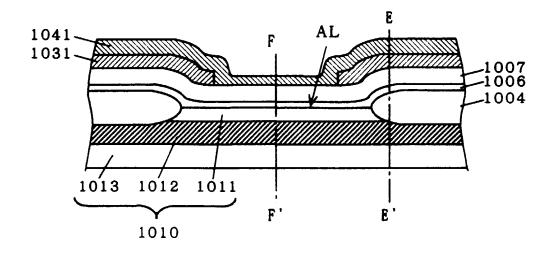

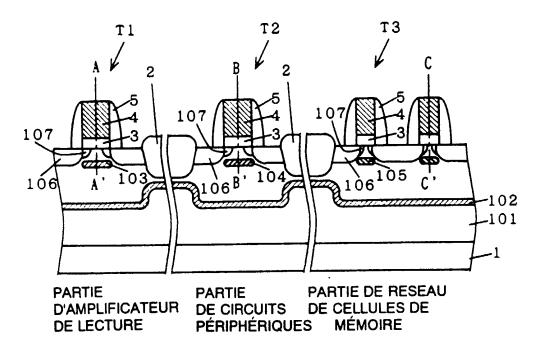

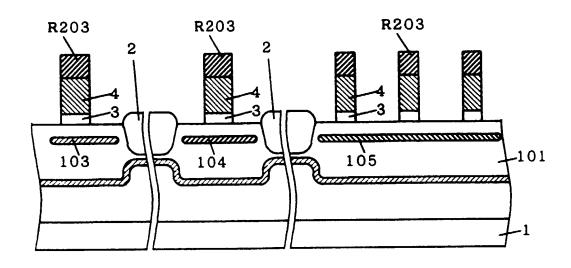

La figure 77 montre (en une vue partielle) un exemple d'une structure d'une mémoire DRAM qui est fabriquée par un procédé de fabrication classique. La figure montre des coupes de transistors MOS à canal N, T1 à T3, qui sont utilisés pour la partie d'amplificateur de lecture, la partie de circuits périphériques et la partie de réseau de cellules de mémoire.

Sur la figure 77, les transistors MOS à canal N T1 à T3 sont formés à l'intérieur d'une couche de caisson de type P 101 qui est formée sur le même substrat semiconducteur 1 (de type P). La couche de caisson 101 fait l'objet d'une séparation entre éléments par une couche de coupure de canal 102 et une couche LOCOS 2 (couche d'oxydation locale

de silicium), de manière que les transistors MOS à canal N T1 à T3 soient formés dans des régions qui sont créées par séparation entre éléments.

Le transistor MOS à canal N T1 de la partie d'amplificateur de lecture comprend une paire de régions de source/drain 106 qui sont formées à l'intérieur de la couche de caisson 101, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches de drain faiblement dopées (que l'on appelle ci-après "couches LDD") 107, formées de façon adjacente à des parties de bords en regard des couches de source/drain 106.

La pellicule d'oxyde de grille 3 est formée sur les couches LDD 107, et une électrode de grille 4 est formée sur la pellicule d'oxyde de grille 3. Une pellicule d'oxyde de paroi latérale 5 est formée sur une surface latérale de la pellicule d'oxyde de grille 3 et de l'électrode de grille 4. Une couche dopée de canal 103 est formée à l'intérieur de la couche de caisson 101, sous l'électrode de grille 4.

10

15

20

25

30

35

Le transistor MOS à canal N T2 de la partie de circuits périphériques comprend une paire de couches de source/drain 106 qui sont formées à l'intérieur de la couche de caisson 101, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 107.

La pellicule d'oxyde de grille 3 est formée sur les couches LDD 107 et une électrode de grille 4 est formée sur la pellicule d'oxyde de grille 3. La pellicule d'oxyde de paroi latérale 5 est formée sur une surface latérale de la pellicule d'oxyde de grille 3 et de l'électrode de grille 4. Une couche dopée de canal 104 est formée à l'intérieur de la couche de caisson 101, sous l'électrode de grille 4.

Le transistor MOS à canal N T3 de la partie de réseau de cellules de mémoire comprend une paire de couches de source/drain 106 formées à l'intérieur de la couche de caisson 101, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 107.

Une pellicule d'oxyde de grille 3 est formée sur les couches de source/drain 106 et sur les couches LDD 107, et une électrode de grille 4 est formée sur la pellicule d'oxyde de grille 3. La pellicule d'oxyde de paroi latérale 5 est formée sur une surface latérale de la pellicule d'oxyde

de grille 3 et de l'électrode de grille 4. Une couche dopée de canal 105 est formée à l'intérieur de la couche de caisson 101, sous l'électrode de grille 4. La partie de réseau de cellules de mémoire a une structure de réseau de grilles dans laquelle des grilles adjacentes se partagent une même couche de source/drain 106. De telles structures sont disposées en succession.

5

Le Tableau 1 indique des valeurs numériques concernant les structures des transistors MOS à canal N T1 à T3.

TABLEAU 1

|                                | Partie d'amplificateur             | Partie de circuits                 | Partie de réseau de                |

|--------------------------------|------------------------------------|------------------------------------|------------------------------------|

|                                | de lecture (T1)                    | périphériques (T2)                 | cellules de mémoire (T3)           |

| Epaisseur de pellicule d'oxyde | 400 nm                             | 400 nm                             | 400 nm                             |

| de champ                       |                                    |                                    |                                    |

| Epaisseur de pellicule d'oxyde | 10 nm                              | 10 nm                              | 10 nm                              |

| de grille                      |                                    |                                    |                                    |

| Epaisseur de pellicule         | 200 nm                             | 200 nm                             | 200 nm                             |

| d'électrode de arille          |                                    |                                    |                                    |

| Concentration en impureté de   | $5 \times 10^{20} \text{ cm}^{-3}$ | $5 \times 10^{20} \text{ cm}^{-3}$ | $5 \times 10^{20} \text{ cm}^{-3}$ |

| grille                         |                                    |                                    |                                    |

| Paroi latérale                 | 100 nm                             | 100 nm                             | 100 nm                             |

|                                |                                    |                                    |                                    |

| Caisson                     | B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> | B 700 keV 1 × 10 13 cm <sup>-2</sup>                   |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Courbe de coupilre de canal | B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> | B 130 keV $5 \times 10^{12} \text{ cm}^{-2}$           |

| Course donée de canal       | B 50 keV 1 x 10 <sup>12</sup> cm <sup>-2</sup> B 50 keV 3 x 10 <sup>12</sup> cm <sup>-2</sup> B 50 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup>    | B 50 keV $5 \times 10^{12} \text{ cm}^{-2}$            |

| Courche LDD                 | As 30 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> As 30 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> As 30 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> | As 30 keV 1 $\times$ 10 <sup>13</sup> cm <sup>-2</sup> |

| Couche de source/drain      | As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup> | As 50 keV $5 \times 10^{15} \text{ cm}^{-2}$           |

|                             |                                                                                                                                                 |                                                        |

60 min

850°C

Traitement thermique

Dans le Tableau 1, les doses d'impureté pour former les couches dopées de canal des transistors MOS à canal N T1, T2 et T3 sont respectivement de 1  $\times$  10<sup>12</sup> cm<sup>-2</sup>, 3  $\times$  10<sup>12</sup> cm<sup>-2</sup> et 5  $\times$  10<sup>12</sup> cm<sup>-2</sup>. On implante du bore (B) à titre d'impureté pour chacune des couches, avec une énergie d'implantation de 50 keV.

5

10

15

20

25

30

35

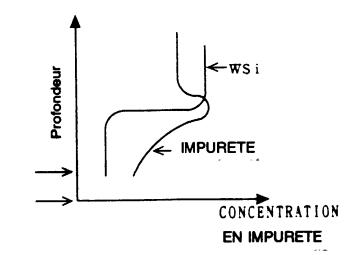

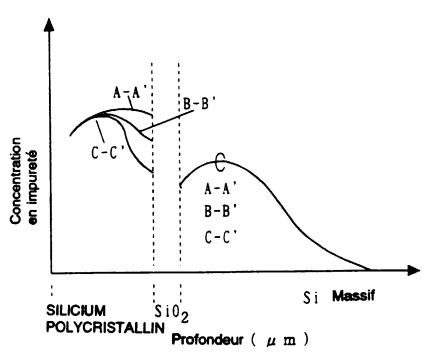

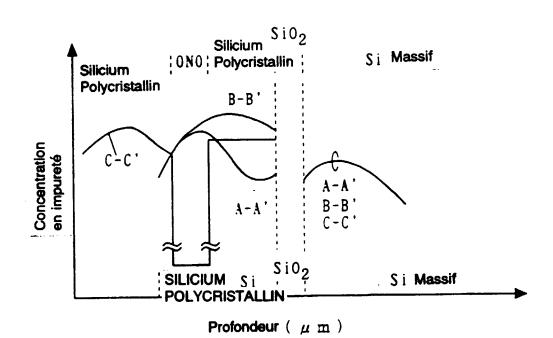

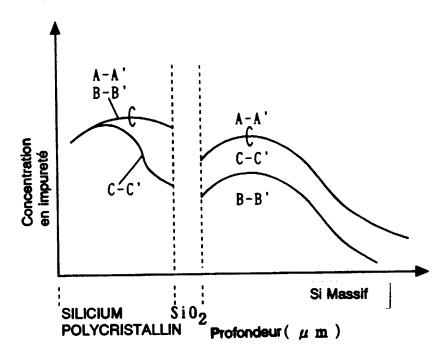

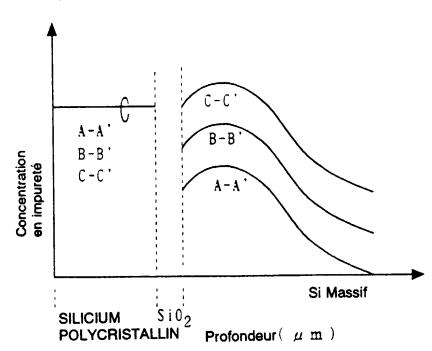

La figure 78 montre des profils d'impureté des transistors MOS à canal N T1, T2 et T3 formant la partie d'amplificateur de lecture, la partie de circuits périphériques et la partie de réseau de cellules de mémoire, qui sont tous représentés sur la figure 77, ces profils correspondant respectivement à des coupes selon la ligne A-A', la ligne B-B' et la ligne C-C'.

Sur la figure 78, une position (en profondeur) dans une direction de coupe est représentée sur un axe horizontal et une concentration en impureté est représentée sur un axe vertical. En partant du côté gauche sur l'axe horizontal on trouve, dans cet ordre, l'électrode de grille (couche de silicium polycristallin), la pellicule d'oxyde de grille (couche de  $SiO_2$ ) et la couche de caisson (couche de silicium massif).

Comme représenté dans le Tableau 1, la concentration en impureté dans l'électrode de grille reste uniformément à la même valeur pour tous les transistors, et par conséquent la ligne A-A', la ligne B-B' et la ligne C-C' sont placées l'une sur l'autre et représentées sous la forme de lignes droites en superposition. D'autre part, dans la couche de caisson, comme décrit précédemment, la dose de canal est plus faible pour un transistor qui exige une valeur de seuil inférieure (c'est-à-dire T1 < T2 < T3), et par conséquent la concentration en impureté est faible à une interface entre la pellicule d'oxyde et le matériau massif. Une position de pic de chaque profil est approximativement la même qu'une position à laquelle chaque couche dopée de canal est formée.

Procédé de fabrication des transistors respectifs

On va maintenant décrire, en se référant aux figures 79 à 84, un procédé de fabrication des transistors MOS à canal N T1, T2 et T3 de la partie d'amplificateur de lecture, de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire, qui sont représentés sur la figure 77.

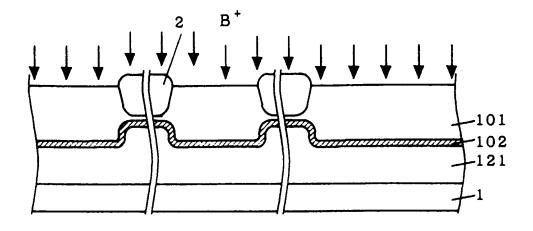

A une étape qui est représentée sur la figure 79, on forme la couche LOCOS 2 (c'est-à-dire la pellicule d'oxyde de champ) avec une

épaisseur qui est par exemple de 400 nm, par un procédé LOCOS, sur une surface du substrat semiconducteur 1 du type P. A la suite de ceci, on implante par exemple des ions de bore avec une énergie de 700 keV et une dose de 1  $\times$  10  $^{13}$  cm  $^{-2}$ , pour former ainsi une région de caisson de type P 101 à l'intérieur du substrat semiconducteur 1. Bien que l'on forme également une région de caisson de type N dans le substrat semiconducteur 1, pour former des transistors MOS à canal P, ceci n'est pas représenté et la description sera omise. Ensuite, on implante par exemple des ions de bore avec une énergie de 130 keV et une dose de 5  $\times$  10  $^{12}$  cm  $^{-2}$ , pour former ainsi la couche de coupure de canal 102 à l'intérieur du substrat semiconducteur 1. La couche de coupure de canal 102 est formée avec une forme qui, conjointement à la couche LOCOS 2, crée les régions avec séparation entre éléments.

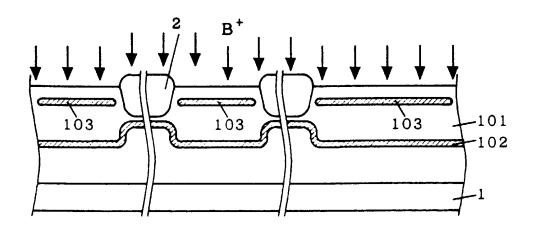

Ensuite, à une étape qui est représentée sur la figure 80, on forme à une position prédéterminée à l'intérieur de la région de caisson 101 la couche dopée de canal 103 qui a la plus faible concentration en impureté, correspondant au transistor T1 de la partie d'amplificateur de lecture. A ce stade, on forme également la couche dopée de canal 103 dans des régions qui se trouvent à l'intérieur des transistors T2 et T3 de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire. On forme la couche dopée de canal 103 par implantation d'ions de bore, par exemple, avec une énergie de 50 keV et une dose de 1 ×  $10^{12}$  cm<sup>-2</sup>.

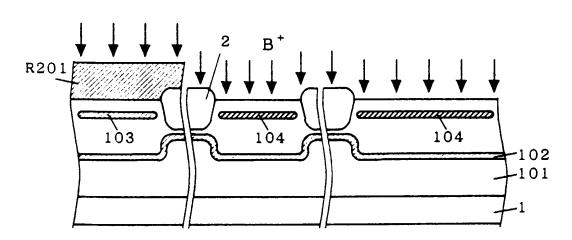

Ensuite, à l'étape qui est représentée sur la figure 81, on forme un masque de matière de réserve R201 sur la partie d'amplificateur de lecture. On implante en outre une impureté de manière sélective dans la couche dopée de canal 103 de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire, pour former ainsi la couche dopée de canal 104 qui a une concentration en impureté correspondant au transistor T2 de la partie de circuits périphériques. A ce stade, on forme également la couche dopée de canal 104 dans une région qui se trouve à l'intérieur du transistor T3 de la partie de réseau de cellules de mémoire. On forme la couche dopée de canal 104 en implantant des ions de bore, par exemple, avec une énergie de 50 keV et une dose de 2 × 10<sup>12</sup> cm<sup>-2</sup>.

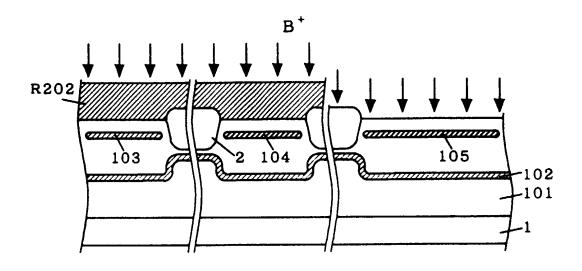

Ensuite, à une étape qui est représentée sur la figure 82, on

forme un masque de matière de réserve R202 sur la partie d'amplificateur de lecture et la partie de circuits périphériques, et on implante en outre une impureté de manière sélective dans la couche dopée de canal 104 de la partie de réseau de cellules de mémoire, pour former ainsi la couche dopée de canal 105 qui a une concentration en impureté correspondant au transistor T3 de la partie de réseau de cellules de mémoire. On forme la couche dopée de canal 105 en implantant des ions de bore, par exemple, avec une énergie de 50 keV et une dose de 2 x 10<sup>12</sup> cm<sup>-2</sup>.

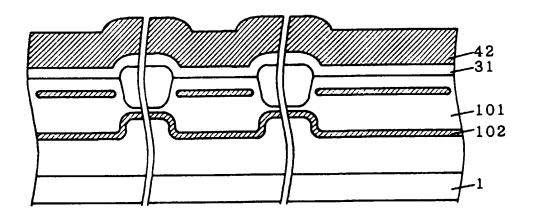

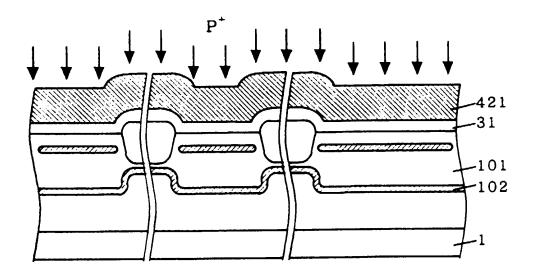

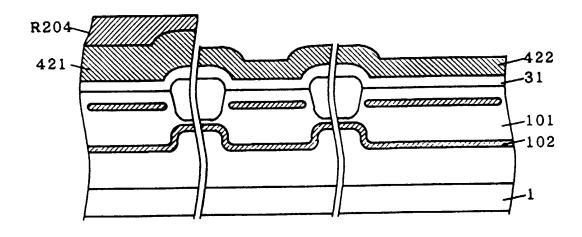

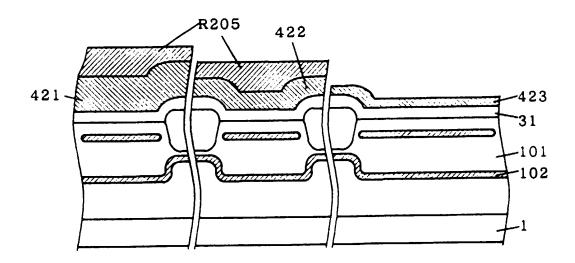

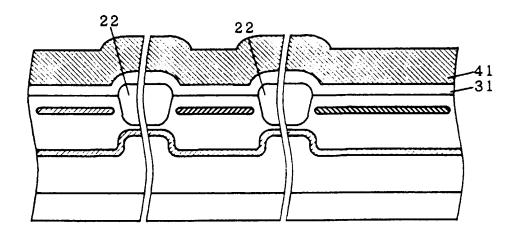

Ensuite, à une étape qui est représentée sur la figure 83, après avoir formé sur une surface principale du substrat semiconducteur 1, par un procédé d'oxydation thermique, une pellicule d'oxyde 31 qui deviendra la pellicule d'oxyde de grille 3, on forme par exemple une couche de silicium polycristallin dopé 41, à titre de matériau d'électrode de grille sur la pellicule d'oxyde 31, par un procédé de dépôt chimique en phase vapeur, ou CVD. La pellicule d'oxyde 31 a une épaisseur d'environ 10 nm, tandis que la couche de silicium polycristallin dopé 41 a une épaisseur d'environ 200 nm. On utilise du phosphore (P) à titre d'impureté. La concentration de l'impureté est d'environ  $5 \times 10^{20} \text{ cm}^{-3}$ .

Ensuite, à une étape qui est représenté sur la figure 84, on forme un masque de matière de réserve R203 sur la couche de silicium polycristallin dopé 41. En définissant un motif, on forme l'électrode de grille 4 et la pellicule d'oxyde de grille 3.

A la suite de ceci, après avoir formé les couches LDD 107 dans la partie d'amplificateur de lecture, la partie de circuits périphériques et la partie de réseau de cellules de mémoire, par implantation ionique, on forme la pellicule d'oxyde de paroi latérale 5 sur une surface latérale de la pellicule d'oxyde de grille 3 et de l'électrode de grille 4, en lui donnant une épaisseur d'environ 100 nm. En utilisant à titre de masque la pellicule d'oxyde de paroi latérale 5, et en procédant par implantation ionique, on forme les couches de source/drain 106. De cette manière, on obtient la structure de la mémoire DRAM qui est représentée sur la figure 77.

On obtient les couches LDD en injectant par exemple des ions d'arsenic (As), avec une énergie de 30 keV et une dose de  $1\times10^{13}$  cm<sup>-2</sup>. D'autre part, on obtient les couches de source/drain 106 en injectant par

exemple des ions d'arsenic, avec une énergie de 50 keV et une dose de  $1\times10^{15}~\text{cm}^{-2}$ , et en effectuant ensuite un recuit à 850°C pendant 60 minutes.

Bien que ceci soit suivi par la formation d'un condensateur, d'une pellicule d'isolation inter-couche, d'une couche d'interconnexion et autres, pour former la mémoire DRAM, ces étapes ne seront pas décrites et elles ne sont pas représentées dans les dessins.

Problèmes affectant la mémoire DRAM classique

5

10

15

20

25

30

35

Comme décrit ci-dessus, dans la mémoire DRAM classique, pour former des transistors qui ont des caractéristiques mutuellement différentes et qui sont utilisés dans la partie d'amplificateur de lecture, la partie de circuits périphériques et la partie de réseau de cellules de mémoire et autres, dans une seule puce, on change la concentration en impureté de la couche dopée de canal en correspondance avec chaque transistor, et on ajuste la valeur de seuil.

Cependant, plus la concentration en impureté de la couche dopée de canal est élevée, plus la valeur de seuil devient grande. Simultanément, du fait que la concentration en impureté est élevée dans une partie de jonction entre une couche de diffusion et le substrat, un courant de fuite provenant de la couche de diffusion (c'est-à-dire la fuite de couche de diffusion) augmente. En d'autres termes, il existe une relation de compromis entre la valeur de seuil et la fuite de couche de diffusion, et par conséquent un courant de fuite est automatiquement déterminé une fois que la valeur de seuil est déterminée. Ainsi, la relation de compromis entre les deux impose une restriction à la conception du circuit. Second exemple classique

Structure d'ensemble d'une mémoire flash

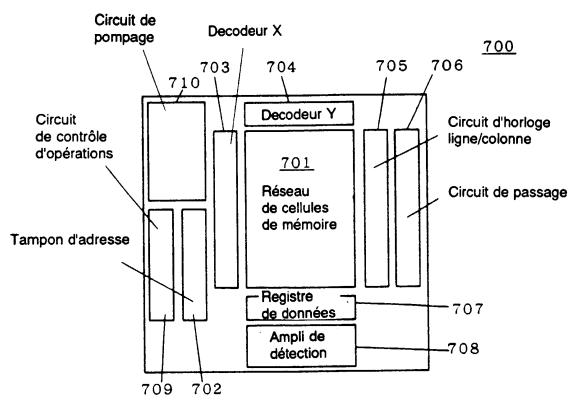

A titre de second exemple classique, on décrira une structure d'une mémoire flash 700 dans laquelle plusieurs types de transistors sont formés, ainsi qu'un procédé de fabrication de cette mémoire.

La figure 85 montre une structure de la mémoire flash 700 (structure de cellule). De façon générale, une mémoire flash diffère d'une mémoire DRAM par l'utilisation d'une tension élevée, telle que 10 V, pour l'écriture et l'effacement. Dans ce but, un circuit de pompe de charge 710 est incorporé à titre de circuit élévateur dans la mémoire flash 700 qui

est représentée sur la figure 85.

La mémoire flash 700 comprend non seulement une partie de réseau de cellules de mémoire 701 pour enregistrer des données, mais également une partie supportant une tension élevée, telle qu'un décodeur X 703 et un décodeur Y 704, qui est utilisée après l'élévation de tension, une partie de circuits périphériques (c'est-à-dire un tampon d'adresse 702, une partie d'horloge de ligne/colonne 705, une partie de transmission d'entrée/sortie 706, une partie de registre de données 707, une partie d'amplificateur de lecture 708, une partie de commande de fonctionnement 709) et autres. Bien que toutes ces parties soient formées par des transistors, du fait de différences entre des tensions utilisées, il est nécessaire d'employer plusieurs types de transistors qui ont des caractéristiques mutuellement différentes.

Par exemple, un transistor dans la partie de réseau de cellules de mémoire 701 exige une épaisseur de pellicule d'oxyde qui est par exemple d'environ 10 nm pour garantir la fiabilité d'une pellicule d'oxyde tunnel. Cependant, un courant de valeur élevée est exigé dans la partie de circuits périphériques, dans le but d'avoir un fonctionnement rapide, et par conséquent une épaisseur de pellicule d'oxyde est souvent fixée à une valeur inférieure à celle de la partie de réseau de cellules de mémoire 701. De plus, dans la partie supportant une tension élevée, il est nécessaire d'avoir un transistor qui supporte une tension de 10 V. Il est donc nécessaire d'utiliser une pellicule d'oxyde épaisse qui a par exemple une épaisseur s'élevant jusqu'à 25 nm. En résumé, plusieurs types de transistors qui ont des épaisseurs de pellicule d'oxyde mutuellement différentes sont nécessaires dans la mémoire flash qui se présente sous la forme d'une seule puce.

Structures des transistors respectifs

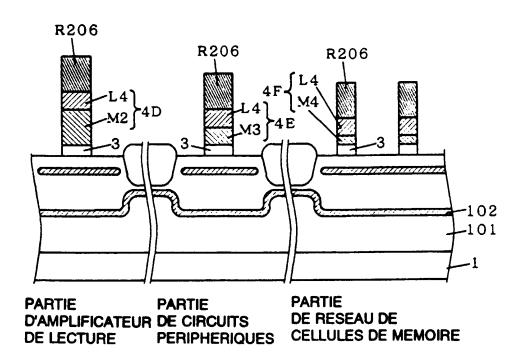

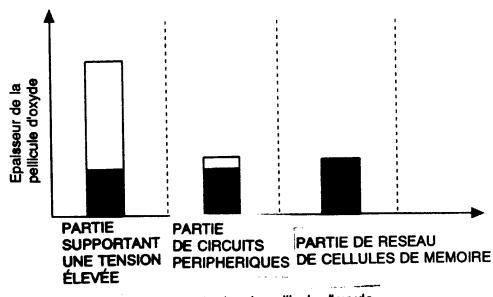

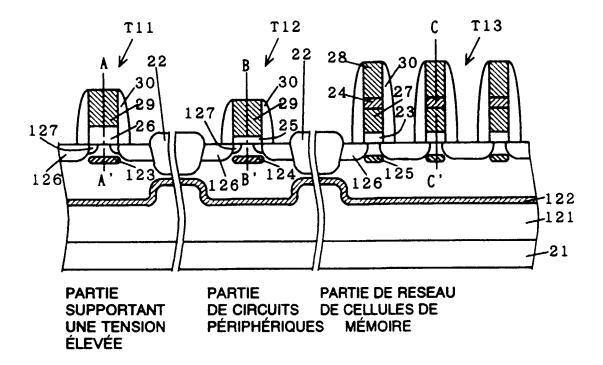

Dans ce qui suit, on décrit un exemple dans lequel une épaisseur de pellicule d'oxyde est changée conformément à un transistor. La figure 86 montre, en une vue partielle, un exemple d'une structure d'une mémoire flash qui est fabriquée par un procédé de fabrication classique. On voit des coupes de transistors MOS à canal N T11 à T13 qui sont utilisés pour la partie supportant une tension élevée, la partie de circuits périphériques et la partie de réseau de cellules de mémoire.

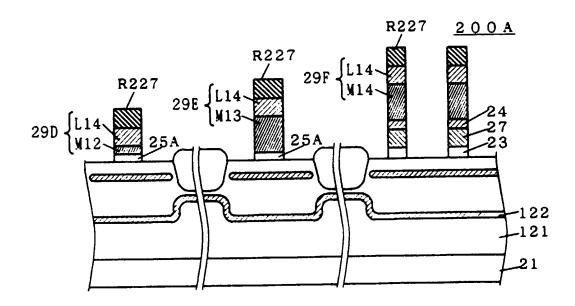

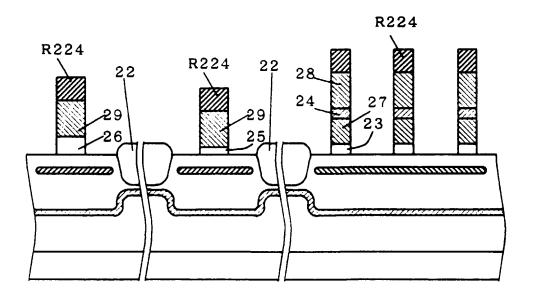

Sur la figure 86, les transistors MOS à canal N T11 à T13 sont formés à l'intérieur d'une couche de caisson de type P 121 qui est formée sur le même substrat semiconducteur 21 (de type P). La couche de caisson 121 fait l'objet d'une séparation entre éléments au moyen d'une couche de coupure de canal 122 qui est formée à l'intérieur de la couche de caisson 121, et d'une couche LOCOS 22, d'une manière telle que les transistors MOS à canal N T11 à T13 soient formés dans des régions qui sont créées par la séparation entre éléments.

5

10

15

20

25

30

35

Le transistor MOS à canal N T11 de la partie supportant une tension élevée comprend une paire de couches de source/drain 126 qui sont formées à l'intérieur de la couche de caisson 121, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 127 qui sont formées dans des positions adjacentes à des parties de bord en regard des couches de source/drain 126.

Une pellicule d'oxyde de grille 26 est formée sur les couches LDD 127 et une électrode de grille 29 est formée sur la pellicule d'oxyde de grille 26. Une pellicule d'oxyde de paroi latérale 30 est formée sur la surface latérale de la pellicule d'oxyde de grille 26 et de l'électrode de grille 29. Une couche dopée de canal 123 est formée à l'intérieur de la couche de caisson 121, sous l'électrode de grille 29.

Le transistor MOS à canal N T12 de la partie de circuits périphériques comprend une paire de couches de source/drain 126 qui sont formées à l'intérieur de la couche de caisson 121, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 127.

Une pellicule d'oxyde de grille 25 est formée sur les couches LDD 127, et une électrode de grille 29 est formée sur la pellicule d'oxyde de grille 25. Une pellicule d'oxyde de paroi latérale 30 est formée sur une surface latérale de la pellicule d'oxyde de grille 25 et de l'électrode de grille 29. Une couche dopée de canal 124 est formée à l'intérieur de la couche de caisson 121, sous l'électrode de grille 29.

Le transistor MOS à canal N T13 de la partie de réseau de cellules de mémoire comprend une paire de couches de source/drain 126 qui sont formées à l'intérieur de la couche de caisson 121, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre. Une pellicule d'oxyde tunnel 23 est formée sur des parties de bord des couches de source/drain 126. Une électrode de grille flottante 27, une pellicule d'isolation inter-couche 24 et une électrode de grille de commande 28 sont formées dans cet ordre sur la pellicule d'oxyde tunnel 23.

La pellicule d'oxyde de paroi latérale 30 est formée sur une surface latérale de la pellicule d'oxyde tunnel 23, de l'électrode de grille flottante 27, de la pellicule d'isolation inter-couche 24 et de l'électrode de grille de commande 28.

5

10

15

20

25

Une couche dopée de canal 125 est formée à l'intérieur de la couche de caisson 121, sous l'électrode flottante 27. La partie de réseau de cellules de mémoire a une structure de réseau de grilles dans laquelle des grilles adjacentes se partagent une même couche de source/drain 126. De telles structures sont disposées en succession.

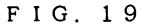

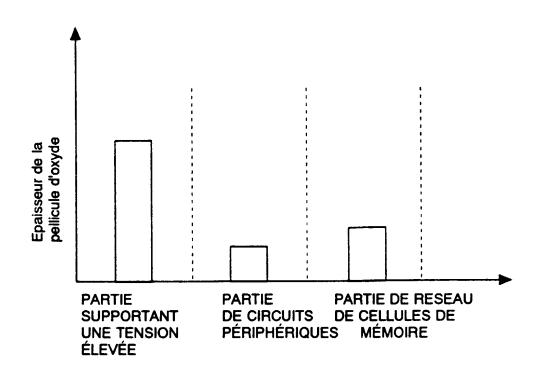

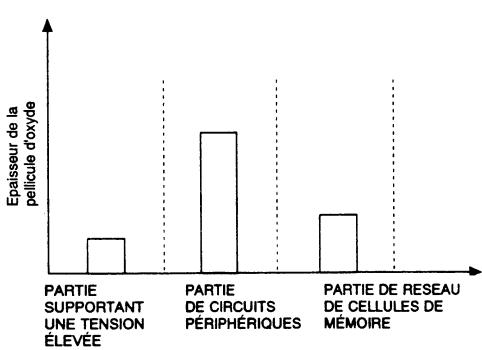

Une caractéristique de la mémoire flash qui est représentée sur la figure 86 consiste en ce que l'épaisseur de la pellicule d'oxyde de grille 26 du transistor MOS à canal N T11 de la partie supportant une tension élevée est la plus grande, suivie par l'épaisseur de la pellicule d'oxyde tunnel 23 du transistor MOS à canal N T13 de la partie de réseau de cellules de mémoire, et par l'épaisseur de la pellicule d'oxyde de grille 25 du transistor MOS à canal N T12 de la partie de circuits périphériques, dans cet ordre.

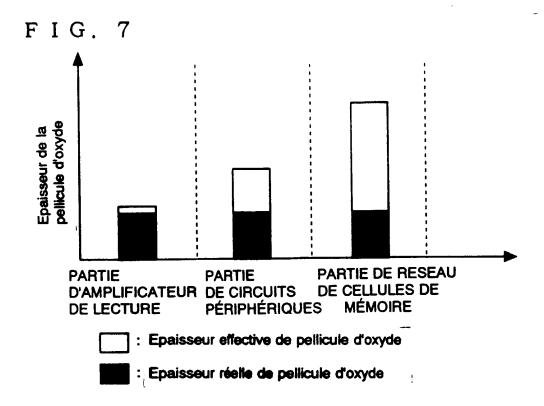

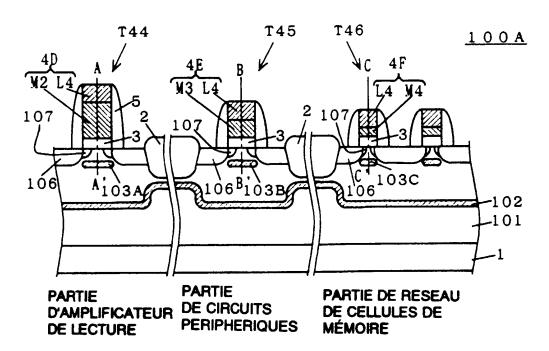

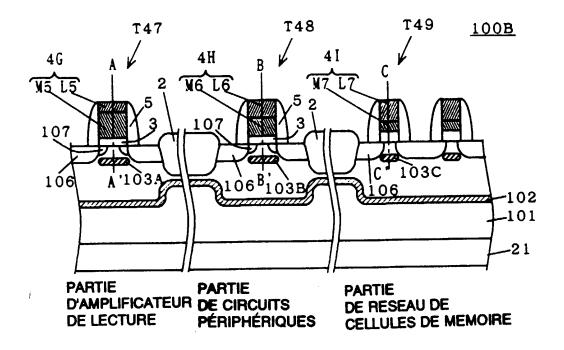

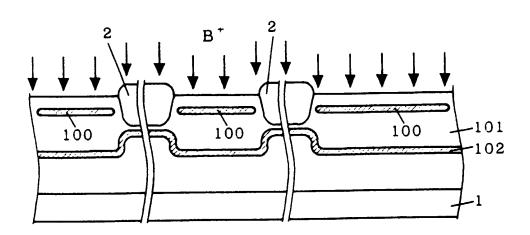

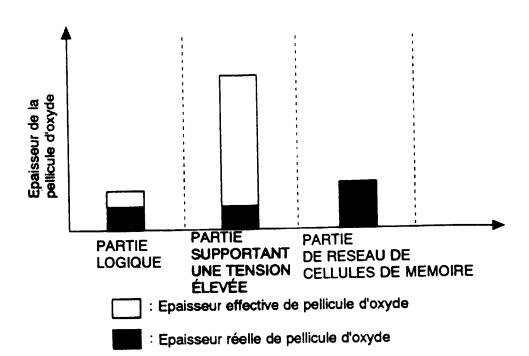

La figure 87 montre les épaisseurs des pellicules d'oxyde de grille respectives. Sur la figure 87, les transistors MOS à canal N de la partie supportant une tension élevée, de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire sont représentés dans cet ordre le long de l'axe horizontal, à partir du côté gauche.

Le Tableau 2 montre des valeurs numériques concernant les structures des transistors MOS à canal N T11 à T13.

TABLEAU 2

|                                 | Partie supportant une              | Partie de circuits                      | Partie de réseau de                   |

|---------------------------------|------------------------------------|-----------------------------------------|---------------------------------------|

|                                 | tension élevée (T11)               | périphériques (T12)                     | cellules de mémoire<br>(T13)          |

| Epaisseur de pellicule d'oxyde  | 400 nm                             | 400 nm                                  | 400 nm                                |

| de champ                        |                                    |                                         |                                       |

| Epaisseur de pellicule d'oxyde  | 25 nm                              | 8 nm                                    | 10 nm                                 |

| de grille                       |                                    |                                         |                                       |

| Epaisseur de pellicule          |                                    | 1 1 1                                   | 100 ກສ                                |

| d'électrode de grille flottante |                                    |                                         | C C                                   |

| Concentration en impureté de    |                                    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 × 10 <sup>-2</sup> cm <sup>-3</sup> |

| grille flottante                |                                    |                                         |                                       |

| Epaisseur de pellicule          | 1 1                                |                                         | TEOS/Si3N4/TEOS =                     |

| d'isolation inter-couche        |                                    |                                         | 10/10/10 nm                           |

| Epaisseur de pellicule d'élec-  | 200 nm                             | 200 nm                                  | 200 nm                                |

| trode de grille de commande     |                                    |                                         |                                       |

| Concentration en impureté de    | $5 \times 10^{20} \text{ cm}^{-3}$ | $5 \times 10^{20} \text{ cm}^{-3}$      | 5 × 10 <sup>20</sup> cm <sup>-3</sup> |

| grille de commande              |                                    |                                         |                                       |

| Paroi latérale                  | 200 nm                             | 200 nm                                  | 200 nm                                |

| Caiscon                    | B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup>   B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup>   B 700 keV 1 × 10 <sup>13</sup> cm <sup>-2</sup> |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Couche de coupure de canal | B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup>     |

| Course donée de canal      | B 50 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 50 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup> B 50 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup>        |

|                            | As 30 keV 1 x 10 <sup>13</sup> cm <sup>-2</sup> As 30 keV 1 x 10 <sup>13</sup> cm <sup>-2</sup>                                                     |

| Couche de source/drain     | As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 × 10 <sup>15</sup> cm <sup>-2</sup>     |

60 min

850°C

Traitement thermique

Dans le Tableau 2, les épaisseurs des pellicules d'oxyde de grille des transistors MOS à canal N T11, T12 et 13 sont respectivement de 25 nm. 8 nm et 10 nm.

Procédé de fabrication des transistors respectifs

5

10

15

20

25

30

35

On va maintenant donner une description d'un procédé de fabrication des transistors MOS à canal N T11, T12 et T13 de la partie supportant une tension élevée, de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire qui sont représentés sur la figure 86, en se référant aux figures 88 à 101.

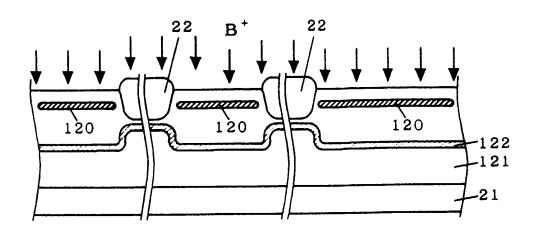

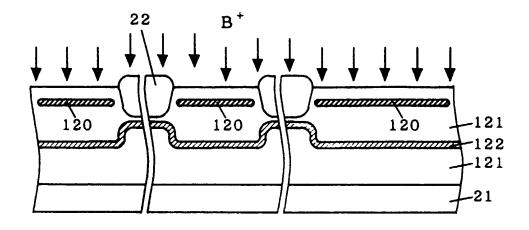

Premièrement, à une étape qui est représentée sur la figure 88, on forme la couche LOCOS (c'est-à-dire une pellicule d'oxyde de champ) 22 en lui donnant par exemple une épaisseur de 400 nm, par un procédé LOCOS, sur une surface du substrat semiconducteur 21 du type P. A la suite de ceci, on implante par exemple des ions de bore avec une énergie de 700 keV et une dose de  $1\times10^{13}$  cm<sup>-2</sup>, pour former ainsi une région de caisson de type P 121 à l'intérieur du substrat semiconducteur 21. Bien que l'on forme également une région de caisson de type N dans le substrat semiconducteur 21, afin de former des transistors MOS à canal P, ceci n'est pas représenté et la description sera omise. Ensuite, on implante par exemple des ions de bore avec une énergie de 130 keV et une dose de  $5\times10^{12}$  cm<sup>-2</sup>, pour former ainsi la couche de coupure de canal 122 à l'intérieur du substrat semiconducteur 21. On forme la couche de coupure de canal 122 en lui donnant une forme qui, en association avec la couche LOCOS 22, crée les régions avec séparation entre éléments.

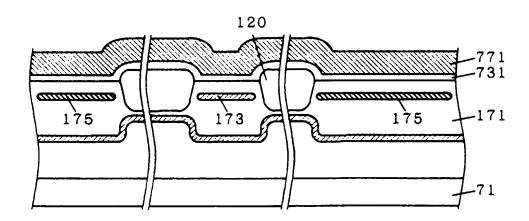

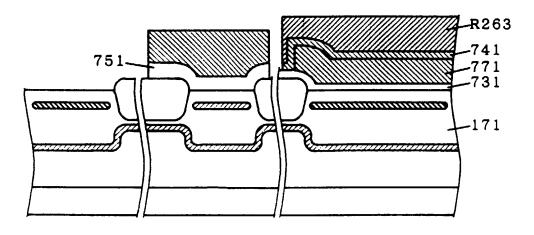

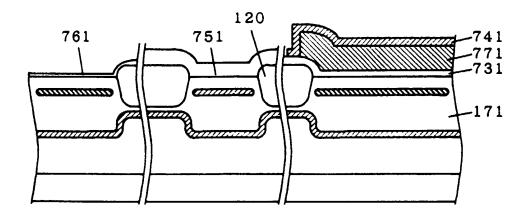

On forme ensuite une couche dopée de canal 120 dans des positions prédéterminées de la partie supportant une tension élevée, de la partie de circuits périphériques et de la partie de réseau de cellules de mémoire, à l'intérieur de la région de caisson 121. On forme la couche dopée de canal 120 en implantant par exemple des ions de bore avec une énergie de 50 keV et une dose de  $1 \times 10^{12}$  cm<sup>-2</sup>.

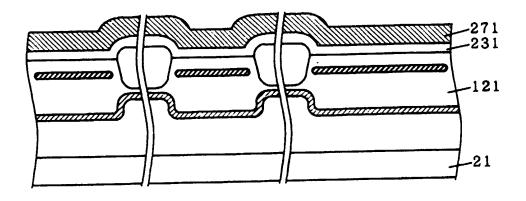

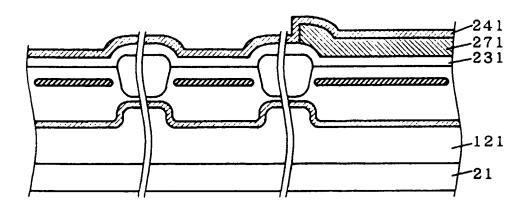

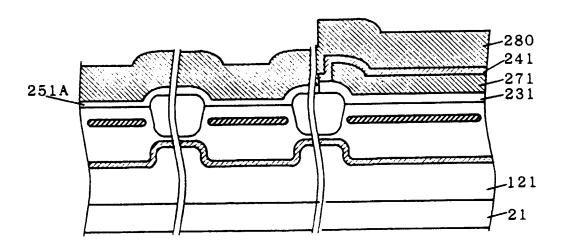

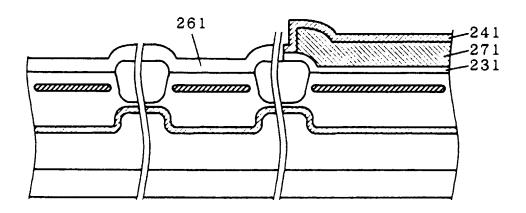

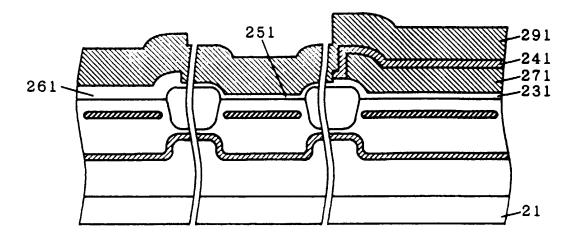

Ensuite, à une étape qui est représentée sur la figure 89, après avoir formé une pellicule d'oxyde 231 qui deviendra la pellicule d'oxyde tunnel 23, sur une surface principale du substrat semiconducteur 21, par un procédé d'oxydation thermique, on forme par exemple une couche de silicium polycristallin dopé 271, à titre de matériau d'électrode de grille,

sur la pellicule d'oxyde 231, par un procédé CVD. La pellicule d'oxyde 231 a une épaisseur d'environ 10 nm, tandis que la couche de silicium polycristallin dopé 271 a une épaisseur d'environ 100 nm. On utilise du phosphore (P) à titre d'impureté. La concentration de l'impureté est d'environ  $1 \times 10^{20}$  cm<sup>-3</sup>.

5

10

15

20

25

30

35

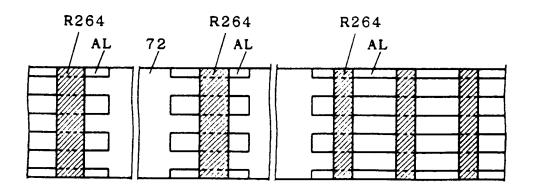

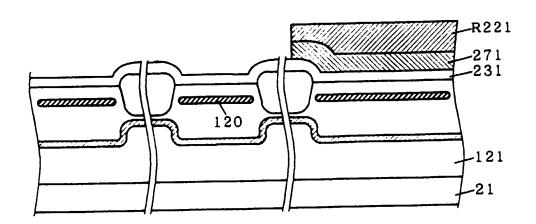

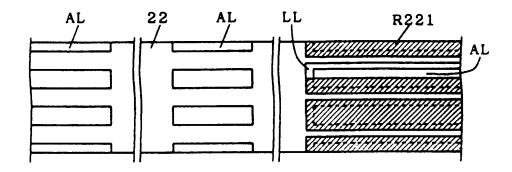

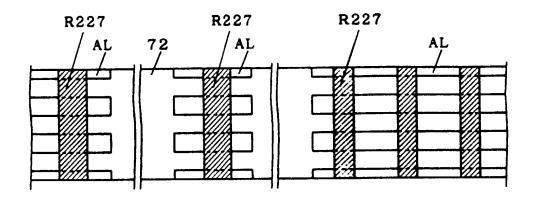

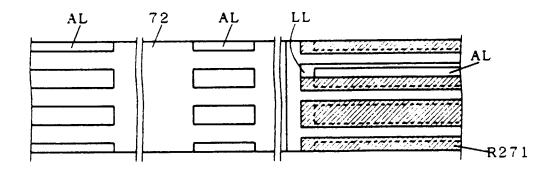

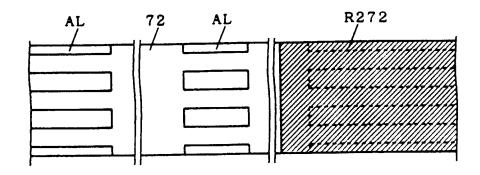

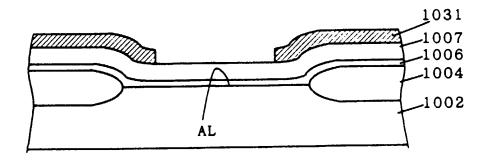

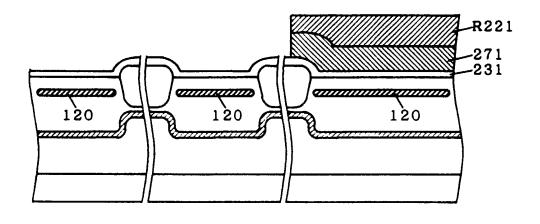

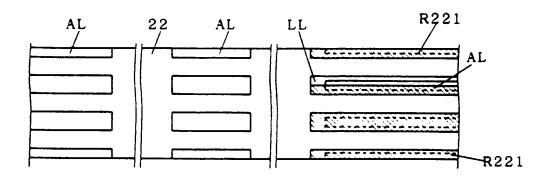

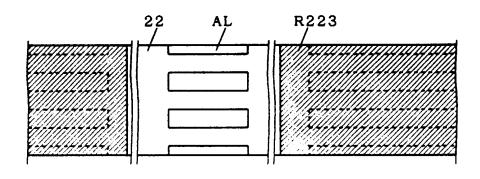

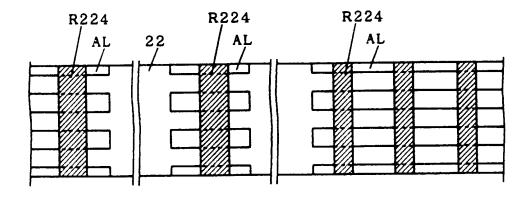

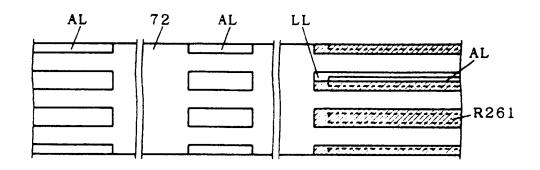

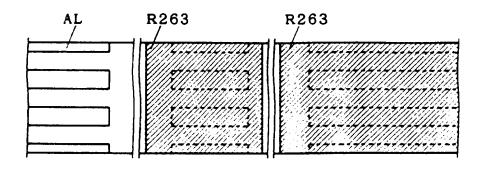

Ensuite, à une étape qui est représentée sur la figure 90, on forme sélectivement un masque de matière de réserve R221 sur la couche de silicium polycristallin dopé 271, à l'intérieur de la partie de réseau de cellules de mémoire. Dans ce cas, on forme le masque de matière de réserve R221 dans la direction de la largeur de grille de la partie de réseau de cellules de mémoire. On enlève par une attaque anisotrope une partie de la couche de silicium polycristallin dopé 271 qui n'est pas recouverte par le masque de matière de réserve R221. La figure 91 montre cette condition.

La figure 91 est une vue en plan qui représente la structure de la figure 90 vue par le côté de la surface supérieure (c'est-à-dire le côté sur lequel est formé le masque de matière de réserve R221). A l'intérieur de la partie de réseau de cellules de mémoire, le masque de matière de réserve R221 est réalisé sous la forme d'îlots rectangulaires qui sont disposés régulièrement. On forme le masque de matière de réserve R221 de façon à recouvrir une couche active AL qui a une configuration semblable à un îlot rectangulaire, et une couche LOCOS LL autour de celle-ci. Du fait que le masque de matière de réserve R221 n'est pas formé à l'intérieur de la partie supportant une tension élevée et de la partie de circuits périphériques, la couche active AL est à nu. Bien que le masque de matière de réserve R221 soit partiellement omis sur la figure 91, de façon que la couche active AL et la couche LOCOS LL soient visibles, c'est uniquement pour la clarté de la représentation de la structure située sous le masque de matière de réserve R221 et simplement pour la commodité de l'illustration.

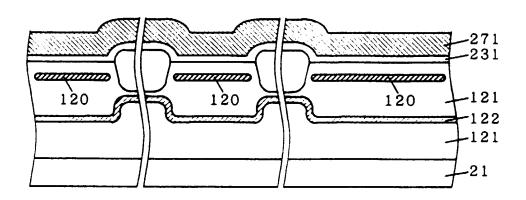

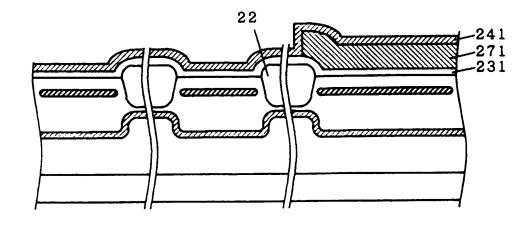

Ensuite, après avoir enlevé le masque de matière de réserve R221, à une étape qui est représentée sur la figure 92, on forme par un procédé CVD sur la couche de silicium polycristallin dopé 271 une pellicule d'isolation 241, qui deviendra la pellicule d'isolation inter-couche 24 qui isole la grille flottante vis-à-vis de la grille de commande. Cette pellicule

a une structure dans laquelle une pellicule de TEOS (tétraéthylorthosilicate), une pellicule de nitrure  $(Si_3N_4)$ , et une pellicule TEOS, ayant chacune une épaisseur de 10 nm, sont superposées dans cet ordre. La pellicule d'isolation inter-couche 24 est appelée dans certains cas une "pellicule ONO". La pellicule d'isolation 241 est également formée sur la partie supportant une tension élevée et sur la partie de circuits périphériques.

5

10

15

20

25

30

35

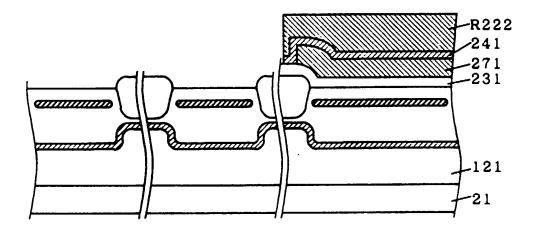

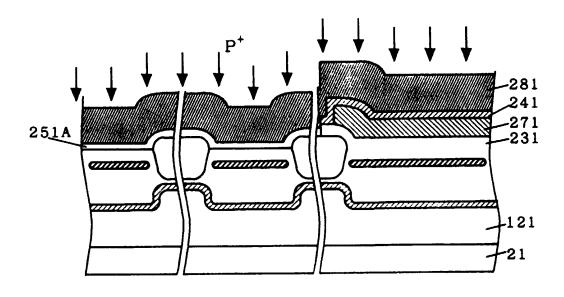

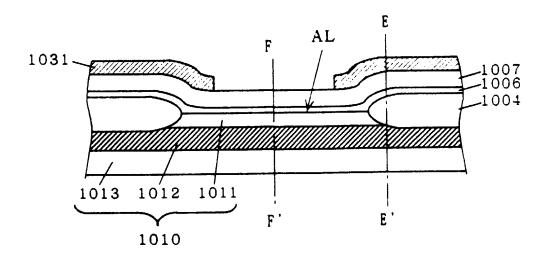

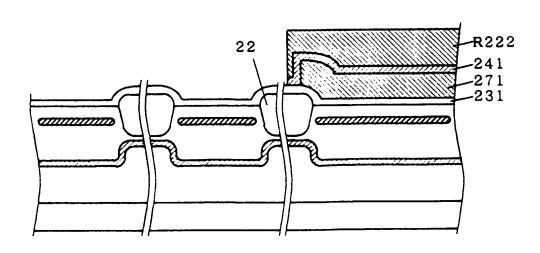

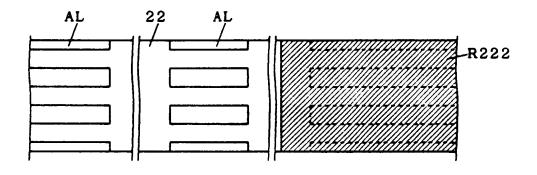

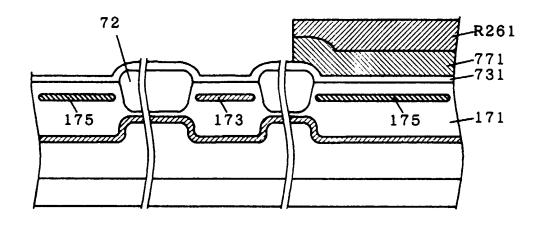

Ensuite, à une étape qui est représentée sur la figure 93, on forme un masque de matière de réserve R222 sur la pellicule d'isolation 241 de la partie de réseau de cellules de mémoire, et on enlève la pellicule d'isolation 241 dans toutes les autres régions. Dans ce cas, dans les autres régions, on enlève également la pellicule d'oxyde 231. La figure 94 montre cette condition.

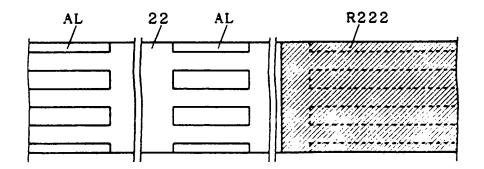

La figure 94 est une vue en plan représentant la structure de la figure 93 vue par le côté de la surface supérieure (c'est-à-dire le côté sur lequel est formé le masque de matière de réserve R222). On forme le masque de matière de réserve R222 de façon à recouvrir entièrement la partie de réseau de cellules de mémoire. Cependant, la couche active AL est à nu à l'intérieur de la partie supportant une tension élevée et de la partie de circuits périphériques, du fait que le masque de matière de réserve R222 n'est pas formé.

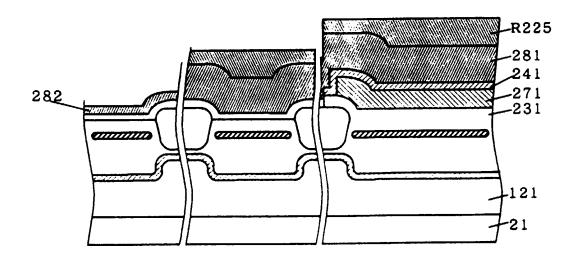

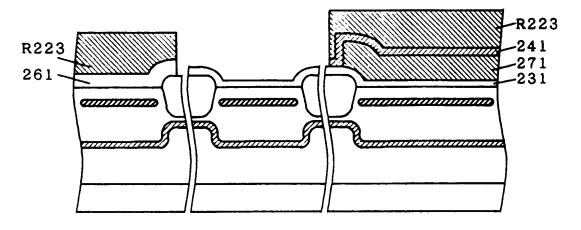

Ensuite, après avoir enlevé le masque de matière de réserve R222, à une étape qui est représentée sur la figure 95, on forme sur la totalité de la surface principale du substrat semiconducteur 21, par un procédé d'oxydation thermique, une pellicule d'oxyde 261 qui deviendra la pellicule d'oxyde de grille 26. A ce stade, du fait que la pellicule d'isolation 241 sur la partie de réseau de cellules de mémoire comprend la pellicule de nitrure, la pellicule d'isolation 241 n'est pas oxydée et l'épaisseur de la pellicule d'isolation 241 est maintenue. L'épaisseur de la pellicule d'oxyde 261 est d'environ 17 nm.

Ensuite, à une étape qui est représentée sur la figure 96, on recouvre par un masque de matière de réserve R223 des régions autres que la partie de circuits périphériques, et on enlève la pellicule d'oxyde 261 sur la partie de circuits périphériques, par attaque par voie humide. La figure 97 montre cette condition.

La figure 97 est une vue en plan représentant la structure de la

figure 96 vue par le côté de la surface supérieure (c'est-à-dire le côté sur lequel est formé le masque de matière de réserve R223). Le masque de matière de réserve R223 est formé de façon à recouvrir entièrement la partie de réseau de cellules de mémoire et la partie supportant une tension élevée. Cependant, dans la partie de circuits périphériques, du fait que le masque de matière de réserve R223 n'est pas formé, la couche active AL est à nu.

5

10

15

20

25

30

35

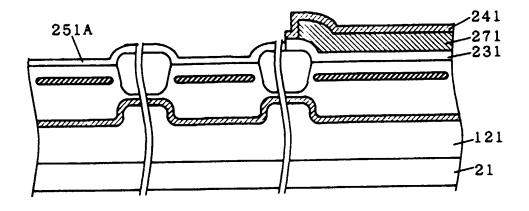

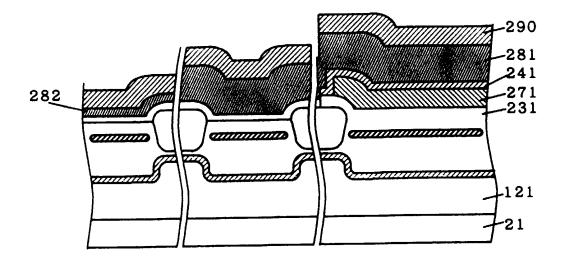

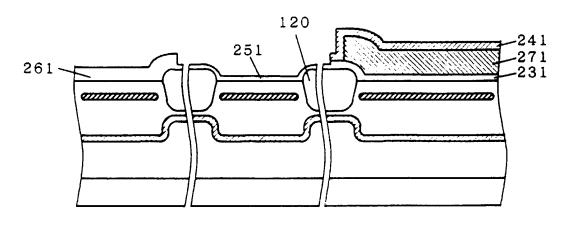

Ensuite, après avoir enlevé le masque de matière de réserve R223, à une étape qui est représentée sur la figure 98, on forme par un procédé d'oxydation thermique une pellicule d'oxyde 251 qui deviendra la pellicule d'oxyde de grille 25. A ce stade, du fait que la pellicule d'isolation 241 sur la partie de réseau de cellules de mémoire comprend la pellicule de nitrure, la pellicule d'isolation 241 n'est pas oxydée et l'épaisseur de la pellicule d'isolation 241 est maintenue. Cependant, dans la partie supportant une tension élevée, la pellicule d'oxyde 261 se développe et son épaisseur augmente. L'épaisseur de la pellicule d'oxyde 251 est d'environ 8 nm. La pellicule d'oxyde 261 se développe jusqu'à environ 25 nm.

Ensuite, à une étape qui est représentée sur la figure 99, on forme une couche de silicium polycristallin dopé 291, à titre de matériau d'électrode de grille, sur la totalité de la surface principale du substrat semiconducteur 21, par un procédé CVD. L'épaisseur de la couche de silicium polycristallin dopé 291 est d'environ 200 nm. On utilise du phosphore (P) à titre d'impureté. La concentration de l'impureté est d'environ  $5 \times 10^{20} \, \mathrm{cm}^{-3}$ .

Ensuite, à une étape qui est représentée sur la figure 100, on forme un masque de matière de réserve R224 sur la couche de silicium polycristallin dopé 291, et on forme un motif dans celui-ci. La figure 101 montre cette condition.

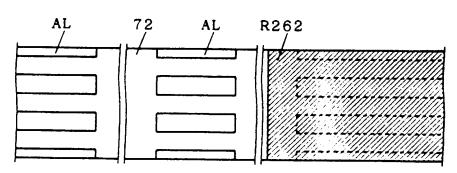

La figure 101 est une vue en plan représentant la structure de la figure 100 vue par le côté de la surface supérieure (c'est-à-dire le côté sur lequel est formé le masque de matière de réserve R224). Le masque de matière de réserve R224 est formé de façon à être perpendiculaire à la couche active AL qui a une configuration rectangulaire.

Sous l'effet de la formation d'un motif, la pellicule d'oxyde de

grille 26 et l'électrode de grille 29 sont formées dans la partie supportant une tension élevée, la pellicule d'oxyde de grille 25 et l'électrode de grille 29 sont formées dans la partie de circuits périphériques, et la pellicule d'oxyde tunnel 23, l'électrode de grille flottante 27 et l'électrode de grille de commande 28 sont formées dans la partie de réseau de cellules de mémoire.

5

10

15

20

25

30

35

A la suite de ceci, après avoir formé les couches LDD 127 par implantation d'ions dans la partie supportant une tension élevée et dans la partie de circuits périphériques, on forme la pellicule d'oxyde de paroi latérale 30, d'environ 100 nm d'épaisseur, sur une surface latérale d'une pellicule d'oxyde de grille 26 et de l'électrode de grille 29, sur une surface latérale de la pellicule d'oxyde de grille 25 et de l'électrode de grille 29, et sur une surface latérale de la pellicule d'oxyde tunnel 23, de l'électrode de grille flottante 27, de la pellicule d'isolation inter-couche 24 et de l'électrode de grille de commande 28. En utilisant à titre de masque la pellicule d'oxyde de paroi latérale 30, et en procédant par implantation ionique, on forme les couches de source/drain 126. De cette manière, on obtient la structure de la mémoire flash qui est représentée sur la figure 86.

On forme les couches LDD 127 en implantant par exemple des ions d'arsenic, avec une énergie de 30 keV et une dose de  $1\times 10^{13}$  cm<sup>-2</sup>. D'autre part, on forme les couches de source/drain 126 en injectant par exemple des ions d'arsenic, avec une énergie de 50 keV et une dose de  $5\times 10^{15}$  cm<sup>-2</sup>, et en effectuant ensuite un recuit à 850°C pendant 60 minutes.

Bien que ceci soit suivi par la formation d'un condensateur, d'une pellicule d'isolation inter-couche, d'une couche d'interconnexion et autres, pour former la mémoire flash, ceci ne sera pas décrit et n'est pas représenté dans les dessins.

Problèmes concernant la mémoire flash classique

Comme décrit ci-dessus, comme dans la mémoire DRAM classique, il existe dans la mémoire flash classique une relation de compromis entre une valeur de seuil et une fuite de couche de diffusion. La relation de compromis impose une restriction à la conception du circuit.

En outre, du fait qu'il est nécessaire de former plusieurs types

de transistors qui ont des épaisseurs de pellicule d'oxyde mutuellement différentes, dans la mémoire flash qui se présente sous la forme d'une seule puce, il est nécessaire dans certains cas de former les pellicules d'oxyde en plusieurs étapes. Par exemple, dans la partie supportant une tension élevée, à l'étape d'enlèvement du masque de matière de réserve R223 (voir la figure 96), la pellicule d'oxyde 261 se développe davantage pendant la formation de la pellicule d'oxyde 251 (voir la figure 98). Ainsi, la pellicule d'oxyde 261 est formée en deux étapes. Ceci conduit à une possibilité plus élevée de permettre l'entrée d'une impureté ou autres, ce qui dégrade à son tour la fiabilité de la pellicule d'oxyde de grille 26 ou amoindrit la maîtrise de l'épaisseur de pellicule. Ceci conduit en outre à un problème qui consiste dans la perte de la fiabilité du transistor MOS à canal N T11 de la partie supportant une tension élevée, etc.

Troisième exemple classique

5

10

15

20

25

30

35

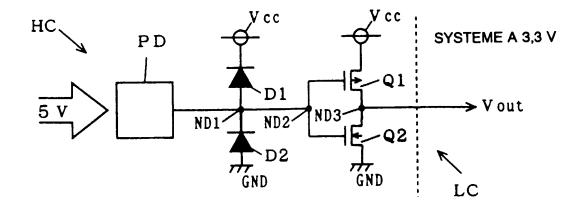

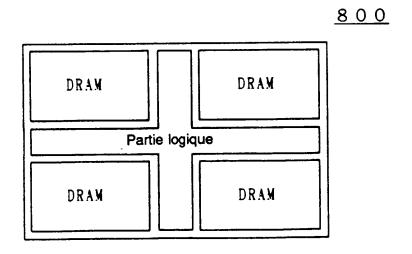

Structure d'ensemble d'une mémoire DRAM comprenant un circuit logique

A titre de troisième exemple classique, on va décrire une structure d'une mémoire DRAM 800 qui comprend un circuit logique (que l'on appelle ci-après "Circuit Logique en Mémoire DRAM"), et un procédé de fabrication de cette structure.

Le Circuit Logique en Mémoire DRAM 800 est un dispositif qui fonctionne avec d'excellentes performances et qui a seulement un faible coût, du fait qu'un circuit logique est formé à l'intérieur de la même puce, de façon que la mémoire DRAM et le circuit logique, qui étaient formés jusqu'à présent sous la forme de puces séparées, soient combinés ensemble.

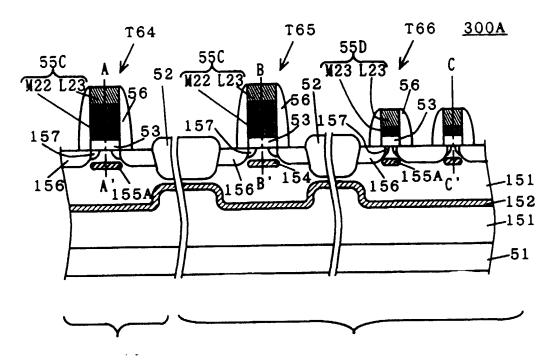

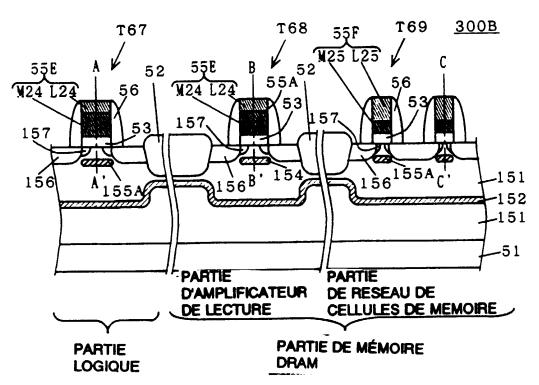

Comme représenté sur la figure 102, le Circuit Logique en Mémoire DRAM 800 est divisé grossièrement en une partie logique et une partie de mémoire DRAM. Une exigence pour la partie logique consiste dans le fonctionnement à une vitesse élevée, c'est-à-dire que cette partie doit avoir une possibilité d'attaque élevée et une faible capacité. D'autre part, comme décrit précédemment, la partie de mémoire DRAM comprend une partie de réseau de cellules de mémoire dans laquelle un faible courant de fuite est exigé, une partie d'amplificateur de lecture dans laquelle un fonctionnement à une tension basse est exigé, etc. Ainsi, plusieurs

types de transistors qui ont des caractéristiques mutuellement différentes sont nécessaires dans le Circuit Logique en Mémoire DRAM 800 qui est réalisé sous la forme d'une seule puce.

Structures des transistors respectifs

5

10

15

20

25

30

35

Une technique classique pour former dans une seule puce des transistors qui ont des caractéristiques mutuellement différentes consiste à changer un profil d'impureté d'une couche dopée de canal ou une épaisseur de pellicule d'oxyde, en correspondance avec un transistor. Dans ce qui suit, en ce qui concerne la partie de mémoire DRAM, on décrira un exemple dans lequel une concentration d'impureté d'une couche dopée de canal est changée en correspondance avec un transistor, tandis qu'en ce qui concerne la partie logique on décrira un exemple dans lequel une épaisseur de pellicule d'oxyde est changée en correspondance avec un transistor.

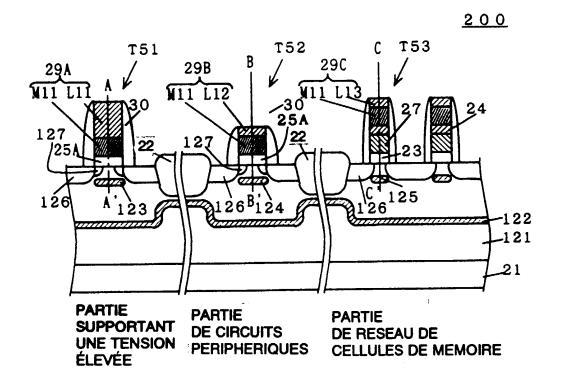

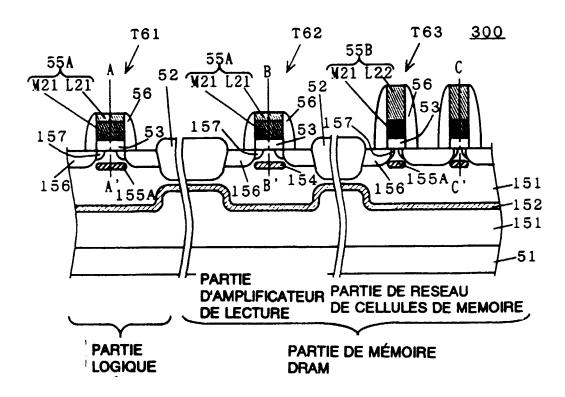

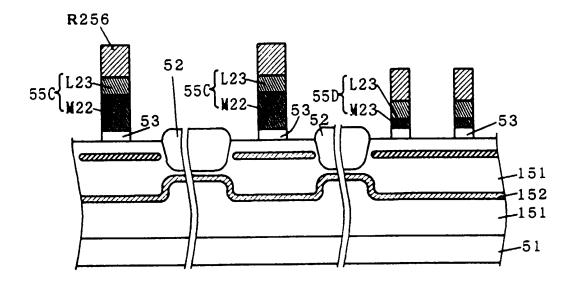

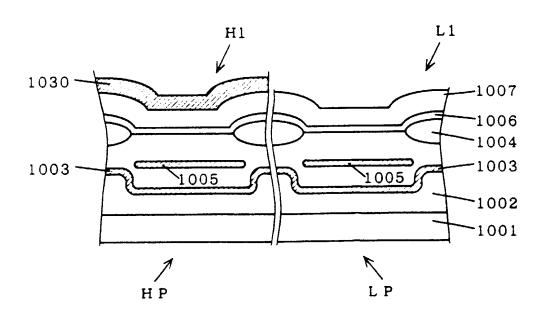

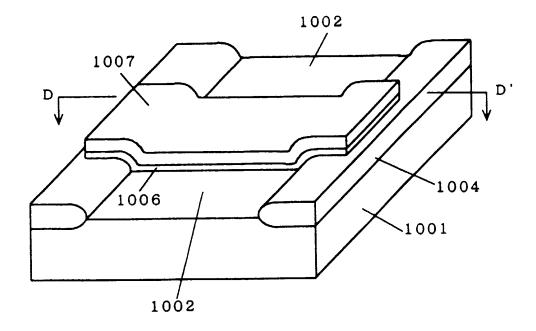

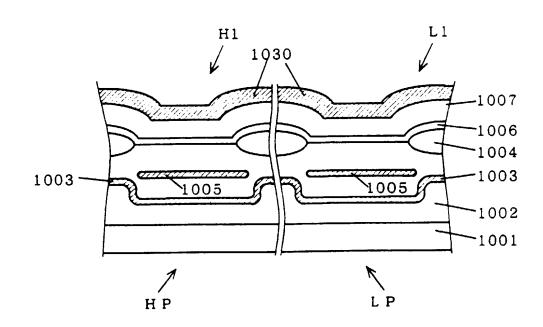

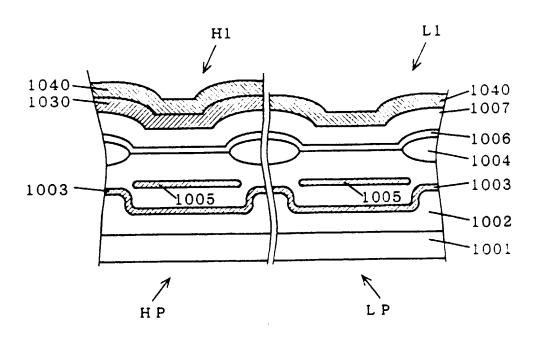

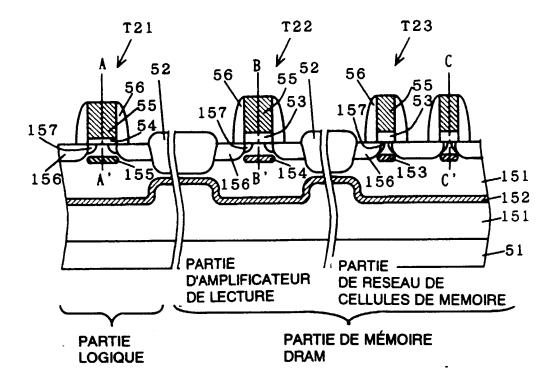

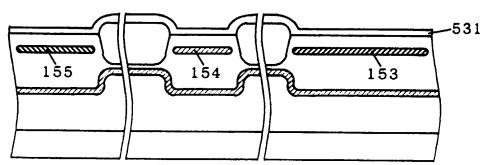

La figure 103 montre (en vue partielle) un exemple d'une structure d'un Circuit Logique en Mémoire DRAM qui est fabriquée par un procédé de fabrication classique. La figure montre des coupes de transistors MOS à canal N T21 à T23 qui sont utilisés pour la partie logique et pour la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire de la partie de mémoire DRAM.

Sur la figure 103, les transistors MOS à canal N T21 à T23 sont formés à l'intérieur d'une couche de caisson de type P 151 qui est formée sur le même substrat semiconducteur 51 (du type P). La couche de caisson 151 fait l'objet d'une séparation entre éléments par une couche de coupure de canal 152 qui est formée à l'intérieur de la couche de caisson 151, et par une couche LOCOS 52, de manière que les transistors MOS à canal N T21 à T23 soient formés dans des régions qui sont créées par séparation entre éléments.

Le transistor MOS à canal N T21 de la partie logique comprend une paire de couches de source/drain 156 qui sont formées à l'intérieur de la couche de caisson 151, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 157 qui sont formées dans des positions adjacentes à des parties de bord en regard des couches de source/drain 156.

Une pellicule d'oxyde de grille 54 est formée sur les couches

LDD 157, et une électrode de grille 55 est formée sur la pellicule d'oxyde de grille 54. Une pellicule d'oxyde de paroi latérale 56 est formée sur la surface latérale de la pellicule d'oxyde de grille 54 et de l'électrode de grille 55. Une couche dopée de canal 155 est formée à l'intérieur de la couche de caisson 151, sous l'électrode de grille 55.

5

10

15

20

25

30

Le transistor MOS à canal N T22 de la partie d'amplificateur de lecture comprend une paire de couches de source/drain 156 qui sont formées à l'intérieur de la couche de caisson 151, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 157.

Une pellicule d'oxyde de grille 53 est formée sur les couches LDD 157, et une électrode de grille 55 est formée sur la pellicule d'oxyde de grille 53. La pellicule d'oxyde de paroi latérale 56 est formée sur une surface latérale de la pellicule d'oxyde de grille 53 et de l'électrode de grille 55. Une couche dopée de canal 154 est formée à l'intérieur de la couche de caisson 151, sous l'électrode de grille 55.

Le transistor MOS à canal N T23 de la partie de réseau de cellules de mémoire comprend une paire de couches de source/drain 156 qui sont formées à l'intérieur de la couche de caisson 151, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 157.

La pellicule d'oxyde de grille 53 est formée sur les couches de source/drain 156 et les couches LDD 157, et la pellicule de grille 55 est formée sur la pellicule d'oxyde de grille 53. La pellicule d'oxyde de paroi latérale 56 est formée sur une surface latérale de la pellicule d'oxyde de grille 53 et de l'électrode de grille 55. Une couche dopée de canal 153 est formée à l'intérieur de la couche de caisson 151, sous l'électrode de grille 55. La partie de réseau de cellules de mémoire a une structure de réseau de grilles dans laquelle des grilles adjacentes se partagent une seule couche de source/drain 156. De telles structures sont disposées en succession.

Le Tableau 3 montre des valeurs numériques concernant les structures des transistors MOS à canal N T21 à T23.

30 min

850°C

Traitement thermique

TABLEAU 3

| Epaisseur de pellicule d'oxyde 400 nm de champ                     | logique<br>21)                 | Partie d'amplificateur             | Partie de réseau de                |

|--------------------------------------------------------------------|--------------------------------|------------------------------------|------------------------------------|

|                                                                    | 21)                            | 100tiles (T00)                     |                                    |

|                                                                    |                                | de lecinie (177)                   | cellules de mémoire                |

|                                                                    |                                |                                    | (T23)                              |

| de champ                                                           | mu (                           | 400 nm                             | 400 nm                             |

|                                                                    |                                |                                    |                                    |

| Epaisseur de pellicule d'oxyde 6 nm                                | mu                             | 10 nm                              | 10 nm                              |

| de grille                                                          |                                |                                    |                                    |

| Epaisseur de pellicule 200 nm                                      | mu (                           | 200 nm                             | 200 nm                             |

| d'électrode de grille                                              |                                |                                    |                                    |

| Concentration en impureté de 5 × 10 <sup>20</sup> cm <sup>-3</sup> | <sup>20</sup> cm <sup>-3</sup> | $5 \times 10^{20} \text{ cm}^{-3}$ | $5 \times 10^{20} \text{ cm}^{-3}$ |

| grille                                                             |                                |                                    |                                    |

| Paroi latérale 100 nm                                              | mu (                           | 100 nm                             | 100 nm                             |

|                                                                    |                                |                                    |                                    |

| Caisson                    | B 700 keV 1 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> B 700 keV 1 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> B 700 keV 1 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> | $keV 1 \times 10^{15} cm^{-2}$        |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Couche de coupure de canal | B 130 keV 5 $\times$ 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 $\times$ 10 <sup>12</sup> cm <sup>-2</sup> B 130 keV 5 $\times$ 10 <sup>12</sup> cm <sup>-2</sup> | $keV 5 \times 10^{12} cm^{-2}$        |

| Couche dopée de canal      | B 50 keV 1 x 10 <sup>13</sup> cm <sup>-2</sup> B 50 keV 1 x 10 <sup>12</sup> cm <sup>-2</sup> B 50 keV 5 x 10 <sup>12</sup> cm <sup>-2</sup>                         | $eV 5 \times 10^{12} \text{ cm}^{-2}$ |

| Couche LDD                 | As 30 keV 1 $\times$ 10 <sup>13</sup> cm <sup>-2</sup> As 30 keV 1 $\times$ 10 <sup>13</sup> cm <sup>-2</sup> As 30 keV 1 $\times$ 10 <sup>13</sup> cm <sup>-2</sup> | $keV 1 \times 10^{13} cm^{-2}$        |

| Couche de source/drain     | As 50 keV 5 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> As 50 keV 5 $\times$ 10 <sup>15</sup> cm <sup>-2</sup> | $keV 5 \times 10^{15} cm^{-2}$        |

Dans le Tableau 3, les doses d'impureté pour former les couches dopées de canal des transistors MOS à canal N T21, T22 et T23 sont respectivement de  $1 \times 10^{13}$  cm<sup>-2</sup>,  $1 \times 10^{12}$  cm<sup>-2</sup> et  $5 \times 10^{12}$  cm<sup>-2</sup>. On implante du bore (B) à titre d'impureté pour toutes les couches, avec une énergie d'implantation de 50 keV.

En outre, les épaisseurs des pellicules d'oxyde de grille des transistors MOS à canal N T21, T22 et T23 sont respectivement de 6 nm, 10 nm et 10 nm.

5

10

15

20

25

30

35

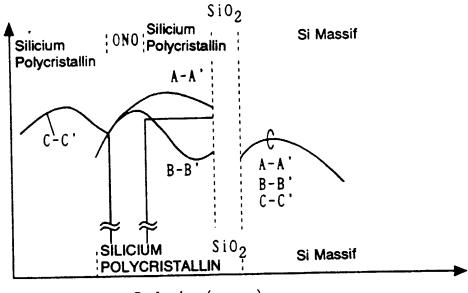

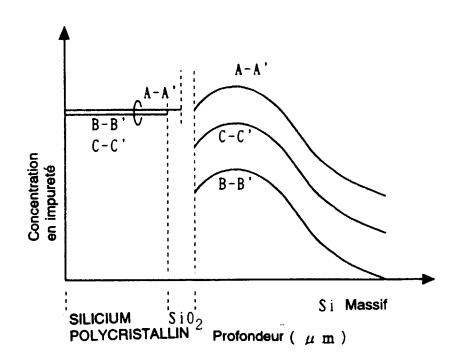

La figure 104 montre des profils d'impureté des transistors MOS à canal N T21, T22 et T23 de la partie logique, de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire, qui sont tous représentés sur la figure 103, ces profils correspondant respectivement à des coupes selon la ligne A-A', la ligne B-B' et la ligne C-C'.

Sur la figure 104, une position (en profondeur) dans une direction de coupe est représentée sur un axe horizontal et une concentration en impureté est représentée sur un axe vertical. On trouve l'électrode de grille (couche de silicium polycristallin), la pellicule d'oxyde de grille (couche de SiO<sub>2</sub>) et la couche de caisson (couche de silicium massif), dans cet ordre, le long de l'axe horizontal, en partant du côté gauche.

Comme indiqué dans le Tableau 3, la concentration en impureté dans l'électrode de grille conserve uniformément la même valeur parmi tous les transistors, et par conséquent la ligne A-A', la ligne B-B' et la ligne C-C' se trouvent l'une au-dessus de l'autre et sont représentées sous la forme de lignes droites en superposition (elles sont représentées par deux lignes dans le dessin pour distinguer la ligne A-A'). D'autre part, dans la couche de caisson, la dose de canal est plus faible pour un transistor dans la partie d'amplificateur de lecture, qui exige une faible valeur de seuil, et par conséquent la concentration en impureté est faible à une interface entre la pellicule d'oxyde et la partie massive. Une position de pic de chaque profil est approximativement la même qu'une position à laquelle est formée chaque couche dopée de canal.

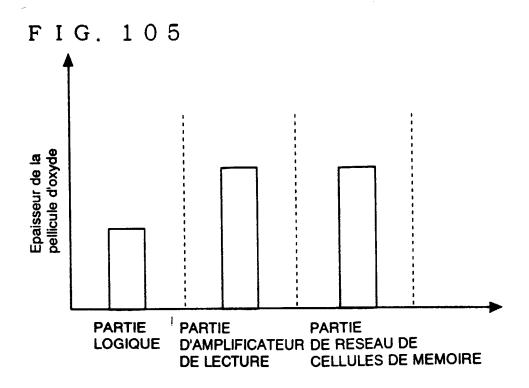

La figure 105 montre des épaisseurs des pellicules d'oxyde de grille respectives. Sur la figure 105, les transistors MOS à canal N de la partie logique, de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire sont représentés dans cet ordre, le long

de l'axe horizontal, en partant du côté gauche. Comme représenté sur la figure 105, pour améliorer la possibilité d'attaque en courant, la partie logique a une épaisseur de pellicule d'oxyde plus faible que celles de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire de la partie de mémoire DRAM.

Procédé de fabrication des transistors respectifs

5

10

15

20

25

30

35

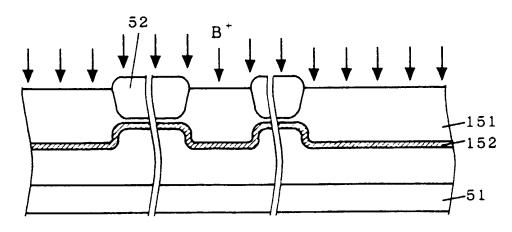

On présentera dans ce qui suit une description d'un procédé de fabrication des transistors MOS à canal N T21, T22 et T23 de la partie logique, de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire de la partie de mémoire DRAM qui sont représentés sur la figure 103, en se référant aux figures 106 à 114.

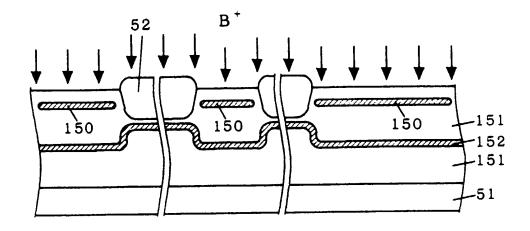

Premièrement, à une étape qui est représentée sur la figure 106, on forme la couche LOCOS (c'est-à-dire une pellicule d'oxyde de champ) 52 de façon à lui donner par exemple une épaisseur de 400 nm, par un procédé LOCOS, sur une surface du substrat semiconducteur 51 du type P. A la suite de ceci, on implante par exemple des ions de bore avec une énergie de 700 keV et une dose de  $1 \times 10^{13}$  cm<sup>-2</sup>, pour former ainsi une région de caisson de type P 151 à l'intérieur du substrat semiconducteur 51. Bien que l'on forme également une région de caisson de type N dans le substrat semiconducteur 51, de façon à former des transistors MOS à canal P, ceci n'est pas représenté et la description sera omise. Ensuite, on implante par exemple des ions de bore avec une énergie de 130 keV et une dose de  $5 \times 10^{12} \text{ cm}^{-2}$ , pour former ainsi la couche de coupure de canal 152 à l'intérieur du substrat semiconducteur 51. On fabrique la couche de coupure de canal 152 avec une forme qui, en association avec la couche LOCOS 52, crée les régions présentant une séparation entre éléments.

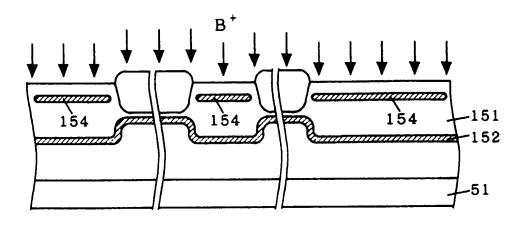

Ensuite, à une étape qui est représentée sur la figure 107, à une position prédéterminée à l'intérieur de la région de caisson 151, on forme la couche dopée de canal 154 qui a la plus faible concentration en impureté, en correspondance avec le transistor T22 de la partie d'amplificateur de lecture. A ce stade, on forme également la couche dopée de canal 154 dans des régions se trouvant à l'intérieur des transistors T21 et T23 de la partie logique et de la partie de réseau de cellules de mémoire. On forme la couche dopée de canal 154 en implantant par exem-

ple des ions de bore, avec une énergie de 50 keV et une dose de 1  $\times$   $10^{12}$  cm<sup>-2</sup>.

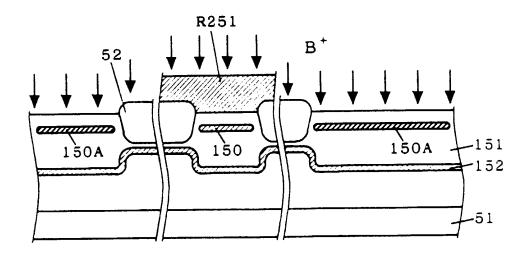

Ensuite, à une étape qui est représentée sur la figure 108, on forme un masque de matière de réserve R251 sur la partie d'amplificateur de lecture. On implante en outre une impureté d'une manière sélective dans la couche dopée de canal 154 de la partie logique et de la partie de réseau de cellules de mémoire, pour former ainsi la couche dopée de canal 153 qui a une concentration en impureté en correspondance avec le transistor T23 de la partie de réseau de cellules de mémoire. A ce stade, on forme également la couche dopée de canal 153 dans une région qui se trouve à l'intérieur du transistor T21 de la partie logique. On forme la couche dopée de canal 153 en implantant par exemple des ions de bore, avec une énergie de 50 keV et une dose de 4 x 10<sup>12</sup> cm<sup>-2</sup>.

5

10

15

20

25

30

35

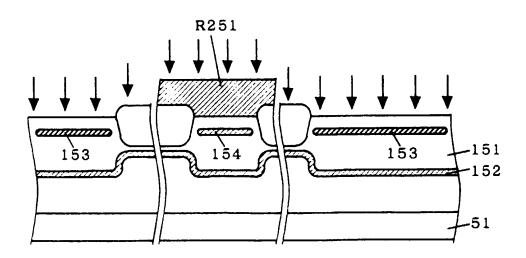

Ensuite, à une étape qui est représentée sur la figure 109, on forme un masque de matière de réserve R252 sur la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire. On implante en outre une impureté d'une manière sélective dans la couche dopée de canal 153 de la partie logique, pour former ainsi la couche dopée de canal 155 qui a une concentration en impureté en correspondance avec le transistor T21 de la partie logique. On forme la couche dopée de canal 155 en implantant par exemple des ions de bore, avec une énergie de 50 keV et une dose de  $5 \times 10^{12}$  cm<sup>-2</sup>.

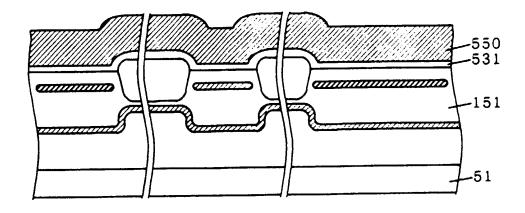

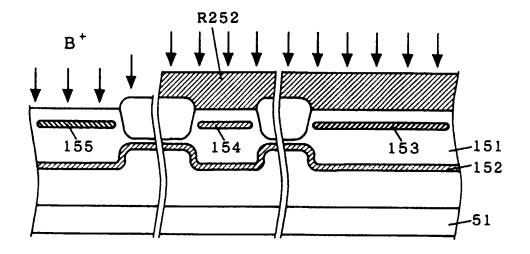

Ensuite, à une étape qui est représentée sur la figure 110, on forme sur la surface principale du substrat semiconducteur 51, par un procédé d'oxydation thermique, une pellicule d'oxyde 531 qui deviendra la pellicule d'oxyde de grille 53. L'épaisseur de la pellicule d'oxyde 531 est d'environ 4 nm.

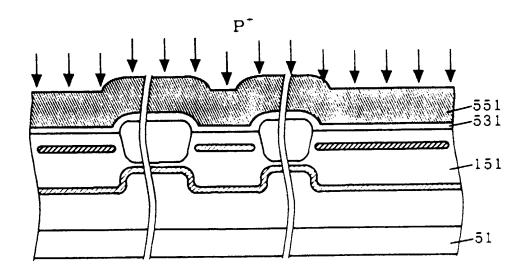

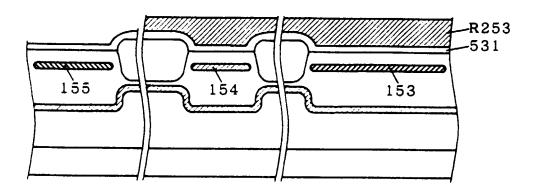

Ensuite, à une étape qui est représentée sur la figure 111, on recouvre avec un masque de matière de réserve R253 l'épaisseur de pellicule d'oxyde 531 de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire, et on enlève sélectivement l'épaisseur de pellicule d'oxyde 531 qui se trouve seulement sur la partie logique.

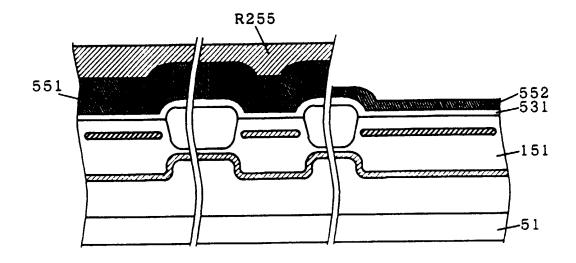

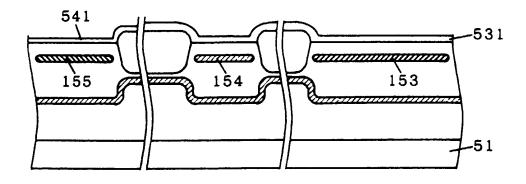

Ensuite, après avoir enlevé le masque de matière de réserve R253, à une étape qui est représentée sur la figure 112, on forme sur la surface principale du substrat semiconducteur 51, par un procédé d'oxy-

dation thermique, une pellicule d'oxyde 541 qui deviendra la pellicule d'oxyde de grille 54. A ce stade, la pellicule d'isolation 531 sur la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire se développe et son épaisseur de pellicule augmente. L'épaisseur de la pellicule d'oxyde 541 est d'environ 6 nm. La pellicule d'oxyde 531 se développe jusqu'à environ 10 nm.

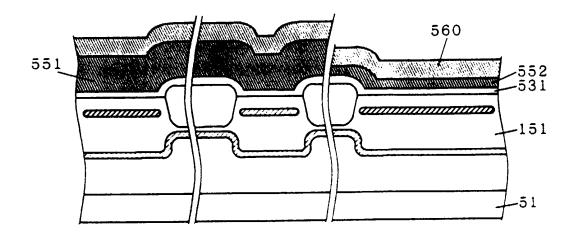

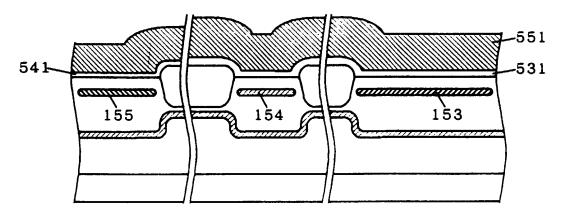

Ensuite, à une étape qui est représentée sur la figure 113, on forme une couche de silicium polycristallin dopé 551, à titre de matériau d'électrode de grille, sur la pellicule d'oxyde 531 et la pellicule d'oxyde 541, par un procédé CVD. L'épaisseur de la couche de silicium polycristallin dopé 551 est d'environ 200 nm. On utilise du phosphore (P) à titre d'impureté. La concentration de l'impureté est d'environ  $1 \times 10^{20} \, \mathrm{cm}^{-3}$ .

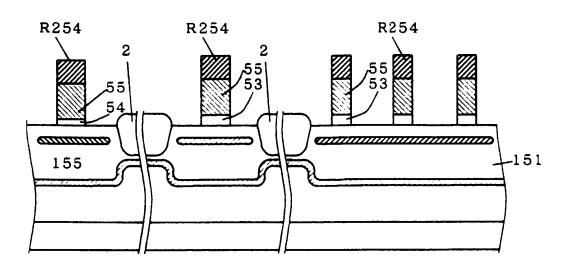

Ensuite à une étape qui est représentée sur la figure 114, on forme un masque de matière de réserve R254 sur la couche de silicium polycristallin dopé 551, et on définit un motif avec ce masque. Par l'opération de définition de motif, l'électrode de grille 54 et l'électrode de grille 55 sont formées dans la partie logique, tandis que la pellicule d'oxyde de grille 53 et l'électrode de grille 55 sont formées dans la partie d'amplificateur de lecture et dans la partie de réseau de cellules de mémoire.

A la suite de ceci, après avoir formé les couches LDD 157 par implantation d'ions dans la partie logique, la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire, on forme la pellicule d'oxyde de paroi latérale 56, d'environ 100 nm d'épaisseur, sur une surface latérale de la pellicule d'oxyde de grille 54 et de l'électrode de grille 55, à l'intérieur de la partie logique, et sur une surface latérale de la pellicule d'oxyde de grille 53 et de l'électrode de grille 55 à l'intérieur de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire. En utilisant à titre de masque la pellicule d'oxyde de paroi latérale 56, on forme les couches de source/drain 156, par implantation ionique. De cette manière, on obtient la structure du Circuit Logique en Mémoire DRAM qui est représentée sur la figure 103.

On forme les couches LDD 157 en implantant par exemple des ions d'arsenic (As), avec une énergie de 30 keV et une dose de 1  $\times$  10<sup>13</sup> cm<sup>-2</sup>. D'autre part, on obtient les couches de source/drain 156 en injectant par exemple des ions d'arsenic, avec une énergie de 50 keV et une

dose de  $5 \times 10^{15}$  cm<sup>-2</sup>, et on effectue ensuite une opération de recuit à  $850^{\circ}$ C pendant 30 minutes.

Bien que ceci soit suivi par la formation d'un condensateur, d'une pellicule d'isolation inter-couche, d'une couche d'interconnexion et autres, pour former le Circuit Logique en Mémoire DRAM, ces opérations ne seront pas décrites et elles ne sont pas représentées dans les dessins.

Problèmes affectant le Circuit Logique en Mémoire DRAM classique Comme décrit ci-dessus, dans le Circuit Logique en Mémoire DRAM classique, pour former à l'intérieur d'une seule puce des transistors qui sont utilisés dans la partie logique, la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire, et qui ont des caractéristiques mutuellement différentes, on change la concentration en impureté de la couche dopée de canal en correspondance avec chaque transistor, et on ajuste une valeur de seuil.

Cependant, lorsque la concentration en impureté de la couche dopée de canal devient plus élevée, la valeur de seuil augmente. En même temps, une fuite de couche de diffusion augmente, du fait que la concentration en impureté devient élevée par exemple dans une partie de jonction entre une couche de diffusion et le substrat. En d'autres termes, la valeur de seuil et la fuite de couche de diffusion sont dans une relation mutuelle de compromis, et par conséquent un courant de fuite est automatiquement déterminé une fois que l'on a déterminé la valeur de seuil. Ainsi, la relation de compromis entre les deux impose une restriction à la conception du circuit.

En outre, dans le but d'améliorer les possibilités d'attaque en courant, la partie logique a une épaisseur de pellicule d'oxyde inférieure à celles des autres parties. Dans ce but, il est nécessaire de former plusieurs types de transistors qui ont des épaisseurs de pellicule d'oxyde différentes les unes des autre, à l'intérieur de la mémoire DRAM qui se présente sous la forme d'une seule puce, et il est nécessaire dans certains cas de former les pellicules d'oxyde en plusieurs étapes. Par exemple, dans la partie d'amplificateur de lecture et la partie de réseau de cellules de mémoire, à l'étape d'enlèvement du masque de matière de réserve R253 (voir la figure 111), la pellicule d'isolation 531 se déve-

loppe davantage au cours de la formation de la pellicule d'oxyde 541 (voir la figure 112). Ainsi, la pellicule d'oxyde 531 est formée en deux étapes. Ceci conduit à une plus grande possibilité de permettre l'entrée d'une impureté ou autre, ce qui dégrade à son tour la fiabilité de la pellicule d'oxyde de grille 53 ou amoindrit la maîtrise de l'épaisseur de pellicule. Ceci conduit en outre à un problème qui consiste en une perte de la fiabilité des transistors MOS à canal N T22 et T23 de la partie d'amplificateur de lecture et de la partie de réseau de cellules de mémoire, etc. Quatrième exemple classique

5

10

15

20

25

30

35

Structure d'ensemble d'une mémoire flash comprenant un circuit logique

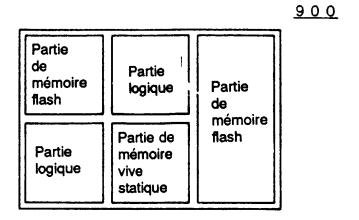

A titre de quatrième exemple classique, on va décrire une structure d'une mémoire flash 900 qui comprend un circuit logique (que l'on appelle ci-après "Circuit Logique en Mémoire Flash"), ainsi qu'un procédé de fabrication de cette structure.

L'un des objectifs en recherche et développement qui retient l'attention au fur et à mesure de l'augmentation de la densité d'implantation de transistors, consiste dans le développement d'un micro-ordinateur en une seule puce, dans lequel un micro-ordinateur est fabriqué à l'intérieur d'une seule puce, tandis qu'un autre objectif de recherche et développement qui suscite une grande attention est l'obtention d'une plus grande capacité. En particulier, un élément dans lequel une mémoire flash et un microprocesseur sont formés à l'intérieur d'une seule puce, est appelé un élément logique intégré avec une mémoire flash, comme celui qui a été divulgué dans le document 1995 IDEM SHORT COURSE PROGRAM, "EMBEDDED FLASH MEMORY APPLICATIONS, TECHNOLOGY AND DESIGN", CLINTON KUO, MOTOROLA, et autres.

La figure 115 montre un exemple. Comme représenté sur la figure 115, le Circuit Logique en Mémoire Flash 900 est divisé grossièrement en une partie logique et une partie de mémoire flash. Une exigence pour la partie logique consiste en un fonctionnement à vitesse élevée, c'est-à-dire une possibilité d'attaque élevée et une faible capacité.

La partie de mémoire flash comprend une partie supportant une tension élevée, dans laquelle une tension élevée est appliquée, une partie de réseau de cellules de mémoire dans laquelle une pellicule d'oxyde tunnel doit être très fiable, et autres. Ainsi, un ensemble de types de transistors qui ont des caractéristiques mutuellement différentes sont nécessaires dans le Circuit Logique en Mémoire Flash qui est formé en une seule puce.

Structures des transistors respectifs

5

10

15

20

25

30

35

Une technique classique pour former dans une seule puce des transistors qui ont des caractéristiques mutuellement différentes consiste à changer une épaisseur de pellicule d'oxyde en correspondance avec un transistor, ou si nécessaire, à changer un profil d'impureté d'une couche dopée de canal. Dans ce qui suit, on décrira un exemple dans lequel une épaisseur de pellicule d'oxyde est changée en correspondance avec un transistor, tout en changeant une concentration d'impureté d'une couche dopée de canal.

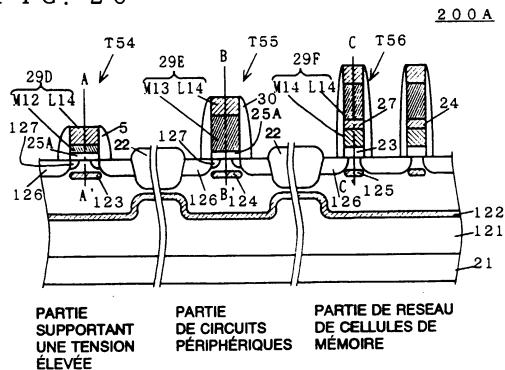

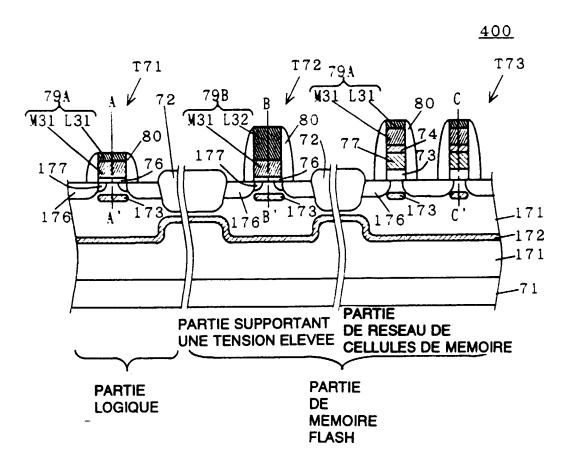

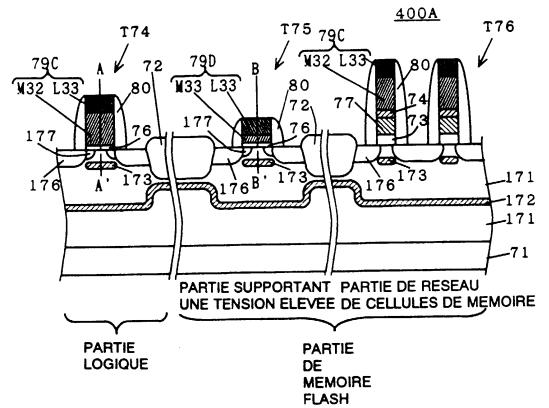

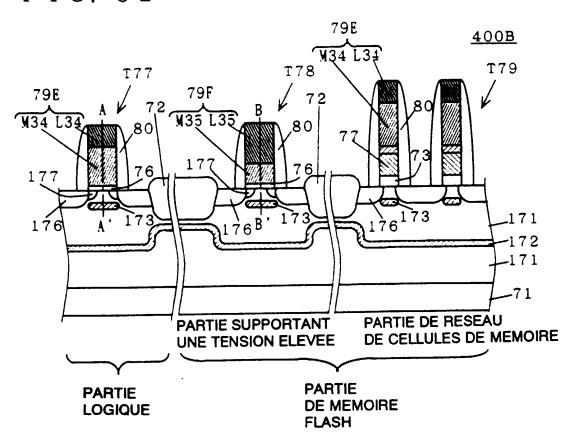

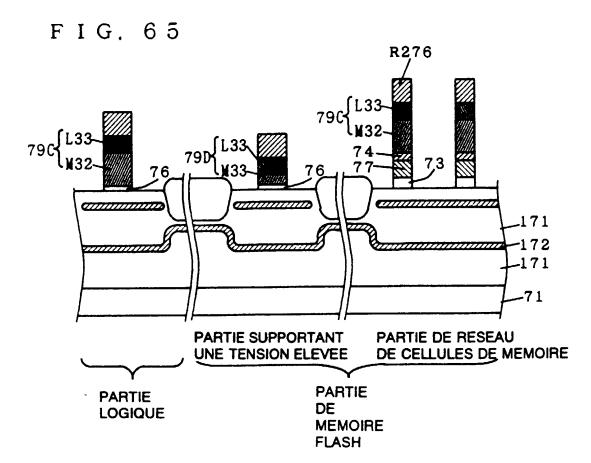

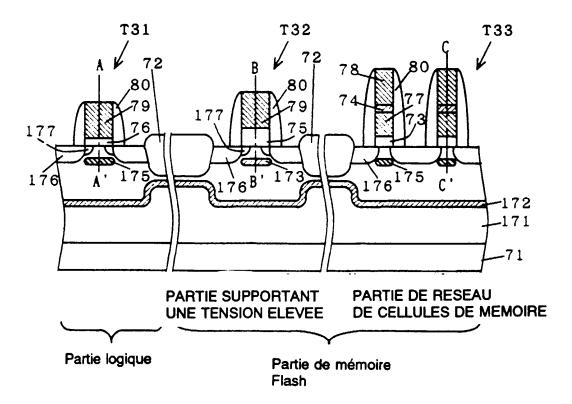

La figure 116 montre (en une vue partielle) un exemple d'une structure d'un Circuit Logique en Mémoire Flash qui est fabriquée par un procédé de fabrication classique. La figure montre des coupes de transistors MOS à canal N T31 à T33 qui sont utilisés pour la partie logique et pour la partie supportant une tension élevée et la partie de réseau de cellules de mémoire de la partie de mémoire flash.

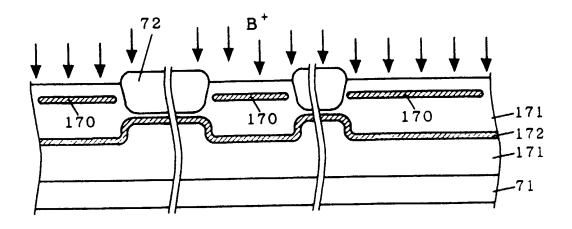

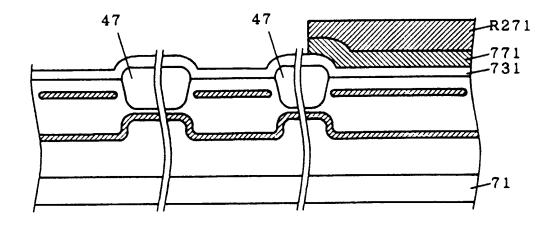

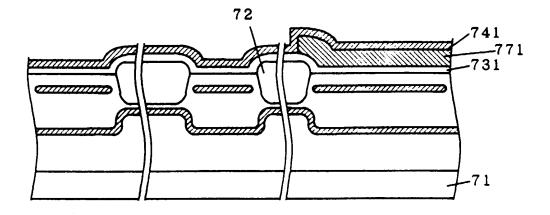

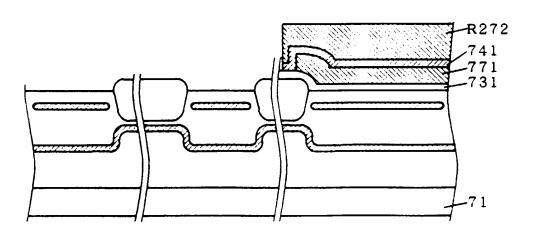

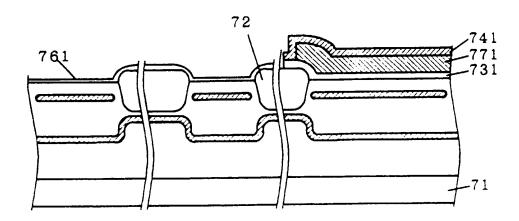

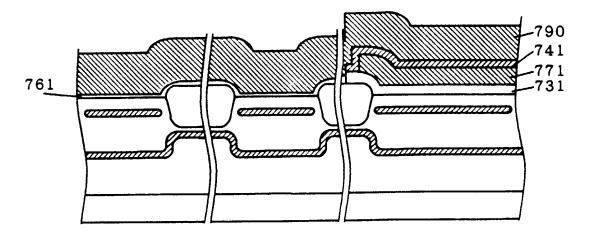

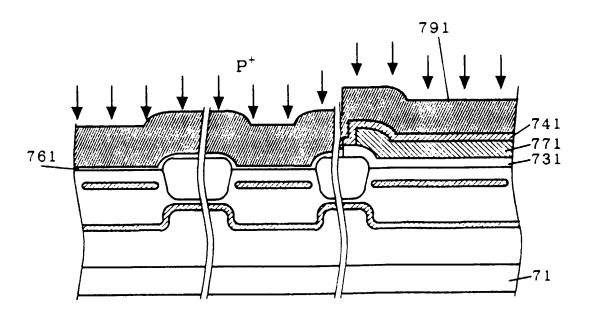

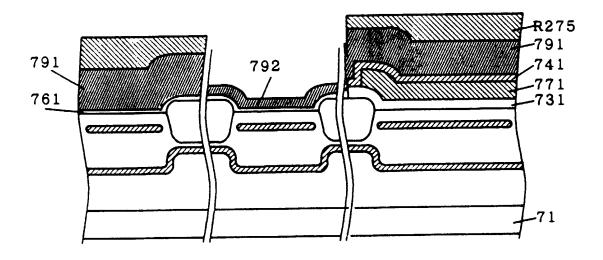

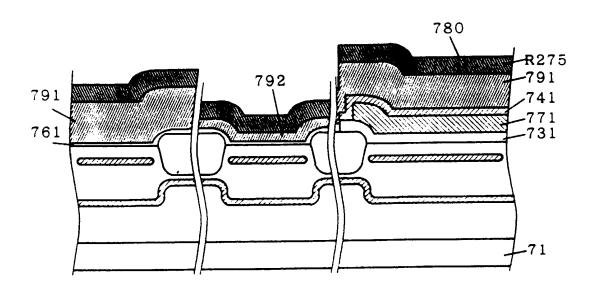

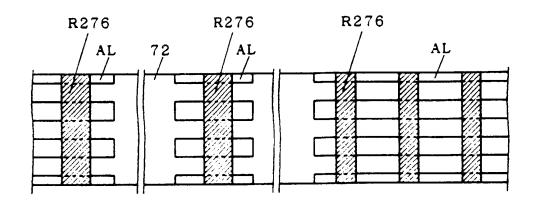

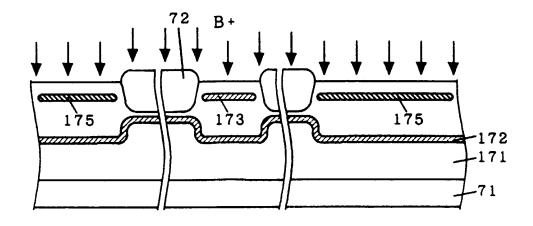

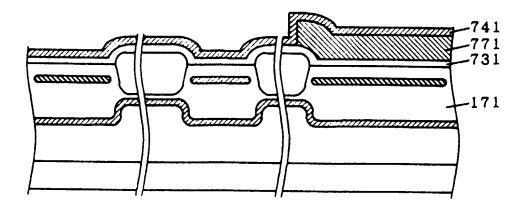

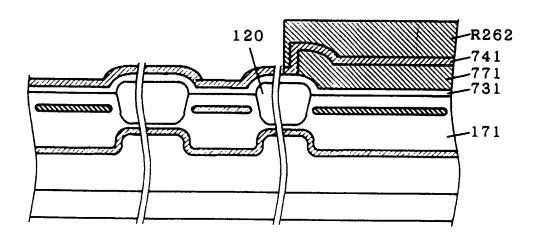

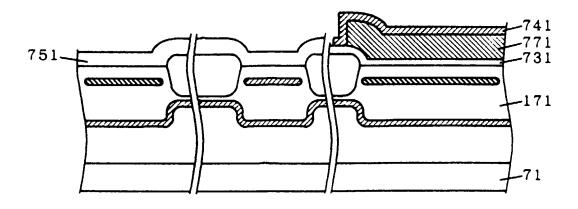

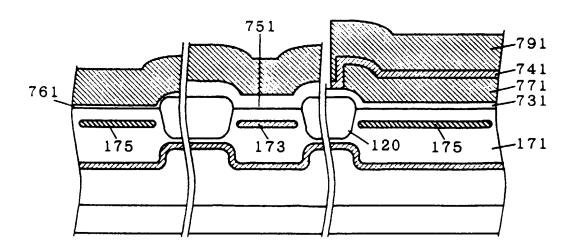

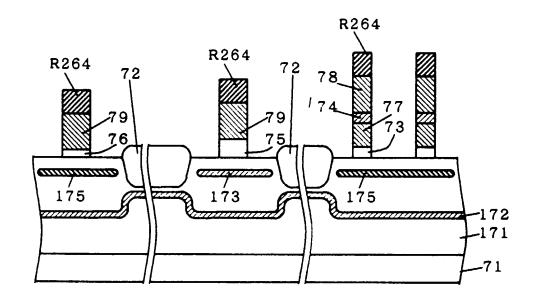

Sur la figure 116, les transistors MOS à canal N T31 à T33 sont formés à l'intérieur d'une couche de caisson de type P 171 qui est formée sur le même substrat semiconducteur 71 (du type P). La couche de caisson 171 fait l'objet d'une séparation entre éléments par une couche de coupure de canal 172 qui est formée à l'intérieur de la couche de caisson 171, et par une couche LOCOS 72, d'une manière telle que les transistors MOS à canal N T31 à T33 soient formés dans des régions qui sont créées par la séparation entre éléments.

Le transistor MOS à canal N T31 de la partie logique comprend une paire de couches de source/drain 176 qui sont formées à l'intérieur de la région de caisson 171, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 177 qui sont formées dans des positions adjacentes à des parties de bord en regard des couches de source/drain 176.

Une pellicule d'oxyde de grille 76 est formée sur les couches LDD 177, et une électrode de grille 79 est formée sur la pellicule d'oxyde de grille 76. Une pellicule d'oxyde de paroi latérale 80 est formée sur une surface latérale de la pellicule d'oxyde de grille 76 et de l'électrode de grille 79. Une couche dopée de canal 175 est formée à l'intérieur de la couche de caisson 171, sous l'électrode de grille 79.

Le transistor MOS à canal N T32 de la partie supportant une tension élevée dans la partie de mémoire flash, comprend une paire de couches de source/drain 176 qui sont formées à l'intérieur de la couche de caisson 171, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre, et une paire de couches LDD 177.

5

10

15

20

25

30

35

Une pellicule d'oxyde de grille 75 est formée sur les couches LDD 177, et une électrode de grille 79 est formée sur la pellicule d'oxyde de grille 75. La pellicule d'oxyde de paroi latérale 80 est formée sur une surface latérale de la pellicule d'oxyde de grille 75 et de l'électrode de grille 79. Une couche dopée de canal 173 est formée à l'intérieur de la couche de caisson 171, sous l'électrode de grille 79.

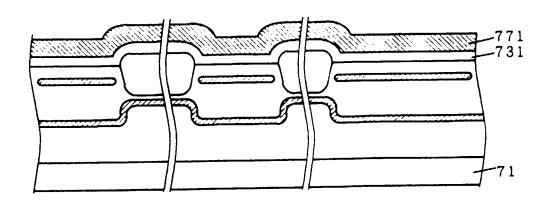

Le transistor MOS à canal N T33 de la partie de réseau de cellules de mémoire de la partie de mémoire flash comprend une paire de couches de source/drain 176 qui sont formées à l'intérieur de la couche de caisson 171, indépendamment l'une de l'autre, mais parallèlement l'une à l'autre. Une pellicule d'oxyde tunnel 73 est formée sur des parties de bord des couches de source/drain 176. Une électrode de grille flottante 77, une pellicule d'isolation inter-couche 74 et une électrode de grille de commande 78 sont formées dans cet ordre sur la pellicule d'oxyde tunnel 73.

La pellicule d'oxyde de paroi latérale 80 est formée sur une surface latérale de la pellicule d'oxyde tunnel 73, de l'électrode de grille flottante 77, de la pellicule d'isolation inter-couche 74 et de l'électrode de grille de commande 78.

Une région dopée de canal 175 est formée à l'intérieur de la couche de caisson 171, sous l'électrode flottante 77. La partie de réseau de cellules de mémoire a une structure de réseau de grilles dans laquelle des grilles adjacentes se partagent une seule couche de source/drain 176. De telles structures sont disposées en succession.

Une caractéristique de la mémoire flash qui est représentée sur la figure 116 consiste en ce que l'épaisseur de la pellicule d'oxyde de

grille 75 du transistor MOS à canal N T32 de la partie supportant une tension élevée est la plus grande, et elle est suivie par l'épaisseur de la pellicule d'oxyde tunnel 73 du transistor MOS à canal N T33 de la partie de réseau de cellules de mémoire, et par l'épaisseur de la pellicule d'oxyde de grille 76 du transistor MOS à canal N T31 de la partie logique, dans cet ordre, et en ce que la concentration en impureté de la couche dopée de canal 173 du transistor MOS à canal N T32, de la partie supportant une tension élevée, est inférieure à celles des autres couches dopées de canal.

Le Tableau 4 montre des valeurs numériques concernant les structures des transistors MOS à canal N T31 à T33.

TABLEAU 4

| Epaisseur de pellicule d'oxyde de champ<br>Epaisseur de pellicule d'oxyde de grille | 400 nm<br>6 nm                     | (T32)                              |                                    |

|-------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|

| Epaisseur de pellicule d'oxyde de champ<br>Epaisseur de pellicule d'oxyde de grille | 400 nm<br>6 nm                     |                                    | (T33)                              |

| de champ<br>Epaisseur de pellicule d'oxyde<br>de grille                             | 6 nm                               | 400 nm                             | 400 nm                             |

| Epaisseur de pellicule d'oxyde de arille                                            | 6 nm                               |                                    |                                    |

| de arille                                                                           |                                    | 25 nm                              | 10 nm                              |

|                                                                                     |                                    |                                    |                                    |

| Epaisseur de pellicule                                                              | 1 6 0 1                            | -                                  | 100 nm                             |

| d'électrode de grille flottante                                                     |                                    |                                    | C                                  |

| Concentration en impureté de                                                        | 1                                  |                                    | $1 \times 10^{20} \text{cm}^{-3}$  |

| grille flottante                                                                    |                                    |                                    |                                    |

| Epaisseur de pellicule                                                              |                                    | 1                                  | TEOS/Si3N4/TEOS =                  |

| d'isolation inter-couche                                                            |                                    |                                    | 10/10/10 nm                        |

| Epaisseur de pellicule d'élec-                                                      | 200 nm                             | 200 nm                             | 200 nm                             |

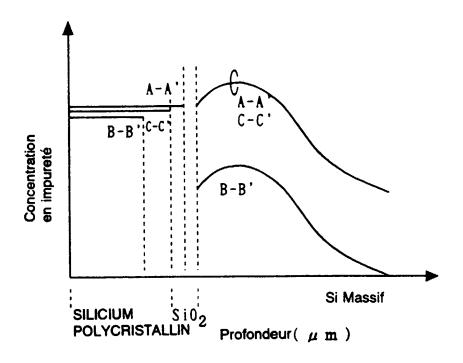

| trode de grille de commande                                                         |                                    |                                    |                                    |