## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**HO3F 3/45** (2006.01) **HO4R 3/06** (2006.01)

(21) 출원번호

10-2014-0142066

(22) 출원일자

2014년10월20일

심사청구일자 2014년10월20일

(56) 선행기술조사문헌

KR101151985 B1\*

JP2004527169 A\*

W02003049282 A1\*

KR100408796 B1

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2016년03월08일

(11) 등록번호 10-1601179

(24) 등록일자 2016년03월02일

(73) 특허권자

## 현대자동차 주식회사

서울특별시 서초구 헌릉로 12 (양재동)

(72) 발명자

#### 양상혁

경기도 수원시 장안구 덕영대로395번길 4-11, 30 1호 (율전동)

#### 박상규

서울특별시 서초구 나루터로4길 39,319동 308호 (잠원동, 신반포아파트)

(74) 대리인

유미특허법인

전체 청구항 수 : 총 8 항

심사관 : 손희수

(54) 발명의 명칭 마이크로폰의 아날로그 신호 처리 회로

## (57) 요 약

본 발명의 일 실시예에 따른 마이크로폰의 아날로그 신호 처리 회로는, 마이크로폰으로부터 신호를 입력 받아 제 1 신호를 출력하는 제1 서브회로 및 기준 전압을 입력 받아 제2 신호를 출력하는 제2 서브회로를 포함하는 바이어스 회로부; 및 상기 제1 신호 및 제2 신호를 입력 받아 완전 차동 신호를 출력하는 완전 차동 회로부;를 포함한다. 각각의 상기 제1 서브회로 및 제2 서브회로는 바이어스 전압을 인가하는 바이어스 회로를 포함한다.

#### 대 표 도 - 도2

## 명세서

## 청구범위

#### 청구항 1

마이크로폰으로부터 신호를 입력 받아 제1 신호를 출력하는 제1 서브회로 및 기준 전압을 입력 받아 제2 신호를 출력하는 제2 서브회로를 포함하는 바이어스 회로부; 및

상기 제1 신호 및 제2 신호를 입력 받아 완전 차동 신호를 출력하는 완전 차동 회로부;

를 포함하며,

각각의 상기 제1 서브회로 및 제2 서브회로는 바이어스 전압을 인가하는 바이어스 회로를 포함하고,

상기 바이어스 회로는 제1 역평행 다이오드 쌍 및 제2 역평행 다이오드 쌍을 포함하고,

상기 제1 역평행 다이오드 쌍은 제2 역평행 다이오드 쌍과 직결되어 있고,

상기 제1 역평행 다이오드 쌍에는 제1 기준 전압이 인가되고, 상기 제2 역평행 다이오드 쌍에는 제2 기준 전압이 인가되어, 상기 제1 및 제2 역평행 다이오드 쌍의 접점에 제1 및 제2 기준 전압의 중간 전압이 인가되<u>는</u> 마이크로폰의 아날로그 신호 처리 회로.

#### 청구항 2

삭제

#### 청구항 3

제1항에서,

상기 제1 및 제2 기준 전압은 서로 다른 크기를 가지는 마이크로폰의 아날로그 신호 처리 회로.

### 청구항 4

제1항에서.

각각의 상기 제1 서브회로 및 제2 서브회로는 상기 바이어스 회로의 전단에 커패시터를 포함하는 마이크로폰의 아날로그 신호 처리 회로.

### 청구항 5

제4항에서,

상기 제1 서브회로의 커패시터의 정전 용량과 상기 제2 서브회로의 커패시터의 정전 용량은 서로 동일한 마이크로폰의 아날로그 신호 처리 회로.

#### 청구항 6

제1항에서,

상기 완전 차동 회로부는 완전 차동 증폭기 및 저항 분할기를 포함하는 마이크로폰의 아날로그 신호 처리 회로.

## 청구항 7

제6항에서.

상기 저항 분할기는 가변 저항기를 포함하는 마이크로폰의 아날로그 신호 처리 회로.

## 청구항 8

제6항에서,

상기 완전 차동 회로부는 각각 두 개의 입력 단자를 가진 제1 차동 입력단 및 제2 차동 입력단, 그리고 두 개의 출력 단자를 가진 차동 출력단을 포함하고,

상기 제1 신호는 제1 차동 입력단의 한 입력 단자에 입력되고, 상기 제2 신호는 제2 차동 입력단의 한 입력 단자에 입력되는 마이크로폰의 아날로그 신호 처리 회로.

#### 청구항 9

제8항에서,

상기 저항 분할기는 상기 제1 차동 입력단의 다른 입력 단자와 상기 차동 출력단의 한 출력 단자 사이에 연결되어 있는 제1 저항 분할기 및 상기 제2 차동 입력단의 다른 입력 단자와 상기 차동 출력단의 다른 출력 단자 사이에 연결되어 있는 제2 저항 분할기를 포함하는 마이크로폰의 아날로그 신호 처리 회로.

### 발명의 설명

#### 기술분야

[0001] 본 발명은 마이크로폰에 관한 것으로, 특히 마이크로폰의 아날로그 신호 처리 회로에 관련된다.

#### 배경기술

- [0002] 모바일 기기, 음향 기기 또는 자동차 등에 널리 사용되는 마이크로폰은 소리 즉, 음파를 감지하여 물리적인 값 또는 전기적인 값으로 변환시킨다. 변환된 신호는 최종적으로 사람 또는 기계가 알아들을 수 있는 신호가 되도록 처리된다.

- [0003] 마이크로폰은 음파 등의 자연적인 신호를 입력 받으므로, 신호 변환에 있어서 아날로그 신호 처리가 필수적이다. 아날로그 신호 처리를 위한 회로의 성능은 마이크로폰의 전체 성능에 직접적인 영향을 줄 수 있다. 특히 마이크로폰은 특성상 넓은 주파수 범위를 입력으로 받으므로, 잡음 특성이 매우 중요하다.

- 마이크로폰에서 출력되는 신호는 단일 신호(single signal)이므로 잡음 특성에 유리한 완전 차동 신호로 변환하는 것이 필요하다. 또한, 완전 차동 구조에서의 입력단 직류(DC) 바이어스 기능, 그리고 신호의 크기 즉, 감도를 조절해 주는 증폭률 조절 기능도 필수적인 것으로 여겨진다. 통상적으로, 아날로그 신호 처리 회로는 이들세 가지 기능을 각각 구현하는 회로들의 조합으로 구성된다. 하지만 여러 회로의 조합은 결과적으로 전기적 잡음이 증가하는 원인이 될 수 있다.

## 발명의 내용

[0004]

[0005]

### 해결하려는 과제

본 발명의 목적은 마이크로폰의 아날로그 신호 처리에 필요한 기능들을 포함하며 잡음 특성이 유리한 신호 처리 회로를 제공하는 것이다.

#### 과제의 해결 수단

- [0006] 본 발명의 일 실시예에 따른 마이크로폰의 아날로그 신호 처리 회로는, 마이크로폰으로부터 신호를 입력 받아 제1 신호를 출력하는 제1 서브회로 및 기준 전압을 입력 받아 제2 신호를 출력하는 제2 서브회로를 포함하는 바이어스 회로부; 및 상기 제1 신호 및 제2 신호를 입력 받아 완전 차동 신호를 출력하는 완전 차동 회로부;를 포함한다. 각각의 상기 제1 서브회로 및 제2 서브회로는 바이어스 전압을 인가하는 바이어스 회로를 포함한다.

- [0007] 상기 바이어스 회로는 두 개의 역평행 다이오드 쌍을 포함할 수 있다.

- [0008] 각각의 역평행 다이오드 쌍에 서로 다른 기준 전압이 인가될 수 있다.

- [0009] 각각의 상기 제1 서브회로 및 제2 서브회로는 상기 바이어스 회로의 전단에 커패시터를 포함할 수 있다.

- [0010] 상기 제1 서브회로의 커패시터의 정전 용량과 상기 제2 서브회로의 커패시터의 정전 용량은 서로 동일할 수 있다

- [0011] 상기 완전 차동 회로부는 완전 차동 증폭기 및 저항 분할기를 포함할 수 있다.

- [0012] 상기 저항 분할기는 가변 저항기를 포함할 수 있다.

- [0013] 상기 완전 차동 회로부는 각각 두 개의 입력 단자를 가진 제1 차동 입력단 및 제2 차동 입력단, 그리고 두 개의 출력 단자를 가진 차동 출력단을 포함할 수 있다. 상기 제1 신호는 제1 차동 입력단의 한 입력 단자에 입력될 수 있고, 상기 제2 신호는 제2 차동 입력단의 한 입력 단자에 입력될 수 있다.

- [0014] 상기 저항 분할기는 상기 제1 차동 입력단의 다른 입력 단자와 상기 차동 출력단의 한 출력 단자 사이에 연결되어 있는 제1 저항 분할기 및 상기 제2 차동 입력단의 다른 입력 단자와 상기 차동 출력단의 다른 출력 단자 사이에 연결되어 있는 제2 저항 분할기를 포함할 수 있다.

#### 발명의 효과

[0015] 본 발명에 따른 신호 처리 회로는 마이크로폰의 아날로그 신호 처리 회로에 필요한 기능들을 모두 포함한다. 여러 기능이 하나의 회로에서 모두 구현되므로, 회로 구성을 단순화하여 회로에서 발생하는 전기적 잡음을 최소화할 수 있고, 회로에서 전류 소모가 감소할 수 있다. 또한, 회로의 전체 면적을 줄일 수 있으므로 제조 원가를 낮출 수 있다.

## 도면의 간단한 설명

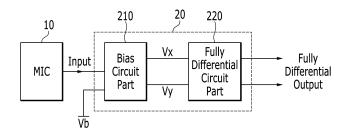

[0016] 도 1은 본 발명의 일 실시예에 따른 아날로그 신호 처리 회로의 블록도이다.

도 2는 본 발명의 일 실시예에 따른 아날로그 신호 처리 회로의 회로도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0017] 첨부한 도면을 참고로 하여, 본 발명의 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다.

- [0018] 본 발명의 실시예를 명확하게 설명하기 위해서 설명과 관계 없는 부분은 생략하였으며, 명세서 전체를 통하여 동일 또는 유사한 구성 요소에 대해서는 동일한 참조 부호를 붙이도록 한다.

- [0019] 명세서 전체에서 어떤 부분이 다른 부분과 "연결"되어 있다고 할 때, 이는 "직접적으로 연결"되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 "전기적으로 연결"되어 있는 경우도 포함한다. 또한 어떤 부분이 어떤 구성 요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성 요소를 제외하는 것이 아니라 다른 구성 요소를 더 포함할 수 있는 것을 의미한다.

- [0020] 이하 본 발명의 실시예에 따른 마이크로폰의 아날로그 신호 처리 회로에 대하여 도면을 참고로 하여 상세하게 설명한다. 마이크로폰의 아날로그 신호 처리 회로는 신호 처리 회로로 간단하게 언급될 수 있다.

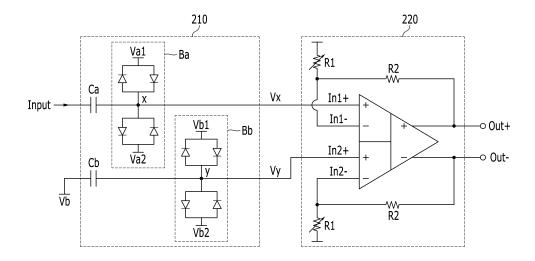

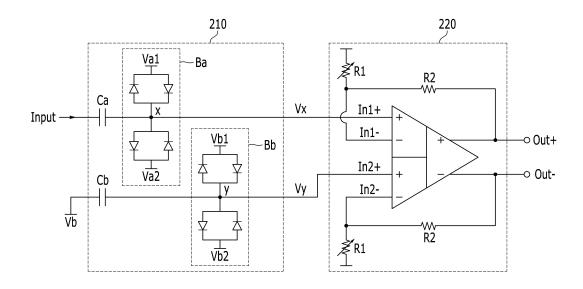

- [0021] 도 1은 본 발명의 일 실시예에 따른 아날로그 신호 처리 회로의 블록도이고, 도 2는 본 발명의 일 실시예에 따른 아날로그 신호 처리 회로의 회로도이다.

- [0022] 먼저 도 1을 참조하면, 본 발명의 일 실시예에 따른 아날로그 신호 처리 회로(20)는 마이크로폰(10)으로부터 단일 신호(single signal)를 입력 받아 완전 차동 신호(fully differential signals)를 출력한다. 신호 처리 회로(20)는 마이크로폰(10)에서 발생하는 정전 용량의 변화를 전압 신호로 변환할 수 있다.

- [0023] 마이크로폰(10)은 음파를 받아서 그 진동에 따른 전기 신호를 발생시키는 장치로서, 예컨대 MEMS(micro electro mechanical system) 마이크로폰일 수 있다. 일반적으로, MEMS 마이크로폰은 정전 용량 방식과 압전 방식으로 구분된다. 정전 용량 방식은 커패시터를 형성하는 고정 전극과 진동막을 포함한다. 음파에 따른 음압이 외부로부터 진동막에 가해지면 진동막이 진동하면서 고정 전극과 진동막 사이의 간격이 변하게 되고, 이에 따라 커패시터의 정전 용량이 변하게 된다. 이때 마이크로폰은 전기 신호를 발생시킨다. 정전 용량 방식과 달리 압전 방식은 진동막만을 포함한다. 외부 음압에 의해 진동막이 변형되면, 마이크로폰은 압전 효과로 인해 전기 신호를 발생시킨다.

- [0024] 신호 처리 회로(20)는 바이어스 회로부(210) 및 완전 차동 회로부(220)를 포함한다. 바이어스 회로부(210)와 완전 차동 회로부(220)는 하나의 회로로 구성될 수 있다.

- [0025] 완전 차동 회로부(220)는 기본적으로 마이크로폰에서 출력되는 단일 신호를 공통 잡음 특성에 유리한 완전 차동

신호로 변환하는 기능을 수행한다. 바이어스 회로부(210)는 기본적으로 완전 차동 회로부(220)의 입력단에 연결되어 원하는 바이어스 전압을 인가하는 한편, 단일 신호를 완전 차동 신호로 변환하면서 발생할 수 있는 차동 신호 간 DC 오프셋을 최소화하는 기능을 수행한다.

- [0026] 도 2를 참조하면, 바이어스 회로부(210)는 서로 분리되어 있는 두 개의 서브회로(sub-circuit) 즉, 제1 및 제2 서브회로를 포함한다. 제1 서브회로는 입력단에 마이크로폰(10)으로부터의 AC 신호를 입력 받아 원하는 DC 바이어스 전압이 실린 AC 신호인 제1 신호(Vx)를 출력한다. 제2 서브회로는 기준 전압(Vb)을 입력 받아 제1 신호(Vx)의 바이어스 전압과 동일한 바이어스 전압을 가진 제2 신호(Vy)를 출력한다.

- [0027] 각각의 서브회로는 커패시터(Ca, Cb) 및 바이어스 회로(Ba, Bb)를 포함한다.

- [0028] 제1 서브회로의 커패시터(Ca)는 노드(x)에 연결되어 있고, 제2 서브회로의 커패시터(Cb)는 노드(y)에 연결되어 있다. 커패시터(Ca, Cb)는 입력단으로 들어오는 신호에서 DC 전류를 막아주어 두 노드(x, y)의 환경을 최대한 유사하게 만들어 줄 수 있다. 즉, 커패시터(Ca, Cb)는 DC 차단(blocking) 용도로 사용되며, 커패시터(Ca, Cb)에 의해 유사 임피던스 환경이 설정될 수 있다. 유사 임피던스 환경 설정을 위해, 제1 서브회로의 커패시터(Ca)와 제2 서브회로의 커패시터(Cb)는 정전 용량이 서로 동일할 수 있다.

- [0029] 제1 서브회로의 바이어스 회로(Ba)는 노드(x)에 연결되어 있고, 제2 서브회로의 바이어스 회로(Bb)는 노드(x)에 연결되어 있다. 바이어스 회로(Ba, Bb)는 입력 신호가 흘러가는 통로(pass)에 바이어스 전압을 인가하는 역할을 한다.

- [0030] 바이어스 회로(Ba)는 두 개의 역평행(anti-parallel) 다이오드 쌍이 노드(x)에 연결되어 있는 구조를 갖는다. 역평행 다이오드 쌍은 역평행 방식으로 접속된 두 개의 다이오드를 포함하며, 이들 다이오드는 서로 대향 분극을 갖는 상태로 접속된다. 역평형행 다이오드 쌍은 작은 면적을 차지하면서 큰 저항을 만들 수 있다. 하나의 역평행 다이오드 쌍에는 기준 전압(Va1)이 인가되고 다른 하나의 역평행 다이오드 쌍에는 기준 전압(Va2)이 인가된다. 이에 의해 노드(x)에는 두 기준 전압(Va1, Va2)의 중간 전압인 [(Va1 + Va2)/2]으로 바이어스 전압이인가될 수 있다.

- [0031] 바이어스 회로(Bb) 또한 2개의 역평행 다이오드 쌍이 노드(y)에 연결되어 있는 구조를 갖는다. 이들 중 하나의 역평행 다이오드 쌍에는 기준 전압(Vb1)이 인가되고 다른 하나의 역평행 다이오드 쌍에는 기준 전압(Vb2)이 인가된다. 따라서 노드(y)에는 두 기준 전압(Vb1, Vb2)의 중간 전압인 [(Vb1+Vb2)/2]으로 바이어스 전압이 인가될 수 있다.

- [0032] 제1 서브회로의 바이어스 회로(Ba)와 제2 서브회로의 바이어스 회로(Bb)는 서로 동일한 구조를 가질 수 있다. 또한, 바이어스 회로(Ba)와 바이어스 회로(Bb)에 인가되는 기준 전압은 서로 동일할 수 있다. 즉, Va1과 Vb1이 동일할 수 있고 Va2와 Vb2가 동일할 수 있다. 실시예에 따라서 바이어스 회로(Ba, Bb)는 하나의 역평행 다이오 드 쌍을 포함할 수 있고, 직렬, 병렬 및/또는 다른 어레이 구성으로 접속된 다수의 다이오드를 포함할 수도 있다.

- [0033] 위와 같이, 바이어스 회로부(210)는 두 노드(x, y)에 1차로 커패시터(Ca, Cb)를 이용하여 유사 임피던스 환경을 설정하고, 이후 바이어스 회로(Ba, Bb)를 이용하여 두 바이어스 전압의 중간 전압으로 동일한 DC 전압을 바이어 싱 한다. 이에 의해 두 입력단 중 하나의 입력단으로 신호를 받는 완전 차동 구조에서, 바이어스 회로부(210)는 차동 AC 신호의 DC 오프셋을 최소화하여 출력 신호의 왜곡을 최소화할 수 있다.

- [0034] 완전 차동 회로부(220)는 완전 차동 증폭기(fully differential difference amplifier, FDDA) 및 저항 분할기 (resistive divider)를 포함한다.

- [0035] FDDA는 일반적인 연산 증폭기의 차동 입력을 다시 차동으로 나누는 이중 차동 구조로 볼 수 있다. FDDA는 입력 단(input stage)으로서 제1 차동 입력단 및 제2 차동 입력단을 포함한다. 제1 차동 입력단은 두 개의 입력 단자(In1+, In1-)를 갖고, 제2 차동 입력단 또한 두 개의 입력 단자(In2+, In2-)를 갖는다. 따라서 FDDA는 모두 네 개의 입력 단자를 갖는다. FDDA는 두 개의 출력 단자(Out+, Out-)를 갖는 차동 출력단을 포함한다. 이상적으로(ideally), 두 개의 차동 입력 전압은 제1 및 제2 입력단을 통해 전류로 변환된 후 출력단에 의해 증폭될 수 있다. 이상적인 FDDA는 공통 모드 전압을 억제하면서 차동 전압을 증폭할 수 있다. 이상적으로, FDDA의 거동(behavior)은 다음 식과 같이 정의되며, 식에서 A는 어느 차동 입력단에서 출력까지의 전압 이득을 나타낸다.

- [0036]  $V_{0ut+} V_{0ut-} = A[(V_{In1+} V_{In1-}) (V_{In2+} V_{In2-})]$

[0037]

FDDA는 바이어스 회로부(210)의 제1 서브회로에서 출력되는 제1 신호(Vx)를 제1 차동 입력단의 입력 단자(In1+)를 통해 입력 받는다. 바이어스 회로부(210)의 제2 서브회로에서 출력되는 제2 신호(Vy)는 제2 차동 입력단의 입력 단자(In2+)로 입력된다. 실시예에 따라서, 제1 신호(Vx)는 제2 차동 입력단의 입력 단자(In2+)로 입력되고 제2 신호는 제1 차동 입력단의 입력 단자(In1+)로 입력될 수 있다. 또한, 제1 신호(Vx)는 제1 차동 입력단의 입력 단자(In1-)로 입력되고 제2 신호는 제2 차동 입력단의 입력 단자(In2-)로 입력될 수 있으며, 반대로 제1 신호(Vx)는 제2 차동 입력단의 입력 단자(In2-)로 입력되고 제2 신호는 제1 차동 입력단의 입력 단자(In1-)로 입력된 수 있다. 다시 말해, 제1 신호(Vx) 및 제2 신호(Vy)는 제1 및 제2 차동 입력단에 각각 있는 같은 부호의 입력 단자로 입력될 수 있다. FDDA는 출력 단자(Out+, Out-)를 통해 완전 차동 신호를 출력한다.

[0038]

저항 분할기는 제1 차동 입력단의 한 입력 단자(In1-)과 차동 출력단의 출력 단자(Out+) 사이에 연결되어 있는 제1 저항 분할기, 그리고 제2 차동 입력단의 한 입력 단자(In2-)과 차동 출력단의 출력 단자(Out-) 사이에 연결되어 있는 제2 저항 분할기를 포함한다. 따라서 두 출력 전압(V<sub>Out+</sub>, V<sub>Out-</sub>)의 피드백 루프가 서로 대칭적이다. 제1 및 제2 저항 분할기는 제1 및 제2 차동 입력단에 각각 있는 같은 부호의 입력 단자(In1-, In2-; 또는 In1+, In2+)에 연결될 수 있지만, 제1 및 제2 신호(Vx, Vy)가 입력되는 입력 단자로는 연결되지 않는다.

[0039]

제1 및 제2 저항 분할기는 예컨대 두 개의 저항기(R1, R2)를 포함한다. 저항기(R2)는 차동 출력단의 출력 단자 (Out+)와 제1 차동 입력단의 한 입력 단자(In1-) 사이에 연결될 수 있고, 저항기(R1)는 제1 차동 입력단의 상기한 입력 단자(In1-)와 기준 전압 또는 접지 전압 사이에 연결될 수 있다. 제2 저항 분할기에서, 저항기(R2)는 차동 출력단의 출력 단자(Out-)와 제2 차동 입력단의 한 입력 단자(In2-) 사이에 연결될 수 있고, 저항기(R1)는 제2 차동 입력단의 상기 한 입력 단자(In2-)와 기준 전압 또는 접지 전압 사이에 연결될 수 있다. 이들 저항기(R1, R2) 중 저항기(R1)는 가변 저항기일 수 있다. 실시예에 따라서 저항기(R2)가 가변 저항기일 수 있다. 저항 분할기는 커패시터를 포함할 수도 있다.

[0040]

저항 분할기는 FDDA의 전압 이득(A)을 설정할 수 있다. 출력 전압( $V_{Out+}$ ,  $V_{Out-}$ )이 저항기(R2)를 거쳐 반전 입력 단자(In1-, In2-)에 다시 전달되도록 도 2에 도시된 것처럼 연결되어 있는 경우, FDDA는 비반전 증폭기(non-inverting amplifier)를 형성하고, 전압 이득(A)은 다음 식과 같이 정의된다.

[0041]

A = (1 + R2/R1)

[0042]

따라서 FDDA의 전압 이득은 두 저항(R1, R2)의 비율에 의해 결정되므로, 두 저항(R1, R2) 중 어느 하나를 가변 시킴으로써 신호의 증폭률을 조절할 수 있다. 한편, 통상의 기술자에게 이해되는 바와 같이, FDDA가 반전 증폭 회로를 형성하는 경우에도 두 저항(R1, R2) 중 어느 하나를 가변시켜 신호의 증폭률을 조절할 수 있다.

[0043]

전술한 바와 같이, 본 발명의 일 실시예에 따른 신호 처리 회로(20)는 아날로그 신호 처리에 필요한 세 가지 기능을 모두 포함한다. 회로가 통합됨으로써, 전기적 잡음을 최소화하고, 전류 소모를 감소시킬 수 있으며, 면적 감소되어 제조 비용을 절감할 수 있다.

[0044]

이상에서 본 발명의 바람직한 실시예에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고, 다음의 청구범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 통상의 기술자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것으로 이해되어야 한다.

#### 부호의 설명

[0045]

10: 마이크로폰

20: 마이크로폰의 아날로그 신호 처리 회로

210: 바이어스 회로부

220: 완전 차동 회로부

## 도면

# 도면1

# 도면2