## (10) **DE 10 2004 053 393 B4** 2007.01.11

(12)

# **Patentschrift**

(21) Aktenzeichen: 10 2004 053 393.8

(22) Anmeldetag: 05.11.2004 (43) Offenlegungstag: 11.05.2006

(45) Veröffentlichungstag

der Patenterteilung: 11.01.2007

(51) Int Cl.8: **H01L 21/331** (2006.01)

H01L 29/737 (2006.01) H01L 29/732 (2006.01) H01L 21/8222 (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

#### (73) Patentinhaber:

ATMEL Germany GmbH, 74072 Heilbronn, DE

(72) Erfinder:

Bromberger, Christoph, 74074 Heilbronn, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

DE 198 45 790 A1

DE 102 54 663 A1

DE 43 01 333 A1

DF 693 15 813 T2

US 64 65 317 B2

US2004/00 14 271 A1

US2002/01 68 829 A1

US 56 68 022 A

US 54 59 084 A

US 47 71 013 A

US 65 18 111 B1

US 62 39 477 B1

11 39 452 A2 EP 02 48 606 A2

JP 05-2 75 437 A

IEEE-IEDM 2002. Artikel 31.6.1:

IEEE-IDEM 2003, Technical Digest, Artikel 5.3.1;

### (54) Bezeichnung: Verfahren zur Herstellung einer vertikal integrierten Kaskodenstruktur und vertikal integrierte Kaskodenstruktur

- (57) Hauptanspruch: Verfahren zur Herstellung einer vertikal integrierten Kaskodenstruktur, wobei

- ein erster Basisbereich (10) und ein zweiter (1) Basisbereich ausgebildet wird,

- zwischen dem ersten Basisbereich (10) und dem zweiten Basisbereich (1) ein Zwischenbasisbereich (900) ausgebildet wird,

- eine an den ersten Basisbereich (10) angrenzende Anschlussschicht (20) aufgebracht wird, die aus einem Silizidmaterial ausgebildet ist, das mit zumindest einem Fremdstoff versetzt ist, welcher in einem an das Silizidmaterial angrenzenden Halbleitermaterial (901, 10, 91, 9') als Dotierstoff wirken, kann, und die als Diffusionsquelle zur Dotierung eines an die Anschlussschicht (20) angrenzenden Halbleiterbereichs (901, 10, 91, 9') dient,

- an den ersten Basisbereich (10) angrenzend ein Kollektorbereich (91, 9') ausgebildet wird,

- der zweite Basisbereich (1) aus einem ersten Halbleitermaterial aufgebracht wird,

- oberhalb des zweiten Basisbereichs (1) eine Silizidschicht (2) aufgebracht wird,

- nach dem Aufbringen der Silizidschicht (2) in der Silizid-

schicht (2) eine...

FP

### **Beschreibung**

**[0001]** Die vorliegende Erfindung betrifft ein Verfahren zur Herstellung einer vertikal integrierten Kaskodenstruktur und eine vertikalintegrierte Kaskodenstruktur.

#### Stand der Technik

[0002] In der DE 43 01 333 A1 werden verschiedene Prozessschritte beim Herstellungsverfahren eines NPN-Silizium-Germanium-Heterobipolartransistors mit einer P-Silizium-Gernianium Basisschicht offenbart. Auf diese Schrift wird vollumfänglich Bezug genommen und die Prozessschritte in den Fig. 1a bis 1i erläutert.

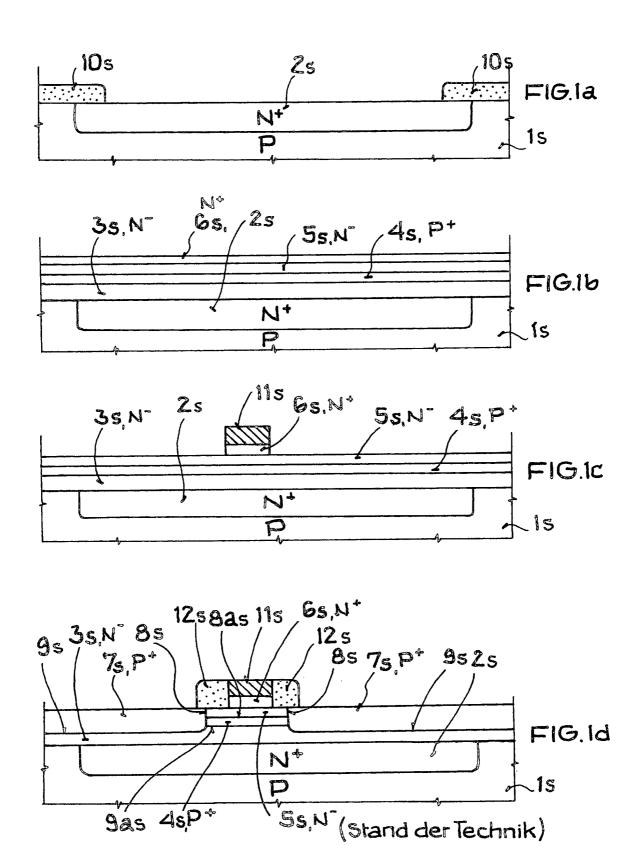

**[0003]** Fig. 1a: Auf der Oberfläche einer P-dotierten Silizium-Substratscheibe **1s** wird durch thermische Oxidation eine (Maskier-) Oxidschicht **10s** gebildet und unter Verwendung von Fotolack strukturiert; eine N<sup>+</sup>-Kollektoranschlussschicht **2s** ("burried layer") wird durch Implantation und Nachdiffusion von Arsen-lonen gebildet.

[0004] Fig. 1b: Nach Entfernen der Maskier-Oxidschicht 10s wird die Schichtenfolge des SiGe-HBTs in einem einzigen Prozess (beispielsweise mittels Molekularstrahlepitaxie MBE) ohne Unterbrechung bei gleichzeitiger Dotierung der Schichten gewachsen. Die Schichtenfolge umfasst die N-Kollektorschicht 3s (bspw. mit einer Schichtdicke 300 nm und einer Dotierungskonzentration von 10<sup>16</sup> bis 10<sup>17</sup> cm<sup>-3</sup>), die P<sup>+</sup>-SiGe-Basisschicht **4s** (Germaniumanteil beispielsweise 20%, Schichtdicke 50 nm und Dotierungskonzentration 10<sup>19</sup> cm<sup>-3</sup>), die N<sup>-</sup>-Emitterschicht 5s (bspw. mit einer Schichtdicke von 100 nm und einer Dotierungskonzentration von 10<sup>18</sup> cm<sup>-3</sup>) sowie die N<sup>+</sup>-Emitteranschlussschicht **6s** bspw. Schichtdicke 50 nm und Dotierungskonzentration größer 10<sup>20</sup> cm<sup>-3</sup>).

**[0005]** Fig. 1c: Auf die N<sup>+</sup>-Emitteranschlussschicht **6s** wird ganzflächig (beispielsweise durch CVD-Verfahren) eine Hilfsschicht **11s** (beispielsweise aus Siliziumnitrid  $Si_3N_4$ ) mit einer Schichtdicke von ca. 0,3 µm abgeschieden und mittels Fotolack strukturiert; ein Teilbereich der  $Si_3N_4$ -Hilfsschicht **11s** und der Si-Emitteranschlussschicht **6s** wird anisotrop abgeätzt – die Emitterschicht **5s** verbleibt weiterhin über der SiGe-Basisschicht **4s**.

[0006] Fig. 1d: Auf die Oberfläche der Halbleiteranordnung wird eine CVD-Oxid (TEOS) 12s (beispielsweise mit einer Schichtdicke von 0,3 µm) konform abgeschieden und derart anisotrop rückgeätzt, dass nur an den senkrechten Kanten der Hilfsschicht 11s und der Emitteranschlussschicht 6s eine Oxidschicht 12s (Spacer) verbleibt und die restliche Oberfläche (für den Basisanschluss) freigelegt wird; in die freiliegende Oberfläche werden BF2-lonen (Dosis beispielsweise 4 × 10<sup>15</sup> cm<sup>-2</sup>, Beschleunigungsspannung beispielsweise 40–80 kV) bis in eine Tiefe knapp unterhalb der SiGe-Basisschicht **4s** implantiert und dadurch das seitlich der Oxidspacer **12s** liegende Emittergebiet **5s** zum P<sup>+</sup>-Basisanschlussgebiet **7s** umdotiert sowie der Basis-Kollektor-PN-Übergang **9s** unter die Basis-Kollektor-Grenzschicht **9as** und der Emitter-Basis-PN-Übergang **8s** unter die Spacer-Oxidschicht **12s** verschoben.

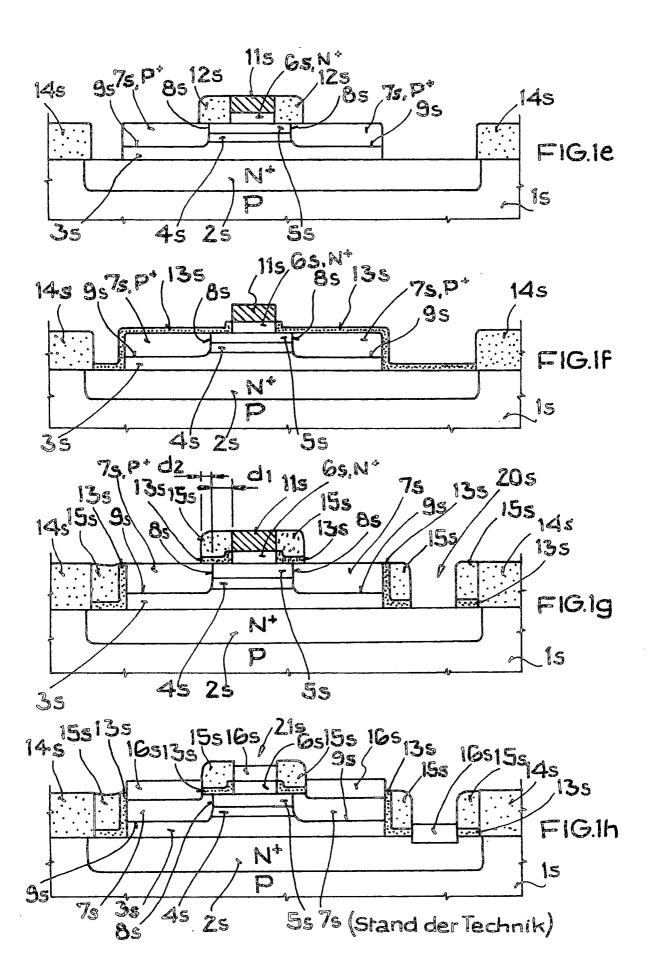

[0007] Fig. 1e: Die endgültige Mesastruktur wird herausgebildet, indem Basisanschlussgebiet 7s und Kollektorschicht 3s durch anisotropes Ätzen strukturiert werden; durch Abscheidung und Strukturierung eines CVD-Oxids (Schichtdicke beispielsweise 0,5 µm) werden Feldoxidgebiete 14s gebildet, die die einzelnen Bauelemente bzw. aktiven Strukturen der integrierten Schaltung voneinander separieren.

[0008] Fig. 1f: Durch thermische Oxidation bei einer Temperatur von beispielsweise 700°C wird die freiliegende Oberfläche der Halbleiteranordnung mit einer beispielsweise 10 nm dicken SiO<sub>2</sub>-Schicht 13s überzogen. Sowohl der Basis-Emitter-PN-Übergang 8s als auch der Kollektor-Basis-PN-Übergang 9s werden an der Oberfläche passiviert und somit vor Leckströmen geschützt.

[0009] Fig. 1g: Auf die Oberfläche der Halbleiteranordnung wird ganzflächig ein CVD-Oxid 15s (TEOS) abgeschieden (bspw. mit einer Schichtdicke von 0,5  $\mu$ m) und derart anisotrop rückgeätzt, dass zum einen die Kollektor-Kontaktöffnung 20s gebildet wird und zum anderen Oxidspacer 15s verbleiben, die die Oberfläche des Basis-Emitter-PN-Übergangs 8s über eine Länge  $d_2$  schützen. Die Abstände  $d_1$  (vom Rand der Emitteranschlussschicht 6s bis zum Basisanschlussgebiet 7s) und  $d_2$  (vom Basisanschlussgebiet 7s bis zum späteren Basis-Metall 16s) werden durch die beschriebene Spacertechnik unter Verwendung der Oxidschichten 12s und 15s selbstjustiert und minimal.

[0010] Fig. 1h: Der restliche Teil der Si<sub>3</sub>N<sub>4</sub>-Hilfsschicht 11s wird entfernt und die Emitter-Kontaktöffnung 21s freigelegt. Durch Aufdampfen einer Metallschicht 16s (beispielsweise Titan) und deren Temperaturbehandlung wird auf der Oberfläche der Silizium-Bereiche 2s, 6s, 7s ein Metall-Silizid (Bsp. Titan-Silizid) gebildet, während auf der Oberfläche der Oxidbereiche 13s, 14s, 15s das reine Metall verbleibt; die Metallschicht über den Oxidbereichen 13s, 14s, 15s wird mittels einer Ätzlösung selektiv entfernt. Anschließend kann nach Aufbringen einer Oxidschicht und Herstellung von Kontaktöffnungen für Emitter, Basis und Kollektor eine Metallisierung mittels üblicher Verfahren aufgebracht werden. Derartige SiGe-HBTs der Fig. 1h können jedoch nicht nur, wie dargestellt, auf einfach strukturierten Substraten gefertigt werden, sondern beispielsweise auch auf Substraten, die bereits fertige Bauelemente in reiner Silizium-Technologie (bspw. MOS oder Bipolar) enthalten.

[0011] Die Basis des zuvor beschriebenen Transistors lässt sich gedanklich in eine innere Basis und eine äußere Basis gliedern. Die innere Basis bildet mit angrenzenden Emitter- und Kollektorgebieten ebene und im Wesentlichen parallele pn-Übergänge aus, während die äußere Basis zur elektrischen Verbindung der inneren Basis mit zumindest einem äußeren Kontakt ausgebildet ist.

**[0012]** Für viele Anwendungen von Bipolartransistoren, so beispielsweise für die Hochfrequenz-Leistungsverstärkung, ist der Basiswiderstand ein wichtiger Parameter, der die elektrischen Eigenschaften der Transistoren, insbesondere deren Grenzfrequenz begrenzt. Häufig wird der Basiswiderstand vom Widerstand der äußeren Basis dominiert.

[0013] Um den Widerstand der äußeren Basis zu reduzieren, ist die äußere Basis in hochdotiertem Halbleitermaterial vom selben Dotierstofftyp wie dem der inneren Basis ausgeführt, jedoch mit einer erheblich höheren Schichtdicke, um so einen niedrigen Schichtwiderstand zu erzielen. Bei dem in der Druckschrift "IEEE-IEDM 2002, Artikel 31.6.1" gelehrten Verfahren wird beispielsweise die äußere Basis in Polysilizium einer Schichtdicke ausgeführt, die erheblich über der Weite der inneren Basis liegt. Zudem kann die äußere Basis als hochdotierter implantierter Bereich ausgeführt sein.

[0014] Um den Widerstand der äußeren Basis von Bipolartransistoren der Siliziumtechnologie zu reduzieren, wird die äußere Basis silizidiert wie dies bspw. in den Druckschriften US 5,459,084 A US 2002/0168829 A1 oder US 6,465,31 B2 ausgeführt ist. Hierbei wird auf die äußere Basis eine Schicht aus einem mit Silizium reaktionsfähigen Metall aufgebracht und dieses mit dem Siliziummaterial der äußeren Basis zur Reaktion gebracht. Durch ein Tempern oberhalb einer Umwandlungstemperatur werden die entstehenden Silizide in eine Modifikation mit einem geringen spezifischen Widerstand überführt.

[0015] Für viele Anwendungen, insbesondere im Hochfrequenzbereich, ist es wünschenswert, neben Silizium ein weiteres Halbleitermaterial, beispielsweise Germanium oder Kohlenstoff, in die innere Basis eines Bipolartransistors einzubringen, um einen Heterobipolartransistor herzustellen. Bei der epitaktischen Abscheidung des Halbleitermaterials für die innere Basis wird auch in Teile der äußeren Basis neben Silizium das weitere Halbleitermaterial eingebracht. Germanium und Kohlenstoff verhalten sich chemisch ähnlich wie Silizium, so dass ein mit Silizium reaktionsfähiges Metall unter den selben Reakti-

onsbedingungen auch mit Germanium oder Kohlenstoff reagiert.

[0016] Insbesondere Verbindungen zwischen Titan und Germanium weisen eine geringere thermische Stabilität auf als homologe Verbindungen zwischen Titan und Silizium und dissoziieren bei der Umwandlungstemperatur der Silizide. Die bei der Dissoziierung gebildeten Germanium- und Titan-Ausscheidungen wirken widerstandserhöhend.

**[0017]** Bei Vorhandensein eines weiteren Halbleitermaterials (Germanium) in der inneren Basis kann es daher wünschenswert sein, die Silizidierungsreaktion so zu führen, dass die Silizidierungsfront nicht bis in die Tiefe der inneren Basis vordringt. Dennoch ist zur Verringerung des Basiswiderstandes eine hohe Siliziddicke wünschenswert.

[0018] Hierzu ist, wie zuvor in der DE 43 01 333 A1 beschrieben, eine dicke Emitterschicht 5s vorgesehen, die dazu dient, Siliziummaterial für eine dicke Silizidschicht 16s vorzuhalten, ohne dass die Silizidierungsfront bis in die Tiefe der Schicht 4s aus Silizium-Germanium-Mischmaterial vordringt. Am Rand des dicken Emittergebietes wird ein relativ großflächiger pn-Übergang ausgebildet, wobei der pn-Übergang vollständig im Silizium liegt. Der Basis-Emitter-Diode des Heterobipolartransistors ist eine relativ großflächige Silizium-Diode parallel geschaltet. Diese beeinflusst die elektrischen Eigenschaften des entstehenden Bauelementes und begrenzt dessen geometrische Skalierbarkeit.

[0019] Aus der DE 198 45 790 A1 ist ein Herstellungsverfahren für SiGe-Heterobipolartransistoren unter Vermeidung großflächiger Silizium-Randtransistoren bekannt, indem zur nasschemischen Abdünnung von Siliziumschichten im aktiven Emittergebiet eines Bipolartransistors, eine zusätzlich mittels "Atomic Layer Doping" (ALD) in eine Deckelschicht eingebrachte Dotierung mit einer Dicke kleiner 3 nm als Ätzstoppschicht für nasschemische Ätzmittel wirkt. Nachfolgend wird die Ätzstoppschicht mit einem nasschemischen Ätzmittel entfernt wird.

[0020] Das Schichtwachstum der Deckelschicht erfolgt über der Ätzstoppschicht weiter einkristallin, so dass mit Hilfe eines Silizium-Ätzmittels, das einkristalline Silizium der Deckelschicht hochselektiv zur Ätzstoppschicht und zu einem Dielektrikum entfernt werden kann. In einer Ausführungsform des Verfahrens der DE 198 45 790 A1 wird die epitaktische Abscheidung der dicken Emitterschicht unterbrochen durch Aufbringen der dünnen Ätzstopschicht, beispielsweise aus hoch-p-dotiertem Silizium, die als Ätzstop bei einer selektiven, nasschemischen Dünnung der dicken Emitterschicht zur Eintiefung des Emitterfensters, am Ort des Emitterfensters dient.

## DE 10 2004 053 393 B4 2007.01.11

[0021] Aus der Druckschrift "IEEE IEDM 2003, Technical Digest, Artikel 5.3.1" ist ebenfalls ein Herstellungsverfahren unter Vermeidung relativ großflächiger Randtransistoren bekannt, indem auf der äußeren Basis eine hohe Siliziddicke erzielt wird, während gleichzeitig die Silizidierungsfront oberhalb der Germanium enthaltenden Schicht zum Stehen gebracht wird. Hierzu wird das Siliziummaterial nach Fertigstellung des Emitteranschlusses ausschließlich oberhalb der äußeren Basis durch selektive Epitaxie abgeschieden und anschließend silizidiert.

**[0022]** Es besteht die Gefahr der Bildung nadelförmiger oder pyramidaler Silizid-Kristallite, welche in das Siliziumgebiet hineinragen. Zur Vermeidung eines Kurzschlusses ("spike") zwischen der Silizidschicht auf der äußeren Basis und dem Emittergebiet muss hiernach ein ausreichender lateraler Abstand zwischen der Silizidkante und der Emitterkante vorgesehen werden. Hierdurch wird der Bahnwiderstand der äußeren Basis erhöht.

[0023] Insbesondere bei den in den Schriften US 6,518,111 B1 und US 6,239,477 B1 gelehrten Verfahren wird versucht, den Basis-Bahnwiderstandsanteil aufgrund des nicht silizidierten Bereiches der äußeren Basis zu reduzieren. Hierbei wird zwischen dem Emitterfenster und der äußeren Basis ein großer Mindestabstand gewahrt, um Basis-Emitterkurzschlüsse durch seitlich wachsende Silizidkristalle, so genannte Spikes zu verhindern. Zur Reduktion des Widerstandes wird der Bereich der äußeren Basis, der zwischen dem Silizid und der inneren Basis gelegen ist, durch Dotanden aus einer Feststoff-Dotierstoffquelle möglichst hoch dotiert, ohne die Eigenschaften des Basis-Emitter-PN-Übergangs zu beeinträchtigen.

[0024] Als Dotierstoffquelle sieht die US 6,518,111 B1 eine dielektrische Schicht (Bor-Silikat-Glas) als Diffusionsquelle zur Verringerung des Schichtwiderstandes des Verbindungsbereichs zwischen der inneren Basis und einer äußeren Basis aus Polysilizium vor, während die US 6,239,477 B1 eine Dotierung zwischen den inneren Basis und einer silizidierten äußeren Basis vorsieht. In der US 2004/0014271 A1 ist als Feststoffquelle eine selektiv epitaktisch abgeschiedene hochdotierte Siliziumschicht vorgesehen.

**[0025]** Aus der JP 05275437 A ist ein Bipolartransistor bekannt. Auf einer Basisschicht werden eine nicht-dotierte Halbleiterschicht und eine Silizidschicht aufgebracht. Auf der Silizidschicht wird eine Isolatorschicht aufgebracht. Eine Öffnung wird durch die Isolatorschicht und durch die Silizidschicht eingebracht, die die Halbleiterschicht erreicht. Nachfolgend wird durch die Öffnung eine Emitterschicht ausgebildet.

**[0026]** In der US 5,668,022 A ist eine Herstellung eines Silizium/Silizium-Germanium-Bipolartransistors bekannt. Als Elektrode ist eine Silizidschicht auf eine

Nitridschicht aufgebracht, die eine äußere Basis bedeckt. In die Silizidschicht und in die Nitridschicht werden zwei Öffnungen geätzt und die Silizidschicht und die die Basisschicht durch dotiertes Polysilizium miteinander verbunden.

**[0027]** Aus der DE 102 54 663 A1 ist ein Transistor mit niederohmigem Basisanschluss bekannt. Der Bereich des extrinsischen Basis wird durch höhere Dotierung niederohmig gestaltet. Dies erfolgt durch Ausdiffusion von Ladungsträgern aus einer Dotierstoffquellschicht, insbesondere einer Polysiliziumschicht, die im Bereich der extrinsischen Basis unterhalb der epitaktisch aufgewachsenen Basisschicht angeordnet wird.

[0028] Aus der DE 693 15 813 T2 ist eine Kaskodenschaltungsstruktur mit bipolarem Epitoxial-Transistoren und niedrig gelegenem Basisanschluss bekannt. Die Kaskodenschaltungsstruktur ist in Form einer Mesa-Struktur ausgebildet. Aus der EP 0 248 606 A2 ist hingegen ein Submikrometer-Bipolartransistor mit einer vergrabenen Silizidregion bekannt. Die Silizidregion ist elektrisch parallel mit einer konventionellen hoch-dotierten Polysilizium-Basisregion angeordnet.

**[0029]** Die US 4,771,013 A offenbart ein Halbleiterbauelement mit gestapelten Schichtstrukturen, die durch Silizidschichten voneinander getrennt sind. Die Schichten bilden dabei Bipolartransistoren mit Hetero-Übergängen aus. Hingegen ist aus der EP 1 139 452 A2 eine Triode mit Hetero-Übergängen bekannt.

### Aufgabenstellung

**[0030]** Der Erfindung liegt die Aufgabe zu Grunde den Basiswiderstand in einer Kaskodenstruktur möglichst zu reduzieren, wobei die Nachteile großer lateraler Ausdehnung und Einflüsse parasitäre Randtransistoren, die zwischen Anschlussgebieten entstehen können, möglichst reduziert werden.

**[0031]** Diese Aufgabe wird durch ein Verfahren mit den Merkmalen des Anspruchs 1 oder durch eine Hochfrequenz-Kaskodenstruktur mit den Merkmalen des Anspruchs 12 gelöst. Weiterbildungen der Erfindung sind Gegenstand von Unteransprüchen.

**[0032]** Demzufolge ist ein Verfahren zur Herstellung einer vertikal integrierten Kaskodenstruktur vorgesehen. Dabei werden ein erster Basisbereich und ein zweiter Basisbereich ausgebildet. Die beiden Basisbereiche werden bevorzugt von einander getrennt angeschlossen und sind vorteilhafterweise getrennt durch unterschiedliche Basisströme steuerbar.

[0033] Zwischen dem ersten Basisbereich und dem zweiten Basisbereich wird ein Zwischenbasisbereich ausgebildet, der vorzugsweise monokristallines

Halbleitermaterial aufweist, das an beide Basisbereiche grenzt. An den ersten Basisbereich angrenzend wird ein Kollektorbereich ausgebildet. Vorzugsweise wird der zweite Basisbereich aus einem ersten Halbleitermaterial, beispielsweise Si oder SiGe aufgebracht.

[0034] Oberhalb des zweiten Basisbereichs wird eine Silizidschicht aufgebracht. Nach dem Aufbringen der Silizidschicht wird in der Silizidschicht eine Öffnung erzeugt, indem die Silizidschicht im Bereich der Öffnung entfernt wird. Nachfolgend wird innerhalb der Öffnung ein an den zweiten Basisbereich angrenzender Emitterbereich ausgebildet.

[0035] Es wird eine Anschlussschicht aufgebracht, die an den ersten Basisbereich grenzt. Die Anschlussschicht ist dabei aus einem Silizidmaterial gebildet, das mit zumindest einem Fremdstoff, vorzugsweise einem Material der Gruppe 3A des Periodensystems (Bor, etc.), versetzt ist, das in einem angrenzenden Halbleitermaterial als Dotierstoff wirkt, so dass die Anschlussschicht als Dotierstoff-Diffusionsquelle für angrenzende Halbleiterbereiche dient.

**[0036]** In einer Weiterbildung der Erfindung wird die Anschlussschicht durch Aufbringen eines ersten Dielektrikums von dem Kollektorbereich und/oder durch Aufbringen eines zweiten Dielektrikums vom Zwischenbasisbereich isoliert. Ein derartiges Dielektrikum ist beispielsweise  $SiO_2$  oder  $Si_3N_4$ .

[0037] Die Erfindung vorteilhaft weiterbildend ist vorgesehen, dass zumindest in der Anschlussschicht ein Basisfenster geöffnet wird, in das eine oder mehrere monokristalline Halbleiterschichten des ersten Basisbereichs selektiv epitaktisch abgeschieden werden. Vorteilhafterweise wird eine der monokristallinen Halbleiterschichten aus einem Mischkristall, beispielsweise SiGe gebildet.

[0038] Eine andere bevorzugte Weiterbildung der Erfindung sieht vor, dass zur Ausbildung des Zwischenbasisbereichs auf dem zweiten Dielektrikum und auf der offenliegenden Halbleiterschicht des ersten Basisbereichs zumindest ein Teil des Halbleitermaterials der Zwischenbasisschicht amorph abgeschieden und durch Festphasenepitaxie ausgehend von der offenliegenden Halbleiterschicht des ersten Basisbereichs als Kristallisationskeim kristallisiert wird.

[0039] Um die Erfindung weiter vorteilhaft auszugestalten ist vorgesehen, dass die Anschlussschicht aus abgeschiedenem oder durch Silizidierung hergestellten bordotiertem Kobaldsilizid gebildet wird. Hierzu wird in einer ersten Ausgestaltungsvariante der Erfindung die Anschlussschicht aus abgeschiedenem in-situ bordotiertem Kobaltsilizid gebildet, während in einer zweiten Ausgestaltungsvariante die An-

schlussschicht aus vermittels Implantation bordotiertem Kobaltsilizid gebildet wird. Vorteilhafterweise wird nach dem Abscheiden der Anschlussschicht ein Temperschritt durchgeführt. Ein weiterer Aspekt der Erfindung ist eine vertikal integrierte Hochfrequenz-Kaskodenstruktur. Diese kann vorteilhafterweise mittels des zuvor erläuterten Verfahrens hergestellt werden.

**[0040]** Die Hochfrequenzanordnung weist einen aus einem Halbleitermaterial bestehenden ersten Basisbereich und einem zweiten Basisbereich auf. Zwischen dem ersten Basisbereich und dem zweiten Basisbereich ist ein Zwischenbasisbereich aus einem Halbleitermaterial angeordnet. Zudem sind ein an den ersten Basisbereich angrenzenden Kollektorbereich und ein an den zweiten Basisbereich angrenzenden Emitterbereich vorgesehen.

[0041] Weiterhin weist die Hochfrequenzanordnung einen Anschlussbereich auf, der zum elektrischen Anschluss an den ersten Basisbereich angrenzt und durch ein Dielektrikum vom Zwischenbasisbereich isoliert ist. Dabei ist der erste Basisbereich in einer Anschlussbereichsöffnung durch selektive Epitaxie als monokristallines Halbleitermaterial ausgebildet. Der Emitterbereich ist in eine Öffnung eingebracht ist, die in eine zum elektrischen Anschluss des zweiten Basisbereichs ausgebildete Silizidschicht geätzt ist.

[0042] In einer vorteilhaften Weiterbildung des Verfahrens zur Herstellung ist vorgehen, indem der zweite Basisbereich aus einem ersten Halbleitermaterial und oberhalb des zweiten Basisbereichs eine Silizidschicht aufgebracht wird. Die Silizidschicht dient dabei vorzugsweise einem elektrischen Anschluss des zweiten Basisbereichs. Für eine gute elektrische Leitfähigkeit wird die Silizidschicht entweder an den zweiten Basisbereich angrenzend oder auf eine dünne Zwischenschicht (cap-layer) aus einem Halbleitermaterial aufgebracht.

**[0043]** Im Weiteren wird dieser zweite Basisbereich zu Weiterbildungen der Erfindung näher erläutert. Nach dem Aufbringen der Silizidschicht wird in der Silizidschicht eine Öffnung erzeugt, indem die Silizidschicht im Bereich der Öffnung entfernt wird. Demzufolge wird in dieser Öffnung jegliches Silizid entfernt, so dass zumindest eine Oberfläche des unterhalb der Silizidschicht befindlichen monokristallinen Halbleitermaterials freigelegt wird.

**[0044]** Nachfolgend wird innerhalb der Öffnung ein Emitterbereich ausgebildet. Der Emitterbereich ist dabei vorzugsweise derart ausgebildet, dass der Emitterbereich und der Basisbereich einen PN-Übergang bilden der innerhalb eines monokristallinen Bereichs des Halbleitermaterials ausgebildet ist.

[0045] Eine besonders vorteilhafte Weiterbildung

der Erfindung sieht vor, dass zwischen dem zweiten Basisbereich und der Silizidschicht eine erste Halbleiterschicht eingefügt wird, indem die erste Halbleiterschicht vor dem Aufbringen der Silizidschicht auf eine erste Oberfläche des Basisbereichs aufgebracht wird. Diese Halbleiterschicht weist vorzugsweise eine gegenüber dem Basisbereich um zumindest eine Größenordnung geringere Dotierstoffkonzentration auf. Beispielsweise ist der Leitungstyp der Dotierstoffe in dieser ersten Halbleiterschicht vom selben Typ des Basisbereichs. Vorteilhafterweise weist die erste Halbleiterschicht eine Dicke kleiner 20 nm auf.

[0046] In einer anderen, auch kombinierbaren Weiterbildung der Erfindung ist vorgesehen zwischen der Silizidschicht und der ersten Halbleiterschicht eine zweite Halbleiterschicht einzubringen. Vorzugsweise wird diese zweite Halbleiterschicht in Folge der Erzeugung der Öffnung für den Emitterbereich mit entfernt. Die zweite Halbleiterschicht wird dabei eingebracht, indem die zweite Halbleiterschicht vor dem Aufbringen der Silizidschicht auf eine (zweite) Oberfläche der ersten Halbleiterschicht aufgebracht wird. Dabei weist die zweite Halbleiterschicht gegenüber der ersten Halbleiterschicht vorzugsweise eine höhere Dotierstoffkonzentration auf. Vorteilhafterweise ist die Dotierstoffkonzentration um mindestens eine Größenordnung höher. Die in der zweiten Halbleiterschicht eingebrachten Dotanden sind dabei vom selben Leitungstyp wie die im Basisbereich enthaltenen Dotanden. Die Dotierstoffe können vorteilhafterweise in situ während des epitaktischen Aufbringens der zweiten Halbleiterschicht eingebracht oder alternativ nachträglich implantiert werden. Vorteilhafterweise weist die zweite Halbleiterschicht eine Dicke kleiner 20 nm auf.

[0047] Eine vorteilhafte Ausgestaltung der Erfindung sieht vor, dass die Öffnung mit einer Tiefe zumindest bis zur zweiten Oberfläche der ersten Halbleiterschicht oder bis zur ersten Oberfläche der zweiten Basisschicht erzeugt wird. Vorteilhafterweise wird die Öffnung bis zu einer Tiefe ausgebildet, dass oberhalb des Basisbereichs monokristallines Halbleitermaterial verbleibt, das als Teil des Emitterhalbleitergebietes mit dem Einbringen des Emitterbereichs entsprechend dotiert wird und vorteilhafterweise nach der Dotierung einen Leitungstyp aufweist, der dem Leitungstyp des Basisbereichs entgegengesetzt ist.

[0048] In einer ersten Ausgestaltungsvariante der Erfindung ist vorgesehen, dass die Silizidschicht durch eine Maskierung im Bereich der Öffnung zu deren Erzeugung geätzt wird. Vorzugsweise wird für die Ätzung ein Ätzmittel verwendet, dass eine gegenüber dem unten liegenden, monokristallinen Halbleitermaterial selektive Ätzung der Silizidschicht ermöglicht.

**[0049]** Eine zweite, alternative Ausgestaltungsvariante sieht vor, dass die Öffnung durch einen Abhebetechnik-Verfahrensschritt (lift-off) erzeugt wird. Hierzu wird vor dem Aufbringen der Silizidschicht eine Photolackmaske strukturiert und nachfolgend die Silizidschicht durch Sputtern eines Silizidtarget aufgebracht. Nachfolgend wird die strukturierte Photolackmaske entfernt, so dass die Öffnung in der Silizidschicht gebildet wird.

[0050] Eine vorteilhafte Weiterbildung der Erfindung sieht vor, dass der Emitterbereich innerhalb der Öffnung selbstjustierend ausgebildet wird. Hierzu definieren die Ränder der Öffnung der Silizidschicht die Außenmaße des Emitterbereichs, so dass der Emitterbereich innerhalb der Öffnung symmetrisch ausgebildet wird. Hierzu ist vorteilhafterweise vorgesehen, dass zur Ausbildung des Emitterbereichs innerhalb der Öffnung Innenspacer erzeugt werden, zwischen denen eine Spaceröffnung ausgebildet wird und anschließend eine leitfähige Schicht oder Schichtfolge aufgebracht wird. Die Innenspacer dienen zur Positionierung des aktiven Emitterhalbleitergebietes unterhalb der Spaceröffnung. Weiterhin dienen die Innenspacer und gegebenenfalls ein weiteres Dielektrikum der Isolation des Emitteranschlusses von der Silizidschicht und/oder des Basisbereichs. Demzufolge wird durch die Innenspacer das Gebiet der inneren Basis festgelegt. Die äußere Basis reicht dabei von der inneren Basis bis unter die Silizidschicht, wobei das Halbleitergebiet des Basisbereichs der äußeren Basis zumindest zum größten Teil durch die Silizidschicht zur Anschlusskontaktierung bedeckt ist.

[0051] Um den Emitterbereich möglichst niederohmig zu kontaktieren, ist in einer vorteilhaften Weiterbildung der Erfindung vorgesehen, dass in die leitfähige Schicht oder Schichtfolge ein einem ersten Leitungstyp des Emitterbereichs entsprechender Dotierstoff eingebracht wird, der in einem Temperschritt in die monokristalline Halbleiterschicht im Bereich der Spaceröffnung eindiffundiert wird, so dass die leitfähige Schicht oder Schichtfolge als Quelle des Dotierstoffs wirkt. Die Eindiffusion ist dabei durch entsprechende Temperatur/Zeit-Wahl vorzugsweise auf einen Bereich unterhalb der Spaceröffnung zwischen den Innenspacern beschränkt.

[0052] Um die Basis möglichst niederohmig zu kontaktieren und um Schottky-Kontakte zu vermeinden ist gemäß einer Weiterbildung der Erfindung vorgesehen, dass in die Silizidschicht und/oder in die zweite Halbleiterschicht ein einem zweiten Leitungstyp des Basisbereichs entsprechender Dotierstoff eingebracht wird. Dieser wird in einem Temperschritt in die erste Halbleiterschicht und/oder in den Basisbereich außerhalb des Bereichs der Öffnung für den Emitterbereich eindiffundiert, so dass die Silizidschicht und/oder die zweite Halbleiterschicht als Quelle des Dotierstoffs wirkt.

**[0053]** Eine Ausgestaltung dieser Weiterbildung der Erfindung sieht vorteilhafterweise vor, dass die leitfähige Schichtfolge aus einer untenliegenden, insbesondere polykristallinen Siliziumschicht des ersten Leitungstyps und einer obenliegenden weiteren Silizidschicht gebildet wird. Dabei ist die polykristalline Siliziumschicht vorzugsweise hoch dotiert.

**[0054]** Die Silizidschicht oder die weitere Silizidschicht wird in einer ersten vorteilhaften Ausgestaltungsvariante der Erfindung aufgebracht, indem zu einer Formierung eine Siliziumschicht und eine oder mehrere Metallschichten, insbesondere ein Titanschicht und/oder eine Kobaltschicht aufgebracht werden und nachfolgend eine Silizidierung erfolgt. Vor und/oder nach der Silizidierung können Dotierstoffe vorzugsweise durch eine entsprechende Maskierung selektiv implantiert werden.

**[0055]** Die Silizidschicht oder die weitere Silizidschicht wird in einer zweiten vorteilhaften Ausgestaltungsvariante der Erfindung aufgebracht, indem ein silizidhaltiges Target gesputtert wird. Dotierstoffe können während des Sputterprozesses in situ eingebracht werden.

[0056] Eine vorteilhafte Weiterbildung der Erfindung sieht vor, dass der zweite Basisbereich zumindest eine Silizium-Germanium-Schicht aufweist, indem während des epitaktischen Aufbringens des Basisbereichs ein Gemisch aus Silizium und Germanium aufgebracht wird. Vorteilhafterweise wird diese Silizium-Germanium-Schicht durch eine Schutzschicht, beispielsweise durch die erste Halbleiterschicht abgedeckt, um eine Reaktion des Germaniums mit einem während der Bildung der Silizidschicht aufgebrachten Metalls zu verhindern.

#### Ausführungsbeispiel

**[0057]** Im Folgenden wird die Erfindung in Ausführungsbeispielen anhand von zeichnerischen Darstellungen näher erläutert. Dabei zeigen

**[0058]** Fig. 1a bis 1i eine schematische Darstellung eines Herstellungsprozesses eines HBTs nach dem Stand der Technik,

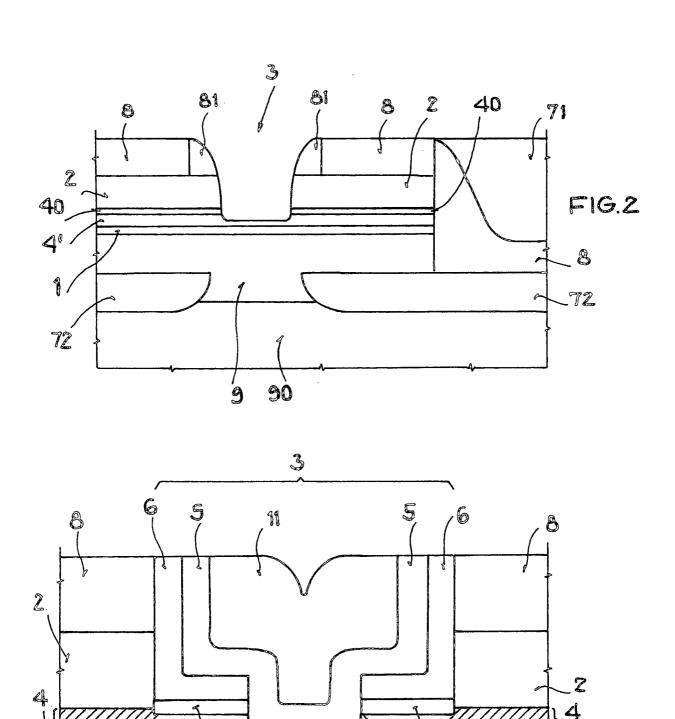

**[0059]** Fig. 2 eine schematische Schnittdarstellung eines Fertigungszustands eines HBTs einer Hochfrequenz-Kaskodenstruktur

**[0060]** Fig. 3 eine schematische Schnittdarstellung eines Ausschnitts eines HBTs einer Hochfrequenz-Kaskodenstruktur, und

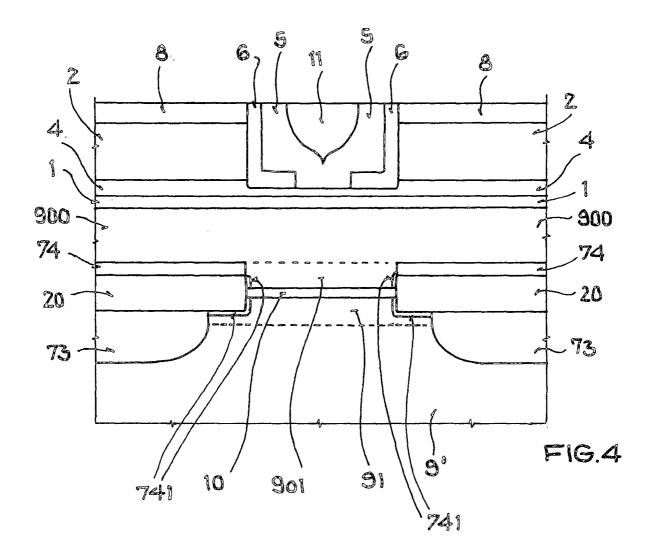

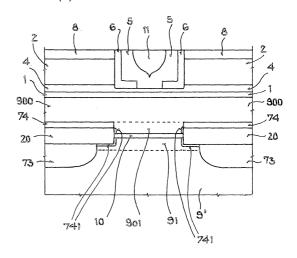

**[0061]** Fig. 4 ein schematische Schnittdarstellung einer erfindungsgemäßen vertikal integrierten Hochfrequenz-Kaskodenstruktur

**[0062]** In einem Beispiel zur Herstellung eines Hochfrequenzbipolartransistors (HBTs) werden die folgenden Fertigungsverfahrensschritte nacheinander durchgeführt. Zur Vereinfachung sind Detailverfahrensschritte, wie die Reinigung von Oberflächen etc. fortgelassen:

- Einbringen einer vergrabenen n<sup>+</sup>-Schicht 90 in einen Siliziumwafer und

- epitaktisches Aufwachsen von 450 nm Silizium

g, 2e16 cm<sup>-3</sup> Asdotiert,

- Ätzen einer flachen STI-Grabenisolation mit Nitrid-Hartmaske und

- Verfüllen mit thermischem und/oder aufgebrachtem Oxid,

- Rückätzen des Oxids mit STI-Inversmaske und

- Oxid-CMP mit Nitrid-Hartmaske als Polierstop,

- Basisepitaxie, mit den Schritten

- 5 nm n<sup>-</sup>-Si-Startschicht,

- 10 nm intrinsische SiGe-Schicht,

- 5 nm p\*-SiGe-Schicht,

- 5 nm intrinsische SiGe-Schicht,

- 10 nm bordotierte p-Si-Schicht 4,

- 10 nm bordotierte p<sup>+</sup>-Si-Capschicht **40** als Diffusionsquelle.

- Sputterabscheidung von 100 nm CoSi, und

- Abscheiden von 200 nm Plasma-Si<sub>3</sub>N<sub>4</sub>,

- Entfernen der Si<sub>3</sub>N<sub>4</sub>-Schicht **8** an den Stellen, an denen ein Emitterfenster vorgesehen ist,

- Abscheiden von 200 nm Plasma-Si₃N₄ und

- Si₃N₄-Rückätzen auf Zeit, nomineller Abtrag 250 nm (Spacerätzen),

- CoSi<sub>2</sub> trocken auf Zeit ätzen, beispielsweise

Cl<sub>2</sub>:O<sub>2</sub>-Plasma mit einer Selektivität von 30:1 zum unterliegenden Silizium mit etwa 2 bis 3 nm Si-Abtrag,

- Si-Softetch mit 5 nm Si-Abtrag.

[0063] Den Fertigungsverfahrenszustand nach diesen Verfahrensschritten zeigt schematisch Fig. 2. Dabei gelten die folgenden Leitungstypen für einen Hochfrequenz-npn-Biplartransistor. Der Kollektorbereich ist durch eine n<sup>+</sup>-dotierte, vergrabene Schicht 90 und durch eine n<sup>-</sup>-Schicht 9 gebildet, wobei diese Schichten 90 und 9 zwischen zwei dielektrischen Schichten 72 aneinander grenzen und in diesem Bereich das Kristallgitter des Substrats fortsetzten. Auf der n-Schicht 9 ist der Basisbereich 1 angeordnet, der in diesem Ausführungsbeispiel zur vereinfachten Darstellung lediglich aus eine Schicht besteht. Auf dem Basisbereich 1 sind eine erste Halbleiterschicht 4' und eine zweite Halbleiterschicht 40 angeordnet, die im Gegensatz zum Basisbereich 1 kein Germanium aufweisen. Weiterhin ist zur Separierung dieser Hochfrequenzhalbleiteranordnung von Hochfrequenzhalbleiteranordnungen ein Dielektrikum aus einer Si<sub>3</sub>N<sub>4</sub>-Schicht 8 und einer SiO<sub>2</sub>-Schicht **71** vorgesehen.

[0064] Oberhalb der zweiten Halbleiterschicht 40 und somit auch oberhalb des Basisbereichs 1 ist eine

Silizidschicht **2** angeordnet, in die mittels der Hartmaske aus der  $\mathrm{Si_3N_4}$ -Schicht **8** und den Spacern **81** eine Öffnung **3** geätzt ist, wobei innerhalb dieser Öffnung in nachfolgenden Schritten der Emitterbereich ausgebildet wird.

**[0065]** In der <u>Fig. 3</u> ist in einem weiteren Beispiel eine Schnittansicht durch den Basis-Emitterbereich eines npn-Hochfrequenzbipolartransistors schematisch dargestellt. Analog zu <u>Fig. 2</u> bildet die Schicht **9** einen Teil eines niedrig n-dotierten Kollektorbereiches, auf dem der p-dotierte Basisbereich **1** angeordnet ist. Oberhalb des Basisbereichs **1** ist lediglich eine Halbleiterschicht **4** angeordnet, oberhalb derer wiederum eine Silizidschicht **2** und eine Hartmaske aus  $Si_3N_4$  (**8**) angeordnet ist. Durch die Silizidschicht **2** hindurch reicht eine Öffnung **3** innerhalb derer der Emitterbereich (**5**, **11**) angeordnet ist.

[0066] Innerhalb der Öffnung 3 sind zwei Innenspacer 6 jeweils oberhalb von einem thermischen Oxid 7 angeordnet. An die Innenspacer 6 angrenzend ist polykristallines, n<sup>†</sup>-(hoch)dotiertes Silizium aufgebracht, das ebenfalls eine Spaceröffnung zwischen den beiden Innenspacern 6 verfüllt. Der verbleibende Teil der Öffnung 3 des Emitterbereichs ist mit einem Silizid 11 und ggf. weiteren (in Fig. 3 nicht dargestellten) metallischen Leitern verfüllt.

[0067] Das Polysilizium 5 dient zudem als Dotierstoffquelle zur Dotierung der monokristallinen Halbleiterschicht 4 im Emitterbereich 45, der hierzu durch Dotanden aus dem Polysilizium 5 hoch n<sup>+</sup>-dotiert ist und das aktive Emittergebiet 45 bildet. Weiterhin wirkt die Silizidschicht 2 als Dotierstoffquelle, wobei die erste Halbleiterschicht 4 im Bereich der äußeren Basis 42 hoch p<sup>+</sup>-dotiert ist. Dies ermöglicht einen besonders niederohmigen Anschluss der äußeren Basis 42, 1.

[0068] Fig. 4 zeigt in Form einer schematischen Schnittdarstellung eine vertikal integrierte Kaskodenstruktur. Die Bezeichnungen 2, 4, 5, 6, 8 und 11 entsprechen dem Beispiel der Fig. 2. Die Fig. 2 zeigt jedoch einen Ausschnitt eines Hochfrequenzbipolartransistors, während Fig. 4 eine schematische Darstellung einer Hochfrequenzkaskodenstruktur zeigt. Demzufolge ist in der Fig. 4 ein erster Basisbereich 10 und ein zweiter Basisbereich 1 vorgesehen. Oberhalb des zweiten Basisbereichs 1 entspricht der Aufbau der vertikal integrierten Kaskodenstruktur dem Bipolartransistor aus Fig. 2.

[0069] Zwischen dem ersten Basisbereich und dem zweiten Basisbereich ist ein Zwischenbasisbereich 900 angeordnet. Dieser Zwischenbasisbereich 900 weist einen dem Leitungstyp der beiden Basisbereiche 1, 10 entgegengesetzten Leitungstyp auf. In diesem Ausführungsbeispiel sind die Basisbereiche 1, 10 p-dotiert, während der Zwischenbasisbereich 900

n-dotiert ist.

[0070] Zum Anschluss des ersten Basisbereichs 10 ist eine Silizidschicht 20 vorgesehen, die durch ein Dielektrikum 73, 74, beispielsweise SiO<sub>2</sub>, von dem Kollektorbereich 9' und dem Zwischenbasisbereich 900 isoliert ist. Zwischen den Silizidbereichen 20 ist monokristallines Halbleitermaterial durch selektive Epitaxie aufgebracht, das einen Schichtstapel aus den Schichten 91, 10 und 901 bildet. Sowohl der erste Basisbereich als auch der zweite Basisbereich weisen einen SiGe-Mischkristall auf.

[0071] Die Silizidschicht 20 ist im Ausführungsbeispiel mit Bor versetzt und dient unter Temperaturbeaufschlagung als Feststoffquelle für die Dotierung der angrenzenden Siliziumbereiche 91, 901. Hierbei bilden sich p-dotierte Randbereiche 741 um die Silizidschicht 20. Es werden auf diese Weise Kurzschlüsse zwischen der Silizidschicht 20 und dem n-dotierten Schichten 9, 91 und 901 vermieden.

**[0072]** Zur Herstellung der vertikal integrierten Kaskodenstruktur aus <u>Fig. 4</u> werden vorzugsweise folgende Fertigungsverfahrensschritte durchgeführt:

- Erzeugen einer einen Kollektorbereich aus der Kollektorschicht 9' bedeckenden Hartmaske auf einer ersten Siliziumoberfläche,

- Selektives Entfernen der nicht von der Hartmaske bedeckten Teile der Kollektorschicht 9',

- Thermisches Oxidieren der nach dem selektivem Entfernen der Kollektorschicht freiliegenden Siliziumoberfläche,

- Abscheiden einer ersten dielektrischen Schicht

73.

- Abtragen des oberhalb der der ersten Siliziumoberfläche abgewandten Oberfläche der Hartmaske liegenden Materials der ersten dielektrischen Schicht 73.

- Entfernen der Hartmaske,

- Aufbringen einer Schichtfolge aus einer Anschlussschicht 20, wobei die Anschlussschicht aus Silizidmaterial ausgeführt ist und mit einem Material der Gruppe 3A des Periodensystems versetzt ist, so dass diese Anschlussschicht 20 als Feststoff-Diffusionsquelle für angrenzende Halbleiterbereiche 10 dient,

- Aufbringen einer zweiten dielektrischen Schicht

74,

- Öffnen eines Basisfensters oberhalb des Kollektorbereichs in der zweiten dielektrischen Schicht

74 und der Anschlussschicht 20,

- Selektives epitaktisches Abscheiden einer ersten monokristallinen Halbleiterschicht 10 oder eines ersten monokristallinen Halbleiterschichtstapels in der Öffnung des Basisfensters, wobei die erste monokristalline Halbleiterschicht 10 eine erste p-dotierten SiGe-Schicht bzw. der Stapel eine SiGe-Schicht aufweist,

- Nicht-selektives Abscheiden einer amorphen,

n-dotierten Siliziumschicht,

– Kristallisation der amorphen, n-dotierten Siliziumschicht durch Festphasenepitaxie zu zumindest einem Teil der Zwischenbasisschicht 900, ausgehend von der ersten monokristallinen Halbleiterschicht 10 oder dem Halbleiterschichtstapel, so dass zumindest Bereiche der Zwischenbasisschicht 900 monokristallin ausgebildet werden.

**[0073]** Für den Bereich oberhalb der Zwischenbasisschicht **900** gelten die Verfahrensschritte zum Bipolartransistor analog.

#### **Patentansprüche**

- 1. Verfahren zur Herstellung einer vertikal integrierten Kaskodenstruktur, wobei

- ein erster Basisbereich (10) und ein zweiter (1) Basisbereich ausgebildet wird,

- zwischen dem ersten Basisbereich (10) und dem zweiten Basisbereich (1) ein Zwischenbasisbereich (900) ausgebildet wird,

- eine an den ersten Basisbereich (10) angrenzende Anschlussschicht (20) aufgebracht wird, die aus einem Silizidmaterial ausgebildet ist, das mit zumindest einem Fremdstoff versetzt ist, welcher in einem an das Silizidmaterial angrenzenden Halbleitermaterial (901, 10, 91, 9') als Dotierstoff wirken, kann, und die als Diffusionsquelle zur Dotierung eines an die Anschlussschicht (20) angrenzenden Halbleiterbereichs (901, 10, 91, 9') dient,

- an den ersten Basisbereich (10) angrenzend ein Kollektorbereich (91, 9') ausgebildet wird,

- der zweite Basisbereich (1) aus einem ersten Halbleitermaterial aufgebracht wird,

- oberhalb des zweiten Basisbereichs (1) eine Silizidschicht (2) aufgebracht wird,

- nach dem Aufbringen der Silizidschicht (2) in der Silizidschicht (2) eine Öffnung (3) erzeugt wird, indem die Silizidschicht (2) im Bereich der Öffnung (3) entfernt wird, und

- nachfolgend innerhalb der Öffnung (3) ein an den zweiten Basisbereich (1) angrenzender Emitterbereich ausgebildet wird.

- 2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass der erste Basisbereich (10), der zweite Basisbereich (1) und/oder der Zwischenbasisbereich (900) als Schichten ausgebildet wird, wobei diese vorzugsweise zueinander horizontale Grenzflächen ausbilden.

- 3. Verfahren nach einem der Ansprüche 1 oder 2, dadurch gekennzeichnet, dass die Anschlussschicht (20) durch Aufbringen eines ersten Dielektrikums (73) von dem Kollektorbereich (9') isoliert wird.

- 4. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die Anschlussschicht (20) durch Aufbringen eines zweiten

Dielektrikums (74) von dem Zwischenbasisbereich (900) isoliert wird.

- 5. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass zumindest in der Anschlussschicht (20) ein Basisfenster geöffnet wird, in das eine oder mehrere monokristalline Halbleiterschichten des ersten Basisbereichs (10) selektiv epitaktisch abgeschieden werden.

- 6. Verfahren nach den Ansprüchen 4 und 5, dadurch gekennzeichnet, dass zur Ausbildung des Zwischenbasisbereichs (900) auf dem zweiten Dielektrikum (74) und auf der offenliegenden Halbleiterschicht des ersten Basisbereichs (1) zumindest ein Teil des Halbleitermaterials der Zwischenbasisschicht (900) amorph abgeschieden und durch Festphasenepitaxie, ausgehend von der offenliegenden Halbleiterschicht des ersten Basisbereichs (1) als Kristallisationskeim, kristallisiert wird.

- 7. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die Anschlussschicht (20) aus abgeschiedenem oder durch Silizidierung hergestellten mit Bor versetztem Kobaldsilizid gebildet wird.

- 8. Verfahren nach Anspruch 7, dadurch gekennzeichnet, dass die Anschlussschicht (20) aus abgeschiedenem in-situ mit Bor versetztem Kobaltsilizid gebildet wird.

- 9. Verfahren nach Anspruch 7, dadurch gekennzeichnet, dass die Anschlussschicht (**20**) aus mittels Implantation bordotiertem Kobaltsilizid gebildet wird.

- 10. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass nach dem Abscheiden der Anschlussschicht (20) ein Temperschritt durchgeführt wird.

- 11. Verfahren nach Anspruch 10, dadurch gekennzeichnet, dass auf die Aufbringung der Anschlussschicht (20) nachfolgende Epitaxie- oder Abscheideschritte als Temperschritte wirken.

- 12. Vertikal integrierte Hochfrequenz-Kaskodenstruktur, mit

- einem ersten Basisbereich (**10**) und einem zweiten Basisbereich (**1**),

- einem zwischen dem ersten Basisbereich (10) und dem zweiten Basisbereich (1) angeordneten Zwischenbasisbereich (900),

- einem an den ersten Basisbereich (10) angrenzenden Kollektorbereich (91, 9'),

- einem an den zweiten Basisbereich (1) angrenzenden Emitterbereich, und

- einem aus einem Silizidmaterial ausgebildeten Anschlussbereich (20), der zum elektrischen Anschluss an den ersten Basisbereich (10) angrenzt und durch

# DE 10 2004 053 393 B4 2007.01.11

ein Dielektrikum (**74**) vom Zwischenbasisbereich (**900**) isoliert ist,

wobei

- der erste Basisbereich (10) in einer Anschlussbereichsöffnung durch selektive Epitaxie als monokristallines Halbleitermaterial ausgebildet ist, und

- der Emitterbereich in eine Öffnung (3) eingebracht ist, die in eine zum elektrischen Anschluss des zweiten Basisbereichs (1) ausgebildete Silizidschicht (2) eingebracht ist.

Es folgen 4 Blatt Zeichnungen

# DE 10 2004 053 393 B4 2007.01.11

## Anhängende Zeichnungen

9

45

42

FIG.3

42