# (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L 21/8247 (2006.01) H01L 27/115

(2006.01)

(21) 출원번호10-2011-0064318(22) 출원일자2011년06월30일심사청구일자2011년06월30일(65) 공개번호10-2013-0007200

(43) 공개일자 **2013년01월18일**

(56) 선행기술조사문헌

KR1020070096972 A KR1020090130180 A KR1020110095676 A (45) 공고일자 2013년04월04일

(11) 등록번호 10-1250851

(24) 등록일자 2013년03월29일

(73) 특허권자

### 서울대학교산학협력단

서울특별시 관악구 관악로 1 (신림동)

(72) 발명자

#### 박병국

서울특별시 서초구 방배동 1015 임광아파트

7-1004

#### 김완동

서울특별시 관악구 남부순환로246라길 3, 302호 (봉천동)

### 김윤

서울특별시 동작구 여의대방로24다길 79 (대방동)

(74) 대리인

권오준

전체 청구항 수 : 총 4 항

심사관 : 구본재

### (54) 발명의 명칭 3차원 적충형 메모리 어레이의 컨택 형성 방법

### (57) 요 약

본 발명은 3차원 적충형 메모리 어레이에서 적충되는 충 수의 증가와 무관하게 계단형 컨택을 한번에 형성할 수 있는 3차원 적충형 메모리 어레이의 컨택 형성 방법이 제공된다.

#### 대 표 도 - 도11

#### 특허청구의 범위

#### 청구항 1

기판 상에 일정한 수직 거리 d로 이격되며 적어도 일 단부가 순차적으로 드러나도록 계단형 돌출부를 갖는 복수 개의 반도체층 사이를 제 1 층간 절연막으로 채우고 평탄화시키는 제 1 단계;

상기 제 1 층간 절연막 상에 제 1 하드 마스크 물질층을 형성하는 제 2 단계;

상기 제 1 하드 마스크 물질층을 식각하여 상기 계단형 돌출부 상에 상기 수직 거리와 동일한 수평 간격 d로 상기 반도체층의 수만큼 복수개의 컨택 홀 패턴을 형성하는 제 3 단계;

상기 기판 전면에 제 2 층간 절연막으로 상기 복수개의 컨택 홀 패턴을 채우며 증착하여 상기 제 1 하드 마스크 물질층 상에 일정 두께로 남아 있도록 하는 제 4 단계;

상기 제 1 하드 마스크 물질층 상에 남아 있는 상기 제 2 층간 절연막을 식각하여 상기 복수개의 반도체층 상에 만 남아 있도록 제 2 층간 절연막 패턴을 형성하는 제 5 단계;

상기 기판 전면에 제 2 하드 마스크 물질층을 증착한 후 일측에 상기 제 2 충간 절연막 패턴이 드러나도록 식각하는 제 6 단계;

상기 제 1, 2 하드 마스크 물질층을 이용하여 드러난 상기 제 2 층간 절연막 패턴을 따라 상기 제 2 층간 절연 막을 등방성으로 식각하여 상기 복수개의 컨택 홀 패턴이 상기 수평 간격 d 만큼 식각 깊이에 차이를 내며 드러나도록 하는 제 7 단계;

상기 제 2 하드 마스크 물질층을 식각하여 상기 복수개의 컨택 홀 패턴이 노출되도록 하는 제 8 단계;

상기 제 1 하드 마스크 물질층을 이용하여 상기 제 1, 2 층간 절연막을 비등방성으로 식각하여 상기 복수개의 반도체층의 계단형 돌출부가 드러나도록 복수개의 컨택 홀을 형성하는 제 9 단계; 및

상기 기판 전면에 도전성 물질로 상기 복수개의 컨택 홀을 채워 복수개의 택 플러그를 한번에 형성하는 제 10 단계를 포함하여 구성된 것을 특징으로 하는 3차원 적충형 메모리 어레이의 컨택 형성 방법.

#### 청구항 2

제 1 항에 있어서.

상기 제 1, 2 층간 절연막은 동일한 물질의 절연막인 것을 특징으로 하는 3차원 적층형 메모리 어레이의 컨택형성 방법.

#### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 제 8 단계는 상기 제 2 층간 절연막이 등방성으로 식각되어 생긴 공간에 컨택 보호층을 채우는 단계;

상기 컨택 보호층이 드러나도록 상기 제 2 하드 마스크 물질층을 식각하는 단계; 및

상기 컨택 보호층을 제거하여 상기 복수개의 컨택 홀 패턴이 노출되도록 하는 단계로 구성된 것을 특징으로 하는 3차원 적층형 메모리 어레이의 컨택 형성 방법.

#### 청구항 4

제 3 항에 있어서,

상기 제 1, 2 층간 절연막은 산화막이고,

상기 제 1, 2 하드 마스크 물질층은 질화막층이고,

상기 컨택 보호층은 실리콘계 물질, 실리콘게르마늄(SiGe) 및 감광막(PR) 중 어느 하나의 물질인 것을 특징으로 하는 3차원 적층형 메모리 어레이의 컨택 형성 방법.

#### 명 세 서

#### 기술분야

[0001] 본 발명은 메모리 어레이의 제조방법에 관한 것으로, 더욱 상세하게는 3차원 적충형 메모리 어레이의 컨택 형성 방법에 관한 것이다.

#### 배경기술

- [0002] 고집적의 대용량 저장 소자로서 플래시 메모리의 활용도가 높아지는 반면에, 평면 구조에서 20nm 이하로는 포토 -리쏘그래피(photo-lithography) 기술의 한계로 집적도 향상이 어려워짐에 따라 3차원 적층형 플래시 메모리 어레이가 다양하게 고안되고 있다.

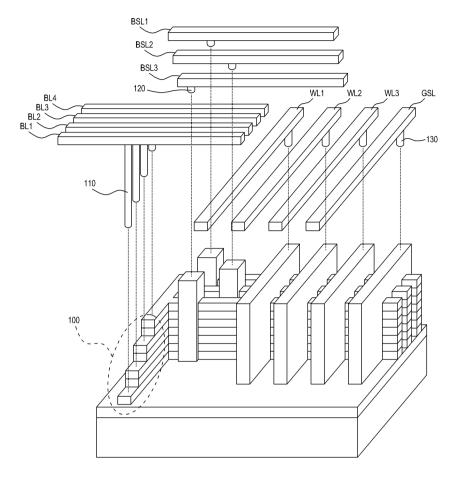

- [0003] 이러한 3차원 적충형 플래시 메모리 어레이 구조에서는, 도 1과 같이, 각 충의 전기적 신호를 주기 위한 계단형 컨택(stair-like contact) 부위(100)와 상기 부위에 연결되는 계단형 컨택 플러그(110) 형성 공정이 필수적으로 요구된다.

- [0004] 그런데, 상기 계단형 컨택 플러그 형성 공정은 각 층의 컨택 깊이가 다르기 때문에 N층의 컨택 플러그를 형성하기 위해서는 N번의 포토-리쏘그래피 공정과 N번의 식각 공정을 반복 수행해야 하므로, 층수가 증가할수록 공정 비용(cost)도 증가하게 되는 문제점이 제기되어 왔다. 특히, 3차원 적충형 낸드 플래시 메모리 어레이 구조에서 8층, 16층, 32층 등 적층의 수가 기하급수적으로 증가하게 되면 이러한 문제점은 더욱 분명해 진다.

- [0005] 따라서, 3차원 적층형 낸드 플래시 메모리 어레이와 같이 3차원 적충형 메모리 어레이에서 계단형 컨택 플러그형성 공정의 개선은 계속 요구되어 왔다.

#### 발명의 내용

#### 해결하려는 과제

[0006] 본 발명은 상기 종래 기술의 문제점을 해결하기 위하여 제안된 것으로서, 3차원 적층형 메모리 어레이에서 층수의 증가와 무관하게 계단형 컨택을 한 번에 형성할 수 있는 3차원 적층형 메모리 어레이의 컨택 형성 방법을 제공하는 것을 그 목적으로 한다.

#### 과제의 해결 수단

[0007] 상기 목적을 달성하기 위하여 본 발명에 의한 3차원 적층형 메모리 어레이의 컨택 형성 방법은 기판 상에 일정 한 수직 거리 d로 이격되며 적어도 일 단부가 순차적으로 드러나도록 계단형 돌출부를 갖는 복수개의 반도체층 사이를 제 1 층간 절연막으로 채우고 평탄화시키는 제 1 단계; 상기 제 1 층간 절연막 상에 제 1 하드 마스크 물질층을 형성하는 제 2 단계; 상기 제 1 하드 마스크 물질층을 식각하여 상기 계단형 돌출부 상에 상기 수직 거리와 동일한 수평 간격 d로 상기 반도체층의 수만큼 복수개의 컨택 홀 패턴을 형성하는 제 3 단계; 상기 기판 전면에 제 2 층간 절연막으로 상기 복수개의 컨택 홀 패턴을 채우며 증착하여 상기 제 1 하드 마스크 물질층 상 에 일정 두께로 남아 있도록 하는 제 4 단계; 상기 제 1 하드 마스크 물질층 상에 남아 있는 상기 제 2 층간 절 연막을 식각하여 상기 복수개의 반도체층 상에만 남아 있도록 제 2 층간 절연막 패턴을 형성하는 제 5 단계; 상 기 기판 전면에 제 2 하드 마스크 물질층을 증착한 후 일측에 상기 제 2 층간 절연막 패턴이 드러나도록 식각하 는 제 6 단계; 상기 제 1, 2 하드 마스크 물질층을 이용하여 드러난 상기 제 2 층간 절연막 패턴을 따라 상기 제 2 층간 절연막을 등방성으로 식각하여 상기 복수개의 컨택 홀 패턴이 상기 수평 간격 d 만큼 식각 깊이에 차 이를 내며 드러나도록 하는 제 7 단계; 상기 제 2 하드 마스크 물질층을 식각하여 상기 복수개의 컨택 홀 패턴 이 노출되도록 하는 제 8 단계; 상기 제 1 하드 마스크 물질층을 이용하여 상기 제 1, 2 층간 절연막을 비등방 성으로 식각하여 상기 복수개의 반도체층의 계단형 돌출부가 드러나도록 복수개의 컨택 홀을 형성하는 제 9 단 계; 및 상기 기판 전면에 도전성 물질로 상기 복수개의 컨택 홀을 채워 복수개의 택 플러그를 한번에 형성하는 제 10 단계를 포함하여 구성된 것을 특징으로 한다.

- [0008] 그리고, 상기 제 1, 2 충간 절연막은 동일한 물질의 절연막인 것을 본 발명에 의한 3차원 적충형 메모리 어레이의 컨택 형성 방법의 다른 특징으로 한다.

- [0009] 그리고, 상기 제 8 단계는 상기 제 2 충간 절연막이 등방성으로 식각되어 생긴 공간에 컨택 보호충을 채우는 단계; 상기 컨택 보호충이 드러나도록 상기 제 2 하드 마스크 물질충을 식각하는 단계; 및 상기 컨택 보호충을 제거하여 상기 복수개의 컨택 홀 패턴이 노출되도록 하는 단계로 구성된 것을 본 발명에 의한 3차원 적충형 메모리 어레이의 컨택 형성 방법의 또 다른 특징으로 한다.

- [0010] 그리고, 상기 제 1, 2 층간 절연막은 산화막이고, 상기 제 1, 2 하드 마스크 물질층은 질화막층이고, 상기 컨택 보호층은 실리콘계 물질, 실리콘게르마늄(SiGe) 및 감광막(PR) 중 어느 하나의 물질인 것을 본 발명에 의한 3차 원 적층형 메모리 어레이의 컨택 형성 방법의 또 다른 특징으로 한다.

#### 발명의 효과

[0011] 본 발명은 3차원 적충형 메모리 어레이에서 적충된 반도체충의 충수와 무관하게 서로 다른 깊이를 갖는 계단형 컨택을 한 번에 형성할 수 있게 됨으로써, 관련 공정비용과 공정단계를 획기적으로 줄일 수 있는 효과가 있다.

#### 도면의 간단한 설명

[0012] 도 1은 계단형 컨택 부위(100)와 이에 연결되는 계단형 컨택 플러그(110)를 갖는 3차원 적층형 플래시 메모리 어레이 구조의 일 예를 도시한 분해 사시도이다.

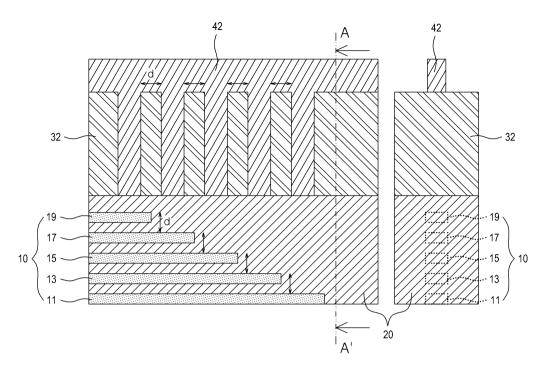

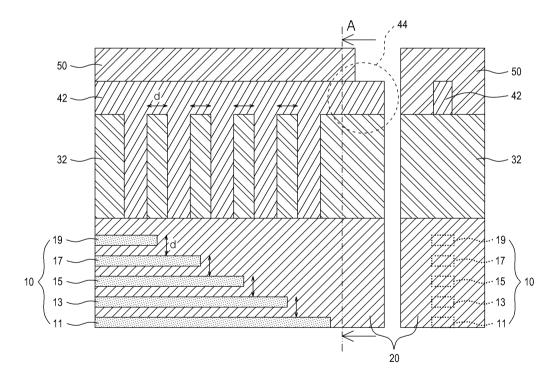

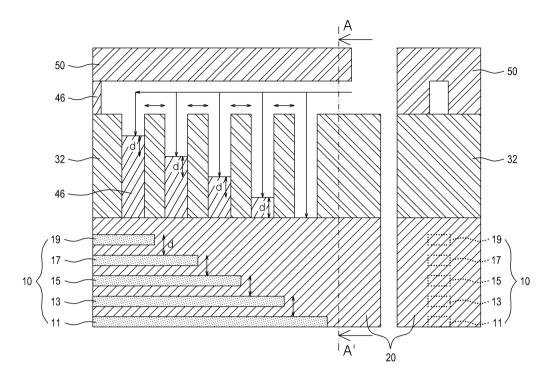

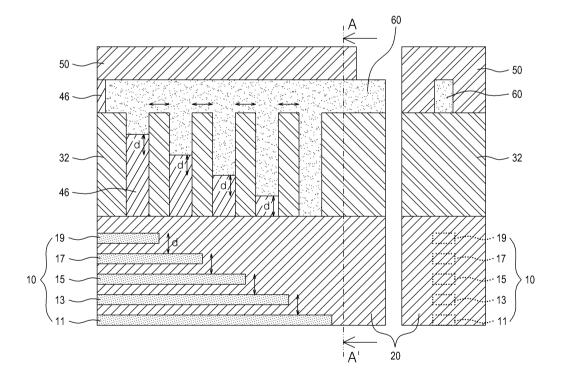

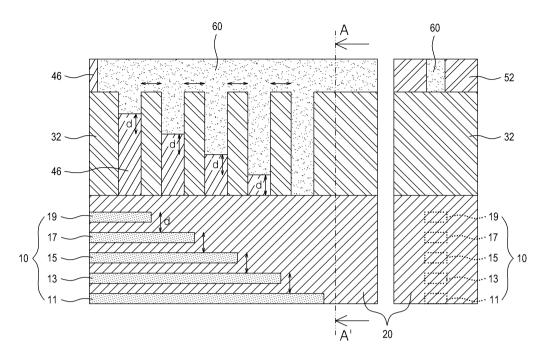

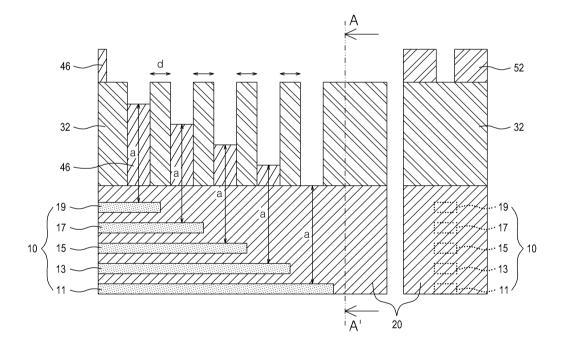

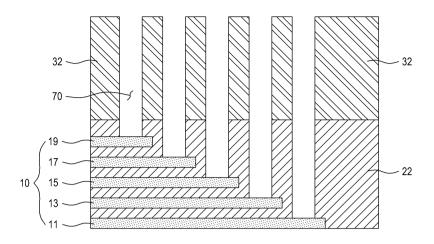

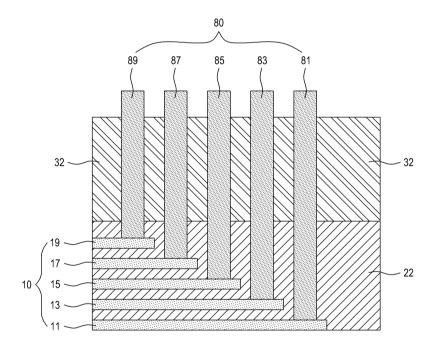

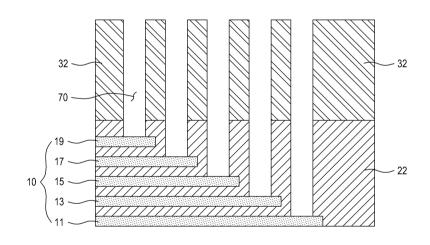

도 2 내지 도 12는 본 발명의 공정 단계를 보여주는 공정 단면도이고, 도 2 내지 도 10에서 우측에 도시된 각 도면은 좌측 도의 AA'선 단면도를 도시한 것이다.

### 발명을 실시하기 위한 구체적인 내용

- [0013] 이하, 첨부된 도면을 참조하며 본 발명에 의한 3차원 적증형 메모리 어레이 컨택 형성 방법의 바람직한 실시예에 대하여 상세히 설명한다.

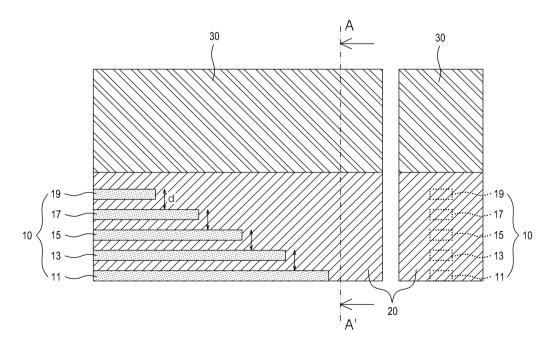

- [0014] 우선, 도 2와 같이, 기판(미도시) 상에 일정한 수직 거리 d로 이격되며 적어도 일 단부가 순차적으로 드러나도록 계단형 돌출부를 갖는 복수개의 반도체층(10: 11, 13, 15, 17, 19) 사이를 제 1 층간 절연막(20)으로 채우고 평탄화시킨다(제 1 단계).

- [0015] 여기서, 상기 제 1 충간 절연막(20)은 산화막(oxide)일 수 있고, 도 2에 도시된 바와 같이, 최상단 반도체충 (19) 위로 일정 두께 남아 있도록 평탄화시킨다.

- [0016] 이어, 도 2와 같이, 상기 제 1 층간 절연막(20) 상에 제 1 하드 마스크 물질층(30)을 형성한다(제 2 단계).

- [0017] 여기서, 상기 제 1 하드 마스크 물질층(30)은 상기 제 1 층간 절연막(20)과 식각률 차이가 나는 물질이면 어느 것이나 이용될 수 있으나, 상기 제 1 층간 절연막(20)이 산화막일 경우 질화막(nitride)으로 형성함이 바람직하다.

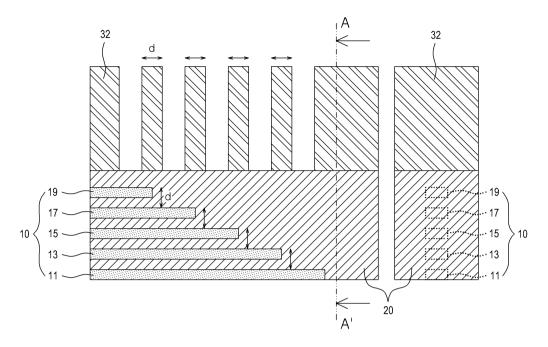

- [0018] 다음, 도 3과 같이, 상기 제 1 하드 마스크 물질층(30)을 식각하여 상기 계단형 돌출부 상에 상기 수직 거리와 동일한 수평 간격 d로 상기 반도체층(10)의 수만큼 복수개의 컨택 홀 패턴(32)을 형성한다(제 3 단계).

- [0019] 여기서, 상기 복수개의 컨택 홀 패턴(32)은 반도체충(10) 간의 수직 거리 d와 동일하게 수평 간격 d로 이격되며 수직하게 복수개의 컨택 홀이 형성되도록 함으로써, 차후 공정에서 계단형 돌출부에 맞추어 컨택 홀 패턴에 채워진 물질의 식각 깊이에 차이를 둘 수 있게 된다.

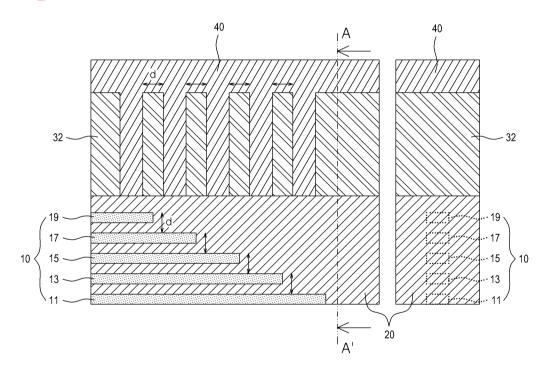

- [0020] 이어, 도 4와 같이, 상기 기판 전면에 제 2 층간 절연막(40)으로 상기 복수개의 컨택 홀 패턴(32)을 채우며 증착하여 상기 제 1 하드 마스크 물질층(30) 상에 일정 두께로 남아 있도록 한다(제 4 단계).

- [0021] 이때, 상기 제 2 층간 절연막(40)은 상기 제 1 층간 절연막(20)과 동일한 식각률을 가지면 충분하므로, 서로 다른 물질일 수 있으나, 서로 동일한 물질로 사용함이 바람직하다. 이렇게 함으로써, 차후 공정에서 상기 복수개의 컨택 홀 패턴(32)을 따라 상기 제 1, 2 층간 절연막(20)(40)을 식각할 경우 같은 시간이면 같은 깊이로 식각하게 된다.

- [0022] 다음, 도 5와 같이, 상기 제 1 하드 마스크 물질층(30) 상에 남아 있는 상기 제 2 층간 절연막(40)을 식각하여 상기 복수개의 반도체층(10) 상에만 남아 있도록 패터닝함으로써, 제 2 층간 절연막 패턴(42)을 형성한다(제 5

단계).

- [0023] 이어, 도 6과 같이, 상기 기판 전면에 제 2 하드 마스크 물질층(50)을 증착한 후 일측에 상기 제 2 층간 절연막 패턴(42)이 드러나도록 식각한다(제 6 단계).

- [0024] 여기서, 상기 제 2 하드 마스크 물질층(50)은 상기 제 2 층간 절연막(40)과 식각률이 다른 물질이면 충분하나, 상기 제 1 하드 마스크 물질층(30)과 동일한 물질로, 질화막일 수 있다.

- [0025] 다음, 도 7과 같이, 상기 제 1, 2 하드 마스크 물질층(30: 32)(50)을 이용하여 드러난 상기 제 2 층간 절연막 패턴(42)을 따라 화학적 건식 식각(chemical dry etch)과 같은 등방성 식각으로 상기 제 2 층간 절연막(40)을 식각하게 되면, 상기 복수개의 컨택 홀 패턴(32)이 상기 수평 간격 d 만큼 식각 깊이에 차이를 내며 드러나게 되고, 그 결과 도 10과 같이, 각 반도체층의 돌출부와의 거리 a가 동일하게 된다(제 7 단계).

- [0026] 이어, 상기 제 2 하드 마스크 물질층(50)을 식각하여 상기 복수개의 컨택 홀 패턴(32)이 노출되도록 한다(제 8 단계).

- [0027] 여기서, 상기 제 2 하드 마스크 물질층(50)을 바로 식각하고, 상기 복수개의 컨택 홀 패턴(32)을 노출시킬 수도 있으나, 도 8과 같이, 상기 제 2 층간 절연막(40)이 등방성으로 식각되어 생긴 공간에 컨택 보호층(60)을 채우는 단계와, 도 9와 같이, 상기 컨택 보호층(60)이 드러나도록 상기 제 2 하드 마스크 물질층(50)을 식각하는 단계와, 도 10과 같이, 상기 컨택 보호층(60)을 습식식각 등으로 선택적으로 제거하여 상기 복수개의 컨택 홀 패턴(32)이 노출되도록 하는 단계로 진행하는 것이 바람직하다. 후자와 같이 함으로써, 상기 복수개의 컨택 홀 패턴(32)을 손상 없이 유지할 수 있게 되어 추후 이를 층간 절연막으로 이용할 수 있는 장점이 있다.

- [0028] 또한, 상기 컨택 보호층(60)은 상기 제 2 하드 마스크 물질층(50)과 식각률 차이가 있으면 어떤 물질도 가능하나, CVD 방법으로 빈 공간을 채울 수 있도록 실리콘계 물질(폴리실리콘 등), 실리콘게르마늄(SiGe) 및 감광막(PR) 중 어느 하나의 물질로 사용될 수 있다.

- [0029] 다음, 도 11과 같이, 상기 제 1 하드 마스크 물질층(30)의 복수개의 컨택 홀 패턴(32)을 이용하여 상기 제 1, 2 층간 절연막(20)(46)을 비등방성으로 일정 시간 식각하게 되면, 상기 복수개의 반도체층(10)의 계단형 돌출부가 드러나도록 복수개의 컨택 홀(70)을 한번에 형성하게 된다(제 9 단계).

- [0030] 이어, 도 12와 같이, 상기 기판 전면에 도전성 물질로 상기 복수개의 컨택 홀(70)을 채우게 되면, 복수개의 컨택 플러그(80: 81, 83, 85, 87, 89)를 한번에 형성하게 된다(제 10 단계).

- [0031] 이상 설명된 바에 의하면, 아무리 반도체층수가 증가 된다고 하더라도, 한번에 복수개의 컨택 홀(70)과 컨택 플러그(80)를 각각 형성할 수 있게 되어 공정비용과 공정단계를 획기적으로 줄일 수 있게 된다.

#### 부호의 설명

- [0032] 10: 복수개의 반도체층

- 20: 제 1 층간 절연막

- 30: 제 1 하드 마스크 물질층

- 40: 제 2 층간 절연막

- 50: 제 2 하드 마스크 물질층

- 60: 컨택 보호층

- 70: 컨택 홀

- 80: 컨택 플러그

## 도면1