US 20220044990A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2022/0044990 A1

## Machida

Feb. 10, 2022 (43) **Pub. Date:**

#### (54) WIRING SUBSTRATE, SEMICONDUCTOR PACKAGE AND METHOD OF MANUFACTURING WIRING SUBSTRATE

- (71) Applicant: SHINKO ELECTRIC INDUSTRIES CO., LTD., Nagano-shi (JP)

- (72) Inventor: Tomoaki Machida, Nagano-shi (JP)

- (21) Appl. No.: 17/497,158

- (22) Filed: Oct. 8, 2021

### **Related U.S. Application Data**

(62) Division of application No. 16/811,731, filed on Mar. 6, 2020, now Pat. No. 11,171,081.

#### (30)**Foreign Application Priority Data**

Mar. 20, 2019 (JP) ...... 2019-053623

## **Publication Classification**

(2006.01)

(2006.01)

(2006.01)

(51) Int. Cl. H01L 23/498 H01L 23/00 H01L 21/48

(52) U.S. Cl. CPC ...... H01L 23/49822 (2013.01); H01L 24/16 (2013.01); H01L 2224/16227 (2013.01); H01L 21/4857 (2013.01); H01L 23/49811 (2013.01); H01L 23/49838 (2013.01)

#### (57) ABSTRACT

A second wiring layer is connected to a first wiring layer via an insulating layer. The second wiring layer comprises pad structures. Each pad structure includes a first metal layer formed on the insulating layer, a second metal layer formed on the first metal layer, and a third metal layer formed on the second metal layer. The pad structures comprises a first pad structure and a second pad structure. A via-wiring diameter of the first pad structure is different from a via-wiring diameter of the second pad structure. A distance from an upper surface of the insulating layer to an upper surface of the second metal layer of the first pad structure is the same as a distance from the upper surface of the insulating layer to an upper surface of the second metal layer of the second pad structure.

FIG. 1B

FIG. 2C

FIG. 3Å

FIG. 3B

FIG. 3D

FIG. 4A

#### WIRING SUBSTRATE, SEMICONDUCTOR PACKAGE AND METHOD OF MANUFACTURING WIRING SUBSTRATE

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a divisional of U.S. application Ser. No. 16/811,731, filed Mar. 6, 2020.

**[0002]** This application is based upon and claims the benefit of priority from prior Japanese patent application No. 2019-053623, filed on Mar. 20, 2019, the entire contents of which are incorporated herein by reference.

#### TECHNICAL FIELD

**[0003]** The present disclosure relates to a wiring substrate, a semiconductor package and a method of manufacturing a semiconductor package.

#### BACKGROUND ART

**[0004]** Known is a wiring substrate including a first wiring layer, a first insulating layer configured to cover the first wiring layer, and a second wiring layer connected to the first wiring layer via the first insulating layer. In the wiring substrate, the second wiring layer has a plurality of pad structures each of which has a via-wiring formed in the first insulating layer, and a first pad for semiconductor chip connection formed integrally with the via-wiring on an upper surface of the first insulating layer, for example.

**[0005]** The pad structures may be formed by following processes, for example. First, a first insulating layer tot covering a first wiring layer is formed and the first insulating layer is formed with via-holes for exposing an upper surface of the first wiring layer. Then, a seed layer is continuously formed on a surface of the first insulating layer including inner walls of the via-holes and on a surface of the first wiring layer exposed in the via-holes.

**[0006]** Subsequently, a resist pattern having opening portions each conforming to a shape of the first pad is formed on the seed layer, and an electrolytic plated layer is formed on the seed layer exposed in the opening portions of the resist pattern by an electrolytic plating method of feeding power from the seed layer. Thereafter, the resist pattern is removed.

**[0007]** Then, an etching is performed by using the electrolytic plated layer as a mask, so that the seed layer exposed from the electrolytic plated layer is removed. Thereby, a plurality of pad structures each having a via-wiring and a first pad integrally formed with the via-wiring is formed,

[0008] [PTL 1] JP-A-2017-73520

**[0009]** However, opening diameters of the via-holes in the respective pad structures may not be uniform. In this case, a filling time (a time for which a via-wiring is formed) of the electrolytic plating is shorter in the small-diameter via-holes than in the large-diameter via-holes. Since the first pad is formed integrally with the via-wiring on the via-wiring filling the via-hole, a height of the first pad is relatively high in the small-diameter via-hole and is relatively low in the large-diameter via-hole. That is, when the opening diameters of the via-holes are not uniform, the heights of the first pads are also not uniform, so that connection reliability upon interconnection of the first pads and the semiconductor chip is lowered.

**[0010]** For example, for a portion in which the height of the first pad is low, when connection is made by soldering, an interval between the first pad and an electrode pad of the semiconductor chip increases, so that an amount of solder rig necessary for connection is not enough for connection and an open defect may thus occur. Also, for a portion in which the height of the first pad is high, when connection is made by soldering, the interval between the first pad and the electrode pad of the semiconductor chip decreases, so that an excessive amount of solder flows laterally to connect the first pads adjacent to each other and a short defect may thus occur.

#### SUMMARY OF INVENTION

**[0011]** Aspect of non-limiting embodiments of the present disclosure is to provide a wiring substrate, a semiconductor package and a method of manufacturing a semiconductor package, which can improve connection reliability of pads for semiconductor chip connection and a semiconductor chip upon connection with the semiconductor chip.

**[0012]** A wiring substrate according to non-limiting embodiment of the present disclosure comprises:

[0013] a first wiring layer;

**[0014]** an insulating layer formed to cover the first wiring layer; and

**[0015]** a second wiring layer connected to the first wiring layer via the insulating layer,

**[0016]** wherein the second wiring layer comprises a plurality of pad structures, each of the pad structures including a via-wiring and a pad for semiconductor chip connection, the via-wiring filled in a via-hole, the via hole penetrating the insulating layer and formed to expose an upper surface of the first wiring layer, the pad for semiconductor chip connection formed on an upper surface of the insulating layer and integrally formed with the via-wiring,

[0017] wherein each of the pad structures comprises:

**[0018]** a first metal layer continuously formed on the upper surface of the insulating layer, on an inner wall surface of the via-hole, and on the upper surface of the first wiring layer exposed in the via-hole,

**[0019]** a second metal layer formed on the first metal layer, filling the via-hole, extending upwardly beyond the upper surface of the insulating layer, and having an upper surface being flat, and

**[0020]** a third metal layer formed on an upper surface of the second metal layer,

**[0021]** wherein the plurality of pad structures comprises a first pad structure and a second pad structure, and a viawiring diameter of the first pad structure is different from a via-wiring diameter of the second pad structure, and

**[0022]** wherein a distance from the upper surface of the insulating layer to the upper surface of the second metal layer of the first pad structure is the same as a distance from the upper surface of the insulating layer to the upper surface of the second metal layer of the second pad structure.

**[0023]** According to the disclosed technology, in the wiring substrate including pads for semiconductor chip connection, it is possible to improve connection reliability of the pads and the semiconductor chip upon connection with the semiconductor chip.

#### BRIEF DESCRIPTION OF DRAWINGS

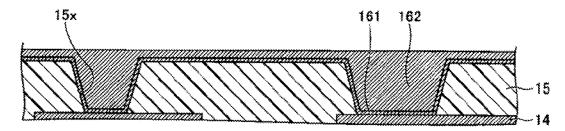

**[0024]** FIGS. 1A and 1B are sectional views exemplifying a wiring substrate in accordance with a first embodiment. **[0025]** FIGS. 2A to 2C are views exemplifying a manufacturing process of the wiring substrate in accordance with the first embodiment (1 thereof).

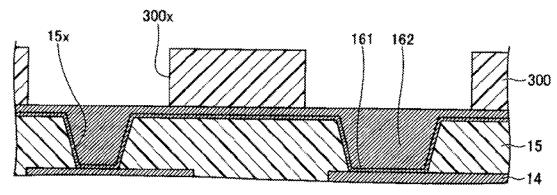

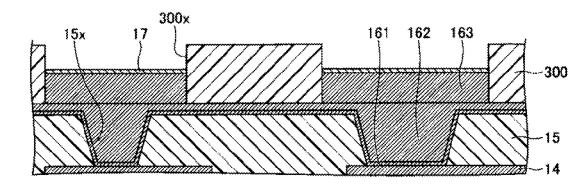

**[0026]** FIGS. **3**A to **3**D are views exemplifying a manufacturing process of the wiring substrate in accordance with the first embodiment (2 thereof).

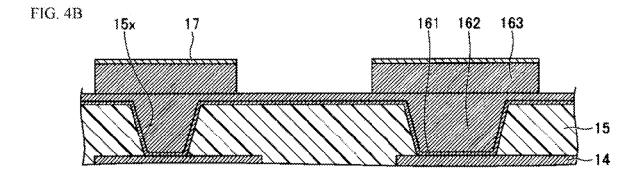

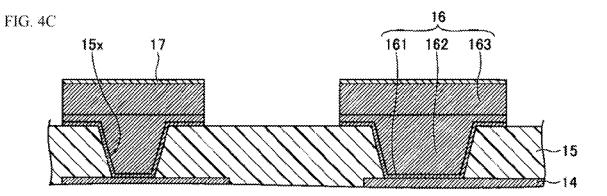

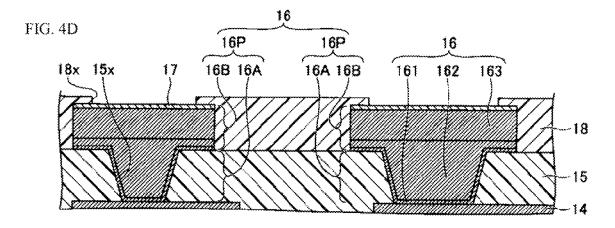

**[0027]** FIGS. **4**A to **4**D are views exemplifying a manufacturing process of the wiring substrate in accordance with the first embodiment (3 thereof).

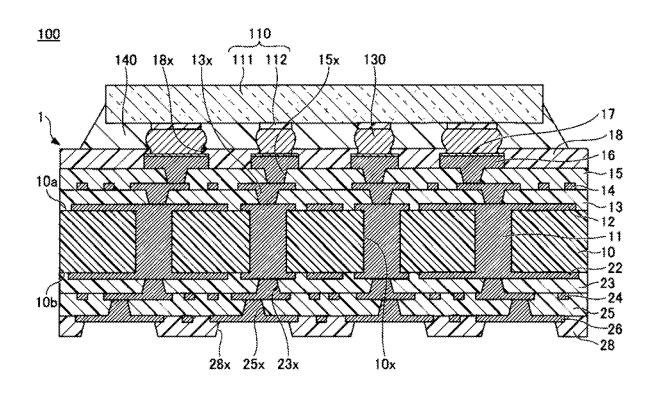

**[0028]** FIG. **5** is a sectional view exemplifying a semiconductor package in accordance with a second embodiment.

#### DETAILED DESCRIPTION OF EMBODIMENTS

**[0029]** Hereinbelow, embodiments of the present disclosure will be described with reference to the drawings. Meanwhile, in the respective drawings, the same constitutional parts are denoted with the same reference numerals, and the overlapping descriptions thereof may be omitted.

#### First Embodiment

[0030] [Structure of Wiring Substrate of First Embodiment]

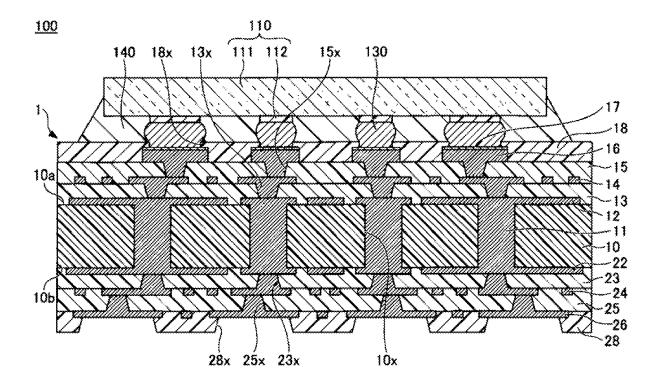

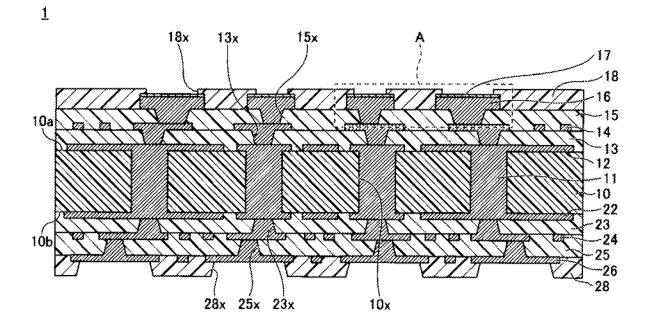

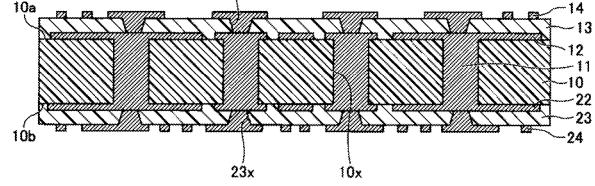

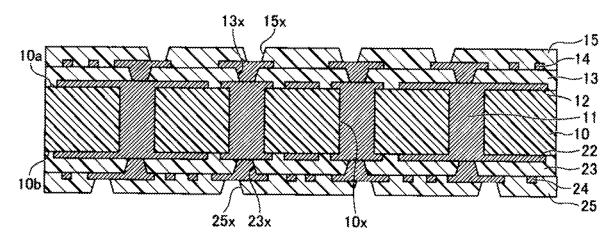

**[0031]** First, a structure of a wiring substrate of a first embodiment is described. FIGS. **1A** and **1B** are sectional views exemplifying the wiring substrate in accordance with the first embodiment, in which FIG. **1A** is an overall view and FIG. **1B** is a partially enlarged view.

**[0032]** Referring to FIG. 1A, the wiring substrate 1 is a wiring substrate in which wiring layers and insulating layers are stacked on both sides of a core layer 10.

[0033] Specifically, in the wiring substrate 1, a wiring layer 12, an insulating layer 13, a wiring layer 14, an insulating layer 15, a wiring layer 16, a surface-treated layer 17, and a solder resist layer 18 are sequentially stacked on one surface 10*a* of the core layer 10. Also, a wiring layer 22, an insulating layer 23, a wiring layer 24, an insulating layer 25, a wiring layer 26, and a solder resist layer 28 are sequentially stacked on the other surface lob of the core layer 10. In the meantime, the solder resist layers 18 and 28 are layers that are optionally provided, as required. That is, the formation of the solder resist layers 18 and 28 is not necessarily required.

[0034] Meanwhile, in the first embodiment, for convenience sake, the solder resist layer 18-side of the wiring substrate 1 is referred to as 'upper side' or 'one side', and the solder resist layer 28-side is referred to as 'lower side' or 'other side'. Also, a surface of each part facing toward the solder resist layer 18 is referred to as 'one surface' or 'upper surface', and a surface facing toward the solder resist layer 28 is referred to as 'other surface' or 'lower surface'. However, the wiring substrate 1 can be used with being vertically reversed or can be arranged at any angle. Also, the description as seen from above' indicates that a target object is seen in a normal direction of one surface 10a of the core layer 10, and a planar shape indicates a shape of the target object as seen from the normal direction of one surface 10a of the core layer 10.

**[0035]** As the core layer **10**, for example, a so-called glass epoxy substrate where an insulating resin such as an epoxy-

based resin is impregnated in glass cloth may be used. As the core layer 10, a substrate where an epoxy-based resin, a polyimide-based resin or the like is impregnated in woven fabric or non-woven fabric of glass fiber, carbon fiber, aramid fiber and the like may also be used. A thickness of the core layer 10 may be set to about 60 to 400  $\mu$ m, for example. The core layer 10 is formed with through-holes 10x penetrating the core layer 10 in a thickness direction. A planar shape of the through-hole 10x is circular, for example.

[0036] The wiring layer 12 is formed on one surface 10a of the core layer 10. Also, the wiring layer 22 is formed on the other surface 10b of the core layer 10. The wiring layer 12 and the wiring layer 22 are electrically interconnected by through-wirings 11 formed in the through-holes 10x. The wiring layers 12 and 22 are respectively patterned into a predetermined planar shape. For the wiring layers 12. and 22 and the through-wiring 11, copper (Cu) or the like may be used, for example. A thickness of each of the wiring layers 12 and 22 may be set to about 10 to 30 µm, for example. In the meantime, the wiring layer 12, the wiring layer 22 and the through-wirings 11 may also be integrally formed.

[0037] The insulating layer 13 is formed on one surface 10a of the core layer 10 so as to cover the wiring layer 12. As a material of the insulating layer 13, for example, a non-photosensitive thermosetting resin of which a main component is an epoxy-based resin, a polyimide-based resin or the like may be used. As a material of the insulating layer 13, for example, a photosensitive resin of which a main component is an epoxy-based resin, an acryl-based resin or the like may also be used. A thickness of the insulating layer 13 may be set to about 30 to 40 µm, for example. The insulating layer 13 may contain a filler such as silica  $(SiO_2)$ . [0038] The wiring layer 14 is formed on one side of the insulating layer 13. The wiring layer 14 includes via-wirings filled in via-holes 13x penetrating the insulating layer 13 and formed to expose an upper surface of the wiring layer 12, and a wiring pattern formed on an upper surface of the insulating layer 13. The wiring pattern of the wiring layer 14 is electrically connected to the wiring layer 12 through the via-wirings. The via-hole 13x is a concave portion having an inverted conical shape of which a diameter of an opening portion opened toward the insulating layer 15 is larger than a diameter of a bottom surface of an opening portion formed by the upper surface of the wiring layer 12. A material of the wiring layer 14 and a thickness of the wiring pattern are similar to those of the wiring layer 12, for example.

[0039] The insulating layer 15 is formed on the upper surface of the insulating layer 13 so as to cover the wiring layer 14. A material and a thickness of the insulating layer 15 are similar to those of the insulating layer 13, for example. The insulating layer 15 may contain a filler such as silica (SiO<sub>2</sub>).

[0040] The wiring layer 16 is formed on one side of the insulating layer 15. The wiring layer 16 includes via-wirings filled in via-holes 15x penetrating the insulating layer 15 and formed to expose an upper surface of the wiring layer 14 and pads formed on an upper surface of the insulating layer 15. The pads of the wiring layer 16 are electrically connected to the wiring layer 14 through the via-wirings. The via-hole 15x is a concave portion having an inverted conical shape of which a diameter of an opening portion opened toward the solder resist layer 18 is larger than a diameter of a bottom surface of an opening portion formed by the upper surface of the wiring layer 14. A material of the wiring layer 16 and

a thickness of the pad are similar to those of the wiring layer **12**, for example. In the meantime, a detailed structure of the wiring layer **16** will be described later.

[0041] The surface-treated layer 17 is formed on an upper surface of the wiring layer 16. As the surface-treated layer 17, a metal layer may be formed, or an organic film may be formed by performing antioxidant processing such as OSP (Organic Solderability Preservative) processing. As the metal layer, an Au layer, a Ni/Au layer (a metal layer having a Ni layer and an Au stacked in corresponding order), a Ni/Pd/Au layer (a metal layer having a Ni layer, a Pd layer and an Au layer stacked in corresponding order), a Sn layer and the like may be exemplified. In the meantime, the surface-treated layer 17 is a layer that is optionally formed, as required. That is, the formation of the surface-treated layer 17 is not necessarily required,

**[0042]** The solder resist layer **18** is an outermost layer on one side of the wiring substrate **1**, and is formed on the upper surface of the insulating layer **15** so as to cover the wiring layer **16** and the surface-treated layer **17**. The solder resist layer **18** may be formed of a photosensitive resin of which a main component is an epoxy-based resin, an acryl-based resin or the like, for example. A thickness of the solder resist layer **18** may be set to about 15 to 35 µm, for example.

[0043] The solder resist layer 18 has opening portions 18x, and parts of an upper surface of the surface-treated layer 17 are exposed to bottom portions of the opening portions 18x. A planar shape of the opening portion 18x is circular, for example. In the meantime, a tip end-side of the wiring layer 16 and the surface-treated layer 17 may extend beyond an upper surface of the solder resist layer 18. In this case, inner wall surfaces of the opening portions 18x cover parts of a side surface of the wiring layer 16.

[0044] The insulating layer 23 is formed on the other surface 10b of the core layer 10 so as to cover the wiring layer 22. A material and a thickness of the insulating layer 23 are similar to those of the insulating layer 13, for example. The insulating layer 23 may contain a filler such as silica (SiO<sub>2</sub>).

[0045] The wiring layer 24 is formed on the other side of the insulating layer 23. The wiring layer 24 includes viawirings filled in via-holes 23x penetrating the insulating layer 23 and formed to expose a lower surface of the wiring layer 22, and a wiring pattern formed on a lower surface of the insulating layer 23. The wiring pattern of the wiring layer 24 is electrically connected to the wiring layer 22 through the via-wirings. The via-hole 23x is a concave portion having a conical shape of which a diameter of an opening portion opened toward the insulating layer 25 is larger than a diameter of a bottom surface of an opening portion formed by the lower surface of the wiring layer 24 are similar to those of the wiring layer 12, for example.

[0046] The insulating layer 25 is formed on the lower surface of the insulating layer 23 so as to cover the wiring layer 24. A material and a thickness of the insulating layer 25 are similar to those of the insulating layer 13, for example The insulating layer 25 may contain a filler such as silica (SiO<sub>2</sub>).

[0047] The wiring layer 26 is formed on the other side of the insulating layer 25. The wiring layer 26 includes viawirings filled in via-holes 25x penetrating the insulating layer 25 and formed to expose a lower surface of the wiring layer 24, and a wiring pattern formed on a lower surface of the insulating layer 25. The wiring pattern of the wiring layer 26 is electrically connected to the wiring layer 24 through the via-wirings. The via-hole 25x is a concave portion having a conical shape of which a diameter of an opening portion opened toward the solder resist layer 28 is larger than a diameter of a bottom surface of an opening portion formed by the lower surface of the wiring layer 24. A material and a thickness of the wiring layer 26 are similar to those of the wiring layer 12, for example.

[0048] The solder resist layer 28 is an outermost layer on the other side of the wiring substrate 1, and is formed on a lower surface of the insulating layer 25 so as to cover the wiring layer 26. A material and a thickness of the solder resist layer 28 are similar to those of the solder resist layer 18. The solder resist layer 28 has opening portions 28x, and parts of a lower surface of the wiring layer 26 are exposed in the opening portions 28x. A planar shape of the opening 28x is circular, for example. The wiring layer 26 exposed in the opening portions 28x may be used as a pad for electrical connection with a mounting substrate (not shown) such as a motherboard. If necessary, the lower surface of the wiring layer 26 exposed in the opening portions 29x may be formed with the above-described metal layer or may be formed with an organic film by performing the antioxidant processing such as OSP processing.

[0049] Herein, the wiring layer 16 is described in detail. As shown in FIG. 1B, the wiring layer 16 has a plurality of pad structures 16P. Each of the pad structures 16P includes a via-wiring 16A and a pad 16B for semiconductor chip connection. The via-wiring 16A is filled in the via-hole 15x, which penetrates the insulating layer 15 and is formed to expose the upper surface of the wiring layer 14. The pad 1613 for semiconductor chip connection is formed on the upper surface of the insulating layer 15 and formed integrally with the via wiring 16A. A planar shape of the via-wiring 16A and the pad 168 is circular, respectively, for example. In the below, a case in which the planar shapes of the via-wiring 16A and the pad 16B are respectively circular is described.

**[0050]** The plurality of pad structures **16**P includes pad structures of which pad diameters and diameters of viawirings (hereinbelow, referred to as 'via-wiring diameter') are different. For example, in the pad structure **16**P on the left side in FIG. **1B**, the pad diameter  $\phi$ **11** is about 40 to 50 µm, and the via-wiring diameter  $\phi$ **12** is about 20 to 30 µm. Also, in the pad structure **16**P on the right side in FIG **1B**, the pad diameter  $\phi$ **11** is about 20 to 30 µm. Also, in the pad structure **16**P on the right side in FIG **1B**, the pad diameter  $\phi$ **11** is about 60 to 80 µm, and the via-wiring diameter  $\phi$ **22** is about 40 to 50 µm.

[0051] Each pad structure 16P included in the wiring layer 16 includes a first metal layer 161, a second metal layer 162, and a third metal layer 163.

**[0052]** The first metal layer **161** is continuously formed on the upper surface of the insulating layer **15**, on the inner wall surface of the via-hole **15**x, and on the upper surface of the wiring layer **14** exposed in the via-hole **15**x. A material of the first metal layer **161** is, for example, copper. A thickness of the first metal layer **161** is, for example, 1 µm or less.

[0053] The second metal layer 162 is formed on the first metal layer 161. The second metal layer 162 fills the via-hole 15x and extends upwardly beyond the upper surface of the insulating layer 15. A thickness of a pan of the second metal layer 162 formed outside of the via-hole 15x is thicker than the first metal layer 161, and is, for example, about 1 to 5  $\mu$ m.

[0054] The third metal layer 163 is formed on an upper surface of the second metal layer 162. A thickness of the third metal layer 163 is constant, and is, for example, about 10 to 30  $\mu$ m.

[0055] The second metal layer 162 and the third metal layer 163 are formed of the same metal material such as copper. Even in a case in which the second metal layer 162 and the third metal layer 163 are formed of the same metal material, the boundary between them can be recognized. The second metal layer 162 and the third metal layer 163 have a circular planar shape, respectively, and cross-sectional areas thereof are the same. That is, the second metal layer 162 and the third metal layer 163 have a circular column shape. In the meantime, the first metal layer 161 may be formed of the same metal material as the second metal layer 162 and the third metal layer 163. Also, a cross-sectional area of the first metal layer 161 may be the same as those of the second metal layer 161 may be the same as those of the second metal layer 162 and the third metal layer 163. Also, a cross-sectional area of the first metal layer 161 may be the same as those of the second metal layer 162 and the third metal layer 163.

**[0056]** In the meantime, the cross-sectional area means an area of a cross-section taken in a direction orthogonal to a direction in which the second metal layer **162** and the third metal layer **163** are stacked. For example, in a case in which the second metal layer **162** and the third metal layer **163** have a circular column shape, the cross-sectional area is an area of a circular cross-section taken in a direction orthogonal to the direction in which the second metal layer **163** are stacked.

[0057] The upper surface of the second metal layer 162 is flat, so that positions on the upper surfaces of the second metal layers 162 of the pad structures 16P are on the same plane even in the pad structures 16P of which the pad diameters and the via-wiring diameters are different. That is, a distance from the upper surface of the insulating layer 15 to the upper surface of the second metal layer 162 is constant, irrespective of the pad diameters and the viawiring diameters. For example, in FIG. 1B, the pad diameter and the via-wiring diameter of the pad structure 16P on the left side is smaller than the pad diameter and the via-wiring diameter of the pad structure 16P on the right side; however, a distance from the upper surface of the insulating layer 15 to the upper surface of the second metal layer 162 of the pad structure 16P on the left side is the same as a distance from the upper surface of the insulating layer 15 to the upper surface of the second metal layer 162 of the pad structure 16P on the right side. Since a thickness of the third metal layer 163 is constant, a distance from the upper surface of the insulating layer 15 to an upper surface of the third metal layer 163 is constant, irrespective of the pad diameters and the via-wiring diameters of the pad structures 16P,

**[0058]** As used herein, the description "flat", "on the same plane", "constant" and the like include a case in which there is an error in degree of manufacturing variation.

[0059] [Manufacturing Method of Wiring Substrate of First Embodiment]

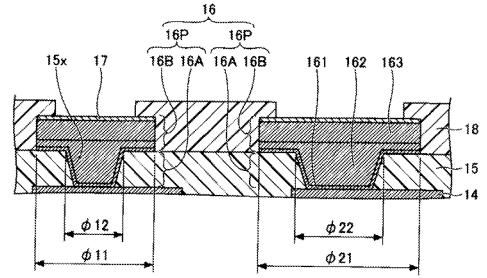

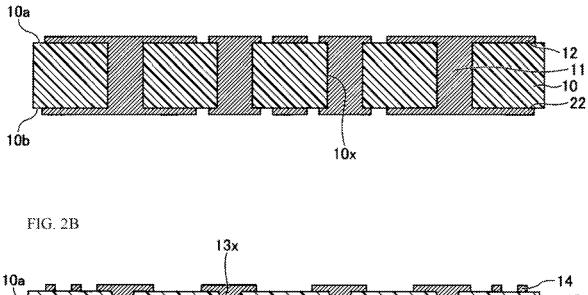

**[0060]** Subsequently, a manufacturing method of the wiring substrate of the first embodiment is described. FIGS. **2**A to **4**D exemplify manufacturing processes of the wiring substrate of the first embodiment. FIGS. **2**A to **2**C are sectional views corresponding to FIG. **1**A, and FIGS. **3**A to **4**D are sectional views corresponding to FIG 1B. In the meantime, an example of the process for manufacturing one wiring substrate is herein described. However, a plurality of

parts becoming wiring substrates may be manufactured and divided into individual parts to make the respective wiring substrates.

**[0061]** First, in a process of FIG. 2A, a core layer 10 is formed with through-wirings 11 and wiring layers 12 and 22. Specifically, for example, a deposited plate where plain copper foils are formed on one surface 10a and the other surface 10b of the core layer 10 is prepared. The plain copper foils are copper foils which are not patterned. The core layer 10 is such as a so-called glass epoxy substrate. The copper foils on the respective surfaces of the prepared deposited plate are made to be thin, as required. Then, through-holes 10x, which penetrates the core layer 10 and the copper foils on the respective surfaces, are formed by a laser processing method of using  $CO_2$  laser or the like.

[0062] Then, desmear processing is performed to remove the remaining resin included in the core layer 10, which is attached to the inner wall surfaces of the through-holes 10x, as needed. Then, a seed layer (copper or the like) configured to cover the copper foils on the respective surfaces and the inner surfaces of the through-holes 10x is formed by an electroless plating method, a sputter method or the like, for example. An electrolytic plated layer (copper or the like) is formed on the seed layer by an electrolytic plating method in which the seed layer is used as a power feeding layer. Thereby, the through-holes 10x are filled by the electrolytic plated layer formed on the seed layer, and wiring layers 12 and 22 in which the copper foil, the seed layer and the electrolytic plated layer are stacked are formed on one surface 10a and the other surface 10b of the core layer 10. Then, the wiring layers 12 and 22 are patterned into a predetermined planar shape by a subtractive method or the like.

[0063] Subsequently, in a process of FIG. 2B, one surface 10a of the core layer 10 is formed with an insulating layer 13 by laminating a non-photosensitive thermosetting resin of which a main component is a semi-cured film-like epoxybased resin, polyimide-based resin or the like so as to cover the wiring layer 12 and curing the same. Also, the other surface 10b of the core layer 10 is formed with an insulating layer 23 by laminating a non-photosensitive thermosetting resin of which a main component is a semi-cured film-like epoxy-based resin, polyimide-based resin or the like so as to cover the wiring layer 22 and curing the same. Alternatively, instead of the laminating of the film-like epoxy-based resin or the like, a liquid form or paste-like epoxy-based resin or the like may be applied and cured to form the insulating layers 13 and 23. A thickness of each of the insulating layers 13 and 23 may be set to about 30 to 40  $\mu$ m, for example. Each of the insulating layers 13 and 23 may contain a filler such as silica (SiO<sub>2</sub>).

**[0064]** Then, the insulating layer **13** is formed with viaholes **13***x* penetrating the insulating layer **13** and configured to expose an upper surface of the wiring layer **12**. Also, the insulating layer **23** is formed with viaholes **23***x* penetrating the insulating layer **23** and configured to expose a lower surface of the wiring layer **22**. The viaholes **13***x* and **23***x* may be formed by a laser processing method of using CO<sub>2</sub> laser or the like, for example. After forming the viaholes **13***x* and **23***x*, desmear processing is preferably performed to remove the remaining resin attached to surfaces of the wiring layers **12** and **22** exposed to bottom portions of the viaholes **13***x* and **23***x*.

[0065] In the meantime, the insulating layers 13 and 23 may be formed of a photosensitive resin of which a main component is an epoxy-based resin, an acryl-based resin or the like. In this case, the via-holes 13x and 23x nay be formed by a photolithography method. This applies to the other insulating layers, too.

[0066] Subsequently, a wiring layer 14 is formed on one side of the insulating layer 13. The wiring layer 14 includes via-wirings filled in the via-holes 13x, and a wiring pattern formed on an upper surface of the insulating layer 13. A material of the wiring layer 14 and a thickness of the wiring pattern are similar to those of the wiring layer 12, for example. The wiring pattern of the wiring layer 14 is electrically connected to the wiring layer 12 exposed to the bottom portions of the via-holes 13x.

[0067] Also, a wiring layer 24 is formed on the other side of the insulating layer 23. The wiring layer 24 includes via-wirings filled in the via-holes 23x and a wiring pattern formed on a lower surface of the insulating layer 23. A material of the wiring layer 24 and a thickness of the wiring pattern are similar to those of the wiring layer 12, for example. The wiring layer 24 is electrically connected to the wiring layer 22 exposed to the bottom portions of the via-holes 23x. The wiring layers 14 and 24 may be formed using a variety of wiring forming methods such as a semiadditive method, a subtractive method and the like.

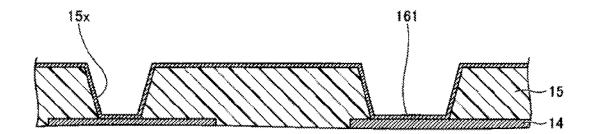

[0068] Subsequently, in a process of FIG. 2C, an insulating layer 15 is formed on the upper surface of the insulating layer 13 so as to cover the wiring layer 14 by the similar formation method to the insulating layer 13. A material and a thickness of the insulating layer 15 are similar to those of the insulating layer 13, for example. Then, via-holes 15x are formed by the similar method to the via-hole 13x. Also, an insulating layer 13 so as to cover the wiring layer 24 by the similar formation method to the insulating layer 24 by the similar formation method to the insulating layer 25 are similar to those of the insulating layer 13, for example. Then, via-holes 25x are formed by the similar method to the via-hole 13x.

**[0069]** Subsequently, in a process of FIG. **3**A, a first metal layer **161** to become a seed layer is continuously formed on a surface of the insulating layer **15** including inner walls of the via-holes **15**x and on a surface of the wiring layer **14** exposed in the via-holes **15**x. A material of the first metal layer **161** is, for example, copper. A thickness of the first metal layer **161** is, for example, 1  $\mu$ m or less. The first metal layer **161** may be formed by an electroless plating method or a sputter method, for example.

[0070] Subsequently in a process of FIG. 3B, an electrolytic plated layer formed of copper or the like is formed on the first metal layer 161 by an electrolytic plating method in which power is fed from the first metal layer 161, so that a second metal layer 162 is formed. The second metal layer 162 fills the via-holes 15*x*, and is formed to extend upwardly beyond an upper surface of the insulating layer 15. Specifically, the electrolytic plating is stopped at a point of time at which a thickness of a part of the second metal, layer 162 formed outside of the via-holes 1 is substantially uniform over an entire surface The thickness of the part of the second metal layer 162 formed outside of the via-holes 15*x* is, for example, about 10  $\mu$ m.

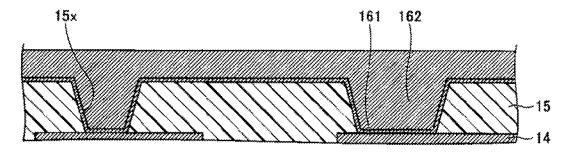

[0071] Subsequently, in a process of FIG. 3C, the second metal layer 162 is thinned to be entirely uniform. The upper

surface of the second metal layer 162 after the thinning is flat, so that positions on the upper surfaces of the second metal layers 162 of the pad structures are on the same plane with each other even in pad structures of which pad diameters and via-wiring diameters are different. That is, a distance from the upper surface of the insulating layer 15 to the upper surface of the second metal layer 162 is constant, irrespective of the pad diameters and the via-wiring diameters. After the thinning, the thickness of the part of the second metal layer 162 formed outside of the via-holes 15x is, for example, about 1 to 5  $\mu$ m. As the thinning method, etching, buffing, CMP (Chemical Mechanical Polishing) and the like may be used, for example.

[0072] Subsequently, in a process of FIG. 3D, a resist pattern 300 having opening portions 300x each conforming to a shape of a third metal layer 163 is formed on the upper surface of the second metal layer 162 after the thinning. As the resist pattern 300, for example, a photosensitive dry film resist may be used. The opening portions 300x may be thrilled by a photolithography method, for example.

[0073] Subsequently, in a process of FIG. 4A, an electrolytic plated layer formed of copper or the like is formed on the second metal layer 162 by an electrolytic plating method in which power is fed from the first metal layer 161 and the second metal layer 162, so that a third metal layer 163 is selectively formed in the opening portions 300x. A thickness of the third metal layer 163 is constant and is for example, about 10 to 30 µm. A distance from the upper surface of the insulating layer 15 to an upper surface of the third metal layer 163 is constant, irrespective of the pad diameters and the via-wiring diameters. Subsequently, a surface-treated layer 17 is formed on the upper surface of the third metal layer 163 by the similar electrolytic plating method to the above method. The surface-treated layer 17 is as described above. However, the surface-treated layer 17 may also be formed by an electroless plating method.

[0074] Subsequently, in a process of FIG. 4B, the resist pattern 300 is removed. The resist pattern 300 may be removed using a peeling solution, for example.

[0075] Subsequently, in a process of FIG. 4C, the first metal layer 161 and the second metal layer 162 exposed from the third metal layer 163 are removed by performing an etching process in which the third metal layer 163 is used as a mask. In a case in which the first metal layer 161 and the second metal layer 162 are formed of copper, a hydrogen peroxide/sulfuric acid-based aqueous solution, a sodium persulfate aqueous solution, an ammonium persulfate aqueous solution. By the above processes, a wiring layer 16 having a plurality of pad structures 16P each of which includes a via-wiring 16A and a pad 16B is obtained.

[0076] In the meantime, although not shown, a wiring layer 26 is formed on the other side of an insulating layer 25 between the processes of FIGS. 3A to 4C. The wiring layer 26 includes via-wirings filled in via-holes 25x, and a wiring pattern formed on a lower surface of the insulating layer 25. A material of the wiring layer 26 and a thickness of the wiring pattern are similar to those of the wiring layer 12, for example. The wiring layer 26 is electrically connected to the wiring hoer 24 exposed to bottom portions of the via-holes 25x. The wiring layer 26 may be formed using a variety of wiring forming methods such as a semi-additive method, a subtractive method and the like.

[0077] Subsequently, in a process of FIG. 4D, a solder resist layer 18 is formed on the upper surface of the insulating layer 15 so as to cover the wiring layer 16 and the surface-treated layer 17. Also, a solder resist layer 28 is formed on the lower surface of the insulating layer 25 so as to cover the wiring layer 26. The solder resist layer 18 may be formed by applying a liquid form or paste-like photosensitive epoxy-based insulating resin or acryl-based insulating resin to the upper surface of the insulating. layer 15 so as to cover the wiring layer 16 and the surface-treated layer 17 by a screen printing method, a roll coat method, a spin coat method or the like. Alternatively, for example, the solder resist layer 18 may be formed by laminating a film-like photosensitive epoxy-based insulating resin or acryl-based insulating resin on the upper surface of the insulating layer 15 so as to cover the wiring layer 16 and the surface-treated layer 17. The formation method of a solder resist layer 28 is similar to that of the solder resist layer 19. [0078] Subsequently, by exposing and developing the solder resist layers 18 and 28, the solder resist layer 18 is formed with opening portions 18x configured to expose portions of the upper surface of the surface-treated layer 17 (photolithography method). Also, the solder resist layer 28 is formed with opening portions 28x configured to expose portions of the lower surface of the wiring layer 26 (photolithography method). In the meantime, the opening portions 18x and 28x may be formed by laser processing or blast processing, too. In this case, the photosensitive material may not be used for the solder resist layers 18 and 28. A planar shape of each of the opening portions 18x and 28x is circular, for example. A diameter of each of the opening portions 18xand 28x may be arbitrarily designed in conformity with a connection target (a semiconductor chip, a motherboard and the like). By the above processes, a wiring substrate 1 is completed.

[0079] As described above, in the process of FIG. 3B, the second metal layer 162 is formed thick so as to fill the via-holes 15x and to extend upwardly beyond the upper surface of the insulating layer 15. and in the process of FIG. 3C, the second metal layer 162 is uniformly thinned as a whole. Then, in the processes of FIG. 3D to 4A, the upper surface of the second metal layer 162 after the thinning is formed with the third metal layer 163.

[0080] Thereby, the second metal layer 162 fills the viaholes 15x and extends upwardly beyond the upper surface of the insulating layer 15, so that the upper surface thereof is flat. At this time, the distance from the upper surface of the insulating layer 15 to the upper surface of the second metal layer 162 is constant, irrespective of the pad diameters and the via-wiring diameters. Then, the flat upper surface of the second metal layer 162 is formed with the third metal layer 163 having a constant thickness.

**[0081]** That is, even when the pad structures P of which the pad diameters and the via-wiring diameters are different coexist in the wiring layer 16, the distance from the upper surface of the insulating layer 15 to the upper surface of the third metal layer 163 is constant. In other words, even when the pad structures P of which the pad diameters and the via-wiring diameters are different coexist, the thickness of the wiring layer 16 with respect to the upper surface of the insulating layer 15 is constant.

**[0082]** As a result, when mounting a semiconductor chip on the wiring substrate **1**, intervals between the upper surface of the wiring layer **16** (the upper surface of the third metal layer **163**) and electrode pads of the semiconductor chip are constant. Thereby, an amount of soldering necessary for connection of the wiring substrate **1** and the semiconductor chip is secured, so that a possibility of an open defect is reduced. Also, an excessive amount of soldering does not occur, so that a possibility of a short defect is reduced. Accordingly, it is possible to improve connection reliability of the wiring substrate **1** and the semiconductor chip.

**[0083]** In the above, the case in which the pad structures P of which the pad diameters and the via-wiring diameters are different intentionally (in design) coexist in the wiring layer 16 has been described. However, even in a case in which the pad structures P of which the pad diameters and the via-wiring diameters are different do not coexist in design in the wiring layer 16 and the via-wiring diameters are not uniform due to factors such as manufacturing variations, it is possible to improve connection reliability of the wiring substrate 1 and the semiconductor chip by the similar reasons as described above.

#### Second Embodiment

**[0084]** In a second embodiment, an example of a semiconductor package in which a semiconductor chip is mounted on the wiring substrate of the first embodiment is described. Meanwhile, in the second embodiment, the descriptions of the same constitutional components as the present embodiment described already may be omitted.

**[0085]** FIG. **5** is a sectional view exemplifying a semiconductor package in accordance with the second embodiment. Referring to FIG. **5**, a semiconductor package **100** includes the wiring substrate **1** shown in FIG. **1**A, a semiconductor chip **110**, bumps **130**, and an under-fill resin **140**.

**[0086]** The semiconductor chip **110** has such a structure that a semiconductor integrated circuit (not shown) and the like are formed on a thin semiconductor substrate **111** formed of silicon or the like, for example. The semiconductor substrate **111** is formed with electrode pads **120** electrically connected to the semiconductor integrated circuit (not shown).

[0087] The semiconductor chip 110 is flip-chip mounted on the wiring substrate 1, Specifically, the electrode pads 112 of the semiconductor chip 110 and the surface-treated layer 17 of the wiring substrate 1 are electrically connected by the bumps 130. The under-fill resin 140 is filled between the semiconductor chip 110 and the upper surface of the wiring substrate 1 (the upper surface of the solder resist layer 18). The bumps 130 are, for example, solder bumps. As a material of the solder bump, an alloy including Pb, an alloy of Sn and Cu, an alloy of Sn and Ag, an alloy of Sn, Ag and Cu and the like may be used.

**[0088]** In this way, the semiconductor package **100** in which the semiconductor chip **110** is mounted on the wiring substrate **1** of the first embodiment can be implemented. When mounting the semiconductor chip **110** on the wiring substrate **1**, the connection reliability of the wiring substrate **1** and the semiconductor chip **110** can be improved because the intervals between the upper surface of the surface-treated layer **17** and the electrode pads **112** of the semiconductor chip **110** are constant.

**[0089]** Although the preferred embodiments have been described in detail, the present disclosure is not limited to

the above embodiments and the embodiments can be diversely modified and replaced without departing from the scope defined in the claims.

**[0090]** For example, in the above embodiments, the present disclosure is applied to the wiring substrate including the core layer manufactured by a buildup process. However, the present disclosure can be applied to a coreless wiring substrate manufactured by the buildup process, too. Also, the present disclosure is not limited thereto, and can be applied to a variety of wiring substrates.

What is claimed is

1. A method of manufacturing a wiring, substrate comprising a first wiring layer; an insulating layer formed to cover the first wiring layer; and a second wiring layer connected to the first wiring layer via the insulating layer, the method comprising:

- forming the second wiring layer comprising a plurality of pad structures, each of the pad structures including a via-wiring and a pad for semiconductor chip connection, the via-wiring filled in a via-hole, the via-hole penetrating the insulating layer and formed to expose an upper surface of the first wiring layer, the pad for semiconductor chip connection formed on an upper surface of the insulating layer and integrally formed with the via-wiring,

- wherein the forming of the second wiring layer comprises:

- forming via-holes penetrating the insulating layer and configured to expose the upper surface of the first wiring layer,

- forming continuously a first metal layer on the upper surface of the insulating layer, on inner wall surfaces of the via-holes, and on the upper surface of the first wiring layer exposed in the via-holes,

- forming a second metal layer on the first metal layer by an electrolytic plating method in which power is fed from the first metal layer, the second metal layer filling the via-holes and extending upwardly beyond the upper surface of the insulating layer,

- thinning the entire second metal layer to flatten an upper surface of the second metal layer,

- forming selectively a third metal layer on the upper surface of the thinned second metal layer by the electrolytic plating method, and

removing the first metal layer and second metal layer exposed from the third metal layer by etching in which the third metal layer is used as a mask.

2. The method of manufacturing according to claim 1, wherein thinning the entire second metal layer to flatten the upper surface of the second metal layer includes thinning the second metal layer by buffing so that the upper surface of the second metal layer becomes flat.

3. The method of manufacturing according to claim 1, wherein thinning the entire second metal layer to flatten the upper surface of the second metal layer includes thinning the second metal layer by etching so that the upper surface of the second metal layer becomes flat.

4. The method of manufacturing according to claim 1, wherein the electrolytic plating method performed to form the second metal layer on the first metal layer is stopped at a time at which a thickness of a part of the second metal layer formed outside of the via-hole is substantially uniform over an entire surface.

**5**. The method of manufacturing according to claim **1**, wherein, in forming the second wiring layer, the pad structures are formed to include a first pad structure with a first via diameter and a second pad structure with a second via diameter different from the first via diameter, and so that, at each of the pad structures, a distance from the upper surface of the insulating layer to an upper surface of the third metal layer is constant.

6. The method of manufacturing according to claim 1, wherein, in forming the second wiring layer, at each of the pad structures, a thickness of the third metal layer is constant.

7. The method of manufacturing according to claim 1, wherein, in forming the second wiring layer, at each of the pad structures, a cross-sectional area of the second metal layer is same as a cross-sectional area of the third metal layer, wherein the cross-sectional area of the second metal layer and the cross-sectional area of the third metal layer are areas of a cross-section taken in a direction orthogonal to a direction in which the second metal layer and the third metal layer are stacked.

\* \* \* \* \*