US 20150031180A1

## (19) United States

# (12) Patent Application Publication CHO et al.

# (10) Pub. No.: US 2015/0031180 A1

### (43) **Pub. Date: Jan. 29, 2015**

#### (54) VERTICAL CHANNEL TRANSISTOR WITH SELF-ALIGNED GATE ELECTRODE AND METHOD FOR FABRICATING THE SAME

- (71) Applicant: SK hynix Inc., Gyeonggi-do (KR)

- (72) Inventors: **Heung-Jae CHO**, Gyeonggi-do (KR); **Eui-Seong HWANG**, Gyeonggi-do (KR); **Eun-Shil PARK**, Gyeonggi-do (KR)

- (73) Assignee: SK hynix Inc.

- (21) Appl. No.: 14/512,091

- (22) Filed: Oct. 10, 2014

#### Related U.S. Application Data

- (62) Division of application No. 13/605,550, filed on Sep. 6, 2012, now Pat. No. 8,860,127.

- (30) Foreign Application Priority Data

May 31, 2012 (KR) ...... 10-2012-0058607

#### Publication Classification

(51) Int. Cl. *H01L 29/66* (2006.01) *H01L 29/423* (2006.01)

#### (57) ABSTRACT

A method for fabricating vertical channel transistors includes forming a plurality of pillars which have laterally opposing both sidewalls, over a substrate; forming a gate dielectric layer on both sidewalls of the pillars; forming first gate electrodes which cover any one sidewalls of the pillars and shield gate electrodes which cover the other sidewalls of the pillars and have a height lower than the first gate electrodes, over the gate dielectric layer; and forming second gate electrodes which are connected with upper portions of sidewalls of the first gate electrodes.

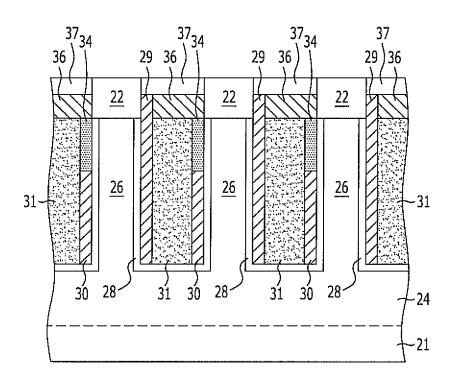

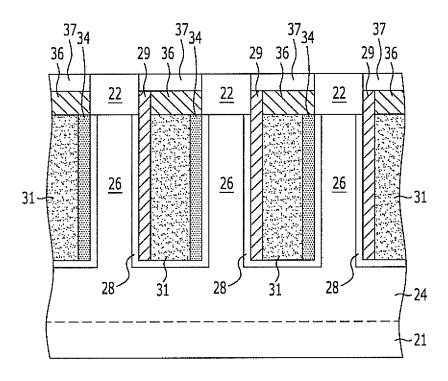

FIG. 1A

FIG. 1B

FIG. 1C

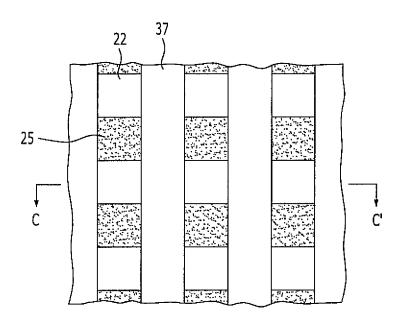

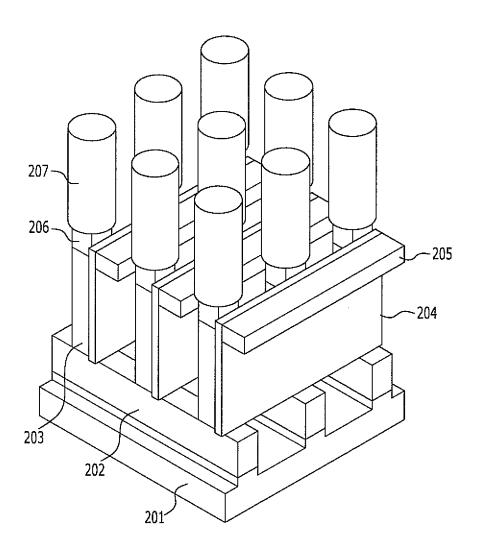

FIG. 2

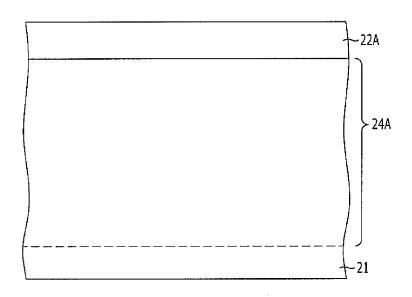

FIG. 3A

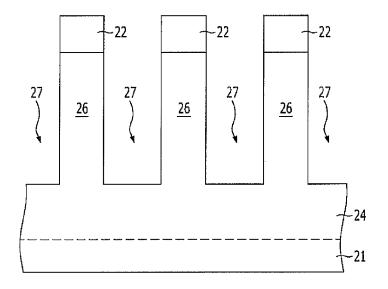

FIG. 3B

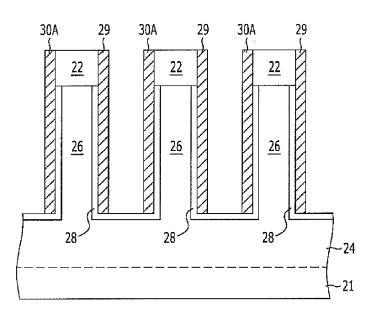

FIG. 3C

FIG. 3D

FIG. 3E

FIG. 3F

FIG. 3G

FIG. 3H

FIG. 3I

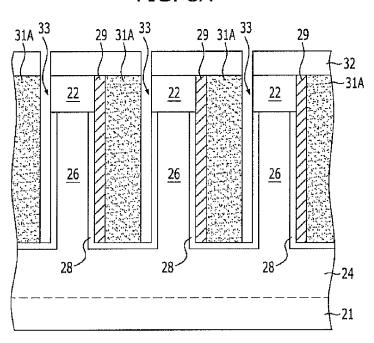

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

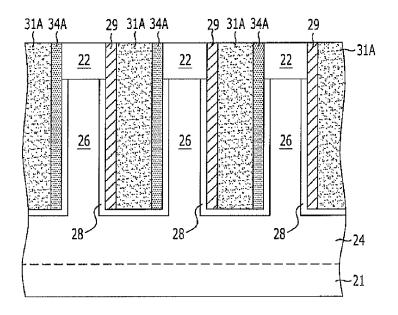

FIG. 4E

31A 33 29 31A 33 29 31A 32 29 31A 32 32 31A 32 31A

FIG. 4F

281

281

-21

28-

FIG. 4G

FIG. 4H

FIG. 4I

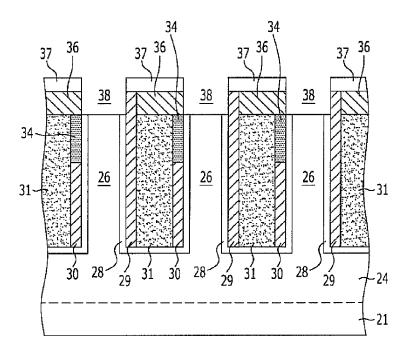

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

FIG. 7

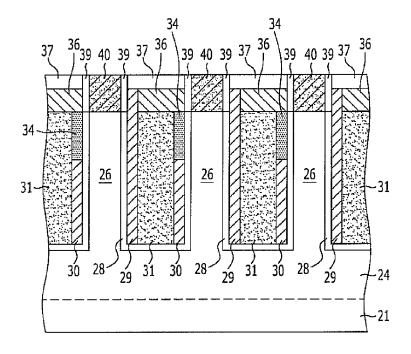

FIG. 8A

FIG. 8B

FIG. 8C

FIG. 8D

FIG. 8E

FIG. 9

FIG. 10

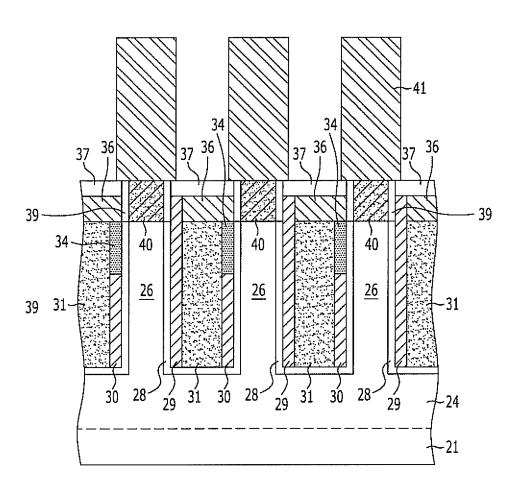

FIG. 11A

FIG. 11B

FIG. 11C

FIG. 11D

FIG. 11E

FIG. 11F

FIG. 11G

FIG. 11H

FIG. 11I

FIG. 11J

FIG. 12A

FIG. 12B

FIG. 12C

FIG. 13

FIG. 14

FIG. 15A

FIG. 15B

FIG. 15C

FIG. 15D

FIG. 15E

FIG. 15F

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 16D

FIG. 16E

FIG. 16F

FIG. 16G

FIG. 16H

FIG. 16I

FIG. 16J

FIG. 16K

## VERTICAL CHANNEL TRANSISTOR WITH SELF-ALIGNED GATE ELECTRODE AND METHOD FOR FABRICATING THE SAME

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims priority of Korean Patent Application No. 10-2012-0058607, filed on May 31, 2012, which is incorporated herein by reference in its entirety.

#### BACKGROUND

[0002] 1. Field

[0003] Exemplary embodiments of the present invention relate to a semiconductor device, and more particularly, to a semiconductor device with a vertical channel transistor and a method for fabricating the same.

[0004] 2. Description of the Related Art

[0005] Most semiconductor devices include transistors. For example, in a memory device such as a DRAM, a memory cell includes a cell transistor such as a MOSFET. In general, in a MOSFET, source/drain regions are formed in a semiconductor substrate, and by this fact, a planar channel is formed between the source region and the drain region. Such a general MOSFET is referred to as a 'planar channel transistor'.

[0006] As improvements in the degree of integration and performance are continuously required in a memory device, a MOSFET fabrication technology has a physical limit. For instance, as the size of a memory cell decreases, the size of a MOSFET decreases, and due to this fact, the channel length of the MOSFET cannot help but decrease. If the channel length of a MOSFET decreases, the characteristics of a memory device are likely to deteriorate due to various problems caused in that data retention characteristics deteriorate.

[0007] In consideration of these problems, a vertical channel transistor has been suggested. The vertical channel transistor (VCT) has a source region and a drain region which are formed in top and bottom portions of a pillar. The pillar serves as a channel, and a vertical gate electrode is formed on the sidewall of the pillar.

[0008] The vertical gate electrode is formed as an all-around gate structure or a double gate structure.

[0009] However, as the critical dimension decreases to 20 nm or below due to high integration, since a gap between pillars is narrow, a gate electrode cannot help but be formed thin. If the gate electrode is formed thin, resistance is likely to increase.

[0010] Also, since the gap between pillars is narrow, if electrodes are deposited to be thicker than a predetermined thickness, it is difficult to separate electrodes. If an overetching process is performed to separate the electrodes, an underlying structure is likely to be etched and attacked in a region with a wide gap (for example, a pad region).

#### **SUMMARY**

[0011] Embodiments of the present invention are directed to a semiconductor device which has a vertical channel transistor capable of reducing the resistance of a vertical gate electrode, and a method for fabricating the same.

[0012] In accordance with an embodiment of the present invention, a method for fabricating vertical channel transistors may include: forming a plurality of pillars which have laterally opposing both sidewalls, over a substrate; forming a gate dielectric layer on both sidewalls of the pillars; forming

first gate electrodes which cover any one sidewalls of the pillars and shield gate electrodes which cover the other sidewalls of the pillars and have a height lower than the first gate electrodes, over the gate dielectric layer; and forming second gate electrodes which are connected with upper portions of sidewalls of the first gate electrodes.

[0013] In accordance with another embodiment of the present invention, a method for fabricating vertical channel transistors may include: forming a plurality of pillars which have laterally opposing both sidewalls, over a substrate; forming a gate dielectric layer on both sidewalls of the pillars; forming first gate electrodes which cover any one sidewalls of both sidewalls of the pillars; and forming second gate electrodes which are connected with upper portions of sidewalls of the first gate electrodes.

[0014] In accordance with yet another embodiment of the present invention, a method for fabricating a semiconductor device may include: forming hard mask layer patterns over a semiconductor substrate; forming bodies by etching the semiconductor substrate using the hard mask layer patterns as an etch barrier; forming buried bit lines in the bodies; etching the hard mask layer patterns and upper portions of the bodies to form pillars which have laterally opposing both sidewalls; forming first gate electrodes on any one sidewalls of both sidewalls of the pillars; forming second gate electrodes which are connected with upper portions of sidewalls of the first gate electrodes; and forming storage nodes which are connected with the pillars.

[0015] In accordance with still another embodiment of the present invention, vertical channel transistors may include: a plurality of pillars vertically formed over a substrate and having laterally opposing both sidewalls; a gate dielectric layer formed on both sidewalls of the pillars; first gate electrodes formed on any one sidewalls of the pillars over the gate dielectric layer; and second gate electrodes, wherein each of the second gate electrode is connected with an upper portion of a corresponding first gate electrode.

[0016] In accordance with yet still another embodiment of the present invention, a semiconductor device may include: vertical channel transistors including a plurality of pillars which are formed on a substrate and have laterally opposing both sidewalls, a gate dielectric layer which is formed on both sidewalls of the pillars, and vertical gate electrodes which are formed on any one sidewalls of the pillars over the gate dielectric layer; capacitors including storage nodes which are connected with top portions of the pillars; and buried bit lines connected with bottom portions of the pillars.

## BRIEF DESCRIPTION OF THE DRAWINGS

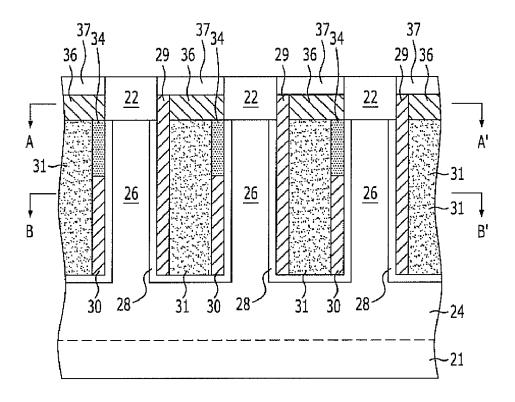

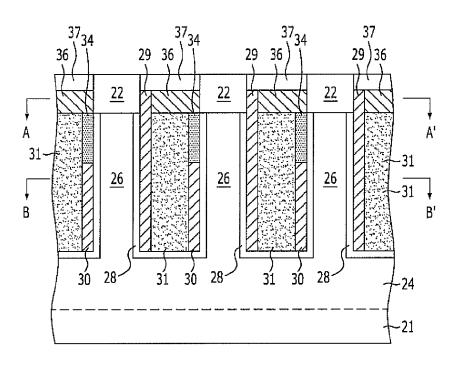

[0017] FIG. 1A is a view illustrating vertical channel transistors in accordance with a first embodiment of the present invention.

[0018] FIG. 1B is a plan view taken along the line A-A' of FIG. 1A.

[0019] FIG. 1C is a plan view taken along the line B-B' of FIG. 1A.

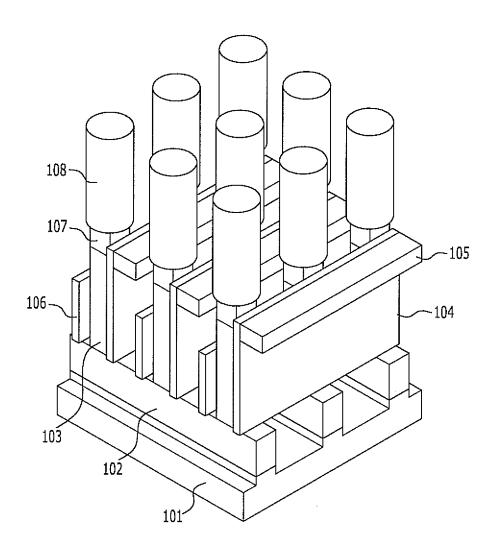

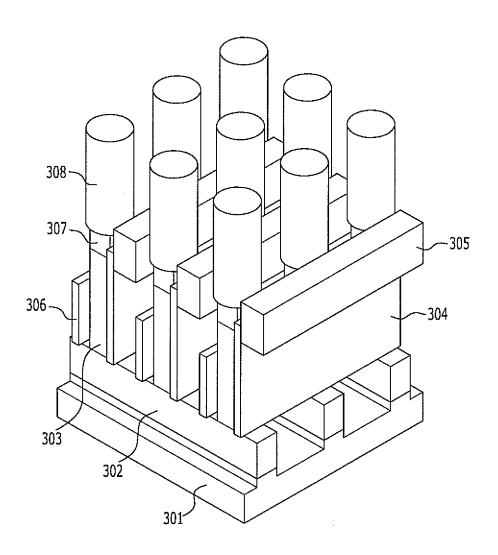

[0020] FIG. 2 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the first embodiment of the present invention are applied.

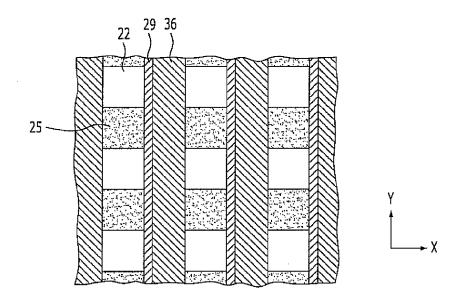

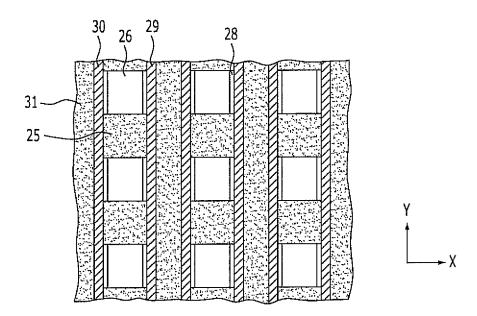

[0021] FIGS. 3A to 3I are plan views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the first embodiment of the present invention

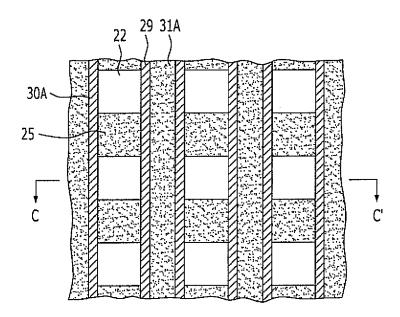

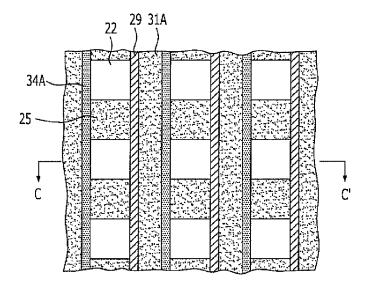

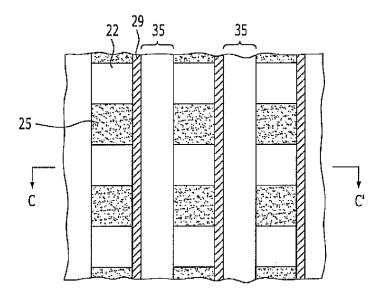

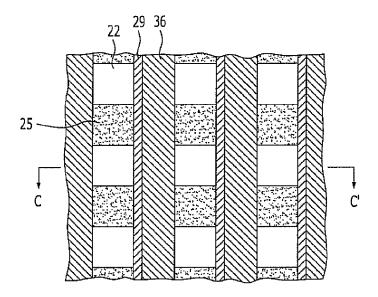

[0022] FIGS. 4A to 4I are cross-sectional views taken along the line C-C' of FIGS. 3A to 3I.

[0023] FIGS. 5A to 5C are views explaining a method for fabricating a capacitor of the semiconductor device to which the vertical channel transistors in accordance with the first embodiment of the present invention are applied.

[0024] FIG. 6 is a view illustrating vertical channel transistors in accordance with a second embodiment of the present invention.

[0025] FIG. 7 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the second embodiment of the present invention are applied.

[0026] FIGS. 8A to 8E are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the second embodiment of the present invention

[0027] FIG. 9 is a view illustrating vertical channel transistors in accordance with a third embodiment of the present invention.

[0028] FIG. 10 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the third embodiment of the present invention are applied.

[0029] FIGS. 11A to 11J are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the third embodiment of the present invention.

[0030] FIGS. 12A to 12C are views explaining a method for fabricating a capacitor of the semiconductor device to which the vertical channel transistors in accordance with the third embodiment of the present invention are applied.

[0031] FIG. 13 is a view illustrating vertical channel transistors in accordance with a fourth embodiment of the present invention.

[0032] FIG. 14 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the fourth embodiment of the present invention are applied.

[0033] FIGS. 15A to 15F are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the fourth embodiment of the present invention.

[0034] FIGS. 16A to 16K are views explaining a method for forming a buried bit line of the semiconductor device to which the vertical channel transistors in accordance with the embodiments of the present invention are applied.

### DETAILED DESCRIPTION

[0035] Exemplary embodiments of the present invention will be described below in more detail with reference to the accompanying drawings. The present invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the present invention to those skilled in the art. Throughout the disclosure, like reference numerals refer to like parts throughout the various figures and embodiments of the present invention.

[0036] The drawings are not necessarily to scale and in some instances, proportions may have been exaggerated in order to clearly illustrate features of the embodiments. When a first layer is referred to as being "on" a second layer or "on"

a substrate, it not only refers to a case where the first layer is formed directly on the second layer or the substrate but also a case where a third layer exists between the first layer and the second layer or the substrate.

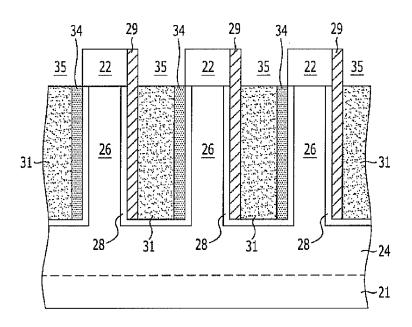

[0037] FIG. 1A is a view illustrating vertical channel transistors in accordance with a first embodiment of the present invention. FIG. 1B is a plan view taken along the line A-A' of FIG. 1A, and FIG. 1C is a plan view taken along the line B-B' of FIG. 1A.

[0038] Referring to FIGS. 1A to 1C, vertical channel transistors in accordance with a first embodiment of the present invention may include pillars 26, first gate electrodes 29, shield gate electrodes 30, and second gate electrodes 36.

[0039] First, a plurality of pillars 26 are formed on a semiconductor substrate 21 to vertically project from the surface of the semiconductor substrate 21. Bodies 24 may be further formed under the pillars 26. The pillars 26 may vertically project from the surfaces of the bodies 24. Hard mask layer patterns 22 may be formed on the pillars 26. The plurality of pillars 26 may have a matrix arrangement. The pillars 26 may be quadrangular pillars each of which has a plurality of sidewalls. The pillars 26 may be arranged to be isolated by a dielectric layer 25 in a first direction Y, and the first and second sidewalls of the pillars 26 laterally opposing each other may be exposed in a second direction X. Each pillar 26 may have a source region, a drain region and a channel region (not numbered). The drain region may be formed in top portion of the pillar 26, and the source region may be formed in bottom portion of the pillar 26. The channel region may be formed between the drain region and the source region. The semiconductor substrate 21, the bodies 24 and the pillars 26 include a silicon-containing substance. For example, a silicon substrate or a silicon-germanium substrate may be used. Accordingly, the pillar 26 may include a semiconductor pillar, a silicon pillar or a silicon-germanium pillar.

[0040] A gate dielectric layer 28 is formed on the first sidewalls and the second sidewalls of the pillars 26. The gate dielectric layer 28 may include a silicon oxide or a high-k substance.

[0041] The first gate electrodes 29 are formed on the gate dielectric layer 28 to cover the first sidewalls of the pillars 26. The shield gate electrodes 30 are formed on the gate dielectric layer 28 to cover the second sidewalls of the pillars 26. The shield gate electrodes 30 are formed to have a height lower than the first gate electrodes 29. The first gate electrodes 29 may be vertical gate electrodes.

[0042] The second gate electrodes 36 which are connected to the upper portions of the sidewalls of the first gate electrodes 29 are formed between the plurality of pillars 26. The second gate electrodes 36 may serve as word lines. The second gate electrodes 36 may have shapes which are buried in the upper portions of the spaces defined between the plurality of pillars 26. For example, the second gate electrodes 36 may be buried between the hard mask layer patterns 22. A first dielectric layer 31 may be formed between the first gate electrodes 29 and the shield gate electrodes 30, and a second dielectric layer 34 may be formed on the shield gate electrodes 30. The first dielectric layer 31 and the second dielectric layer 34 may be recessed by a predetermined depth, and the second gate electrodes 36 may be formed on the first dielectric layer 31 and the second dielectric layer 34 which are recessed. The shield gate electrodes 30 neighboring the second gate electrodes 36 are isolated by the second dielectric layer 34.

[0043] The first gate electrodes 29 and the shield gate electrodes 30 have line-shaped vertical gate structures which extend in the first direction Y. The second gate electrodes 36 have shapes which extend in the first direction Y in the same manner as the first gate electrodes 29. The first gate electrodes 29 and the shield gate electrodes 30 may include a metal nitride or a low resistance metal. For example, the first gate electrodes 29 and the shield gate electrodes 30 may include TiN, TiAlN, WN, TaN, W, Al, Ru, Pt, Au, or the like. The second gate electrodes 36 may include W, Al, Ru, Pt, Au, or the like. The first gate electrodes 29 and the second gate electrodes 36 may be recessed by a predetermined depth, and a capping layer 37 may be additionally formed on the first gate electrodes 29 and the second gate electrodes 36 which are recessed.

[0044] According to FIGS. 1A to 1C, the vertical channel transistors in accordance with the first embodiment of the present invention have double gate structures in which the shield gate electrodes 30 and the first gate electrodes 29 are formed on both sidewalk of the pillars 26. The first gate electrodes 29 become the gate electrodes of vertical channel transistors. Furthermore, as only the first gate electrodes 29 are formed on the sidewalk of the pillars 26, the first gate electrodes 29 may be formed to have a substantial thickness. According to this fact, gate resistance may be reduced. The shield gate electrodes 30 function to shield electric fields by neighbor gates, that is, the neighbor first gate electrodes 29, by which a neighbor gate effect may be minimized.

[0045] FIG. 2 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the first embodiment of the present invention are applied.

[0046] Referring to FIG. 2, vertical channel transistors include first gate electrodes 104, second gate electrodes 105, and pillars 103. Shield gate electrodes 106 are formed on the sidewalls of the pillars 103. As buried bit lines 102 and capacitors 108 are connected to the vertical channel transistors, a semiconductor device such as a DRAM may be realized. The buried bit lines 102 may be electrically connected with the bottom portions of the pillars 103. The buried bit lines 102 may be vertically formed on a semiconductor substrate 101 and may extend in a first direction. The first gate electrodes 104 and the second gate electrodes 105 may extend in a second direction perpendicularly crossing with the first direction. The capacitors 108 may be electrically connected with the top portions of the pillars 103. Contact plugs 107 may be additionally formed between the capacitors 108 and the pillars 103. While not shown, the capacitors 108 may include storage nodes, a dielectric layer and plate nodes. The vertical channel transistors may be applied not only to a memory such as a DRAM but also to a nonvolatile memory such as a flash memory.

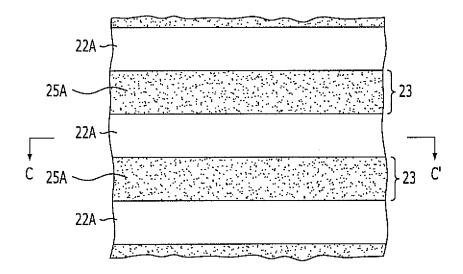

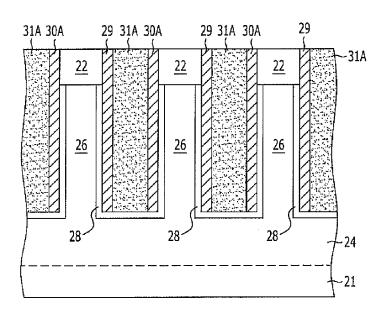

[0047] FIGS. 3A to 3I are plan views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the first embodiment of the present invention. FIGS. 4A to 4I are cross-sectional views taken along the line C-C' of FIGS. 3A to 3I.

[0048] Referring to FIGS. 3A and 4A, hard mask layer patterns 22A are formed on a semiconductor substrate 21. The semiconductor substrate 21 includes a silicon-containing substance. For example, the semiconductor substrate 21 includes a silicon substrate or a silicon-germanium substrate. The hard mask layer patterns 22A include a nitride such as a silicon nitride. Also, the hard mask layer patterns 22A may

include a silicon oxide or amorphous carbon. The hard mask layer patterns 22A may have a multi-layered structure including an oxide or a nitride. For example, the hard mask layer patterns 22A may be stacked in order of a hard mask (HM) nitride and a hard mask oxide. Also, the hard mask layer patterns 22A may be stacked in order of a hard mask nitride, a hard mask oxide, a hard mask silicon oxynitride and hard mask carbon. In the case where a hard mask nitride is included, a pad oxide may be additionally formed between the semiconductor substrate 21 and the hard mask layer patterns 22A. The pad oxide may include a silicon oxide. The hard mask layer patterns 22A may be formed by being patterned using photoresist patterns after forming a hard mask layer. The hard mask layer patterns 22A may be formed to extend in a second direction.

[0049] By etching the semiconductor substrate 21 by a predetermined depth using the hard mask layer patterns 22A as an etch mask, a plurality of bodies 24A are formed. The bodies 24A are separated from one another by first trenches 23. The plurality of bodies 24A are separated from one another by the first trenches 23. The bodies 24A are formed to vertically extend from the surface of the semiconductor substrate 21. The bodies 24A have laterally opposing sidewalls. When viewed from the top, the bodies 24A have linear shapes which are separated from one another by the first trenches 23. For example, the bodies 24A have linear structures which extend in the second direction.

[0050] By forming the bodies 24A as described above, a plurality of structures including the bodies 24A and the hard mask layer patterns 22A are formed on the semiconductor substrate 21. The plurality of structures are separated from one another by the first trenches 23. While not shown, after defining the first trenches 23, buried bit lines (BBL) may be additionally formed in the bodies 24A using a substance such as a metal nitride. This will be described later.

[0051] Next, an interlayer dielectric layer 25A is formed to fill the spaces between the bodies 24A. The interlayer dielectric layer 25A may include an oxide layer such as a silicon oxide. The interlayer dielectric layer 25A may be planarized through CMP (chemical mechanical polishing) or the like until the surfaces of the hard mask layer patterns 22A are exposed.

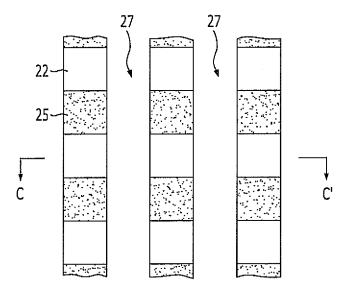

[0052] Referring to FIGS. 3B and 4B, photoresist patterns (not shown) are formed to extend in a direction crossing with the bodies 24A, that is, a first direction. The hard mask layer patterns 22A and the bodies 24A are etched using the photoresist patterns as an etch barrier. According to this fact, a plurality of pillars 26 are formed. When etching the bodies 24A, the interlayer dielectric layer 25A and the hard mask layer patterns 22A may also be etched. Accordingly, the hard mask layer patterns 22A and the interlayer dielectric layer 25A may remain as indicated by the reference numerals 22 and 25, respectively.

[0053] The plurality of pillars 26 are separated from one another by second trenches 27. The bodies 24A remain as indicated by the reference numeral 24, and the pillars 26 are formed on the bodies 24. The plurality of pillars 26 may have a matrix arrangement. Each pillar 26 may have four sidewalls. The sidewalls of each pillar 26 which oppose each other in any one direction (the first direction in which the pillars 26 are separated from one another by the first trenches 23) may contact the interlayer dielectric layer 25. That is to say, the interlayer dielectric layer 25 is formed between the pillars 26 which are arranged in the first direction. The other laterally

opposing sidewalls (hereinafter, referred to as 'first sidewalls and second sidewalls') of the pillars 26 which are arranged in the second direction are exposed by the second trenches 27. The second trenches 27 extend in the direction crossing with the first trenches 23, and may have a depth shallower than the first trenches 23. Accordingly, the pillars 26 are formed in a plural number on each body 24. The plurality of bodies 24 are separated from one another by the first trenches 23, and the plurality of pillars 26 are separated from one another by the second trenches 27.

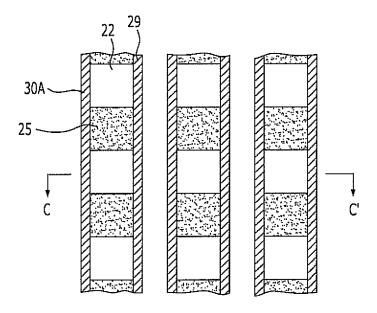

[0054] Referring to FIGS. 3C and 4C, a gate dielectric layer

28 is formed on the first sidewalls and the second sidewalls of the pillars 26. The gate dielectric layer 28 may be formed through oxidation such as thermal oxidation or plasma oxidation. The gate dielectric layer 28 may be formed on the entire surface through chemical vapor deposition (CVD) or atomic layer deposition (ALD). The gate dielectric layer 28 may include a silicon oxide, a high-k substance, or the like. [0055] Next, first gate electrodes 29 and preliminary shield gate electrodes 30A are respectively formed on the first sidewalls and the second sidewalls of the pillars 26 which are formed with the gate dielectric layer 28. The preliminary shield gate electrodes 30A and the first gate electrodes 29 may extend in the first direction. In order to form the preliminary shield gate electrodes 30A and the first gate electrodes 29, an etch-back process may be performed after forming a first conductive layer on the entire surface. According to this fact, the preliminary shield gate electrodes 30A and the first gate electrodes 29 may be simultaneously formed. The first conductive layer may include an oxide, a metal nitride with low reactivity or a low resistance metal. For example, the preliminary shield gate electrodes 30A may include TIN, TiAlN, WN, TaN, W, Al, Ru, Pt, Au, or the like. Hereafter, in the present embodiment, the first conductive layer may be

[0056] Referring to FIGS. 3D and 4D, a first dielectric layer 31A is formed to fill the spaces between the pillars 26 which are formed with the first gate electrodes 29 and the preliminary shield gate electrodes 30A. The first dielectric layer 31A may include an oxide such as a silicon oxide. The first dielectric layer 31A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 22 are exposed.

formed using a titanium nitride (TiN).

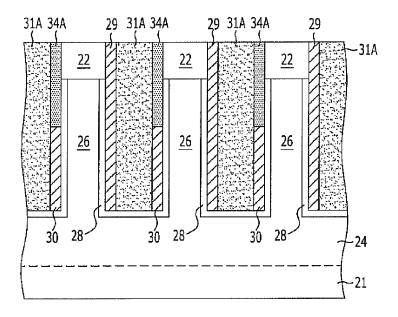

[0057] Referring to FIGS. 3E and 4E, photoresist patterns 32 are formed. The photoresist patterns 32 may have shapes which expose the upper surfaces of the preliminary shield gate electrodes 30A.

[0058] The preliminary shield gate electrodes 30A are etched by a predetermined depth using the photoresist patterns 32 as an etch barrier. According to this fact, shield gate electrodes 30 are formed, and gaps 33 are defined on the shield gate electrodes 30.

[0059] By forming the shield gate electrodes 30 as described above, double gate structures including the shield gate electrodes 30 and the first gate electrodes 29 are formed in a self-aligned manner on the first sidewalls and the second sidewalls of the pillars 26. The shield gate electrodes 30 and the first gate electrodes 29 have a height difference. While the first gate electrodes 29 serve as the gate electrodes of vertical channel transistors, the shield gate electrodes 30 do not serve as gate electrodes. The shield gate electrodes 30 may perform a function of shielding electric fields by the neighbor first gate electrodes 29, by which it is possible to minimize a neighbor gate effect.

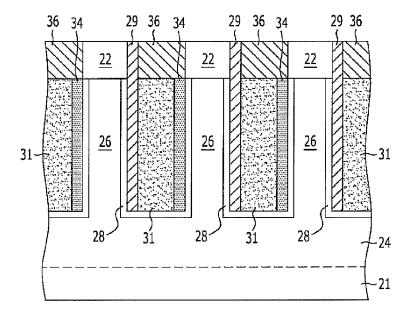

[0060] Referring to FIGS. 3F and 4F, a second dielectric layer 34A is formed to fill the gaps 33. The second dielectric layer 34A may include an oxide such as a silicon oxide. Also, the second dielectric layer 34A may include a nitride such as a silicon nitride. The second dielectric layer 34A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 22 are exposed. The second dielectric layer 34A is formed on the shield gate electrodes 30.

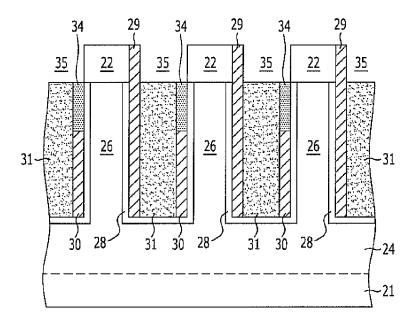

[0061] Referring to FIGS. 3G and 4G, the first dielectric layer 31A and the second dielectric layer 34A are recessed by a predefined depth. According to this fact, recesses 35 are defined. The depth of the recesses 35 may be the same as the height of the hard mask layer patterns 22. The depth of the recesses 35 may be controlled to be lower than the upper surfaces of the pillars 26. The recesses 35 may be defined between neighboring hard mask layer patterns 22. The upper portions of the sidewalls of the first gate electrodes 29 are exposed due to defining the recesses 35, and the first and second dielectric layers 31 and 34 remain on the bottoms of the recesses 35. The recesses 35 are defined such that the shield gate electrodes 30 are not exposed.

[0062] Referring to FIGS. 3H and 4H, second gate electrodes 36 are formed to fill the recesses 35. The second gate electrodes 36 may extend in the first direction. In order to form the second gate electrodes 36, an etch-back process may be performed after forming a second conductive layer on the entire surface. The second conductive layer may include W, Al, Ru, Pt, Au, or the like. Hereafter, the second conductive layer may be formed of tungsten (W). The second gate electrodes 36 may have structures which are buried in the recesses 35.

[0063] The second gate electrodes 36 are connected with the first gate electrodes 29, and the first and second gate electrodes 29 and 36 and the shield gate electrodes  $30\,\mathrm{may}$  be isolated by the first and second dielectric layers 31 and 34.

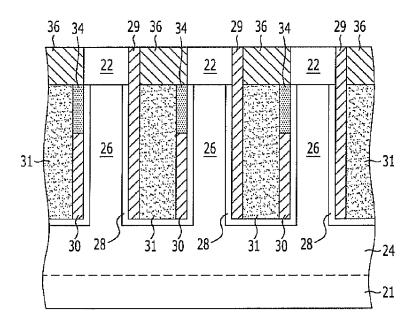

[0064] Referring to FIGS. 3I and 4I, the first and second gate electrodes 29 and 36 are recessed by a predetermined depth. A capping layer 37 is formed to fill recessed regions. The capping layer 37 may include an oxide layer such as a silicon oxide. By forming the capping layer 37 in this way, the first and second gate electrodes 29 and 36 are isolated from surrounding structures.

[0065] FIGS. 5A to 5C are views explaining a method for fabricating a capacitor of the semiconductor device to which the vertical channel transistors in accordance with the first embodiment of the present invention are applied.

[0066] Referring to FIG. 5A, contact holes 38 are defined by removing the hard mask layer patterns 22. Since the interlayer dielectric layer 25 and the capping layer 37 are a silicon oxide and the hard mask layer patterns 22 are a silicon nitride, the hard mask layer patterns 22 may be removed through a wet etching using a phosphoric acid. According to this fact, the contact holes 38 are defined in a self-defined manner by the capping layer 37 and the interlayer dielectric layer 25. The upper surfaces of the pillars 26 are exposed on the bottoms of the contact holes 38.

[0067] Referring to FIG. 5B, spacers 39 are formed to surround the sidewalls of the contact holes 38. The spacers 39 may include an oxide such as a silicon oxide. In order to form the spacers 39, an etch-back process may be performed after depositing a silicon oxide.

[0068] Contact plugs 40 are formed to be buried in the contact holes 38. The contact plugs 40 may include a polysilicon, a metal or the like. For example, after depositing a

polysilicon to fill the contact holes **38**, a planarization process may be performed. The spacers **39** surround the sidewalls of the contact plugs **40**. While not shown, ion implantation for forming sources/drains may be carried out before forming the contact plugs **40**.

[0069] Referring to FIG. 5C, storage nodes 41 of capacitors are formed on the contact plugs 40. The storage nodes 41 may have pillar shapes. In another embodiment, the storage nodes 41 may have cylinder shapes. As a method for forming the storage nodes 41, well-known methods may be adopted. For example, after forming a mold layer (not shown), open parts are formed by etching the mold layer, and the storage nodes 41 are formed in the open parts. Then, the mold layer is removed through a full dip-out process.

[0070] While not shown, supporters for supporting the outer walls of the storage nodes 41 may be additionally formed. For example, a substance for supporters is formed on the mold layer, and supporters may be formed by partially etching the substance for supporters before performing the full dip-out process. Furthermore, a dielectric layer and plate nodes may be additionally formed on the storage nodes 41.

[0071] FIG. 6 is a view illustrating vertical channel transistors in accordance with a second embodiment of the present invention.

[0072] Referring to FIG. 6, vertical channel transistors in accordance with a first embodiment of the present invention may include pillars 26, first gate electrodes 29, and second gate electrodes 36.

[0073] First, a plurality of pillars 26 are formed on a semiconductor substrate 21 to vertically project from the surface of the semiconductor substrate 21. Bodies 24 may be further formed under the pillars 26. The pillars 26 may vertically project from the surfaces of the bodies 24. Hard mask layer patterns 22 may be formed on the pillars 26. The plurality of pillars 26 may have a matrix arrangement. The pillars 26 may be quadrangular pillars each of which has a plurality of sidewalls. The pillars 26 may be arranged to be isolated by an interlayer dielectric layer in a first direction Y, and the first and second sidewalls of the pillars 26 laterally opposing each other may be exposed in a second direction X. Each pillar 26 may have a source region, a drain region and a channel region (not numbered). The drain region may be formed in top portion of the pillar 26, and the source region may be formed in bottom portion of the pillar 26. The channel region may be formed between the drain region and the source region. The semiconductor substrate 21, the bodies 24 and the pillars 26 include a silicon-containing substance. For example, a silicon substrate or a silicon-germanium substrate may be used. Accordingly, the pillar 26 may include a semiconductor pillar, a silicon pillar or a silicon-germanium pillar.

[0074] A gate dielectric layer 28 is formed on the first sidewalls and the second sidewalls of the pillars 26. The gate dielectric layer 28 may include a silicon oxide or a high-k substance.

[0075] The first gate electrodes 29 are formed on the gate dielectric layer 28 to cover the first sidewalls of the pillars 26. The first gate electrodes 29 are vertical gate electrodes. The first gate electrodes 29 are not formed on the second sidewalls of the pillars 26. Also, unlike the first embodiment, shield gate electrodes to cover the second sidewalls are not formed.

[0076] The second gate electrodes 36 which are connected to the upper portions of the sidewalls of the first gate electrodes 29 are formed between the plurality of pillars 26. The second gate electrodes 36 may serve as word lines. The sec-

ond gate electrodes 36 may have shapes which are buried in the upper portions of the spaces defined between the plurality of pillars 26. For example, the second gate electrodes 36 may be buried between the hard mask layer patterns 22. A first dielectric layer 31 and a second dielectric layer 34 may be formed between the first gate electrodes 29 and adjoining pillars 26. The first dielectric layer 31 and the second dielectric layer 34 may be recessed by a predetermined depth, and the second gate electrodes 36 may be formed on the first dielectric layer 31 and the second dielectric layer 34 which are recessed

[0077] The first gate electrodes 29 have line-shaped vertical gate structures which extend in the first direction Y. The second gate electrodes 36 have shapes which extend in the first direction Y in the same manner as the first gate electrodes 29. The first gate electrodes 29 may include a metal nitride or a low resistance metal. For example, the first gate electrodes 29 may include TiN, TiAlN, WN, TaN, W, Al, Ru, Pt, Au, or the like. The second gate electrodes 36 may include W, Al, Ru, Pt, Au, or the like. The first gate electrodes 29 and the second gate electrodes 36 may be recessed by a predetermined depth, and a capping layer 37 may be additionally formed on the first gate electrodes 29 and the second gate electrodes 36 which are recessed.

[0078] According to FIG. 6, the vertical channel transistors in accordance with the second embodiment of the present invention have single gate structures in which the first gate electrodes 29 are formed on only one sidewalls of the pillars 26. The first gate electrodes 29 become the gate electrodes of vertical channel transistors. Furthermore, as only the first gate electrodes 29 are formed on the sidewalls of the pillars 26, the first gate electrodes 29 may be formed to have a substantial thickness. According to this fact, gate resistance may be reduced. In particular, because only the first gate electrodes 29 are formed without forming shield gate electrodes, a neighbor gate effect may be originally prevented.

[0079] FIG. 7 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the second embodiment of the present invention are applied.

[0080] Referring to FIG. 7, vertical channel transistors include first gate electrodes 204, second gate electrodes 205, and pillars 203. As buried bit lines 202 and capacitors 207 are connected to the vertical channel transistors, a semiconductor device such as a DRAM may be realized. The buried bit lines 202 may be electrically connected with the bottom portions of the pillars 203. The buried bit lines 202 may be vertically formed on a semiconductor substrate 201 and may extend in a first direction. The first gate electrodes 204 and the second gate electrodes 205 may extend in a second direction perpendicularly crossing with the first direction. The capacitors 207 may be electrically connected with the top portions of the pillars 203. Contact plugs 206 may be additionally formed between the capacitors 207 and the pillars 203. While not shown, the capacitors 207 may include storage nodes, a dielectric layer and plate nodes. The vertical channel transistors may be applied not only to a memory such as a DRAM but also to a nonvolatile memory such as a flash memory.

[0081] FIGS. 8A to 8E are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the second embodiment of the present invention. Unlike the first embodiment, when defining gaps, shield

gate electrodes are entirely removed. Hereinbelow, reference will be made to FIGS. **4**A to **4**D for processes before defining the gaps.

[0082] Referring to FIG. 8A, photoresist patterns 32 are formed. The photoresist patterns 32 may have shapes which expose the upper surfaces of the preliminary shield gate electrodes 30A.

[0083] The exposed preliminary shield gate electrodes 30A are entirely removed using the photoresist patterns 32 as an etch barrier. According to this fact, gaps 33 are defined. Unlike the first embodiment, in the second embodiment, as the preliminary shield gate electrodes 30A are entirely removed, shield gate electrodes are not formed. The preliminary shield gate electrodes 30A removed in this way may be sacrificial gate electrodes.

[0084] By entirely removing the preliminary shield gate electrodes 30A as described above, only the first gate electrodes 29 remain on the one sidewalls of the pillars 26.

[0085] The first gate electrodes 29 serve as the gate electrodes of the vertical channel transistors. By not forming shield gate electrodes, a neighbor gate effect by neighbor gates may be originally prevented.

[0086] Referring to FIG. 8B, a second dielectric layer 34A is formed to fill the gaps 33. The second dielectric layer 34A may include an oxide such as a silicon oxide. Also, the second dielectric layer 34A may include a nitride such as a silicon nitride. The second dielectric layer 34A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 22 are exposed.

[0087] Referring to FIG. 8C, the first dielectric layer 31A and the second dielectric layer 34A are recessed by a predefined depth. According to this fact, recesses 35 are defined. The depth of the recesses 35 may be the same as the height of the hard mask layer patterns 22. The depth of the recesses 35 may be controlled to be lower than the upper surfaces of the pillars 26. The recesses 35 may be defined between neighboring hard mask layer patterns 22. The upper portions of the sidewalls of the first gate electrodes 29 are exposed due to defining the recesses 35, and the first and second dielectric layers 31 and 34 remain on the bottoms of the recesses 35.

[0088] Referring to FIG. 8D, second gate electrodes 36 are formed to fill the recesses 35. The second gate electrodes 36 may extend in the first direction. In order to form the second gate electrodes 36, an etch-back process may be performed after forming a second conductive layer on the entire surface. The second conductive layer may include W, Al, Ru, Pt, Au, or the like. The second conductive layer may be formed of tungsten (W). The second gate electrodes 36 may have structures which are buried in the recesses 35.

[0089] The second gate electrodes 36 are connected with the upper portions of the sidewalls of the first gate electrodes 29, and the first and second gate electrodes 29 and 36 and adjoining pillars 26 may be isolated by the first and second dielectric layers 31 and 34.

[0090] Referring to FIG. 8E, the first and second gate electrodes 29 and 36 are recessed by a predetermined depth. A capping layer 37 is formed to fill recessed regions. The capping layer 37 may include an oxide layer such as a silicon oxide. By forming the capping layer 37 in this way, the first and second gate electrodes 29 and 36 are isolated from surrounding structures.

[0091] Contact plugs and capacitors are subsequently formed. Reference may be made to FIGS. 5A to 5C for a method for forming the contact plugs and the capacitors.

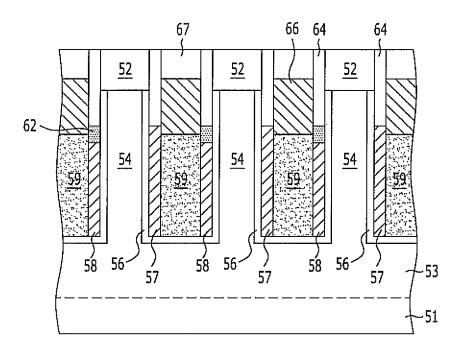

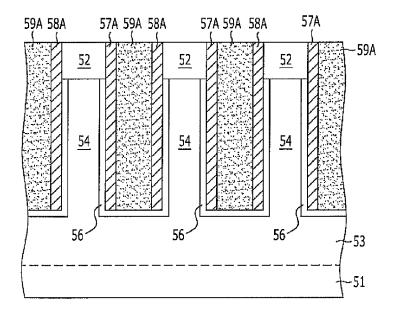

[0092] FIG. 9 is a view illustrating vertical channel transistors in accordance with a third embodiment of the present invention.

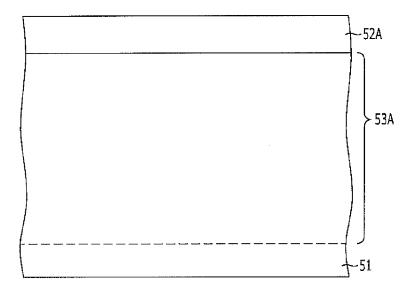

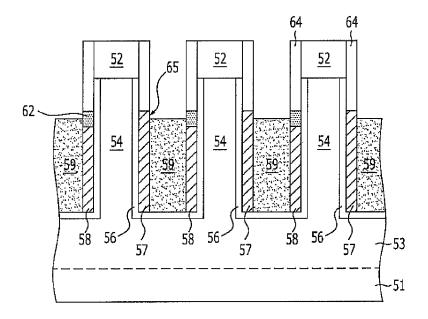

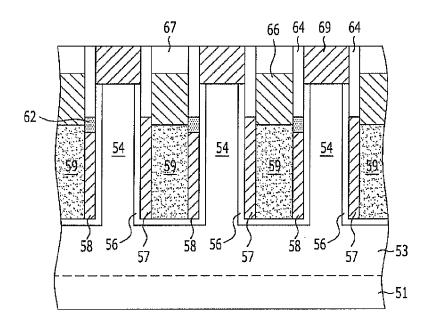

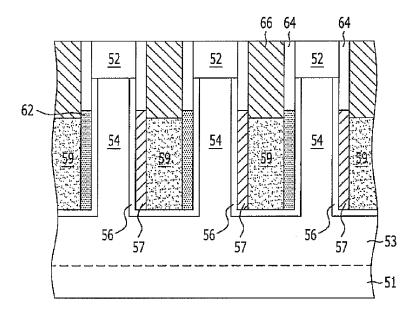

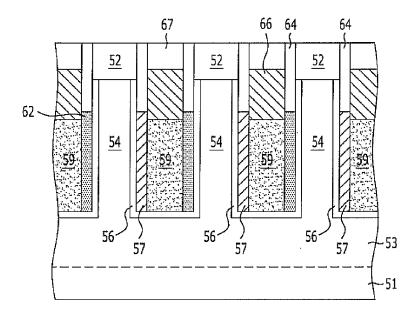

[0093] Referring to FIG. 9, vertical channel transistors in accordance with a third embodiment of the present invention may include pillars 54, first gate electrodes 57, shield gate electrodes 58, and second gate electrodes 66.

[0094] First, a plurality of pillars 54 are formed on a semiconductor substrate 51 to vertically project from the surface of the semiconductor substrate 51. Bodies 53 may be further formed under the pillars 54. The pillars 54 may vertically project from the surfaces of the bodies 53. The plurality of pillars 54 may have a matrix arrangement. The pillars 54 may be quadrangular pillars each of which has a plurality of sidewalls. The pillars 54 may be arranged to be isolated by an interlayer dielectric layer (not shown) in a first direction Y, and the first and second sidewalls of the pillars 54 laterally opposing each other may be exposed in a second direction X. Each pillar 54 may have a source region, a drain region and a channel region (not numbered). The drain region may be formed in top portion of the pillar 54, and the source region may be formed in bottom portion of the pillar 54. The channel region may be formed between the drain region and the source region. The semiconductor substrate 51, the bodies 53 and the pillars 54 include a silicon-containing substance. For example, a silicon substrate or a silicon-germanium substrate may be used. Accordingly, the pillar 54 may include a semiconductor pillar, a silicon pillar or a silicon-germanium pillar. [0095] A gate dielectric layer 56 is formed on the first sidewalls and the second sidewalls of the pillars 54. The gate dielectric layer 56 may include a silicon oxide or a high-k substance.

[0096] The first gate electrodes 57 are formed on the gate dielectric layer 56 to cover the first sidewalls of the pillars 54. The first gate electrodes 57 may be vertical gate electrodes. The shield gate electrodes 58 are formed to cover the second sidewalls of the pillars 54. The shield gate electrodes 58 may be formed to have a height lower than the first gate electrodes 57. Also, the first gate electrodes 57 and the shield gate electrodes 58 may be formed to have heights lower than the height of the pillars 54.

[0097] The second gate electrodes 66 which are connected to the upper portions of the sidewalls of the first gate electrodes 57 are formed between the plurality of pillars 54. The second gate electrodes 66 may serve as word lines. The second gate electrodes 66 may have shapes which are buried in the upper portions of the spaces defined between the plurality of pillars 54. For example, the second gate electrodes 66 may be buried between hard mask layer patterns 52. A first dielectric layer 59 may be formed between the first gate electrodes 57 and the shield gate electrodes 58, and a second dielectric layer 62 may be formed on the shield gate electrodes 58. The first dielectric layer 59 and the second dielectric layer 62 may be recessed by predetermined depths, and the second gate electrodes 66 may be formed on the first dielectric layer 59 which is recessed. The shield gate electrodes 58 neighboring the second gate electrodes 66 are isolated by the second dielectric layer 62. Spacers 64 may be formed on the second dielectric layer 62 and the first gate electrodes 57. The second gate electrodes 66 may be isolated from the surrounding structures by the spacers 64. A capping layer 67 may be additionally formed on the second gate electrodes 66.

[0098] The first gate electrodes 57 and the shield gate electrodes 58 have line-shaped vertical gate structures which

extend in the first direction Y. The second gate electrodes 66 have shapes which extend in the first direction Y in the same manner as the first gate electrodes 57. The first gate electrodes 57 and the shield gate electrodes 58 may include a metal nitride or a low resistance metal. For example, the first gate electrodes 57 and the shield gate electrodes 58 may include TiN, TiAlN, WN, TaN, W, Al, Ru, Pt, Au, or the like. The second gate electrodes 66 may include W, Al, Ru, Pt, Au, or the like.

[0099] According to FIG. 9, the vertical channel transistors in accordance with the third embodiment of the present invention have double gate structures in which the shield gate electrodes 58 and the first gate electrodes 57 are formed on both sidewalls of the pillars 54. The first gate electrodes 57 become the gate electrodes of vertical channel transistors. Furthermore, as only the first gate electrodes 57 are formed on the sidewalls of the pillars 54, the first gate electrodes 57 may be formed to have a substantial thickness. According to this fact, gate resistance may be reduced. The shield gate electrodes 58 function to shield electric fields by neighbor gates, by which a neighbor gate effect may be minimized.

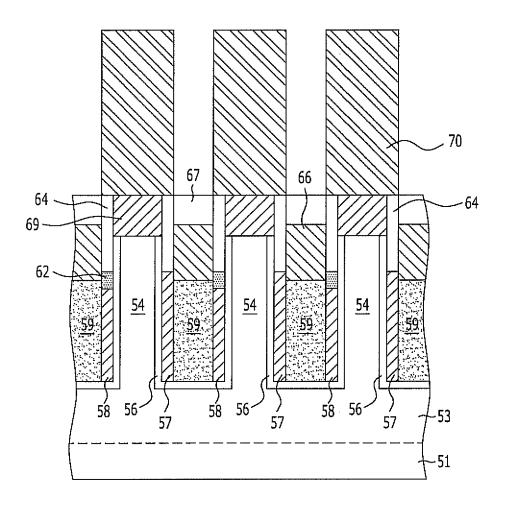

[0100] FIG. 10 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the third embodiment of the present invention are applied.

[0101] Referring to FIG. 10, vertical channel transistors include first gate electrodes 304, second gate electrodes 305, and pillars 303. Shield gate electrodes 306 are formed on the sidewalls of the pillars 303. As buried bit lines 302 and capacitors 308 are connected to the vertical channel transistors, a semiconductor device such as a DRAM may be realized. The buried bit lines 302 may be electrically connected with the bottom portions of the pillars 303. The buried bit lines 302 may be vertically formed on a semiconductor substrate 301 and may extend in a first direction. The first gate electrodes 304 and the second gate electrodes 305 may extend in a second direction perpendicularly crossing with the first direction. The capacitors 308 may be electrically connected with the top portions of the pillars 303. Contact plugs 307 may be additionally formed between the capacitors 308 and the pillars 303. While not shown, the capacitors 308 may include storage nodes, a dielectric layer and plate nodes. The vertical channel transistors may be applied not only to a memory such as a DRAM but also to a nonvolatile memory such as a flash memory.

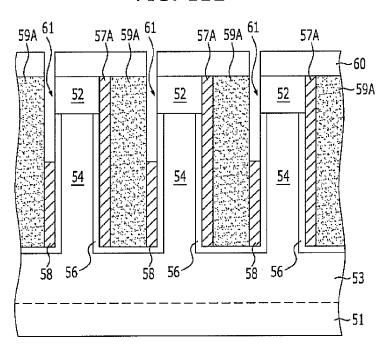

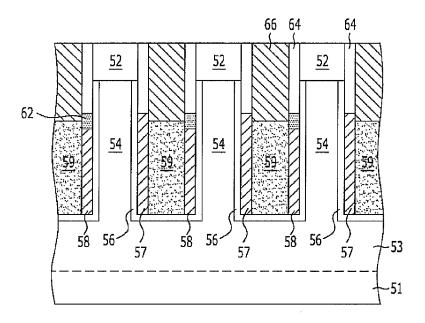

[0102] FIGS. 11A to 11J are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the third embodiment of the present invention.

[0103] Referring to FIG. 11A, hard mask layer patterns 52A are formed on a semiconductor substrate 51. The semiconductor substrate 51 includes a silicon-containing substance. For example, the semiconductor substrate 51 includes a silicon substrate or a silicon-germanium substrate. The hard mask layer patterns 52A include a nitride such as a silicon nitride. Also, the hard mask layer patterns 52A may include a silicon oxide or amorphous carbon. The hard mask layer patterns 52A may have a multi-layered structure including an oxide or a nitride. For example, the hard mask layer patterns 52A may be stacked in order of a hard mask (HM) nitride and a hard mask oxide. Also, the hard mask layer patterns 52A may be stacked in order of a hard mask nitride, a hard mask oxide, a hard mask silicon oxynitride and hard mask carbon. In the case where a hard mask nitride is included, a pad oxide

may be additionally formed between the semiconductor substrate 51 and the hard mask layer patterns 52A. The pad oxide may include a silicon oxide. The hard mask layer patterns 52A may be formed by being patterned using photoresist patterns after forming a hard mask layer. The hard mask layer patterns 52A may be formed to extend in a second direction.

[0104] By etching the semiconductor substrate 51 by a predetermined depth using the hard mask layer patterns 52A as an etch mask, a plurality of bodies 53A are formed. The bodies 53A are separated from one another by first trenches (not shown). The plurality of bodies 53A are separated from one another by the first trenches. The bodies 53A are formed to vertically extend from the surface of the semiconductor substrate 51. The bodies 53A have laterally opposing sidewalls. When viewed from the top, the bodies 53A have linear shapes which are separated from one another by the first trenches. For example, the bodies 53A have linear structures which extend in the second direction. Reference may be made to the first trenches 23 of FIG. 3A for the first trenches.

[0105] By forming the bodies 53A as described above, a plurality of structures including the bodies 53A and the hard mask layer patterns 52A are formed on the semiconductor substrate 51. The plurality of structures are separated from one another by the first trenches. While not shown, after defining the first trenches, buried bit lines (BBL) may be additionally formed in the bodies 53A using a substance such as a metal nitride. This will be described later.

[0106] Next, an interlayer dielectric layer (not shown) is formed to fill the spaces between the bodies 53A. The interlayer dielectric layer may include an oxide layer such as a silicon oxide. The interlayer dielectric layer may be planarized through CMP (chemical mechanical polishing) or the like until the surfaces of the hard mask layer patterns 22A are exposed. Reference may be made to the interlayer dielectric layer 25A of FIG. 3A for the interlayer dielectric layer.

[0107] Referring to FIG. 11B, photoresist patterns (not shown) are formed to extend in a direction crossing with the bodies 53A, that is, a first direction. The hard mask layer patterns 52A and the bodies 53A are etched using the photoresist patterns as an etch barrier. According to this fact, a plurality of pillars 54 are formed. When etching the bodies 53A, the hard mask layer patterns 52A may also be etched. Accordingly, the hard mask layer patterns 52A may remain as indicated by the reference numeral 52.

[0108] The plurality of pillars 54 are separated from one another by second trenches 55. The bodies 53A remain as indicated by the reference numeral 53, and the pillars 54 are formed on the bodies 53. The plurality of pillars 54 may have a matrix arrangement. Each pillar 54 may have four sidewalls. The sidewalls of each pillar 54 which oppose each other in any one direction (the first direction in which the pillars 54 are separated from one another by the first trenches) may contact the interlayer dielectric layer. That is to say, the interlayer dielectric layer is formed between the pillars 54 which are arranged in the first direction. The other laterally opposing sidewalls (hereinafter, referred to as 'first sidewalls and second sidewalls') of the pillars 54 which are arranged in the second direction are exposed by the second trenches 55. The second trenches 55 extend in the direction crossing with the first trenches, and may have a depth shallower than the first trenches. Accordingly, the pillars 54 are formed in a plural number on each body 53. The plurality of bodies 53 are separated from one another by the first trenches, and the plurality of pillars **54** are separated from one another by the second trenches **55**.

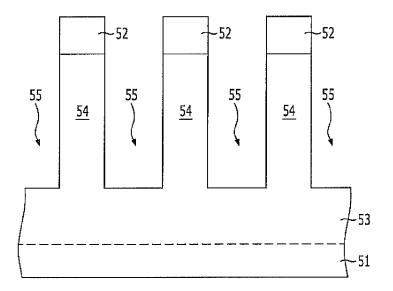

[0109] Referring to FIG. 11C, a gate dielectric layer 56 is formed on the first sidewalls and the second sidewalls of the pillars 54. The gate dielectric layer 56 may be formed through oxidation such as thermal oxidation or plasma oxidation. The gate dielectric layer 56 may be formed on the entire surface through chemical vapor deposition (CVD) or atomic layer deposition (ALD). The gate dielectric layer 56 may include a silicon oxide, a high-k substance, or the like.

[0110] Next, preliminary first gate electrodes 57A and preliminary shield gate electrodes 58A are respectively formed on the first sidewalls and the second sidewalls of the pillars 54 which are formed with the gate dielectric layer 56. The preliminary shield gate electrodes 58A and the preliminary first gate electrodes 57A may extend in the first direction. In order to form the preliminary shield gate electrodes 58A and the preliminary first gate electrodes 57A, an etch-back process may be performed after forming a first conductive layer on the entire surface. According to this fact, the preliminary shield gate electrodes 58A and the preliminary first gate electrodes 57A may be simultaneously formed. The first conductive layer may include an oxide, a metal nitride with low reactivity or a low resistance metal. For example, the preliminary shield gate electrodes 58A may include TIN, TiAIN, WN, TaN, W, Al, Ru, Pt, Au, or the like. Hereafter, in the present embodiment, the first conductive layer may be formed using a titanium nitride (TiN).

[0111] Referring to FIG. 11D, a first dielectric layer 59A is formed to fill the spaces between the pillars 54 which are formed with the preliminary first gate electrodes 57A and the preliminary shield gate electrodes 58A. The first dielectric layer 59A may include an oxide such as a silicon oxide. The first dielectric layer 59A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 52 are exposed.

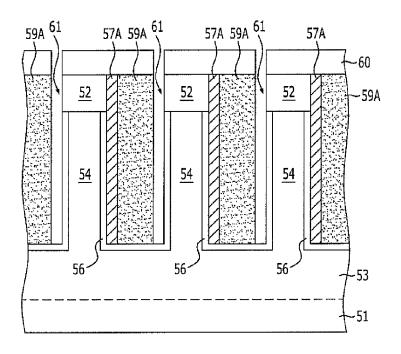

[0112] Referring to FIG. 11E, photoresist patterns 60 are formed. The photoresist patterns 60 may have shapes which expose the upper surfaces of the preliminary shield gate electrodes 58A.

[0113] The preliminary shield gate electrodes 58A are etched by a predetermined depth using the photoresist patterns 60 as an etch barrier. According to this fact, shield gate electrodes 58 are formed, and gaps 61 are defined on the shield gate electrodes 58.

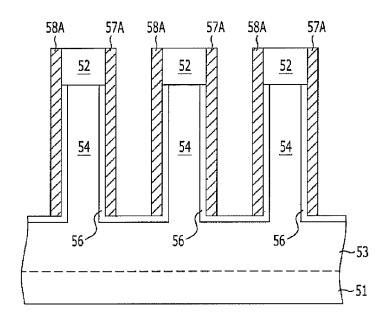

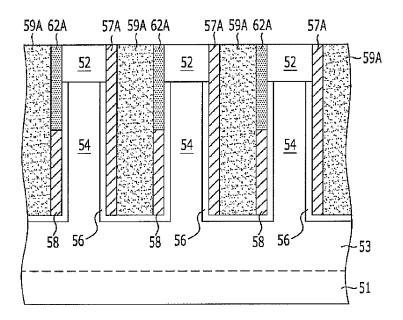

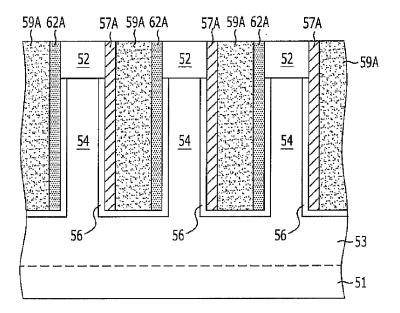

[0114] Referring to FIG. 11F, a second dielectric layer 62A is formed to fill the gaps 61. The second dielectric layer 62A may include an oxide such as a silicon oxide. Also, the second dielectric layer 62A may include a nitride such as a silicon nitride. The second dielectric layer 62A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 52 are exposed. The second dielectric layer 62A is formed on the shield gate electrodes 58.

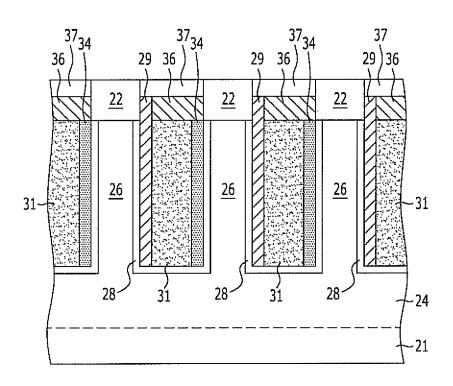

[0115] Referring to FIG. 11G, the preliminary first gate electrodes 57A, the first dielectric layer 59A and the second dielectric layer 62A are recessed by a predefined depth. According to this fact, first recesses 63 are defined. The depth of the first recesses 63 may be lower than the upper surfaces of the pillars 54. First gate electrodes 57 are formed by the first recesses 63, and the upper surfaces of the first gate electrodes 57 are exposed. First and second dielectric layers 59 and 62 remain on the bottoms of the first recesses 63. The first recesses 63 are defined such that the shield gate elec-

trodes **58** are not exposed. In other wards, the second dielectric layer **62** remains by a predetermined thickness on the shield gate electrodes **58**.

[0116] By forming the first gate electrodes 57 as described above, double gate structures including the shield gate electrodes 58 and the first gate electrodes 57 are formed in a self-aligned manner on the first sidewalls and the second sidewalls of the pillars 54. The shield gate electrodes 58 and the first gate electrodes 57 have a height difference. The shield gate electrodes 58 have a height lower than the first gate electrodes 57. While the first gate electrodes 57 serve as the gate electrodes of vertical channel transistors, the shield gate electrodes 58 do not serve as gate electrodes. The shield gate electrodes 58 may perform a function of shielding electric fields by the neighbor first gate electrodes 57, by which it is possible to minimize a neighbor gate effect.

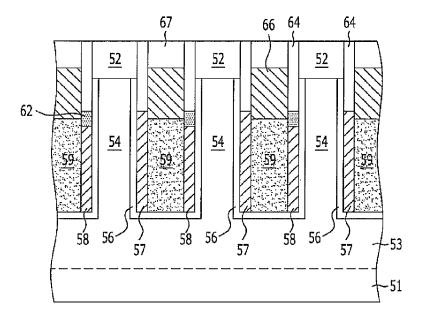

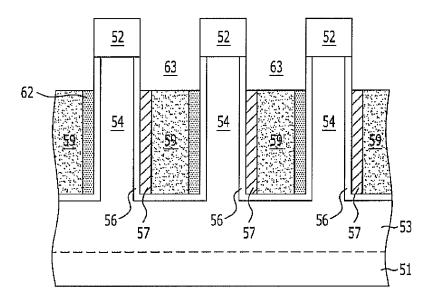

[0117] Referring to FIG. 11H, spacers 64 are formed on both sidewalls of the first recesses 63. The spacers 64 may be formed using an oxide such as a silicon oxide. For example, the spacers 64 are formed by depositing a silicon oxide on the entire surface and then performing etch-back. The thickness of the spacers 64 may be the same as the thickness of the underlying first gate electrodes 57.

[0118] The first dielectric layer 59 is partially etched back to be self-aligned with the spacers 64. By this fact, the upper portions of the sidewalls of the first gate electrodes 57 are exposed. When etching back the first dielectric layer 59, a depth is controlled such that the shield gate electrodes 58 are not exposed. Namely, the second dielectric layer 62 remains on the shield gate electrodes 58.

[0119] By etching back the first dielectric layer 59 using the spacers 64 in this way, the upper portions of the sidewalls of the first gate electrodes 57 are exposed as indicated by the reference numeral 65.

[0120] Referring to FIG. 111, second gate electrodes 66 are formed to fill the spaces defined on the first dielectric layer 59. The second gate electrodes 66 may extend in the first direction. In order to form the second gate electrodes 66, an etchback process may be performed after forming a second conductive layer on the entire surface. The second conductive layer may include W, Al, Ru, Pt, Au, or the like. Hereafter, the second conductive layer may be formed of tungsten (W). The second gate electrodes 66 may have buried structures.

[0121] The second gate electrodes 66 are connected with the first gate electrodes 57, and may be isolated from the shield gate electrodes 58 by the first and second dielectric layers 59 and 62.

[0122] As can be readily seen from the above descriptions, the vertical channel transistors in accordance with the third embodiment of the present invention has a double gate structure in which the first gate electrodes 57 and the shield gate electrodes 58 are formed on both sidewalls of the pillars 54. [0123] Referring to FIG. 11J, the surfaces of the second

[0123] Referring to FIG. 11J, the surfaces of the second gate electrodes 66 are recessed.

[0124] A capping layer 67 is formed to fill the spaces which are defined on the recessed second gate electrodes 66. The capping layer 67 may include an oxide layer such as a silicon oxide. By forming the capping layer 67 in this way, the first and second gate electrodes 57 and 58 are isolated from surrounding structures.

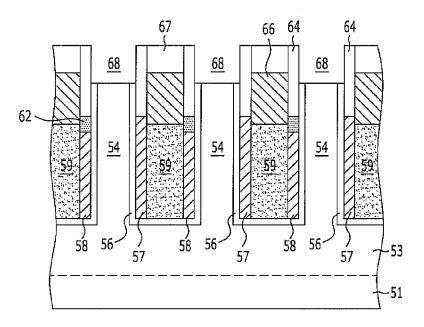

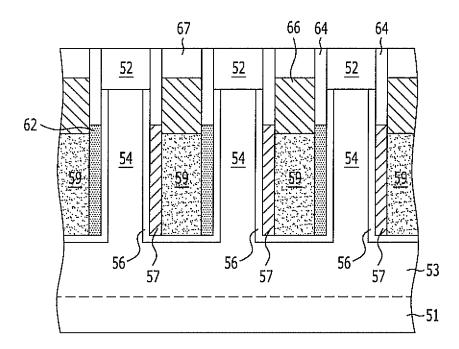

[0125] FIGS. 12A to 12C are views explaining a method for fabricating a capacitor of the semiconductor device to which the vertical channel transistors in accordance with the third embodiment of the present invention are applied.

[0126] Referring to FIG. 12A, contact holes 68 are defined by removing the hard mask layer patterns 52. Since the spacers 64 and the capping layer 67 are a silicon oxide and the hard mask layer patterns 52 are a silicon nitride, the hard mask layer patterns 52 may be removed through a wet etching using a phosphoric acid. According to this fact, the contact holes 68 are defined in a self-defined manner by the capping layer 67 and the spacers 64. The upper surfaces of the pillars 54 are exposed on the bottoms of the contact holes 68.

[0127] Referring to FIG. 12B, contact plugs 69 are formed to be buried in the contact holes 68. The contact plugs 69 may include a polysilicon, a metal or the like. For example, after depositing a polysilicon to fill the contact holes 68, a planarization process may be performed. The spacers 64 surround the sidewalls of the contact plugs 69. While not shown, ion implantation for forming sources/drains may be carried out before forming the contact plugs 69.

[0128] Referring to FIG. 12C, storage nodes 70 of capacitors are formed on the contact plugs 69. The storage nodes 70 may have pillar shapes. In another embodiment, the storage nodes 70 may have cylinder shapes. As a method for forming the storage nodes 70, well-known methods may be adopted. For example, after forming a mold layer (not shown), open parts are formed by etching the mold layer, and the storage nodes 70 are formed in the open parts. Then, the mold layer is removed through a full dip-out process.

[0129] While not shown, supporters for supporting the outer walls of the storage nodes 70 may be additionally formed. For example, a substance for supporters is formed on the mold layer, and supporters may be formed by partially etching the substance for supporters before performing the full dip-out process. Furthermore, a dielectric layer and plate nodes may be additionally formed on the storage nodes 70.

[0130] FIG. 13 is a view illustrating vertical channel transistors in accordance with a fourth embodiment of the present invention.

[0131] Referring to FIG. 13, vertical channel transistors in accordance with a fourth embodiment of the present invention may include pillars 54, first gate electrodes 57, and second gate electrodes 66.

[0132] First, a plurality of pillars 54 are formed on a semiconductor substrate 51 to vertically project from the surface of the semiconductor substrate 51. Bodies 53 may be further formed under the pillars 54. The pillars 54 may vertically project from the surfaces of the bodies 53. The plurality of pillars 54 may have a matrix arrangement. The pillars 54 may be quadrangular pillars each of which has a plurality of sidewalls. The pillars 54 may be arranged to be isolated by an interlayer dielectric layer (not shown) in a first direction Y, and the first and second sidewalls of the pillars 54 laterally opposing each other may be exposed in a second direction X. Each pillar 54 may have a source region, a drain region and a channel region (not numbered). The drain region may be formed in top portion of the pillar 54, and the source region may be formed in bottom portion of the pillar 54. The channel region may be formed between the drain region and the source region. The semiconductor substrate 51, the bodies 53 and the pillars 54 include a silicon-containing substance. For example, a silicon substrate or a silicon-germanium substrate may be used. Accordingly, the pillar 54 may include a semiconductor pillar, a silicon pillar or a silicon-germanium pillar.

[0133] A gate dielectric layer 56 is formed on the first sidewalls and the second sidewalls of the pillars 54. The gate dielectric layer 56 may include a silicon oxide or a high-k substance.

[0134] The first gate electrodes 57 are formed on the gate dielectric layer 56 to cover the first sidewalls of the pillars 54. The first gate electrodes 57 may be formed to be lower than the height of the pillars 54. The first gate electrodes 57 may become vertical gate electrodes.

[0135] The second gate electrodes 66 which are connected to the upper portions of the sidewalls of the first gate electrodes 57 are formed between the plurality of pillars 54. The second gate electrodes 66 may serve as word lines. The second gate electrodes 66 may have shapes which are buried in the upper portions of the spaces defined between the plurality of pillars 54. For example, the second gate electrodes 66 may be buried between the hard mask layer patterns 52. A first dielectric layer 59 may be formed between the first gate electrodes 57 and adjoining pillars 54. The first gate electrodes 57 and a second dielectric layer 62 may have the same height. The first dielectric layer 59 may have a height lower than the first gate electrodes 57 and the second dielectric layer 62. The second dielectric layer 62 may be formed on the facing-away sidewalls of the pillars 54. The first dielectric layer 59 may be recessed by a predetermined depth, and the second gate electrodes 66 may be formed on the first dielectric layer 59 which is recessed. Spacers 64 may be formed on the second dielectric layer 62 and the first gate electrodes 57. The second gate electrodes 66 may be isolated from the surrounding structures by the spacers 64. A capping layer 67 may be additionally formed on the second gate electrodes 66. [0136] The first gate electrodes 57 have line-shaped vertical gate structures which extend in the first direction Y. The second gate electrodes 66 have shapes which extend in the first direction Y in the same manner as the first gate electrodes 57. The first gate electrodes 57 may include a metal nitride or a low resistance metal. For example, the first gate electrodes 57 may include TIN, TiAlN, WN, TaN, W, Al, Ru, Pt, Au, or the like. The second gate electrodes 66 may include W, Al, Ru, Pt, Au, or the like.

[0137] According to FIG. 13, the vertical channel transistors in accordance with the fourth embodiment of the present invention have single gate structures in which the first gate electrodes 57 are formed on only one sidewalls of the pillars 54. The first gate electrodes 57 become the gate electrodes of vertical channel transistors. Furthermore, as only the first gate electrodes 57 are formed on the sidewalls of the pillars 54, the first gate electrodes 57 may be formed to have a substantial thickness. According to this fact, gate resistance may be reduced. In particular, because only the first gate electrodes 57 are formed without forming shield gate electrodes, a neighbor gate effect may be originally prevented.

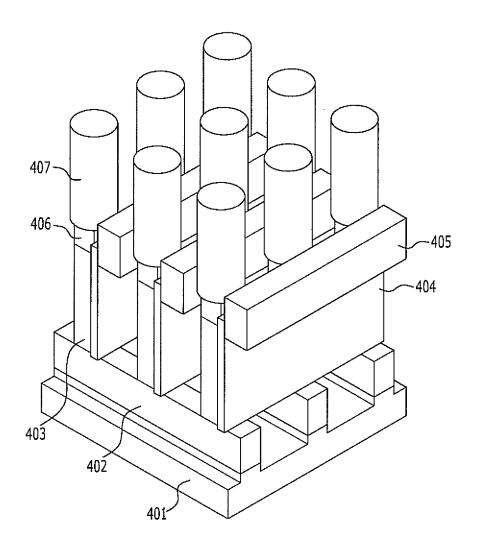

[0138] FIG. 14 is a perspective view illustrating a semiconductor device to which the vertical channel transistors in accordance with the fourth embodiment of the present invention are applied.

[0139] Referring to FIG. 14, vertical channel transistors include first gate electrodes 404, second gate electrodes 405, and pillars 403. As buried bit lines 402 and capacitors 407 are connected to the vertical channel transistors, a semiconductor device such as a DRAM may be realized. The buried bit lines 402 may be electrically connected with the bottom portions of the pillars 403. The buried bit lines 402 may be vertically formed on a semiconductor substrate 401 and may extend in

a first direction. The first gate electrodes 404 and the second gate electrodes 405 may extend in a second direction perpendicularly crossing with the first direction. The capacitors 407 may be electrically connected with the top portions of the pillars 403. Contact plugs 406 may be additionally formed between the capacitors 407 and the pillars 403. While not shown, the capacitors 407 may include storage nodes, a dielectric layer and plate nodes. The vertical channel transistors may be applied not only to a memory such as a DRAM but also to a nonvolatile memory such as a flash memory.

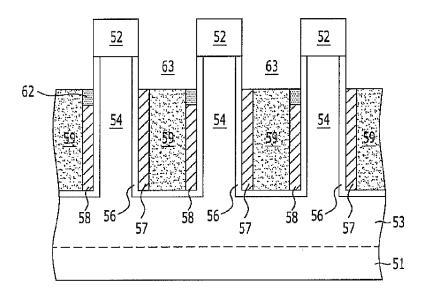

[0140] FIGS. 15A to 15F are views explaining an exemplary method for fabricating the vertical channel transistors in accordance with the fourth embodiment of the present invention. Unlike the third embodiment, when defining gaps, shield gate electrodes are entirely removed. Hereinbelow, reference will be made to FIGS. 11A to 11D for processes before defining the gaps.

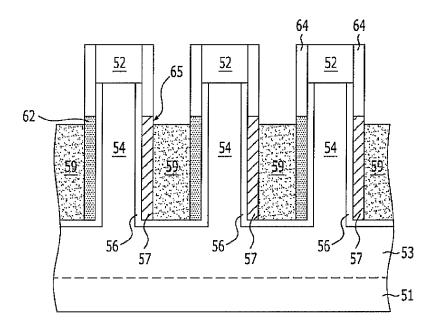

[0141] Referring to FIG. 15A, photoresist patterns 60 are formed. The photoresist patterns 60 may have shapes which expose the upper surfaces of the preliminary shield gate electrodes 58A.

[0142] The preliminary shield gate electrodes 58A are entirely etched using the photoresist patterns 60 as an etch barrier. According to this fact, gaps 61 are defined. The preliminary shield gate electrodes 58A removed in this way may become sacrificial gate electrodes.

[0143] By entirely removing the preliminary shield gate electrodes 58A, only preliminary first gate electrodes 57A remain on the one sidewalls of the pillars 54.

[0144] Referring to FIG. 15B, a second dielectric layer 62A is formed to fill the gaps 61. The second dielectric layer 62A may include an oxide such as a silicon oxide. Also, the second dielectric layer 62A may include a nitride such as a silicon nitride. The second dielectric layer 62A may be planarized through CMP or the like until the surfaces of the hard mask layer patterns 52 are exposed.

[0145] Referring to FIG. 15C, the preliminary first gate electrodes 57A, the first dielectric layer 59A and the second dielectric layer 62A are recessed by a predefined depth. According to this fact, first recesses 63 are defined. The depth of the first recesses 63 may be lower than the surfaces of the pillars 54. First gate electrodes 57 are formed by the first recesses 63, and the upper surfaces of the first gate electrodes 57 are exposed. The first and second dielectric layers 59 and 62 remain on the bottoms of the first recesses 63.

[0146] The first gate electrodes 57 serve as the gate electrodes of the vertical channel transistors. By not forming shield gate electrodes, a neighbor gate effect by neighbor gates may be originally prevented.

[0147] Referring to FIG. 15D, spacers 64 are formed on both sidewalls of the first recesses 63. The spacers 64 may be formed of an oxide such as a silicon oxide. For example, the spacers 64 may be formed by depositing a silicon oxide on the entire surface and etching back the silicon oxide. The thickness of the spacers 64 may be the same as the thickness of the underlying first gate electrodes 57.

[0148] The first dielectric layer 59 is partially etched back to be self-aligned with the spacers 64. Due to this fact, the upper portions of the sidewalls of the first gate electrodes 57 are exposed.

[0149] By etching back the first dielectric layer 59 using the spacers 64 in this way, the upper portions of the sidewalls of the first gate electrodes 57 are exposed as indicated by the reference numeral 65.

[0150] Referring to FIG. 15E, second gate electrodes 66 are formed to fill the spaces defined on the first dielectric layer 59. The second gate electrodes 66 may extend in the first direction. In order to form the second gate electrodes 66, an etchback process may be performed after forming a second conductive layer on the entire surface. The second conductive layer may include W, Al, Ru, Pt, Au, or the like. The second conductive layer may be formed of tungsten (W). The second gate electrodes 66 may have buried structures.

[0151] The second gate electrodes 66 are connected with the upper portions of the sidewalls of the first gate electrodes 57

[0152] As can be readily seen from the above descriptions, the vertical channel transistors in accordance with the fourth embodiment of the present invention have single gate structures in which the first gate electrodes 57 are formed on only any one sidewalls of the pillars 54.

[0153] Referring to FIG. 15F, the surfaces of the second gate electrodes 66 are recessed.

[0154] A capping layer 67 is formed to fill the spaces defined on the second gate electrodes 66 which are recessed. The capping layer 67 may include an oxide such as a silicon oxide.

[0155] Contact plugs and capacitors are subsequently formed. Reference may be made to FIGS. 12A to 12C for a method for forming the contact plugs and the capacitors.

[0156] A method for forming the buried bit lines in accordance with the first to fourth embodiments of the present invention will be described below. Hereinbelow, explanations will be made for a method for forming the buried bit lines of the semiconductor device to which the vertical channel transistors in accordance with the first embodiment shown in FIG. 2 is applied. The same method may be applied to the other embodiments. The buried bit lines may be formed before forming the first dielectric layer in FIG. 3B. That is to say, after forming the bodies shown in FIG. 3A, the buried bit lines may be formed before forming the first dielectric layer in FIG.

[0157] FIGS. 16A to 16K are views explaining a method for forming a buried bit line of the semiconductor device to which the vertical channel transistors in accordance with the embodiments of the present invention are applied.

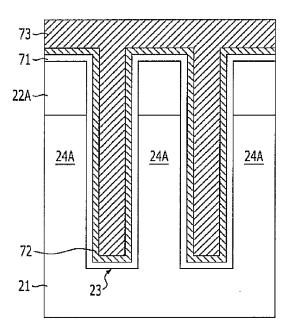

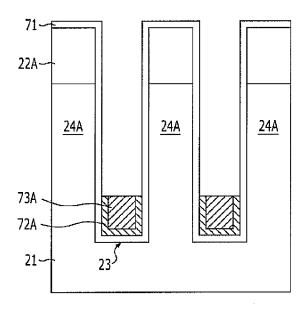

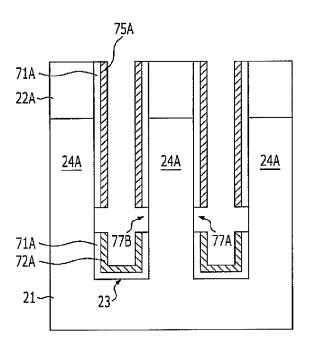

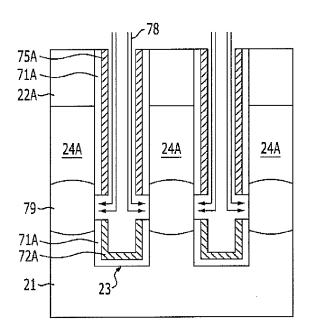

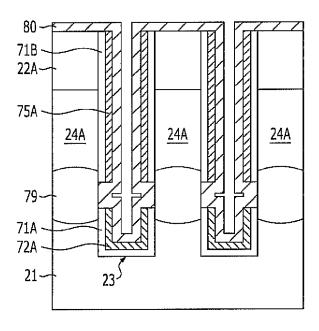

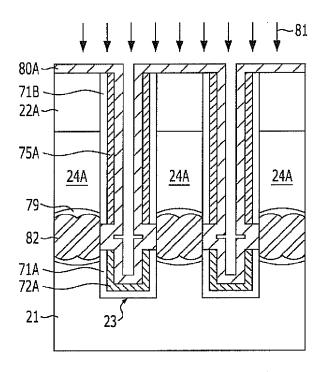

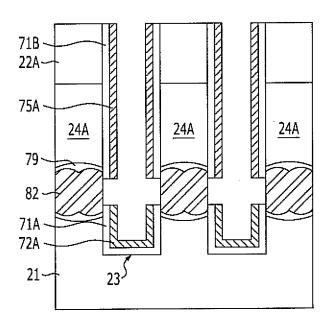

[0158] Referring to FIG. 16A, passivation layers are formed on the entire surface including bodies (see the reference numeral 24A of FIG. 4A). As the passivation layers, a first passivation layer 71 and a second passivation layer 72 may be stacked. Each of the first passivation layer 71 and the second passivation layer 72 may include an oxide, a nitride, or the like. Because the first passivation layer 71 and the second passivation layer 72 should have etching selectivities, different substances are selected as the first passivation layer 71 and the second passivation layer 72. For example, if an oxide is used to form the first passivation layer 71, a substance with an etching selectivity with respect to the oxide is selected to form the second passivation layer 72. If the first passivation layer 71 is formed of an oxide, the second passivation layer 72 may be formed of a nitride.

[0159] A first sacrificial layer 73 is formed on the entire surface of a resultant structure including the second passivation layer 72 in such a way as to gapfill first trenches 23 between the bodies 24A. A substance having a different etching selectivity with respect to the first and second passivation layers 71 and 72 may be used to form the first sacrificial layer 73. The first sacrificial layer 73 may include an oxide layer, a

nitride layer, a silicon layer, or the like. Here, while a substance used as the first and second passivation layers 71 and 72 may be repeatedly used as the first sacrificial layer 73, a different substance is used to have a different etching selectivity. Hereinbelow, as the first sacrificial layer 73, a silicon layer may be used.

[0160] Referring to FIG. 16B, the first sacrificial layer 73 is planarized. The planarization of the first sacrificial layer 73 includes a CMP (chemical mechanical polishing) process. Successively, an etch-back process is performed. By the etch-back process, first sacrificial layer patterns 73A which are recessed are formed. During the etch-back process, the second passivation layer 72 is not etched since it has an etching selectivity different from that of the first sacrificial layer 73.

[0161] Referring to FIG. 16C, portions of the second passivation layer 72 which are exposed by the recessed first sacrificial layer patterns 73A are selectively removed. By this fact, second passivation layer patterns 72A with the same height as the first sacrificial layer patterns 73A are formed. In order to remove the second passivation layer 72, wet etching or dry etching may be adopted.

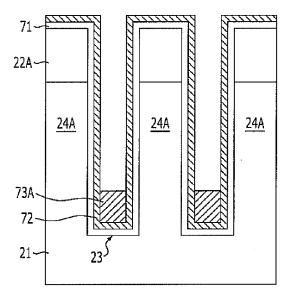

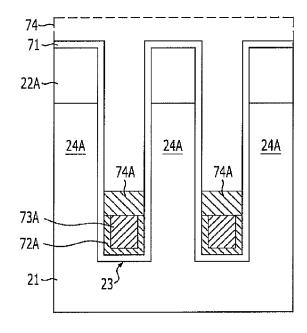

[0162] Referring to FIG. 16D, a second sacrificial layer 74 is formed on the entire surface of the resultant structure formed with the second passivation layer patterns 72A. The second sacrificial layer 74 gapfills the first trenches 23. The second sacrificial layer 74 may be formed of a substance with a different etching selectivity from the first passivation layer 71. The second sacrificial layer 74 may include an oxide layer, a nitride layer, a silicon layer, or the like. Here, while a substance used as the first passivation layer 71 may be repeatedly used as the second sacrificial layer 74, a different substance is used to have a different etching selectivity. Hereinbelow, according to the present embodiment, as the second sacrificial layer 74, a silicon layer may be used.

[0163] The second sacrificial layer 74 is planarized. The planarization of the second sacrificial layer 74 includes a CMP (chemical mechanical polishing) process. Successively, an etch-back process is performed. By the etch-back process, second sacrificial layer patterns 74A which are recessed are formed. During the etch-back process, the first passivation layer 71 is not etched since it has an etching selectivity different from that of the second sacrificial layer 74.

[0164] Referring to FIG. 16E, a third passivation layer 75 is formed on the entire surface of the resultant structure including the second sacrificial layer patterns 74A. The third passivation layer 75 may include an oxide layer, a nitride layer, a silicon layer, or the like. The third passivation layer 75 may be formed of a substance with a different etching selectivity from the first passivation layer 71. Therefore, different substances are selected as the first passivation layer 71 and the third passivation layer 75. For example, if an oxide layer is used as the first passivation layer 71, a substance with a different etching selectivity from the oxide layer is selected as the third passivation layer 75. If the oxide layer is used as the first passivation layer 71, a nitride layer may be used as the third passivation layer 75.

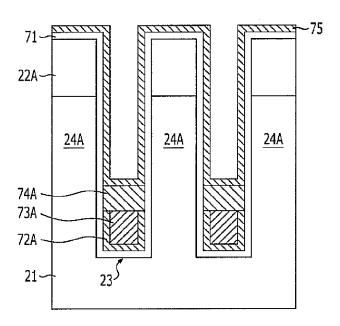

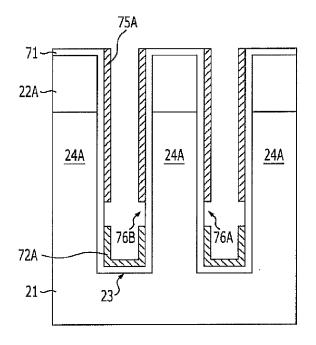

[0165] Referring to FIG. 16F, the third passivation layer 75 is selectively etched through spacer etching. According to this fact, third passivation layer patterns 75A are formed. The third passivation layer patterns 75A have the forms of spacers which cover the sidewalls of the bodies 24A and the hard mask layer patterns 22A. The third passivation layer patterns 75A have a height that covers the sidewalls of the bodies 24A and the hard mask layer patterns 22A on the second sacrificial

layer patterns 74A. The third passivation layer patterns 75A cover the first passivation layer 71. By the third passivation layer patterns 75A, the underlying second sacrificial layer patterns 74A are exposed.

[0166] The second sacrificial layer patterns 74A are removed. The second sacrificial layer patterns 74A are removed using dry etching or wet etching.