### (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(45) 공고일자 2021년04월07일 (11) 등록번호 10-2237563

(24) 등록일자 2021년04월01일

(51) 국제특허분류(Int. Cl.) *G11C 29/04* (2006.01)

(21) 출원번호 **10-2014-0163266**

(22) 출원일자 **2014년11월21일** 심사청구일자 **2019년10월23일**

(65) 공개번호10-2016-0060974(43) 공개일자2016년05월31일

(56) 선행기술조사문헌

KR1020000032852 A\*

US20100322024 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

#### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 김윤길

경기도 수원시 영통구 영통로 498, 150동 1202호 (영통동, 황골마을주공1단지아파트)

#### 차정윤

충청남도 아산시 배방읍 배방로 131, 109동 603호 (아산배방한라비발디아파트)

(74) 대리인 **박영우**

전체 청구항 수 : 총 10 항

심사관: 신우열

#### (54) 발명의 명칭 테스트 시간을 감축하는 메모리 장치 및 이를 포함하는 컴퓨팅 시스템

#### (57) 요 약

메모리 장치는 메모리 셀 어레이 및 어드레스 디코더를 포함한다. 메모리 셀 어레이는 일반 메모리 영역 및 여분 메모리 영역을 포함한다. 일반 메모리 영역은 데이터 신호 및 복수의 일반 메모리 영역 신호들에 응답하여 동작한다. 여분 메모리 영역은 데이터 신호 및 복수의 여분 메모리 영역 신호들에 응답하여 동작한다. 어드레스 디코더는 일반 메모리 영역 신호 생성기 및 여분 메모리 영역 신호 생성기를 포함한다. 어드레스 디코더가 테스트 모드로 동작 시, 일반 메모리 영역 신호 생성기는 어드레스 신호에 상응하고 복수의 일반 메모리 영역 신호들에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 여분 메모리 영역 신호 생성기는 어드레스 신호에 상응하고 복수의 여분 메모리 영역 신호들에 포함되는 제1 여분 메모리 영역 신호들에 포함되는 제1 여분 메모리 영역 신호를 동시에 활성화한다.

#### 대표도

#### 명 세 서

#### 청구범위

#### 청구항 1

데이터 신호 및 복수의 일반 메모리 영역 신호들에 응답하여 동작하는 일반 메모리 영역 및 상기 데이터 신호 및 복수의 여분 메모리 영역 신호들에 응답하여 동작하는 여분 메모리 영역을 구비하는 메모리 셀 어레이; 및

일반 메모리 영역 신호 생성기 및 여분 메모리 영역 신호 생성기를 구비하는 어드레스 디코더를 포함하고,

상기 어드레스 디코더가 테스트 모드로 동작 시, 상기 일반 메모리 영역 신호 생성기는 어드레스 신호에 상응하고 상기 복수의 일반 메모리 영역 신호들에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 상기 여분 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 여분 메모리 영역 신호들에 포함되는 제1 여분 메모리 영역 신호를 동시에 활성화하고,

상기 어드레스 디코더는 상기 여분 메모리 영역 신호들에 대한 논리 합 연산의 결과를 차단 신호로서 출력하는 차단 신호 생성기를 더 포함하고,

상기 일반 메모리 영역 신호 생성기는 일반 모드에서 상기 차단 신호에 응답하여 상기 여분 메모리 영역 신호들 중 하나가 활성화되는 경우, 상기 일반 메모리 영역 신호들을 비활성화하는 메모리 장치.

#### 청구항 2

제1 항에 있어서.

상기 어드레스 디코더가 상기 테스트 모드로 동작 시, 상기 복수의 일반 메모리 영역 신호들이 각각 한 번씩 활성화되는 동안, 상기 복수의 여분 메모리 영역 신호들이 각각 한 번씩 활성화되는 메모리 장치.

#### 청구항 3

제1 항에 있어서,

상기 메모리 셀 어레이는 복수의 블록들을 포함하고, 상기 일반 메모리 영역은 복수의 하위 일반 메모리 영역들을 포함하고, 상기 여분 메모리 영역은 복수의 하위 여분 메모리 영역들을 포함하는 메모리 장치.

#### 청구항 4

제3 항에 있어서.

상기 블록들 중 제1 블록은 상기 하위 일반 메모리 영역들 중 제1 하위 일반 메모리 영역 및 상기 하위 여분 메 모리 영역들 중 제1 하위 여분 메모리 영역을 포함하고,

상기 블록들 중 제2 블록은 상기 하위 일반 메모리 영역들 중 제2 하위 일반 메모리 영역 및 상기 하위 여분 메 모리 영역들 중 제2 하위 여분 메모리 영역을 포함하는 메모리 장치.

#### 청구항 5

제4 항에 있어서,

상기 제1 일반 메모리 영역 신호들은 상기 제1 하위 일반 메모리 영역에 상응하고, 상기 제1 여분 메모리 영역 신호는 상기 제1 하위 여분 메모리 영역에 상응하는 메모리 장치.

#### 청구항 6

제4 항에 있어서,

상기 제1 일반 메모리 영역 신호들은 상기 제1 하위 일반 메모리 영역에 상응하고, 상기 제1 여분 메모리 영역 신호는 상기 제2 하위 여분 메모리 영역에 상응하는 메모리 장치.

#### 청구항 7

제1 항에 있어서,

테스트 신호가 논리 하이 레벨을 갖는 경우, 상기 어드레스 디코더는 상기 테스트 모드로 동작하고,

상기 테스트 신호가 논리 로우 레벨을 갖는 경우, 상기 어드레스 디코더는 상기 일반 모드로 동작하는 메모리 장치.

#### 청구항 8

제7 항에 있어서,

상기 여분 메모리 영역 신호 생성기는,

상기 어드레스 신호에 기초하여 상기 복수의 일반 메모리 영역 신호들이 각각 한 번씩 활성화 되는 동안, 각각 한 번씩 활성화되는 제1 내부 여분 메모리 영역 신호들을 생성하는 제1 여분 메모리 영역 신호 생성 유닛;

퓨즈 회로에 포함된 불량 어드레스 값들과 상기 어드레스 신호의 값을 비교하여 제2 내부 여분 메모리 영역 신호들을 생성하는 제2 여분 메모리 영역 신호 생성 유닛; 및

상기 테스트 신호가 논리 하이 레벨을 갖는 경우 상기 제1 내부 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력하고, 상기 테스트 신호가 논리 로우 레벨을 갖는 경우 상기 제2 내부 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력하는 선택 유닛을 포함하고,

상기 제1 여분 메모리 영역 신호 생성 유닛은 상기 어드레스 신호의 일부가 사용자가 미리 정한 값과 상이할 때 상기 제1 내부 여분 메모리 영역 신호들을 비활성화하는 활성화 빈도 조절기를 포함하는 메모리 장치.

#### 청구항 9

제7 항에 있어서,

상기 여분 메모리 영역 신호 생성기는,

퓨즈 회로에 포함된 불량 어드레스 값들과 상기 어드레스 신호의 값을 비교하여 내부 여분 메모리 영역 신호들을 생성하는 여분 메모리 영역 신호 생성 유닛; 및

상기 테스트 신호가 논리 하이 레벨을 갖는 경우 상기 복수의 일반 메모리 영역 신호들 중 일부를 상기 복수의 여분 메모리 영역 신호들로서 출력하고, 상기 테스트 신호가 논리 로우 레벨을 갖는 경우 상기 내부 여분 메모 리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력하는 선택 유닛을 포함하는 메모리 장치.

#### 청구항 10

데이터 신호 및 어드레스 신호를 생성하는 프로세서; 및

병렬적 테스트가 가능한 메모리 장치를 포함하고,

상기 메모리 장치는

상기 데이터 신호 및 복수의 일반 메모리 영역 신호들에 응답하여 동작하는 일반 메모리 영역과 상기 데이터 신호 및 복수의 여분 메모리 영역 신호들에 응답하여 동작하는 여분 메모리 영역을 구비하는 메모리 셀 어레이; 및

일반 메모리 영역 신호 생성기 및 여분 메모리 영역 신호 생성기를 구비하는 어드레스 디코더를 포함하고,

상기 어드레스 디코더가 테스트 모드로 동작 시, 상기 일반 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 일반 메모리 영역 신호들에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 상기 여분 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 여분 메모리 영역 신호들에 포함되는 제1 여분 메모리 영역 신호를 동시에 활성화하고,

상기 어드레스 디코더는 상기 여분 메모리 영역 신호들에 대한 논리 합 연산의 결과를 차단 신호로서 출력하는 차단 신호 생성기를 더 포함하고, 상기 일반 메모리 영역 신호 생성기는 일반 모드에서 상기 차단 신호에 응답하여 상기 여분 메모리 영역 신호들 중 하나가 활성화되는 경우, 상기 일반 메모리 영역 신호들을 비활성화하는 컴퓨팅 시스템.

#### 발명의 설명

### 기술분야

[0001] 본 발명은 메모리 장치에 관한 것으로서, 더욱 상세하게는 일반 메모리 영역과 여분 메모리 영역의 테스트를 동시에 진행하여 테스트 시간을 감축하는 메모리 장치 및 이를 포함하는 컴퓨팅 시스템에 관한 것이다.

### 배경기술

- [0002] 메모리 장치를 생산하는 공정이 세분화되면서, 메모리 장치가 포함하는 불량 메모리 셀들의 수는 기하급수적으로 증가하고 있다. 메모리 장치의 메모리 셀 어레이는 일반 메모리 영역과 여분 메모리 영역으로 구분될 수 있다. 여분 메모리 영역의 테스트 과정 중 찾아진 불량 여분 메모리 셀은 사용되지 않도록 비활성화될 수 있다. 일반 메모리 영역의 테스트 과정 중에 찾아진 불량 일반 메모리 셀은 여분 메모리 영역에 포함되는 불량 여분 메모리 셀이 아닌 여분 메모리 셀로 대체하여 메모리 장치의 기능을 복원할 수 있다.

- [0003] 메모리 장치의 초기 불량 테스트(Infant fault test)는 메모리 장치가 판매되어 일반 유저에 의해 사용되기 전에 일반 메모리 영역의 테스트와 여분 메모리 영역의 테스트를 많은 횟수에 걸쳐 수행하여 메모리 장치의 초기 불량을 찾는 테스트를 말한다. 메모리 장치의 초기 불량 테스트에 많은 시간이 소요되는 것이 문제가 되고 있다.

#### 발명의 내용

#### 해결하려는 과제

- [0004] 상기와 같은 문제점을 해결하기 위한 본 발명의 일 목적은 일반 메모리 영역과 여분 메모리 영역의 테스트를 동시에 진행하여 테스트 시간을 감축하는 메모리 장치를 제공하는데 있다.

- [0005] 본 발명의 일 목적은 일반 메모리 영역과 여분 메모리 영역의 테스트를 동시에 진행하여 테스트 시간을 감축하는 메모리 장치를 포함하는 컴퓨팅 시스템을 제공하는데 있다

#### 과제의 해결 수단

- [0006] 상기 일 목적을 달성하기 위해, 본 발명의 일 실시예에 따른 메모리 장치는 메모리 셀 어레이 및 어드레스 디코 더를 포함한다. 상기 메모리 셀 어레이는 일반 메모리 영역 및 여분 메모리 영역을 포함한다. 상기 일반 메모리 영역은 데이터 신호 및 복수의 일반 메모리 영역 신호들에 응답하여 동작한다. 상기 여분 메모리 영역은 상기데이터 신호 및 복수의 여분 메모리 영역 신호들에 응답하여 동작한다. 상기 어드레스 디코더는 일반 메모리 영역 신호 생성기 및 여분 메모리 영역 신호 생성기를 포함한다. 상기 어드레스 디코더가 테스트 모드로 동작 시, 상기 일반 메모리 영역 신호 생성기는 어드레스 신호에 상응하고 상기 복수의 일반 메모리 영역 신호들에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 상기 여분 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 여분 메모리 영역 신호들에 포함되는 제1 여분 메모리 영역 신호를 동시에 활성화한다.

- [0007] 일 실시예에 있어서, 상기 어드레스 디코더가 상기 테스트 모드로 동작 시, 상기 복수의 일반 메모리 영역 신호들이 각각 한 번씩 활성화되는 동안, 상기 복수의 여분 메모리 영역 신호들이 각각 한 번씩 활성화될 수 있다.

- [0008] 일 실시예에 있어서, 상기 메모리 셀 어레이는 복수의 블록들을 포함하고, 상기 일반 메모리 영역은 복수의 하위 일반 메모리 영역들을 포함하고, 상기 여분 메모리 영역은 복수의 하위 여분 메모리 영역들을 포함할 수 있다.

- [0009] 일 실시예에 있어서, 상기 블록들 중 제1 블록은 상기 하위 일반 메모리 영역들 중 제1 하위 일반 메모리 영역 및 상기 하위 여분 메모리 영역들 중 제1 하위 여분 메모리 영역을 포함하고, 상기 블록들 중 제2 블록은 상기 하위 일반 메모리 영역들 중 제2 하위 일반 메모리 영역 및 상기 하위 여분 메모리 영역들 중 제2 하위 여분 메모리 영역을 포함할 수 있다.

- [0010] 일 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들은 상기 제1 하위 일반 메모리 영역에 상응하고, 상기

제1 여분 메모리 영역 신호는 상기 제1 하위 여분 메모리 영역에 상응할 수 있다.

- [0011] 일 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들은 상기 제1 하위 일반 메모리 영역에 상응하고, 상기 제1 여분 메모리 영역 신호는 상기 제2 하위 여분 메모리 영역에 상응할 수 있다.

- [0012] 일 실시예에 있어서, 감지 증폭기는 상기 제1 블록에 포함된 제1 메모리 셀의 데이터 신호를 상기 제2 블록에 포함되고, 상기 제1 메모리 셀에 상응하는 제2 메모리 셀의 기준 신호에 기초하여 증폭하여 출력 신호를 생성하고, 상기 제1 일반 메모리 영역 신호들이 상기 제1 하위 일반 메모리 영역에 상응하는 경우, 상기 제1 여분 메모리 영역 신호는 상기 제2 하위 여분 메모리 영역에 상응하지 않을 수 있다.

- [0013] 일 실시예에 있어서, 상기 감지 증폭기는 상기 제1 블록과 상기 제2 블록 사이에 위치할 수 있다.

- [0014] 일 실시예에 있어서, 상기 블록들은 제1 블록 및 제2 블록을 포함하고, 상기 제1 블록은 상기 하위 일반 메모리 영역들 중 제1 하위 일반 메모리 영역 및 상기 하위 여분 메모리 영역들 중 제1 하위 여분 메모리 영역을 포함하고, 상기 제2 블록은 상기 하위 일반 메모리 영역들 중 제2 하위 일반 메모리 영역을 포함할 수 있다.

- [0015] 일 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들은 상기 제1 하위 일반 메모리 영역에 상응하고, 상기 제1 여분 메모리 영역 신호는 상기 제1 하위 여분 메모리 영역에 상응할 수 있다.

- [0016] 일 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들은 상기 제2 하위 일반 메모리 영역에 상응하고, 상기 제1 여분 메모리 영역 신호는 상기 제1 하위 여분 메모리 영역에 상응할 수 있다.

- [0017] 일 실시예에 있어서, 상기 어드레스 디코더는 상기 복수의 여분 메모리 영역 신호들의 논리합 연산 결과를 차단 신호로서 출력하는 차단 신호 생성기를 더 포함할 수 있다.

- [0018] 일 실시예에 있어서, 상기 어드레스 디코더가 상기 테스트 모드로 동작하는 경우, 상기 일반 메모리 영역 신호생성기는 상기 차단 신호에 무관하게 상기 제1 일반 메모리 영역 신호들을 활성화할 수 있다.

- [0019] 일 실시예에 있어서, 상기 일반 메모리 영역 신호 생성기가 일반 모드로 동작하고 상기 차단 신호가 논리 로우 레벨을 갖는 경우, 상기 일반 메모리 영역 신호 생성기는 상기 제1 일반 메모리 영역 신호들을 활성화하고, 상기 일반 메모리 영역 신호 생성기가 상기 일반 모드로 동작하고 상기 차단 신호가 논리 하이 레벨을 갖는 경우, 상기 일반 메모리 영역 신호 생성기는 상기 복수의 일반 메모리 영역 신호들을 비활성화할 수 있다.

- [0020] 일 실시예에 있어서, 테스트 신호가 논리 하이 레벨을 갖는 경우, 상기 어드레스 디코더는 상기 테스트 모드로 동작하고, 상기 테스트 신호가 논리 로우 레벨을 갖는 경우, 상기 어드레스 디코더는 일반 모드로 동작할 수 있다.

- [0021] 일 실시예에 있어서, 상기 여분 메모리 영역 신호 생성기는 제1 여분 메모리 영역 신호 생성 유닛, 제2 여분 메모리 영역 신호 생성 유닛 및 선택 유닛을 포함할 수 있다. 상기 제1 여분 메모리 영역 신호 생성 유닛은 상기 어드레스 신호에 기초하여 상기 복수의 일반 메모리 영역 신호들이 각각 한 번씩 활성화 되는 동안, 각각 한 번씩 활성화되는 제1 내부 여분 메모리 영역 신호들을 생성할 수 있다. 상기 제2 여분 메모리 영역 신호 생성 유닛은 퓨즈 회로에 포함된 불량 어드레스 값들과 상기 어드레스 신호의 값을 비교하여 제2 내부 여분 메모리 영역 신호들을 생성할 수 있다. 상기 선택 유닛은 상기 테스트 신호가 논리 하이 레벨을 갖는 경우 상기 제1 내부 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력하고, 상기 테스트 신호가 논리 로우 레벨을 갖는 경우 상기 제2 내부 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력할수 있다.

- [0022] 일 실시예에 있어서, 상기 제1 여분 메모리 영역 신호 생성 유닛은 상기 어드레스 신호의 일부가 사용자가 미리 정한 값과 상이할 때 상기 제1 내부 여분 메모리 영역 신호들을 비활성화하는 활성화 빈도 조절기를 포함할 수 있다.

- [0023] 일 실시예에 있어서, 상기 여분 메모리 영역 신호 생성기는 여부 메모리 영역 신호 생성 유닛 및 선택 유닛을 포함할 수 있다. 상기 여분 메모리 영역 신호 유닛은 퓨즈 회로에 포함된 불량 어드레스 값들과 상기 어드레스 신호의 값을 비교하여 내부 여분 메모리 영역 신호들을 생성할 수 있다. 상기 선택 유닛은 상기 테스트 신호가 논리 하이 레벨을 갖는 경우 상기 복수의 일반 메모리 영역 신호들 중 일부를 상기 복수의 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들을 상기 복수의 여분 메모리 영역 신호들로서 출력할 수 있다.

- [0024] 일 실시예에 있어서, 상기 복수의 일반 메모리 영역 신호들은 각각 상기 일반 메모리 영역의 워드 라인 신호들

이고, 상기 복수의 여분 메모리 영역 신호들은 각각 상기 여분 메모리 영역의 워드 라인 신호들일 수 있다.

- [0025] 일 실시예에 있어서, 상기 복수의 일반 메모리 영역 신호들은 각각 상기 일반 메모리 영역의 비트 라인 신호들이고, 상기 복수의 여분 메모리 영역 신호들은 각각 상기 여분 메모리 영역의 비트 라인 신호들일 수 있다.

- [0026] 상기 일 목적을 달성하기 위해, 본 발명의 일 실시예에 따른 컴퓨팅 시스템은 데이터 신호 및 어드레스 신호를 생성하는 프로세서 및 병렬적 테스트가 가능한 메모리 장치를 포함한다. 상기 메모리 장치는 메모리 셀 어레이 및 어드레스 디코더를 포함한다. 상기 메모리 셀 어레이는 상기 데이터 신호 및 복수의 일반 메모리 영역 신호들에 응답하여 동작하는 일반 메모리 영역과 상기 데이터 신호 및 복수의 여분 메모리 영역 신호들에 응답하여 동작하는 여분 메모리 영역을 포함한다. 상기 어드레스 디코더는 일반 메모리 영역 신호 생성기 및 여분 메모리 영역 신호 생성기를 포함한다. 상기 어드레스 디코더가 테스트 모드로 동작 시, 상기 일반 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 일반 메모리 영역 신호들에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 상기 여분 메모리 영역 신호 생성기는 상기 어드레스 신호에 상응하고 상기 복수의 여분 메모리 영역 신호를 동시에 활성화한다.

#### 발명의 효과

[0027] 본 발명의 실시예들에 따른 메모리 장치는 메모리 장치에 포함되는 일반 메모리 영역과 여분 메모리 영역을 테스트를 동시에 수행하여, 메모리 장치가 판매되어 일반 유저에 의해 사용되기 전에 많은 횟수에 걸쳐 일반 메모리 영역과 여분 메모리 영역의 테스트들을 수행하는 초기 불량 테스트에 소요되는 시간을 감축시킬 수 있다.

#### 도면의 간단한 설명

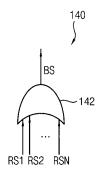

[0028] 도 1은 본 발명의 일 실시예에 따른 메모리 장치를 나타내는 블록도이다.

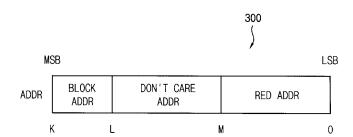

도 2는 도 1의 메모리 장치에 포함되는 일반 메모리 영역 신호 생성기가 어드레스 신호를 사용하는 방법을 나타 내는 블록도이다.

도 3은 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기가 어드레스 신호를 사용하는 방법을 나타내는 블록도이다.

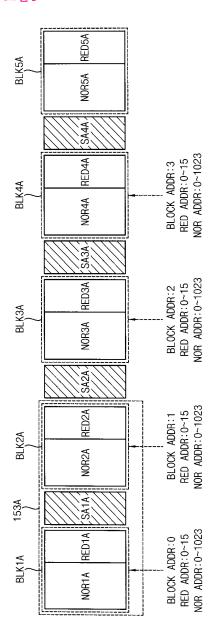

도 4는 도 1의 메모리 장치에 포함되는 메모리 셀 어레이의 일 실시예를 나타내는 블록도이다.

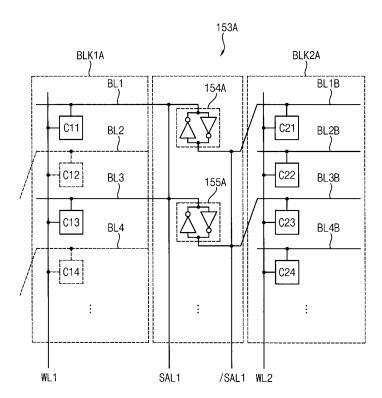

도 5는 도 4의 메모리 셀 어레이에 포함되는 제1 회로를 나타내는 회로도이다.

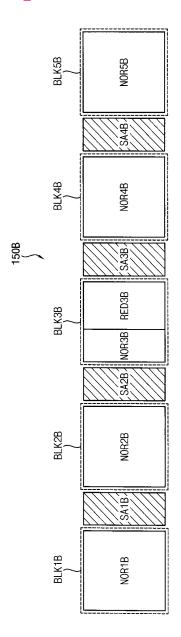

도 6은 도 1의 메모리 장치에 포함되는 메모리 셀 어레이의 다른 실시예를 나타내는 블록도들이다.

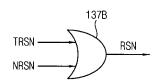

도 7은 도 1의 메모리 장치에 포함되는 차단 신호 생성기를 나타내는 블록도이다.

도 8은 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기의 일 실시예를 나타내는 블록도이다.

도 9는 도 8의 여분 메모리 영역 신호 생성기에 포함되는 제1 여분 메모리 영역 신호 생성 유닛의 일 실시예를 나타내는 블록도이다.

도 10은 도 9의 제1 여분 메모리 영역 신호 생성 유닛에 포함되는 제1 블록 신호 생성 회로를 나타내는 블록도이다.

도 11은 도 8의 여분 메모리 영역 신호 생성기에 포함되는 제1 여분 메모리 영역 신호 생성 유닛의 다른 실시예를 나타내는 블록도이다.

도 12는 도 11의 제1 여분 메모리 영역 신호 생성 유닛에 포함되는 제1 블록 신호 생성 회로를 나타내는 블록도이다.

도 13은 도 8의 여분 메모리 영역 신호 생성기에 포함되는 선택 유닛의 일 실시예를 나타내는 블록도이다.

도 14는 도 8의 여분 메모리 영역 신호 생성기에 포함되는 선택 유닛의 다른 실시예를 나타내는 블록도이다.

도 15는 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기의 다른 실시예를 나타내는 블록도이다.

도 16은 본 발명의 실시예들에 따른 메모리 장치를 포함하는 메모리 시스템을 나타내는 블록도이다.

도 17은 본 발명의 실시예들에 따른 메모리 장치를 포함하는 서버 시스템을 나타낸다.

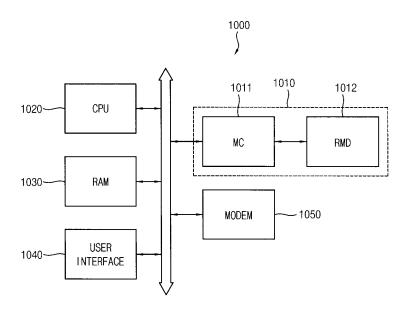

도 18은 본 발명의 실시예들에 따른 메모리 장치가 장착된 컴퓨팅 시스템을 나타내는 블록도이다.

도 19는 본 발명의 실시예들에 따른 메모리 장치를 컴퓨팅 시스템에 응용한 다른 예를 나타내는 블록도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0029] 본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 안 된다.

- [0030] 본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나, 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다. 각 도면을 설명하면서 유사한 참조부호를 구성요소에 대해 사용하였다.

- [0031] 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용된다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다.

- [0032] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0033] 본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0034] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가지고 있다. 일 반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥 상 가지는 의미와 일치하는 의미를 가지는 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0035] 이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다. 도면 상의 동일한 구성 요소에 대해서는 동일한 참조 부호를 사용하고 동일한 구성 요소에 대해서 중복된 설명은 생략한다.

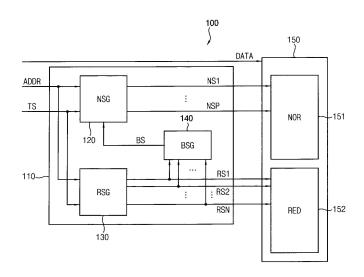

- [0036] 도 1은 본 발명의 일 실시예에 따른 메모리 장치를 나타내는 블록도이다.

- [0037] 도 1을 참조하면, 메모리 장치(100)는 메모리 셀 어레이(150) 및 어드레스 디코더(110)를 포함한다. 메모리 셀 어레이(150)는 일반 메모리 영역(NOR; 151) 및 여분 메모리 영역(RED; 152)을 포함한다. 일반 메모리 영역(151)은 데이터 신호(DATA) 및 복수의 일반 메모리 영역 신호들(NS1 내지 NSP; P는 자연수)에 응답하여 동작한다. 여분 메모리 영역(152)은 데이터 신호(DATA) 및 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN; N은 P보다 작은 자연수)에 응답하여 동작한다. 어드레스 디코더(110)는 일반 메모리 영역 신호 생성기(NSG; 120) 및 여분 메모리 영역 신호 생성기(RSG; 130)를 포함한다.

- [0038] 어드레스 디코더(110)가 테스트 모드로 동작 시, 일반 메모리 영역 신호 생성기(120)는 어드레스 신호(ADDR)에 상응하고 복수의 일반 메모리 영역 신호들(NS1 내지 NSP)에 포함되는 제1 일반 메모리 영역 신호들을 활성화하고, 여분 메모리 영역 신호 생성기(130)는 어드레스 신호(ADDR)에 상응하고 복수의 여분 메모리 영역 신호들 (RS1, RS2 내지 RSN)에 포함되는 제1 여분 메모리 영역 신호를 동시에 활성화한다.

- [0039] 상기 제1 일반 메모리 영역 신호들 및 상기 제1 여분 메모리 영역 신호가 활성화된 경우, 어드레스 디코더(11 0)는 상기 제1 일반 메모리 영역 신호들에 상응하고 일반 메모리 영역(151)에 포함되는 일반 메모리 셀들과 상

기 제1 여분 메모리 영역 신호에 상응하고 여분 메모리 영역(152)에 포함되는 여분 메모리 셀들을 테스트할 수있다.

- [0040] 테스트 신호(TS)가 논리 하이 레벨을 갖는 경우, 어드레스 디코더(110)는 테스트 모드로 동작하고, 테스트 신호 (TS)가 논리 로우 레벨을 갖는 경우, 어드레스 디코더(110)는 일반 모드로 동작할 수 있다.

- [0041] 어드레스 디코더(110)는 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)의 논리합 연산 결과를 차단 신호 (BS)로서 출력하는 차단 신호 생성기(BSG; 140)를 더 포함할 수 있다.

- [0042] 어드레스 디코더(110)가 테스트 모드로 동작하는 경우, 일반 메모리 영역 신호 생성기(120)는 차단 신호(TS)에 무관하게 상기 제1 일반 메모리 영역 신호들을 활성화할 수 있다. 일반 메모리 영역 신호 생성기(120)가 일반 모드로 동작하고 차단 신호(TS)가 논리 로우 레벨을 갖는 경우, 일반 메모리 영역 신호 생성기(120)는 상기 제1 일반 메모리 영역 신호들을 활성화할 수 있다. 일반 메모리 영역 신호 생성기(120)가 일반 모드로 동작하고 차단 신호(TS)가 논리 하이 레벨을 갖는 경우, 일반 메모리 영역 신호 생성기(120)는 복수의 일반 메모리 영역 신호들(NS1 내지 NSP)을 비활성화할 수 있다.

- [0043] 어드레스 디코더(110)가 테스트 모드로 동작 시, 복수의 일반 메모리 영역 신호들(NS1 내지 NSP)이 각각 한 번씩 활성화되는 동안, 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)이 각각 한 번씩 활성화될 수 있다.

- [0044] 일 실시예에 있어서, 복수의 일반 메모리 영역 신호들(NS1 내지 NSP)은 각각 일반 메모리 영역(151)의 워드 라인 신호들이고, 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)은 각각 여분 메모리 영역(152)의 워드 라인 신호들일 수 있다.

- [0045] 다른 실시예에 있어서, 복수의 일반 메모리 영역 신호들(NS1 내지 NSP)은 각각 일반 메모리 영역(151)의 비트라인 신호들이고, 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)은 각각 여분 메모리 영역(152)의 비트라인 신호들일 수 있다.

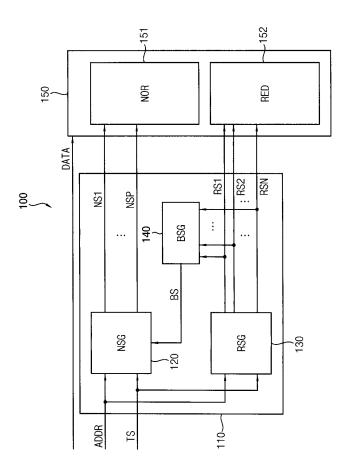

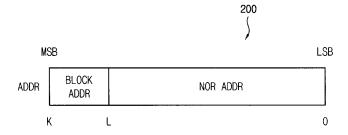

- [0046] 도 2는 도 1의 메모리 장치에 포함되는 일반 메모리 영역 신호 생성기가 어드레스 신호를 사용하는 방법을 나타 내는 블록도이다.

- [0047] 도 2를 참조하면, 어드레스 신호(ADDR)는 K 비트들을 가질 수 있다 (K는 자연수). 일반 메모리 영역 신호 생성기(120)는 어드레스 신호(ADDR)의 상위 비트들((L+1) 번째 비트~(K) 번째 비트)을 블록 어드레스(BLOCK ADD R)로 사용할 수 있다(L은 K보다 작은 자연수). 일반 메모리 영역 신호 생성기(120)는 어드레스 신호(ADDR)의 하위 비트들(첫 번째 비트~(L) 번째 비트)을 일반 메모리 영역 어드레스(NOR ADDR)로 사용할 수 있다.

- [0048] 도 3은 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기가 어드레스 신호를 사용하는 방법을 나타 내는 블록도이다.

- [0049] 도 3을 참조하면, 어드레스 신호(ADDR)는 K 비트들을 가질 수 있다. 여분 메모리 영역 신호 생성기(130)는 어드레스 신호(ADDR)의 상위 비트들((L+1) 번째 비트~(K) 번째 비트)을 블록 어드레스(BLOCK ADDR)로 사용할 수 있다. 여분 메모리 영역 신호 생성기(130)는 어드레스 신호(ADDR)의 중간 비트들((M+1) 번째 비트~(L) 번째 비트)을 사용하지 않을 수 있다(M은 L보다 작은 자연수). 여분 메모리 영역 신호 생성기(130)는 어드레스 신호(ADDR)의 하위 비트들(첫 번째 비트~(M) 번째 비트)을 여분 메모리 영역 어드레스(RED ADDR)로 사용할 수 있다.

- [0050] 도 4는 도 1의 메모리 장치에 포함되는 메모리 셀 어레이의 일 실시예를 나타내는 블록도이다.

- [0051] 도 4를 참조하면, 메모리 셀 어레이(150A)는 K가 13, L은 10, M은 4인 경우를 도시한다.

- [0052] 일 실시예에 있어서, 메모리 셀 어레이(150A)는 제1 블록(BLK1A), 제2 블록(BLK2A), 제3 블록(BLK3A), 제4 블록(BLK4A), 제1 감지 증폭기(SA1A), 제2 감지 증폭기(SA2A), 제3 감지 증폭기(SA3A) 및 제4 감지 증폭기(SA4A)를 포함할 수 있다.

- [0053] 제1 블록(BLK1A)은 제1 하위 일반 메모리 영역(NOR1A) 및 제1 하위 여분 메모리 영역(RED1A)을 포함할 수 있다. 제2 블록(BLK2A)은 제2 하위 일반 메모리 영역(NOR2A) 및 제2 하위 여분 메모리 영역(RED2A)을 포함할 수 있다. 제3 블록(BLK3A)은 제3 하위 일반 메모리 영역(NOR3A) 및 제3 하위 여분 메모리 영역(RED3A)을 포함할 수 있다. 제4 블록(BLK4A)은 제4 하위 일반 메모리 영역(NOR4A) 및 제4 하위 여분 메모리 영역(RED4A)을 포함할 수 있다. 제1 회로(153A)는 제1 블록(BLK1A), 제2 블록(BLK2A) 및 제1 감지 증폭기(SA1A)를 포함할 수 있다.

- [0054] 일반 메모리 영역(151)은 제1 하위 일반 메모리 영역(NOR1A), 제2 하위 일반 메모리 영역(NOR2A), 제3 하위 일반 메모리 영역(NOR3A) 및 제4 하위 일반 메모리 영역(NOR4A)을 포함할 수 있다. 여분 메모리 영역(152)은 제1하위 여분 메모리 영역(RED1A), 제2 하위 여분 메모리 영역(RED3A) 및 제4하위 여분 메모리 영역(RED4A)을 포함할 수 있다.

- [0055] 제1 하위 일반 메모리 영역(NOR1A)은 블록 어드레스(BLOCK ADDR)가 0의 값을 가지고, 일반 메모리 영역 어드레스(NOR ADDR)가 0에서 1023의 값을 가지는 경우에 상응하고, 제1 하위 여분 메모리 영역(RED1A)은 블록 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지는 경우에 상응한다. 제2 하위 일반 메모리 영역(NOR2A)은 블록 어드레스(BLOCK ADDR)가 1의 값을 가지고, 일반 메모리 영역 어드레스(NOR ADDR)가 0에서 1023의 값을 가지는 경우에 상응하고, 제2 하위 여분 메모리 영역(RED2A)은 블록 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지는 경우에 상응한다. 제3 하위 일반 메모리 영역(NOR3A)은 블록 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지고, 일반 메모리 영역 어드레스(NOR ADDR)가 0에서 1023의 값을 가지는 경우에 상응하고, 제3 하위 여분 메모리 영역(RED3A)은 블록 어드레스(BLOCK ADDR)가 0에서 1023의 값을 가지는 경우에 상응하고, 제3 하위 여분 메모리 영역(RED3A)은 블록 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지고, 일반 메모리 영역 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지고, 일반 메모리 영역 어드레스(BLOCK ADDR)가 3의 값을 가지고, 일반 메모리 영역 어드레스(BLOCK ADDR)가 3의 값을 가지고, 일반 메모리 영역 어드레스(NOR ADDR)가 0에서 1023의 값을 가지는 경우에 상응하고, 제4 하위 여분 메모리 영역(RED4A)은 블록 어드레스(BLOCK ADDR)가 0에서 15의 값을 가지는 경우에 상응한다.

- [0056] 제1 감지 증폭기(SA1A)는 제1 블록(BLK1A)과 제2 블록(BLK2A) 사이에 위치하고, 제2 감지 증폭기(SA2A)는 제2 블록(BLK2A)과 제3 블록(BLK3A) 사이에 위치하고, 제3 감지 증폭기(SA3A)는 제3 블록(BLK3A)과 제4 블록(BLK4A) 사이에 위치할 수 있다.

- [0057] 제1 감지 증폭기(SA1A)는 제1 하위 일반 메모리 영역(NOR1A) 및 제1 하위 여분 메모리 영역(RED1A)에 저장된 신호들을 증폭하여 데이터 신호(DATA)를 생성할 수 있다. 제2 감지 증폭기(SA2A)는 제2 하위 일반 메모리 영역(NOR2A) 및 제2 하위 여분 메모리 영역(RED2A)에 저장된 신호들을 증폭하여 데이터 신호(DATA)를 생성할 수 있다. 제3 감지 증폭기(SA3A)는 제3 하위 일반 메모리 영역(NOR3A) 및 제3 하위 여분 메모리 영역(RED3A)에 저장된 신호들을 증폭하여 데이터 신호(DATA)를 생성할 수 있다. 제4 감지 증폭기(SA4A)는 제4 하위 일반 메모리 영역(NOR4A) 및 제4 하위 여분 메모리 영역(RED4A)에 저장된 신호들을 증폭하여 데이터 신호(DATA)를 생성할 수 있다.

- [0058] 상기 제1 일반 메모리 영역 신호들은 제1 내지 제4 하위 일반 메모리 영역들(NOR1A, NOR2A, NOR3A 및 NOR4A)에 상응하고, 상기 제1 여분 메모리 영역 신호는 제1 내지 제4 하위 여분 메모리 영역들(RED1A, RED2A, RED3A 및 RED4A)에 상응할 수 있다.

- [0059] 도 5는 도 4의 메모리 셀 어레이에 포함되는 제1 회로를 나타내는 회로도이다.

- [0060] 도 5는 도 4의 메모리 셀 어레이(150A)가 제5 블록(BLK5A)을 더 포함하는 경우를 설명한다. 제5 블록(BLK5A)은 제5 하위 일반 메모리 영역(NOR5A) 및 제5 하위 여분 메모리 영역(RED5A)을 포함할 수 있다.

- [0061] 제1 블록(BLK1A)은 제1 메모리 셀(C11) 및 제5 메모리 셀(C13)을 포함할 수 있다. 제2 블록(BLK2A)은 제2 메모리 셀(C21), 제4 메모리 셀(C22), 제6 메모리 셀(C23) 및 제8 메모리 셀(C24)을 포함할 수 있다.

- [0062] 제1 메모리 셀(C11)에 연결된 제1 워드 라인(WL1) 및 제1 비트 라인 (BL1)이 활성화되고, 제2 메모리 셀(C21)에 연결된 제2 워드 라인(WL2)이 비활성화되고, 제2 메모리 셀(C21)에 연결된 제1 반전 비트 라인(BL1B)이 활성화된 전 경우, 제1 감지 증폭기(SA1A)에 포함되는 제1 감지 증폭 셀(154A)은 제1 메모리 셀(C11)의 데이터 신호를 제1 메모리 셀(C11)에 상응하는 제2 메모리 셀(C21)의 기준 신호에 기초하여 증폭하여 출력 신호들(SAL1, /SAL1)을 생성할 수 있다.

- [0063] 제5 메모리 셀(C13)에 연결된 제1 워드 라인(WL1) 및 제3 비트 라인 (BL3)이 활성화되고, 제6 메모리 셀(C23)에 연결된 제2 워드 라인(WL2)이 비활성화되고, 제6 메모리 셀(C23)에 연결된 제3 반전 비트 라인(BL3B)이 활성화된 경우, 제1 감지 증폭기(SA1A)에 포함되는 제2 감지 증폭 셀(155A)은 제5 메모리 셀(C13)의 데이터 신호를 제5 메모리 셀(C13)에 상응하는 제6 메모리 셀(C23)의 기준 신호에 기초하여 증폭하여 출력 신호들(SAL1, /SAL1)을 생성할 수 있다.

- [0064] 제2 감지 증폭기(SA2A)는 제2 블록(BLK2A)의 기준 신호들에 기초하여 제1 블록(BLK1A)에 포함된 제4 및 제8 메

모리 셀들(C22, C24)의 데이터 신호들을 증폭하여 출력 신호들(SAL2, /SAL2)을 생성할 수 있다.

- [0065] 제3 및 제7 메모리 셀들(C12, C14)이 제1 블록(BLK1A)에 포함되는 경우 제3 및 제7 메모리 셀들(C12, C14)의 데이터 신호는 기준 신호가 제1 블록(BLK1A)의 좌측에 존재하지 않기 때문에 감지 증폭기에 의해 증폭될 수 없다. 제3 및 제7 메모리 셀들(C12, C14)은 제1 블록(BLK1A)이 아닌 제5 블록(BLK5A)에 위치할 수 있고, 제4 감지 증폭기(SA4A)는 제4 블록(BLK4A)의 기준 신호들에 기초하여 제3 및 제7 메모리 셀들(C12, C14)의 데이터 신호들을 증폭하여 출력 신호들(SAL4, /SAL4)을 생성할 수 있다.

- [0066] 제2 블록(BLK2A), 제3 블록(BLK3A) 및 제4 블록(BLK4A)은 상기 설명에 기초하여 이해할 수 있으므로 설명을 생략한다.

- [0067] 이 경우, 제1 블록(BLK1A), 제3 블록(BLK3A) 및 제5 블록(BLK5A)에 저장되는 데이터와 제2 블록(BLK2A) 및 제4 블록(BLK4A)에 저장되는 데이터는 서로 반전 상태를 가지게 된다. 일 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들이 제1 하위 일반 메모리 영역(NOR1A)에 상응하는 경우, 상기 제1 여분 메모리 영역(RED5A)에 상응할 수 있으나, 상기 제1 여분 메모리 영역(RED3A) 및 제5 하위 여분 메모리 영역(RED5A)에 상응할 수 있으나, 상기 제1 여분 메모리 영역 신호는 제2 하위 여분 메모리 영역(RED2A) 및 제4 하위 여분 메모리 영역(RED4A)에 상응할 수 없다. 다른 실시예에 있어서, 상기 제1 일반 메모리 영역 신호들이 제2 하위 일반 메모리 영역(NOR2A)에 상응하는 경우, 상기 제1 여분 메모리 영역 신호는 제2 하위 여분 메모리 영역(RED2A) 및 제4 하위 여분 메모리 영역(RED4A)에 상응할 수 있으나, 상기 제1 여분 메모리 영역 신호는 제1 하위 여분 메모리 영역(RED1A), 제3 하위 여분 메모리 영역(RED3A) 및 제5 하위 여분 메모리 영역(RED5A)에 상응할 수 없다. 나머지 경우는 상기 설명에 기초하여 이해할 수 있으므로 설명을 생략한다.

- [0068] 도 6은 도 1의 메모리 장치에 포함되는 메모리 셀 어레이의 다른 실시예를 나타내는 블록도들이다.

- [0069] 도 6의 메모리 셀 어레이(150B)는 하위 여분 메모리 영역의 위치를 제외하고 도 4의 메모리 셀 어레이(150A)와 동일 또는 유사하다.

- [0070] 제1 블록(BLK1B)은 제1 하위 일반 메모리 영역(NOR1B)을 포함한다. 제2 블록(BLK2B)은 제2 하위 일반 메모리 영역(NOR2B)을 포함한다. 제3 블록(BLK3B)은 제3 하위 일반 메모리 영역(NOR3B) 및 하위 여분 메모리 영역(RED3 B)을 포함한다. 제4 블록(BLK4B)은 제4 하위 일반 메모리 영역(NOR4B)을 포함한다. 제5 블록(BLK5B)은 제5 하위 일반 메모리 영역(NOR5B)을 포함한다.

- [0071] 상기 제1 일반 메모리 영역 신호들은 제1 내지 제5 하위 일반 메모리 영역(NOR1B, NOR2B, NOR3B, NOR4B 및 NOR5B)에 상응하고, 상기 제1 여분 메모리 영역 신호는 하위 여분 메모리 영역(RED3B)에 상응할 수 있다.

- [0072] 도 7은 도 1의 메모리 장치에 포함되는 차단 신호 생성기를 나타내는 블록도이다.

- [0073] 도 7을 참조하면, 차단 신호 생성기(140)는 논리합 연산기(142)를 포함한다. 논리합 연산기(142)는 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)의 논리합 연산 결과를 차단 신호(BS)로서 출력할 수 있다.

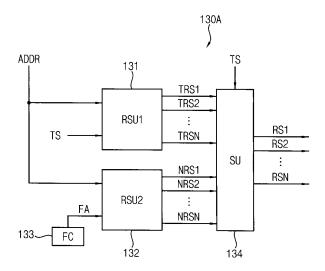

- [0074] 도 8은 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기의 일 실시예를 나타내는 블록도이다.

- [0075] 도 8을 참조하면, 여분 메모리 영역 신호 생성기(130A)는 제1 여분 메모리 영역 신호 생성 유닛(RSU1; 131), 제 2 여분 메모리 영역 신호 생성 유닛(RSU2; 132) 및 선택 유닛(SU; 134)을 포함할 수 있다.

- [0076] 제1 여분 메모리 영역 신호 생성 유닛(131)은 어드레스 신호(ADDR)에 기초하여 복수의 일반 메모리 영역 신호들 (NS1 내지 NSP)이 각각 한 번씩 활성화 되는 동안, 각각 한 번씩 활성화되는 제1 내부 여분 메모리 영역 신호들 (TRS1, TRS2 내지 TRSN)을 생성할 수 있다. 제2 여분 메모리 영역 신호 생성 유닛(132)은 퓨즈 회로(FC; 133)에 포함된 불량 어드레스 값들(FA)과 어드레스 신호(ADDR)의 값을 비교하여 제2 내부 여분 메모리 영역 신호들 (NRS1, NRS2 내지 NRSN)을 생성할 수 있다. 선택 유닛(134)은 테스트 신호(TS)가 논리 하이 레벨을 갖는 경우 제1 내부 여분 메모리 영역 신호들(TRS1, TRS2 내지 TRSN)을 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력하고, 테스트 신호(TS)가 논리 로우 레벨을 갖는 경우 제2 내부 여분 메모리 영역 신호들(NRS1, NRS2 내지 NRSN)을 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력할 수 있다.

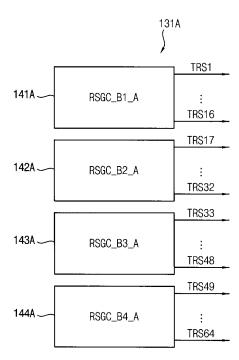

- [0077] 도 9는 도 8의 여분 메모리 영역 신호 생성기에 포함되는 제1 여분 메모리 영역 신호 생성 유닛의 일 실시예를 나타내는 블록도이다.

- [0078] 도 9는 N이 64이고, 메모리 셀 어레이(150)가 도 4의 구조를 가지는 경우의 제1 여분 메모리 영역 신호 생성 유닛(131A)을 도시한다. 제1 여분 메모리 영역 신호 생성 유닛(131A)은 제1 블록 신호 생성 회로(RSGC\_B1\_A;

141A), 제2 블록 신호 생성 회로(RSGC\_B2\_A; 142A), 제3 블록 신호 생성 회로(RSGC\_B3\_A; 143A) 및 제4 블록 신호 생성 회로(RSGC\_B4\_A; 144A)를 포함한다.

- [0079] 도 8의 제1 내부 여분 메모리 영역 신호들(TRS1, TRS2 내지 TRSN)은 제1 블록 신호들(TRS1 내지 TRS16), 제2 블록 신호들(TRS17 내지 TRS32), 제3 블록 신호들(TRS33 내지 TRS48) 및 제4 블록 신호들(TRS49 내지 TRS64)을 포함한다. 제1 블록 신호 생성 회로(141A)는 제1 블록(BLK1A)에 상응하는 제1 블록 신호들(TRS1 내지 TRS16)을 출력한다. 제2 블록 신호 생성 회로(142A)는 제2 블록(BLK2A)에 상응하는 제2 블록 신호들(TRS17 내지 TRS32)을 출력한다. 제3 블록 신호 생성 회로(143A)는 제3 블록(BLK3A)에 상응하는 제3 블록 신호들(TRS33 내지 TRS48)을 출력한다. 제4 블록 신호 생성 회로(144A)는 제4 블록(BLK4A)에 상응하는 제4 블록 신호들(TRS49 내지 TRS64)을 출력한다.

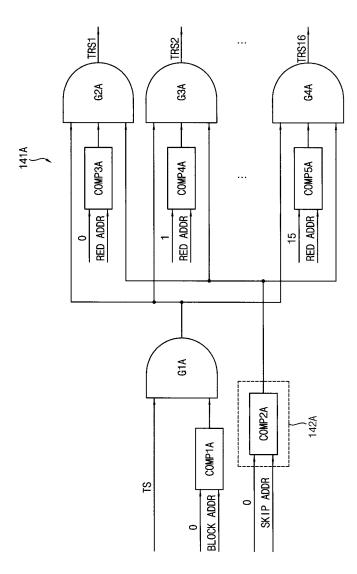

- [0080] 도 10은 도 9의 제1 여분 메모리 영역 신호 생성 유닛에 포함되는 제1 블록 신호 생성 회로를 나타내는 블록도 이다.

- [0081] 도 10을 참조하면, 제1 블록 신호 생성 회로(141A)는 활성화 빈도 조절기(142A), 제1 논리곱 게이트(G1A), 제2 논리곱 게이트(G2A), 제3 논리곱 게이트(G3A), 제4 논리곱 게이트(G4A), 제1 비교기(COMP1A), 제3 비교기(COMP3A), 제4 비교기(COMP4A) 및 제5 비교기(COMP5A)를 포함한다. 활성화 빈도 조절기(142A)는 제2 비교기(COMP2A)를 포함한다.

- [0082] 도 2 및 3에서 K는 13, L은 10, M은 4의 값을 갖고, 일반 메모리 영역 신호 생성기(120)가 도 1의 복수의 일반 메모리 영역 신호들(NS1 내지 NSP) 중 5개의 신호를 동시에 상기 제1 일반 메모리 영역 신호들로서 활성화하기 위해 어드레스 신호(ADDR)의 세 번째 비트(RA2), 다섯 번째 비트(RA4), 여섯 번째 비트(RA5), 여덟 번째 비트(RA7) 및 아홉 번째 비트(RA8)를 무정의 어드레스(Don't care address)로 사용하는 경우, 일반 메모리 영역 신호 생성기(120)는 실질적으로 어드레스 신호(ADDR)의 첫 번째 비트(RA0), 두 번째 비트(RA1), 네 번째 비트(RA3), 일곱 번째 비트(RA6) 및 열 번째 비트(RA9)를 사용하고, 여분 메모리 영역 신호 생성기(130)는 실질적으로 어드레스 신호(ADDR)의 첫 번째 비트(RA1) 및 네 번째 비트(RA3)를 사용한다. 어드레스 신호(ADDR)를 순차적으로 0부터 1023까지 증가시키면서 메모리 셀 어레이(150)를 테스트할 경우, 여분 메모리 영역(152)은 일반 메모리 영역(151)보다 4배 더 많은 테스트가 이루어지게 되는 문제가 있다.

- [0083] 활성화 빈도 조절기(142A)는 어드레스 신호(ADDR)의 일부(SKIP ADDR)가 사용자가 미리 정한 값(0)과 상이할 때제1 블록 신호들(TRS1 내지 TRS16)을 비활성화할 수 있다. 일 실시예에 있어서, 어드레스 신호(ADDR)의 일부(SKIP ADDR)를 어드레스 신호의 일곱 번째 비트(RA6) 및 열 번째 비트(RA9)로 정하고, 어드레스 신호의 일곱 번째 비트(RA6) 및 열 번째 비트(RA6) 및 열 번째 비트(RA9)가 사용자가 미리 정한 값인 0을 가질 때 제1 블록 신호들(TRS1, TRS2 내지 TRS16)을 활성하게 되는 경우, 일반 메모리 영역(151)과 제1 블록(BLK1A)은 동일한 빈도로 테스트될 수 있다. 상기 사용자가 미리 정한 값은 0이 아닌 다른 자연수 일 수 있다.

- [0084] 제1 비교기(COMP1A)는 블록 어드레스(BLOCK ADDR)가 0의 값을 가지는 경우 논리 하이 레벨을 출력하고, 블록 어 드레스(BLOCK ADDR)가 0 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제1 게이트(G1A)는 테스트 신호 (TS)와 제1 비교기(COMP1A)의 출력 신호를 논리곱 연산한 결과를 출력한다. 제2 비교기(COMP2A)는 어드레스 신 호(ADDR)의 일부(SKIP ADDR)가 0의 값을 가지는 경우 논리 하이 레벨을 출력하고, 어드레스 신호(ADDR)의 일부 (SKIP ADDR)가 0 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제3 비교기(COMP3A)는 여분 메모리 영역 어드레스(RED ADDR)가 0의 값을 가지는 경우 논리 하이 레벨을 출력하고, 여분 메모리 영역 어드레스(RED ADD R)가 0 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제2 게이트(G2A)는 제1 게이트(G1A)의 출력 신호, 제3 비교기(COMP3A)의 출력 신호 및 제2 비교기(COMP2A)의 출력 신호를 논리곱 연산한 결과를 제1 블록 내부 신 호(TRS1)로서 출력한다. 제4 비교기(COMP4A)는 여분 메모리 영역 어드레스(RED ADDR)가 1의 값을 가지는 경우 논리 하이 레벨을 출력하고, 여분 메모리 영역 어드레스(RED ADDR)가 1 이외의 값을 가지는 경우 논리 로우 레 벨을 출력한다. 제3 게이트(G3A)는 제1 게이트(G1A)의 출력 신호, 제4 비교기(COMP4A)의 출력 신호 및 제2 비교 기(COMP2A)의 출력 신호를 논리곱 연산한 결과를 제2 블록 내부 신호(TRS2)로서 출력한다. 제5 비교기(COMP5A) 는 여분 메모리 영역 어드레스(RED ADDR)가 15의 값을 가지는 경우 논리 하이 레벨을 출력하고, 여분 메모리 영 역 어드레스(RED ADDR)가 15 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제4 게이트(G4A)는 제1 게이 트(G1A)의 출력 신호, 제5 비교기(COMP5A)의 출력 신호 및 제2 비교기(COMP2)의 출력 신호를 논리곱 연산한 결 과를 제16 블록 내부 신호(TRS16)로서 출력한다.

- [0085] 도 11은 도 8의 여분 메모리 영역 신호 생성기에 포함되는 제1 여분 메모리 영역 신호 생성 유닛의 다른 실시예를 나타내는 블록도이다.

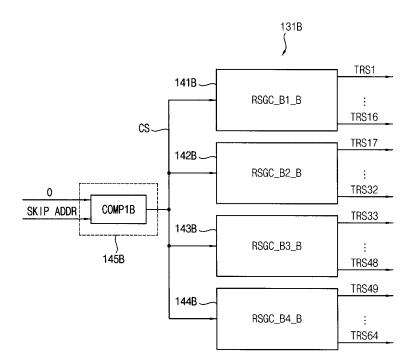

- [0086] 도 11은 N이 64이고, 메모리 셀 어레이(150)가 도 4의 구조를 가지는 경우의 제1 여분 메모리 영역 신호 생성 유닛(131B)을 도시한다. 제1 여분 메모리 영역 신호 생성 유닛(131B)은 제1 블록 신호 생성 회로(RSGC\_B1\_B; 141B), 제2 블록 신호 생성 회로(RSGC\_B2\_B; 142B), 제3 블록 신호 생성 회로(RSGC\_B3\_B; 143B) 및 제4 블록 신호 생성 회로(RSGC\_B4\_B; 144B) 및 활성화 빈도 조절기(145B)를 포함한다.

- [0087] 활성화 빈도 조절기(145B)는 어드레스 신호(ADDR)의 일부(SKIP ADDR)와 사용자가 미리 정한 값(0)을 비교한 결과를 비교 신호(CS)로서 출력한다. 상기 사용자가 미리 정한 값은 0이 아닌 다른 자연수 일 수 있다. 활성화 빈도 조절기(145B)는 제1 비교기(COMP1B)를 포함한다. 제1 비교기(COMP1B)는 어드레스 신호(ADDR)의 일부(SKIP ADDR)가 0의 값을 가지는 경우 비교 신호(CS)로서 논리 하이 레벨을 출력하고, 어드레스 신호(ADDR)의 일부(SKIP ADDR)가 0 이외의 값을 가지는 경우 비교 신호(CS)로서 논리 로우 레벨을 출력한다.

- [0088] 제1 블록 신호 생성 회로(141B)는 비교 신호(CS)에 기초하여 제1 블록(BLK1A)에 상응하는 제1 블록 신호들(TRS1 내지 TRS16)을 출력한다. 제2 블록 신호 생성 회로(142B)는 비교 신호(CS)에 기초하여 제2 블록(BLK2A)에 상응하는 제2 블록 신호들(TRS17 내지 TRS32)을 출력한다. 제3 블록 신호 생성 회로(143B)는 비교 신호(CS)에 기초하여 제3 블록(BLK3A)에 상응하는 제3 블록 신호들(TRS33 내지 TRS48)을 출력한다. 제4 블록 신호 생성 회로 (144B)는 비교 신호(CS)에 기초하여 제4 블록(BLK4A)에 상응하는 제4 블록 신호들(TRS49 내지 TRS64)을 출력한다.

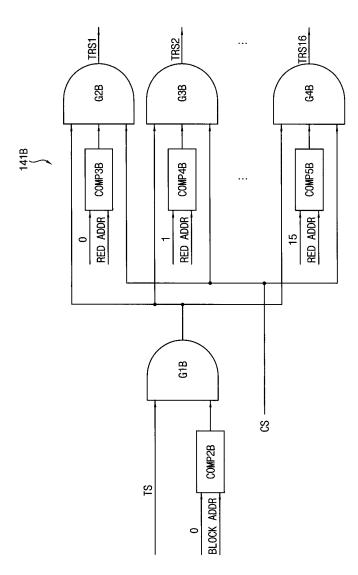

- [0089] 도 12는 도 11의 제1 여분 메모리 영역 신호 생성 유닛에 포함되는 제1 블록 신호 생성 회로를 나타내는 블록도 이다.

- [0090] 제2 비교기(COMP2B)는 블록 어드레스(BLOCK ADDR)가 0의 값을 가지는 경우 논리 하이 레벨을 출력하고, 블록 어드레스(BLOCK ADDR)가 0 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제1 게이트(G1B)는 테스트 신호 (TS)와 제2 비교기(COMP2B)의 출력 신호를 논리곱 연산한 결과를 출력한다. 제3 비교기(COMP3B)는 여분 메모리 영역 어드레스(RED ADDR)가 0의 값을 가지는 경우 논리 하이 레벨을 출력하고, 여분 메모리 영역 어드레스(RED ADDR)가 0 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제2 게이트(G2B)는 제1 게이트(G1B)의 출력 신호, 제3 비교기(COMP3B)의 출력 신호 및 비교 신호(CS)를 논리곱 연산한 결과를 제1 블록 내부 신호(TRS1)로서 출력한다. 제4 비교기(COMP4B)는 여분 메모리 영역 어드레스(RED ADDR)가 1의 값을 가지는 경우 논리 하이 레벨을 출력하고, 여분 메모리 영역 어드레스(RED ADDR)가 1 이외의 값을 가지는 경우 논리 로우 레벨을 출력한다. 제3 게이트(G3B)는 제1 게이트(G1B)의 출력 신호, 제4 비교기(COMP4B)의 출력 신호 및 비교 신호(CS)를 논리곱 연산한 결과를 제2 블록 내부 신호(TRS2)로서 출력한다. 제5 비교기(COMP5B)는 여분 메모리 영역 어드레스(RED ADDR)가 15의 값을 가지는 경우 논리 라이 레벨을 출력하고, 여분 메모리 영역 어드레스(RED ADDR)가 15의 값을 가지는 경우 논리 라이 레벨을 출력한다. 제4 게이트(G4B)는 제1 게이트(G1B)의 출력 신호, 제5 비교기(COMP5B)의 출력 신호 및 비교 신호(CS)를 논리곱 연산한 결과를 제16 블록 내부 신호(TRS16)로서 출력한다.

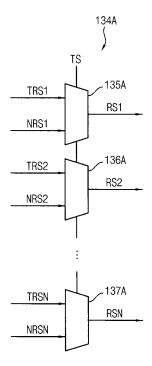

- [0091] 도 13은 도 8의 여분 메모리 영역 신호 생성기에 포함되는 선택 유닛의 일 실시예를 나타내는 블록도이다.

- [0092] 도 13을 참조하면, 선택 유닛(134A)은 멀티플렉서들(135A, 136A, 137A)을 포함할 수 있다. 멀티플렉서들(135A, 136A, 137A)은 테스트 신호(TS)가 논리 하이 레벨을 가지는 경우 제1 내부 여분 메모리 영역 신호들(TRS1, TRS2 내지 TRSN)을 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력할 수 있다. 멀티플렉서들(135A, 136A, 137A)은 테스트 신호(TS)가 논리 로우 레벨을 가지는 경우 제2 내부 여분 메모리 영역 신호들(NRS1, NRS2 내지 NRSN)을 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력할 수 있다.

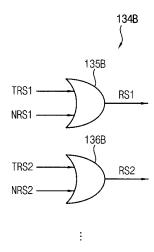

- [0093] 도 14는 도 8의 여분 메모리 영역 신호 생성기에 포함되는 선택 유닛의 다른 실시예를 나타내는 블록도이다.

- [0094] 도 14를 참조하면, 선택 유닛(134B)은 논리합 연산기들(135B, 136B, 137B)을 포함할 수 있다. 논리합 연산기들 (135B, 136B, 137B)은 제1 내부 여분 메모리 영역 신호들(TRS1, TRS2 내지 TRSN)과 제2 내부 여분 메모리 영역 신호들(NRS1, NRS2 내지 NRSN)을 비트 단위로 논리합 연산하여 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)을 출력할 수 있다.

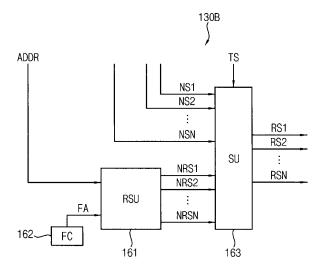

- [0095] 도 15는 도 1의 메모리 장치에 포함되는 여분 메모리 영역 신호 생성기의 다른 실시예를 나타내는 블록도이다.

- [0096] 도 15를 참조하면, 여분 메모리 영역 신호 생성기(130B)는 여부 메모리 영역 신호 생성 유닛(RSU; 151) 및 선택 유닛(SU)을 포함할 수 있다. 여분 메모리 영역 신호 유닛(RSU; 161)은 퓨즈 회로(FC; 162)에 포함된 불량 어드 레스 값들(FA)과 어드레스 신호(ADDR)의 값을 비교하여 내부 여분 메모리 영역 신호들(NRS1, NRS2 내지 NRSN)을 생성할 수 있다. 선택 유닛(163)은 테스트 신호(TS)가 논리 하이 레벨을 갖는 경우 복수의 일반 메모리 영역 신

호들(NS1, NS2 내지 NSP) 중 일부(NS1, NS2 내지 NSN)를 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력하고, 테스트 신호(TS)가 논리 로우 레벨을 갖는 경우 내부 여분 메모리 영역 신호들(NRS1, NRS2 내지 NRSN)을 복수의 여분 메모리 영역 신호들(RS1, RS2 내지 RSN)로서 출력할 수 있다.

- [0097] 일 실시예에 있어서, 선택 유닛(163)은 복수의 일반 메모리 영역 신호들(NS1, NS2 내지 NSP) 중 일부(NS1, NS2 내지 NSN) 대신 복수의 일반 메모리 영역 신호들(NS1, NS2 내지 NSP)에 포함되는 다른 일부 일반 메모리 영역 신호들을 입력받을 수 있다.

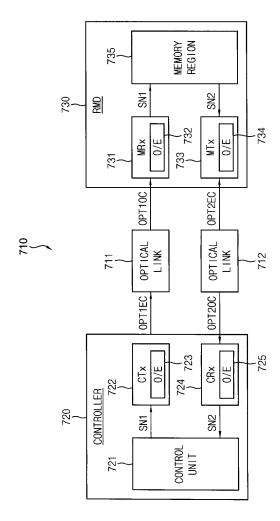

- [0098] 도 16은 본 발명의 실시예들에 따른 메모리 장치를 포함하는 메모리 시스템을 나타내는 블록도이다.

- [0099] 도 16을 참조하면, 메모리 시스템(710)은 광 연결 장치들(711, 712)과 컨트롤러(720) 그리고 메모리 장치(730)를 포함한다. 광 연결 장치들(711, 712)은 컨트롤러(720)와 메모리 장치(730)를 상호 연결한다(interconnect). 컨트롤러(720)는 컨트롤 유닛(721), 제1 송신부(722), 제1 수신부(724)를 포함한다. 컨트롤 유닛(721)은 제1 전기 신호(SN1)를 제1 송신부(722)로 전송한다. 제1 전기 신호(SN1)는 메모리 장치(730)로 전송되는 커맨드 신호들, 클럭킹 신호들, 어드레스 신호들 또는 기입 데이터 등으로 구성될 수 있다.

- [0100] 제1 송신부(722)는 제1 광 변조기(723)를 포함하고, 제1 광 변조기(723)는 제1 전기 신호(SN1)를 제1 광 송신신 호(OTP1EC)로 변환하여 광 연결 장치(711)로 전송한다. 제1 광 송신 신호(OTP1EC)는 광 연결 장치(711)를 통하여 시리얼 통신으로 전송된다. 제1 수신부(724)는 제1 광 복조기(725)를 포함하고, 제1 광 복조기(725)는 광 연결 장치(712)로부터 수신된 제2 광 수신 신호(OPT20C)를 제2 전기 신호(SN2)로 변환하여 컨트롤 유닛(721)으로 전송한다.

- [0101] 메모리 장치(730)는 제2 수신부(731), 저항성 메모리 셀들이나 동적 메모리 셀들로 구현되는 메모리 셀을 구비하는 메모리 영역(735) 및 제2 송신부(733)를 포함한다. 제2 수신부(731)는 제2 광 복조기(732)를 포함하고, 제2 광 복조기(732)는 광 연결 장치(711)로부터 제1 광 수신 신호(OPT10C)를 제1 전기 신호(SN1)로 변환하여 메모리 영역(735)으로 전송한다.

- [0102] 메모리 영역(735)에서는 제1 전기 신호(SN1)에 응답하여 기입 데이터를 메모리 셀들 기입하거나 메모리 영역 (735)으로부터 독출된 데이터를 제2 전기 신호(SN2)로서 제2 송신부(733)로 전송한다. 제2 전기 신호(SN2)는 컨트롤러(720)로 전송되는 클럭킹 신호, 독출 데이터 등으로 구성될 수 있다. 제2 송신부(733)는 제2 광변조기 (734)를 포함하고, 제2 광변조기(734)는 제2 전기 신호(SN2)를 제2 광 데이터 신호(OPT2EC)로 변환하여 광 연결 장치(712)로 전송한다. 제2 광 송신 신호(OTP2EC)는 광 연결 장치(712)를 통하여 시리얼 통신으로 전송된다. 메모리 영역(735)은 도 1의 메모리 장치(100)로 구현될 수 있다. 메모리 영역(735)의 구조에 대하여 도 1 내지 15를 참조하여 이해할 수 있으므로 설명을 생략한다.

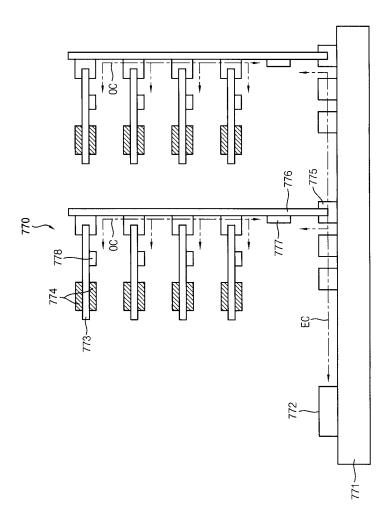

- [0103] 도 17은 본 발명의 실시예들에 따른 메모리 장치를 포함하는 서버 시스템을 나타낸다.

- [0104] 도 17을 참조하면, 서버 시스템(770)은 메모리 컨트롤러(772) 및 복수의 메모리 모듈들(773)을 구비한다. 각각의 메모리 모듈(773)은 복수의 반도체 메모리 칩들(774)을 포함할 수 있다. 반도체 메모리 칩(774)은 저항성 메모리 셀들 또는 동적 메모리 셀들을 포함하는 메모리 셀 어레이를 구비할 수 있다. 각각의 메모리 모듈(773)은 도 1의 메모리 장치(100)로 구현될 수 있다.

- [0105] 서버 시스템(770)은 제1 회로 기판(771)의 소켓들(775)에 제2 회로 기판(776)이 결합되는 구조를 가질 수 있다. 서버 시스템(770)은 신호 채널 별로 하나의 제2 회로 기판(776)이 제1 회로 기판(771)과 연결되는 채널 구조를 가질 수 있다.

- [0106] 한편, 메모리 모듈들(773)의 신호의 전달이 광학적 입출력 접속(Optical IO Connection)으로 수행될 수 있다. 광학적 입출력 접속을 위해, 서버 시스템(770)은 전-광 변환 유닛(777)을 더 포함할 수 있으며, 메모리 모듈들 (773) 각각은 광-전 변환 유닛(778)을 더 포함할 수 있다.

- [0107] 메모리 컨트롤러(772)는 전기적 채널(EC)을 통하여 전-광 변환 유닛(777)에 접속된다. 전-광 변환 유닛(777)은 전기적 채널(EC)을 통하여 메모리 컨트롤러(772)로부터 수신된 전기적 신호를 광 신호로 변환시켜 광 채널(OC) 측으로 전달한다. 또한, 전-광 변환 유닛(777)은 광 채널(OC)을 통하여 수신되는 광 신호를 전기적 신호로 변환시켜 전기적 채널(EC) 측으로 전달하는 신호 처리를 실행한다.

- [0108] 메모리 모듈들(773)은 광 채널(0C)을 통하여 전-광 변환 유닛(777)과 접속된다. 메모리 모듈(773)로 인가된 광 신호는 광-전 변환 유닛(778)을 통해 전기적 신호로 변환되어 저항성 메모리 칩들(774)로 전달될 수 있다. 이와

같은 광 연결 메모리 모듈들로 구성된 서버 시스템(770)은 높은 저장 용량과 빠른 처리 속도를 지원할 수 있다.

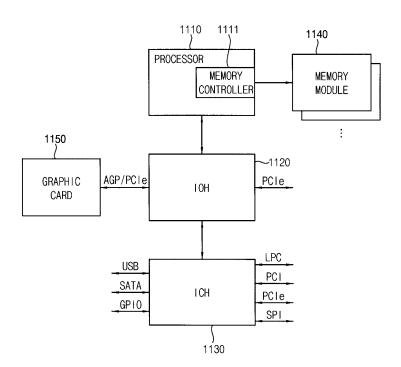

- [0109] 도 18은 본 발명의 실시예들에 따른 메모리 장치가 장착된 컴퓨팅 시스템을 나타내는 블록도이다.

- [0110] 도 18을 참조하면, 컴퓨팅 시스템(1000)은 모바일 기기나 데스크 톱 컴퓨터 등에 장착될 수 있다. 컴퓨팅 시스템(1000)은 시스템 버스(1005)에 전기적으로 연결되는 메모리 시스템(1010), 중앙 처리 장치(CPU, 1020), RAM(1030), 사용자 인터페이스(1040) 및 베이스밴드 칩셋(Baseband chipset)과 같은 모뎀(1050)을 포함할 수 있다. 컴퓨팅 시스템(1000)은 응용 칩셋(Application Chipset), 카메라 이미지 프로세서(Camera Image Processor: CIS), 입출력 장치 등을 더 포함할 수 있다.

- [0111] 사용자 인터페이스(1040)는 통신 네트워크로 데이터를 전송하거나 통신 네크워크로부터 데이터를 수신하기 위한 인터페이스일 수 있다. 사용자 인터페이스(1040)는 통신 네트워크로 데이터를 전송하거나 통신 네크워크로부터 데이터를 수신하기 위한 인터페이스일 수 있다. 사용자 인터페이스(1040)는 유무선 형태일 수 있고, 안테나 또는 유무선 트랜시버 등을 포함할 수 있다. 사용자 인터페이스(1040) 또는 모뎀(1050)을 통해 제공되거나 중앙처리 장치(1020)에 의해서 처리된 데이터는 메모리 시스템(1010)에 저장될 수 있다.

- [0112] 메모리 시스템(1010)은 메모리 장치(1012)와 메모리 컨트롤러(1011)를 포함할 수 있다. 메모리 장치(1012)에는 중앙 처리 장치(1020)에 의해서 처리된 데이터 또는 외부에서 입력된 데이터가 저장된다. 메모리 장치(1012)는 도 1의 메모리 장치(100)로 구현될 수 있다. 메모리 장치(1012)는 도 1 내지 15를 참조하여 이해할 수 있으므로 설명을 생략한다.

- [0113] 컴퓨팅 시스템(1000)이 무선 통신을 수행하는 장비인 경우, 컴퓨팅 시스템(1000)은 CDMA(Code Division Multiple Access), GSM(Global System for Mobile communication), NADC(North American Multiple Access), CDMA2000과 같은 통신 시스템에서 사용될 수 있다. 컴퓨터 시스템(740)은 개인 휴대용 정보 단말기(PDA: Personal Digital Assistant), 휴대용 컴퓨터, 웹 태블렛(web tablet), 디지털 카메라, PMP(Portable Media Player), 모바일 폰, 무선폰, 랩탑 컴퓨터와 같은 정보 처리 장치에 장착될 수 있다.

- [0114] 도 19는 본 발명의 실시예들에 따른 메모리 장치를 컴퓨팅 시스템에 응용한 다른 예를 나타내는 블록도이다.

- [0115] 도 19를 참조하면, 컴퓨팅 시스템(1100)은 프로세서(1110), 입출력 허브(1120), 입출력 컨트롤러 허브(1130), 적어도 하나의 메모리 모듈(1140) 및 그래픽 카드(1150)를 포함한다. 실시예에 따라, 컴퓨팅 시스템(1100)은 개인용 컴퓨터(Personal Computer; PC), 서버 컴퓨터(Server Computer), 워크스테이션(Workstation), 노트북(Laptop), 휴대폰(Mobile Phone), 스마트 폰(Smart Phone), 개인 정보 단말기(personal digital assistant; PDA), 휴대형 멀티미디어 플레이어(portable multimedia player; PMP), 디지털 카메라(Digital Camera), 디지털 TV(Digital Television), 셋-탑 박스(Set-Top Box), 음악 재생기(Music Player), 휴대용 게임 콘솔(portable game console), 네비게이션(Navigation) 시스템 등과 같은 임의의 컴퓨팅 시스템일 수 있다.

- [0116] 프로세서(1110)는 특정 계산들 또는 태스크들과 같은 다양한 컴퓨팅 기능들을 실행할 수 있다. 예를 들어, 프로세서(1110)는 마이크로프로세서 또는 중앙 처리 장치(Central Processing Unit; CPU)일 수 있다. 실시예에 따라, 프로세서(1110)는 하나의 프로세서 코어(Single Core)를 포함하거나, 복수의 프로세서 코어들(Multi-Core)을 포함할 수 있다. 예를 들어, 프로세서(1110)는 듀얼 코어(Dual-Core), 쿼드 코어(Quad-Core), 헥사 코어(Hexa-Core) 등의 멀티 코어(Multi-Core)를 포함할 수 있다. 또한, 도 21에는 하나의 프로세서(1110)를 포함하는 컴퓨팅 시스템(1100)이 도시되어 있으나, 실시예에 따라, 컴퓨팅 시스템(1100)은 복수의 프로세서들을 포함할 수 있다. 또한, 실시예에 따라, 프로세서(1110)는 내부 또는 외부에 위치한 캐시 메모리(Cache Memory)를 더 포함할 수 있다.

- [0117] 프로세서(1110)는 메모리 모듈(1140)의 동작을 제어하는 메모리 컨트롤러(1111)를 포함할 수 있다. 프로세서 (1110)에 포함된 메모리 컨트롤러(1111)는 집적 메모리 컨트롤러(Integrated Memory Controller; IMC)라 불릴 수 있다. 메모리 컨트롤러(1111)와 메모리 모듈(1140) 사이의 메모리 인터페이스는 복수의 신호선들을 포함하는 하나의 채널로 구현되거나, 복수의 채널들로 구현될 수 있다. 또한, 각 채널에는 하나 이상의 메모리 모듈 (1140)이 연결될 수 있다. 실시예에 따라, 메모리 컨트롤러(1111)는 입출력 허브(1120) 내에 위치할 수 있다. 메모리 컨트롤러(1111)를 포함하는 입출력 허브(1520)는 메모리 컨트롤러 허브(Memory Controller Hub; MCH)라 불릴 수 있다.

- [0118] 메모리 모듈(1140)은 메모리 컨트롤러(1111)로부터 제공된 데이터를 저장하는 메모리 장치들을 포함할 수 있다. 상기 메모리 장치들 각각은 도 1의 메모리 장치(100)로 구현될 수 있다. 상기 메모리 장치들은 도 1 내지 15를

참조하여 이해할 수 있으므로 설명을 생략한다.

- [0119] 입출력 허브(1120)는 그래픽 카드(1150)와 같은 장치들과 프로세서(1110) 사이의 데이터 전송을 관리할 수 있다. 입출력 허브(1120)는 다양한 방식의 인터페이스를 통하여 프로세서(1110)에 연결될 수 있다. 예를 들어, 입출력 허브(1120)와 프로세서(1110)는, 프론트 사이드 버스(Front Side Bus; FSB), 시스템 버스(System Bus), 하이퍼트랜스포트(HyperTransport), 라이트닝 데이터 트랜스포트(Lightning Data Transport; LDT), 퀵패스 인터커넥트(QuickPath Interconnect; QPI), 공통 시스템 인터페이스(Common System Interface; CSI) 등의 다양한 표준의 인터페이스로 연결될 수 있다. 도 19에는 하나의 입출력 허브(1120)를 포함하는 컴퓨팅 시스템(1100)이 도시되어 있으나, 실시예에 따라, 컴퓨팅 시스템(1100)은 복수의 입출력 허브들을 포함할 수 있다.

- [0120] 입출력 허브(1120)는 장치들과의 다양한 인터페이스들을 제공할 수 있다. 예를 들어, 입출력 허브(1120)는 가속 그래픽 포트(Accelerated Graphics Port; AGP) 인터페이스, 주변 구성요소 인터페이스-익스프레스(Peripheral Component Interface-Express; PCIe), 통신 스트리밍 구조(Communications Streaming Architecture; CSA) 인터페이스 등을 제공할 수 있다.

- [0121] 그래픽 카드(1150)는 AGP 또는 PCIe를 통하여 입출력 허브(1120)와 연결될 수 있다. 그래픽 카드(1150)는 영상을 표시하기 위한 디스플레이 장치(미도시)를 제어할 수 있다. 그래픽 카드(1150)는 이미지 데이터 처리를 위한 내부 프로세서 및 내부 메모리 장치를 포함할 수 있다. 실시예에 따라, 입출력 허브(1120)는, 입출력 허브(1120)의 외부에 위치한 그래픽 카드(1150)와 함께, 또는 그래픽 카드(1150) 대신에 입출력 허브(1120)의 내부에 그래픽 장치를 포함할 수 있다. 입출력 허브(1520)에 포함된 그래픽 장치는 집적 그래픽(Integrated Graphics)이라 불릴 수 있다. 또한, 메모리 컨트롤러 및 그래픽 장치를 포함하는 입출력 허브(1120)는 그래픽 및 메모리 컨트롤러 허브(Graphics and Memory Controller Hub; GMCH)라 불릴 수 있다.

- [0122] 입출력 컨트롤러 허브(1130)는 다양한 시스템 인터페이스들이 효율적으로 동작하도록 데이터 버퍼링 및 인터페이스 중재를 수행할 수 있다. 입출력 컨트롤러 허브(1130)는 내부 버스를 통하여 입출력 허브(1120)와 연결될 수 있다. 예를 들어, 입출력 허브(1120)와 입출력 컨트롤러 허브(1130)는 다이렉트 미디어 인터페이스(Direct Media Interface; DMI), 허브 인터페이스, 엔터프라이즈 사우스브릿지 인터페이스(Enterprise Southbridge Interface; ESI), PCIe 등을 통하여 연결될 수 있다.

- [0123] 입출력 컨트롤러 허브(1530)는 주변 장치들과의 다양한 인터페이스들을 제공할 수 있다. 예를 들어, 입출력 컨트롤러 허브(1130)는 범용 직렬 버스(Universal Serial Bus; USB) 포트, 직렬 ATA(Serial Advanced Technology Attachment; SATA) 포트, 범용 입출력(General Purpose Input/Output; GPIO), 로우 핀 카운트(Low Pin Count; LPC) 버스, 직렬 주변 인터페이스(Serial Peripheral Interface; SPI), PCI, PCIe 등을 제공할 수 있다.

- [0124] 실시예에 따라, 프로세서(1110), 입출력 허브(1120) 및 입출력 컨트롤러 허브(1130)는 각각 분리된 칩셋들 또는 집적 회로들로 구현되거나, 프로세서(1110), 입출력 허브(1120) 또는 입출력 컨트롤러 허브(1130) 중 2 이상의 구성요소들이 하나의 칩셋으로 구현될 수 있다.

#### 산업상 이용가능성

- [0125] 본 발명의 실시예들에 따른 메모리 장치는, 메모리 장치를 필요로 하는 임의의 장치 또는 시스템에 유용하게 이용될 수 있다. 특히 본 발명의 실시예들에 따른 메모리 장치는 컴퓨터(computer), 노트북(laptop), 핸드폰 (cellular), 스마트폰(smart phone), MP3 플레이어, 피디에이(Personal Digital Assistants; PDA), 피엠피 (Portable Multimedia Player; PMP), 디지털 TV, 디지털 카메라, 포터블 게임 콘솔(portable game console) 등과 같은 전자 기기에 유용하게 적용될 수 있다.

- [0126] 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 숙련된 당업자는 하기의 특 허청구범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 것이다.

## 도면1

### 도면2

1100