# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114726368 A (43) 申请公布日 2022.07.08

(21) 申请号 202210637748.7

(22)申请日 2022.06.08

(71) 申请人 成都世源频控技术股份有限公司 地址 610000 四川省成都市武侯区武兴四 路166号7栋2单元1层4、5号2、3层4、5、 6、7号

(72) 发明人 赵乾坤

(74) 专利代理机构 成都众恒智合专利代理事务 所(普通合伙) 51239

专利代理师 朱杰

(51) Int.CI.

*H03L* 7/23 (2006.01) *H03L* 7/10 (2006.01)

权利要求书2页 说明书5页 附图3页

#### (54) 发明名称

一种低相位噪声环路及应用该环路的环路 预置方法

#### (57) 摘要

本发明公开了一种低相位噪声环路及应用 该环路的环路预置方法,用于解决混频锁相环中 易出现的错锁、失锁问题。该环路包括产生预置 电压的预置环路,与预置环路相连的高阻电路, 混频环锁定时产生压控电压的主环路,与主环路 相连的低阻电路,以及与高阻电路和低阻电路相 连的匹配电路。本发明的低相位噪声环路可实现 单个压控振荡器覆盖一个倍频程的宽带混频环。 同时避免了传统宽带混频环采用开关切换预置 环路带来的锁定不稳定的问题,解决了混频环的 功能性问题,进一步地减小了调试工作量,批量 生产时电路一致性较好,适合大规模生产。

CN 114726368 A

- 1.一种低相位噪声环路,其特征在于,包括产生预置电压的预置环路,与预置环路相连的高阻电路,混频环锁定时产生压控电压的主环路,与主环路相连的低阻电路,以及与高阻电路和低阻电路相连的匹配电路。

- 2.根据权利要求1所述的一种低相位噪声环路,其特征在于,所述预置环路包括同相输入端接基准电压VREF的运算放大器N1,一端与运算放大器N1的反相输入端相连的电阻R1、电阻R2及电容C1,一端与电阻R1的另一端相连且另一端接地的电容C2,连接于电阻R2另一端与运算放大器N1的输出端之间的电容C3,与运算放大器N1的输出端相连的电阻R3,以及一端与电阻R3的另一端相连且另一端接地的电容C5;其中,电容C1的另一端与运算放大器N1的输出端相连;电阻R1、电容C2的公共端作为预置环路的输入端;电阻R3、电容C5的公共端作为预置环路的输出端。

- 3.根据权利要求2所述的一种低相位噪声环路,其特征在于,所述高阻电路包括同相输入端接预置环路的输出端的运算放大器N2,以及并联后连接于运算放大器N2的反相输入端与输出端之间的电阻R4、电容C6;其中,所述运算放大器N2的输出端作为高阻电路的输出端。

- 4.根据权利要求3所述的一种低相位噪声环路,其特征在于,所述主环路包括运算放大器N3,一端经电阻R5与运算放大器N3的反相输入端相连且另一端接地的电容C7,一端经电阻R6与运算放大器N3的同相输入端相连且另一端接地的电容C8,一端经电阻R7与运算放大器N3的同相输入端相连且另一端接地的电容C9,串联后连接于运算放大器N3的反相输入端与输出端之间的电阻R8、电容C10;其中,电阻R5、电容C7的公共端作为主环路的一个输入端;电阻R6、电容C8的公共端作为主环路的另一个输入端;述运算放大器N3的输出端作为主环路的输出端。

- 5.根据权利要求4所述的一种低相位噪声环路,其特征在于,所述低阻电路包括一端与 主环路的输出端相连的电阻R8,以及串联后并联于电阻R9两端的电容C11、电阻R10;其中, 电阻R8的另一端作为低阻电路的输出端。

- 6.根据权利要求5所述的一种低相位噪声环路,其特征在于,所述匹配电路包括一端与高阻电路的输出端和低阻电路的输出端均相连的电阻R11,并联于电阻R11两端的电容C12,以及一端与电阻R11的另一端相连且另一端接地的电容C13;其中,电阻R11、电容C12、电容C13的公共端作为匹配电路的输出端。

- 7.一种应用低相位噪声环路的环路预置方法,其特征在于,采用了如权利要求6所述的低相位噪声环路,用于混频锁相电路中;所述混频锁相电路包括用于产生锁相环路所需的参考基准信号的参考时钟,与参考时钟的输出端分别连接的含有N分频器的辅助鉴相器、主鉴相器和混频本振,以及用于输出两路反馈信号压控振荡器;其中,一路反馈到辅助鉴相器,另一路经过分频再与混频本振混频,然后经低通滤波器后反馈到主鉴相器;辅助鉴相器的输出端与预置环路相连,主鉴相器的输出端与主环路相连,匹配电路的输出端和压控振荡器相连;

在环路工作于预置状态时,所述预置方法如下:

(a) 压控振荡器的一路输出信号在经过辅助鉴相器和参考时钟信号鉴相后产生误差电流,经过预置环路后产生预置电压,再分别经过高阻电路和匹配电路后控制压控振荡器输出所需频率信号,此处工作时,环路仅工作于单一闭环环路,从而使输出频率在所需目标频

#### 率附近;

- (b) 压控振荡器输出的另一路输出信号在经过分频后,通过混频器和混频本振混频得到频率较低的中频信号,直接进入主鉴相器和参考时钟信号进行鉴相,鉴相得到的误差电流在经过主环路后产生主环电压,该电压再分别经过低阻电路和匹配电路后也控制压控振荡器输出所需目标频率。

- 8.根据权利要求7所述的一种应用低相位噪声环路的环路预置方法,其特征在于,使输出频率在所需目标频率附近的具体方法为:

当压控振荡器输出频率与所需频率相差较远时,预置环是单环,具有很强的捕获能力,在锁定至目标频率的过程中预置环将迫使输出频率接近所需目标频率,此过程,主环的捕获能力较弱,不对预置环产生影响;当预置环使压控振荡器输出频率与所需目标频率相近时,此时,主环反馈频率进入主环的捕获范围内,又由于主环路输出是低阻电路,因此主环起主要作用;同时,预置环路输出为高阻电路,将限制辅助鉴相器的噪声进入压控振荡器,低阻电路使得压控振荡器压控端噪声的来源主要为主鉴相器,进而,优化输出信号的相位噪声。

# 一种低相位噪声环路及应用该环路的环路预置方法

### 技术领域

[0001] 本发明属于混频锁相频率合成技术领域,具体地说,是涉及一种低相位噪声环路及应用该环路的环路预置方法。

## 背景技术

[0002] 随着电子技术的快速发展,现代电子设备对功能电路的电性能要求也越来越高,低相位噪声锁相环频率合成技术作为频率再生的重要手段,在频率合成、高频、宽带信号产生等方面有着非常重要的应用,在宽带低相位噪声锁相频率合成中采用混频环设计有重要的意义,宽带混频环存在易错锁失锁的问题,故需要采用环路预置手段。

[0003] 环路预置主要是指在混频锁相电路中,在环路滤波的位置预置一个与输出频率对应的预置电压,主要为解决宽带混频锁相时易出现的错锁、失锁问题。

[0004] 传统的方法在采用宽带混频环频率合成时:

(a) 采用DA输出预置电压,再将该电压和环路滤波器电压进行相加,然后控制压控振荡器输出所需频率。此方法,由于DA本身存在数字和模拟信号的转换,这会使输出电压有很高的噪声,锁相时此噪声会调制到压控振荡器上,使得所需的频率信号相位噪声较差,因此不适合低相位噪声锁相使用。

[0005] (b) 在专利CN104022738A中,采用DA输出预置电压,该电压和环路滤波器输出电压通过开关进行切换,首先DA输出电压控制压控振荡器输出与所需频率相近的预置频率,然后切换开关,将环路滤波器输出电压施加到压控振荡器,令其输出所需频率。此方法在物理上需要使用开关切换,在复杂条件下,特别是环境温度变化很大的情况下,存在混频环失锁的潜在问题,造成频率合成失败。

[0006] (c)采用两个鉴相器和环路滤波器,一个作为预置环,另一个作为主环,预置环和主环之间通过开关进行切换。此方法中,由于二者通过开关进行切换,存在环境温度变化较大时,易出现混频环失锁的问题。

[0007] (d)采用多级电压分段预置,如专利CN215646752U所述。此方法,采用多个低压差线性稳压器输出电压进行预置,电路较复杂,操作,同时设计中存在大量的开关切换,带来的问题是锁定不可靠,易失锁。

[0008] (e) 用分段式压控振荡器预置, 如专利CN110719099A所述。此方法, 仅适用于分段式集成压控振荡器, 对单片宽带压控振荡器 (输出频率覆盖一个倍频程) 组成的混频环不适用, 且预置电路中预置环和主环采用的是开关切换的方式, 存在切换失锁的潜在风险。

#### 发明内容

[0009] 本发明的目的在于提供一种低相位噪声环路,使得混频锁相电路在预置环和主环通过高低阻电路直接相连的情况下,既可实现输出信号低相位噪声,又能解决混频锁相环中易出现的错锁、失锁问题。

[0010] 为实现上述目的,本发明采用的技术方案如下:

一种低相位噪声环路,包括产生预置电压的预置环路,与预置环路相连的高阻电路,混频环锁定时产生压控电压的主环路,与主环路相连的低阻电路,以及与高阻电路和低阻电路相连的匹配电路。

[0011] 进一步地,在本发明中,所述预置环路包括同相输入端接基准电压VREF的运算放大器N1,一端与运算放大器N1的反相输入端相连的电阻R1、电阻R2及电容C1,一端与电阻R1的另一端相连且另一端接地的电容C2,连接于电阻R2另一端与运算放大器N1的输出端之间的电容C3,与运算放大器N1的输出端相连的电阻R3,以及一端与电阻R3的另一端相连且另一端接地的电容C5;其中,电容C1的另一端与运算放大器N1的输出端相连;电阻R1、电容C2的公共端作为预置环路的输入端;电阻R3、电容C5的公共端作为预置环路的输出端。

[0012] 进一步地,在本发明中,所述高阻电路包括同相输入端接预置环路的输出端的运算放大器N2,以及并联后连接于运算放大器N2的反相输入端与输出端之间的电阻R4、电容C6;其中,所述运算放大器N2的输出端作为高阻电路的输出端。

[0013] 进一步地,在本发明中,所述主环路包括运算放大器N3,一端经电阻R5与运算放大器N3的反相输入端相连且另一端接地的电容C7,一端经电阻R6与运算放大器N3的同相输入端相连且另一端接地的电容C8,一端经电阻R7与运算放大器N3的同相输入端相连且另一端接地的电容C9,串联后连接于运算放大器N3的反相输入端与输出端之间的电阻R8、电容C10;其中,电阻R5、电容C7的公共端作为主环路的一个输入端;电阻R6、电容C8的公共端作为主环路的另一个输入端;述运算放大器N3的输出端作为主环路的输出端。

[0014] 进一步地,在本发明中,所述低阻电路包括一端与主环路的输出端相连的电阻R8,以及串联后并联于电阻R9两端的电容C11、电阻R10;其中,电阻R8的另一端作为低阻电路的输出端。

[0015] 进一步地,在本发明中,所述匹配电路包括一端与高阻电路的输出端和低阻电路的输出端均相连的电阻R11,并联于电阻R11两端的电容C12,以及一端与电阻R11的另一端相连且另一端接地的电容C13;其中,电阻R11、电容C12、电容C13的公共端作为匹配电路的输出端。

[0016] 基于上述低相位噪声环路,本发明还提供一种环路预置方法,用于混频锁相电路中;所述混频锁相电路包括用于产生锁相环路所需的参考基准信号的参考时钟,与参考时钟的输出端分别连接的含有N分频器的辅助鉴相器、主鉴相器和混频本振,以及用于输出两路反馈信号压控振荡器;其中,一路反馈到辅助鉴相器,另一路经过分频再与混频本振混频,然后经低通滤波器后反馈到主鉴相器;辅助鉴相器的输出端与预置环路相连,主鉴相器的输出端与主环路相连,匹配电路的输出端和压控振荡器相连;

在环路工作于预置状态时,所述预置方法如下:

- (a) 压控振荡器的一路输出信号在经过辅助鉴相器和参考时钟信号鉴相后产生误差电流,经过预置环路后产生预置电压,再分别经过高阻电路和匹配电路后控制压控振荡器输出所需频率信号,此处工作时,环路仅工作于单一闭环环路,从而使输出频率在所需目标频率附近;

- (b) 压控振荡器输出的另一路输出信号在经过分频后,通过混频器和混频本振混频得到频率较低的中频信号,直接进入主鉴相器和参考时钟信号进行鉴相,鉴相得到的误差电流在经过主环路后产生主环电压,该电压再分别经过低阻电路和匹配电路后也控制压

控振荡器输出所需目标频率。

[0017] 进一步地,在本发明中,使输出频率在所需目标频率附近的具体方法为:

当压控振荡器输出频率与所需频率相差较远时,预置环是单环,具有很强的捕获能力,在锁定至目标频率的过程中预置环将迫使输出频率接近所需目标频率,此过程,主环的捕获能力较弱,不对预置环产生影响;当预置环使压控振荡器输出频率与所需目标频率相近时,此时,主环反馈频率进入主环的捕获范围内,又由于主环路输出是低阻电路,因此主环起主要作用;同时,预置环路输出为高阻电路,将限制辅助鉴相器的噪声进入压控振荡器,低阻电路使得压控振荡器压控端噪声的来源主要为主鉴相器,进而,优化输出信号的相位噪声。

[0018] 与现有技术相比,本发明具有以下有益效果:

(1)本发明的低相位噪声环路可实现单个压控振荡器覆盖一个倍频程的宽带混频环。同时避免了传统宽带混频环采用开关切换预置环路带来的锁定不稳定的问题,解决了混频环的功能性问题,进一步地,减小了调试工作量,批量生产时电路一致性较好,适合大规模生产。

[0019] (2)本发明的环路预置方法,有效避免了传统DA预置带来的相位噪声恶化严重和杂波严重的问题。本发明在10GHz输出频率时,可实现-113dBc/Hz@1kHz、-128dBc/Hz@10kHz的相位噪声指标。

#### 附图说明

[0020] 图1为本发明的结构示意图。

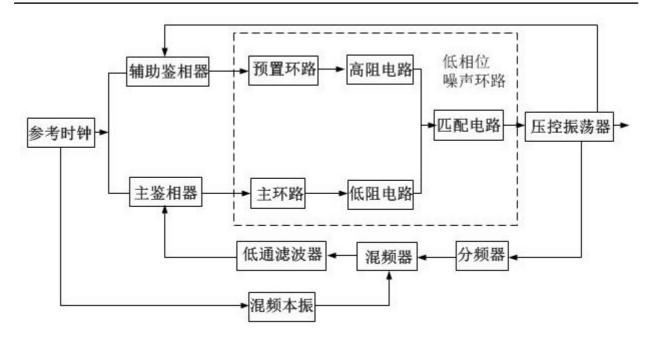

[0021] 图2为本发明中的预置环工作原理图(虚线框内)。

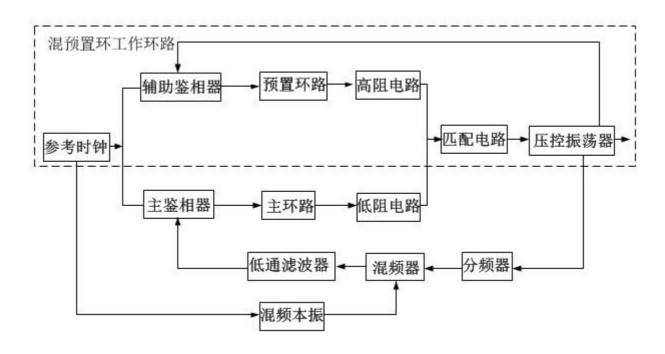

[0022] 图3为本发明中的混频环工作原理图(虚线框内)。

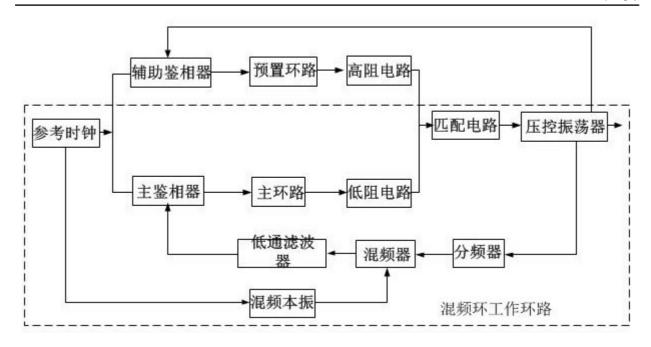

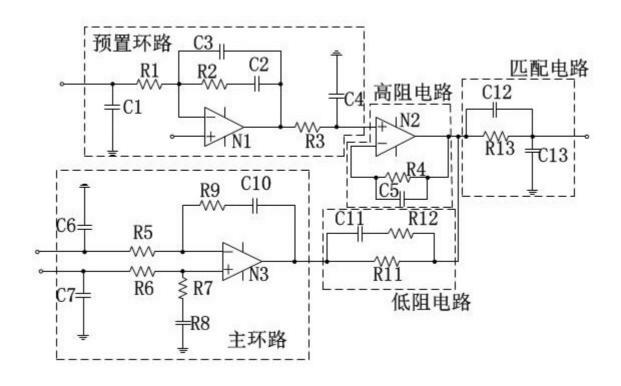

[0023] 图4为本发明的电路原理图。

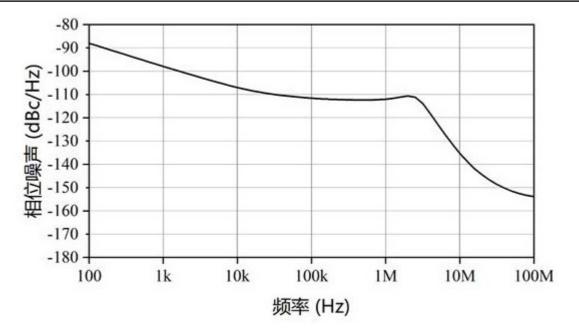

[0024] 图5为本发明实施例提供的预置环(单环)输出10GHz时的相位噪声测试曲线。

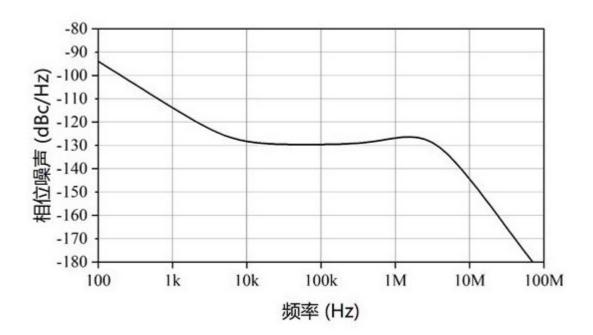

[0025] 图6为本发明实施例提供的主环(混频环)输出10GHz时的相位噪声测试曲线。

#### 具体实施方式

[0026] 下面结合附图说明和实施例对本发明作进一步说明,本发明的方式包括但不仅限于以下实施例。

#### 实施例

[0027] 如图1~6所示,本发明公开的一种低相位噪声环路,包括产生预置电压的预置环路,与预置环路相连的高阻电路,混频环锁定时产生压控电压的主环路,与主环路相连的低阻电路,以及与高阻电路和低阻电路相连的匹配电路。该电路用于混频锁相电路中;所述混频锁相电路包括用于产生锁相环路所需的参考基准信号的参考时钟,与参考时钟的输出端分别连接的含有N分频器的辅助鉴相器、主鉴相器和混频本振,以及用于输出两路反馈信号压控振荡器;其中,一路反馈到辅助鉴相器,另一路经过分频再与混频本振混频,然后经低通滤波器后反馈到主鉴相器;辅助鉴相器的输出端与预置环路相连,主鉴相器的输出端与主环路相连,匹配电路的输出端和压控振荡器相连。

[0028] 在本实施例中,作为优选,参考时钟选用超低相噪恒温晶振,辅助鉴相器选用ADF41513,主环鉴相器选用HMC3716,压控振荡器选用HMC733。

[0029] 如图4所示,所述预置环路包括同相输入端接基准电压VREF的运算放大器N1,一端与运算放大器N1的反相输入端相连的电阻R1、电阻R2及电容C1,一端与电阻R1的另一端相连且另一端接地的电容C2,连接于电阻R2另一端与运算放大器N1的输出端之间的电容C3,与运算放大器N1的输出端相连的电阻R3,以及一端与电阻R3的另一端相连且另一端接地的电容C5;其中,电容C1的另一端与运算放大器N1的输出端相连;电阻R1、电容C2的公共端作为预置环路的输入端;电阻R3、电容C5的公共端作为预置环路的输出端。预置环路用于将辅助鉴相器产生的误差电流转换成预置环路电压。

[0030] 在本实施例中,所述高阻电路包括同相输入端接预置环路的输出端的运算放大器 N2,以及并联后连接于运算放大器N2的反相输入端与输出端之间的电阻R4、电容C6;其中, 所述运算放大器N2的输出端作为高阻电路的输出端。

[0031] 在本实施例中,所述主环路包括运算放大器N3,一端经电阻R5与运算放大器N3的反相输入端相连且另一端接地的电容C7,一端经电阻R6与运算放大器N3的同相输入端相连且另一端接地的电容C8,一端经电阻R7与运算放大器N3的同相输入端相连且另一端接地的电容C9,串联后连接于运算放大器N3的反相输入端与输出端之间的电阻R8、电容C10;其中,电阻R5、电容C7的公共端作为主环路的一个输入端;电阻R6、电容C8的公共端作为主环路的另一个输入端;述运算放大器N3的输出端作为主环路的输出端。主环路用于将主鉴相器产生的误差电压转换成主环路电压。

[0032] 在本实施例中,所述低阻电路包括一端与主环路的输出端相连的电阻R8,以及串联后并联于电阻R9两端的电容C11、电阻R10;其中,电阻R8的另一端作为低阻电路的输出端。

[0033] 在本实施例中,所述匹配电路包括一端与高阻电路的输出端和低阻电路的输出端均相连的电阻R11,并联于电阻R11两端的电容C12,以及一端与电阻R11的另一端相连且另一端接地的电容C13;其中,电阻R11、电容C12、电容C13的公共端作为匹配电路的输出端。

[0034] 在环路工作于预置状态时,压控振荡器的一路输出信号在经过辅助鉴相器和参考时钟信号鉴相后产生误差电流,经过预置环路后产生预置电压,再分别经过高阻电路和匹配电路后控制压控振荡器输出所需频率信号,此处工作时,环路仅工作于单一闭环环路,从而使输出频率在所需目标频率附近;压控振荡器输出的另一路输出信号在经过分频后,通过混频器和混频本振混频得到频率较低的中频信号,直接进入主鉴相器和参考时钟信号进行鉴相,鉴相得到的误差电流在经过主环路后产生主环电压,该电压再分别经过低阻电路和匹配电路后也控制压控振荡器输出所需目标频率。

[0035] 当压控振荡器输出频率与所需频率相差较远时,预置环是单环,具有很强的捕获能力,在锁定至目标频率的过程中预置环将迫使输出频率接近所需目标频率,此过程,主环的捕获能力较弱,不对预置环产生影响;当预置环使压控振荡器输出频率与所需目标频率相近时,此时,主环反馈频率进入主环的捕获范围内,又由于主环路输出是低阻电路,因此主环起主要作用;同时,预置环路输出为高阻电路,将限制辅助鉴相器的噪声进入压控振荡器,低阻电路使得压控振荡器压控端噪声的来源主要为主鉴相器,进而,优化输出信号的相位噪声。

[0036] 请参阅图1、图4,本发明设计的低相位噪声环路不存在环路开关切换,并且经过数次的实验及图5、图6均可看出,本发明的环路预置方法锁定稳定可靠,最终输出信号具有很低的相位噪声。根据附图,输出10GHz频率时,传统单环(预置环)的相位噪声-97dBc/Hz@1kHz、-107dBc/Hz@10kHz,通过本发明的环路预置方法将混频环相位噪声优化到了-113dBc/Hz@1kHz、-128dBc/Hz@10kHz。

[0037] 并且本实施例中,混频环采用的压控振荡器最终输出频率可覆盖一个倍频程(10~20GHz)。

[0038] 经过实施例的多次验证测试,本实施例中的混频锁相电路输出频率锁定稳定,不会出现错锁、失锁的情况,此环路预置方法适合大规模推广应用。

[0039] 上述实施例仅为本发明的优选实施方式之一,不应当用于限制本发明的保护范围,但凡在本发明的主体设计思想和精神上作出的毫无实质意义的改动或润色,其所解决的技术问题仍然与本发明一致的,均应当包含在本发明的保护范围之内。

图1

图2

图3

图4

图5

图6