# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>6</sup>:

(11) International Publication Number: WO 98/36341

(43) International Publication Date: 20 August 1998 (20.08.98)

(21) International Application Number: P

PCT/US97/02355

(22) International Filing Date:

12 February 1997 (12.02.97)

(71) Applicant (for all designated States except US): INTEL COR-PORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

(72) Inventor; and

(75) Inventor/Applicant (for US only): ALEXIS, Ranjeet [IN/US]; 101 Alvaston Court, Folsom, CA 95630 (US).

(74) Agents: TAYLOR, Edwin, H. et al.; Blakely, Sokoloff, Taylor & Zafman LLP, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 (US).

(81) Designated States: AL, AM, AT, AT (Utility model), AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CU, CZ, CZ (Utility model), DE, DE (Utility model), DK, DK (Utility model), EE, EE (Utility model), ES, FI, FI (Utility model), GB, GE, HU, IL, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SK (Utility model), TJ, TM, TR, TT, UA, UG, US, UZ, VN, YU, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

#### **Published**

With international search report.

(54) Title: SELF-COMPENSATING GEOMETRY-ADJUSTED CURRENT MIRRORING CIRCUITRY

#### (57) Abstract

A self compensating current mirroring circuit including first and second transistor devices (21 and 22) respectively joined in the path of a current to be mirrored and the path of a mirrored current, the first transistor device (21) being in circuit with a compensating transistor device (23), the sizes of the first and second transistor devices (21 and 22) being such that the currents through them are maintained at identical levels during operation.

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|    |                          |     |                     | T.C | Y                     | SI | Slovenia                 |

|----|--------------------------|-----|---------------------|-----|-----------------------|----|--------------------------|

| AL | Albania                  | ES  | Spain               | LS  | Lesotho               |    | Slovakia                 |

| AM | Armenia                  | FI  | Finland             | LT  | Lithuania             | SK |                          |

| AT | Austria                  | FR  | France              | LU  | Luxembourg            | SN | Senegal                  |

| AU | Australia                | GA  | Gabon               | LV  | Latvia                | SZ | Swaziland                |

| AZ | Azerbaijan               | GB  | United Kingdom      | MC  | Monaco                | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE  | Georgia             | MD  | Republic of Moldova   | TG | Togo                     |

| BB | Barbados                 | GH  | Ghana               | MG  | Madagascar            | TJ | Tajikistan               |

| BE | Belgium                  | GN  | Guinea              | MK  | The former Yugoslav   | TM | Turkmenistan             |

| BF | Burkina Faso             | GR  | Greece              |     | Republic of Macedonia | TR | Turkey                   |

| BG | Bulgaria                 | HU  | Hungary             | ML  | Mali                  | TT | Trinidad and Tobago      |

| BJ | Benin                    | IE  | Ireland             | MN  | Mongolia              | UA | Ukraine                  |

| BR | Brazil                   | IL  | Israel              | MR  | Mauritania            | UG | Uganda                   |

| BY | Belarus                  | IS  | Iceland             | MW  | Malawi                | US | United States of America |

| CA | Canada                   | IT  | Italy               | MX  | Mexico                | UZ | Uzbekistan               |

| CF | Central African Republic | JР  | Japan               | NE  | Niger                 | VN | Viet Nam                 |

| CG | Congo                    | KE  | Kenya               | NL  | Netherlands           | YU | Yugoslavia               |

| CH | Switzerland              | KG  | Kyrgyzstan          | NO  | Norway                | zw | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP  | Democratic People's | NZ  | New Zealand           |    |                          |

| CM | Cameroon                 | 144 | Republic of Korea   | PL  | Poland                |    |                          |

| CN | China                    | KR  | Republic of Korea   | PT  | Portugal              |    |                          |

|    |                          | KZ  | Kazakstan           | RO  | Romania               |    |                          |

| CU | Cuba                     | LC  | Saint Lucia         | RU  | Russian Federation    |    |                          |

| CZ | Czech Republic           | LI  | Liechtenstein       | SD  | Sudan                 |    |                          |

| DE | Germany                  |     | Sri Lanka           | SE  | Sweden                |    |                          |

| DK | Denmark                  | LK  |                     | SG  | Singapore             |    |                          |

| EE | Estonia                  | LR  | Liberia             | au  | Singapore             |    |                          |

- 1 -

# SELF-COMPENSATING GEOMETRY-ADJUSTED CURRENT MIRRORING CIRCUITRY

#### BACKGROUND OF THE INVENTION

#### Field Of The Invention

This invention relates to circuitry for controlling the value of currents and, more particularly, to methods and apparatus for providing improved current mirroring circuitry.

# History Of The Prior Art

In electronic circuitry, it is often desirable to provide a current which has a value identical to that of a current through some other circuit device not in series with the first This is typically accomplished through the use of a device. By maintaining the voltage levels current mirroring circuit. equal at gate and source terminals of a pair of field effect transistor (FET) devices operating in saturation, the current through the devices may be kept equal. However, there are situations in which circuit conditions tend to vary during use; and it is necessary to maintain the current equality in the face of these variations. To accomplish this, a negative feedback scheme has been used as a part of the current mirror circuitry to adjust the currents in response to current variations caused by noise, changes in ambient temperatures, or the like.

A problem with such a feedback scheme is that it produces an inherent mismatch in the drain voltages of the mirroring transistors and a degradation of the accuracy of the mirror. Sometimes more accuracy of current equality is necessary than is provided by the standard negative feedback arrangement.

It is desirable to provide circuitry which will produce a more accurate self-compensating arrangement for current mirroring.

Another problem encountered with current mirroring arrangements which use negative feedback for compensation is that such systems must be designed to operate with a particular supply voltages. For example, some portable computers are designed to perform with either five volt or 3.5 volt power supplies. To function with one system or the other, the current mirroring arrangements must be designed for the particular range. It is possible for a current mirroring arrangement which use negative feedback to perform well in one range but improperly outside that designed range. Often circuit boards must be designed so that they may be used with more than one range of supply voltages. This has eliminated the ability to use self compensating current mirroring arrangements.

It is desirable for a current mirror circuit to be able to mirror currents very accurately within its designed range of operation yet continue to mirror current with acceptable accuracy outside the designed range of operation.

# Summary Of The Invention

It is, therefore, an object of the present invention to provide apparatus and a method for mirroring current very accurately within a designed operational range of voltages.

It is another object of the present invention to provide apparatus and a method for mirroring current very accurately within a designed operational range of voltages and within acceptable accuracy outside the designed range of operation.

- 3 -

These and other objects of the present invention are realized using apparatus which includes a first current mirroring circuit which is used to provide a precise mirroring of currents using a unique negative feedback circuit. contrast to all prior art current mirrors, the current mirroring arrangement uses field effect transistor devices with unequal dimensions which allow the inequalities produced by self-The first current mirroring compensation to be eliminated. circuit may also be used with a second current mirroring circuit and means for enabling one or the other of the circuits depending on the voltage range in which the circuits are operating. The first current mirroring circuit may be used in a higher of two possible voltage ranges. The second current mirroring circuit is more standard in form and is switched into operation in place of the first circuit to provide a mirroring of currents when the supply voltage falls into a lower of the two The combined circuit provides possible voltage ranges. mirroring of currents across a number of possible ranges of the system while providing very precise self-compensating current mirroring in the higher voltage range.

These and other objects and features of the invention will be better understood by reference to the detailed description which follows taken together with the drawings in which like elements are referred to by like designations throughout the several views.

## Brief Description Of The Drawings

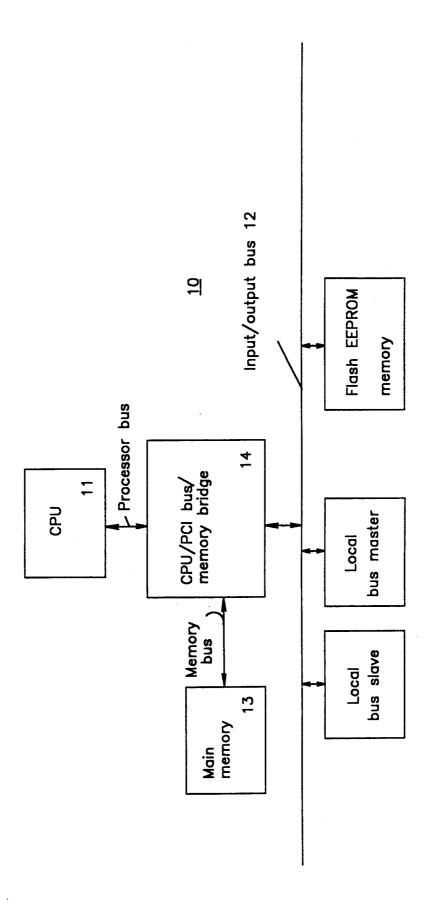

Figure 1 is a block diagram of a computer system which may utilize the present invention.

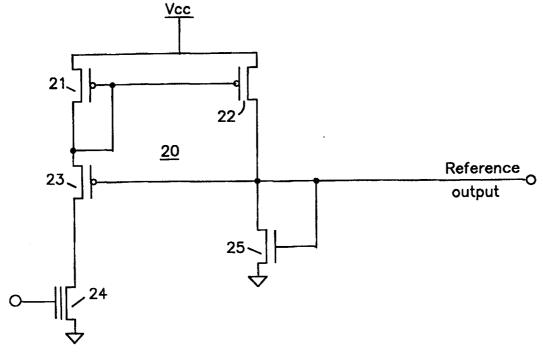

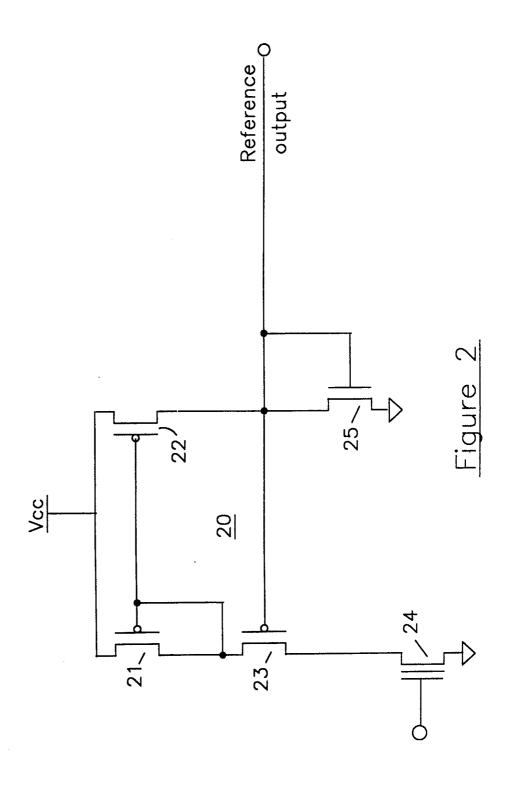

Figure 2 is a block diagram of a self-compensating current mirroring circuit designed in accordance with the present invention.

- 4 -

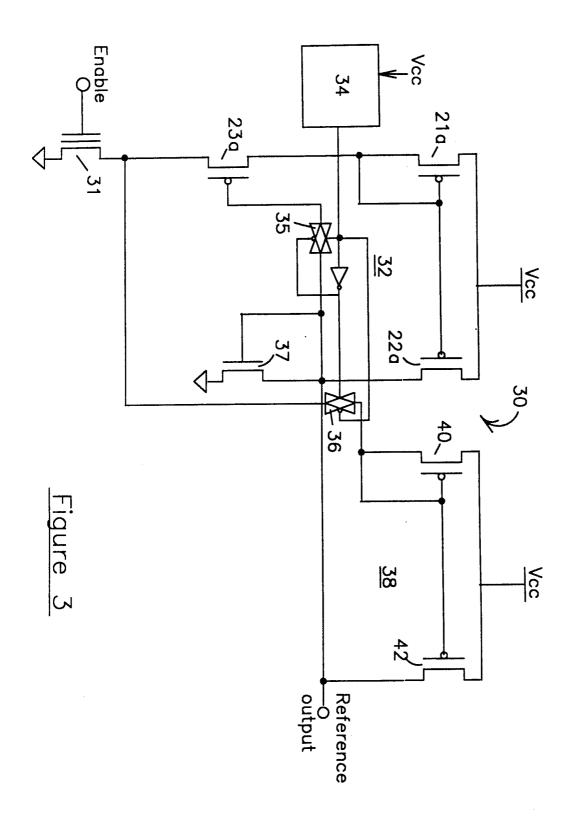

Figure 3 is a block diagram of a current mirroring circuit designed in accordance with the present invention.

### Notation And Nomenclature

Some portions of the detailed descriptions which follow presented in terms of symbolic representations of operations on data bits within a computer memory. descriptions and representations are the means used by those skilled in the data processing arts to most effectively convey the substance of their work to others skilled in the art. operations are those requiring physical manipulations of physical quantities. Usually, though not necessarily, these quantities take the form of electrical or magnetic signals capable of being stored, transferred, combined, compared, and otherwise manipulated. It has proven convenient at times, principally for reasons of common usage, to refer to these signals as bits, values, elements, symbols, characters, terms, numbers, or the like. It should be borne in mind, however, that all of these and similar terms are to be associated with the appropriate physical quantities and are merely convenient labels applied to these quantities.

Further, the manipulations performed are often referred to in terms, such as adding or comparing, which are commonly associated with mental operations performed by a human operator. No such capability of a human operator is necessary or desirable in most cases in any of the operations described herein which form part of the present invention; the operations are machine operations. Useful machines for performing the operations of the present invention include general purpose digital computers or other similar devices. In all cases the distinction between the method operations in operating a computer and the method of computation itself should be borne in mind. The present invention relates to a

- 5 -

method and apparatus for operating a computer in processing electrical or other (e.g. mechanical, chemical) physical signals to generate other desired physical signals.

# **Detailed** Description

Referring now to Figure 1, there is illustrated a block diagram of a digital system 10 configured in accordance with one embodiment of the present invention. The present invention has application in any system, including a computer system, utilizing circuitry in which a current is to be very The system 10 illustrated includes a precisely mirrored. central processing unit 11 which executes the various instructions provided to control the operations of the system The central processing unit 11 is typically joined by a processor bus to a bridge circuit 14 which controls access to an input/output bus 12 adapted to carry information between the various components of the system 10. The bridge 14 is also typically joined by a memory bus to main memory 13 which is typically constructed of dynamic random access memory arranged in a manner well known to those skilled in the prior art to store information during a period in which power is provided to the system 10. In Figure 1, the bus 12 is preferably a peripheral component interface (PCI) bus or other local bus adapted to provide especially fast transfers of data. In a typical system 10, various input/output devices are connected as bus master and bus slave circuits to the bus 12.

In addition to the usual input/output devices typically joined to a system bus 12, additional memory may be provided for the system by a flash EEPROM memory array which may be positioned on the bus. A flash EEPROM memory array is one instance in which the present invention finds use in a computer system. A flash EEPROM memory array is constructed of a large plurality of floating-gate metal-oxide-

silicon field effect transistor devices arranged as memory cells in typical row and column fashion with circuitry for accessing individual cells and placing the memory transistors of those cells in different memory conditions. Such memory transistors may be programmed by storing a charge on the floating gate. This charge remains when power is removed from the array. The charge level may be detected by interrogating the devices.

In order to detect the value of the charges stored in one type of flash memory manufactured by Intel Corporation of Santa Clara, California, reference cells are provided which utilize additional flash EEPROM transistor devices to furnish reference currents to each of the sensing outputs of each word. The current through the flash storage cells is compared with these reference currents through the flash reference cells to determine whether a "zero" or a "one" condition exists in the flash storage cells. Since these reference currents are used to measure the state of the storage cells, these currents must be very precise in value. In one particular flash EEPROM memory array, in order to reduce the die area used by reference cells, current from a single reference cell is mirrored a number of times to provide identical reference currents for each of sixteen sensing cells used to generate a word wide output.

Figure 2 is a circuit diagram illustrating a basic configuration of a self-compensating current mirroring circuit 20 which may be used in circuitry furnishing reference currents for flash EEPROM memory arrays as well as in other circuits. The circuit 20 includes a pair of identically-sized P type field effect transistor devices 21 and 22 having their source and gate terminals joined so that the voltages applied to these terminals are identical. With this configuration and appropriate biasing values to cause the devices to be operated in saturation, current from a flash EEPROM reference device

- 7 -

24 will produce identical currents in the two devices 21 and 22 and a N type transistor device 25.

Variations in temperature, noise, or other ambient conditions in the circuit 20 may cause the current through the two devices 21 or 22 to vary with respect to the other. maintain currents through the two devices constant in the face of such variations, a P type field effect transistor device 23 is connected with its source and drain terminals in the current path between the flash device 24 and the device 21 and with its gate terminal at the drain terminal of the device 22. arrangement provides negative feedback which corrects for changes in ambient conditions. For example, if the voltage at the drain of the device 23 increases, the voltage at the drain of the device 21 will also increase. Increasing the voltage at the drain of the device 21 increases the voltage at the gate of the device 22, decreasing the voltage at the gate of the device 23 and reducing the level of the voltage at the drain of the device Thus when the current through the device 21 varies, the change in voltage at the gate of the device 23 changes the current through the device 21 in the same manner. feedback assures that accurate current mirroring occurs over the operational range of the devices.

However, it will be noted that using this feedback arrangement, the voltage at the drains of the two devices 21 and 22 are not equal but vary by the amount of the voltage drop between the source and gate terminals of the device 23. This means that the currents through the two devices are not, in fact, exactly equal because even in saturation the current through a device is a function of the drain voltage. Most designers simply ignore this difference. However, there are many situations such as those involved in accurately sensing

- 8 -

the values of memory cells in which it may be desirable to provide more precise current mirroring.

The present invention provides equal currents through the mirroring transistors 21 and 22 by a unique approach. Rather than using identical devices 21 and 22, the dimensions of these devices are made sufficiently different to compensate for the difference in the voltages at the drain terminals of the two devices. This causes the currents through the devices 21 and 22 to be identical and restores the precise current mirroring of the non-compensated circuit.

The amounts by which the dimensions are varied depend on the particular operating parameters and device sizes of the current mirroring circuitry. However, in one circuit the device 21 was designed with a length of five microns and a width of 150 microns while the device 22 was designed with a length of five microns and a width of 140 microns. Operating in a range in which the voltage Vcc was five volts, the circuit 20 provides the identical currents desired.

One problem with compensated current mirroring circuits, however, is that outside of the range of operating parameters in which they are designed to operate, the compensation provided no longer functions correctly. For example, at some point, the source voltage Vcc is insufficient to provide a sufficient threshold voltage for the device 23; and the circuit will not function. Consequently, with circuits which may be operated in a plurality of ranges, such self-compensating circuits may not function correctly. The present invention overcomes this problem of the prior art and allows current to be correctly mirrored over a plurality of supply voltage ranges.

- 9 -

Figure 3 is a block diagram of a circuit 30 designed in accordance with the present invention to allow current mirroring to take place with a plurality of different supply voltages Vcc. The circuit 30 mirrors a voltage provided across a flash EEPROM memory device 31 when an enabling signal is provided at the gate terminal of the device 31. operating at supply voltage Vcc of five volts, a signal having a positive value is provided by a detector circuit 34 causing a pair of transmission gates 35 and 36 to switch current from the device 31 through a first current mirroring circuit 32 essentially identical to the circuit described in Figure 2. current through the device 31 thus is transferred between ground and the voltage Vcc through a compensating P type device 23a and a P type device 21a. Since the device 21a and a device 22a have their respective source and gate terminals joined, and because the dimensions of the devices 21a and 22a are chosen such that the gate-source voltage Vgs of the device 23a is just sufficient that identical currents flow through the devices 21a and 22a even though the drain voltages of the devices 21a and 22a differ. Moreover, the compensating device 23a will maintain these currents equal although ambient conditions of the circuit 30 change. The current through the device 22a flows to ground through a N type The current through the device 37 transistors device 37. provides a reference voltage level which may be used in a particular embodiment to provide an input to a sense amplifier of a flash EEPROM memory array.

In a second range of operation in which the voltage Vcc is 3.6 or less volts, a digital signal of a negative value is provided by the detector circuit 34 causing the transmission gates 35 and 36 to switch the current from the device 31 through a second current mirroring circuit 38. The circuit 38 includes a pair of identical P type transistor devices 40 and 42

connected in a standard non-compensated current mirroring arrangement. As will be seen, current through the flash device 31 is transferred through the device 40 and mirrored through the device 42 to provide the desired reference potential at the output.

Thus, the present invention allows precise control of current values with compensation for ambient conditions in a first operating range but continues to provide uncompensated mirrored currents suitable for operation in the second range of operation.

It would be possible to provide a compensated current mirroring circuit in place of the standard circuit used in the circuit 38 in order to attain additional precision in both ranges of operation shown. It would also be possible within the present invention to include additional current compensating circuits for additional operating ranges without departing from the present invention.

Although the present invention has been described in terms of a preferred embodiment, it will be appreciated that various modifications and alterations might be made by those skilled in the art without departing from the spirit and scope of the invention. The invention should therefore be measured in terms of the claims which follow.

## What Is Claimed Is:

- 1. A current mirroring circuit comprising:

- a source of current to be mirrored,

- a supply voltage,

- a first field effect transistor device arranged to provide a current path between the source of current and the supply voltage,

- a compensating field effect transistor device arranged to provide a current path between the source of current and the supply voltage,

- a second field effect transistor device arranged to provide a second current path between the supply voltage and a reference node.

the first and second field effect transistor devices having gate terminals and source terminals connected together,

the gate terminal of the compensating field effect transistor device being joined to the drain terminal of the second field effect transistor device, and

the size of the first and second field effect transistor devices being such that the currents of each device in saturation are equal.

2. A current mirroring circuit as claimed in Claim 1 further comprising:

- a second supply voltage,

- a third field effect transistor device arranged to provide a current path between the source of current and the second supply voltage,

- a fourth field effect transistor device arranged to provide a current path between the second supply voltage and the reference node,

- a detector circuit for determining the supply voltage in use, and

- a switching circuit for connecting the current path between the source of current and the supply voltage if the supply voltage is in use and for connecting the current path between the source of current and the second supply voltage if the second supply voltage is in use.

- 3. A current mirroring circuit as claimed in Claim 2 in which the supply voltage has a value of five volts, and

the second supply voltage has a value of not greater than 3.6 volts.

4. A current mirroring circuit as claimed in Claim 1 in which the first field effect transistor device has a width of 150 microns and a length of 5 microns, and

the second field effect transistor device has a width of 140 microns and a length of 5 microns.

# 5. A computer system comprising:

a central processing unit;

main memory;

a system bus; and

secondary memory joined to the system bus including:

- a current mirroring circuit comprising:

- a source of current to be mirrored,

- a supply voltage,

- a first field effect transistor device arranged to provide a current path between the source of current and the supply voltage,

- a compensating field effect transistor device arranged to provide a current path between the source of current and the supply voltage,

- a second field effect transistor device arranged to provide a second current path between the supply voltage and a reference node,

the first and second field effect transistor devices having gate terminals and source terminals connected together,

the gate terminal of the compensating field effect transistor device being joined to the drain terminal of the second field effect transistor device, and

the size of the first and second field effect transistor devices being such that the currents of each in saturation are equal.

- 6. A computer system as claimed in Claim 5 further comprising:

- a second supply voltage,

- a third field effect transistor device arranged to provide a current path between the source of current and the second supply voltage,

- a fourth field effect transistor device arranged to provide a current path between the second supply voltage and the reference node.

- a detector circuit for determining the supply voltage in use, and

- a switching circuit for connecting the current path between the source of current and the supply voltage if the supply voltage is in use and for connecting the current path between the source of current and the second supply voltage if the second supply voltage is in use.

- 7. A computer system as claimed in Claim 6 in which the supply voltage has a value of five volts, and

the second supply voltage has a value of not greater than 3.6 volts.

8. A computer system as claimed in Claim 5 in which the first field effect transistor device has a width of 150 microns and a length of 5 microns, and

the second field effect transistor device has a width of 140 microns and a length of 5 microns.

# 9. A current mirroring circuit comprising:

means for supplying a current to be mirrored,

means for supplying a voltage,

first field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a voltage,

compensating field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a voltage,

second field effect transistor means arranged to provide a current path between the means for supplying a voltage and a reference node.

the first and second field effect transistor means having gate terminals and source terminals connected together,

the gate terminal of the compensating field effect transistor means being joined to the drain terminal of the second field effect transistor means, and

the size of the first and second field effect transistor means being such that the drain voltages of each in saturation are equal.

10. A current mirroring circuit as claimed in Claim 9 further comprising:

means for supplying a second voltage,

third field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a second voltage,

fourth field effect transistor means arranged to provide a current path between the means for supplying a second voltage and the reference node,

means for determining the voltage in use, and

means for connecting the current path between the means for supplying a current and the means for supplying a voltage if the means for supplying a voltage is in use and for connecting the current path between the means for supplying a current and the means for supplying a second voltage if the means for supplying a second voltage is in use.

11. A current mirroring circuit as claimed in Claim 9 in which the voltage supplied by the means for supplying a voltage has a value of five volts, and

the voltage supplied by the means for supplying a second voltage has a value of not greater than 3.6 volts.

12. A computer system comprising:

a central processing means;

main memory means;

system busing means; and

secondary memory means joined to the system busing means including:

current mirroring circuit comprising:

means for supplying a current to be mirrored,

means for supplying a voltage,

first field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a voltage,

compensating field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a voltage,

second field effect transistor means arranged to provide a current path between the means for supplying a voltage and a reference node.

the first and second field effect transistor means having gate terminals and source terminals connected together,

the gate terminal of the compensating field effect transistor means being joined to the drain terminal of the second field effect transistor means, and

the size of the first and second field effect transistor means being such that the currents of each in saturation are equal.

13. A computer system as claimed in Claim 12 further comprising:

means for supplying a second voltage,

third field effect transistor means arranged to provide a current path between the means for supplying a current and the means for supplying a second voltage,

fourth field effect transistor means arranged to provide a current path between the means for supplying a second voltage and the reference node,

means for determining the voltage in use, and

means for connecting the current path between the means for supplying a current and the means for supplying a voltage if the means for supplying a voltage is in use and for connecting the current path between the means for supplying a current and the means for supplying a second voltage if the means for supplying a second voltage is in use.

14. A computer system as claimed in Claim 12 in which the voltage supplied by the means for supplying a voltage has a value of five volts, and

the voltage supplied by the means for supplying a second voltage has a value not greater than 3.6 volts.

- 15. A current mirroring system comprising:

- a source of current to be mirrored,

- a first supply voltage,

- a second supply voltage,

- a first self-compensating current mirroring circuit adapted to join the source of current, the first supply voltage,

and a reference node to mirror the current from the source of current at the node:

a second current mirroring circuit adapted to join the source of current, the second supply voltage, and the reference node to mirror the current from the source of current at the node; and

a switching circuit for connecting the first self-compensating current mirroring circuit between the source of current, the first supply voltage, and the reference node if the supply voltage is in use and for connecting the second current mirroring circuit between the source of current, the second supply voltage, and the reference node if the second supply voltage is in use.

- 16. A current mirroring system as claimed in Claim 15 in which the second current mirroring circuit is a self-compensating current mirroring circuit.

- 17. A current mirroring system as claimed in Claim 15 further comprising:

additional supply voltages;

additional mirroring circuits each adapted to join the source of current, one of the additional supply voltages, and the reference node to mirror the current from the source of current at the node; and

in which the switching circuit is adapted to connect one of the additional current mirroring circuit between the source

of current, one of the additional supply voltages, and the reference node if the additional supply voltage is in use.

18. A current mirroring system as claimed in Claim 15 in which the switching circuit includes a circuit generating signals to indicate a voltage level detected, and

transmission gates for connecting the source of current to the reference node through one of the mirroring circuits in response to signals generated to indicate a voltage level detected.

Figure 1

٤/٤

## INTERNATIONAL SEARCH REPORT

International application No. PCT/US97/02355

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(6) :G05F 3/16, 3/20 US CL :323/312, 315; 327/530, 543  According to International Patent Classification (IPC) or to both national classification and IPC |                                                                                                                                     |                                  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

| B. FIELDS SEARCHED                                                                                                                                                                                |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Minimum documentation searched (classification system followed by classification symbols)                                                                                                         |                                                                                                                                     |                                  |  |  |  |  |  |  |

| U.S. : 323/312, 315; 327/530, 543, 403, 404, 538, 545, 546                                                                                                                                        |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched NONE                                                                |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)  APS                                                                 |                                                                                                                                     |                                  |  |  |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                            |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Category* Citation of document, with indication, where a                                                                                                                                          | appropriate, of the relevant passages                                                                                               | Relevant to claim No.            |  |  |  |  |  |  |

| X US 4,300,091 A (SCHADE                                                                                                                                                                          | ET AL) 10 November                                                                                                                  | 1 and 9                          |  |  |  |  |  |  |

| 1981(10/11/81), Fig. 1-2                                                                                                                                                                          |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Y                                                                                                                                                                                                 |                                                                                                                                     | 5 and 12                         |  |  |  |  |  |  |

| Y US 4,629,973 A (VOOF 1986(16/12/86), Fig. 1b                                                                                                                                                    | RMAN) 16 December                                                                                                                   | 1, 5, 9, and 12                  |  |  |  |  |  |  |

|                                                                                                                                                                                                   |                                                                                                                                     |                                  |  |  |  |  |  |  |

| Further documents are listed in the continuation of Box                                                                                                                                           |                                                                                                                                     |                                  |  |  |  |  |  |  |

| <ul> <li>Special categories of cited documents:</li> <li>A document defining the general state of the art which is not considered</li> </ul>                                                      | "T" later document published after the inte<br>date and not in conflict with the applica<br>principle or theory underlying the inve | tion but cited to understand the |  |  |  |  |  |  |

| to be of particular relevance  *E* earlier document published on or after the international filing date                                                                                           | "X" document of particular relevance; the                                                                                           | claimed invention cannot be      |  |  |  |  |  |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other                                                         | considered novel or cannot be consider<br>when the document is taken alone                                                          | -                                |  |  |  |  |  |  |

| special reason (as specified)  O document referring to an oral disclosure, use, exhibition or other                                                                                               | "Y" document of particular relevance; the considered to involve an inventive combined with one or more other such                   | step when the document is        |  |  |  |  |  |  |

| means  "P" document published prior to the international filing date but later than                                                                                                               | being obvious to a person skilled in the art  "&" document member of the same patent family                                         |                                  |  |  |  |  |  |  |

| the priority date claimed  Date of the actual completion of the international search                                                                                                              | Date of mailing of the international search report                                                                                  |                                  |  |  |  |  |  |  |

| 16 JUNE 1997                                                                                                                                                                                      | <b>3 0</b> JUN 1997                                                                                                                 |                                  |  |  |  |  |  |  |

| Name and mailing address of the ISA/US Commissioner of Patents and Trademarks Box PCT Washington, D.C. 20231 Facsimile No. (703) 305-3230                                                         | Authorized officer  JUNG HO KIM  Telephone No. (703) 308-0956                                                                       |                                  |  |  |  |  |  |  |