- (54) An improved semiconductor read-only VLSI memory.

- (57) The performance of a hysteresis address input buffer of a VLSI ROM is improved by providing additional driving power to establish the high and low voltage transition points of the input buffer. The address transition detection circuit is improved by holding the previously latched address signal until a predetermined delay after receipt of the new address signal. The operation of signal buffers can be stabilized and the emission electrons avoided by selectively coupling the input to the last stage of the buffer to a predetermined voltage during any precharge hold time interval. The memory array is improved by providing an architecture for the columns of memory cells so that the signal from the address memory cell need propagate only on the diffusion bit lines by a distance no greater and no less than the length of the diffusion bit line within a single block of the memory cells. The architecture of the memory layout is improved by providing bit line and virtual ground line contacts at opposing ends of the memory block and by replicating the memory block through mirror symmetry on the semiconductor substrate.

10

15

20

25

30

35

40

45

The present invention relates to a read only memory (ROM), and in particular to improvements in the circuitry and methodology of the subcircuits included within a very large scale integrated (VLSI) ROM.

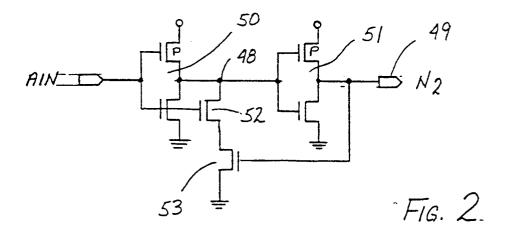

As shown in Figure 1, the overall structure of a prior art ROM is typically comprised of an input buffer circuit, an address transition detector circuit (ATD), an X and Y decoder circuit, a sense amplifier for reading the memory cells. A plurality of memory cells coupled to the input buffer and accessed through the X and Y decoder with their output completed to the sense amplifier, and an output buller circuit having its input coupled to the output of the sense amplifier. The function of the input buffer is to convert a TTL level signal into a voltage level compatible with the ROM when an address signal is received at the ATD circuit. The function of the address transition detector circuit is to detect address transitions from the output of the input buffer in order to generate appropriate timing signals within the ROM. The X and Y decoders decode an address to select a predetermined memory cell within the array. The sense amplifier reads the data stored in the memory cell. The output from the sense amplifier is then buffered to the output circuit for a TTL level output. Such prior art architectures are prone to several limitations as discussed below.

Prior art input buffer circuits typically have an input inverter stage with a threshold of 1.4 volts and operate within a 0.8 low logic level and 2.0 volt high logic level from a 5-volt supply voltage. The output voltage levels of the typical input buffer has a high logic level of 2.4 volts and a low logic level of 0.4 volts. Noise in the power supply line or signal line into the input buffer can often cause a malfunction, particularly at high data rates in an LSI chip. The voltage margins between ground level and the level of the low logic output or between the low level output voltage in the low logic level input voltage is only 0.4 volts.

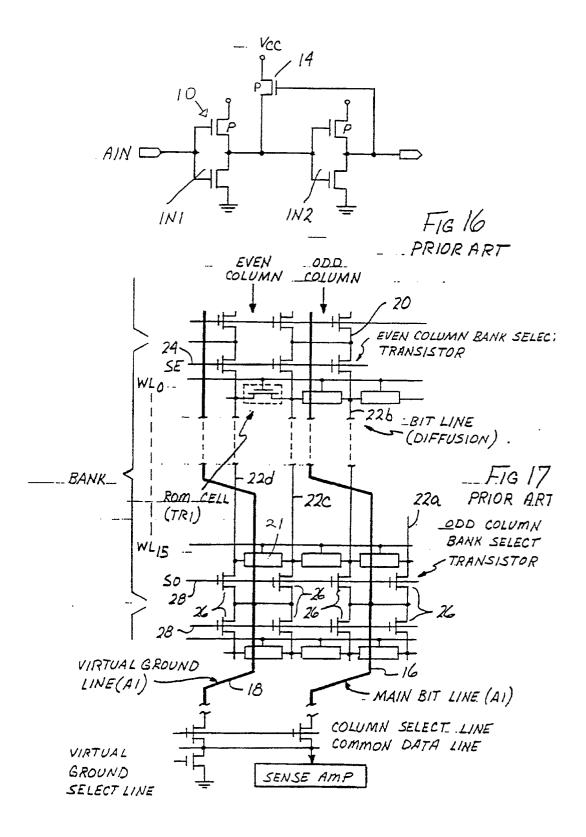

Therefore, the prior art has attempted to devise a solution wherein the initial input stage inverter of the input buffer is provided with a hysteresis property to prevent an instability which arises from ringing. The ringing can be caused when the input signal is converted from a high to low level or there is a drift or variation in the ground level. Figure 16 shows a typical prior art circuit having just such a hysteresis property as described in IEEE International Solid State Circuits Conference Digest of Technical Papers (1988), at pages 182-183. The prior art circuit is comprised of two CMOS inverter stages 10 and 12. The output of the first inverter stage 10 is connected to the input of the second inverter stage 12. The output of the second inverter stage 12 is fedback to the gate of a PMOS transistor 14 coupled to the voltage supply VCC. PMOS transistor 14 is turned on when the input is at a low level, thereby maintaining the output of the

inverter combination 10 and 12 at a low logic level. The buffer circuit of Figure 16 can thus not again go high until a voltage of sufficient level and stability is provided to switch both inverter circuits 10 and 12 to turn off load transistor 14 allowing a high logic output.

However, the prior art circuit of Figure 16 is subject to noise-induced malfunction. The LSI chip itself may create noise when the output buffer circuit is switched, in addition to being subject to externally created noise. The output buffer creates noise when the charge on a load capacitance flows into the ground line of the LSI chip from a driving transistor in the output buffer. A large transconductance, g<sub>m</sub>, of the driving transistor in the output buffer circuit causes the threshold value of an input inverter in the output buffer circuit to be substantially reduced and therefore easily influenced by a noise. For example, in the circuit of Figure 16, the threshold value of the initial input inverter 10 is inevitably shifted by the high transconductance of the driving transistor to cancel out the hysteresis property normally provided by load transistor 14 as described above. Hence, the input buffer of Figure 16 becomes susceptible to noise based malfunctions, either from spikes on the LSI ground line or from externally created noise sources. Furthermore, the input buffer of Figure 16 has the disadvantage that it cannot be implemented using only an NMOS methodology since PMOS load transistors are required.

Another limitation in the prior art pertains to address transition detection circuits. Conventional address transition detection circuits generate internal timing signals on the occurrence of an address transition. Typically in such an event all internal decode signals are set at a low level for a predetermined period after the address transition. This method is used in order to prevent power consumption caused by invalid addresses which occur during the transient state. However, this methodology results in a change in status of the internal decoding lines twice every time an address transition takes place. For example, after an address becomes valid the internal decoding is changed a first time to reflect the valid address and then goes to an all-logic low state and then transitions a second time to the next valid address. Power consumption is therefore increased at high data rates.

The prior art memories have also experienced shortcomings with respect to the memory array itself. A typical prior art planar memory cell array uses bit 50 lines formed by diffusion layers and word lines of polycide which intersect the bit lines. The source and drain regions of the MOS transistors are defined in the intersections between the word and bit lines. Channels are formed between the source and drain regions. The prior art has employed the concept of utilizing a bank selection methodology to preselect a prescribed memory cell in such a planar memory

2

10

15

20

30

35

40

45

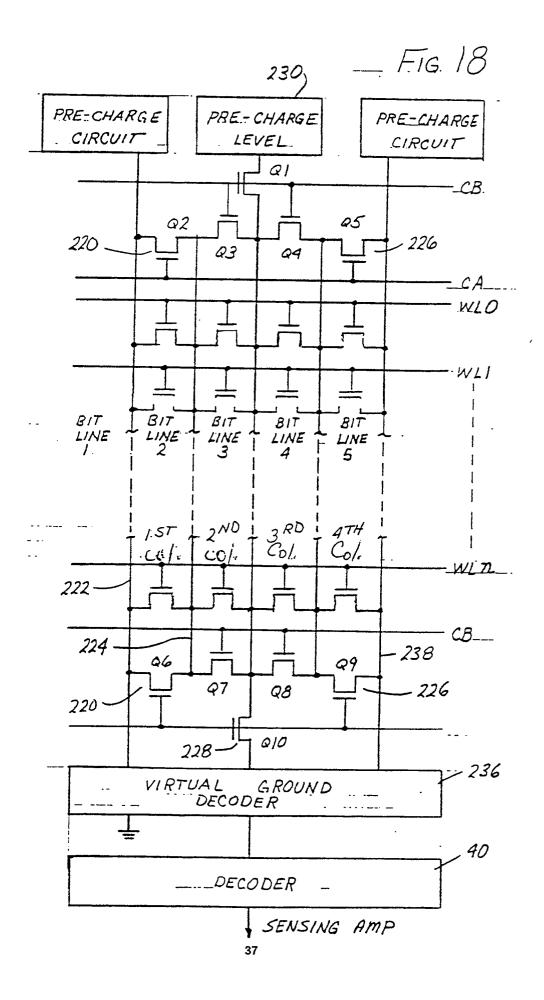

array. As previously stated, the bit lines are fabricated as diffusion lines and are characterized by approximate 30 ohms per square sheet resistance. Since the pitch of the diffusion lines in the array is about equal to the pitch of the gate wiring, about two diffusion ire sheets are provided for every memory cell. In the embodiment shown in Figure 17 there is a resistance of about 2 kilo-ohms for 32 cells in terms of parasitic wiring resistance.

When a memory cell is on, it has an internal resistance of about 19 kilo-ohms assuming that the on-state current is approximately 150 microamps and the bit line voltage is 1.5 volts. As a result, the number of memory cells provided between each group of bank select transistors 20 and 26, for example, is necessarily restricted in order to avoid unacceptable low relative voltage drops across the memory cells. This restriction in the number of cells between the bank select transistors not only decreases the degree of integration which can be achieved on the chip, but also limits the operational speed of the memory array.

As discussed above, the bit lines of such arrays are conventionally made of N + diffusion layers while the word lines are constructed of polycide. The selection transistor placed on the even bit lines is, as described, positioned at the upper end of each bit line. The gates of the selection transistors are driven by a common gate selection signal, SE. Similarly, transistors are placed in the lower end of the array for selecting the odd lines and are driven through their gates through a common select signal, SO. The main bit line, typically composed of aluminum is connected to a contact opposite the nth and nth + 1 bit lines. The same main bit line is connected to a contact opposite the nth + 1 and nth + 2 selection transistor bit lines. Analogously a virtual ground line is connected to the nth + 2 and nth + 3 odd selection bit transistors as well as the nth + 3 and nth + 4 even selection transistors. Main bit line 16 is connected directly to bit lines 22a and 22b respectively in the lower portion of the memory array in the proximity of column select transistors 26 and is connected to bit lines 22b and 22c respectively in the upper portion of the array in the vicinity of column select transistors 20. Similarly, the virtual ground line 18 is connected to bit lines 22c and 22d respectively in the lower portion of the array and is directly connected to bit lines (not shown) in the upper portion of the array.

When the even word lines or rows of the array are selected, the signal transmission path in the prior art circuit of Figure 17 includes a path through the corresponding bit line selection transistor 20, a first bit line, 22c, for example, through the target memory transistor 21, through a second bit line, 22d, for example, and then through a corresponding selection transistor 26 to the virtual ground 18. The capacity and resistance of the transmission path of the signal is thus twice that of the length of the bit line within the block. The same is true if the lowest row within an odd row is selected. As a result, such prior memories are subject to speed limitations and a restriction on the number of transistors which can be placed in a row within a single block. The degree of LSI integration is therefore limited.

It can also be readily appreciated by viewing Figure 17 that the bank select transistors 20 and 26 which are associated with main bit line 16 and virtual ground line 18 are both disposed in the same proximity within the chip. Therefore, any memory cell in the array has a symmetrical wiring resistance relative to main bit line 16 and virtual ground line 18.

Prior art ROM circuitry also suffered from a limitation in the dynamic timing and control of the output signal. Information is stored in the ROM, depending on whether or not a preset electrical charge is discharged in response to an address signal. This charge is read by a sense circuit. The read decision of a memory cell is made depending on whether a precharge level in the memory cell is changed to a circuit threshold value by a transistor in

difference between the memory cell current and leakage current sometimes cannot be distinguished by the sense amplifier. This causes a malfunction upon generation of unacceptably high leakage currents.

the memory array. In such a read methodology the

In conventional read-only memories, especially NOR-type memories, fast response times and low power consumption has been difficult to achieve due to poor manipulation of the bit lines. More recently larger and faster memory devices are being developed for NOR-type read-only memories. Thus far, none has utilized any technology which has improved the management of the bit lines within the memory.

A large capacity ROM necessarily contemplates LSI architecture for the memory cells, whether NOR or NAND type. In order to make a conventional large scale and a greater memory cell respond faster, dynamic manipulation of the bit lines has been attempted. However, this approach has resulted in unacceptable power consumption and therefore has not been utilized.

What is needed then is a way to manipulate bit lines in an LSI memory cell dynamically without consuming a large amount of power.

To solve this, one prior art system as described in the 1988 IEEE International Solid State Circuits Conference Digest of Technical Papers, pages 124-125 is provided with reference cells and array cells to detect the difference in current between the array cell and reference cell between the on and off states by adding an offset current only on the on-state reading cycle of the array. While this approach solved the problem of leakage currents, an access delay is caused if the offset current is not equal to the average

10

15

20

25

30

35

40

45

50

current flowing through the array cell during both the on and off states. Moreover, it is difficult to generate such an offset current independently of the voltage supply level.

Prior art output buffer circuits have experienced slow switching speeds in the NMOS output transistors. For example, as described in the IEEE Journal of Solid State Circuits, Vol. 23, No. 5, 1988 at pages 1054 1058, an output buffer circuit suppresses the peak of current flowing from an output pin by temporarily setting its output at an intermediate potential between the high and low logic levels. However, since the output is temporarily set at an intermediate potential, current flows through the output circuitry if a CMOS device is provided as the input of the next stage. In the circuit described in the 1988 IEEE Solid State Circuits Conference Digest of Technical Papers, pages 120-121, a bias signal is applied to an NMOS transistor in the final inverter stage of the output buffer circuit through a coupling transistor. The bias voltage is applied to a coupling transistor. Since the bias voltage is fixed between zero volts and the supply voltage, the switching speed of the final stage, NMOS transistor is increased. The increase in switching speed is utilized to suppress the peak current which flows from the output pin to ground when the output level switches from a high to a low logic level. However, since the switching rate of the NMOS transistor is increased, excessive time is required to convert the output to a high output level.

Among the efforts currently being made in the art to produce larger and denser semiconductor devices, is the use of dynamic circuits for constructing larger scale and faster memories. However, a conventional dynamic circuit has a data hold period in the buffer, that is, the period during which data must be held regardless of the circuit's gated diffusion capacity. Therefore, due to pattern layout architecture, performance during hold periods may be erratic. If the signal is affected by coupling noise input through a gate, the transistor may enter a half-on state, if not malfunctioning altogether, because the gate voltage is boating and not driven. This in turn leads to the emission of hot electrons. Hot electrons can affect the reliability of the array and can be substantial where the circuit is highly miniaturized. Therefore, what is needed is a dynamic circuit which is not affected by these coupling noises.

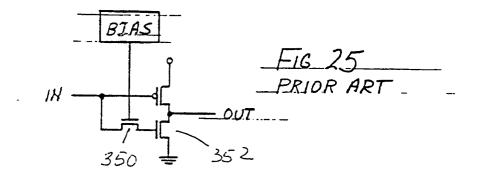

Refer briefy to Figure 25 which shows a prior art circuit used to deal with noise in an output buffer. Noise is reduced by applying an intermediate voltage or bias to the gate of a transistor 350 when the input signal, IN, changes from the logic low to the logic high to cause transistor 352 to enter a half-on state which would gradually drain the current from the output port to ground. This increases the buffer's time delay when the process variations, device temperatures and/or voltage levels are in their slowest state. The usual methods to generate a bias level is to generate an analog voltage that varies with temperature and process conditions and that allows some compensation in response to those conditions. In using these prior methods it is difficult to adjust the voltage level. The solution suffers from the limitation and the compensation tends to slow down to the slowest circuit part, thereby causing a substantial degradation in the worse case speed specification in the circuit. It is also important to note that when the circuit is in its slowest condition, compensation may not be necessary and may in effect be detrimental.

In this case, if the bias voltage is fixed at an intermediate level, delay of the output buffer becomes excessively large even though the noise in the output buffer is reduced. What is needed then is a means and method of solving the problem with a bias voltage supply circuit which can adjust the bias voltage, taking process variations into consideration as well as circuit speed reaction to voltage level.

Therefore, it is an object of this invention to provide a ROM circuit which overcomes above-discussed shortcomings of the prior art. For example, one object of the invention is to avoid noise induced malfunctions caused by the driving transistor in the input buffer circuit.

Another object is to provide an input buffer circuit which is usable in LSI chips based both on NMOS and CMOS technologies.

It is another object of the invention to provide a memory array which can be laid out in a smaller area as well as providing an increase in memory speed or decrease in access time.

It is further an object of the invention to provide a sense circuit in the ROM which can compensate for off-state current of the memory cells and leakage current in the memory cells to avoid malfunction.

It is still further an object of the invention to provide a sense circuit which can adjust loads in response to the driving signal from the memory cells in order to prevent loss of circuit speed and to reduce noise even if the on-state current in the memory cell is varied.

It is still further an object of the invention to provide an output buffer circuit which is not characterized by a high switching current and still has a fast switching speed.

## Brief Summary of the Invention

The performance of a very large scale integrated READ ONLY MEMORY circuit is improved by improvements in one or more of various circuits and methodologies utlized in the memory. The performance of a hysteresis address input buffer is improved by providing additional driving power to establish the high and low voltage transition points of the input buffer. The address transition detection

4

5

10

15

20

25

circuit is improved by holding the previously latched address signal until a predetermined delay after receipt of the new address signal. The operation of signal buffers can be stabilized and the emission of hot electrons avoided by selectively coupling the input to the last stage of the buffer to a predetermined voltage during any precharge hold time interval. The memory array is improved by providing an architecture for the columns of memory cells so that the signal from the address memory cell need propagate only on the diffusion bit lines by a distance no greater and no less than the length of the diffusion bit line within a single block of the memory cells. The architecture of the memory layout is improved by providing bit line and virtual ground line contacts at opposing ends of the memory block and by replicating the memory block through mirror symmetry on the semiconductor substrate. The memory array is further improved by providing bank selection transistors for each bank at each opposing end of a memory block so that propagation of the contents of an address memory cell need only travel the length of a single bit diffusion line. The operation of the memory array is improved by a precharge methodology wherein virtual ground lines, main bit lines and bit diffusion lines are precharged on each memory cycle even though not selected and wherein said bit line to the sense amplifier is precharged though not selected. The operation of the sense amplifier is improved by providing dummy bit lines corresponding to the ON state and OFF state of the memory cells, averaging the voltage on the dummy bit lines, and comparing that average to the bit line voltage to generate a differential sense output. Leakage currents and voltages common to both the dummy bit lines and selected bit line are thus cancelled out. Sense amplifiers incorporating this advantage may also be used in combination with a dynamic latch which is selectively disconnected from the memory array at all times other than during a memory cycle to avoid noise interference. The bias of such sense amplifiers can be compensated to reflect individual process and operating variations in each memory circuit. Noise inserted on the ground line from an output buffer is avoided by providing a two-staged transition of the output buffer when selected to generate a low active output. Dummy word lines used in combination with dummy predecoder and decoder are used to make on-chip determinations of the transition points when an address signal is valid and complete. The actual initiation of the addressing of the memory may then be triggered according to a modeled transition point within each memory circuit. The ON state and OFF state voltages on dummy bit lines are used in a trigger circuit to generate a trigger signal for use in sense amplifiers which will reliably indicate when a valid sense decision can be made taking into consideration the individual process parameters and operating

conditions of the actual memory circuit. Appropriate bias levels are generated by a bias circuit for use in the output buffer according to whether a process temperature and voltage variations within the memory circuit are such that variation sensitive components will be slowed upon the occurrence of such variations. The bias circuit otherwise generates a bias signal appropriate for fast speed operations within the output buffer circuit when process temperature and voltage variations are such that they do not effect circuit speed of sensitive circuit portions. The back bias generator which operates asynchronously from the memory cycle is improved by disabling the charge pumping action during a memory cycle. Output enabling signals are selectively inhibited by a control circuit which determines when the memory cycle is actual completed. Memory circuit operation is further improved by performing a predecode precharge signal to the memory circuit beginning with the detection of an address transition and holding a predecode charge until the memory cycle is begun notwithstanding conflicts which may later occur between address transition detection signals and signals indicative of memory cycle initiation so that inadvertent lockup of the memory cycle is prevented.

The invention is an improvement in a read only memory including an addressable memory. The memory is addressed by an address signal through an input buffer. The improvement comprises a first inverter stage of the input buffer. The first inverter 30 stage has an output and an input coupled to the address signal. A second inverter stage is provided in the input buffer. The second inverter stage has an input coupled to the output of the first inverter stage 35 and has an output for coupling with the memory. A first and second transistor are coupled together in series circuit. The first transistor is coupled to the output of the first inverter stage and the input of the second inverter stage. The second transistor is coupled to 40 ground. The first and second transistors are controlled by corresponding gates. The gate of the first transistor is coupled to the address signal and the gate of the second transistor is coupled to the output of the second inverter stage.

As a result, operation of the input buffer has a hysteresis characteristic substantially independent of noise.

The invention is an address input buffer in an addressable memory circuit addressable by a 50 plurality of address signals. The invention comprises an input of the buffer circuit coupled to one of the address signals. An output of the buffer circuit is coupled to the memory. A circuit establishes a threshold voltage of the input of the buffer circuit when 55 the address signal goes from a low logic level to a high logic level. The threshold voltage is established at a first predetermined level. Another circuit establishes a second threshold voltage at a second

5

The input of the input buffer circuit comprises a first inverter stage and the output is a second inverter stage coupled with the first inverter stage. The circuit for establishing the first threshold voltage comprises the first inverter stage and the circuit for establishing the second threshold voltage comprises two transistors coupled in series circuit from the output of the first inverter stage and the input of the second inverter stage to ground. The two transistors each have a gate. The gate of one of the two transistors is coupled to the input of the buffer circuit and the gate of the other one of the two transistors is coupled to the output of the buffer circuit.

The invention is an improvement in a memory circuit including an address transition detection circuit for receiving an address signal to address the memory and for generating an address transition detection signal indicating validity of the address signal. The improvement comprises a latch circuit included within the address transition detection circuit for selectively holding the address signal and, at a predetermined command, for latching a successor address signal. The address transition detection circuit detects a change of state of the address signal. A delay circuit is coupled to the address transition detection circuit and generates the predetermined command signal to the latch circuit in response to detection of address transition from the address transition detection circuit.

As a result, the address state of a preceding cycle is maintained while the address signal is indefinite. As a further result, the new address state is established only after the address is defined therefore avoiding unnecessary power consumption caused by unnecessary switching in the memory circuit.

The latch circuit is not reset to the new address state until expiration of a predetermined time interval defined in part by the delay circuit so that address signals coupled to the address transition detection circuit do not cause output changes during the predetermined time interval.

The delay circuit comprises a delay circuit and transistor circuit coupled to the input of the latch circuit. The transistor circuit receives signals corresponding to the address signals and transits the corresponding signals to the latch circuit when selectively permitted by a delayed command signal generated by the delay circuit.

The address transition detection circuit comprises a first and second selectively controlled transistor having gates controlled by the output of the latch circuit. The first and second transistor passes

the address signal through the transistors to the output of the address transition detection circuit. One of the first and second transistors has the logical complement of the address signal input thereto with the other one of the transistors having the address signal input thereto.

The invention is an improvement in a memory circuit having an array of addressable memory cells organized into blocks of memory cells and including a plurality of diffusion bit lines, virtual ground lines and a main bit line. Each the diffusion bit lines, virtual ground lines and main bit line longitudinally disposed through the blocks of memory cells. Each block has a first and second end. The diffusion bit lines, virtual ground lines and main bit line are disposed between the first and second end of each the block. The improvement comprises a plurality of contacts connected to the virtual ground lines and main bit line at each the end of each block. A ground selectively is

coupled to one of the plurality of contacts. A sense amplifier is selectively coupled to the main bit line through one of the plurality of contacts. The ground and sense amplifier are connected to corresponding ones of the contacts at each the end of each the block.

A circuit selectively couples the ground and sense 25 amplifier to selected ones of the virtual ground lines and main bit line in response to command signals. Access to any one of the memory cells within each block made through the selected virtual ground lines, corresponding bit diffusion lines, main bit line and sense amplifier never exceeds the length of the selected block of memory cells.

As a result, parasitic capacitance is avoided, memory access speed is increased, and the capacity for memory cell density is increased.

Two virtual ground lines are provided and the circuit for selective coupling the virtual ground lines to ground selectively couples one of the two virtual ground lines to ground and the other of the two virtual ground lines to a precharge voltage.

Each of the virtual ground lines and main bit line has a contact connected therewith at opposing ends of each the block of memory cells.

Each virtual ground line and main bit line has one of the plurality of contacts connected therewith at each the end of each the block of memory cells so that a circuit path through the contact to the virtual ground line, addressed memory cell, at least one diffusion bit line and the main bit line is never substantially more than the length of the addressed block of memory cells. No memory cell is further distant from corresponding contact circuit connected to the virtual ground line and main bit line than approximately one half the length of the block of memory cells.

The invention is also an improvement in a memory circuit having a plurality of addressable memory cells arranged in a plurality of blocks. The plurality of memory cells is logically organized in

55

10

15

5

20

- 30

35

40

45

10

15

blocks.

columns. The columns of memory cells are coupled together by diffusion bit lines. The memory blocks are provided with at least one virtual ground line and a main bit line. The improvement comprises a first circuit for selectively coupling the virtual ground line to the diffusion bit line. The first circuit is coupled to one end of the addressed blocks of memory cells. A second circuit selectively couples a selected one of the diffusion bit lines to the main bit line. The second circuit is coupled to the opposing end of the addressed block from the first circuit. Access to a selected one of the addressable memory cells requires transmission of a signal on a path including at least one of the diffusion bit lines no greater in aggregate length than the length of the addressed block.

The block of memory cells is comprised of four columns of memory cells. The first circuit is coupled to two of the columns while the second circuit is coupled to the other two of the four columns. Two diffusion bit lines correspond to each column of the memory cells. The first circuit selectively shorts together two corresponding diffusion bit lines corresponding to columns selected by the first and second circuit respectively. An addressable memory cell is read through the main bit line which is selectively coupled to the addressable memory cell through the second circuit with completion of the circuit path through the addressed memory cell through the first circuit to the virtual ground.

The memory circuit is provided with two virtual ground lines symmetrically disposed relative to the main bit line and further comprises a second block of memory cells identical in architecture to the first block of memory cells but laid out with mirror symmetry relative to an imaginary line perpendicular to the virtual ground lines and disposed at one end of the first block of memory cells.

The improvement further comprises contacts with the main bit line and the virtual ground lines. The contacts provided to the first block of memory cells are used in common with the mirror symmetrical second block of memory cells.

In another embodiment the invention is an improvement in a memory comprising a plurality of addressable memory cells arranged in logical columns to form a plurality of blocks of memory cells. Each column has two corresponding diffusion bit lines disposed along the length of the block of memory cells. The memory cells are arranged and configured into four columns with the main bit diffusion line corresponding to the second and third columns of memory cells. The improvement comprises a virtual ground decoder for selectively coupling a first and second one of the diffusion lines to ground. A first circuit is disposed at each end of the blocks for selectively coupling the diffusion bit lines coupled to the virtual ground decoder to an adjacent diffusion bit line. A second circuit is disposed at each end of the blocks for selectively coupling the main bit diffusion line with two adjacent bit diffusion lines. The adjacent bit diffusion lines also are coupled through the first circuit to the virtual ground decoder. The virtual ground decoder is disposed solely at one end of the

As a result, the length of the circuit path of a signal read from any one of the addressed memory cells through the bit diffusion lines does not exceed in aggregate substantially more than one length of the memory block.

The improvement further comprises a precharge circuit. The first and second diffusion lines and the main bit line bit diffusion line are each coupled to the precharge circuit. The precharge circuit is disposed at the end of the memory blocks opposing the virtual ground decoder.

The invention is still further a memory circuit comprising a plurality of word lines. A memory block comprises a plurality of addressable memory cells coupled to the word lines. A control circuit is coupled to the memory block for producing a plurality of precharge and control signals for reading the memory block. A word line decoder is coupled to the memory

block. A word line decoder is coupled to the memory block for providing address signals to the memory block A dummy word line decoder generates simulative address signals. A first and second dummy word line are electrically simulative to word lines

within the memory block. One of the dummy word 30 lines models a previously selected word line within the memory block and the other one of the dummy word lines models a newly selected word line within the memory block. A circuit alternately designates to the dummy word line decoder which one of the first and 35 second dummy word lines models a previously selected word line and which one models a newly selected word line. The circuit is coupled to the first and second dummy word lines. A transition control circuit is coupled to the first and second dummy word 40 lines for determining the transitional time when the dummy word lines have set up a complete and valid address. The transition control circuit is coupled to the control circuit to initiate operation of the control circuit to allow reading of the memory block by the word line 45 decoder depending upon the transition completion as

determined by the transition control circuit. The first and second dummy word lines are constructed to electrically match word lines used within the memory block.

Precharge, timing and control signals generated by the control circuit are initiated by the control circuit in response to determinations made by the transition control circuit as individualized to the memory circuit according to actual observed transition points within the first and second dummy word lines.

The control circuit comprises a dummy memory cell constructed to model memory cells within the

55

10

15

20

25

30

35

40

45

50

memory block. The control circuit determines when a preselected voltage transition point in the output of the model memory cell occurs to determine the time of complete address setup.

The invention is still further an improvement in a memory circuit including an address decoder for providing an address signal to addressable memory cells within a memory array. The address decoder comprises a decoding block having an input for receiving address signals, a prebuffer block coupled to the decoding block, and a buffer block coupled to the prebuffer block for generating decoded output address signal. The improvement comprises a first circuit for selectively coupling the output voltage of the decoding block. A second circuit receives the output voltage from the decoding block from the first circuit and selectively couples the voltage to the input of the buffer block when the buffer block is enabled for output.

The first circuit and second circuit selectively couple the output voltage of the decoding block to stabilize the buffer block and avoid emission of hot electrons.

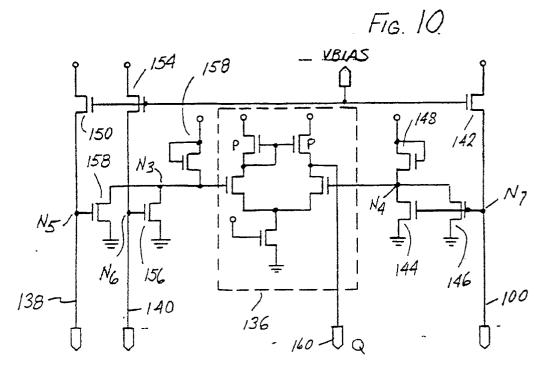

The invention is an improvement in a sense amplifier in a memory circuit having an array of addressable memory cells. The sense amplifier reads the output from the memory array. The improvement comprises a differential amplifier and first and second dummy bit lines. A first and second plurality of dummy memory cells, which are each capable of being selectively programmed into an ON or OFF state, are provided. Each dummy memory cell is electrically similar to the memory cells in the array. The first plurality of dummy memory cells is coupled to the first dummy bit line and is programmed into the ON state. The second plurality of dummy memory cells is coupled to the second dummy line and is programmed into the OFF state. A main bit line is coupled to the memory cells in the array. An addressed one of the memory cells is selectively coupled to the main bit line. A buffer has an input coupled to the main bit line and an output coupled to the differential amounter. An averaging buffer has an input coupled to the st and second dummy bit lines and an output coupled to the differential amplifier. The differential amplifier amplifies the difference between the output of the buffer and the averaging buffer.

As a result, leakage current in the memory circuit is uniformly applied to the main bit line and to the first and second dummy bit lines so that dependence on the leakage current in the output of the sense amplifier is eliminated.

The first plurality of dummy memory cells is disposed within the memory circuit in a region where word line voltage within the memory circuit is at its maximum level.

The second plurality of dummy memory cells is disposed within the memory circuit in a region where word line voltage will be a minimum.

The averaging buffer produces at its output a voltage which is substantially the arithmetic average of the voltage on the first and second dummy bit lines. The arithmetic average is substantially equal to sum of the average voltage between the ON and OFF state of the memory cells within the memory array and the leakage voltage within the memory circuit.

The invention is an improvement in a memory circuit having a plurality of addressable memory cells including a trigger circuit for sensing the contents of the memory cells. The improvement comprises a first and second dummy word line. A first and second plurality of dummy memory cells are coupled to the first and second dummy word lines respectively. The dummy memory cells are each capable of being selectively programmed into an ON state or OFF state. The first plurality of dummy memory cells is preprogrammed to the ON state and the second plurality of dummy memory cells is preprogrammed to the OFF state. A sensing stage circuit detects the difference in potential between the first and second dummy word lines. The sensing stage circuit is coupled to the first and second dummy word lines.

The memory includes output drivers and the sensing stage circuit determines when there is enough current in the first and second dummy word lines to latch data and to turn on the output drivers within the memory circuit.

The memory circuit further includes a sensing stage and wherein the sensing stage has an input which electrically emulates the input of the sensing latch.

The improvement further comprises a sense amplifier coupled to the memory cells. The sensing stage determines the amount of current drive received from the first and second dummy word lines which is required before the sense amplifier is allowed to make a decision as to the contents of the addressed memory cell.

The improvement further comprises an amplifier circuit having its input coupled to the output of the sensing stage circuit and having an output for generating the amplified difference of the voltage on the first and second dummy word lines. A level detect circuit has an input coupled to the output of the amplifier circuit. The level detect circuit converts the output of the amplifier circuit to a preconditioned signal. An inhibit circuit prevents false triggering during a nonsensing time period when a predetermined precharge signal is active.

The memory cells are organized into blocks of memory cells in a memory circuit having an memory array with a plurality of addressable memory cells. The invention is an improvement wherein each block of memory cells is provided with a virtual ground line and main bit line. A low address Y decoder circuit selectively couples the virtual ground line and main bit

8

line of a selected block of the memory array. A high address Y decoder circuit selectes a subportion of the selected block. The high address Y decoder circuit is coupled to the low address Y decoder circuit. The output of the high address Y decoder circuit is provided as an output bit signal of the addressed memory cell within the memory array. A bit precharge circuit charges a selected main bit lines of the memory array to be coupled with the sense amplifier. A blanket precharge circuit charges all main bit lines and virtual ground lines within the memory array to a predetermined precharge level. A bank precharge circuit selectively couples together the virtual ground lines and main bit line within a selected block of memory cells so that previous data from any previously selected memory cells within the block is eliminated and the main bit lines and virtual ground line within the selected block are equally precharged with a predetermined precharge level.

The improvement further comprises a bit line, and a sense amplifier coupled to the memory array by the bit line. The bit precharge circuit precharges the bit line coupled to the input of the sense amplifier even when the bit line coupled to the sense amplifier is not selected, thereby improving speed of the sense amplifier when the bit line is in fact selected and protecting the sensing amplifier from switching noise within the memory cycle.

The blanket precharge circuit simulates a static precharge of all the main bit lines of the memory array.

Each of the block of memory are organized into banks and the bank precharge circuit precharges all bit lines within the selected block of memory cells including nonselected banks of memory cells within the block to eliminate the effect of any preceding memory cycle and prepare the block for a new memory cycle and to suppress bit line delay.

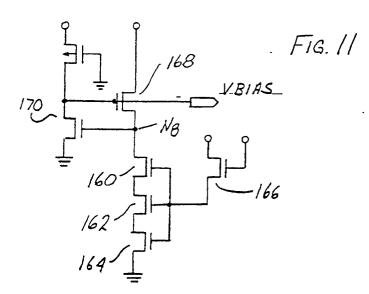

The invention is an improvement in a memory circuit having a memory array with a plurality of addressable memory cells. The memory cells are read by a biased sense circuit. The improvement comprises an output inverter stage having a drive transistor controlled by a gate. The output inverter stage generates a bias voltage applied to the sense circuit. A compensation inverter has a plurality of drive transistors for conducting a drive current through the compensation inverter responsive to variations in process parameters and operating conditions. The compensation inverter has an output coupled to the gate of the drive transistor of the output inverter so that the sense amplifier is biased in response to the variations in process parameters and operating conditions.

The plurality of drive transistors in the compensation inverter electrically simulate the memory cells within the memory array in terms of device parameters and operating conditions.

The invention is an improvement in a memory

circuit having a memory array with a plurality of addressable memory cells including a sense amplifier for reading the contents of the addressable memory cells. The invention comprises a first and second

dummy bit line. A corresponding first and second 5 plurality of dummy memory cells coupled to the first and second dummy bit lines respectively. A bit line is selectively coupled to an addressable one of the memory cells within the memory array. A dynamic

latch is provided. An averaging circuit is coupled to 10 the first and second dummy bit lines for averaging the voltage on the dummy bit lines and coupling the voltage to the dynamic latch. The bit line is also coupled to the dynamic latch. The dynamic latch 15

latches to a logic state depending on whether the logic level on the bit line is higher or lower than the average of the logic levels on the first and second dummy bit lines. The dynamic latch latches to a high logic level when the bit line is at a higher logic level than the average of the logic levels on the first and second

20 dummy bit lines. The dynamic latch latches to a low logic level if the logic level on the bit line is lower than the average logic level on the first and second dummy bit lines. First and second buffer circuits are coupled to the dynamic latch for coupling the latched state of 25

the dynamic latch to an output. The improvement further comprises a circuit for

disconnecting the dynamic latch from the memory cells of the memory array during a predetermined addressing time interval so that the dynamic latch is insensitive to noise occurring outside the predetermined addressing time interval.

The invention is an improvement in a memory circuit having a memory array including a plurality of addressable memory cells and an output buffer for generating an output signal corresponding to an addressed one of the memory cells at an output. The improvement comprises a buffer circuit for receiving a data signal derived from the memory array and for generating an output data signal from the memory circuit. A control circuit is coupled to the buffer circuit and changes the current of the output data signal by a plurality of steps so that peak current is controlled to suppress instability of ground voltages at the output of the buffer circuit. 45

The control circuit comprises a bias circuit for generating a two-step bias voltage. The bias circuit is coupled to the buffer circuit. The buffer circuit comprises a drive circuit coupled between the output and ground. The bias voltage is applied to the drive circuit to connect the output to ground at a first level of conduction and after a predetermined time delay at a second level of conduction so that current flowing from the output to ground is provided in two steps.

The invention is an improvement in a memory circuit having a memory array comprising a plurality of addressable memory cells including a bias circuit for generating a bias voltage for use within the memory

9

55

50

30

35

10

15

20

25

30

35

40

45

50

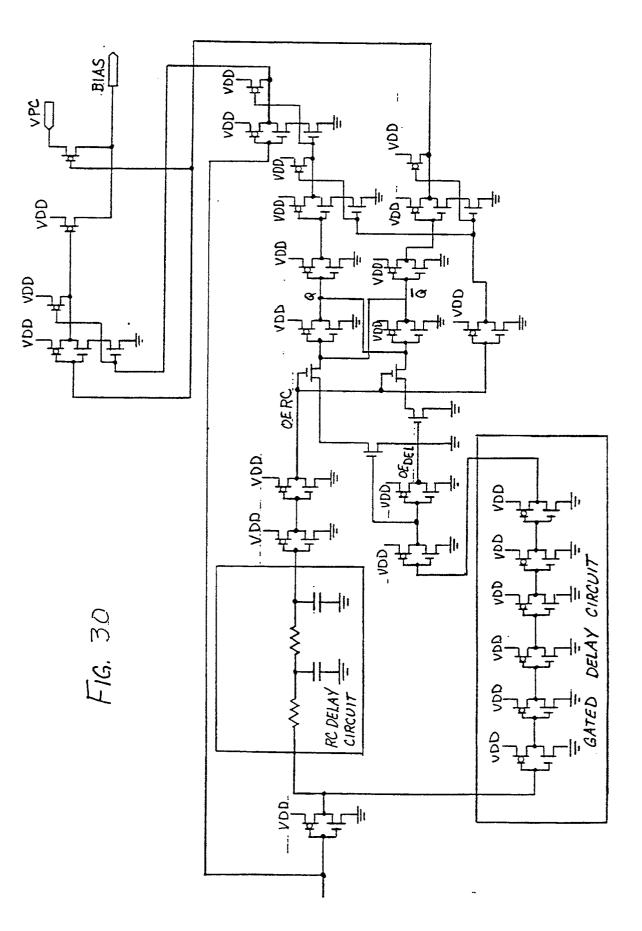

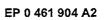

circuit for setting of operating points of circuits therein. The improvement in the bias circuit comprises an RC delay circuit for generating a timed delay. The RC delay circuit has an input coupled to a memory circuit enable signal input. A gate delay circuit generates a time delay based on average gate performance within the memory circuit. The gate delay circuit has an input coupled to a memory circuit enable signal input. A latched logical compare circuit is coupled to the RC delay circuit and gate delay circuit. The latched logical compare circuit compares the delayed signals from the RC delay circuit and gate delay circuit, and determines which is first in time. The latched logical compare circuit latches to a distinguishable state depending upon which of the delay signals from the RC delay circuit and gate delay circuit is first in time. A switching circuit generates a bias potential depending upon the state of the latched logical compare circuit.

17

The RC delay circuit is comprised of a plurality of capacitors and resistors and is substantially independent of process, temperature and voltage variations. The gate delay circuit comprises a plurality of inverters constructed to be representative of the general circuit speed within the memory circuit.

The gate delay circuit is constructed to model portions of the memory circuit whose speed of operation is affected by variations in temperature and voltage.

Among the circuits in the memory circuit is an output buffer circuit. The switching circuit provides a bias voltage to the output buffer circuit at a voltage level sufficient to reduce noise within the output buffer circuit.

The invention is an improvement in a memory circuit having a memory array including a plurality of addressable memory cells. The memory cells are addressed in a memory cycle. The improvement comprises an oscillator for generating a clock signal. A buffer receives the clock signal and generates a predetermined buffered signal in response. A charge pump receives the buffered clock signal ad generates a back bias voltage for use within the memory circuit. A circuit selectively disables the oscillator to prevent generation of the clock signal upon a predetermined logical condition. The circuit disconnects the oscillator from the buffer during the memory cycle.

The invention is an improvement in a memory circuit having a memory array and a plurality of addressable memory cells within the array. The improvement comprises a back bias generator for generating a back bias voltage coupled to the substrate in which the memory circuit is disposed. A circuit is provided for inhibiting generation of the back bias voltage during the memory cycle.

The invention is an improvement in a memory circuit having a memory array and a plurality of memory cells within the memory array, further including a sense circuit for reading the contents of an addressed one of the memory cells and an output buffer coupled to the sense circuit to generate a data output signal from the memory circuit. The improvement comprises a first circuit for generating a first state when an address transition is detected within the memory circuit and for generating a second state when the sense amplifier has completed reading of an address memory cell. A second circuit resets the first circuit in the second state after the sense amplifier has completed reading the addressed memory cell. A third circuit inhibits a memory circuit enable signal until the first circuit has determined that a memory cycle is complete by detection of the address transition followed by completion of the sense amplifier reading of the address memory cell.

The invention is an improvement in a memory circuit having a memory array comprising a plurality of addressable memory cells including a memory control circuit for controlling operation of the memory circuit in response to address changes. The improvement comprises a first circuit for storing a signal indicative of the fact that an address transition has occurred within the memory circuit. The first circuit generates a predecode precharge signal to initiate a memory cycle within the memory array. A second circuit is coupled to the first circuit. The second circuit inhibits any additional latching action of the first circuit after the memory cycle is begun and until the memory cycle is completed.

The first circuit comprises a latch set by any one of a plurality of address transition detection signals provided by the memory circuit thereto.

The second circuit is a latch to inhibit any latching of the first circuit after initiation of the memory cycle following receipt by the first circuit of the address transition detection signal from the memory circuit until completion of the memory cycle as determined by the control circuit so that lockup of the first circuit is prevented regardless of conflict between receipt of the address transition detecting signals and the beginning of the memory cycle.

The various embodiments of the invention can better be visualized and understood by turning to the following drawings wherein like elements are referenced by like numerals.

## **Brief Description of the Drawings**

Figure 1 is a block diagram showing a typical read only memory architecture in which the invention is embodied.

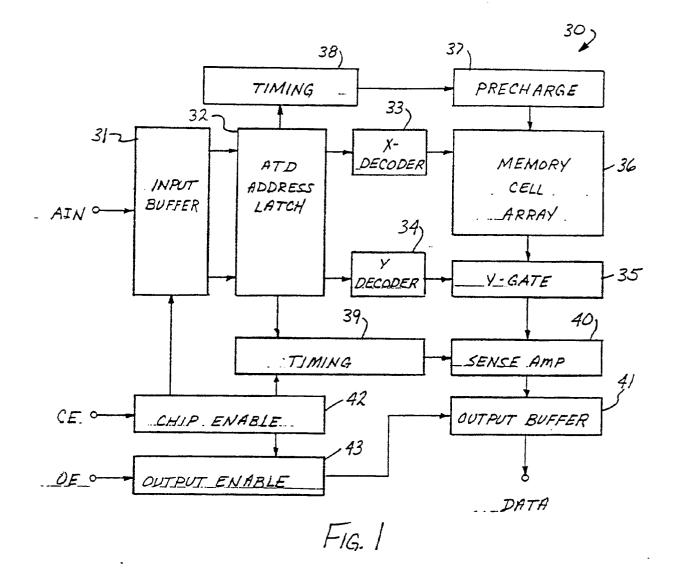

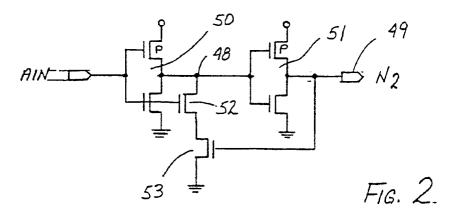

Figure 2 is a schematic of an input buffer circuit incorporating the invention.

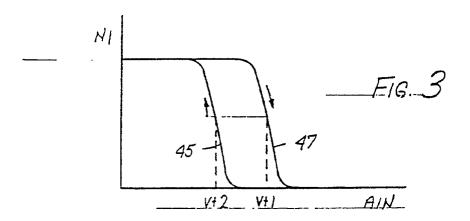

Figure 3 is a graph of the operating voltages of the circuit of Figure 2.

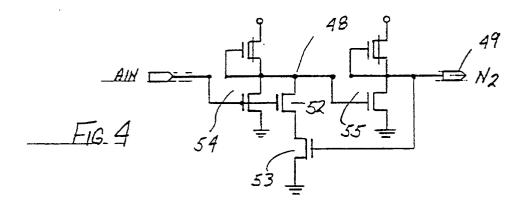

Figure 4 is a circuit diagram showing another embodiment of an input buffer incorporating the

10

15

20

25

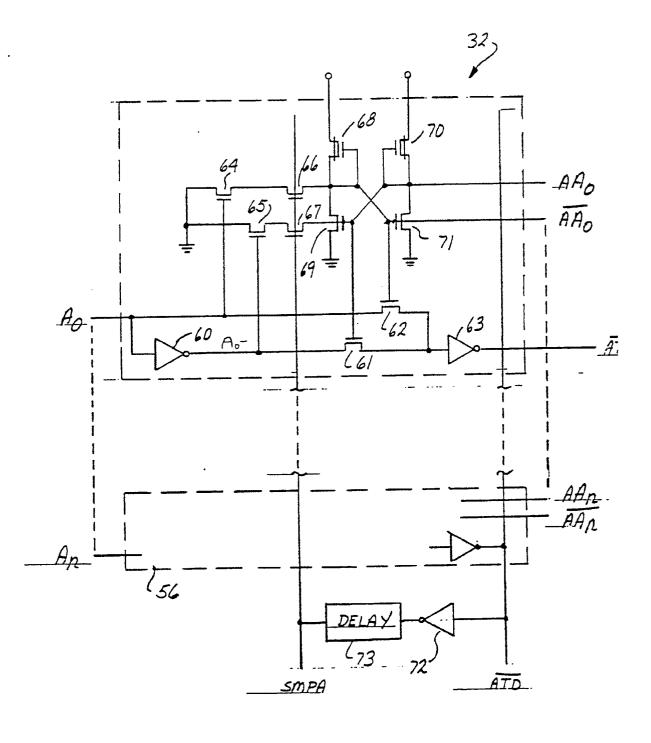

invention. Figure 5 is a schematic diagram showing an address transition detection circuit of the invention.

19

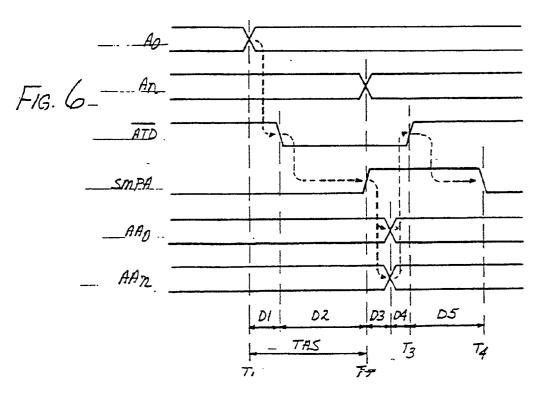

Figure 6 is a timing diagram of the circuit of Figure 5.

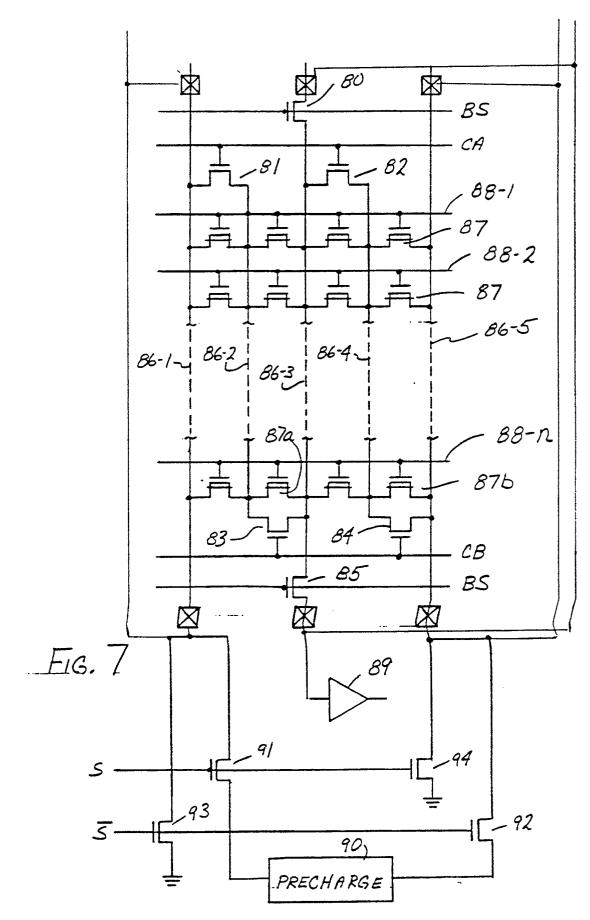

Figure 7 is a schematic diagram showing a memory cell array incorporating the invention.

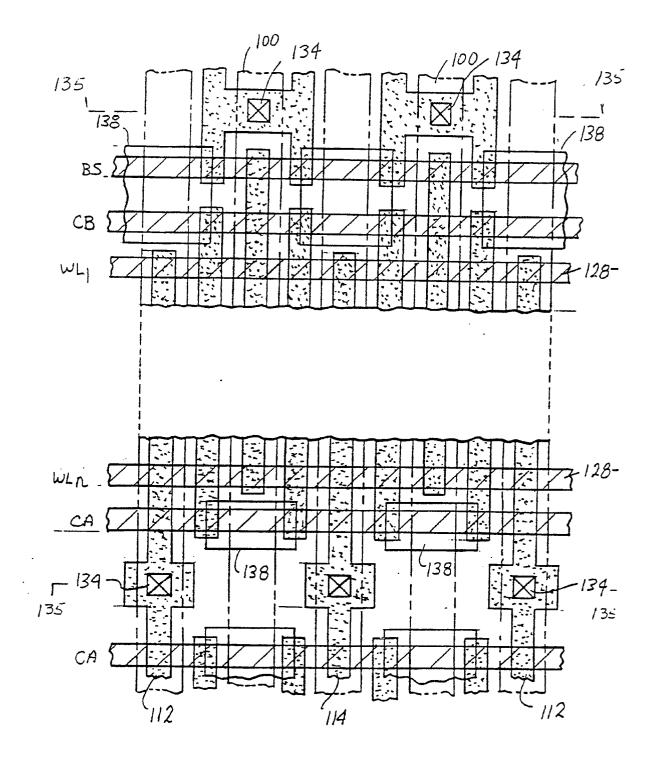

Figure 8 is a plan view of the diffusion and wiring pattern in an integrated circuit chip showing another embodiment of a memory cell array incorporating the invention.

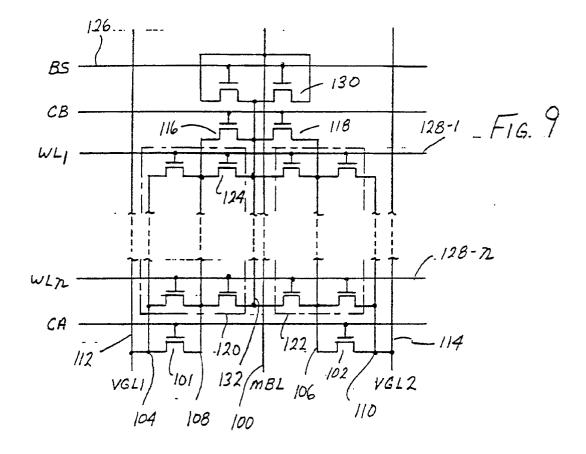

Figure 9 is a circuit diagram of the memory array shown in Figure 8.

Figure 10 is a circuit diagram of a sense amplifier incorporating the invention.

Figure 11 is a circuit diagram for a bias circuit to generate a bias voltage utilized in the sense circuit of Figure 10.

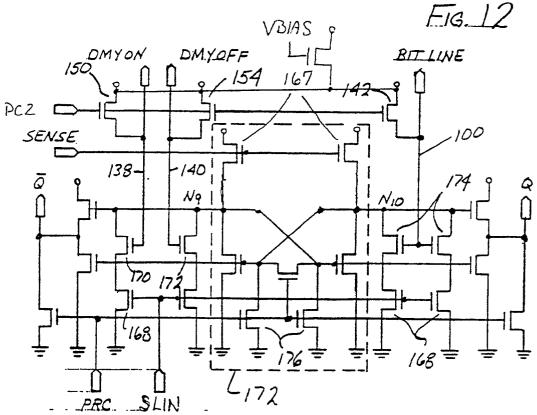

Figure 12 is a schematic diagram of another embodiment of the sense circuit incorporating the invention.

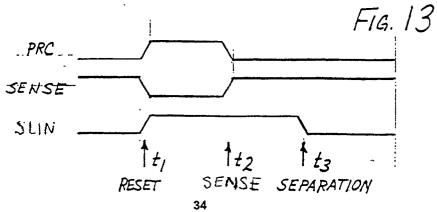

Figure 13 is a timing diagram of the sense circuit illustrated in Figure 12.

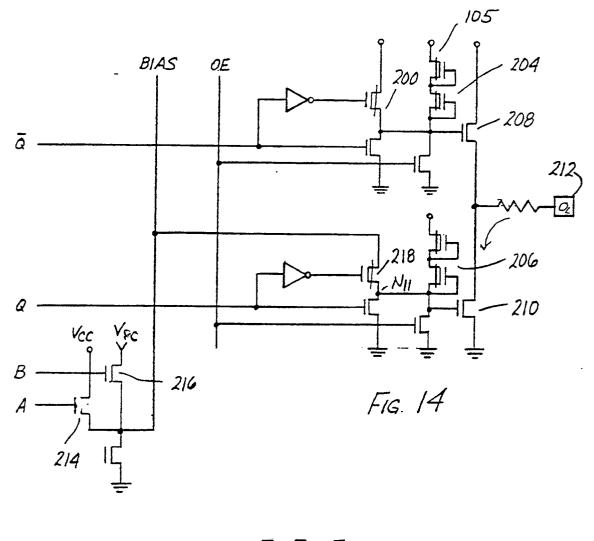

Figure 14 is a schematic diagram showing an output buffer circuit incorporating the invention.

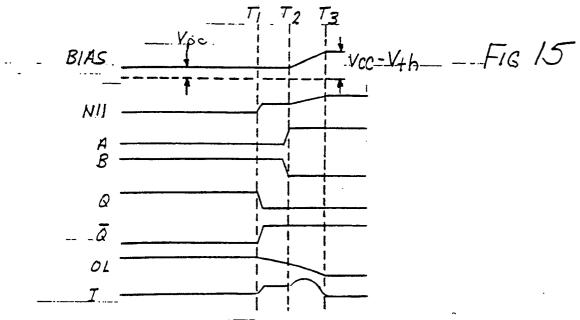

Figure 15 is a timing diagram of the circuit of Figure 14.

Figure 16 is a circuit diagram of a prior art input buffer circuit.

Figure 17 is a schematic diagram of a prior art memory cell array.

Figure 18 is a schematic diagram of another memory cell array incorporating the invention.

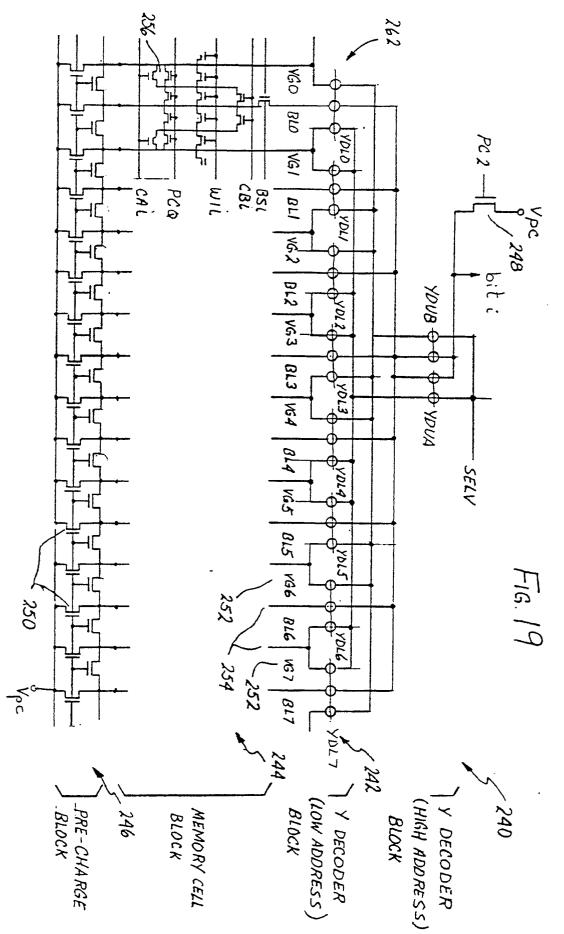

Figure 19 is a schematic diagram of a precharging scheme of a memory array incorporating the invention.

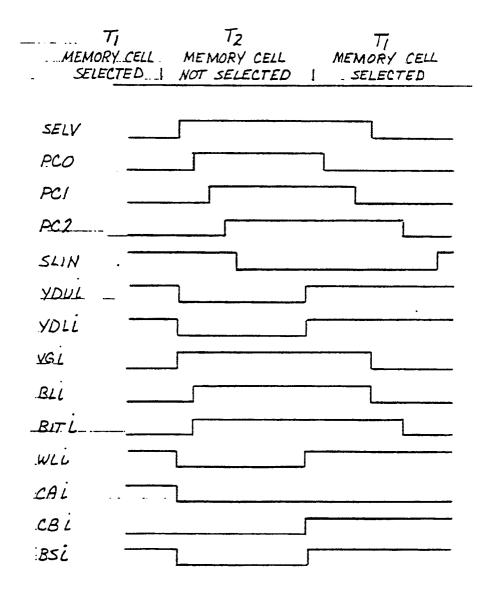

Figure 20 is a timing diagram of the circuit of Figure 19.

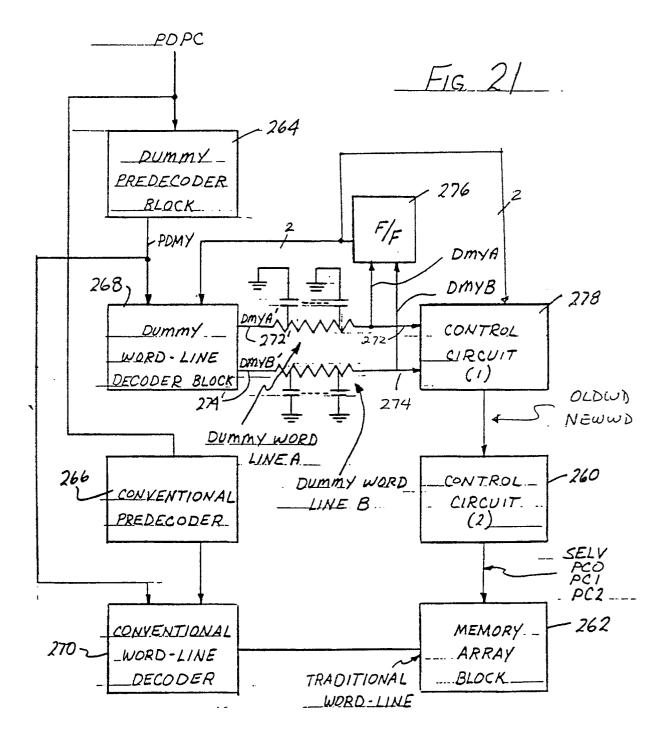

Figure 21 is a block diagram of a memory array architecture incorporating the invention.

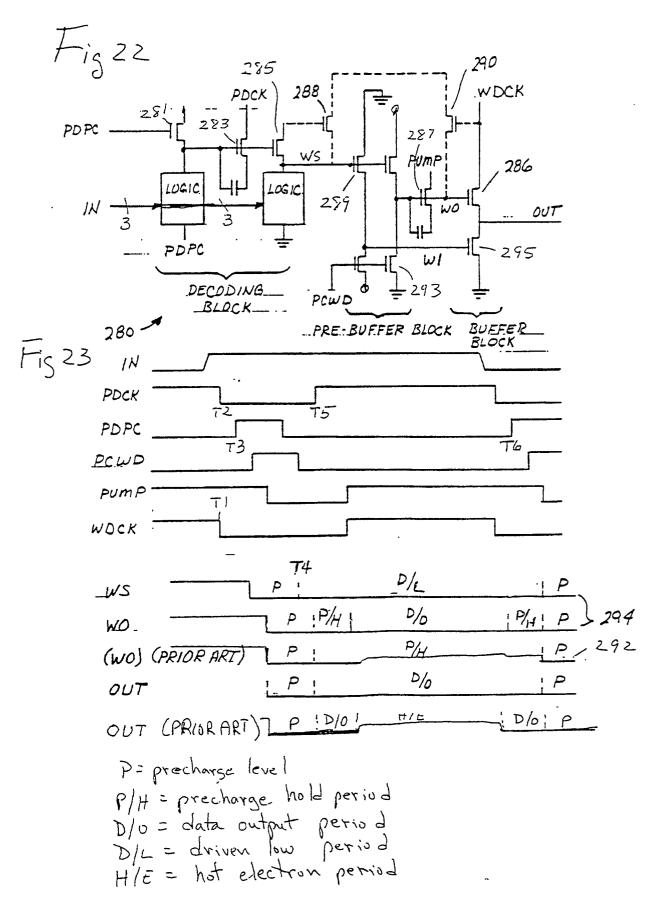

Figure 22 is a schematic diagram of a buffer circuit incorporating the invention.

Figure 23 is a timing diagram of the signals depicted in Figure 22.

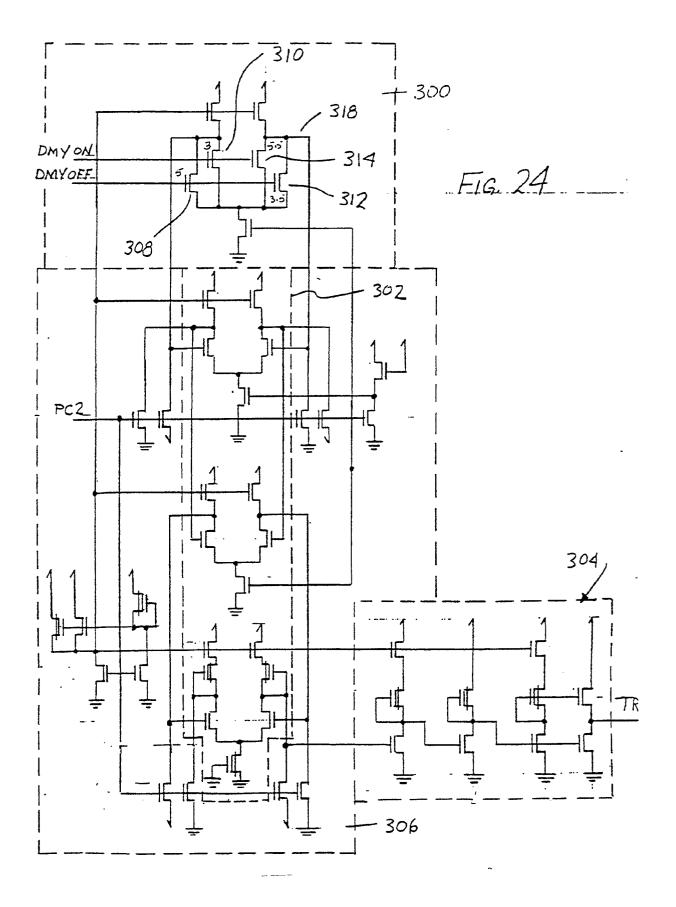

Figure 24 is a schematic diagram of a sense amplifier trigger circuit incorporating the invention.

Figure 25 is a schematic diagram of a prior art output buffer circuit.

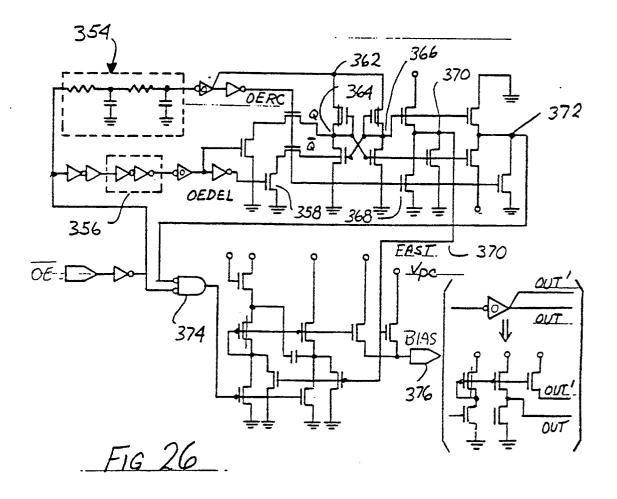

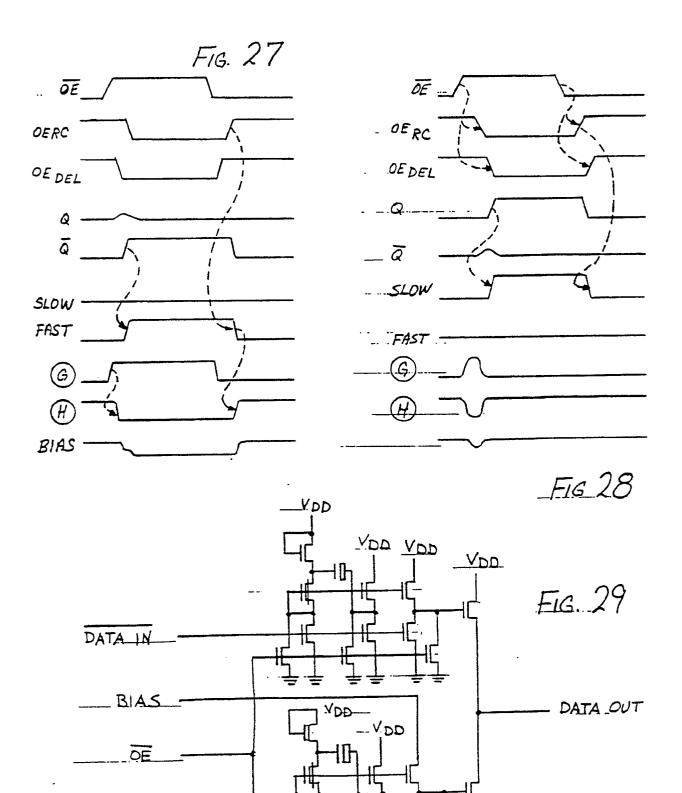

Figure 26 is a schematic diagram of a bias circuit for an output buffer circuit incorporating the invention.

Figure 27 is a timing diagram of the circuit of Figure 26 when the typical circuit delay is faster than a predetermined RC delay.

Figure 28 is a timing diagram of the circuit of Figure 26 when the substratetypical circuit delay is slower than a predetermined RC delay.

Figure 29 is a schematic diagram of an NMOS output buffer circuit incorporating the bias signal

discussed in connection with Figures 26-28.

Figure 30 is a schematic diagram of a CMOS circuit for equivalently performing the functions discussed in connection with the NMOS circuit of Figure 26.

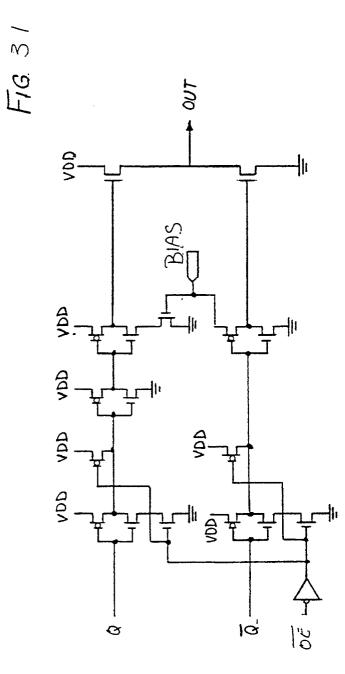

Figure 31 is a schematic diagram of a CMOS output buffer circuit for use in combination with the bias circuit of Figure 30.

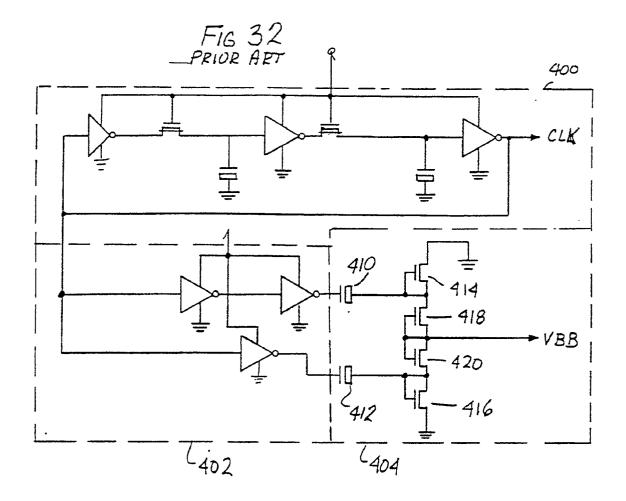

Figure 32 is a schematic diagram of a substrate charge pump of the prior art.

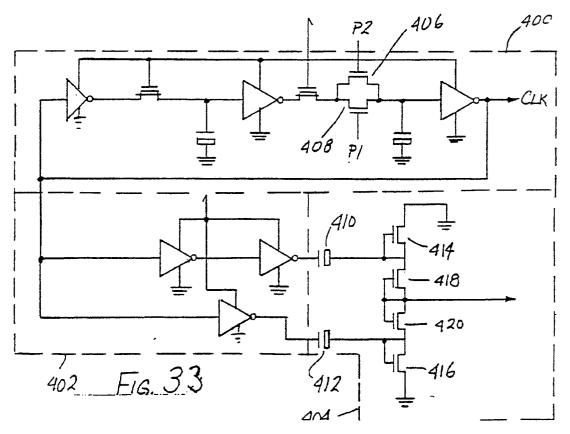

Figure 33 is a schematic diagram of a substrate charge pump incorporating the invention.

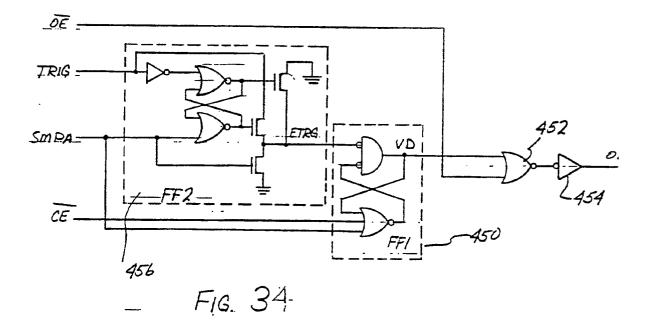

Figure 34 is a schematic diagram of an output buffer control circuit incorporating the invention.

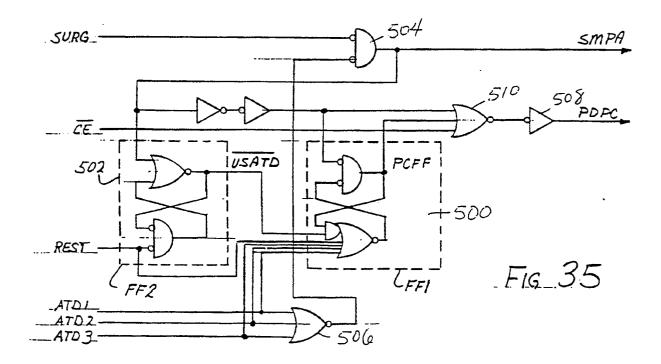

Figure 35 is a schematic diagram of an address transition detection control circuit incorporating the invention.

The invention and its various embodiments can now be better understood by turning to the following detailed description.

## Detailed Description of the Preferred Embodiments

The invention comprises a memory cell array formed by a plurality of memory cells which are divided into blocks. The memory cells are symmetrically patterned with respect to conductive lines which correct junctions between the memory cell blocks and a main bit line. The conductive lines are

perpendicular to the main bit line.

30

35

40

45

50

The invention further includes an input buffer circuit having a threshold voltage of its initial inverter stage controlled by a driving transistor.

The invention also comprises an output buffer circuit in a ROM which includes a two-stage circuit for controlling current flowing from an output pin into the ground.

The invention comprises a sense circuit including means for adjusting loads in response to the driving signal from the memory cells.

Turn now to the block diagram of Figure 1, wherein a typical read only memory, denoted by reference numeral 30, is depicted. An address input signal, AIN, is coupled to an input buffer 31 and converted from TTL level logic to the logic levels required within memory 30. An address detection circuit and latch 32 detects the transition of the address signal and produces appropriate timing signals which are coupled to timing circuitry 38 and 39.

The address signal is coupled through ATD 32 to X decoder 33 and Y decoder 34. The bit lines of a memory cell array 36 are precharged by a precharge circuit 37 controlled by timing circuit 38. A memory cell is selectively accessed within memory array 36 by X decoder 33 and a Y gate select circuit 35. Y gate select circuit 35 in turn is controlled by Y decoder 34.

10

15

20

25

30

35

The output of the accessed memory cell is coupled to sense amplifier 40. Sense amplifier 40 detects voltage levels on the precharged bit lines according to whether a 1 or a 0 is stored in the memory cell. Timing circuit 39 is coupled to and controls sense amplifier 40. The output signal from sense amplifier 40 is coupled to output buffer 41 whose output in turn is the data signal, Q and its logical complement Q-. Throughout this specification the "-" suffxed to a signal symbol designates the logical complement of the signal. Discrete control commands, such as chip enable, CE, are coupled through chip enable circuit 42 which in turn controls input buffer 31, timing circuit 39 and an output enable circuit 43. Output enable circuit 43 is also responsive to an external control signal OE, output enable. Output enable circuit 43 is connected to and controls output buffer 41.

Turn now to Figure 2, which is a schematic diagram of a first embodiment of an input buffer such as input buffer 31 of Figure 1. Only one bit is illustrated in Figure 2 and it must be understood that the circuit of Figure 2 is replicated as many times as there are input address bits. An address input bit, AIN, is coupled to a first inverter 50 whose output is coupled to a node 52. The input of a second inverter 51 is coupled to node 48. Node 48 in turn is coupled to the input of a second inverter 51. The signal from the output of inverter 51 is fed back to an NMOS transistor 53. The input to inverter 50 is also coupled to the gate of an NMOS transistor 52. Transistors 52 and 53 are in series between node 48 and ground.

When the address input signal AIN is at a low logic level, the voltage at node 48 is high and at output 49 low. The low logic output voltage is supplied back to the gate of transistor 53 which is thus held in the off or in nonconductive state.

When address signal AIN goes to a high logic level, it must exceed a threshold voltage VT1 which is determined by the characteristics of inverter 50 before the voltage at node 48 inverts. See curve 47 in Figure 3. When AIN is at a high logic level, the voltage at node 49 is also high thereby turning transistor 53 on or making it conductive. Transistor 52 is also turned on by the high input from AIN thereby pulling node 48 to ground in parallel with inverter 50.

Now when the address input, AIN, switches to a low logic level from a high logic level, the address input must be less than the threshold voltage VT2 which will be determined according to the operating characteristics of inverter 50 and transistors 52 and 53. See curve 45 in Figure 3. The threshold voltage VT2 as set by inverter 50, and transistors 52 and 53, is lower than the threshold voltage VT1 which is determined by inverter 50 alone since the driving force to inverter node 48 is increased by transistors 52 and 53.

Once the address signal AIN goes low, the threshold voltage is raised from VT2 to VT1. As a

result, node 49 is stably maintained at a lower logic level even if the address input is thereafter subjected to noise. First the threshold voltage is raised from VT2 to VT1 through reduction in the driving force applied to node 48. The amount of the shift of the threshold voltage can be insured since transistor 52 will not be turned on even if the noise caused in the LSI itself is increased notwithstanding a large transconductance g<sub>m</sub> of the driving circuitry coupled to node 48.

The performance of the circuitry of Figure 2 is summarized in the operational graph of Figure 3. The voltage level on node 48 is depicted in the vertical scale while the voltage level of the address input signal is illustrated on the horizontal scale. The threshold voltages are taken at the approximate half way points of the two logic states of node 48. What results is a hysteresis shaped curve. The arrows associated with curves 47 and 45 indicate the circuit performance which will be produced depending upon whether node 48 is being switched from high to low or from low to high as symbolically denoted by the arrows in Figure 3. For example, if node 48 is in a high state it will switch to a low state only on curve 47 characterized by the higher voltage VT1. Once node 48 is in a low state it will then switch back to the high state again only on curve 45 characterized by the lower threshold voltage VT2.

Turn now to Figure 4 wherein a second embodiment of input buffer 31 is depicted. Whereas the inverters 50 and 51 of the input buffer of Figure 2 were comprised of a PMOS and NMOS transistor, the circuit of Figure 4 is comprised only of NMOS transistors. Depletion type NMOS transistors are employed as the load transistor for inverters 54 and 55 which comprise the first and second stages of the input buffer respectively. The circuit topology of the input buffer of Figure 4 is otherwise identical to that shown in Figure 2 and the operation is analogous.

Turn now to Figure 5 which is a schematic of the address transition detector (ATD) 32 of Figure 1. In 40 the upper portion of the diagram a single bit line A0 is shown coupled to the depicted circuitry. This circuitry is replicated for each bit line as symbolically denoted by box 56. ATD circuit 32 generates internal address signals AA0 and AA0-. The buffered address bit from 45 input buffer 31 is coupled through a first inverter 60, a gated transistor 61 to a second inverter 63 to produce the address transition discrimination signal, ATD-. The address bit is also coupled directly through a gated transistor 62 to inverter 63. The signal A0 is 50 provided to the gate of transistor 64. Transistor 64 has one terminal coupled to ground and its output coupled to the input of transistor 66. Transistor 66 is controlled by a timing signal, sample address, SMPA, or by the output of delay circuit 73, which has a constant delay 55 with respect to the ATD- signal as determined by inverter 72 and delay circuit 73. A0- from inverter 60 is similarly provided to the gate of transistor 65.

10

15

20

Transistor 65 in turn is coupled in series with transistor 67 whose gate is also controlled by the output of delay circuit 73. The output of transistors 66 and 67 are provided to the inputs of a flip-flop comprised of transistors 68-71. Transistors 68 and 70 are depletion load transistors with corresponding series driving transistors 69 and 71 being coupled to ground. The internal address signals AA0 and AA0- then are provided respectively to the gates of transistors 61 and 62 to gate through a change of the address bit A0 or A0- as ATD-.

Consider now the operation of the circuit shown in Figure 5 as summarized by the timing diagram of Figure 6. Assume that the address A0 is at a low logic level. AA0 will be low, AA0- will be high, ATD- will be high due to the circuit connections in Figure 5 and the output of delay circuit 73, which is an internally generated timing signal, is low and as shown by the signal relationships of Figure 6. When address A0 goes high at a transition point T1, shown in Figure 6, signal ATD- goes low since transistor 62 is in a conductive state. The internal address signals AA0 and AA0- do not change state at this time as shown in Figure 6 because the output of delay circuit 73 is still held low leaving the blocking transistors 66, 67 nonconductive.

After a lapse of a delay time D2 following the transition of ATD- as shown in Figure 6, the output of delay circuit 73 goes high at time T2 as determined by delay circuit 73. Blocking transistors 66 and 67 will now be rendered conductive and the flip-flop 68-71 will change state. This occurs after a switching delay time of D3 after T2. Transistor 61 will now be turned on and transistor 62 turned off. This now causes ATD-to go high after a delay D4 at time T3 as illustrated in Figure 6. After a further delay time of D5 the change of state of ATD- is coupled through inverter 72 and delay circuit 73 and the output of delay circuit 73 again goes low at time T4. This is then the operation of a single change in logic level of an address bit.

Even if the difference in address timing between the first address bit to be changed, assumed here to be A0, and the last address bit to be changed, assumed to be AN, is as large as the time interval TAS shown in Figure 6, internal address signals AA0 and AAN will nevertheless transition at the same time, namely between T2 and T3 in synchronization with the leading edge of the output of delay circuit 73. Synchronization occurs as long as delay circuit 73 is set so that the delay time D2 is at least as great as the difference between TAS and D1. It should also be specifically understood that the NMOS circuit structure of Figure 5 can be replaced by an equivalent CMOS structure without departing from the spirit and the scope of the invention.

As a result of an ATD circuit of this design, the address state of a preceding cycle is maintained during the time period when the address signal is indefinite. The new address state is established only after the address is defined and therefore unnecessary power consumption caused by unnecessary switching of internal circuitry is avoided.

Now having considered the invention as embodied in the input buffer 31 and ATD circuit 32 of Figure 1, consider the improvement of memory cell array 36 as depicted in greater detail in the schematic of Figure 7. A portion of memory cell array 36 is illustrated in Figure 7 showing a plurality of bit lines 86-1 through 86-5 which are shown as vertical lines in Figure 7 which are formed from diffusion layers and

word lines 88-1 through 88-n which are shown as horizontal lines in Figure 7 and formed of silicide. The memory cells are comprised of a plurality of memory cell transistors 87.

In the illustrated embodiment a block select transistor 80 shown in the upper portion of the schematic and block select transistor 85 is shown in the lower portion of the schematic, which are connected in series with a center bit line 86-3. NMOS column select transistors 81-84 are coupled between adjacent bit lines and gated by a column A or column B select signal CA and CB, respectively. For example,

25 column select NMOS transistor 81 is coupled between bit lines 86-1 and 86-2. Column select transistor 83 is coupled between bit line 86-2 and 86-3 and so forth. Therefore, it can be readily seen from the diagram that column select signal CA will short out all the set of the select signal CA will short out all

the memory cells in the first and third columns, while column select signal CB will short out all the memory cells in the second and fourth columns. The center bit line, 86-3, which is provided with block select transistors 80 and 85, is connected to an aluminum

line which in turn is connected to the input of a sense amplifier 40.

Each of the bit lines 86-1 through 86-5 are selectively precharged through a precharge circuit 90 through NMOS transistors 91 and 92 and selectively grounded through NMOS transistors 93 and 94. Transistors 91 and 94 are driven by a select signal S, while the complement S- drives discharge transistors 92 and 93.

Consider now the operation of the memory array

shown in Figure 7. In particular, focus your attention upon memory cell 87a shown in the second column near the center of the schematic. A block select signal, BS, is coupled to the gates of transistors 80 and 85 for block selection. This block of memory cells

can now be connected through center bit line 86-3 to sense amplifier 40 as described below.

The column select signal, CA, then goes high turning on column select transistors 81 and 82 to short out the first and third columns of the memory array and hence select for readout from the second arid fourth columns. The column select signal, CB, is maintained at a low logic level.

Word line 88-n then goes high, thereby selecting

55

10

15

20

25

30

35

40

45

50

each of the memory cells in the nth row, or in this example the memory cell 87a in the second column and 87b in the fourth column. In order to read out the contents of memory cell 87a, bit line 86-1 is pulled to ground by controller transistor 93 and a precharge applied to bit line 86-5 through controller transistor 92. This is accomplished by forcing the select signal S to go low and its complement S- high. Sense amplifier 40, whose input is precharged, is a low level seeking amplifier and therefore only reads out the contents of memory cell 87a. Comparison of the signal path of the memory array of Figure 7 to that of Figure 17 illustrates that in the worst case, the transmission of data signal along the diffusion or bit lines is half as long in Figure 7 for arrays of the same size.

An alternative embodiment of the memory cell array is shown in the plan view layout of Figure 8 and in the schematic of Figure 9. As shown in schematic Figure 9, main bit line 100 is coupled through NMOS transistors 130 to a center bit line 132. A plurality of pairs of memory cells 124 are then coupled between center bit line 132 and a first virtual ground 112 and a second virtual ground 114. Two memory cells 124 coupled in series with each other form a pair and the pairs coupled in parallel between center line 132 to virtual grounds 112 and 114. The gates of memory cells 124 are coupled to word lines 128-1 through 128-N. Column select NMOS transistors 116 and 118 are coupled in parallel with N memory cells on each side of center bit line 132. Column select NMOS transistors 101 and 102 are coupled in parallel with in N memory cells which are corrected to virtual ground lines 112 and 114.

Referring to Figure 9, a column select signal, CA is converted to a logic high level in order to select memory cells (second and third columns) immediately adjacent to a main bit line 100 shown in the middle of the schematic Figure 9. Column select signal, CA turns on transistors 101 and 102 to short lines 104 and 106 to lines 108 and 110, respectively. Lines 104 and 110 in turn are coupled to virtual ground lines 112 and 114, respectively, VGL1 and VGL2.

Meanwhile, column select signal, CB, shorts lines 106 and 108 to main bit line 100 through transistors 116 and 118, respectively. In other words, signal CA will select the second and third column while column select signal, CB, will select the first and fourth columns, the columns being ordered and numbered from left to right in the array of Figure 9.

All left block cells, denoted by dotted outline 120 are selected by converting virtual ground line 112 to a logic low level and setting virtual ground line 114 to the same potential as main bit line 100. In such an instance, the cells within block 120 as opposed to the symmetrically disposed block of memory cells 122 could be read out while those in block 122 could not.

In order to select, for example, cell 124, bit select signal, BS, on bit select line 126 goes to a logical high

selecting the block shown in Figure 9, namely blocks 120 and 122. Signal BS on line 126 is coupled to the gates of transistors 130 which in turn selectively couple main bit line 100 to a center bit line of the array 132. Column select signal, CA to a logical high, and column select line, CB, to a logical low thereby selecting the second and third columns. Virtual ground line 112 goes to a logical low, and virtual ground line 114 to the level of main bit line 100 thereby selecting the second row. Word line 128-1 to a logical high with each remaining word lines 128-2 to 128-N to a logical low thereby reading cell 124.

Referring specifically to Figure 8, word lines 128-1 to 128-N and lines for supplying the column select signals, CA, CB and BS, are polysilicon wires. Bit lines 104, 108, 132, 106 and 110 are N diffusion wires while main bit line 100 and virtual ground lines 112 and 114 are metal wires of aluminum. The metallic contacts are denoted by the x-ed squares denoted by reference number 134. Regions 138 denote ion-implanted regions. Threshold voltages in ion-implanted regions 138 exceeds the supply voltage so that NMOS transistors disposed in regions 138 are not turned on even if the gate voltage goes to a logic high.

In each of the embodiments shown in both the embodiments of Figures 7 and 9, the metal contacts 134 connecting the diffusion wiring to main bit line 100, and metal contacts 134 connecting the diffusion wiring to virtual ground lines 112, 114 are positioned at opposite ends of the memory cell blocks as best depicted in Figure 8. Therefore, the resistance of the diffusion wiring elements remains constant regardless of the position of the selected memory cell because the resistance corresponds to the distance between the metal contacts 134. Therefore, as compared to the conventional prior art memory cell array as shown in Figure 17, wherein the resistance is twice the distance between the contacts, the number of memory cells disposed within any one block can be doubled in the present embodiment with the same diffusion resistance. This allows the degree of integration to be increased relative to the resistance limitations imposed by prior art structures.

Since the contacts between main bit line 100 and memory cell blocks are positioned on the ends of the memory cell block as shown in Figure 8. The memory layout can be designed so that the memory cell blocks are mirror symmetrical about line 135 with respect to transverse or horizontal lines (not shown) connecting contacts 134. As a result, the number of contacts can be reduced by fifty percent as compared to conventional layout.

As a further consequence the capacitance and leakage current parasitic to main bit line 100 can also be reduced by fifty percent, thereby increasing switching speeds.

Another embodiment of the memory array of the invention is depicted in Figure 18. Consider, for

example, access to a memory transistor at the second column and nth row . Selection signal, CA, goes to a logical high. Thus, transistors 220 at each end of the block are turned on and bit lines 222 and 224 are shorted together. Transistors 226 at each end of the block are also driven on by the select signal, CA, so that bit lines 4 and 5 are shorted together. The first and fourth columns, for example, are shorted together at each end of the array. Transistor 228 is similarly turned on and bit line 231, and middle bit line 240 precharged by precharge circuit 230.

Now the nth word line, WL<sub>n</sub>, is pulled high, pulling the gates of transistors 232 and 234 high. At this time if virtual ground decoder 236 is set to select bit line 222 by selectively coupling it to ground while maintaining bit line 238 high, the contents of memory cell 232 can be read through center bit line 240 by a bit line decoder 233. Bit line decoder 233 will select one of many block inputs on lines similar to middle bit line 240 from other identical memory blocks to that shown in Figure 18.

As can be readily understood by viewing the schematic of Figure 18, the architecture of the memory layout allows selection transistors 220-226 to be disposed near the highest and lowest rows of the memory block and thus forms a signal by-path through them. Therefore, the transmission path in the memory array of the contents of the selected memory cell does not travel twice the length of the diffusion layer lines or bit lines as in the previous technology. A higher speed array and a larger number of memory transistors per block is therefore achievable.

The invention also includes a methodology which utilizes the generation of dynamically modeled clock signals to manipulate bit lines in a large scale integrated memory dynamically. Turn, for example, to the block diagram of Figure 21 and the associated timing diagram of Figure 20. A dummy decoder generator and dummy word line is used in addition to the decoder and word lines conventionally employed in read-only memories. A control block outputs a signal based on a signal from the dummy generator. The generated signal is used as a clock signal for the memory array to run the memory cell at a high speed with low power consumption.

Control circuit 260 generates the signals SELV (select voltage), PCO, PC1 and PC2, described in connection with Figures 19 and 20 and as shown in Figure 22. These signals are coupled and employed in memory block array 262 of Figure 19 as therein described.