US 20140138850A1

## (19) United States

# (12) Patent Application Publication Takayama

# (10) Pub. No.: US 2014/0138850 A1

### (43) **Pub. Date:** May 22, 2014

#### (54) SEMICONDUCTOR POWER MODULE, PRODUCTION METHOD OF SEMICONDUCTOR POWER MODULE AND CIRCUIT BOARD

### (75) Inventor: Yasushi Takayama, Aichi-ken (JP)

#### (73) Assignee: NGK SPARK PLUG CO., LTD., Nagoya-shi, Aichi (JP)

(21) Appl. No.: 14/234,323

(22) PCT Filed: Jul. 31, 2012

(86) PCT No.: **PCT/JP2012/004865**

§ 371 (c)(1),

(2), (4) Date: Jan. 22, 2014

#### (30) Foreign Application Priority Data

| Aug. 1, 2011  | (JP) | 2011-168295 |

|---------------|------|-------------|

| Aug. 1, 2011  | (JP) | 2011-168296 |

| Mar. 19, 2012 | (JP) | 2012-061859 |

#### **Publication Classification**

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | H01L 23/36 | (2006.01) |

|      | H01L 23/48 | (2006.01) |

|      | H01L 21/50 | (2006.01) |

|      | H05K 7/20  | (2006.01) |

(52) U.S. Cl.

USPC ...... **257/774**; 361/736; 438/455

#### (57) ABSTRACT

A semiconductor power module (10) includes a ceramic multilayer substrate (100), a bonding layer (110), a diffusion layer (120) and a semiconductor device (130). The bonding layer is placed on a first surface (105) of the ceramic multilayer substrate and is provided as a planar thin film layer including conductive bonding parts (111) configured to electrically connect the semiconductor device with the ceramic multilayer substrate and insulating bonding parts (112) configured to isolate the semiconductor device from the ceramic multilayer substrate. Also disclosed is a production method of the semiconductor power module.

Fig.1

Fig.2

Fig.3

Fig.4

Fig.5

Fig.6

# APPLICATION OF HEAT AND PRESSURE

Fig.7

т С С

Fig.9

Fig.10

Fig.11

<u>1010</u>

Fig.14

Fig.15

Fig.16

Fig.17

Fig. 18

Fig.19

Fig.20

Fig.21

r D V

#### SEMICONDUCTOR POWER MODULE, PRODUCTION METHOD OF SEMICONDUCTOR POWER MODULE AND CIRCUIT BOARD

#### TECHNICAL FIELD

[0001] The present invention relates to a semiconductor power module having a semiconductor device mounted on a circuit board, a production method of a semiconductor power module and a circuit board.

#### BACKGROUND ART

[0002] With recent advances of small-size, low-profile and high-density mounting for power module packaging, as the alternative of the conventional mounting scheme using wire bonding, a mounting scheme that uses a ceramic multilayer substrate and makes flip chip connection of a semiconductor device has been proposed for production of semiconductor modules. The flip chip connection is a bonding method that arranges conductive projections called bumps on a semiconductor device, adjusts the bumps to the location where the semiconductor device is to be mounted on the ceramic multilayer substrate and directly bonds the semiconductor device to the ceramic multilayer substrate. This mounting scheme reduces the area required for mounting the semiconductor device by about 20 to 30% and has contribution to the high-density mounting.

[0003] In some proposed semiconductor modules by such flip chip mounting scheme, as the alternative of an organic material conventionally used as the sealing material, an inorganic material is filled in the gaps of the bumps between the ceramic multilayer substrate and the semiconductor device (for example, Patent Literature 1).

#### CITATION LIST

#### Patent Literature

[0004] PTL 1: JP 2004-253579A

[0005] PTL 2: JP 2006-066582A

[0006] PTL 3: JP 2010-287869A

[0007] PTL 4: JP 2009-170930A

#### SUMMARY OF INVENTION

#### Technical Problem

[0008] In the semiconductor power modules with the advancement of the higher-density mounting by the flip chip mounting scheme, reduction of the heat radiation area results in deteriorating the heat radiation performance by the size effect. It is accordingly required to further improve the heat diffusion performance from the semiconductor device to the ceramic multilayer substrate. In the conventional semiconductor power modules, however, there are problems that voids are produced between the ceramic multilayer substrate and the semiconductor device due to the occurrence of gas bubbles in the process of filling the sealing material or the occurrence of cracks at the junction caused by a thermal stress during use and that the air enters such voids. Accordingly, the conventional semiconductor power modules have problems, such as degradation of the heat radiation performance of the semiconductor device due to reduction of the heat diffusion performance from the semiconductor device to the ceramic multilayer substrate, reduction of the bond strength between the ceramic multilayer substrate and the semiconductor device and deterioration of the reliability. The conventional semiconductor power modules also have problems, such as poor electrical connection caused by manufacturing variation among the structural components, which may be attributed to little warpage of the ceramic multilayer substrate. It is accordingly desired to provide a module configuration and a production process that are unlikely to cause deterioration of the reliability.

#### Solution to Problem

[0009] In order to solve at least part of the problems described above, the invention provides aspects and embodiments described below.

[0010] (1) In one aspect of the present invention, there is provided a semiconductor power module. The semiconductor power module comprises: a multilayer substrate having a via and an interconnecting pattern formed thereon; a semiconductor device placed on a first surface side of the multilayer substrate; and a bonding layer formed on the first surface of the multilayer substrate for bonding the multilayer substrate to the semiconductor device, and wherein the bonding layer includes: a planar conductive bonding part arranged at a first region corresponding to the via and configured to have a conductive projection formed on the semiconductor device and a conductive connector arranged to provide electrical continuity between the projection and the multilayer substrate; and a planar insulating bonding part arranged at a second region different from the first region and made of an inorganic material as a main constituent. In the semiconductor power module according to this aspect, the bonding layer is made planar. This configuration suppresses the occurrence of voids between the multilayer substrate and the semiconductor device when the multilayer substrate is bonded to the semiconductor device. This accordingly improves the heat diffusion performance from the semiconductor devices to the multilayer substrate and the bond strength between the multilaver substrate and the semiconductor device.

[0011] (2) In the semiconductor power module according to above described aspect, the multilayer substrate and the bonding layer may be bonded by diffusion bonding, and the semiconductor device and the bonding layer may be bonded by diffusion bonding, and the semiconductor power module may further comprise: a diffusion layer formed between the multilayer substrate and the bonding layer and between the semiconductor device and the bonding layer during the diffusion bonding. In the semiconductor power module according to this aspect, the diffusion layer is formed by diffusion of atoms occurring at the interface between the multilayer substrate and the bonding layer and at the interface between the bonding layer and the semiconductor device during diffusion bonding between the multilayer substrate and the bonding layer and between the bonding layer and the semiconductor device. This improves the bond strength between the multilayer substrate and the bonding layer and the bond strength between the bonding layer and the semiconductor device.

[0012] (3) In the semiconductor power module according to above described aspect, a first bonding start temperature which is a bonding start temperature of a material constituting the conductive bonding part may be lower than a second bonding start temperature which is a bonding start temperature of a material constituting the insulating bonding part. In the semiconductor power module according to this aspect, the conductive bonding part is bonded, prior to the insulating

bonding part. Accordingly, in the state that the conductive connector is bonded to the projection of the semiconductor device and that the conductive bonding part is bonded to the interconnecting substrate, i.e., in the state that there is no void between the conductive connector and the projection of the semiconductor device and between the conductive bonding part and the interconnecting substrate, the insulating bonding part starts softening and deforming, so as to be bonded to the semiconductor device and to the interconnecting substrate. This configuration suppresses deterioration of the conductive performance of the conductive bonding part due to invasion of the material constituting the insulating bonding part between the conductive connector and an electrode pad, i.e., mixing of the material into the conductive bonding part.

[0013] (4) In the semiconductor power module according to above described aspect, the first bonding start temperature may be equal to or higher than a sintering start temperature at which at least part of the material constituting the conductive bonding part starts a sintering reaction, and the second bonding start temperature may be equal to or higher than a sintering start temperature at which at least part of the material constituting the insulating bonding part starts a sintering reaction. In the semiconductor power module according to this aspect, the first bonding start temperature is equal to or higher than the temperature at which at least part of the material constituting the conductive bonding part starts the sintering reaction. The second bonding start temperature is equal to or higher than the temperature at which at least part of the material constituting the insulating bonding part starts the sintering reaction. Accordingly this enables each of the conductive bonding part and the insulating bonding part to be bonded to another member without being heating to the melting point. In another example, the first bonding start temperature may be a melting start temperature of the material constituting the conductive bonding part, and the second bonding start temperature may be a melting start temperature of the material constituting the insulating bonding part. This ensures the conductive bonding part and the insulating bonding part to be effectively melted, thus improving the bond strength between each of the conductive bonding part and the insulating bonding part with another member.

[0014] (5) In one aspect of the present invention, there is provided a production method of a semiconductor power module. The production method of a semiconductor power module comprises: a substrate manufacturing step that manufactures a multilayer substrate having a via and an interconnecting pattern; a first placement step that places a bonding part on a first surface of the multilayer substrate, wherein the bonding part has a planar conductive connector for providing electrical continuity between the interconnecting pattern and a semiconductor device at a first region corresponding to the via and a planar insulating bonding part at a second region different from the first region; a second placement step that places the semiconductor device on the bonding part such as to provide electrical continuity between a conductive projection formed on the semiconductor device and the conductive connector; and a bonding step that bonds the multilayer substrate, the bonding part and the semiconductor device by application of heat and pressure, so as to make diffusion bonding between the multilayer substrate and the bonding part and between the bonding part and the semiconductor device. In the production method of the semiconductor power module according to this aspect, the planar bonding layer for bonding the multilayer substrate to the semiconductor device is formed by the bonding part and the projection between the multilayer substrate and the semiconductor device. This configuration suppresses the occurrence of voids between the multilayer substrate and the semiconductor device. Accordingly this improves the heat diffusion performance from the semiconductor device to the multilayer substrate and the bond strength between the multilayer substrate and the semiconductor device.

[0015] (6) In the production method of a semiconductor power module according to above described aspect, a first bonding start temperature may be a temperature at which a material constituting the conductive connector starts bonding to the semiconductor device, and a second bonding start temperature may be a temperature at which a material constituting the insulating bonding part starts bonding to the multilayer substrate and to the semiconductor device and which is higher than the first bonding start temperature, wherein the bonding step may include: a step of bonding the multilayer substrate, the bonding part and the semiconductor device by application of pressure and heat at the first bonding start temperature, so as to bond the conductive connector to the projection of the semiconductor device; and a step of bonding the multilayer substrate, the bonding part and the semiconductor device by application of pressure and heat at the second bonding start temperature, so as to bond the multilayer substrate to the bonding part and bond the bonding part to the semiconductor device, after the conductive connector is bonded to the projection of the semiconductor device. In the production method of the semiconductor power module according to this aspect, the conductive bonding part is bonded, prior to the insulating bonding part. Accordingly, in the state that the conductive connector is bonded to the projection of the semiconductor device and that the conductive connector is bonded to the interconnecting substrate, i.e., in the state that there is no void between the conductive connector and the projection of the semiconductor device and between the conductive connector and the interconnecting substrate, the insulating bonding part starts softening and deforming, so as to be bonded to the semiconductor device and to the interconnecting substrate. This configuration suppresses deterioration of the conductive performance of the conductive connector due to invasion of the material constituting the insulating bonding part between the conductive connector and the projection, i.e., mixing of the material into the conductive connector.

[0016] (7) In the production method of a semiconductor power module according to above described aspect, the first bonding start temperature may be equal to or higher than a sintering start temperature at which at least part of the material constituting the conductive connector starts a sintering reaction, and the second bonding start temperature may be equal to or higher than a sintering start temperature at which at least part of the material constituting the insulating bonding part starts a sintering reaction. In the production method of the semiconductor power module according to this aspect, the first bonding start temperature is equal to or higher than the temperature at which at least part of the material constituting the conductive connector starts the sintering reaction. The second bonding start temperature is equal to or higher than the temperature at which at least part of the material constituting the insulating bonding part starts the sintering reaction. Accordingly this enables each of the conductive connector and the insulating bonding part to be bonded to another member without being heating to the melting point. In another example, the first bonding start temperature may be a melting start temperature of the material constituting the conductive connector, and the second bonding start temperature may be a melting start temperature of the material constituting the insulating bonding part. This ensures the conductive connector and the insulating bonding part to be effectively melted, thus improving the bond strength between each of the conductive connector and the insulating bonding part with another member.

[0017] (8) In the production method of a semiconductor power module according to above described aspect, a first bonding start temperature may be a temperature at which a material constituting the conductive connector starts bonding to the semiconductor device, and a second bonding start temperature may be a temperature at which a material constituting the insulating bonding part starts bonding to the multilayer substrate and to the semiconductor device and which is higher than the first bonding start temperature, wherein the bonding step may perform the application of heat, based on a temperature profile which is set to maintain the first bonding start temperature for a predetermined time and subsequently maintain the second bonding start temperature for a predetermined time. In the production method of the semiconductor power module according to this aspect, the bonding part, the interconnecting substrate and the semiconductor device are bonded, based on the temperature profile having a stepwise temperature change. Accordingly, this enables diffusion bonding to be made with a stepwise temperature change by the simple configuration, thus improving the production effi-

[0018] (9) In the production method of a semiconductor power module according to above described aspect, the first placement step may include: a step of placing the insulating bonding part having an opening portion at the first region on the first surface; and a step of placing the conductive connector made thinner than the insulating bonding part in the opening portion, and the second placement step may include: a step of placing the semiconductor device on the bonding part such that the projection is fit in the opening portion, so as to provide electrical continuity between the projection of the semiconductor device and the conductive connector, and wherein d3>d2-d1 may be satisfied where d1 represents a thickness of the conductive connector, d2 represents a thickness of the insulating bonding part and d3 represents a height of the projection. In the production method of the semiconductor power module according to this aspect, the conductive connector and the insulating bonding part are formed to satisfy d3>d2-d1 where d1 represents the thickness of the conductive connector, d2 represents the thickness of the insulating bonding part and d3 represents the thickness of the projection. This accordingly enables the semiconductor device to be placed in the recess in the state that good electrical connection is ensured between the projection and the conductive connector. In this state, the semiconductor device is off the surface of the bonding layer when the semiconductor device is placed on the bonding layer. The bonding process, however, applies heat to melt the projection and applies pressure in this molten state, so that the semiconductor device is bonded to the bonding layer via a void-free plane.

[0019] (10) In the production method of a semiconductor power module according to above described aspect, the step of placing the insulating bonding part may arrange the insulating bonding part to be in such a shape that narrows from an end bonded to the semiconductor device toward an end

bonded to the multilayer substrate. In the production method of the semiconductor power module according to this aspect, the insulating bonding part is formed in such a shape that narrows from the semiconductor device side toward the multilayer substrate side. This configuration provides the wider contact area between the semiconductor device and the insulating bonding part, compared with the contact area between the semiconductor device and the insulating bonding part that is formed in an approximately columnar shape. This accordingly improves the heat diffusion performance from the semiconductor device to the multilayer substrate, while ensuring the bond strength and the insulation performance between the multilayer substrate and the semiconductor device.

[0020] (11) In the production method of a semiconductor power module according to above described aspect, the step of placing the insulating bonding part may arrange the insulating bonding part to be in a tapered shape. In the production method of the semiconductor power module according to this aspect, the insulating bonding part is formed in a tapered shape. This configuration enables the insulating bonding part to be readily formed in such a shape that narrows from the semiconductor device side toward the multilayer substrate side.

[0021] (12) In one aspect of the present invention, there is provided a circuit board. The circuit board comprises: a multilayer substrate having a via and an interconnecting pattern formed thereon; and a bonding layer formed on a first surface of the multilayer substrate for bonding the multilayer substrate to a semiconductor device, wherein the bonding layer includes: a conductive connector arranged at a first region corresponding to the via and configured to provide electrical continuity with the interconnecting pattern and with the semiconductor device, wherein at least a first surface-side surface of the conductive connector is made planar; and an insulating bonding part arranged at a second region different from the first region and made of an inorganic material as a main constituent, wherein at least a first surface-side surface of the insulating bonding part is made planar. In the circuit board according to this aspect, the semiconductor device and the multilayer substrate are bonded via a plane. This suppresses the occurrence of voids between the multilayer substrate and the semiconductor device. Accordingly this improves the heat diffusion performance from the semiconductor device to the multilayer substrate and the bond strength between the multilayer substrate and the semiconductor device.

[0022] (13) In the circuit board according to above described aspect, the conductive connector may be made thinner than the insulating bonding part, and the bonding layer may have a recess formed by the insulating bonding part and the conductive connector, and wherein before a conductive projection formed on the semiconductor device is fit in the recess, d3>d2-d1 may be satisfied where d1 represents a thickness of the conductive connector, d2 represents a thickness of the insulating bonding part and d3 represents a height of the projection. In the circuit board according to this aspect, with respect to fitting of the projection into the recess, the conductive connector and the insulating bonding part are formed to satisfy d3>d2-d1 where d1 represents the thickness of the conductive connector, d2 represents the thickness of the insulating bonding part and d3 represents the thickness of the projection. This configuration ensures the good electrical connection between the projection and the conductive connector when the semiconductor device is set in the recesses.

[0023] (14) In the circuit board according to above described aspect, the insulating bonding part may be formed in such a shape that narrows from an end bonded to the semiconductor device toward an end bonded to the multilayer substrate. In the circuit board according to this aspect, the insulating bonding part is formed in such a shape that narrows from the semiconductor device side toward the multilayer substrate side. This configuration provides the wider contact area between the semiconductor device and the insulating bonding part, compared with the contact area between the semiconductor device and the insulating bonding part that is formed in an approximately columnar shape. This accordingly improves the heat diffusion performance from the semiconductor device to the multilayer substrate, while ensuring the bond strength and the insulation performance between the multilayer substrate and the semiconductor device.

[0024] (15) In the circuit board according to above described aspect, the insulating bonding part may be formed in a tapered shape. In the circuit board according to this aspect, the insulating bonding part is formed in a tapered shape. This configuration enables the insulating bonding part to be readily formed in such a shape that narrows from the semiconductor device side toward the multilayer substrate side.

[0025] The plurality of structural components included in each aspect of the invention described above are not all essential, but some structural components among the plurality of structural components may be appropriately changed, omitted or replaced with other structural components or part of the limitations may be deleted, in order to solve part or all of the problems described above or in order to achieve part or all of the advantageous effects described herein. In order to solve part or all of the problems described above or in order to achieve part or all of the advantageous effects described herein, part or all of the technical features included in one aspect of the invention described above may be combined with part or all of the technical features included in another aspect of the invention described above to provide still another independent aspect of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

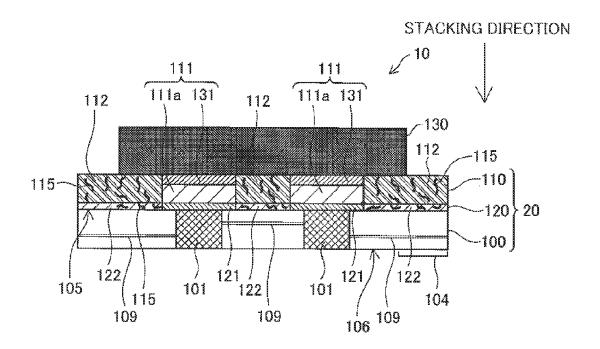

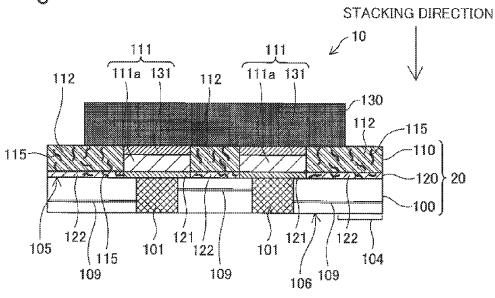

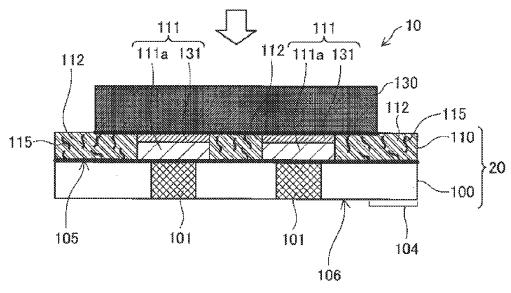

[0026] FIG. 1 is a cross sectional diagram illustrating the schematic configuration of a semiconductor power module 10 according to a first embodiment;

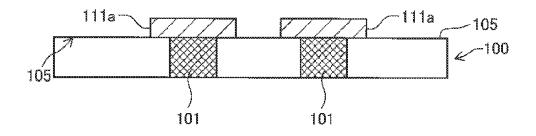

[0027] FIG. 2 is a diagram illustrating a circuit board 20 according to the first embodiment;

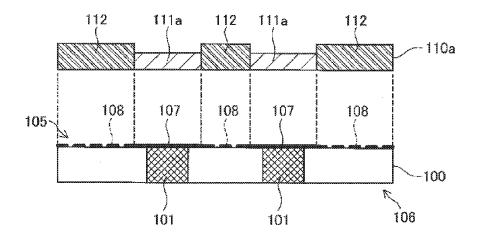

[0028] FIG. 3 is a flowchart showing a production method of the semiconductor power module 10 according to the first embodiment;

[0029] FIG. 4 is a diagram illustrating the process of arranging the conductive connectors 111a at step S12;

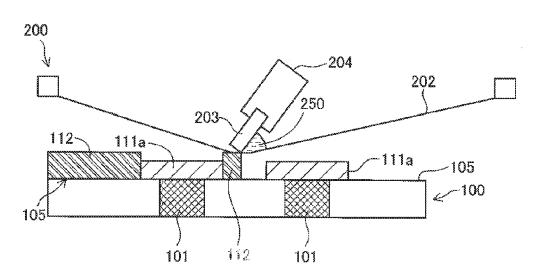

[0030] FIG. 5 is a diagram illustrating screen printing of the insulating bonding parts 112 at step S14;

[0031] FIG. 6 is a diagram illustrating the bonding process of the semiconductor power module 10 according to the first embodiment:

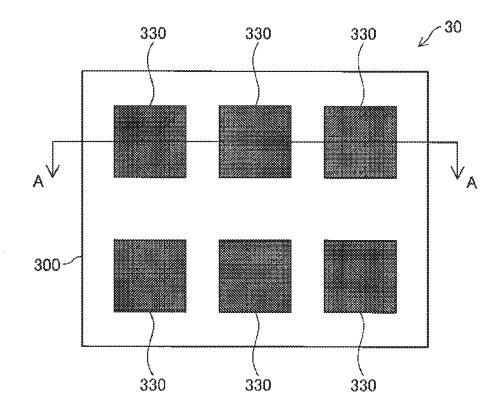

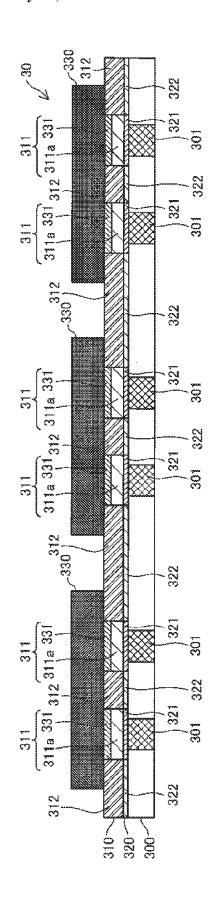

[0032] FIG. 7 is a plan view illustrating a semiconductor power module 30 according to the second embodiment;

[0033] FIG. 8 is a cross sectional view illustrating the semiconductor power module 30 of the second embodiment;

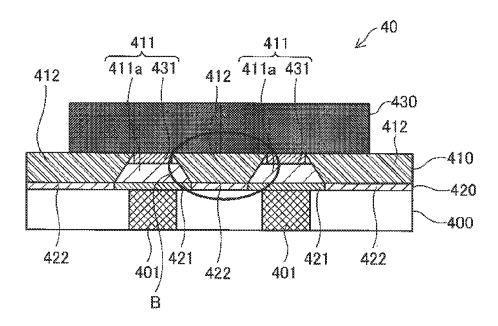

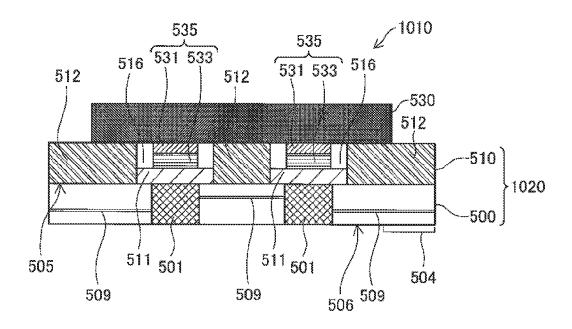

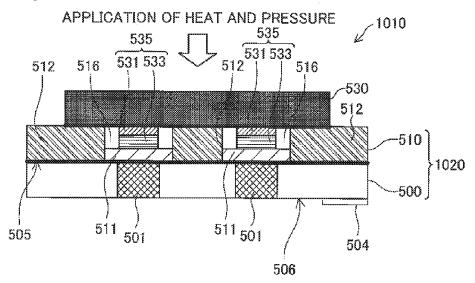

[0034] FIG. 9 is a cross sectional view illustrating a semiconductor power module 40 according to a fourth embodiment; [0035] FIG. 10 is a cross sectional view illustrating the schematic configuration of a semiconductor power module 1010 according to a fifth embodiment;

[0036] FIG. 11 is a diagram illustrating the semiconductor power module 1010 of the fifth embodiment;

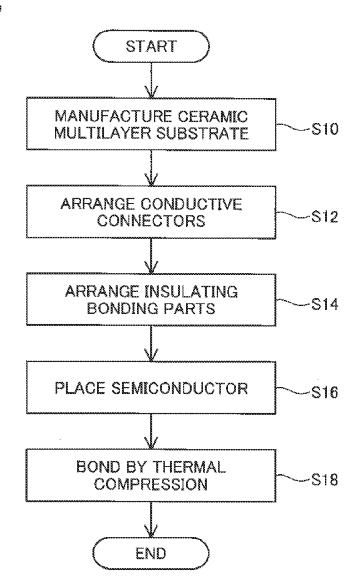

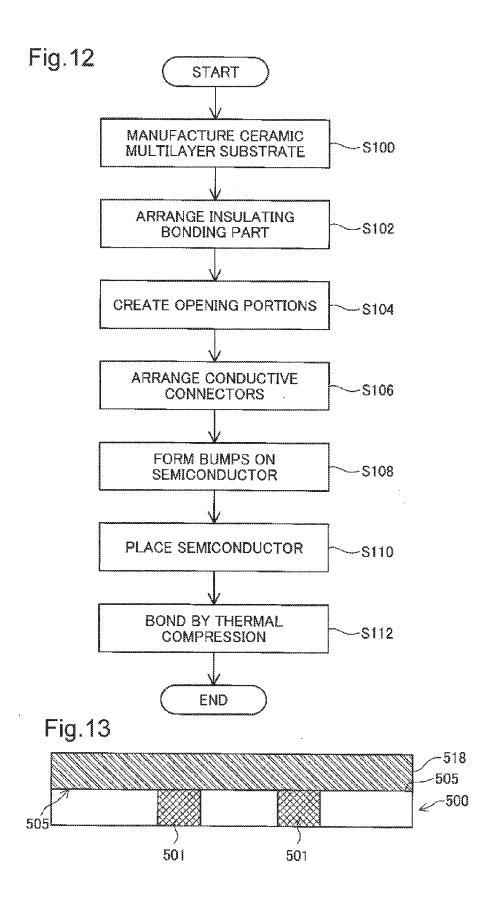

[0037] FIG. 12 is a flowchart showing a production method of the semiconductor power module 1010 according to the fifth embodiment;

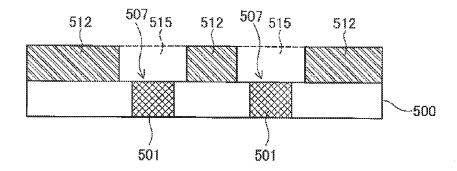

[0038] FIG. 13 is a diagram illustrating the process of arranging the insulating bonding part 512 at step S102;

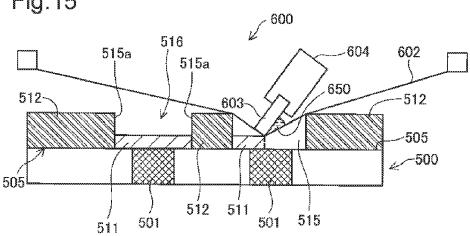

[0039] FIG. 14 is a diagram illustrating the process of creating the opening portions 515 at step S104;

[0040] FIG. 15 is a diagram illustrating the process of arranging the conductive connectors 511 at step S106;

[0041] FIG. 16 is a diagram illustrating the bonding process of the semiconductor power module 1010 according to the fifth embodiment:

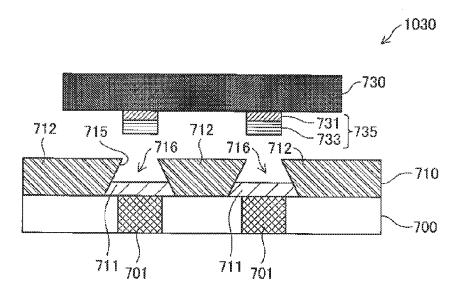

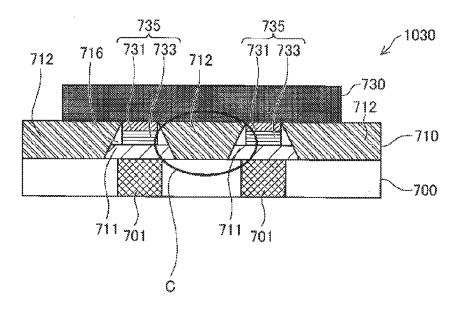

[0042] FIG. 17 is a sectional view illustrating the configuration of a semiconductor power module 1030 according to a sixth embodiment:

[0043] FIG. 18 is a sectional view illustrating the configuration of a semiconductor power module 1030 according to a sixth embodiment;

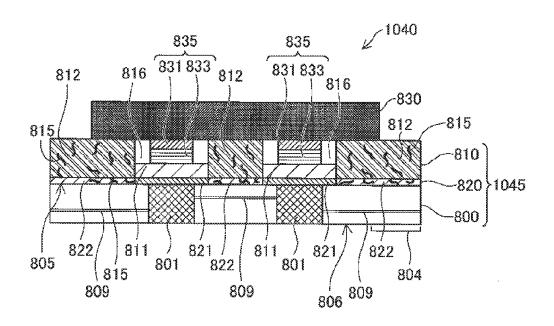

[0044] FIG. 19 is a diagram illustrating the schematic configuration of a semiconductor power 1040 according to Modification 5;

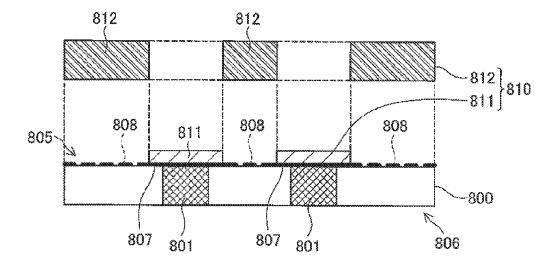

[0045] FIG. 20 is a diagram illustrating the process of arranging the bonding layer 810 in Modification 5;

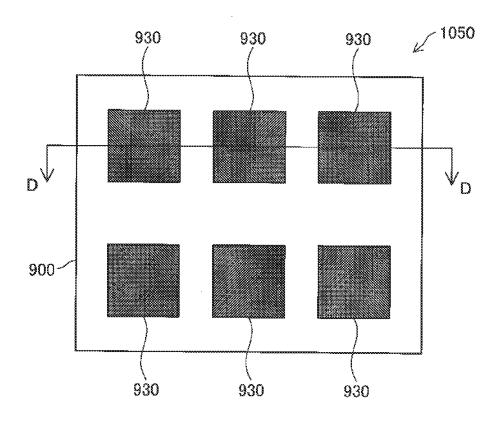

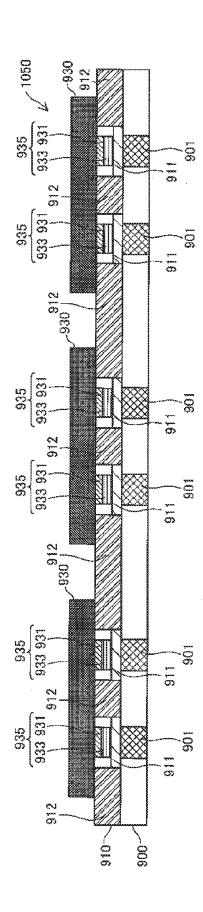

[0046] FIG. 21 is a plan view illustrating a semiconductor power module 1050 according to Modification 6; and

[0047] FIG. 22 is a cross sectional view illustrating the semiconductor power module 1050 of Modification 6.

#### DESCRIPTION OF EMBODIMENTS

#### A. First Embodiment

#### A1. Schematic Configuration of Semiconductor Power Module

[0048] FIG. 1 is a cross sectional diagram illustrating the schematic configuration of a semiconductor power module 10 according to a first embodiment. FIG. 2 is a diagram illustrating a circuit board 20 according to the first embodiment. The semiconductor power module 10 includes a circuit board 20 and a semiconductor device 130. The circuit board 20 includes a ceramic multilayer substrate 100, a bonding layer 110 and a diffusion layer 120.

[0049] The ceramic multilayer substrate 100 is made of a ceramic material. As the ceramic material used may be, for example, aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN) or silicon nitride (Si<sub>3</sub>N<sub>4</sub>). The ceramic multilayer substrate 100 includes a first surface 105 with the semiconductor device mounted thereon, inner layer via holes 101 each arranged to electrically connect the first surface 105 with the other surface or a second surface 106 opposed to the first surface 105 and configured to mount other electronic components such as a control circuit and a capacitor, interconnecting patterns 109 and an electrode terminal 104 for external connection placed on the second surface 106. The interconnecting patterns 109 are formed on the surfaces of the ceramic multilayer substrate 100 and the surfaces of inner layers. The interconnecting patterns formed on the surfaces of the ceramic multilayer substrate 100 are omitted from illustration of FIG. 1. Electrode lands (not shown) for mounting the semiconductor device 130 and other electronic components are formed on the first surface 105 and the second surface 106 of the ceramic multilayer substrate 100. The semiconductor device 130 is electrically connected with the electrode terminal 104 placed on the second surface 106 via the inner layer via holes 101 and the interconnecting patterns 109.

[0050] The bonding layer 110 is placed on the first surface 105 of the ceramic multilayer substrate 100 and is provided as a planar thin film layer including conductive bonding parts 111 and insulating bonding parts 112.

[0051] The conductive bonding parts 111 include conductive connectors 111a and electrode pads 131 of the semiconductor device 130 and are arranged to electrically connect the semiconductor device 130 with the ceramic multilayer substrate 100. The conductive connectors 111a are made of a conductive metal as the main constituent and are arranged on the first surface 105 of the ceramic multilayer substrate 100 or specifically at first regions 107 (shown by the thick solid line) corresponding to the inner layer via holes 101 as shown in FIG. 2. For example, copper, silver or metal aluminum may be used as the conductive metal. The conductive connectors 111a are made thinner than the insulating bonding parts 112 as described below, so that recesses are formed by the insulating bonding parts 112 and the conductive connectors 111a. The electrode pads 131 are arranged to be fit in the recesses, so as to form the conductive bonding parts 111. The electrode pads 131 of the first embodiment correspond to the "protruded part" of the claims. The same applies to second to fourth embodiments described later.

[0052] The insulating bonding parts 112 isolate the semi-conductor device 130 from the ceramic multilayer substrate 100. As shown in FIG. 2, the insulating bonding parts 112 are arranged on the first surface 105 of the ceramic multilayer substrate 100 or specifically at second regions 108 (shown by the thick broken line) different from the first regions 107. The insulating bonding parts 112 are made of powder glass, which is made of an insulating inorganic material as the main constituent and is softened in a heating process in the course of mounting the semiconductor device. The powder glass may be formed to have a multiphase of, for example, silicon oxide, zinc oxide, boron oxide and bismuth oxide, such as ZnO—  $B_2O_3$ —SiO<sub>2</sub>.

[0053] According to the first embodiment, the second regions 108 cover the residual area other than the first regions 107 or the regions where the conductive bonding parts 111 are placed. The conductive bonding parts 111 and the insulating bonding parts 112 have substantially the same thicknesses to enable the bonding layer 110 to form a uniform plane. A surface of the bonding layer 110 opposed to the semiconductor device 130 also forms a uniform plane.

[0054] In this embodiment, the uniform plane may include minute curvatures and irregularities. The bonding layer 110 forming the uniform plane includes that the surface of the bonding layer 110 opposed to the first surface 105 of the ceramic multilayer substrate is formed along the shape of the first surface 105 and the conductive bonding parts 111 and the insulating bonding parts 112 are continuously made flat, and that the surface of the bonding layer 110 opposed to the semiconductor device 130 is formed along the shape of an opposing surface of the semiconductor device 130 opposed to the bonding layer 110.

[0055] It is preferable that the insulating bonding parts 112 contain a filler 115 to such an extent that does not deteriorate the insulation performance. The filler 115 herein may be a

metal filler made of, for example, copper or aluminum powder, or an inorganic filler. The inorganic filler is preferably a filler having high radiation performance, such as a ceramic filler made of, for example, boron oxide, alumina, silicon nitride or aluminum nitride. Inclusion of the filler 115 enables improvement in heat transfer performance and adjustment of the thermal expansion of the insulating bonding parts 112. [0056] The diffusion layer 120 is a layer formed by diffusion bonding of the ceramic multilayer substrate 100 and the bonding layer 110. The diffusion layer 120 includes conductive diffusive parts 121 and insulating diffusive parts 122. The conductive diffusive parts 121 are formed by diffusion bonding of the ceramic multilayer substrate 100 and the conductive connectors 111a of the bonding layer 110. The insulating diffusive parts 122 are formed by diffusion bonding of the ceramic multilayer substrate 100 and the insulating bonding parts 112 of the bonding layer 110. Like the insulating bonding parts 112, the insulating diffusive parts 122 may also contain a filler 115. For the purpose of illustration, the boundaries between the conductive diffusive parts 121 and the insulating diffusive parts 122 are clearly shown in FIG. 1. The boundaries between the conductive diffusive parts 121 and the insulating diffusive parts 122 may, however, be unclear. [0057] The semiconductor device 130 includes the electrode pads 131. The electrode pads 131 are made of, for example, gold (Au) as the main constituent. The semiconductor device 130 is arranged on the bonding layer 110 such that the electrode pads 131 are in contact with the conductive connectors 111a of the bonding layer 110. The semiconductor device 130 is electrically connected with the ceramic multilayer substrate 100 via the electrode pads 131 and the conductive connectors 111a (i.e., conductive bonding parts 111).

#### A2. Production Method

[0058] A production method of the semiconductor power module 10 is described with reference to FIGS. 3 to 6. FIG. 3 is a flowchart showing a production method of the semiconductor power module 10 according to the first embodiment. [0059] The procedure manufactures the ceramic multilayer substrate 100 with the inner layer via holes 101 and the interconnecting patterns 109 formed therein (step S10). Manufacturing the ceramic multilaver substrate 100 includes formation of thin-film electrode lands for mounting the semiconductor device 130 and other electronic components on the surface of the ceramic multilayer substrate 100. The electrode lands may be formed by a printing method using a conductive paste, by physical vapor deposition (PVD) or by chemical vapor deposition (CVD). Step S10 of the first embodiment corresponds to the "substrate manufacturing step" of the claims.

[0060] The procedure arranges the conductive connectors 111a on the first surface 105 of the ceramic multilayer substrate 100 or specifically at the first regions corresponding to the inner layer via holes 101 (step S12). FIG. 3 illustrates the process of arranging the conductive connectors 111a at step S12. As shown in FIG. 3, metal projections made of, as the main constituent, a metal species which is melted by a subsequent heating process at step S18 described later are formed as the conductive connectors 111a. This metal projection is also called bump. The bumps may be formed by a ball mounting method that arranges metal balls at desired locations and changes to a columnar shape by heating. The bumps may also be formed by a method that transfers a metal constituting

bumps at corresponding locations onto the first regions 107 of the first surface 105 of the ceramic multilayer substrate 100 or by a method that prints a paste made of, as the main constituent, the metal species described above as the material of the conductive connectors 111a on the first regions 107 of the first surface 105 of the ceramic multilayer substrate 100 by screen printing. Another applicable method may mask the first regions 107 of the first surface 105 of the ceramic multilayer substrate 100 with a photolithographic pattern and form metal bumps at desired locations by plating.

[0061] The procedure subsequently arranges the insulating bonding parts 112 on the first surface 105 of the ceramic multilayer substrate 100 where the conductive connectors 111a have been arranged or specifically at the second regions different from the first regions (step S14). More specifically, the procedure kneads powder glass and a pyrolytic organic binder with a solvent such as an organic solvent or water to produce a glass powder paste and prints the glass powder paste to fill the gaps between the conductive connectors 111a on the first surface 105 of the ceramic multilayer substrate 100 by screen printing.

[0062] FIG. 5 is a diagram illustrating screen printing of the insulating bonding parts 112 at step S14. A screen printing machine 200 includes a screen 202, a squeegee 203 and a squeegee holder 204. The screen 202 has opening portions created only at residual regions other than regions corresponding to the conductive connectors 111a, i.e., at regions corresponding to the insulating bonding parts 112. A glass powder paste 250 is placed on the screen 202, and the squeegee 203 on the screen 202 is slid. This causes the glass powder paste 250 to pass through the opening portions and to be transferred into residual regions other than regions where the conductive connectors 111a are arranged on the first surface 105 of the ceramic multilayer substrate 100, i.e., regions where the insulating bonding parts 112 are to be arranged. This results in forming a bonding part 110a (FIG. 2) which includes the conductive connectors 111a and the insulating bonding parts 112 and has a planar surface adjoining to the first surface 105 of the ceramic multilayer substrate 100. The order of steps S12 and S14 may be reversed. An organic component (organic binder) used for binding the bonding part 110a is degraded and removed in a heating process described later. In the first embodiment, either step S12 or step S14 may be performed first. Steps S12 and S14 of the first embodiment correspond to the "first placement step" of the claims.

[0063] The procedure places the semiconductor device 130 on the formed bonding part 110a (step S16). More specifically, the semiconductor device 130 is arranged, such that the electrode pads 131 are fit in the recesses formed by the conductive connectors 111a and the insulating bonding parts 112. The contact between the conductive connectors 111a and the electrode pads 131 ensures electrical continuity between the semiconductor device 130 and the conductive connectors 111a. Step S16 of the first embodiment corresponds to the "second placement step" of the claims.

[0064] The procedure bonds together the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130 by thermal compression to produce a semiconductor power module (step S18). FIG. 6 is a diagram illustrating the bonding process of the semiconductor power module 10 according to the first embodiment. As shown in FIG. 6, this process applies pressure to and simultaneously heats the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130 to a temperature that

enables thermal fusion bonding between the conductive connectors 111a and the insulating bonding parts 112. This melts the conductive connectors 111a, the insulating bonding parts 112, the first surface 105 of the ceramic multilayer substrate 100 and the surface of the semiconductor device 130 including the conductive bonding parts 111 and an insulating protective film and makes diffusion bonding between the ceramic multilayer substrate 100 and the bonding layer 110 and between the bonding layer 110 and the semiconductor device 130 via void-free uniform planes. Heating to the temperature that enables thermal fusion bonding between the conductive connectors 111a and the insulating bonding parts 112 is, for example, heating to a temperature of 670° C. that enables thermal fusion bonding between both materials when metal aluminum having a melting point of 660° C. is employed as the material of the conductive connectors 111a and ZnO—B<sub>2</sub>O<sub>3</sub>—SiO<sub>2</sub> glass having a softening point of 640° C. is employed as the material of the insulating bonding parts 112. Step S18 of the first embodiment corresponds to the "bonding step" of the claims.

[0065] As described above, application of pressure and heat based on a temperature profile set to enable at least two-step temperature change causes diffusion of atoms at the interface between the ceramic multilayer substrate 100 and the bonding layer 110 to form the diffusion layer 120 and thereby bonds the ceramic multilayer substrate 100 to the bonding layer 110.

[0066] In a section cut in a direction orthogonal to the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130 (stacking direction of the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130), the interface between the bonding layer 110 and the semiconductor device 130 including a compound semiconductor and a surface protective layer and the interface between the bonding layer 110 and the surface of the ceramic multilayer substrate 100 made of a ceramic component (e.g., alumina, silicon nitride or aluminum nitride) are respectively arranged to be approximately linear as shown by the thick solid line in FIG. 6. No minute defects such as gas bubbles are included in the respective interfaces. Inevitable voids in the order of microns are, however, not included in the defects of the embodiment. According to the embodiment, the size of gas bubbles identified as defects may be, for example, not less than 100 µm.

[0067] In the microscopic sense, the above respective interfaces have the diffusion layers 120 formed by diffusion of the structural components of the bonding layer 110 into the semiconductor device 130 and the ceramic multilayer substrate 100. These diffusion layers are defined as layers respectively including a mixed layer with surface components of the semiconductor device 130 (components constituting the protective film, e.g., Zr and Ti) and a mixed layer with the ceramic component of the ceramic multilayer substrate 100 (e.g., aluminum and nitrogen) by mapping analysis, for example, EDS or EPMA.

[0068] In the semiconductor power module 10 of the first embodiment described above, the bonding layer 110 is made planar. More specifically, the surface of the bonding layer 110 opposed to the ceramic multilayer substrate 100 is made planar along the shape of the first surface 105 of the ceramic multilayer substrate 100. The other surface of the bonding layer 110 opposed to the semiconductor device 130 is also made planar along the shape of the bonding layer 110-side surface of the semiconductor device 130. In the process of

bonding the ceramic multilayer substrate 100 to the semiconductor device 130, this reduces the occurrence of voids between the ceramic multilayer substrate 100 and the bonding layer 110 and voids between the bonding layer 110 and the semiconductor device 130. Accordingly this improves the heat diffusion performance from the semiconductor device 130 to the ceramic multilayer substrate 100 and the bond strength between the ceramic multilayer substrate 100 and the semiconductor device 130.

[0069] In the ceramic multilayer substrate 100 of the first embodiment, the insulating bonding parts 112 of the bonding layer 110 are made of, as the main constituent, an inorganic material such as glass having the higher thermal conduction performance than those of organic materials. This configuration improves the heat diffusion performance from the semiconductor device 130 to the ceramic multilayer substrate 100. [0070] Heating in the bonding process of the semiconductor power module 10 (process at step S18 in FIG. 3) causes thermal expansion of the respective members, so that stresses are generated between the ceramic multilayer substrate 100 and the bonding layer 110 and between the bonding layer 110 and the semiconductor device 130. According to the first embodiment, the coefficient of linear thermal expansion of the glass component as the main constituent of the insulating bonding parts 112 is closer to the coefficients of linear thermal expansion of the ceramic multilayer substrate 100 and of the semiconductor device 130 than the coefficient of linear thermal expansion of the metal as the main constituent of the conductive connectors 111a. Accordingly, the stresses generated on the boundaries between the conductive connectors 111a and the ceramic multilayer substrate 100 and between the conductive connectors 111a and the semiconductor device 130 become greater than the stresses generated on the boundaries between the insulating bonding parts 112 and the ceramic multilayer substrate 100 and between the insulating bonding parts 112 and the semiconductor device 130.

[0071] In the semiconductor power module 10 of the first embodiment, the insulating bonding parts 112 are located in the periphery of the conductive connectors 111a, so that deformation of the conductive connectors 111a is reduced by the insulating bonding parts 112. The stresses generated between the conductive connectors 111a and the ceramic multilayer substrate 100 and between the conductive connectors 111a and the semiconductor device 130 can thus be dispersed over the interfaces between the conductive connectors 111a and the insulating bonding parts 112. This configuration accordingly enables dispersion of the stresses generated in a concentrated manner between the bonding layer 110 and the ceramic multilayer substrate 100 and between the bonding layer 110 and the semiconductor device 130, thus reducing damage of the semiconductor power module 10 and improving the reliability of the semiconductor power module

[0072] In the semiconductor power module 10 of the first embodiment, the diffusion layer 120 is formed between the ceramic multilayer substrate 100 and the bonding layer 110 in the course of diffusion bonding of the ceramic multilayer substrate 100 with the bonding layer 110. This accordingly improves the bond strength between the ceramic multilayer substrate 100 and the bonding layer 110.

[0073] In the semiconductor power module 10 of the first embodiment, the filler 115 having the heat transfer performance and the radiation performance is contained in the insulating bonding parts 112 of the bonding layer 110 and in

the insulating diffusive parts 122 of the diffusion layer 120. This improves the heat diffusion performance from the semi-conductor device 130 to the ceramic multilayer substrate 100.

#### B. Second Embodiment

[0074] The first embodiment describes the semiconductor power module with only one semiconductor device 130 mounted thereon. A second embodiment describes a semiconductor power module with a plurality of semiconductor devices mounted thereon, with reference to FIGS. 7 and 8.

#### B1. Schematic Configuration of Semiconductor Power Module

[0075] FIG. 7 is a plan view illustrating a semiconductor power module 30 according to the second embodiment. FIG. 8 is a cross sectional view illustrating the semiconductor power module 30 of the second embodiment. FIG. 8 shows a cross section, taken on the line A-A in FIG. 7.

[0076] As shown in FIGS. 7 and 8, the semiconductor power module 30 of the second embodiment includes a ceramic multilayer substrate 300, a bonding layer 310, a diffusion layer 320 and a plurality of (six in the second embodiment) semiconductor devices 330. The bonding layer 310 includes conductive bonding parts 311, each including a conductive connector 311a and an electrode pad 331 of the semiconductor device 330, and insulating bonding parts 312. The diffusion layer 320 includes conductive diffusive parts 321 and insulating diffusive parts 322. The ceramic multilayer substrate 300, the bonding layer 310, the conductive bonding parts 311, the insulating bonding parts 312, the diffusion layer 320, the conductive diffusive parts 321, the insulating diffusive parts 322 and each of the semiconductor devices 330 of the second embodiment respectively have the same configurations as those of the ceramic multilayer substrate 100, the bonding layer 110, the conductive bonding parts 111, the insulating bonding parts 112, the diffusion layer 120, the conductive diffusive parts 121, the insulating diffusive parts 122 and the semiconductor device 130 of the first embodiment.

[0077] In general, in response to an increase in allowable amount of heat generation of the semiconductor device accompanied with a change from the conventional Si semiconductor device to the compound semiconductor device such as SiC, the semiconductor device is required to have high heat resistance to the peripheral members. In response to a demand for downsizing of a radiator component as a module, on the other hand, the semiconductor device is required to have high heat diffusivity. In the semiconductor power module 30 of the second embodiment, the bonding layer 310 is made planar, so that the semiconductor devices 330 and the ceramic multilayer substrate 300 are bonded to each other not via an organic material having low heat resistance and heat diffusion properties but via a plane made of, as the main constituent, an inorganic material having excellent heat resistance and heat diffusion properties. This accordingly improves the heat diffusion performance from the semiconductor devices 330 to the ceramic multilayer substrate 300 and thereby provides the semiconductor power module 30 of the high reliability with a plurality of compound semiconductor devices (semiconductor devices 330), which are usable in a high temperature range of or above about 300° C., mounted at the high density.

#### C. Third Embodiment

[0078] According to a third embodiment, conductive bonding parts have a first bonding start temperature which is a temperature to start bonding conductive connectors to electrode pads of a semiconductor device. Insulating bonding parts have a second bonding start temperature which is a temperature to start bonding to an interconnecting substrate and to a semiconductor device and is higher than the first bonding start temperature. In the third embodiment, except such bonding start temperatures, the conductive bonding parts and the insulating bonding parts constituting the bonding layer have the similar effects and functions to those of the first embodiments and are thus described by using the same numerical symbols (i.e., bonding layer 110, conductive bonding parts 111, conductive connectors 111a, electrode pads 131 and insulating bonding parts 112).

#### C1. Bonding Layer

[0079] The conductive bonding parts 111 of the bonding layer 110 have a first bonding start temperature which is a temperature to start bonding the conductive connectors 111a to the electrode pads 131. The first bonding start temperature is equal to or higher than a sintering start temperature at which at least a portion of the material constituting the conductive connectors 111a or constituting the electrode pads 131 starts a sintering reaction. The sintering start temperature means a temperature at which the sintering reaction starts, due to formation of a liquid phase by at least a portion of the components constituting the conductive connectors 111a or the electrode pad 131 or due to a reaction on an adhesive interface in a solid phase. The reason why the first bonding start temperature is set to be equal to or higher than the sintering start temperature is attributed to the following. Even when the conductive bonding parts 111 are not melted, sintering adhesion proceeds accompanied with formation of a liquid phase by only a small portion of the components, so as to start bonding members with each other.

[0080] According to the third embodiment, the conductive connectors 111a are made of tin, and the electrode pads 131 are made of copper or tin as the material. The temperature at which diffusion bonding proceeds with melting and softening the conductive connectors 111a and the electrode pads 131, for example,  $300^{\circ}$  C., is set to the first bonding start temperature.

[0081] The insulating bonding parts 112 have a second bonding start temperature which is a temperature to start bonding the insulating bonding parts 112 to the ceramic multilayer substrate 100 and to the semiconductor device 130 and is higher than the first bonding start temperature. The second bonding start temperature is equal to or higher than a sintering start temperature at which at least a portion of the material constituting the insulating bonding parts 112 starts a sintering reaction. The temperature at which at least a portion of the material constituting the insulating bonding parts 112 starts a sintering reaction means a temperature at which the sintering reaction starts, due to formation of a liquid phase by at least a portion of the components constituting the insulating bonding parts 112 or due to a reaction on an adhesive interface in a solid phase. The reason why the second bonding start temperature is set to be equal to or higher than the sintering start temperature is attributed to the following. Even when the insulating bonding parts 112 are not melted, sintering adhesion proceeds accompanied with formation of a liquid phase by only a small portion of the components, so as to start bonding to other members.

[0082] According to the third embodiment, the insulating bonding parts 112 are made of powder glass composed of  ${\rm Bi_2O_3}$  and  ${\rm B_2O_3}$  (softening point: 357° C.). The temperature which is higher than the first bonding start temperature (300° C.) and enables diffusion bonding to sufficiently proceed with softening the insulating bonding parts 112, for example, 450° C., is set to the second bonding start temperature.

#### C2. Production Method

[0083] The third embodiment employs a temperature profile having a stepwise temperature change and bonds together the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130 by a diffusion bonding process allowing multi-step bonding. The outline of the production method of the semiconductor power module 10 is similar to the procedure of FIG. 3 described in the first embodiment, except a diffusion bonding process by thermal compression at step S18. The diffusion bonding process at step S18 is described below.

[0084] In the third embodiment, after the processing flow to step S16 described above with reference to FIG. 3, the procedure makes diffusion bonding of the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130 by thermal compression to produce a semiconductor power module (step S18, FIG. 3). According to the third embodiment, this thermal compression process applies heat based on the temperature profile set to allow a multi-step change in heating temperature for diffusion bonding, while applying pressure to the ceramic multilayer substrate 100, the bonding layer 110 and the semiconductor device 130. The diffusion bonding process including the heating process based on the temperature profile includes maintaining the heating temperature at the first bonding start temperature for a specified time (first bonding step) and subsequently maintaining the heating temperature at the second bonding start temperature for a specified time (second bonding step). The procedure of the third embodiment uses a pressing jig having a slightly smaller area than the rear face area of the semiconductor device 130 to press the semiconductor device 130 against the ceramic multilayer substrate 100. The first bonding step and the second bonding step are described more specifically below.

[0085] The first bonding step performs the heating process by maintaining the heating temperature at the first bonding start temperature (300° C.) for a specified time (for example, about 10 minutes), so that diffusion bonding proceeds between the conductive connectors 111a and the electrode pads 131, so as to form the conductive bonding parts 111. Since the softening point of the insulating bonding parts 112 (357°C.) is higher than the first bonding start temperature, the insulating bonding parts 112 are not softened in the first bonding step. The material constituting the insulating bonding parts 112 accordingly does not enter between the conductive connectors 111a and the electrode pads 131, so that the material constituting the insulating bonding parts 112 is not mixed into the conductive bonding parts 111 formed by diffusion bonding of the conductive connectors 111a and the electrode pads 131.

[0086] When the diffusion bonding between the conductive connectors 111a and the electrode pads 131 sufficiently proceeds to allow integration of the conductive connectors 111a

with the electrode pads 131, the second bonding step starts. The second bonding step performs the heating process at the second bonding start temperature (450° C.). The heating process sufficiently melts and softens the insulating bonding parts 112, the first surface 105 of the ceramic multilayer substrate 100 and the surface of the semiconductor device 130 made of an insulating protective film. Diffusion bonding proceeds with deforming the softened insulating bonding parts 112 to fill the gaps between the semiconductor device 130 and the bonding layer 110 and the gaps between the bonding layer 110 and the ceramic multilayer substrate 100 by the pressing force of the pressing jig that presses the semiconductor device 130 against the ceramic multilayer substrate 100. As a result, diffusion bonding is made via void-free uniform planes between the ceramic multilayer substrate 100 and the insulating bonding parts 112 and between the insulating bonding parts 112 and the surface of the semiconductor device 130. As described above, this completes production of the semiconductor power module 10.

[0087] In the semiconductor power module of the third embodiment described above, the process of forming the conductive bonding parts employs, as the heating temperature, the first bonding start temperature that is lower than the temperature at which the insulating bonding parts start the sintering reaction, so that the conductive bonding parts are bonded, prior to the insulating bonding parts. Accordingly, in the state that the conductive connectors 111a are bonded to the electrode pads 131 of the semiconductor device and that the conductive bonding parts 111 are bonded to the ceramic multilayer substrate 100, i.e., in the state that there is substantially no void between the conductive connectors 111a and the electrode pads 131 of the semiconductor device and between the conductive bonding parts 111 and the ceramic multilayer substrate 100, the insulating bonding parts 112 start softening and deforming, so as to bond the insulating bonding parts 112 to the semiconductor device 130 and bond the insulating bonding parts 112 to the ceramic multilayer substrate 100. This configuration suppresses deterioration of the conductive performance of the conductive bonding parts 111 due to invasion of the material constituting the insulating bonding parts 112 between the conductive connectors 111a and the electrode pads 131, i.e., mixing of the material constituting the insulating bonding parts 112 into the conductive bonding parts 111.

[0088] In the semiconductor power module of the third embodiment, the first bonding start temperature is the melting start temperature of the material constituting the conductive bonding parts, and the second bonding start temperature is the melting start temperature of the material constituting the insulating bonding parts. Accordingly this configuration ensures the conductive bonding parts and the insulating bonding parts to be melted, thus improving the bond strength between the respective conductive bonding parts and insulating bonding parts with other members.

#### D. Fourth Embodiment

#### D1. Schematic Configuration of Semiconductor Power Module

[0089] FIG. 9 is a cross sectional view illustrating a semiconductor power module 40 according to a fourth embodiment. As shown in FIG. 9, like the semiconductor power module 10 of the first embodiment, the semiconductor power module 40 of the fourth embodiment includes a ceramic multilayer substrate 400, a bonding layer 410 and a diffusion layer 420. The diffusion layer 420 includes conductive diffusive parts 421 and insulating diffusive parts 422. The ceramic multilayer substrate 400, the diffusion layer 420, the conductive diffusive parts 421, the insulating diffusive parts 422 and a semiconductor device 430 of Modification 1 respectively have the same configurations as those of the ceramic multilayer substrate 100, the diffusion layer 120, the conductive diffusive parts 121, the insulating diffusive parts 122 and the semiconductor device 130 of the first embodiment.

[0090] The semiconductor power module 40 of the fourth embodiment differs in configuration of the bonding layer 410 from the semiconductor power module 10 of the first embodiment. The bonding layer 410 is provided as a planar thin film and includes conductive bonding parts 411, each including a conductive connector 411a and an electrode pad 431 of the semiconductor device 430, and insulating bonding parts 412. The insulating bonding parts 412 are formed in a tapered shape to have a wider area on the semiconductor device 430-side surface than the area on the ceramic multilayer substrate 400-side surface as shown by encirclement B in FIG. 9. The conductive connector 411a is formed in a specific shape corresponding to the tapered shape of the insulating bonding parts 412. The shape of the insulating bonding parts 412 is, however, not limited to the tapered shape but may be any shape having a wider area on the semiconductor device 430-side surface than the area on the ceramic multilayer substrate 400-side surface, for example, a stepped shape or a curved shape.

[0091] The semiconductor power module 40 may be produced by the similar method to the method of producing the semiconductor power module 10 of the first embodiment, except the process of arranging the bonding layer 410 (corresponding to steps S12 and S14 in FIG. 3). The process of arranging the bonding layer 410 according to the fourth embodiment may employ, for example, the following procedure.

[0092] The procedure arranges the insulating bonding parts 412, prior to the conductive connectors 411a, by screen printing. More specifically, the procedure uses a screen with opening portions in a tapered shape having a wider area on the semiconductor device 430-side and prints a glass powder paste as the material of the insulating bonding parts 412.

[0093] The procedure subsequently uses a screen with opening portions at the regions corresponding to the conductive connectors 411a and prints a paste made of, as the main constituent, a metal species as the material of the conductive connectors 411a. The viscosity of the paste used is adjusted, so that the paste is spread over the wider area on the semiconductor device 430-side than the surface of the opening portions by the dead weight of the paste after application of the paste on the semiconductor device 430. This completes the bonding parts including the insulating bonding parts 412 in the tapered shape and the conductive connectors 411a in the specific shape corresponding to the tapered shape of the insulating bonding parts 412. The procedure then places the semiconductor device 430 such that the electrode pads 431 of the semiconductor device 430 are fit in the recesses formed by the conductive connectors 411a and the insulating bonding parts 412. This forms the planar bonding layer 410.

[0094] In the semiconductor power module 40 of the fourth embodiment, the insulating bonding parts 412 of the bonding layer 410 are formed in the tapered shape having the wider area on the semiconductor device 430-side surface than the

area on the ceramic multilayer substrate 100-side surface. Compared with the insulating bonding parts 112 of the first embodiment, this configuration provides the wider contact area between the insulating bonding parts 412 and the semiconductor device 430. This accordingly improves the heat diffusion performance from the semiconductor device 430 to the bonding layer 410, compared with the semiconductor power module 10 of the first embodiment. This improves the heat diffusion performance and accelerates heat radiation of the semiconductor device 430, while ensuring the insulation performance between the ceramic multilayer substrate 400 and the semiconductor device 430.

#### E. Fifth Embodiment

# E1. Schematic Configuration of Semiconductor Power Module

[0095] FIG. 10 is a cross sectional view illustrating the schematic configuration of a semiconductor power module 1010 according to a fifth embodiment. FIG. 11 is a diagram illustrating the semiconductor power module 1010 of the fifth embodiment. The semiconductor power module 1010 includes a ceramic multilayer substrate 500, a bonding layer 510 and a semiconductor device 530.

[0096] The ceramic multilayer substrate 500 is made of a ceramic material. As the ceramic material used may be, for example, aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), aluminum nitride (AlN) or silicon nitride (Si<sub>3</sub>N<sub>4</sub>). The ceramic multilayer substrate 500 includes a first surface 505 with a semiconductor device mounted thereon, inner layer via holes 501 each arranged to electrically connect the first surface 505 with the other surface or a second surface 506 opposed to the first surface 505 and configured to mount other electronic components such as a control circuit and a capacitor, interconnecting patterns 509 and an electrode terminal 504 for external connection placed on the second surface 506. The interconnecting patterns 509 are formed on the surfaces of the ceramic multilayer substrate 500 and the surfaces of inner layers. The interconnecting patterns formed on the surfaces of the ceramic multilayer substrate 500 are omitted from illustration of FIG. 10. Electrode lands (not shown) for mounting the semiconductor device 530 and other electronic components are formed on the first surface 505 and the second surface 506 of the ceramic multilayer substrate 500. The semiconductor device 530 is electrically connected with the electrode terminal 504 placed on the second surface 506 via the inner layer via holes 501 and the interconnecting patterns 509.

[0097] The bonding layer 510 is placed on the first surface 505 of the ceramic multilayer substrate 500 and is provided as a thin film layer including conductive connectors 511, an insulating bonding part 512 and projections 535 of the semiconductor device 530 described later. The bonding layer 510 has a smooth surface on the first surface 505-side. In the description of the embodiment, the state without the projections 535 is also described as the bonding layer 510. The projections 535 of the fifth embodiment correspond to the "protruded part" of the claims. The same applies to a sixth embodiment described later.

[0098] The insulating bonding part 512 isolates the semiconductor device 530 from the ceramic multilayer substrate 500. As shown in FIG. 11, the insulating bonding part 512 is arranged on the first surface 505 of the ceramic multilayer substrate 500, and opening portions 515 are created at regions 507 (shown by the thick solid line) corresponding to the inner layer via holes 501. In other words, the insulating bonding part 512 is arranged on the first surface 505 of the ceramic multilayer substrate 500 to be placed at regions 508 (shown by the thick broken line) other than the regions 507 corresponding to the inner layer via holes 501. The insulating bonding part 512 is made of a glass composition including an insulating inorganic material as the main constituent. The insulating inorganic material may be, for example, silicon oxide or zinc oxide.

[0099] The conductive connectors 511 electrically connect the semiconductor device 530 with the ceramic multilayer substrate 500. The conductive connectors 511 are placed in the opening portions 515 on the first surface 505 of the ceramic multilayer substrate 500 as shown in FIG. 11. In other words, the conductive connectors 511 are located at the regions 507 corresponding to the inner layer via holes 501. The conductive connectors 511 are made of, as the main constituent, a conductive metal. The conductive metal may be, for example, copper, silver or metal aluminum. The conductive connectors 511 have at least planar interfaces with the first surface 505.

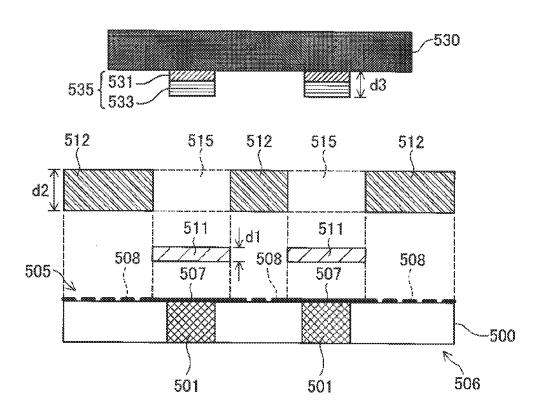

[0100] As shown in FIG. 10, the bonding layer 510 also has recesses 516 formed by the conductive connectors 511 and the insulating bonding part 512. The recess 516 has a volume that is equal to greater than the total volume of the metal projection 535 formed on the semiconductor device 530 as described later. It is here assumed that d1 represents the thickness of the conductive connectors 511; d2 represents the thickness of the insulating bonding part 512; d3 represents the height of the projections 535; and d4 represents an allowable variation in height of the projections 535 caused by warpage of the ceramic multilayer substrate 500 as shown in FIGS. 10 and 11. The height d3 of the projections 535 is designed to be greater than the sum of d4 and the height (d2-d1) of the recesses 516 formed by the insulating bonding part 512 and the conductive connectors 511, i.e., to satisfy  $d3 \ge (d2-d1) + d4$

[0101] The ceramic multilayer substrate 500 may have little warpage during manufacture. When the height of the recesses 516 in the thickness direction is equal to the height of the projections 535 in the thickness direction, the effect of such little warpage of the ceramic multilayer substrate 500 may cause a clearance between a recess 516-side end of the projection 535 and the opposed recess 516. This may result in poor electrical connection between the projections 535 and the conductive connectors 511. Determining the height of the recesses 516 in the thickness direction by taking into account the height variation d4 in the thickness direction of the ceramic multilayer substrate 500, i.e., satisfying d3>d2-d1, ensures the good electrical connection between the projections 535 and the conductive connectors 511 when the semiconductor device 530 is set in the recesses 516. Even when the ceramic multilayer substrate 500 has little warpage, this configuration allows for a height variation of the interface equal to or less than d3-(d2-d1).

[0102] For the purpose of illustration, d1 and d2 are simply expressed as thicknesses in the above description. The thicknesses of the conductive connectors 511 and the insulating bonding part 512 may, however, not be completely uniform. This may result in a variation in thickness according to the measurement position. Additionally, the projections 535 of the semiconductor device 530 are not necessarily made planar as described in the fifth embodiment but may be formed, for example, in a spherical shape. Accordingly, d1 to d3 may be

defined as follows: d1 may represent a maximum value of the distance from the first surface 505 of the ceramic multilayer substrate 500 to the semiconductor device 530-side surface of the conductive connector 511; d2 may represent a maximum value of the distance from the first surface 505 of the ceramic multilayer substrate 500 to the semiconductor device 530-side surface of the insulating bonding part 512; and d3 may represent a maximum value of the height of the projection 535 in the stacking direction from the interface between the semi-conductor device 530 and the bonding layer 510.

[0103] The semiconductor device 530 has the projections 535 as described above. The projection 535 includes an electrode pad 531 and a metal bump 533. The electrode pads 531 are made of, for example, gold (Au) as the main constituent. The bumps 533 are formed to be protruded on the electrode pads 531. The bumps 533 may be formed by arranging metal columns processed in a bump shape at desired locations. The bumps 533 may also be formed by transferring a paste made of a metal specifies such as metal aluminum or silver oxide as the main constituent onto the electrode pads 531 by using a photolithographic pattern or by screen printing the paste.

[0104] The semiconductor device 530 is arranged on the bonding layer 510, such that the projections 535 are received in the recesses 516. When the semiconductor device 530, the ceramic multilayer substrate 500 and the bonding layer 510 are integrally bonded by application of heat and pressure, the ceramic multilayer substrate 500 and the semiconductor device 530 are electrically connected with each other via the conductive connectors 511 and the projections 535 or specifically the bumps 533 and the electrode pads 531. For the purpose of illustration, the bumps 533 and the conductive connectors 511 are illustrated with no change in shape before and after such bonding in the respective drawings. The bumps 533 and the conductive connectors 511 are, however, deformed by application of heat in the bonding process to fill the cavities of the recesses 516, so that the interface between the insulating bonding part 512 and the semiconductor device 530 is made planar. The difference between the volume of the recess 516 and the volume of the projection 535 shown in FIG. 10 is smaller than the volume of the recess 516 prior to integration with the semiconductor device 530. The bond strength between the semiconductor device 530 and the ceramic multilayer substrate 500 is provided by the insulating bonding part 512, in addition to the projections 535 and the conductive connectors 511. The stress caused by the difference in thermal expansion among the respective members by the heat generated during operation of the semiconductor device 530 is dispersed over the conductive connectors 511 and the insulating bonding part 512. This results in improving the endurance reliability of the semiconductor module. The heat generated during operation of the semiconductor device 530 is diffused to the ceramic multilayer substrate 500 via the projections 535 and the conductive connectors 511, while being diffused to the ceramic multilayer substrate 500 via the insulating bonding part 512. This results in suppressing a temperature increase of the semiconductor device.

[0105] It is preferable that the projections 535 and the recesses 516 are formed such that the volume of the projection 535 is substantially equal to the volume of the recess 516. As long as electrical connection is made, the volume of the recess 516 may be greater than the volume of the projection 535.

#### E2. Production Method

[0106] A production method of the semiconductor power module 1010 is described with reference to FIGS. 12 to 16. FIG. 12 is a flowchart showing a production method of the semiconductor power module 1010 according to the fifth embodiment.

[0107] The procedure manufactures the ceramic multilayer substrate 500 with the inner layer via holes 501 and the interconnecting patterns 509 formed therein (step S100). Manufacturing the ceramic multilayer substrate 500 includes formation of thin-film electrode lands for mounting the semiconductor device 530 and other electronic components on the surface of the ceramic multilayer substrate 500. The electrode lands may be formed by a printing method using a conductive paste, by physical vapor deposition (PVD) or by chemical vapor deposition (CVD). Step S100 of the fifth embodiment corresponds to the "substrate manufacturing step" of the claims.

[0108] The procedure subsequently arranges the insulating bonding part 512 on the first surface 505 of the manufactured ceramic multilayer substrate 500 (step S102). The process of arranging the insulating bonding part 512 is described with reference to FIG. 13.

[0109] FIG. 13 is a diagram illustrating the process of arranging the insulating bonding part 512 at step S102. The procedure kneads powder glass as the main constituent of the insulating bonding part 512 and a pyrolytic organic binder with a solvent such as an organic solvent or water to produce a glass powder paste 518 and applies the glass powder paste 518 on the first surface 505 of the ceramic multilayer substrate 500 as shown in FIG. 13.

[0110] The procedure then creates the opening portions 515 in the insulating bonding part 512 formed on the ceramic multilayer substrate 500 (step S104). The process of creating the opening portions 515 is described with reference to FIG. 14