# (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 113380623 A (43) 申请公布日 2021. 09. 10

**H01L 29/778** (2006.01)

(21) 申请号 202110636811.0

(22) 申请日 2016.06.08

(62) 分案原申请数据

201610403535.2 2016.06.08

(71) 申请人 苏州能屋电子科技有限公司 地址 215000 江苏省苏州市工业园区星湖 街218号生物纳米园A4楼110B室

(72) **发明人** 宋亮 郝荣晖 付凯 于国浩 张晓东 范亚明 蔡勇 张宝顺

(74) 专利代理机构 北京方圆嘉禾知识产权代理 有限公司 11385

代理人 杨金娟

(51) Int.CI.

H01L 21/335 (2006.01) H01L 29/06 (2006.01)

权利要求书1页 说明书6页 附图2页

#### (54) 发明名称

通过p型钝化实现增强型HEMT的方法

#### (57) 摘要

本发明公开了一种通过p型钝化实现增强型HEMT的方法,其包括:提供主要由第一、第二半导体组成的异质结构,第二半导体分布于第一半导体上,并具有宽于第一半导体的带隙,且异质结构中形成有二维电子气;在第二半导体上形成p型掺杂的第三半导体;对第三半导体中除栅下区域之外的其余区域进行钝化处理,使p型掺杂区仅存在于栅下区域,所述栅下区域分布在所述HEMT器件的栅极正下方;制作与异质结构连接的源、漏、栅极,并使所述源、漏极能够通过所述二维电子气电连接,且使所述栅极分布于源、漏极之间。本发明还公开了一种增强型HEMT。本发明具有工艺简单,重复性高,器件性能稳定优良,成 聚 本低廉,易于进行大规模生产等优点。

CN 113380623 A

- 1.一种通过p型钝化实现增强型HEMT的方法,其特征在于,由以下步骤组成:

- (1) 在外延生长设备的反应室中对衬底表面进行处理;

- (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为1μm-3μm;A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm,Mg掺杂浓度为10<sup>16</sup>量级,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

- (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,进行台面隔离,可以采用离子注入或等离子体刻蚀;

- (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积欧姆接触金属Ti/Al/Ni/Au并进行剥离清洗,之后对样品进行890℃30s退火形成欧姆接触,分别为源极和漏极;

所述Ti/Al/Ni/Au中Ti层、Al层、Ni层和Au层的厚度分别为20nm、130nm、50nm和150nm;

- (5)进行清洗、光刻形成栅极区,同样利用电子束沉积Ni/Au进行剥离,在氮气气氛下400℃,10min退火形成肖特基接触,完成栅极的制作;所述Ni/Au中Ni层和Au层的厚度分别为50nm和250nm;

- (6)利用栅极作为离子注入的掩膜,使用离子注入机,进行H离子注入,其中H离子注入能量以不进入到二维电子气沟道区为准,使H能与p型掺杂层注入区域内的Mg有效结合,使之失去p型特性,完成器件的制作。

- 2.一种通过p型钝化实现增强型HEMT的方法,其特征在于,包括以下步骤:

- (1) 在反应室中对衬底表面进行处理;

- (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为1μm-3μm,A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm,Mg掺杂浓度为10<sup>16</sup>量级,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

- (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,利用光刻胶做掩膜,使用离子注入机进行H离子注入,使H能与P型掺杂层注入区域内的Mg有效结合,使之失去p型特性。

- (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积欧姆接触金属Ti/A1/Ni/Au(20nm/130/nm/50nm/150nm)并进行剥离清洗,之后对样品进行890℃30s退火形成欧姆接触,分别为源极和漏极;

- (5) 进行清洗、光刻,之后进行台面隔离,可以采用离子注入或等离子体刻蚀;

- (6)进行清洗、光刻形成栅极区7,同样利用电子束沉积Ni/Au(50/250nm)进行剥离,在 氮气气氛下400℃10min退火形成肖特基接触,完成栅极的制作,同时完成器件的制作。

- 3.如权利要求1或2所述的方法,其特征在于,所述等离子注入的方式还包括ICP等离子体处理。

# 通过p型钝化实现增强型HEMT的方法

[0001] 本申请为2016年06月08日提交中国专利局、申请号为201610403535.2、发明名称为"通过p型钝化实现增强型HEMT的方法及增强型HEMT"的中国专利申请的分案申请。

### 技术领域

[0002] 本发明涉及一种通过p型钝化实现增强型HEMT的方法,属于微电子工艺领域。

## 背景技术

[0003] HEMT器件是充分利用半导体的异质结构 (Heterostructure) 结构形成的二维电子气而制成的,与Ⅲ-VI族 (如AlGaAs/GaAs HEMT) 相比,Ⅲ族氮化物半导体由于压电极化和自发极化效应,在异质结构 (如AlGaN/GaN) 中能够形成高浓度的二维电子气。所以在使用Ⅲ族氮化物制成的HEMT器件中,势全层一般不需要进行掺杂。同时,Ⅲ族氮化物具有大的禁带宽度、较高的饱和电子漂移速度、高的临界击穿电场和极强的抗辐射能力等特点,能够满下一代电力电子系统对功率器件更大功率、更高频率、更小体积和更高温度的工作的要求。

[0004] 现有的Ⅲ族氮化物半导体HEMT器件作为高频器件或者高压大功率开关器件使用时,特别是作为功率开关器件时,增强型HEMT器件与耗尽型HEMT器件相比更有助于提高系统的安全性、降低器件的损耗和简化设计电路。目前实现增强型HEMT主要的方法有薄势垒层、凹栅结构、p型盖帽层和F处理等技术,但这些技术都存在不足。例如,薄的势垒层技术不需使用刻蚀工艺,所以带来的损伤小,但是由于较薄的势垒层,器件的饱和电流较小。凹栅结构解决了饱和电流较小的问题,但是一般的HEMT器件之中势垒层只有20-30nm,采用刻蚀工艺形成凹栅结构的工艺难于控制,重复性较差。又例如,F等离子处理也能实现增强型HEMT器件,并且不需要刻蚀,但是F的等离子体在注入的过程中也会刻蚀势垒层,造成器件性能的降低。p型盖帽层同样需要刻蚀工艺,工艺难于控制,重复性较差,同时产生界面态,影响器件的稳定性。

[0005] 因而,业界亟待发展出一种易于实施,重复性好,且能有效保证器件性能的增强型 HEMT器件的实现方法。

#### 发明内容

[0006] 针对现有技术的不足,本发明的主要目的在于提出一种通过p型钝化实现增强型HEMT的方法及增强型HEMT。

[0007] 为实现前述发明目的,本发明采用的技术方案包括:

[0008] 本发明提供了一种通过p型钝化实现增强型HEMT的方法,由以下步骤组成:

[0009] (1) 在外延生长设备的反应室中对衬底表面进行处理;

[0010] (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为 $1\mu$ m- $3\mu$ m; A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm, Mg掺杂浓度为 $10^{16}$ 量级,以能够耗尽A1GaN/GaN异质结沟道内二维电子气为准,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

[0011] (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,进行台面隔离,可以采用离子注入或等离子体刻蚀;

[0012] (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积 欧姆接触金属Ti/Al/Ni/Au并进行剥离清洗,之后对样品进行890℃30s退火形成欧姆接触,分别为源极和漏极;

[0013] 所述Ti/Al/Ni/Au中Ti层、Al层、Ni层和Au层的厚度分别为20nm、130nm、50nm和150nm;

[0014] (5)进行清洗、光刻形成栅极区,同样利用电子束沉积Ni/Au进行剥离,在氮气气氛下400℃,10min退火形成肖特基接触,完成栅极的制作;所述Ni/Au中Ni层和Au层的厚度分别为50nm和250nm;

[0015] (6) 利用栅极作为离子注入的掩膜,使用离子注入机,进行H离子注入,其中H离子注入能量以不进入到二维电子气沟道区为准,使H能与p型掺杂层注入区域内的Mg有效结合,使之失去p型特性,完成器件的制作。

[0016] 本发明还提供了一种通过p型钝化实现增强型HEMT的方法,其特征在于,包括以下步骤:

[0017] (1) 在反应室中对衬底表面进行处理;

[0018] (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为 $1\mu$ m- $3\mu$ m, A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm, Mg掺杂浓度为 $10^{16}$ 量级,以能够耗尽A1GaN/GaN异质结沟道内二维电子气为准,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

[0019] (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,利用光刻胶做掩膜,使用离子注入机进行H离子注入,使H能与P型掺杂层注入区域内的Mg有效结合,使之失去p型特性。

[0020] (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积欧姆接触金属Ti/A1/Ni/Au (20nm/130/nm/50nm/150nm)并进行剥离清洗,之后对样品进行890C30s退火形成欧姆接触,分别为源极和漏极;

[0021] (5) 进行清洗、光刻,之后进行台面隔离,可以采用离子注入或等离子体刻蚀:

[0022] (6) 进行清洗、光刻形成栅极区7,同样利用电子束沉积Ni/Au(50/250nm)进行剥离,在氮气气氛下400℃10min退火形成肖特基接触,完成栅极的制作,同时完成器件的制作。

[0023] 优选的,所述等离子注入的方式还包括ICP等离子体处理。

[0024] 与现有技术相比,本发明的优点包括:通过在异质结构上形成p型掺杂层,再采用H离子注入等钝化方式,使p型掺杂区仅在栅下区域被保留,进而实现了增强型HEMT器件,其中p型掺杂层可与异质结构一次外延而成,相较于传统的采用p-GaN实现增强型HEMT的方式,能有效减小界面态,同时不需要刻蚀工艺,工艺易控制,工艺要求较为宽松,对器件的损伤小,具有工艺简单,重复性高,成本低廉,易于进行大规模生产等特点。

## 附图说明

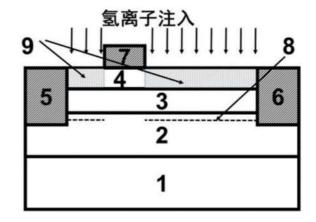

[0025] 图1是普通耗尽型GaN HEMT器件的局部结构示意图:

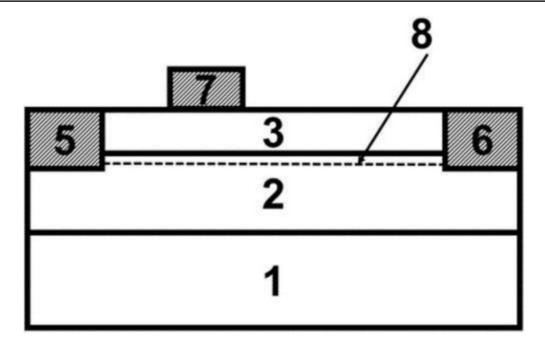

[0026] 图2是普通p-GaN增强型GaN HEMT器件的局部结构示意图:

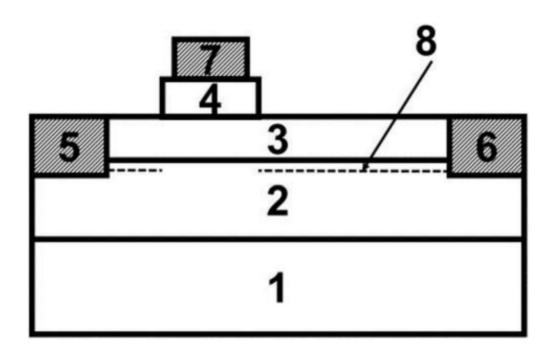

[0027] 图3是仅仅外延p型掺杂层不进行H离子注入的GaN HEMT器件的局部结构示意图:

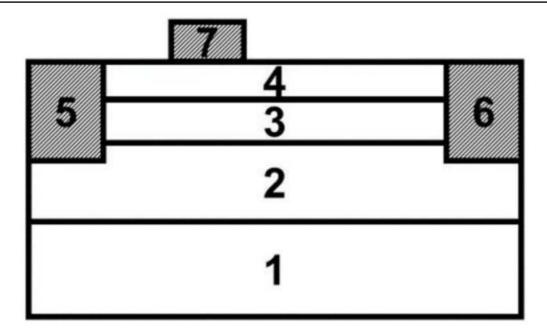

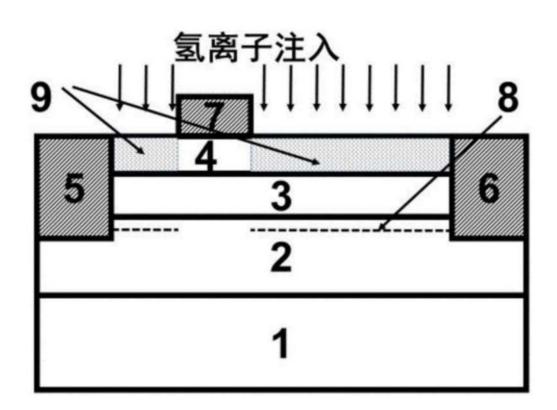

[0028] 图4是本发明一典型实施方案采用H离子注入p型掺杂层实现增强型GaN HEMT的结构示意图:

[0029] 附图标记说明:衬底1、第一半导体2、第二半导体3、p型掺杂层4、源极5、漏极6、栅极7、二维电子气8、离子注入区9。

#### 具体实施方式

[0030] 下文将对本发明的技术方案作更为详尽的解释说明。但是,应当理解,在本发明范围内,本发明的上述各技术特征和在下文(如实施例)中具体描述的各技术特征之间都可以互相组合,从而构成新的或优选的技术方案。限于篇幅,在此不再一一累述。

[0031] 本申请实施例的一个方面提供的一种通过p型钝化实现增强型HEMT的方法包括:

[0032] 提供主要由第一半导体和第二半导体组成的异质结构,所述第二半导体分布于第一半导体上,并具有宽于第一半导体的带隙,且所述异质结构中形成有二维电子气;

[0033] 在所述第二半导体上形成p型掺杂的第三半导体;

[0034] 对所述第三半导体中除栅下区域之外的其余区域进行钝化处理,使p型掺杂区仅存在于栅下区域,所述栅下区域分布在所述HEMT器件的栅极正下方;

[0035] 以及,制作与所述异质结构连接的源极、漏极及栅极,并使所述源极和漏极能够通过所述二维电子气电连接,且使所述栅极分布于源极与漏极之间。

[0036] 在一些实施方案中,所述的方法包括:通过对分布在第二半导体上的第三半导体进行Mg掺杂,从而形成p型掺杂的第三半导体。

[0037] 在一些实施方案中,所述方法包括:在所述第三半导体的栅下区域上设置掩模,之后对所述第三半导体进行钝化处理,从而使p型掺杂区仅存在于栅下区域。

[0038] 其中,所述掩模包括栅极或光刻胶掩模,且不限于此。

[0039] 在一些实施方案中,所述钝化处理至少选用H离子注入,NH<sub>3</sub>等含H的plasma处理 (例如可以通过ICP CVD实现)、离子注入和高温处理中的任意一种方式,且不限于此。

[0040] 较为优选的,所述第一半导体、第二半导体和第三半导体的材质均选自Ⅲ族氮化物。

[0041] 例如,所述第一半导体的材质可选用但不限于GaN等。

[0042] 例如,所述第二半导体的材质可选用但不限于 $Al_xGa_{(1-x)}$ N或InAlN等, $0 < x \le 1$ 。

[0043] 例如,所述第三半导体的材质可选自但不限于GaN等。

[0044] 在一些实施方案中,所述第二半导体与第一半导体之间还分布有插入层。

[0045] 其中,所述插入层的材质可选自但不限于A1N等。

[0046] 在一些较为具体的实施例中,所述方法可以是一种采用H离子注入p型掺杂层实现增强型HEMT的方法,包括:

[0047] 外延生长形成Ⅲ族氮化物增强型HEMT器件的基础结构,包括主要由第一半导体和第二半导体组成的异质结构:

[0048] 在所述第二半导体表面外延p型掺杂层(即第三半导体),其通过对Ⅲ族氮化物进行Mg掺杂得到,通过对非栅下区域的p型掺杂层(此区域可定义为离子注入区)进行H离子注

入,使得p型掺杂区仅存在于栅下区域,从而使栅下区域无二维电子气积累,而沟道其他区域还存在着二维电子气。

[0049] 以及,制作源、漏、栅极。

[0050] 在一些实施方案中,所述的方法包括:至少选用金属有机化学气相沉积 (MOCVD)、分子束外延 (MBE) 或磁控溅射中的任一种方式生长形成所述异质结构、所述第三半导体等。

[0051] 需说明的是,前述的"栅极下方"、"栅下区域"主要是指栅极在异质结构上的正投影所覆盖的区域。

[0052] 本发明实施例还提供了一种增强型HEMT器件,其可由前述任一种方法制备形成。

[0053] 在一些实施例中,所述增强型HEMT器件包括源、漏、栅极和异质结构,所述异质结构包括第一半导体和第二半导体,所述第二半导体分布于第一半导体上,并具有宽于第一半导体的带隙,且所述异质结构中形成有二维电子气,所述源、漏极通过所述二维电子气电连接,所述栅极分布于源、漏极之间,所述栅极与第二半导体之间还设置有第三半导体,所述第三半导体包含仅存在于栅下区域的p型掺杂区,所述栅下区域分布在所述HEMT器件的栅极正下方。

[0054] 进一步的,当在所述HEMT器件的栅极未施加电压或施加的电压低于一阈值电压时,所述HEMT器件处于断开状态,而当在所述HEMT器件的栅极施加的电压大于所述阈值电压时,所述HEMT器件处于开启状态。

[0055] 进一步的,所述源极和漏极分别与电源的低电位和高电位连接。

[0056] 更进一步的,当在栅极施加零偏压或者没有施加偏压时,于栅极正下方的异质结构局部区域内无二维电子气的积累,而当在栅极电压大于阈值电压时,能够于栅极正下方的异质结构局部区域内形成二维电子气。

[0057] 需说明的是,前述的"栅极下方"、"栅下区域"主要是指栅极在异质结构上的正投影所覆盖的区域。

[0058] 在一些实施方案中,所述第一半导体、第二半导体、第三半导体均可优选采用Ⅲ族 氮化物半导体。

[0059] 在一些实施例中,分布于栅极下方、第二半导体之上的p型掺杂层通过对Ⅲ族氮化物进行Mg掺杂得到,通过对非栅下区域的p型掺杂层进行H离子注入,使得p型掺杂区仅存在于栅下区域,从而使栅下区域二维电子气耗尽,而沟道其他区域还存在着二维电子气。

[0060] 在一些较为具体的实施例中,所述增强型HEMT可以包括:主要由Gan层和 $A1_xGa_{(1-x)}$  N (0<x $\le$ 1) 层组成的异质结构以及其上的p型掺杂Gan层,以及,与所述外延结构连接的源、漏、栅极;所述源、漏极分布在A1xGa (1-x) N层上,并且通过形成于异质结构中的二维电子气电连接,栅极设于源、漏极之间近源极一侧,位于p型掺杂区之上。

[0061] 在这些较为具体的实施例中,于所述增强型HEMT制备工艺中采用的离子注入区是可以是分布在 $Al_xGa_{(1-x)}N_{(0< x \le 1)}$ 层之上p型GaN层内的局部区域(非栅下区域),而栅下区域通过掩膜保护。

[0062] 在一些实施例中,所述掩膜可以选择但不限于栅极、光刻胶等。

[0063] 在一些实施例中,所述源极和漏极分别与电源的低电位和高电位连接。

[0064] 在一些实施例中,于第一、第二半导体之间还可设有插入层等,其材质可以是AlN等,但不限于此。

[0065] 在一些实施例中,当未在栅极上施加电压或施加于栅极的电压低于一阈值电压时,在位于栅极下方的第一半导体中电子耗尽,所述HEMT器件处于断开状态,而当施加于栅极的电压超过一阈值电压时,在位于栅极下方的第一半导体中会积累电子形成导电通道,从而使所述HEMT器件处于开启状态。

[0066] 前述的 $GaN/A1_xGa_{(1-x)}N(0 < x \le 1)$  异质结构也可替换为GaN/InA1N等异质结构,或业界所知的其它适用的异质结构。

[0067] 以下结合附图及若干实施例对本发明的技术方案作进一步的解释说明。

[0068] 参阅图1,对于普通HEMT器件(以A1GaN/GaN器件为例,如下均简称"器件"),一般而言,当在栅极7施加零偏压或者没有施加偏压时,漏极6和源极5都与二维电子气8相连接,所以器件的漏极6和源极5是导通的,器件处于开启状态,一般称这种器件为耗尽型HEMT器件,也可以称作常开型HEMT器件。在器件关断过程中,栅极必须施加一定的负偏压,并且所加偏压V<Vth,将栅下二维电子耗尽,在实际的应用过程中,存在功耗高和安全性方面的问题。

[0069] 参阅图2,对于普通p-GaN增强型HEMT器件而言,当在栅极7施加零偏压或者没有施加偏压时,由于p型掺杂层4中的空穴向栅下注入,使得栅极7下面的二维电子气被耗尽,所以源极5和漏极6处于断开状态,一般称这种器件为增强型HEMT器件,也可以称作常关型HEMT器件。为了使器件处于开启状态,必须使栅极的下端积累电子,实现源极5和漏极6之间的连接,当栅极8加偏压达到Vg>Vth时,Vth为器件的阈值电压,对于增强型HEMT器件一般Vth为正值,器件开启。

[0070] 参阅图3是仅仅外延p型掺杂层不进行H离子注入的GaN HEMT器件。p型掺杂层4由Mg掺杂得到。当在栅极7施加零偏压或者没有施加偏压时,由于p型掺杂层4中的空穴向栅下注入,使得整个沟道的二维电子气被耗尽,所以源极5和漏极6处于断开状态。当在栅极7施加较大正向电压时,沟道内除栅下区域内二维电子气仍被耗尽,源极5和漏极6处于断开状态,导致整个器件不能开启。

[0071] 参阅图4是本发明一典型实施方案中采用H离子注入p型掺杂层所实现的增强型HEMT的结构示意图。

[0072] 一种实现所述增强型HEMT的方法可以包括:首先,在衬底1上生长A1GaN/GaN异质结构及p型掺杂GaN。生长方式可以选择但不限于使用金属有机化学气相沉积(MOCVD)、分子束外延(MBE)或磁控溅射等。然后通过图形化的方法,对除栅下区域的p型掺杂GaN进行H离子注入,使激活的Mg与H成键,从而使离子注入区9不再具有p型特性。所以可以实现在栅极区域,无法形成二维电子气的积累,在栅极区域以外,由于势垒层3和沟道层的自发极化和压电极化,会形成高浓度的二维电子气。当在栅极7施加零偏压或者没有施加偏压时,漏极6和源极5都与二维电子气8相连接,但在器件的栅极下方没有二维电子气的积累,所以器件的漏极6和源极5是断开的,器件处于关闭状态,当栅压大于阈值电压时,栅极的下端积累电子,实现源极5和漏极6之间的连接,器件导通,所以器件为常关型GaN HEMT器件。

[0073] 实施例1:请参考图4,本实施例涉及的一种采用H离子注入p型掺杂层实现增强型HEMT的制作方法包括如下步骤:

[0074] (1) 在外延生长设备的反应室中对衬底表面进行处理;

[0075] (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为1µm-3µm, A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm,

Mg掺杂浓度为10<sup>16</sup>量级,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

[0076] (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,进行台面隔离,可以采用离子注入或等离子体刻蚀;

[0077] (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积欧姆接触金属Ti/A1/Ni/Au(20nm/130/nm/50nm/150nm)并进行剥离清洗,之后对样品进行890℃30s退火形成欧姆接触,分别为源极和漏极;

[0078] (5) 进行清洗、光刻形成栅极区7,同样利用电子束沉积Ni/Au(50/250nm)进行剥离,在氮气气氛下400℃10min退火形成肖特基接触,完成栅极的制作。

[0079] (6) 利用栅极作为离子注入的掩膜,使用离子注入机,进行H离子注入(优选的,其中H离子注入能量应较低,以不进入到二维电子气沟道区为宜),使H能与p型掺杂层注入区域内的Mg有效结合,使之失去p型特性,完成器件的制作。

[0080] 实施例2

[0081] 请再次参阅图4,一种采用H离子注入P型掺杂层所实现的增强型HEMT的制作方法包括如下步骤:

[0082] (1) 在反应室中对衬底表面进行处理;

[0083] (2) 在衬底上外延生长A1GaN/GaN外延层及p-GaN,其中GaN的厚度为 $1\mu$ m- $3\mu$ m, A1GaN的厚度为14nm-30nm,其中A1元素的摩尔含量为20%-30%,p-GaN的厚度为5-100nm, Mg掺杂浓度为 $10^{16}$ 量级,从腔室取出以后利用有机溶液进行清洗并用高纯氮气进行吹洗;

[0084] (3) 对清洗干净的样品进行光刻显影,光刻胶采用AZ5214,曝光时间为6.5s,显影时间为50s-60s,利用光刻胶做掩膜,使用离子注入机进行H离子注入,使H能与P型掺杂层注入区域内的Mg有效结合,使之失去p型特性。

[0085] (4) 通过光刻,对源漏区域进行刻蚀,刻掉p型掺杂层,之后放入电子束沉积台沉积欧姆接触金属Ti/A1/Ni/Au (20nm/130/nm/50nm/150nm)并进行剥离清洗,之后对样品进行890°C30s退火形成欧姆接触,分别为源极和漏极;

[0086] (5)进行清洗、光刻,之后进行台面隔离,可以采用离子注入或等离子体刻蚀;

[0087] (6) 进行清洗、光刻形成栅极区7,同样利用电子束沉积Ni/Au(50/250nm)进行剥离,在氮气气氛下400℃10min退火形成肖特基接触,完成栅极的制作,同时完成器件的制作。

[0088] 前述增强型HEMT器件的工作原理如下:阈值电压Vth为正值,当栅电压Vg〈Vth时,由于p型掺杂区中的空穴向栅下注入,使得栅极7下面的二维电子气被耗尽,所以源极5和漏极6处于断开状态。当栅极8加偏压达到Vg〉Vth时,栅下区域会积累电子,积累的电子形成新的导通沟道,使源极5和漏极6导通,器件处于开启状态。

[0089] 此外,本案发明人还参照利用本说明书中述及的其它原料、其它工艺操作及工艺条件,实现了其它一系列增强型HEMT样品的制作。

[0090] 应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

图1

图2

图3

图4