1 Publication number:

0 259 029 B1

EUROPEAN PATENT SPECIFICATION

- (45) Date of publication of patent specification: 28.07.93 (51) Int. CL.<sup>5</sup>: H03F 3/45, H03F 1/32

- 2) Application number: 87307087.4

- ② Date of filing: **11.08.87**

(12)

54 FET transconductance amplifier with improved linearity and gain.

| <ul> <li>Priority: 02.09.86 US 902537</li> <li>Date of publication of application:<br/>09.03.88 Bulletin 88/10</li> </ul>                 | ⑦ Proprietor: TEKTRONIX INC.<br>Howard Vollum Park 14150 S.W. Karl Braun<br>Drive P.O.Box 500, Mail Stop 50-PAT<br>Beaverton Oregon 97077-0001(US) |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Publication of the grant of the patent:</li><li>28.07.93 Bulletin 93/30</li></ul>                                                 | <ul> <li>Inventor: Garuts, Valdis</li> <li>14170 S.W. 22nd Street</li> <li>Beaverton Oregon(US)</li> </ul>                                         |

| <ul> <li>Designated Contracting States:</li> <li>DE FR GB NL</li> </ul>                                                                   |                                                                                                                                                    |

| <ul> <li>References cited:</li> <li>GB-A- 2 013 444</li> <li>US-A- 4 048 577</li> <li>US-A- 4 075 574</li> <li>US-A- 4 146 844</li> </ul> | (4) Representative: Wombwell, Francis et al<br>Potts, Kerr & Co. 15, Hamilton Square<br>Birkenhead Merseyside L41 6BR (GB)                         |

| U. Tietze / Ch. Schenk: Halbleiter-<br>Schaltungstechnik, Springer-Verlag 1983,<br>pages 97 and 98                                        |                                                                                                                                                    |

|                                                                                                                                           |                                                                                                                                                    |

10

15

20

25

30

35

#### Description

## **TECHNICAL FIELD**

The present invention relates to FET amplifiers, and more particularly to FET transconductance amplifiers having improved linearity and gain.

1

Field effect transistors of the gallium arsenide (GaAs) MES FET type are increasingly being used in circuits in which high speed operation is advantageous. Their increasing popularity, however, has not yet extended to high precision, high frequency analog amplifiers. The primary reason is the poor linearity of FET amplifiers. The linearity of FET amplifiers is poor because the drain current of an FET is a nonlinear, power-law function of its gate-to-source voltage. The mechanisms which produce this undesirable trait are inherent in the fundamental physical properties of field effect transistors.

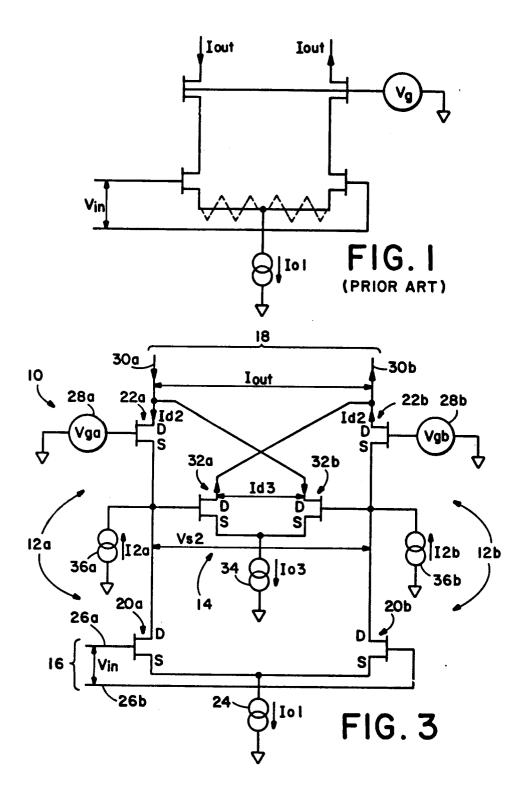

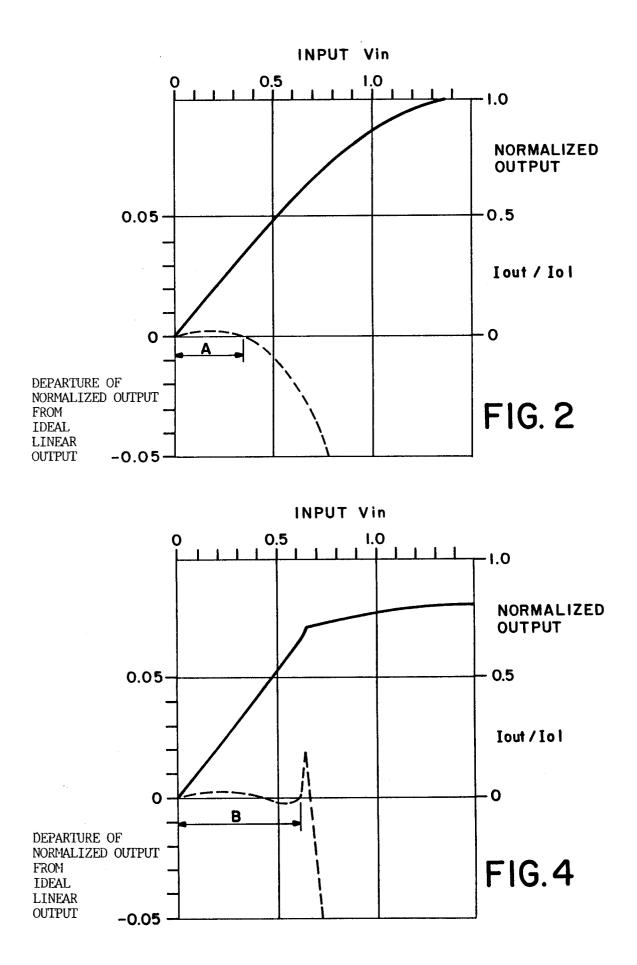

A representative prior art uncompensated FET amplifier, connected in a differential cascode configuration, is shown in Fig. 1. The transfer characteristics of this amplifier are shown by the graph of Fig. 2, which shows the output current Iout normalized to its maximum value Io1 vs. the differential input voltage Vin. The dashed line in the lower portion of Fig. 2 indicates the departure of the actual FET transfer characteristics from an ideal, linear transfer characteristic on the expanded vertical scale on the left. As can be seen, the amplifier's transfer characteristics are approximately linear within the exemplary normalized input voltage range of 0 to .37 volts marked "A" in Fig. 2. The transfer characteristic of the amplifier for input voltages above the range marked "A" are compressively nonlinear. Each increase in voltage input yields a progressively smaller than linear increase in current output.

The signal-amplitude errors induced by FET 40 nonlinearities make uncompensated FET amplifiers unsuited for use in precision analog amplifier applications. One approach to reducing these signalamplitude errors is to constrain the maximum linear output signal to be a relatively small fraction of the total available output signal. For example, in the circuit illustrated in Figs. 1 and 2, the amplifier can be constrained to operate within the operating region marked "A" with a consequent improvement in linearity. This approach, however, severely limits 50 amplifier dynamic range.

A contrasting prior art method to improve linearity over a large signal range is to increase the amplifier's static bias current. By this method, larger output current swings can be accommodated. This method, however, increases device power dissipation and device size. The increased device size in turn increases the fabrication costs and decreases the achievable bandwidth due to larger interelement capacitances.

Still another prior art method of reducing amplifier error is through the use of feedback techniques. In feedback amplifiers, the output signal is sensed and fed back to the input so that linearity errors are canceled to a degree. While feedback amplifiers having very high precision can be designed, they have several limitations which make them unsuited for high precision wideband signal processing. For example, adequate damping becomes difficult to obtain as the frequency increases. Also, small inherent time delays around the feedback loop can cause the output to be out of phase with the input. Phase distortion can thus be introduced which increases with frequency, thereby further degrading amplifier precision and ultimately causing instability.

An example of a current feedback technique applied to the amplifier of Fig. 1 is shown by the dashed resistors connected between the source of each input transistor and current source lo1. These resistors provide a bias voltage to their respective sources which varies with the output current. This varying bias voltage serves to counteract somewhat the nonlinearities inherent in the FETs, thereby reducing signal-amplitude distortion.

The resistive feedback technique illustrated in Fig. 1 also reduces the gain of the amplifier stage. To compensate for this gain loss, more amplifier stages are required. Alternatively, the gain reduction can be minimized by decreasing the size of the feedback resistors and correspondingly increasing the device size and bias current of the transistors. This solution, however, leads to the increased power dissipation and fabrication cost problems noted above.

Accordingly, a need remains for an FET amplifier having improved linearity and gain.

Prior art transistor amplifier circuits seeking greater linearity and increased gain include that described in US-A-4146844 (Quinn) which shows a bipolar differential cascode amplifier compensated with a linearizing stage. GB-A-2013444 (Siemens) discloses a differential amplifier comprising the same linearising circuit as shown in the Quinn reference. In GB-A-2013444 it is suggested to realize the differential amplifier using either bipolar transistors or FETs. Also known in the prior art is the wideband differential amplifier shown in US-A-4075 574, issued to the assignee of the present invention.

# SUMMARY OF THE INVENTION

One object of the present invention is to provide a high precision, high frequency FET amplifier in which transistor nonlinearity is compensated

55

45

10

15

20

25

30

35

40

45

50

without sacrificing gain and without introducing phase distortion.

Another object of the present invention is to increase greatly the fraction of the maximum output signal from an FET amplifier which is usable with good linearity.

Still another object of the present invention is to extend the dynamic range of an FET transconductance amplifier without reducing its gain.

Yet another object of the present invention is to increase the achievable gain-bandwidth product of an FET transconductance amplifier.

Still another object of the present invention is to provide a stable, high-precision amplifier constructed of few parts and being simple in operation.

The above objects are met by the present invention as claimed in claim 1.

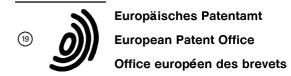

A differential linearization stage is coupled to a FET cascode amplifier to sense the drain current nonlinearities of its input stage and to develop a corresponding error signal. This error signal is injected into the output stage of the amplifier to cancel its distortion. The linearization stage serves the further purpose of increasing amplifier gain.

The main amplifier comprises an input stage including a first source-coupled pair of field effect transistors which receive at their bases a differential input signal. The respective sources of a second pair of field effect transistors in an output stage of such differential amplifier are coupled to the drains of the first pair of transistors in a cascode arrangement. The drains of the second pair of transistors provide the differential amplifier outputs. The gates of the second pair of transistors are biased by biasing voltage sources.

The linearizing circuit connected across the second amplifier transistors includes a third pair of field effect transistors in source-coupled arrangement with their respective bases driven by the drains of the first amplifier transistors. The gates of such third transistors are also connected to biasing current sources. The drains of the linearizing third transistors are cross connected to the drains of the second output transistors, thereby injecting a compensating error signal into each differential output node to provide cancellation of nonlinearities.

The foregoing and additional objects, features and advantages of the present invention will be more readily apparent from the following detailed description of a preferred embodiment thereof, which proceeds with reference to the accompanying drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS.

55

Fig. 1 is a schematic diagram of a prior art uncompensated FET cascode amplifier.

Fig. 2 is a graph illustrating the transfer characteristics of the uncompensated amplifier of Fig. 1.

Fig. 3 is a schematic diagram of a compensated differential FET cascode amplifier circuit according to the present invention.

Fig. 4 is a graph illustrating the transfer characteristics of the compensated amplifier of Fig. 3.

#### DETAILED DESCRIPTION

With reference to Fig. 3, the compensated amplifier circuit 10 of the present invention includes a differential pair of cascode amplifiers 12a and 12b, a linearizing circuit 14, a differential voltage input 16 and a differential current output 18. Since the topology of the differential circuitry is symmetrical and the operation of each half correspondingly identical, the following discussion focuses on the left hand side of the circuit. It should be understood, however, that the discussion is equally applicable to the right hand side of the circuit.

Cascode amplifier 12a includes input and output FETs 20a, 22a connected in cascode arrangement, with the drain of FET 20a connected to the source of FET 22a. The source of FET 20a and the source of corresponding FET 20b are connected to a source 24 of current lo1. The gate of input FET 20a is driven by an input 26a of differential voltage input 16. The gate of output FET 22a is driven by a source 28a of bias voltage Vga and the drain of such FET is connected to a current output node 30a of the differential current output 18.

The linearizing stage 14 includes two FETs, 32a and 32b, connected in a common source arrangement. The common sources of FETs 32a and 32b are connected to a common source 34 of bias current Io3. The gate of FET 32a is connected to the drain of input FET 20a and is also connected to a source 36a of D.C. bias current I2a. The drain of linearizing FET 32a is cross-connected to the drain of output FET 22b at current output node 30b.

Circuit 10 operates as follows. If transistors 22a and 22b have the same geometry as transistors 20a and 20b, and ignoring for a moment current sources 36a and 36b, then the voltage Vs2 across the sources of transistors 22a and 22b is equal to the differential input voltage Vin applied at differential voltage input 16. With bias current sources 36a and 36b added, Vs2 increases nonlinearly faster than Vin (expansive nonlinearity). This voltage is applied across the gates of the common source linearization stage 14. Consequently, the drain current Id3 of linearizing stage transistors 32a and 32b also increases faster than linearly with Vin. Due to the nonlinearity of the input transistors 20, the output current Id2 of differential cascode amplifier transistors 22 (which equals Iout in topologies with-

10

15

20

25

30

35

out the linearization stage) increases slower than linearly with  $V_{in}$  (compressive nonlinearity).

The output signal current  $I_{out}$  is the sum of the differential cascode amplifier's output current (Id2) plus the linearization stage's output current (Id3). By properly proportioning the device sizes and bias currents, the opposite nonlinearities of Id2 and Id3 with respect to V<sub>in</sub> cancel over most of the available output signal range, thereby causing  $I_{out}$  to vary linearly with V<sub>in</sub>. This linearization is achieved without the reduced gain, increased static bias current, increased heat, reduced bandwidth and increased phase distortion problems associated with prior art techniques.

Fig. 4 is a graph illustrating the transfer characteristics of the compensated amplifier of Fig. 3 with the output current Iout normalized to Io1. As can be seen by comparison with the graph of Fig. 2, the present invention provides a substantial expansion of the amplifier's linear operating region. The dashed line shows the departure of the normalized compensated transfer characteristic from an ideal linear transfer characteristic, on the expanded vertical scale on the left. While the uncompensated amplifier is approximately linear over the 0 to .37 volt input range marked "A" in Fig. 2, the compensated amplifier is approximately linear over the 0 to .61 volt input range marked "B" in Fig. 4, an increase in linear dynamic range of over sixty percent.

The results illustrated in Fig. 4 were obtained using equal geometry gallium arsenide. transistors 20, 22 and 32 having pinch off voltages of 2.0 volts and zero bias drain currents of 4.0 milliamperes. The gate bias voltage Vga was set to 5.0 volts and current sources lo1, l2a and lo3 were set to 2.0 ma., 0.4 ma. and 1.6 ma. respectively. The biasing sources on the right hand side of the circuit were set to correspondingly identical valves.

The equal geometry of the six field effect transistors in the illustrative embodiment is not essential to the invention, but rather is used for expository convenience. In alternative embodiments, nonidentical geometries can be employed if corresponding adjustments are made to the biasing 45 sources.

The present invention provides a number of benefits beyond increased linearity. The addition of the linearizing stage 14 increases both the overall transconductance gain and the available signal output current. Linearizing stage 14 also reduces the output admittance (due initially to the drain-to-gate capacitance of output transistors 22a and 22b), thereby increasing the achievable gain-bandwidth product.

The present invention can be practiced using both metal and metal oxide FETs. Gallium arsenide MESFETs with Schottky barrier gates can be used advantageously for very high frequency operation.

In the illustrated embodiment, linearizing transistors 32 are used to model the distortion producing mechanisms of transistors 20 and 22. Accordingly, the characteristics of transistors 20, 22 and 32 should be as evenly matched as possible.

All transistors in the present invention can be connected directly to one another without any intermediate components. Since the circuit topology is so simple, such configuration is ideally adaptable to integrated circuit fabrication. Of course, discrete transistors may alternatively be employed. However, it is easier to match components and insure high performance with integrated circuit construction.

Having described and illustrated the principles of my invention with reference to a preferred embodiment, it should be apparent to those skilled in the art that the invention can be modified in arrangement and detail without departing from such principles. I claim all modifications coming within the scope of the following claims.

### Claims

**1.** A field effect transistor amplifier circuit **(10)** comprising:

a pair of input field effect transistors (20) with their gates connected across a source of input signal voltage (Vin) and a pair of output field effect transistors (22) with their sources connected to the outputs of the input transistors and their outputs connected to output terminals (30) to provide an output signal current, the input and output field effect transistors forming a cascode differential amplifier circuit,

a pair of linearizing field effect transistors (32) connected as a nonlinear common source amplifier stage with their gates connected to the sources of different ones of said output transistors (22) and their drains connected to the outputs of the opposite ones of said output transistors to which their gates are connected; and

a pair of sources (**36**) of D.C. bias current connected directly to the gates of said linearizing transistors so that the linearising amplifier provides greater linearity and increased gain to the differential cascode amplifier circuit.

- 2. An amplifier circuit in accordance with claim 1 in which the input transistors (20) are connected as a common source amplifier stage.

- **3.** An amplifier in accordance with claim 2 in which the output transistors (**22**) are connected as a common gate amplifier stage.

50

55

15

20

25

30

35

40

45

50

- 4. An amplifier circuit in accordance with claim 1 in which the bias current and the linearizing transistors (32) are of the proper size so that the nonlinearities of the drain currents of said output transistors and of said linearizing transistors cancel each other over a substantial portion of the output current signal range.

- An amplifier circuit in accordance with claim 1 in which said field effect transistors are made 10 of gallium arsenide semiconductor material.

- **6.** An amplifier circuit in accordance with claim 1 in which the transistors are directly connected together without using additional circuit components including feedback transistors.

- An amplifier circuit in accordance with claim 1 in which said field effect transistors are of the MES type with Schottky barrier gates.

- 8. An amplifier circuit in accordance with claim 1 in which said field effect transistors are fabricated as an integrated circuit.

# Patentansprüche

**1.** Feldeffekttransistorverstärkerschaltung (10), umfassend:

ein Paar Eingangsfeldeffekttransistoren (20), die mit ihren Gates über eine Quelle oder Source einer Eingangssignalspannung (V<sub>in</sub>) geschaltet sind, und ein Paar Ausgangsfeldeffekttransistoren (22), die mit ihren Sourcen mit den Ausgängen der Eingangstransistoren verbunden sind und mit ihren Ausgängen mit Ausgangsanschlüssen (30) verbunden sind, um einen Ausgangssignalstrom zu erstellen, wobei die Ein- und Ausgangsfeldeffekttransistoren eine Kaskodendifferentialverstärkerschaltung bilden,

ein Paar linearisierender Feldeffekttransistoren (32), die als nichtlineare Verstärkerstufe mit gemeinsamer Source geschaltet sind, wobei ihre Gates mit den Sourcen verschiedener der Ausgangstransistoren (22) verbunden sind und ihre Drains mit den Ausgängen der entgegengesetzten Ausgangstransistoren verbunden sind, mit denen ihre Gates verbunden sind; und

ein Paar Quellen (36) für Vorspannungsgleichstrom, die direkt mit den Gates der linearisierenden Transistoren verbunden sind, so daß der linearisierende Verstärker größere Linearität und erhöhte Verstärkung an die Differentialkaskodenverstärkerschaltung legt.

- Verstärkerschaltung nach Anspruch 1, worin die Eingangstransistoren (20) als Verstärkerstufe mit gemeinsamer Source geschaltet sind.

- **3.** Verstärker nach Anspruch 2, worin die Ausgangstransistoren (22) als Verstärkerstufe mit gemeinsamem Gate geschaltet sind.

- 4. Verstärkerschaltung nach Anspruch 1, worin der Vorspannungsstrom und die linearisierenden Transistoren (32) die richtige Größe haben, so daß die Nichtlinearitäten der Drainströme der Ausgangstransistoren und der linearisierenden Transistoren einander über einen wesentlichen Abschnitt des Ausgangsstromsignalbereiches aufheben.

- 5. Verstärkerschaltung nach Anspruch 1, worin die Feldeffekttransistoren aus Galliumarsenid-Halbleitermaterial sind.

- Verstärkerschaltung nach Anspruch 1, worin die Transistoren direkt miteinander verbunden sind, ohne Verwendung zusätzlicher Schaltungskomponenten einschließlich Rückkopplungstransistoren.

- Verstärkerschaltung nach Anspruch 1, worin die Feldeffekttransistoren des MES-Typs mit Schottky-Sperrgates sind.

- 8. Verstärkerschaltung nach Anspruch 1, worin die Feldeffekttransistoren als integrierte Schaltung hergestellt sind.

# **Revendications**

- 1. Circuit amplificateur à transistors à effet de champ (10), comprenant :

- une paire de transistors à effet de champ d'entrée (20) avec leurs grilles reliées aux bornes d'une source de tension de signal d'entrée V<sub>in</sub> et une paire de transistors à effet de champ de sortie (22) avec leur sources reliées aux sorties des transistors d'entrée et leurs sorties reliées à des bornes de sortie (30) pour fournir un courant de signal de sortie, les transistors à effet de champ d'entrée et de sortie formant un amplificateur différentiel cascode;

- une paire de transistors à effet de champ de linéarisation (32) montés en étage amplificateur non linéaire à source commune avec leurs grilles reliées aux sources de transistors différents parmi lesdits transistors de sortie (22) et leurs drains reliés aux sorties des transistors opposés

desdits transistors de sortie auxquels leurs grilles sont reliées; et

- une paire de sources (36) de courant continu de polarisation reliées directement aux grilles desdits transistors de linéarisation de manière que l'amplificateur de linéarisation assure une plus grande linéarité et un gain accru au circuit amplificateur cascode différentiel.

- 2. Circuit amplificateur selon la revendication 1, dans lequel les transistors d'entrée (20) sont montés en étage amplificateur à source commune.

- 3. Circuit amplificateur selon la revendication 2, dans lequel les transistors de sortie (22) sont montés en étage amplificateur à grille commune.

- Circuit amplificateur selon la revendication 1, dans lequel l'intensité du courant de polarisation et la taille des transistors de linéarisation (32) sont telles que les non-linéarités des courants de drain desdits transistors de sortie et desdits transistors de linéarisation s'annulent mutuellement dans une grande partie de la gamme d'intensités du signal de sortie en courant.

- 30

35

40

45

50

55

- 5. Circuit amplificateur selon la revendication 1, dans lequel lesdits transistors à effet de champ sont en matière semiconductrice constituée par de l'arséniure de gallium.

- 6. Circuit amplificateur selon la revendication 1, dans lequel les transistors sont reliés directement entre eux, sans utiliser de composants de circuit supplémentaires, notamment de transistors de contre-réaction.

- circuit amplificateur selon la revendication 1, dans lequel lesdits transistors à effet de champ sont du type MESFET, avec des grilles à barrière de Schottky.

- Circuit amplificateur selon la revendication 1, dans lequel lesdits transistors à effet de champ sont fabriqués sous la forme d'un circuit intégré.

10

5

15

20