(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4837481号 (P4837481)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int. Cl. F. I.

**HO3L 7/093 (2006.01)** HO3L 7/08

請求項の数 10 (全 9 頁)

(21) 出願番号 特願2006-210442 (P2006-210442)

(22) 出願日 平成18年8月2日 (2006.8.2) (65) 公開番号 特開2007-43712 (P2007-43712A) (43) 公開日 平成19年2月15日 (2007.2.15)

審査請求日 平成21年7月29日 (2009. 7. 29)

(31) 優先権主張番号 11/195267

(32) 優先日 平成17年8月2日 (2005.8.2)

(33) 優先権主張国 米国 (US)

||(73)特許権者 500587067

$\mathbf{E}$

アギア システムズ インコーポレーテッ

ĸ

アメリカ合衆国. 18109 ペンシルヴァニア, アレンタウン, アメリカン パー

クウェイ エヌイー 1110

|(74)代理人 100094112

弁理士 岡部 讓

|(74)代理人 100064447

弁理士 岡部 正夫

(74)代理人 100085176

弁理士 加藤 伸晃

(74)代理人 100096943

弁理士 臼井 伸一

最終頁に続く

(54) 【発明の名称】スケーリングされた制動コンデンサを有する位相ロック・ループ

## (57)【特許請求の範囲】

## 【請求項1】

集積回路(IC)であって、

位相ロック・ループ(PLL)を含み、前記位相ロック・ループが、

電流制御発振器(ICO)(303)と、

ループ・フィルタ出力ノード(207)を有するループ・フィルタとを含み、前記ループ・フィルタは、ループ・フィルタ抵抗器(210)と、前記ループ・フィルタ抵抗器へループ・フィルタ中間ノード(208)で接続するループ・フィルタ制動コンデンサ(212)とを含み、さらに、

電流ミラー出力ノード(305)を有する電流ミラーを含む電流スケーリング回路(301a、301b、302a、302b)を含み、前記電流スケーリング回路は、前記ループ・フィルタ出力ノードと前記ループ・フィルタ中間ノードとに接続して、前記電流ミラー出力ノードで前記ICOへ印加される電流ミラー出力電流を発生する、集積回路(IC)。

#### 【請求項2】

前記電流スケーリング回路が、

入力電流を発生するよう接続された入力トランジスタ(302a)と、

前記入力電流のミラーとしてミラー電流を発生するよう接続されたミラー・トランジスタ(302b)と、

前記入力トランジスタ(302a)から前記入力電流を受信するよう接続された第1の

トランジスタ(301a)と、

前記ミラー・トランジスタから前記ミラー電流の一部を受信するよう接続された第2のトランジスタ(301b)とを含み、前記第1及び第2のトランジスタのゲートが、前記ループ・フィルタ中間ノード及び前記ループ・フィルタ出力ノードにそれぞれ接続され、前記ゲートに印加された電圧を前記ICOへ印加される前記電流ミラー出力電流に変換する、請求項1に記載の集積回路。

#### 【請求項3】

前記電流ミラーが、前記ループ・フィルタ制動コンデンサの両端の電圧降下に比例する前記ミラー電流を発生するように構成される、請求項1に記載の集積回路。

#### 【請求項4】

前記電流スケーリング回路が、前記ループ・フィルタ制動コンデンサの有効容量を増大させるように構成される、請求項1に記載の集積回路。

#### 【請求項5】

前記電流スケーリング回路が、前記PLLループ・ダイナミクスに影響を与えることなく前記ループ・フィルタ制動コンデンサの有効容量を増大させるように構成される、請求項1に記載の集積回路。

#### 【請求項6】

前記ループ・フィルタ出力ノードは、前記ICOの入力に直接接続されていない、請求項1に記載の集積回路。

## 【請求項7】

前記第1及び第2のトランジスタは整合トランジスタである、請求項2に記載の集積回路。

#### 【請求項8】

前記電流ミラーは、前記第2のトランジスタの電流から前記第1のトランジスタの電流を減じる、請求項2に記載の集積回路。

#### 【請求項9】

前記ミラー電流の別の部分が前記ICOへ印加されるように、前記<u>電流ミラー</u>の利得は 1よりも小さい、請求項2に記載の集積回路。

#### 【請求項10】

前記ミラー・トランジスタは、前記電流ミラー出力ノードで前記第2のトランジスタへ接続される、請求項2に記載の集積回路。

# 【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は一般に、位相 / 遅延ロック・ループ回路、および詳細には、スケーリング係数 を有するチャージ・ポンプ位相ロック・ループ回路に関する。

## 【背景技術】

#### [0002]

通信システム、クロック回復回路、周波数乗算器、およびデータ同期回路など、電子回路内のきわめて重要なタイミング要件のために、ローカルに発生されたクロック信号は、基準波形に正確に同期されなければならない。位相ロック・ループ(PLL)は、ローカルに発生された信号の位相または周波数を「ロック時間」と呼ばれる期間内に入力「基準」信号の位相および周波数に一致するように調節するフィードバック制御システムである。一般に、PLLは、低周波オフチップ・クロックを取り除き、高周波オンチップ・クロックを発生するために使用される。遅延ロック・ループ(DLL)は、DLLが入力基準信号に関して規定の遅延で出力信号を発生するように設計されるという点で、PLLに似ている。

#### [0003]

典型的には、PLLは、3つの構成要素、すなわち、位相/周波数検出器(PFD)、ループ・フィルタ(LF)、および制御発振器(CO)を有する。COは電圧制御(VC)

10

20

30

40

10

20

30

40

50

O)でも、電流制御(ICO)でもよい。COの出力はPFDにフィードバックされる。出力信号の周波数は、通常、入力基準周波数の倍数である。上記3つの構成要素のほかに、PLLはまた、PFDの信号に応じてフィルタのコンデンサの充電量を操作する、チャージ・ポンプ(CP)を含むこともできる。言い換えれば、PFDはCPによって電荷出力を増加するあるいは減少する信号を発生し、CPは電荷をLFコンデンサに付加するあるいはそれから除去する。COは、COに入力される電圧または電流に比例する周波数を有する出力クロックを発生する。

#### [0004]

PFD/CPは、位相(または周波数)エラーを電流に変換し、出力周波数を入力周波数にロックすることを可能にする。LFは、PFD/CP出力電流に作用して、COで周波数出力を制御する、電圧を発生する。CO出力は、プログラム可能分周器(デバイス)を通じて供給され、次いで、PFDに戻される。PLLは、そのフィードバック特性のため、PFDにあるエラーがゼロになるまでCOを駆動する。

## [0005]

ループ・フィルタは、1つの抵抗器および2つのコンデンサ、すなわち制動コンデンサ と寄生バイパス・コンデンサ、を含むことができる。制動コンデンサの容量が増大すると 、集積回路の面積が増大する。面積を増大させることなく、有効制動コンデンサ容量を増 大させることが望ましい。コンデンサはPLL内で大きな面積を占めるので、制動コンデ ンサC1の面積、および自動較正ループに関連するコンデンサの面積を縮小することによ って、チャージ・ポンプPLLの面積を縮小することができる。コンデンサのサイズを縮 小する1つの方法は、集積コンデンサを作るために使用されるデバイスのゲート酸化膜を 縮小することであり、この方法によって、はるかに小さな面積で所望の容量を得ることが できる。しかし、より薄いゲート酸化膜は、ゲート漏洩電流を引き起こし、その結果、静 位相オフセットが発生する。静位相オフセットを軽減する技法は、米国特許第60437 15号に記載されているが、この方法は面積を増大させ、それによって面積を縮小すると いう目的を無にする。第2の方法は、より小さな容量値を使用するもので、それによって より小さな面積を達成するが、これは、PLLのループ・ダイナミクスに変化を引き起こ す可能性があり、その閉ループ性能に悪い影響を及ぼす。第3の方法では、2つのチャー ジ・ポンプ、すなわち、ループ・フィルタ電圧の比例成分用ポンプおよび積分成分用ポン プを使用する。しかし、第2のチャージ・ポンプと、2つの別々のコンデンサ電圧を合計 するのに必要な回路との面積は、コンデンサのサイズを縮小することによって得られるど んな節約も無効にする。これまで見てきたように、知られる方法には、望ましくない結果 なしにチャージ・ポンプPLLの面積を縮小するという目的を達成するものは1つもない 。したがって、従来技術の改善が必要である。

【特許文献1】米国特許第6043715号

## 【発明の開示】

【発明が解決しようとする課題】

#### [0006]

チャージ・ポンプPLLの面積を縮小するために、フィードバック・ループのループ・ダイナミクスおよび安定性に普通なら及ぼすような影響を及ぼすことなく、ループ・フィルタを実施するために使用されるコンデンサの面積を縮小することができる。

#### 【課題を解決するための手段】

## [0007]

これは、チャージ・ポンプPLL内で、ループ・フィルタ電圧の比例成分と積分成分を分離し、積分成分が実際に使用されたものよりはるかに大きな値の容量によって影響されたかのように見えるようにするために別の回路を追加することによって、達成することができる。一態様では、電流ミラーを使用して、総ループ・フィルタ電圧からループ・フィルタ電圧の積分成分の一部を減じることができる。次いで、差動信号を使用して、チャージ・ポンプPLL内の発振器を駆動する。他の態様では、第3の積分器または自動較正ループを使用して、発振器の中央周波数を設定する。

本開示のこれらおよび他の特徴、目的および利点は、同様の番号は同様の部品を意味する添付の図面に関連する以下の詳細な説明からより容易に理解されることができる。

【発明を実施するための最良の形態】

#### [0008]

下記の議論は以下の記号を使用する。

Rは、「ゼロ・レジスタ」としても知られる外部ループ・フィルタ抵抗器を意味する。 C<sub>1</sub>は、「制動コンデンサ」と呼ばれることもある、外部ループ・フィルタ内の2つの コンデンサの1つを意味する。このコンデンサは、2つのデバイス・ピンの間のR、また は1つのデバイス・ピンとグラウンドの間のRに、直列に接続される。

#### [0009]

$C_2$  は、「リップル・バイパス・コンデンサ」と呼ばれることもある、外部ループ・フィルタ内の第 2 のコンデンサを意味する。このコンデンサは、 R と  $C_1$  の直列回路に並列に接続される。  $C_1$  は常に  $C_2$  より、一般に係数 1 0 0 だけ、大きい。

#### [0010]

Ipは、デバイスによって供給されるチャージ・ポンプ電流を意味し、ときどきユーザによって調節可能である。

は、電圧信号の位相を意味する。

。は、位相検出器によって出力される位相エラーである。

は、この用途で使用される電流ミラーのミラーリング・パラメータを意味する。

sは、ラプラス変換変数を意味する。

K<sub>vco</sub>は、電圧制御水晶発振器(VCXO)または電圧制御発振器(VCO)の小記号利得を意味する。

Fは、信号の周波数を意味する。

Vは、信号の電圧を意味する。

MおよびNは、出力信号の周波数が入力信号の周波数の分数か倍数のいずれかとすれば、入力およびフィードバック・パスに入れられてよい任意選択の入力、出力またはフィードバック分周器(デバイス)の分周比を意味する。分周が必要ない場合は、分周比は1でよい。

## [0011]

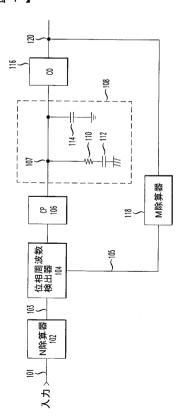

図1は、直列に接続されたPFD104、CP106、ループ・フィルタ108、およびCO116を含むPLLを示す。N分周器(デバイス)102は、PFD104の1つの入力に結合される。M分周器(デバイス)118は、CO116の出力に結合され、M分周器(デバイス)118の出力は、PFD104の別の入力に結合され、フィードバックされる。入力信号101はN分周器(デバイス)102に入れられ、N分周器(デバイス)102は入力信号101を係数Nで割って入力基準信号103を供給する。Nで割られた入力基準信号103は、PFD104に入力される。PLL100の出力信号120は、M分周器(デバイス)118は、出力信号120を係数Mで割って入力フィードバック信号105を発生する。

## [0012]

PFD104は、入力基準信号103とフィードバック信号105の周波数および位相を比較し、CP106に対して位相エラー信号を発生する。位相エラー信号は、現在の出力信号の位相(たとえば、フィードバック信号105の位相)と、あるべき信号の位相(たとえば入力基準信号101の位相)との位相差である。位相エラー信号は、CP106から、電流値(たとえば電荷の流れ)に関するループ・フィルタ108に供給される。ループ・フィルタ108は、ある決まった周波数の電流信号は通し、その他の周波数の電流信号は減衰させることによって、CP106からの電流をフィルタし、制御信号を発生して、実際の制御信号と標準動作信号または最適信号との差に基づいて出力信号120の位相を調整する。制御信号は、CO116に供給されて出力信号120に出力位相を提供し、この出力信号120をループが入力基準周波数101の基準位相でロックする。

## [0013]

50

10

20

~~

制御電圧107は、2つの部分、すなわち、比例成分である抵抗器110にかかる電圧と、ループ・フィルタ電圧の積分成分であるコンデンサ112にかかる電圧とからなる。コンデンサ114は、チャージ・ポンプからの高周波数信号を減衰させるために使用される小さなコンデンサであり、したがって、これらの信号は、CO116によって位相ジッタに調整されない。CO116は、出力位相を有する出力信号120を発生し、ループは、この出力位相を入力基準周波数101の基準位相でロックする。

#### [0014]

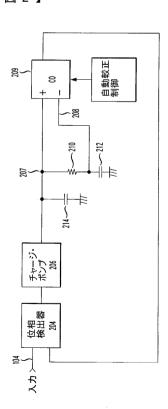

図2は、本明細書中で開示された原理に従って設計されたPLL200のプロック図である。PLL200は、位相/周波数検出器(PFD)204、チャージ・ポンプ(CP)206、リップル・バイパス・コンデンサ214、ループ・フィルタ抵抗器210およびループ・フィルタ・コンデンサ212を有する。フィルタ制御電圧207は、抵抗器210およびコンデンサ212にかかる電圧の合計である。ループ・フィルタ・コンデンサ212の容量は、(図1の)コンデンサ112の容量に比較して小さい。ループ・フィルタ・コンデンサ212から取られた電圧208は、制御発振器(CO)209に入力として供給される。

#### [0015]

CO209は、3つの入力を受け取ることに留意されたい。第1の入力は、CO209の中央周波数を設定するために使用される自動較正回路215からである。第2の入力は、以下では公称低利得入力と称される制御電圧207に接続される。第3の入力(電圧208)は、逆低利得入力と称され、それに小信号利得(K<sub>vco</sub>)が関連しており、この小信号利得の値は、符号が反対で、大きさが公称低利得入力より低い。

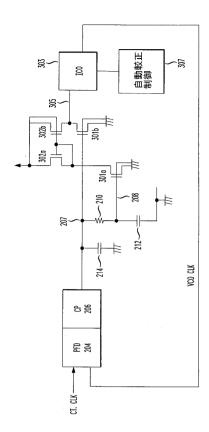

#### [ 0 0 1 6 ]

図3は、積分(制動)コンデンサ212のサイズを縮小するスケーリング係数を有する 電流ミラーを組み込むように構成された例示的チャージ・ポンプPLLのブロック図であ る。この回路を使用してCO209に逆低利得入力を実装することによって、コンデンサ 2 1 2 は、図 1 の P L L 1 0 0 からのループ・ダイナミクスを変えることなく、その値を 低減されることができ、さらに通常型の2入力発振器が使用されることができるようにな る。整合トランジスタ301aおよび301bは、フィルタ電圧207および208を電 流に変換する。トランジスタ301aからの電流は、1より小さい利得を有する電流ミラ ーを使用することによってトランジスタ301bの電流から減じられ、それによって、ト ランジスタ301bによって発生される電流がトランジスタ302bの電流より大きいこ とを保証する。電流305は、電流制御発振器(ICO)303への低利得入力として使 用され、電流制御発振器(ICO)303の高利得入力は、自動較正制御ループ307に よって制御される。電流ミラー利得( )は、1より小さくなければならないことに留意 されたい。トランジスタ302bによって発生された新しい電流は、ICOに入力される 低利得に入力される電流を低減し、それによってその「積分成分」を低減し、「比例成分 」は低減しない。この低減された積分成分は、制動コンデンサ212を、そのサイズを増 大させることなく、スケーリングすることに等しい効果を生み出す。したがって、制動コ ンデンサ212のサイズは、PLLのループ・ダイナミクスを変更することなく、電流ミ ラー204で発生された電流の大きさに応じてスケール・ダウンされることができる。

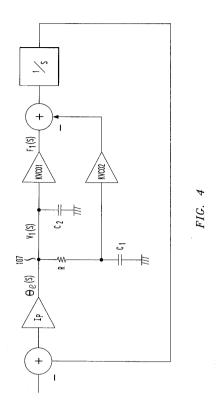

# [0017]

図4は、図3に示されたPLLの数学的小信号モデルを示す。ループ・フィルタは、直列に接続された抵抗器RおよびコンデンサC<sub>1</sub>を有する。第2コンデンサC<sub>2</sub>は、RC低域通過フィルタに並列に接続される。フィルタZ<sub>5</sub>のインピーダンスは、したがって、

#### 【数1】

$$Z(s) = \left(R + \frac{1}{sC1}\right) \left(\frac{1}{sC2}\right) \tag{1}$$

10

20

30

または同等に、

【数2】

$$Z(s) = \left(\frac{1 + sRC1}{sC1(1 + sC2)}\right) \tag{1}$$

これは電圧 V 1 ( s )を

【数3】

$$V1(s) = Ip\theta e(s) \left( \frac{1 + sRC1}{sC1(1 + sC2)} \right)$$

(2)

(6)

として与える。

さらに図4を参照して、

【数4】

$$V2(s) = \left(\frac{Ip\theta e(s)}{sC1(1+sRC2)}\right)$$

(3)

$$F1(s) = \left(\frac{Kvco*Ip\theta e(s)(1+sRC1)}{sC1(1+sRC2)}\right)$$

(4)

【数5】

$$F2(s) = \alpha \left( \frac{Kvco * Ip\theta e(s)}{sC1(1+sRC2)} \right)$$

(5)

図4から、

$$F 3 (s) = F 1 (s) - F 2 (s)$$

(6 a)

または同等に、

【数6】

$$F3(s) = Kvco*Ip\theta e(s)*\left(\frac{(1+sRC1)-\alpha}{sC1(1+sRC2)}\right)$$

(6b)

であることが分かる。

F3(s)は、積分成分と比例成分の組合せとして理解されてよいことに留意されたい。

#### 【数7】

$$F3(s) = \left(\frac{Kvco*Ip\theta e(s)}{sC1(1+sRC2)}\right)[(1-\alpha)+sRC1]$$

(6c)

#### [0018]

がゼロと1の間の値を有するように選択された場合、積分成分(1-)は、比例成分(s R C  $_1$ )に影響を及ぼすことなく低減されることができる。その結果として、コンデンサ C  $_1$  の容量を効果的に増大させることができる。これによって、変更前と同じループ・ダイナミクスを維持しながら、 C  $_1$  の面積を縮小することができる。

## [0019]

当業者は、本発明の範囲から逸脱することなく、本明細書中に示された部品の詳細、材料、および構成に様々な変更を加えることができる。そのような変更は全て、添付の特許請求の範囲の範囲内に当然あるものと解釈されるべきである。

## 【図面の簡単な説明】

#### [0020]

【図1】位相ロック・ループ(PLL)の概略図である。

【図2】電流ミラー・フィード・バック・ループを示す、本明細書中に開示の実施形態によるPLLの概略図である。

【図3】図2の電流ミラーの詳細図を示す、PLLの別の概略図である。

【図4】開示された原理の小信号の数学的モデルの図である。

【図1】

# 【図2】

10

【図3】

【図4】

## フロントページの続き

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 ウィリアム ビー.ウィルソン

アメリカ合衆国 18062 ペンシルヴァニア,マカンギー,ブリアーウッド ドライヴ 49

6 4

# 審査官 上田 智志

(56)参考文献 米国特許第06344772(US,B1)

特開2005-005932(JP,A)

特開平09-312565(JP,A)

米国特許第06437615(US,B1)

(58)調査した分野(Int.CI., DB名)

H03L 7/06-7/23