# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 109842297 B (45) 授权公告日 2021.10.15

- (21) 申请号 201910052887.1

- (22)申请日 2017.02.15

- (65) 同一申请的已公布的文献号 申请公布号 CN 109842297 A

- (43) 申请公布日 2019.06.04

- (62) 分案原申请数据 201710081704.X 2017.02.15

- (73) 专利权人 华为技术有限公司 地址 518129 广东省深圳市龙岗区坂田华 为总部办公楼

- (72) 发明人 汪家轲 陈亮 邹鹏

- (51) Int.CI.

**HO2M** 3/158 (2006.01) **HO2M** 1/32 (2007.01)

#### (56) 对比文件

- CN 104035467 A, 2014.09.10

- CN 1286520 A,2001.03.07

- US 2015372595 A1,2015.12.24

- WO 2011107976 A1,2011.09.09

审查员 魏劲夫

权利要求书1页 说明书6页 附图4页

#### (54) 发明名称

一种输出电压调节装置及方法

#### (57) 摘要

本申请涉及电源管理领域,公开了一种输出电压调节装置及方法,用以实现快速调压,且抑制输出电压调节时的过冲或过跌的现象。该装置包括电压调节电路、控制电路、功率级电路、滤波网络和反馈网络。反馈网络,用于采集滤波网络得到的调节后的输出电压,向控制电路的反馈电压节点输出反馈电压;电压调节电路的输出端连接于反馈网络的输出端和控制电路的反馈电压节点之间,电压调节电路用于调节所述反馈电压;控制电路的输出端与功率级电路的输入端相连,用于接收所述反馈电压,并控制所述功率级电路中功率管的开启与关闭;滤波网络用于对所述功率级电路中功率管的开启与关闭;滤波网络用于对所述功率级电路的输出电压进行滤波,得到所述调工程,

1.一种输出电压调节装置,其特征在于,包括:电压调节电路、控制电路、功率级电路、滤波网络和反馈网络;

所述反馈网络的输入端与所述滤波网络的输出端相连,用于采集所述滤波网络得到的调节后的输出电压,所述反馈网络的输出端与所述控制电路的反馈电压节点相连,用于向所述控制电路的反馈电压节点输出反馈电压;

所述电压调节电路的输出端连接于所述反馈网络的输出端和所述控制电路的反馈电压节点之间,所述电压调节电路的输出端用于输出电流调节信号以调节所述反馈电压;

所述控制电路的输出端与所述功率级电路的输入端相连,用于接收所述反馈电压,并控制所述功率级电路中功率管的开启与关闭:

所述滤波网络的输入端与所述功率级电路的输出端相连,用于对所述功率级电路的输出电压进行滤波,得到所述调节后的输出电压,其中,所述电压调节电路包括:

数模转换电路,用于接收用于表征电压调节的数字信号,根据所述数字信号生成第一基准电压信号,并将所述第一基准电压信号传给电压电流转换电路;

所述电压电流转换电路,用于接收所述第一基准电压信号,将所述第一基准电压信号 转换为所述电流调节信号,并将所述电流调节信号传给所述反馈电压节点。

- 2.如权利要求1所述的输出电压调节装置,其特征在于,所述电流调节信号用于向所述 反馈电压节点注入或抽取电流,从而调节所述反馈电压。

- 3. 如权利要求1所述的输出电压调节装置,其特征在于,所述反馈网络包括第一反馈电阻和第二反馈电阻,所述反馈网络的输出端位于所述第一反馈电阻和所述第二反馈电阻之间。

- 4. 如权利要求1至3中任一项所述的输出电压调节装置,其特征在于,所述控制电路用于输出占空比方波信号,以控制所述功率级电路中所述功率管的开启与关闭。

- 5.如权利要求4所述的输出电压调节装置,其特征在于,所述控制电路包括:误差放大器和比较器;

所述误差放大器,用于将所述反馈网络输出的反馈电压与第二基准电压信号进行误差 放大以输出误差放大信号;

所述比较器,用于比较所述误差放大信号与三角波信号,并输出所述占空比方波信号。

- 6.如权利要求5所述的输出电压调节装置,其特征在于,所述功率级电路包括上功率管和下功率管;所述占空比方波信号用于控制所述上功率管和下功率管的开启与关闭。

- 7.如权利要求6所述的输出电压调节装置,其特征在于,所述功率级电路还包括:分别连接在所述上功率管和所述下功率管的输入端的驱动级,所述驱动级用于接收所述占空比方波信号。

- 8. 如权利要求1至3中任一项所述的输出电压调节装置,其特征在于,所述滤波网络包括电感和电容。

# 一种输出电压调节装置及方法

### 技术领域

[0001] 本申请实施例涉及电源管理领域,尤其涉及一种输出电压调节装置及方法。

#### 背景技术

[0002] 近年来,如智能手机、平板电脑等消费类电子产品呈现快速发展的趋势,电源管理集成电路(Power Management IC,PMIC)是用来管理消费类电子产品主机系统的电源设备,PMIC具有集成度高、转换效率高、成本低等优点。集成电压调制器(Intergraded voltage regulator,IVR)是PMIC的重要组成部分,随着消费类电子产品的快速更新换代,其对IVR性能的要求也越来越高。为了节省系统功耗,需要根据后级负载对IVR的输出电压进行实时的、动态的、快速的调节。

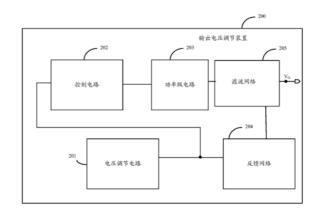

[0003] 现有技术中,一般通过快速调节基准电压或快速调节反馈电阻的值来实现输出电压的快速调节,但是这些方案,通常会带来输出电压的过冲或过跌或毛刺。例如,如图1所示,给出了通过快速调节基准电压来实现输出电压的快速调节时的波形。当基准电压 $V_{REF}$ 从 $V_{REF1}$ 经过 $t_{ramp}$ 时长跳变到 $V_{REF2}$ 时,输出电压 $V_{0}$ 也随之从 $V_{01}$ 快速上升,但是 $V_{0}$ 的波形往往会出现过冲,即图1中标示的 $\triangle V$ ,经过一段恢复时间 $t_{setting}$ 之后, $V_{0}$ 稳定到目标值 $V_{02}$ 。而且 $t_{ramp}$ 时间越短,过冲 $\triangle V$ 就越大,恢复时间 $t_{setting}$ 就越长。反之,当 $V_{REF}$ 从上往下跳变时, $V_{0}$ 也会出现相应的过跌,过跌之后也需要一段恢复时间才能达到稳定值。

[0004] 综上,现有技术实现快速调节IVR的输出电压的方案,容易带来输出电压过冲、过 跌或毛刺的现象,且过冲或过跌的恢复时间很长,对系统性能造成一定的影响。

#### 发明内容

[0005] 本申请实施例提供一种输出电压调节装置及方法,用以实现快速调压,且解决输出电压调节过程中出现的过冲或过跌的问题。

[0006] 本申请实施例提供的具体技术方案如下:

[0007] 第一方面,提供一种输出电压调节装置,在输出电压调节装置中加入电压调节电路,在固定控制电路中的基准电压 $V_{REF}$ 不变的基础上,通过电压调节电路改变控制电路中的反馈电压 $V_{FB}$ 节点的电流来实现快速调节输出电压 $V_{0}$ ,这样,不但能够实现输出电压的快速调节,还能够抑制输出电压调节过程中出现的过冲、过跌或毛刺的现象,并且有效缩短调节到达稳定电压的时间。

[0008] 在一个可能的设计中,该装置包括电压调节电路、控制电路、功率级电路、滤波网络和反馈网络,所述电压调节电路、所述控制电路、所述功率级电路、所述滤波网络和所述反馈网络组成环路,其中:所述反馈网络的输入端与所述滤波网络的输出端相连,用于采集所述滤波网络的输出电压V<sub>0</sub>,所述反馈网络的输出端与所述控制电路的反馈电压节点相连,用于向所述控制电路的反馈电压节点输出反馈电压;所述电压调节电路的输出端连接于所述反馈网络的输出端和所述控制电路的反馈电压节点之间,用于调节所述反馈电压节点的电流I;所述控制电路的输出端与所述功率级电路的输入端相连,用于根据所述反馈电

压节点的电流I,调节所述功率级电路的输出占空比;所述滤波网络的输入端与所述功率级电路的输出端相连,用于对所述功率级电路的输出占空比进行滤波,得到调节后的输出电压 $V_0$ 。通过调节反馈节点的电流来实现快速调节输出电压 $V_0$ 对输出电压的过冲或过跌有很好的抑制作用,更快速稳定的实现调压作用。

[0009] 在一个可能的设计中,所述电压调节电路包括:数模转换电路和电压电流转换电路,其中,所述数模转换电路用于接收用于表征电压调节的数字信号,根据所述数字信号生成第一基准电压信号,并将所述第一基准电压信号传给所述电压电流转换电路;所述电压电流转换电路用于接收所述第一基准电压信号,将所述第一基准电压信号转换为电流调节信号,并将所述电流调节信号传给所述反馈电压节点。

[0010] 在一个可能的设计中,所述电压调节电路还用于:根据所述电流调节信号向所述 反馈电压节点注入电流或接收所述反馈电压节点流出的电流。

[0011] 在一个可能的设计中,所述反馈网络包括第一反馈电阻 $R_{f1}$ 和第二反馈电阻 $R_{f2}$ ,所述反馈网络的输出点位于所述第一反馈电阻和所述第二反馈电阻之间;所述输出电压 $V_0$ 与所述反馈电压节点的电流I之间满足以下关系: $V_0 = V_{REF} * (1 + R_{f1}/R_{f2}) + I * R_{f1}$ , $V_{REF}$ 为所述控制电路获取的第二基准电压信号。

[0012] 第二方面,提供一种输出电压调节方法,在固定控制电路中的基准电压 $V_{REF}$ 不变的基础上,通过改变控制电路中的反馈电压 $V_{FB}$ 节点的电流来实现快速调节输出电压 $V_0$ ,这样,不但能够实现输出电压的快速调节,还能够抑制输出电压调节过程中出现的过冲、过跌或毛刺的现象,并且从调节到达稳定电压的时间有效缩短。

[0013] 在一个可能的设计中,通过反馈网络采集滤波网络的输出电压 $V_0$ ,并向控制电路的反馈电压节点输出反馈电压;通过电压调节电路调节所述反馈电压节点的电流I;通过控制电路根据所述反馈电压节点的电流I,调节所述功率级电路的输出占空比;通过滤波网络对所述功率级电路的输出占空比进行滤波,得到调节后的输出电压 $V_0$ 。通过调节反馈节点的电流来实现快速调节输出电压 $V_0$ 对输出电压的过冲、过跌或毛刺有很好的抑制作用,更快速稳定的实现调压作用。

[0014] 在一个可能的设计中,在通过电压调节电路调节所述反馈电压节点的电流I时,具体为:接收用于表征电压调节的数字信号,根据所述数字信号生成第一基准电压信号,将所述第一基准电压信号转换为电流调节信号,并将所述电流调节信号传给所述反馈电压节点。

[0015] 在一个可能的设计中,在通过电压调节电路调节所述反馈电压节点的电流I时,具体为:根据所述电流调节信号向所述反馈电压节点注入电流或接收所述反馈电压节点流出的电流。

[0016] 在一个可能的设计中,所述输出电压 $V_0$ 与所述反馈电压节点的电流I之间满足以下关系: $V_0 = V_{REF}*(1 + R_{f1}/R_{f2}) + I * R_{f1}$ ;其中, $V_{REF}$ 为所述控制电路获取的第二基准电压信号, $R_{f1}$ 为所述反馈网络中的第一反馈电阻; $R_{f2}$ 为所述反馈网络中的第二反馈电阻,所述反馈网络的输出点位于所述第一反馈电阻和所述第二反馈电阻之间。

[0017] 第三方面,提供一种电源,包括如上述第一方面或第一方面任一种可能的设计中 所述的输出电压调节装置。

## 附图说明

[0018] 图1为现有技术中输出电压快速调节时的波形示意图;

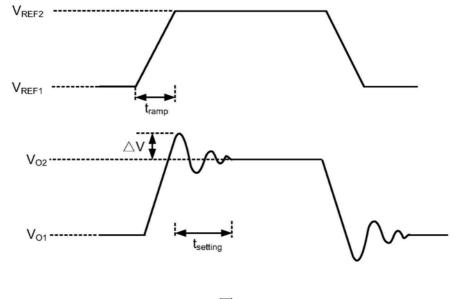

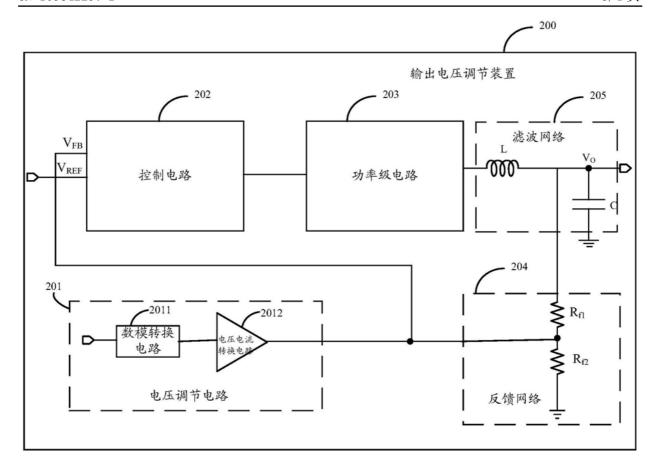

[0019] 图2为本申请实施例中输出电压调节装置结构示意图之一;

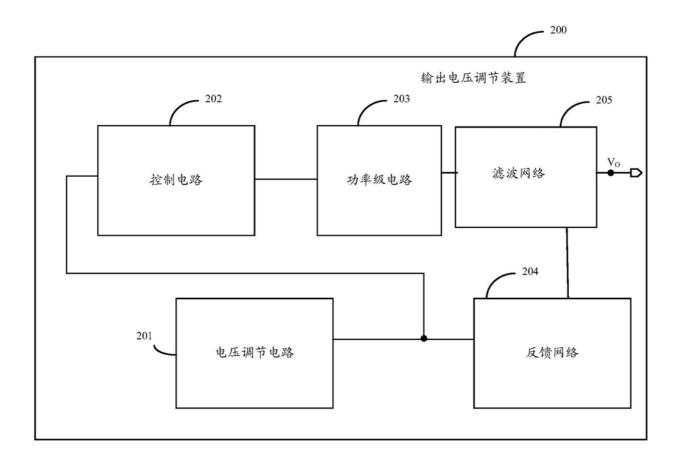

[0020] 图3为本申请实施例中输出电压调节装置结构示意图之二;

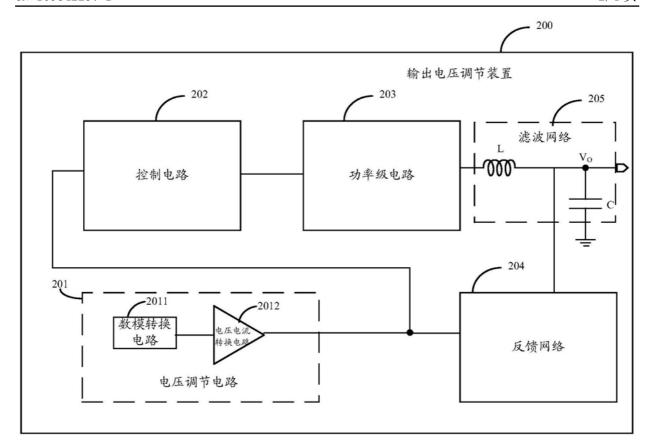

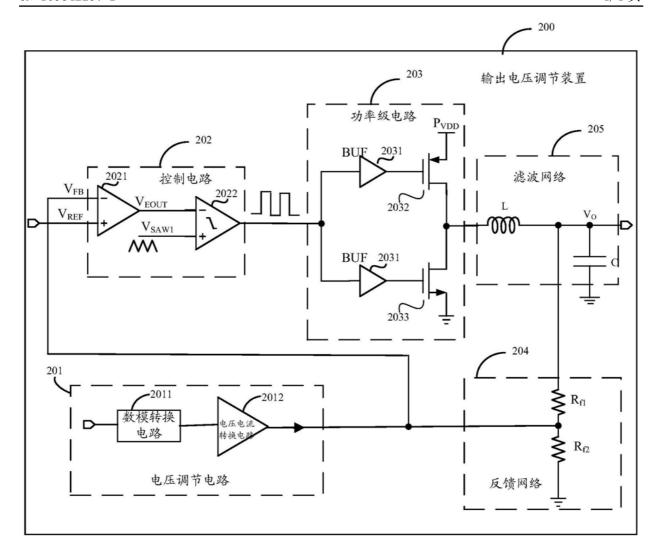

[0021] 图4为本申请实施例中输出电压调节装置结构示意图之三;

[0022] 图5为本申请实施例中输出电压调节装置结构示意图之四。

### 具体实施方式

[0023] 下面将结合附图,对本申请实施例进行详细描述。

[0024] 本申请实施例的调压方案的基本思想是,在输出电压调节装置中加入电压调节电路,在固定控制电路中的基准电压 $V_{REF}$ 不变的基础上,通过电压调节电路改变控制电路中的反馈电压 $V_{FB}$ 节点的电流来实现快速调节输出电压 $V_{0}$ ,这样,不但能够实现输出电压的快速调节,还能够抑制输出电压调节过程中出现的过冲、过跌或毛刺的现象,并且从调节到达稳定电压的时间有效缩短。

[0025] 本申请实施例可应用于直流到直流转换器 (DC to DC Converter, DC-DC) 相关的快速调压设备,也可以应用到交流到直流转换器 (AC to DC Converter, AC-DC) 相关的快速调压设备,本申请实施例中的输出电压调节装置可以是IVR,或者是任意能够应用本申请实施例的方法实现快速调节输出电压的装置。

[0026] 下面对本申请实施例提供的输出电压调节装置和方法做详细说明。

[0027] 如图2所示,输出电压调节装置200包括:电压调节电路201、控制电路202、功率级电路203、反馈网络204和滤波网络205,电压调节电路201、控制电路202、功率级电路203、反馈网络204和滤波网络205组成环路。具体的各个电路之间的连接关系是:反馈网络204的输入端与滤波网络205的输出端相连;反馈网络204的输出端与控制电路202相连,具体与控制电路202的反馈电压节点相连;电压调节电路201的输出端连接于反馈网络204的输出端和控制电路202的反馈电压节点之间;控制电路202的输出端与功率级电路203的输入端相连;功率级电路203的输出端与滤波网络205相连,可选的,滤波网络中包括电感L和电容C。滤波网络205的输出端的输出信号即为输出电压V<sub>0</sub>。

[0028] 其中:

[0029] 反馈网络204用于采集滤波网络205的输出电压 $V_0$ ,以及用于向控制电路202的反馈电压节点输出反馈电压;

[0030] 电压调节电路201用于调节控制电路202的反馈电压节点的电流 I;

[0031] 控制电路202用于根据控制电路202的反馈电压节点的电流I,调节功率级电路203的输出占空比;

[0032] 滤波网络205用于对功率级电路203的输出占空比进行滤波,得到调节后的输出电压 $V_0$ 。

[0033] 可选的,电压调节电路201通过向控制电路202的反馈电压节点注入电流或者抽取电流,可以调节控制电路202的反馈电压节点的电流I,而当反馈电压节点的电流I改变时,能够影响输出电压 $V_0$ 的值,本申请实施例就是通过快速调节反馈电压节点的电流I来实现快速调节输出电压 $V_0$ 的。其中,抽取电流表示接收流出的电流,也就是电压调节电路201接

收反馈电压节点流出的电流。

[0034] 可选的,如图3所示,电压调节电路201包括:数模转换电路2011和电压电流转换电路2012。

[0035] 其中,当输出电压V<sub>0</sub>需要调节时,电压调节电路201会生成电压调节的数字信号,该数字信号表征调节电压的幅度等信息。数模转换电路2011用于接收用于表征电压调节的该数字信号,根据该数字信号生成第一基准电压信号,并将第一基准电压信号传给电压电流转换电路2012;

[0036] 电压电流转换电路2012,用于接收该第一基准电压信号,将该第一基准电压信号转换为电流调节信号,并将电流调节信号传给反馈电压节点。电流调节信号包括向反馈电压节点注入电流或者抽取电流。可选的,电压调节电路201还用于根据电流调节信号向反馈电压节点注入电流或接收反馈电压节点流出的电流。

[0037] 可选的,电压调节的数字信号为调压的码值S<7:0>。当输出电压 $V_0$ 需要从 $V_0$ 1调节到 $V_0$ 2时,电压调节电路201会根据要求生成调压的码值S<7:0>,调压的码值S<7:0>经过数模转换电路(即DAC)2011之后,被转换成第一基准电压信号,可以记作 $V_{REF}$ DAC, $V_{REF}$ DAC传输至电压电流转换电路2012,被转换成电流调节信号,电流调节信号可以用于向反馈电压节点注入电流或抽取电流,具体是注入电流还是抽取电流需要根据调压的码值S<7:0>来确定。

[0038] 可选的,如图4所示,反馈网络204包括第一反馈电阻 $R_{f1}$ 和第二反馈电阻 $R_{f2}$ ,反馈网络204的输出点位于第一反馈电阻 $R_{f1}$ 和第二反馈电阻 $R_{f2}$ 之间。

[0039] 其中,输出电压V<sub>0</sub>与反馈电压节点的电流I之间满足以下关系:

[0040]  $V_0 = V_{REF} * (1 + R_{f1}/R_{f2}) + I * R_{f1}$   $\vec{\Xi}(1)$ ;

[0041] 其中,V<sub>REF</sub>控制电路202获取的第二基准电压信号。

[0042] 如图5所示,一种可能的实施方式中,控制电路202和功率级电路203的具体结构如下所述。

[0043] 控制电路202中包括误差放大器2021、比较器2022,功率级电路203包括:驱动级BUF2031、上功率管2032和下功率管2033。

[0044] 其中,误差放大器2021将反馈网络204输出的反馈电压 $V_{FB}$ ,与上述第二基准电压信号 $V_{REF}$ 进行误差放大后,输出 $V_{EAOUT}$ 信号, $V_{EAOUT}$ 信号与三角波信号 $V_{SAW1}$ 经过比较器2022后,输出占空比方波信号,占空比方波信号用于控制功率级电路203的开启与关闭。其中,电压调节电路201通过电流调节信号向反馈电压节点注入或抽取电流,从而调节反馈电压 $V_{FB}$ 的值。

[0045] 功率级电路203根据比较器2022输出的占空比方波信号进行功率管的开启与关闭,进一步将PVDD的能量作为输出电压 $V_0$ 输出。

[0046] 反馈电压V<sub>FB</sub>节点的基尔霍夫方程为:

$[0047] \qquad \frac{v_{FB}}{R_{f2}} + I - \frac{v_{O} - v_{FB}}{R_{f1}} = 0 \qquad \qquad \vec{\lesssim} \ (\ 2\ )$

[0048] 对于误差放大器2021的两个输入端V<sub>FB</sub>节点和V<sub>FFE</sub>来说,具有关系:

[0049]  $V_{FB} = V_{RFF}$ 。 式(3)

[0050] 由式(2)和式(3)可以推导出上述式(1)。

[0051] 其中,当电流I的方向是流入反馈电压 $V_{FB}$ 节点时,I值取正,当电流I的方向是流出

反馈电压 $V_{FB}$ 节点时,I值取负,即向反馈电压 $V_{FB}$ 节点抽取大小为I的绝对值的电流,式(1)中, $V_0$ 的值等于 $V_{REF}$ \*(1+ $R_{f1}/R_{f2}$ )减去I的绝对值与 $R_{f1}$ 的乘积。

[0052] 电压调节电路201包括硬件芯片。上述硬件芯片可以是专用集成电路 (application-specific integrated circuit, ASIC),可编程逻辑器件 (programmable logic device, PLD) 或其组合。上述PLD可以是复杂可编程逻辑器件 (complex programmable logic device, CPLD),现场可编程逻辑门阵列 (field-programmable gate array, FPGA),通用阵列逻辑 (generic array logic, GAL) 或其任意组合。

[0053] 基于与图2所示的输出电压调节装置同一发明构思,本申请实施例还提供一种输出电压调节方法,在固定控制电路中的基准电压 $V_{REF}$ 不变的基础上,通过改变控制电路中的反馈电压 $V_{FB}$ 节点的电流来实现快速调节输出电压 $V_0$ ,这样,不但能够实现输出电压的快速调节,还能够抑制输出电压调节过程中出现的过冲、过跌或毛刺的现象,并且从调节到达稳定电压的时间有效缩短。

[0054] 具体方法如下:通过反馈网络采集功率级电路的输出电压 $V_0$ ,并向控制电路的反馈电压节点输出反馈电压,通过电压调节电路调节所述反馈电压节点的电流I,以改变所述输出反馈电压,通过控制电路根据所述反馈电压节点的电流I,调节所述功率级电路的输出电压 $V_0$ 。通过调节反馈节点的电流来实现快速调节输出电压 $V_0$ 对输出电压的过冲、过跌或毛刺有很好的抑制作用,更快速稳定的实现调压作用。

[0055] 可选的,在通过电压调节电路调节所述反馈电压节点的电流I时,具体为:接收用于表征电压调节的数字信号,根据所述数字信号生成第一基准电压信号,将所述第一基准电压信号转换为电流调节信号,并将所述电流调节信号传给所述反馈电压节点。

[0056] 可选的,在通过电压调节电路调节所述反馈电压节点的电流I时,具体为:根据所述电流调节信号向所述反馈电压节点注入电流或接收所述反馈电压节点流出的电流。

[0057] 可选的,所述输出电压 $V_0$ 与所述反馈电压节点的电流I之间满足以下关系: $V_0 = V_{REF}*(1+R_{f1}/R_{f2})+I*R_{f1};$ 其中, $V_{REF}$ 为所述控制电路获取的第二基准电压信号, $R_{f1}$ 为所述反馈网络中的第一反馈电阻; $R_{f2}$ 为所述反馈网络中的第二反馈电阻,所述反馈网络的输出点位于所述第一反馈电阻和所述第二反馈电阻之间。

[0058] 本领域内的技术人员应明白,本申请的实施例可提供为方法、系统、或计算机程序产品。因此,本申请可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本申请可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。

[0059] 本申请是参照根据本申请实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0060] 这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指

令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0061] 这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0062] 尽管已描述了本申请的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本申请范围的所有变更和修改。

[0063] 显然,本领域的技术人员可以对本申请实施例进行各种改动和变型而不脱离本申请实施例的精神和范围。这样,倘若本申请实施例的这些修改和变型属于本申请权利要求及其等同技术的范围之内,则本申请也意图包含这些改动和变型在内。

图1

图2

图3

图4

图5