| UK Patent Application (1                                                                                                                                 | 9) GB (11) 2570789 (13) A (13) A (13) Date of A Publication 07.08.2019                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) Application No:       1820512.0         (22) Date of Filing:       17.12.2018                                                                       | (51) INT CL:<br><i>H01L 51/52</i> (2006.01)<br><i>H01L 27/32</i> (2006.01)<br><i>H01L 51/50</i> (2006.01)<br><i>H05B 33/08</i> (2006.01)                    |

| (30) Priority Data:<br>(31) <b>20170182048</b> (32) <b>28.12.2017</b> (33) KR                                                                            | (56) Documents Cited:<br>EP 3480851 A1 WO 2019/071759 A1<br>US 20170110530 A1 US 20160240810 A1<br>US 20160155790 A1 US 20160126304 A1<br>US 20140239262 A1 |

| <ul> <li>(71) Applicant(s):</li> <li>LG Display Co., Ltd.</li> <li>128, Yeoui-daero, Yeongdeungpo-gu, Seoul 07336,</li> <li>Republic of Korea</li> </ul> | (58) Field of Search:<br>INT CL <b>H01L</b><br>Other: <b>EPODOC, WPI</b>                                                                                    |

| (72) Inventor(s):<br>Sungmoo Kim<br>Jinah Kwak<br>Sejin KIm                                                                                              |                                                                                                                                                             |

| (74) Agent and/or Address for Service:<br>Carpmaels & Ransford LLP<br>One Southampton Row, London, WC1B 5HA,<br>United Kingdom                           |                                                                                                                                                             |

(54) Title of the Invention: Electroluminescence display apparatus Abstract Title: Protecting an emissive layer of an electroluminescent display with a further ink-jet deposited layer before applying metallic layers

(57) A electroluminescence (e.g. Organic light emitting diode (OLED)) display apparatus includes a substrate 100 including an active area AA where pixels disposed; a circuit element layer 200 disposed on the substrate 100; first electrode 310 and auxiliary electrode 320 disposed, spaced apart, on the circuit element layer 200; a first light emitting layer 510 disposed on the first electrode 310; a buffer layer 520 disposed on the first light emitting layer 510; a further layer 530 disposed on the buffer layer 520 and the auxiliary electrode 320; and a second electrode 600 disposed on the further layer 530. The further layer 530 is preferably formed of a metal and may act as an electron injection layer (EIL). The buffer layer 520 is preferably formed by an inkjet process, such that the first light emitting layer 510 is not damaged by the deposition of the metallic further layer 530.

FIG. 1 Related art

FIG. 2

1/6

FIG. 3

2/6

FIG. 4

3/6

FIG. 5B

# FIG. 6

FIG. 7

FIG. 8

FIG. 9

#### **ELECTROLUMINESCENCE DISPLAY APPARATUS**

#### **BACKGROUND**

# **Field of the Invention**

**[0001]** The present disclosure relates to an electroluminescence display apparatus, and more particularly, to an electroluminescence display apparatus for preventing the performance, efficiency, and lifetime of a device from being reduced.

#### **Discussion of the Related Art**

**[0002]** Electroluminescence display apparatuses are apparatuses where a light emitting layer is provided between two electrodes and emits light with an electric field between the two electrodes, thereby displaying an image.

**[0003]** The light emitting layer may be formed of an organic material or an inorganic material such as a quantum dot. In the light emitting layer, an exciton is generated by a combination of an electron and a hole, and when the exciton is shifted from an excited state to a ground state, light is emitted.

[0004] Hereinafter, a related art electroluminescence display apparatus will be described with reference to the drawing.

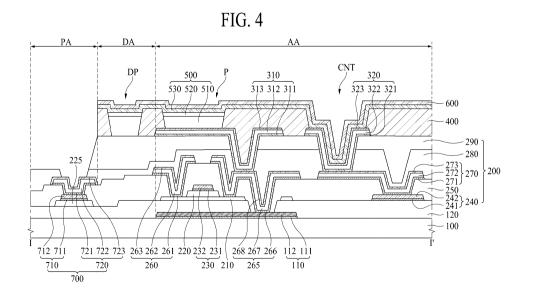

**[0005]** FIG. 1 is a schematic cross-sectional view of a related art electroluminescence display apparatus.

**[0006]** As seen in FIG. 1, the related art electroluminescence display apparatus includes a substrate 10, a circuit element layer 20, a first electrode 30, an auxiliary electrode 35, a bank 40, a light emitting layer 50, and a second electrode 60.

**[0007]** The circuit element layer 20 is provided on the substrate 10. Various signal lines, a thin film transistor (TFT), a capacitor, and a planarization layer are provided in the circuit element layer 20.

**[0008]** The first electrode 30 is provided on the circuit element layer 20. The first electrode 30 is patterned in each of a plurality of pixels and acts as an anode of the related art electroluminescence display apparatus.

**[0009]** The auxiliary electrode 35 is spaced apart from the first electrode 30 and is provided on the circuit element layer 20. The auxiliary electrode 35 is electrically connected to the second electrode 60 and reduces a resistance of the second electrode 60.

**[0010]** The bank 40 is provided in a matrix structure to define an emission area.

**[0011]** The light emitting layer 50 is provided on the first electrode 30 and includes a first light emitting layer 51 and a second light emitting layer 52. The first light emitting layer 51 and the second light emitting layer 52 cooperate to emit light when an electric field is applied across both layers. If the first light emitting layer 51 is not present in an area light will not be emitted from this area.

**[0012]** The first light emitting layer 51 is formed in the emission area defined by the bank 40 through an inkjet process. Layers deposited by an inkjet process may have a thickness in the centre that is smaller than a thickness at the edge. This may lead to a curved upper surface on an inkjet deposited layer or feature. As an example, an inkjet deposited layer, or feature, deposited on a flat surface within an area defined by a bank may have a lower height from the centre of the area compared to the height

at the bank. The first light emitting layer 51 includes a hole injecting layer (HIL), a hole transporting layer (HTL), and a light emitting material layer (EML).

**[0013]** The second light emitting layer 52 is formed all over the substrate 10 through a deposition process. The second light emitting layer 52 includes an electron transporting layer (ETL) and an electron injecting layer (EIL).

[0014] The second electrode 60 is provided on the second light emitting layer

52. The second electrode 60 is provided as a common layer of a plurality of pixels and acts as a cathode of the related art electroluminescence display apparatus.

**[0015]** In the related art electroluminescence display apparatus, the ETL of the second light emitting layer 52 is formed of metal all over the substrate 10 through a deposition process, and thus, is provided on the auxiliary electrode 35 as well as the first electrode 30.

**[0016]** The ETL provided between the auxiliary electrode 35 and the second electrode 60 may be formed of a conductive material in order to electrically connect the auxiliary electrode 35 to the second electrode 60.

**[0017]** Moreover, in the related art electroluminescence display apparatus, since the ETL is formed through a deposition process on the EML which is formed through an inkjet process, an issue occurs at an interface between the EML and the ETL, causing a reduction in efficiency and lifetime of a device.

## **SUMMARY**

**[0018]** Accordingly, the present disclosure is directed to providing an electroluminescence display apparatus that substantially obviates one or more problems due to limitations and disadvantages of the related art.

**[0019]** An aspect of the present disclosure is directed to providing an electroluminescence display apparatus for preventing the performance, efficiency, and lifetime of a device from being reduced.

**[0020]** Additional advantages and features of the disclosure will be set forth in part in the description which follows and in part will become apparent to those having ordinary skill in the art upon examination of the following or may be learned from practice of the disclosure. The objectives and other advantages of the disclosure may be realized and attained by the structure particularly pointed out in the written description and claims hereof as well as the appended drawings.

**[0021]** To achieve these and other advantages and in accordance with the purpose of the disclosure, as embodied and broadly described herein, there is provided an electroluminescence display apparatus including a substrate including an active area where a plurality of pixels are provided, a circuit element layer disposed on the substrate, a first electrode disposed on the circuit element layer, an auxiliary electrode disposed on the circuit element layer, an auxiliary electrode, a first light emitting layer disposed on the first electrode, a buffer layer disposed on the first light emitting layer, a second light emitting layer disposed on the substrate and the auxiliary electrode, and a second electrode disposed on the second light emitting layer.

**[0022]** It is to be understood that both the foregoing general description and the following detailed description of the present disclosure are exemplary and explanatory and are intended to provide further explanation of the disclosure as claimed.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

**[0023]** The accompanying drawings, which are included to provide a further understanding of the disclosure and are incorporated in and constitute a part of this application, illustrate embodiments of the disclosure and together with the description serve to explain the principle of the disclosure. In the drawings:

FIG. 1 is a schematic cross-sectional view of a related art electroluminescence display apparatus;

FIG. 2 is a schematic plan view of an electroluminescence display apparatus according to an embodiment of the present disclosure;

FIG. 3 is a schematic plan view illustrating pixels in an active area and a dummy area of an electroluminescence display apparatus according to an embodiment of the present disclosure;

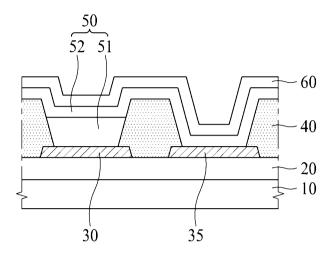

FIG. 4 is a cross-sectional view of an electroluminescence display apparatus according to an embodiment of the present disclosure and is a cross-sectional view taken along line I-I' of FIG. 3;

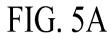

FIG. 5A is a schematic cross-sectional view illustrating an organic light emitting device of an electroluminescence display apparatus according to an embodiment of the present disclosure;

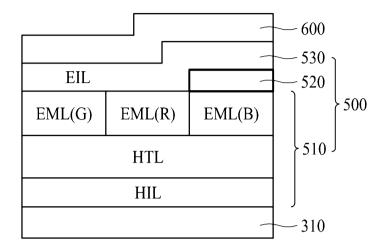

FIG. 5B is a schematic cross-sectional view illustrating an organic light emitting device of an electroluminescence display apparatus according to an embodiment of the present disclosure;

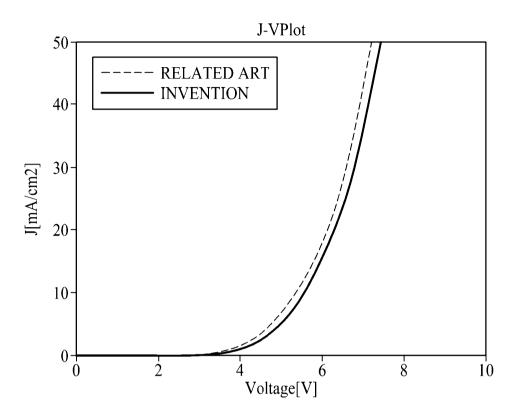

FIG. 6 is a graph comparing a driving voltage of a related art electroluminescence display apparatus with a driving voltage of an

electroluminescence display apparatus according to an embodiment of the present disclosure;

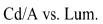

FIG. 7 is a graph comparing a current efficiency of a related art electroluminescence display apparatus with a current efficiency of an electroluminescence display apparatus according to an embodiment of the present disclosure;

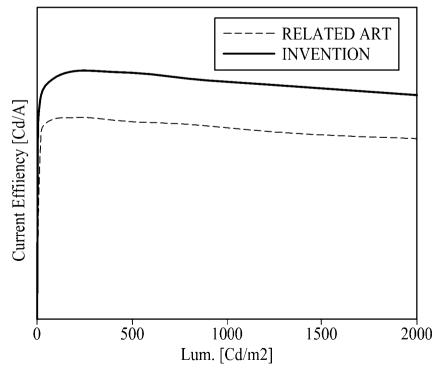

FIG. 8 is a graph comparing a lifetime of a related art electroluminescence display apparatus with a lifetime of an electroluminescence display apparatus according to an embodiment of the present disclosure; and

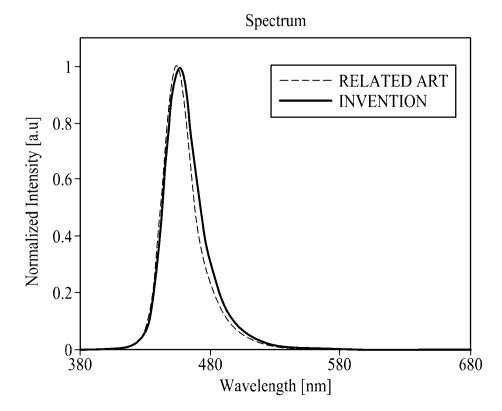

FIG. 9 is a graph comparing a normalized intensity of light of a related art electroluminescence display apparatus with a normalized intensity of light of an electroluminescence display apparatus according to an embodiment of the present disclosure with respect to a wavelength.

#### **DETAILED DESCRIPTION OF THE DISCLOSURE**

**[0024]** Reference will now be made in detail to the exemplary embodiments of the present disclosure, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

**[0025]** The terms described in the specification should be understood as follows.

**[0026]** As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. The terms "first" and "second" are for differentiating one element from the other element,

and these elements should not be limited by these terms. It will be further understood that the terms "comprises", "comprising,", "has", "having", "includes" and/or "including", when used herein, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. The term "at least one" should be understood as including any and all combinations of one or more of the associated listed items. For example, the meaning of "at least one of a first item, a second item, and a third item" denotes the combination of all items proposed from two or more of the first item, the second item, and the third item as well as the first item, the second item, or the third item. The term "on" should be construed as including a case where one element is formed at a top of another element and moreover a case where a third element is disposed therebetween.

**[0027]** Hereinafter, exemplary embodiments of an electroluminescence display apparatus according to the present disclosure will be described in detail with reference to the accompanying drawings. In the specification, in adding reference numerals for elements in each drawing, it should be noted that like reference numerals already used to denote like elements in other drawings are used for elements wherever possible. In the following description, when the detailed description of the relevant known function or configuration is determined to unnecessarily obscure the important point of the present disclosure, the detailed description will be omitted.

**[0028]** Hereinafter, exemplary embodiments of the present disclosure will be described in detail with reference to the accompanying drawings.

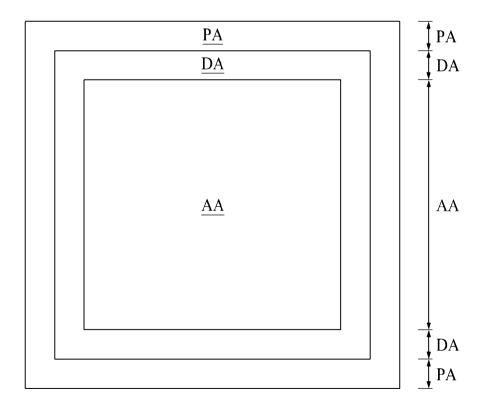

**[0029]** FIG. 2 is a schematic plan view of an electroluminescence display apparatus according to an embodiment of the present disclosure.

**[0030]** As seen in FIG. 2, the electroluminescence display apparatus according to an embodiment of the present disclosure may include an active area AA, a dummy area DA, and a pad area PA.

**[0031]** The active area AA may function as a display area which displays an image. A plurality of pixels may be provided in the active area AA, and an emission area may be provided in each of the plurality of pixels.

**[0032]** In detail, signal lines such as a gate line, a data line, a power line, and a reference line may be provided in each of the plurality of pixels provided in the active area AA. Also, a plurality of thin film transistors (TFTs) for switching transfers of signals applied through the signal lines may be provided in each pixel provided in the active area AA, and a light emitting device which is driven by the plurality of TFTs to emit light may be provided in each pixel.

**[0033]** The dummy area DA may be disposed to surround the active area AA. **[0034]** In detail, the dummy area DA may be disposed outside upper, lower, left, and right sides of the active area AA. A plurality of dummy pixels may be provided in the dummy area DA, and a dummy emission area may be provided in each of the plurality of dummy pixels. Since the dummy area DA is not the display area which displays an image, the dummy pixels provided in the dummy area DA may have a structure which differs from that of each pixel provided in the active area AA. For example, at least one of a signal line, a TFT, and a light emitting device may not be provided or may be incompletely provided in each of the dummy pixels provided in the dummy pixels provided in the dummy not be provided or may be incompletely provided in each of the dummy pixels provided in the dummy pixels provided in each of the dummy pixels provided in the dummy pixels provided in each of the dummy pixels provided in the dummy pixels provided pixels provided pixels pixels pixels pixels pixels pixel the dummy area DA, and thus, light may not be emitted from each dummy pixel provided in the dummy area DA. If light is emitted in the dummy area DA, the image quality of the electroluminescence display apparatus is degraded due to leakage light occurring in the dummy area DA.

**[0035]** The dummy area DA prevents a process error from occurring between a center and an outer portion of the active area AA. This will be described below in detail.

**[0036]** A plurality of stacking processes and a plurality of mask processes may be performed for forming the plurality of pixels in the active area AA. Each of the stacking processes may be a process of forming an insulation layer, a metal layer, or an organic layer through a physical deposition process, a chemical deposition process, a coating process, or an inkjet process, and each of the mask processes may be a process of patterning the insulation layer, the metal layer, or the organic layer formed through the stacking processes to have a certain shape by using a photolithography process known to those skilled in the art.

**[0037]** As described above, when the plurality of stacking processes and the plurality of mask processes are performed on the active area AA, there is a possibility that a process error occurs between the center and an edge of the active area AA due to process characteristic. For this reason, the dummy area DA may be provided in the edge of the active area AA, and thus, in a case where an error occurs, the error occurs in the dummy area DA without occurring in the active area AA.

**[0038]** Particularly, when a light emitting layer of the light emitting device is formed through an inkjet process, a difference in drying the light emitting layer may

occur between a center and an edge of a substrate, and in this case, if the dummy area DA is not provided, light emission between the center and the edge of the active area AA is not uniform.

**[0039]** Therefore, the dummy area DA may be provided outside the active area AA, and thus, in a case where the light emitting layer of the light emitting device is formed through the inkjet process, drying of the light emitting layer is not uniform between the active area AA and the dummy area DA, but drying of the light emitting layer is wholly uniform in the active area AA.

**[0040]** The pad area PA may be disposed outside the dummy area DA.

**[0041]** A circuit driver such as a gate driver or a data driver may be provided in the pad area PA. The circuit driver may be disposed outside at least one of upper, lower, left, and right sides of the dummy area DA. The circuit driver provided in the pad area PA may be connected to the circuit element disposed in the active area AA via the dummy area DA.

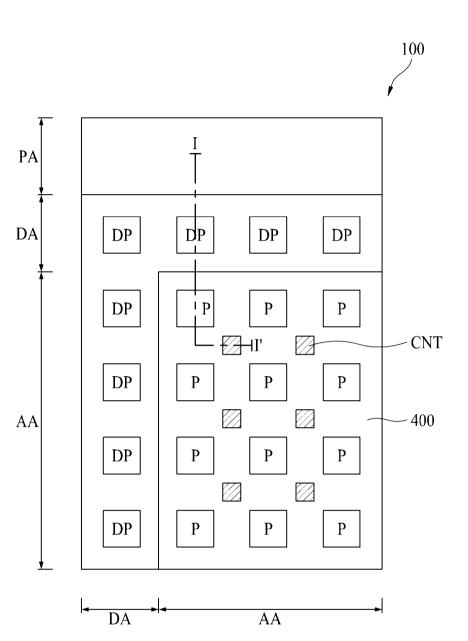

**[0042]** FIG. 3 is a schematic plan view illustrating pixels in an active area and a dummy area of an electroluminescence display apparatus according to an embodiment of the present disclosure.

**[0043]** As seen in FIG. 3, an active area AA may be provided on a substrate 100, and a dummy area DA may be provided outside the active area AA. A pad area PA may be provided outside the dummy area DA, and a plurality of pads may be disposed in the pad area PA. FIG. 3 schematically illustrates a left upper area of the substrate 100.

**[0044]** A plurality of pixels P may be provided in the active area AA. The plurality of pixels P may include a red pixel which emits red light, a green pixel which emits green light, and a blue pixel which emits blue light, but are not limited thereto.

**[0045]** In the plurality of pixels P, an emission area may be defined by a bank 400. The bank 400 may be disposed to surround an edge of each of the plurality of pixels P. In this case, a contact part CNT for electrically connecting a second electrode to an auxiliary electrode may be provided between adjacent pixels of the plurality of pixels P. The contact part CNT may be a region which exposes the auxiliary electrode by a hole provided in the bank 400.

**[0046]** The plurality of pixels P may be arranged in a matrix type as illustrated in FIG. 3, but are not limited thereto. In other embodiments, the plurality of pixels P may be arranged in various types known to those skilled in the art.

**[0047]** A plurality of dummy pixels DP may be provided in the dummy area DA. Some of the plurality of dummy pixels DP may be arranged in a column which differs from a column in which pixels P are arranged. Also, some of the plurality of dummy pixels DP may be arranged in a column that is same with the column in which pixels P are arranged.

**[0048]** FIG. 4 is a cross-sectional view of an electroluminescence display apparatus according to an embodiment of the present disclosure and is a cross-sectional view taken along line I-I' of FIG. 3, and each of FIG. 5A and FIG, 5B is a schematic cross-sectional view illustrating an organic light emitting device of the electroluminescence display apparatus according to an embodiment of the present disclosure.

**[0049]** As seen in FIG. 4, the electroluminescence display apparatus according to an embodiment of the present disclosure may include an active area AA, a dummy area DA, and a pad area PA, which are provided on a substrate 100.

**[0050]** The substrate 100 may be formed of glass, plastic, and/or the like, but is not limited thereto. The substrate 100 may be formed of a transparent material, or may be formed of an opaque material.

**[0051]** A light blocking layer 110 may be disposed on the substrate 100. The light blocking layer 110 may be additionally provided between the substrate 100 and an active layer 210 and may block the traveling of light to the active layer 210, thereby preventing the active layer 210 from being deteriorated. The light blocking layer 110 may include a lower light blocking layer 111 and an upper light blocking layer 112.

**[0052]** The lower light blocking layer 111 may be provided between the substrate 100 and the upper light blocking layer 112 and may enhance an adhesive force between the substrate 100 and the upper light blocking layer 112. Also, the lower light blocking layer 111 may protect a lower surface of the upper light blocking layer 112 from being corroded. Therefore, an oxidation rate of the lower light blocking layer 111 may be lower than that of the upper light blocking layer 112. That is, the lower light blocking layer 111 may be formed of a material which is stronger in corrosion resistance than a material of the upper light blocking layer 112. As described above, the lower light blocking layer 111 may act as an adhesive force enhancement layer or an anti-corrosion layer and may be formed of titanium (Ti) or an alloy (MoTi) of molybdenum (Mo) and Ti, but is not limited thereto.

**[0053]** The upper light blocking layer 112 may be provided on the lower light blocking layer 111. The upper light blocking layer 112 may be formed of copper (Cu) or aluminum (Al), which is low in resistance, but is not limited thereto. The upper light blocking layer 112 may be formed of a material which is relatively lower in resistance than the lower light blocking layer 111. The upper light blocking layer 112 may be connected to a drain electrode 265, and a thickness of the upper light blocking layer 111 so as to reduce a resistance of the drain electrode 265.

**[0054]** A buffer layer 120 may be disposed on the substrate 100. The buffer layer 120 may be disposed on the substrate 100 and the light blocking layer 110, for protecting a thin film transistor (TFT) from water penetrated through the substrate 100 vulnerable to penetration of water.

**[0055]** The electroluminescence display apparatus according to an embodiment of the present disclosure may be implemented as a top emission type where emitted light travels to an upper portion, and in this case, a material of the substrate 100 may use an opaque material as well as a transparent material.

**[0056]** Moreover, the electroluminescence display apparatus according to an embodiment of the present disclosure may be implemented as a bottom emission type where emitted light travels to a lower portion, and in this case, the material of the substrate 100 may use a transparent material.

[0057] A circuit element layer 200, a first electrode 310, an auxiliary electrode 320, a bank 400, a light emitting layer 500, and a second electrode 600 may be provided in the active area AA on the substrate 100.

**[0058]** The circuit element layer 200 may be provided on the substrate 100. The circuit element layer 200 may include the active layer 210, a gate insulation layer 220, a gate electrode 230, an auxiliary line 240, an interlayer insulation layer 250, a source electrode 260, the drain electrode 265, a connection line 270, a passivation layer 280, and a planarization layer 290.

**[0059]** The active layer 210 may be provided on the substrate 100. The active layer 210 may be formed of a silicon-based semiconductor material, an oxide semiconductor material, and/or the like, but is not limited thereto.

**[0060]** The gate insulation layer 220 may be provided on the active layer 210 and may insulate the active layer 210 from the gate electrode 230.

[0061] The gate electrode 230 may be provided on the gate insulation layer 220. The gate electrode 230 may include a lower gate electrode 231 and an upper gate electrode 232.

**[0062]** The lower gate electrode 231 may be provided between the gate insulation layer 220 and the upper gate electrode 232 and may enhance an adhesive force between the gate insulation layer 220 and the upper gate electrode 232. Also, the lower gate electrode 231 may protect a lower surface of the upper gate electrode 232 from being corroded. Therefore, an oxidation rate of the lower gate electrode 231 may be lower than that of the upper gate electrode 232. That is, the lower gate electrode 231 may be formed of a material which is stronger in corrosion resistance than a material of the upper gate electrode 232. As described above, the lower gate electrode 231 may act

as an adhesive force enhancement layer or an anti-corrosion layer and may be formed of Ti or an alloy (MoTi) of Mo and Ti, but is not limited thereto.

**[0063]** The upper gate electrode 232 may be provided on the lower gate electrode 231. The upper gate electrode 232 may be formed of Cu or Al, which is low in resistance, but is not limited thereto. The upper gate electrode 232 may be formed of a material which is relatively lower in resistance than the lower gate electrode 231. A thickness of the upper gate electrode 232 may be set thicker than that of the lower gate electrode 231 so as to reduce a resistance of the gate electrode 230.

**[0064]** The auxiliary line 240 may be disposed on the same layer as the gate electrode 230 and may be spaced apart from the gate electrode 230. The auxiliary line 240 may be formed simultaneously with the gate electrode 230 through the same process and may be formed of the same material as that of the gate electrode 230. The auxiliary line 240 may include a lower auxiliary line 241 and an upper auxiliary line 242. The lower auxiliary line 241 and the upper auxiliary line 242 may be formed of the same material as that of each of the lower gate electrode 231 and the upper gate electrode 232.

**[0065]** The auxiliary line 240 may be electrically connected to the auxiliary electrode 320 which will be described below. Since the auxiliary line 240 is electrically connected to the auxiliary electrode 320, a resistance of each of the auxiliary electrode 320 and the second electrode 600 may be reduced.

**[0066]** The interlayer insulation layer 250 may be provided on the gate electrode 230 and may insulate the gate electrode 230 from the source and drain electrodes 260 and 265.

**[0067]** The source electrode 260 and the drain electrode 265 may face each other and may be spaced apart from each other on the interlayer insulation layer 250. The source electrode 260 may be connected to one end of the active layer 210 through a contact hole which is provided in the interlayer insulation layer 250, and the drain electrode 265 may be connected to the other end of the active layer 210 through another contact hole which is provided in the interlayer insulation layer 250. The source electrode 260 may include a lower source electrode 261, a middle source electrode 262, and an upper source electrode 263, and the drain electrode 265 may include a lower drain electrode 265 may include a lower 267, and an upper drain electrode 268.

**[0068]** The lower source and drain electrodes 261 and 266 may be provided between the interlayer insulation layer 150 and the middle source and drain electrodes 262 and 267 and may enhance an adhesive force between the interlayer insulation layer 150 and the middle source and drain electrodes 262 and 267. Also, the lower source and drain electrodes 261 and 266 may protect lower surfaces of the middle source and drain electrodes 262 and 267, thereby preventing the lower surfaces of the middle source and drain electrodes 262 and 267 from being corroded.

**[0069]** Therefore, an oxidation rate of each of the lower source and drain electrodes 261 and 266 may be lower than that of each of the middle source and drain electrodes 262 and 267. That is, the lower source and drain electrodes 261 and 266 may be formed of a material which is stronger in corrosion resistance than a material of each of the middle source and drain electrodes 262 and 267. As described above, each of the lower source and drain electrodes 261 and 266 may act as an adhesive force

enhancement layer or an anti-corrosion layer and may be formed of an alloy (MoTi) of Mo and Ti, but is not limited thereto.

**[0070]** The middle source and drain electrodes 262 and 267 may be provided between the lower source and drain electrodes 261 and 266 and the upper source and drain electrodes 263 and 268. The middle source and drain electrodes 262 and 267 may be formed of Cu which is low in resistance, but is not limited thereto. The middle source and drain electrodes 262 and 267 may be formed of a material which is relatively lower in resistance than the lower source and drain electrodes 261 and 266. A thickness of each of the middle source and drain electrodes 262 and 267 may be set thicker than that of each of the lower source and drain electrodes 261 and 266 so as to reduce a total resistance of the source and drain electrodes 260 and 265.

**[0071]** The upper source and drain electrodes 263 and 268 may be provided between the passivation layer 280 and the middle source and drain electrodes 262 and 267 and may enhance an adhesive force between the passivation layer 280 and the middle source and drain electrodes 262 and 267. Also, the upper source and drain electrodes 263 and 268 may protect upper surfaces of the middle source and drain electrodes 262 and 267, thereby preventing the upper surfaces of the middle source and drain electrodes 262 and 267 from being corroded.

**[0072]** Therefore, an oxidation rate of each of the upper source and drain electrodes 263 and 268 may be lower than that of each of the middle source and drain electrodes 262 and 267. That is, the upper source and drain electrodes 263 and 268 may be formed of a material which is stronger in corrosion resistance than a material of each of the middle source and drain electrodes 262 and 267. As described above,

each of the upper source and drain electrodes 263 and 268 may act as an adhesive force enhancement layer or an anti-corrosion layer and may be formed of a transparent conductive material such as indium tin oxide (ITO), but is not limited thereto.

**[0073]** The connection line 270 may be disposed on the same layer as the source and drain electrodes 260 and 265 and may be spaced apart from the source and drain electrodes 260 and 265. The connection line 270 and the source and drain electrodes 260 and 265 may be simultaneously formed of the same material through the same process. The connection line 270 may include a lower connection line 271, a middle connection line 272, and an upper connection line 273.

**[0074]** The lower connection line 271 may be formed of the same material as that of each of the lower source and drain electrodes 261 and 266 to have the same thickness as that of each of the lower source and drain electrodes 261 and 266, and the middle connection line 272 may be formed of the same material to have the same thickness as each of the middle source and drain electrodes 262 and 267. Also, the upper connection line 273 may be formed of the same material to have the same thickness as each of the upper source and drain electrodes 263 and 268. In this case, the connection line 270 and the source and drain electrodes 260 and 265 may be simultaneously formed through the same process.

**[0075]** The connection line 270 may be electrically connected to the auxiliary electrode 320 which will be described below. Since the connection line 270 is electrically connected to the auxiliary electrode 320, a resistance of each of the auxiliary electrode 320 and the second electrode 600 may be reduced.

**[0076]** The passivation layer 280 may be provided on the source electrode 260, the drain electrode 265, and the connection line 270 and may protect the TFT.

[0077] The planarization layer 290 may be provided on the passivation layer 280 and may planarize a surface on the substrate 100.

**[0078]** As described above, the circuit element layer 200 may include a TFT which includes the active layer 210, the gate electrode 230, the source electrode 260, and the drain electrode 265. In FIG. 4, a TFT having a top gate structure where the gate electrode 230 is provided on the active layer 230 is illustrated, but is not limited thereto. In other embodiments, the circuit element layer 200 may include a TFT having a bottom gate structure where the gate electrode 230 is provided under the active layer 230.

**[0079]** In the circuit element layer 200, a circuit element including various signal lines, TFTs, and a capacitor may be provided in each of a plurality of pixels. The signal lines may include a gate line, a data line, a power line, and a reference line, and the TFTs may include a switching TFT, a driving TFT, and a sensing TFT. The TFT illustrated in FIG. 4 may correspond to the driving TFT.

**[0080]** The switching TFT may be turned on by a gate signal supplied through the gate line and may transfer a data voltage, supplied through the data line, to the driving TFT.

**[0081]** The driving TFT may be turned on by the data voltage transferred from the switching TFT to generate a data current from a power supplied through the power line and may supply the data current to the first electrode 310.

**[0082]** The sensing TFT may sense a threshold voltage deviation of the driving TFT which causes the degradation in image quality. The sensing TFT may supply a current of the driving TFT to the reference line in response to a sensing control signal supplied through the gate line or a separate sensing line.

**[0083]** The capacitor may hold the data voltage supplied to the driving TFT during one frame and may be connected to a gate electrode and a source electrode of the driving TFT.

**[0084]** In a case where the electroluminescence display apparatus according to an embodiment of the present disclosure is implemented as the top emission type, light emission is not affected by the TFT even when the TFT is disposed under the light emitting layer 500, and thus, the TFT may be disposed under the light emitting layer 500.

**[0085]** The first electrode 310 may be provided on the circuit element layer 200. The first electrode 310 may be patterned in each of the plurality of pixels and may act as an anode of the electroluminescence display apparatus.

**[0086]** When the electroluminescence display apparatus according to an embodiment of the present disclosure is implemented as the top emission type, the first electrode 310 may include a reflective material for reflecting light, emitted from the light emitting layer 500, to an upper portion. In this case, the first electrode 310 may have a stacked structure including a transparent conductive material and the reflective material. On the other hand, when the electroluminescence display apparatus according to an embodiment of the present disclosure is implemented as the bottom

emission type, the first electrode 310 may be formed of the transparent conductive material.

**[0087]** The first electrode 310 may be connected to the drain electrode 265 of the TFT through a contact hole which is provided in the planarization layer 290 and the passivation layer 280. Depending on the case, the first electrode 310 may be connected to the source electrode 260 of the TFT through a contact hole which is provided in the planarization layer 290 and the passivation layer 280.

**[0088]** The auxiliary electrode 320 may be disposed on the same layer as the first electrode 310 and may be spaced apart from the first electrode 310. The auxiliary electrode 320 and the first electrode 310 may be simultaneously formed of the same material through the same process.

**[0089]** The auxiliary electrode 320 may be electrically connected to the second electrode 600. Since the auxiliary electrode 320 is electrically connected to the second electrode 600, the resistance of the second electrode 600 may be reduced.

**[0090]** The auxiliary electrode 320 may include a lower auxiliary electrode 321, a middle auxiliary electrode 322, and an upper auxiliary electrode 323. The first electrode 310 may include a lower first electrode 311, a middle first electrode 312, and an upper first electrode 313.

**[0091]** The lower first electrode 311 may be provided between the planarization layer 290 and the middle first electrode 312 to enhance an adhesive force between the planarization layer 290 and the middle first electrode 312, and the lower auxiliary electrode 321 may be provided between the planarization layer 290 and the middle auxiliary electrode 322 to enhance an adhesive force between the planarization

layer 290 and the middle auxiliary electrode 322. Also, the lower first electrode 311 may protect a lower surface of the middle first electrode 312, and the lower auxiliary electrode 321 may protect a lower surface of the middle auxiliary electrode 322, thereby preventing the lower surfaces of the middle first electrode 312 and the middle auxiliary electrode 322 from being corroded.

**[0092]** Therefore, an oxidation rate of each of the lower first electrode 311 and the lower auxiliary electrode 321 may be lower than that of each of the middle first electrode 312 and the middle auxiliary electrode 322. That is, the lower first electrode 311 and the lower auxiliary electrode 321 may be formed of a material which is stronger in corrosion resistance than a material of each of the middle first electrode 312 and the middle auxiliary electrode 322. As described above, each of the lower first electrode 311 and the lower auxiliary electrode 321 may be formed of an adhesive force enhancement layer or an anti-corrosion layer and may be formed of an alloy (MoTi) of Mo and Ti, but is not limited thereto.

**[0093]** The middle first electrode 312 may be provided between the lower first electrode 311 and the upper first electrode 313, and the middle auxiliary electrode 322 may be provided between the lower auxiliary electrode 321 and the upper auxiliary electrode 323. The middle first electrode 312 and the middle auxiliary electrode 322 may be formed of Cu which is low in resistance, but is not limited thereto. The middle first electrode 312 may be formed of a material which is relatively lower in resistance than the lower first electrode 311 and the lower auxiliary electrode 321. A thickness of each of the middle first electrode 312 and the middle first electrode 321 and the middle first electrode 322 may be set thicker than that of each of the lower first first electrode 322 may be set thicker than that of each of the lower first first electrode 322 may be set thicker than that of each of the lower first first electrode 322 may be set thicker than that of each of the lower first first first first first first first first electrode 322 may be set thicker than that of each of the lower first electrode 322 may be set thicker than that of each of the lower first fi

electrode 311 and the lower auxiliary electrode 321 so as to reduce a total resistance of the first electrode 310 and the auxiliary electrode 320.

**[0094]** The upper first electrode 313 and the upper auxiliary electrode 323 may protect upper surfaces of the middle first electrode 312 and the middle auxiliary electrode 322, thereby preventing the upper surfaces of the middle first electrode 312 and the middle auxiliary electrode 322 from being corroded.

**[0095]** Therefore, an oxidation rate of each of the upper first electrode 313 and the upper auxiliary electrode 323 may be lower than that of each of the middle first electrode 312 and the middle auxiliary electrode 322. That is, the upper first electrode 313 and the upper auxiliary electrode 323 may be formed of a material which is stronger in corrosion resistance than a material of each of the middle first electrode 312 and the middle auxiliary electrode 322. As described above, each of the upper first electrode 313 and the upper auxiliary electrode 322. As described above, each of the upper first electrode 313 and the upper auxiliary electrode 323 may be formed of a material of each of the upper first electrode 313 and the upper auxiliary electrode 323 may act as an adhesive force enhancement layer or an anti-corrosion layer and may be formed of a transparent conductive material such as ITO, but is not limited thereto.

**[0096]** The bank 400 may be provided between adjacent pixels of the plurality of pixels P. The bank 400 may be wholly provided in a matrix structure and may define an emission area in an individual pixel P. The bank 400 may be provided on the planarization layer 290 to hide both ends of each of the first electrode 310 and the auxiliary electrode 320. Therefore, a plurality of first electrodes 300 and auxiliary electrodes 320 respectively patterned in the plurality of pixels may be insulated from one another by the bank 400.

**[0097]** The light emitting layer 500 may be provided on the first electrode 310. The light emitting layer 500 may be provided to emit lights of different colors for each of the plurality of pixels P. For example, the light emitting layer 500 may be provided to emit red light, green light, and blue light, but is not limited thereto. The light emitting layer 500 may be provided to emit white light, and in this case, a color filter may be further provided in a traveling path of light emitted from the light emitting layer 500 for each of the plurality of pixels P.

**[0098]** Referring to FIG. 5A and FIG. 5B, the light emitting layer 500 according to an embodiment of the present disclosure may include a first light emitting layer 510, a buffer layer 520, and a second light emitting layer 530.

**[0099]** The first light emitting layer 510 may be provided on the first electrode 310. The first light emitting layer 510 may be provided in an emission area defined by the bank 400. The first light emitting layer 510 may include a hole injecting layer (HIL), a hole transporting layer (HTL), and a light emitting material layer (EML). In a red pixel, the EML may be a red EML R which emits red light. In a green pixel, the EML may be a green EML G which emits green light. In a blue pixel, the EML may be a blue EML B which emits blue light. The first light emitting layer 510 may be formed through an inkjet process. In detail, the first light emitting layer 510 may be patterned in each of the plurality of pixels P through the inkjet process using an inkjet apparatus without a mask.

[00100] The buffer layer 520 may be provided on the first light emitting layer 510. The buffer layer 520 may be provided in the emission area defined by the bank 400. The buffer layer 520 may be patterned in each of the plurality of pixels P through

the inkjet process using the inkjet apparatus without a mask. That is, the buffer layer 520 may be provided on only the first light emitting layer 510 without being provided between the auxiliary electrode 320 and the second electrode 600. The buffer layer 520 may be formed of an organic material or comprise an organic material, and thus, there is no limitation in enhancing device performance. For example, the buffer layer 520 may be formed of a conductive organic material. Accordingly, the buffer layer 520 may act as a function layer having a desired function, based on a characteristic of each pixel.

[00101] Particularly, referring to FIG. 5A, the buffer layer 520 may be disposed in a blue pixel, and thus, may be disposed on the blue EML B. The buffer layer may not be disposed in a red or green pixel and thus may not be disposed on the red EML R or green EML G. The blue EML B may have a characteristic where combined excitons, electrons, or holes move to adjacent transporting layers due to a low T1 voltage level, and thus, emission efficiency is reduced in comparison with the red EML R and the green EML G. T1 voltage level represents the energy level, or voltage level, of the lowest triplet excited state. Therefore, the buffer layer 520 may be formed of a material which has a T1 voltage level higher than that of the blue EML B and has a highest occupied molecular orbital (HOMO) level value lower than that of the blue EML B, and may be provided on the blue EML B to enhance the device performance of the blue EML B. The buffer layer 520 may act as a blocking layer to prevent excitons, electrons, or holes from moving to adjacent electron injection layer. The buffer layer 520 may be formed of a material which has a T1 voltage level higher than those of the blue EML B, the green EML G and the red EML B. Referring to FIG. 5B,

the buffer layer 520 may be disposed in a blue pixel, in a green pixel and in a red pixel, and thus, may be disposed on the blue EML B, on the green EML G and on the red EML B.

**[00102]** The buffer layer 520 may be formed of a material including carbazole or a material including fluorene or acridine. Also, the buffer layer 520 may be formed of one or more materials selected from the group consisting of an arylamine-based material, a starburst aromatic amine-based material, and a spiro type material, but is not limited thereto.

**[00103]** Moreover, the buffer layer 520 may be formed of a polymer, an oligomer, or a monomer having a molecular weight of 800 or more, or may be formed of a material including an alkyl group. The polymer, the oligomer, the monomer, and the material including the alkyl group may be materials incapable of being applied to a deposition process, and thus, the buffer layer 520 may be formed through an inkjet process. As described above, the buffer layer 520 may be formed on the first light emitting layer 510 formed through the inkjet process by using the inkjet process instead of the deposition process, thereby minimizing an issue of an interface between the first light emitting layer 510 and the buffer layer 520.

**[00104]** Moreover, the buffer layer 520 may be formed of a material for reducing a roughness of an upper surface thereof. Therefore, even when the second light emitting layer 530 is formed on the buffer layer 520 through a deposition process, an issue of interfaces is reduced. Also, the buffer layer 520 may be formed on the first light emitting layer 510 through the inkjet process in a state where the second light emitting layer 530 is not deposited on the first light emitting layer 510, and then, the

second light emitting layer 530 may be formed on the buffer layer 520 through the deposition process, thereby protecting an upper surface of the first light emitting layer 510.

[00105] Moreover, the buffer layer 520 may function as an electron transporting layer (ETL).

**[00106]** The second light emitting layer 530 may be provided on the buffer layer 520 and the auxiliary electrode 320. The second light emitting layer 530 may be wholly formed on the substrate 100 through a deposition process, except the pad area PA. Therefore, the second light emitting layer 530 may also be provided on an upper surface of the bank 400. Since the second light emitting layer 530 is disposed between the auxiliary electrode 320 and the second electrode 600, the second light emitting layer 530 may be formed of a conductive material (for example, metal) so as to electrically connect the auxiliary electrode 320 may be electrically connected to the second light emitting layer 530. The second light emitting layer 530 may include an electron injecting layer (EIL).

**[00107]** The second electrode 600 may be provided on the light emitting layer 500. In more detail, the second electrode 600 may be provided on the second light emitting layer 530. The second electrode 600 may function as a cathode of the electroluminescence display apparatus. The second electrode 600 may be provided on the bank 400 as well as the light emitting layer 500. Therefore, the second electrode 600 may function as a common electrode which applies a common voltage to the plurality of pixels.

**[00108]** An encapsulation layer (not shown) may be provided on the second electrode 600. The encapsulation layer may be disposed to cover the active area AA, and moreover, may be disposed to cover the dummy area DA. The encapsulation layer may prevent oxygen or water from penetrating into the TFT and the light emitting layer 500. To this end, the encapsulation layer may include at least one inorganic layer and at least one organic layer.

**[00109]** A circuit element layer 200, a bank 400, a dummy light emitting layer 500, and a second electrode 600 may be provided in the dummy area DA on the substrate 100.

**[00110]** The circuit element layer 200 provided in the dummy area DA may be formed to have the same structure through the same process as the circuit element layer 200 provided in the active area AA.

**[00111]** However, the present embodiment is not limited thereto. In other embodiments, some of signal lines such as a gate line, a data line, a power line, and a reference line may not be provided in the circuit element layer 200 provided in the dummy area DA, or at least one of a switching TFT and a driving TFT may not be provided in the circuit element layer 200. Therefore, light may not be emitted in the dummy area DA. Depending on the case, the circuit element layer 200 provided in the dummy area DA may be incompletely configured so that one of the switching TFT and the driving TFT does not operate.

**[00112]** The bank 400 provided in the dummy area DA may be provided between adjacent dummy pixels of a plurality of dummy pixels DP. The bank 400 provided in the dummy area DA may define a dummy emission area in an individual

dummy pixel DP. In the drawing, only one pixel DP is illustrated as being provided in the dummy area DA, but the plurality of dummy pixels DP may be provided in the dummy area DA.

**[00113]** Similarly to the bank 400 provided in the active area AA, the bank 400 provided in the dummy area DA may be wholly provided in a matrix structure and may define the dummy emission area in an individual dummy pixel DP. As a result, the bank 400 may be provided in the matrix structure in the active area AA and the dummy area DA.

**[00114]** The dummy light emitting layer 500 provided in the dummy area DA may be provided on the circuit element layer 200. The dummy light emitting layer 500 provided in the dummy area DA may be formed of the same material to have the same thickness as the light emitting layer 500 provided in the active area AA.

**[00115]** Since the dummy area DA is not a display area which displays an image, the dummy pixels DP provided in the dummy area DA may be configured so as not to emit light. However, when light is emitted in the dummy area DA, the display quality of the electroluminescence display apparatus is degraded due to leakage light occurring in the dummy area DA.

**[00116]** In order for light not to be emitted from the dummy pixels DP, a TFT may not be provided in the circuit element layer 200 disposed in the dummy area DA, or a first electrode may not be provided in the dummy area DA.

**[00117]** The second electrode 600 provided in the dummy area DA may be formed in a structure which extends from the second electrode 600 provided in the

active area AA. However, the second electrode 600 may not be provided in the dummy area DA, and thus, light may not be emitted in the dummy area DA.

[00118] A pad 700 may be provided in the pad area PA on the substrate 100. The pad 700 may include a signal pad 710 and a pad electrode 720.

**[00119]** The signal pad 710 may be provided on the insulation layer 225. The signal pad 710 may be provided on the same layer as the gate electrode 230 provided in the active area AA. The signal pad 710 may include a lower signal pad 711 and an upper signal pad 712.

**[00120]** The lower signal pad 711 may be formed of the same material to have the same thickness as the lower gate electrode 231, and the upper signal pad 712 may be formed of the same material to have the same thickness as the upper gate electrode 232. In this case, the signal pad 710 and the gate electrode 230 may be simultaneously formed through the same process.

**[00121]** The pad electrode 720 may be provided on the interlayer insulation layer 250. The pad electrode 720 may be provided on the same layer as the source and drain electrodes 260 and 265 provided in the active area AA. The pad electrode 720 may be connected to the signal pad 710 through a contact hole. The pad electrode 720 may be externally exposed and may be connected to an external driver. The pad electrode 720 may include a lower pad electrode 721, a middle pad electrode 722, and an upper pad electrode 723.

**[00122]** The lower pad electrode 721 may be formed of the same material to have the same thickness as the lower source and drain electrodes 261 and 266, the middle pad electrode 722 may be formed of the same material to have the same

thickness as the middle source and drain electrodes 262 and 267, and the upper pad electrode 723 may be formed of the same material to have the same thickness as the upper source and drain electrodes 263 and 268. In this case, the pad electrode 720 and the source and drain electrodes 260 and 265 may be simultaneously formed through the same process.

**[00123]** As described above, in the electroluminescence display apparatus according to the embodiments of the present disclosure, since the buffer layer 520 is formed on the first light emitting layer 510 through the inkjet process, the buffer layer 520 may be provided on only the first light emitting layer 510, and thus, the buffer layer 520 may be formed of an organic material or comprise an organic material, thereby enhancing the device performance of the blue pixel.

**[00124]** Moreover, in the electroluminescence display apparatus according to the embodiments of the present disclosure, since the buffer layer 520 is formed on the first light emitting layer 510 through the inkjet process, an issue occurring on the interface between the first light emitting layer 510 formed through the inkjet process and the second light emitting layer 530 formed through the deposition process is reduced, thereby preventing the efficiency and lifetime of the organic light emitting device from being reduced.

**[00125]** FIGS. 6 to 9 are graphs comparing a related art electroluminescence display apparatus with an electroluminescence display apparatus according to an embodiment of the present disclosure.

**[00126]** In the related art electroluminescence display apparatus, an organic light emitting device includes a first electrode, a first light emitting layer, a second

light emitting layer, and a second electrode without a buffer layer. On the other hand, in the electroluminescence display apparatus according to an embodiment of the present disclosure, as described above with reference to FIGS. 4 and 5, an organic light emitting device includes a first electrode, a first light emitting layer, a buffer layer, a second light emitting layer, and a second electrode.

**[00127]** FIG. 6 is a graph comparing a driving voltage of the related art electroluminescence display apparatus with a driving voltage of the electroluminescence display apparatus according to an embodiment of the present disclosure.

**[00128]** Referring to FIG. 6, in the related art electroluminescence display apparatus, when a current density is  $0 \text{ mA/cm}^2$  to  $50 \text{ mA/cm}^2$ , a driving voltage is within a range of about 3 V to 7 V. In the electroluminescence display apparatus according to an embodiment of the present disclosure, when a current density is  $0 \text{ mA/cm}^2$  to  $50 \text{ mA/cm}^2$ , a driving voltage is within a range of about 3 V to 7.2 V. In comparison with the related art electroluminescence display apparatus, the electroluminescence display apparatus according to an embodiment of the present disclosure further includes the buffer layer 520, but there is hardly a difference between the driving voltages.

**[00129]** FIG. 7 is a graph comparing a current efficiency of the related art electroluminescence display apparatus with a current efficiency of the electroluminescence display apparatus according to an embodiment of the present disclosure.

**[00130]** Referring to FIG. 7, when panel luminance is  $0 \text{ Cd/m}^2$  to 2,000 Cd/m<sup>2</sup>, a current efficiency of the electroluminescence display apparatus according to an embodiment of the present disclosure is far higher than a current efficiency of the related art electroluminescence display apparatus.

**[00131]** FIG. 8 is a graph comparing a lifetime of the related art electroluminescence display apparatus with a lifetime of the electroluminescence display apparatus according to an embodiment of the present disclosure.

**[00132]** Referring to FIG. 8, in the related art electroluminescence display apparatus, luminescence is reduced from about 101% to about 83% with time. In the electroluminescence display apparatus according to an embodiment of the present disclosure, even when the same time as the related art electroluminescence display apparatus elapses, luminescence is reduced from about 101% to about 86%. As described above, a lifetime of the electroluminescence display apparatus according to an embodiment of the present disclosure is longer than a lifetime of the related art electroluminescence display apparatus.

**[00133]** FIG. 9 is a graph comparing a normalized intensity of light of a related art electroluminescence display apparatus with a normalized intensity of light of an electroluminescence display apparatus according to an embodiment of the present disclosure with respect to a wavelength.

**[00134]** Referring to FIG. 9, in comparison with the related art electroluminescence display apparatus, the electroluminescence display apparatus according to an embodiment of the present disclosure further includes the buffer layer 520, but a normalized intensity of light of the electroluminescence display apparatus

according to an embodiment of the present disclosure is almost similar to a normalized intensity of light of the related art electroluminescence display apparatus with respect to a wavelength.

**[00135]** As described above, in the electroluminescence display apparatus according to the embodiments of the present disclosure, since the buffer layer is formed on the first light emitting layer through the inkjet process, the buffer layer may be provided on only the first light emitting layer, and thus, the buffer layer may be formed of an organic material or comprise an organic material, thereby enhancing the device performance of the blue pixel.

**[00136]** Moreover, in the electroluminescence display apparatus according to the embodiments of the present disclosure, since the buffer layer is formed on the first light emitting layer through the inkjet process, an issue occurring on the interface between the first light emitting layer formed through the inkjet process and the second light emitting layer formed through the deposition process is reduced, thereby preventing the efficiency and lifetime of the organic light emitting device from being reduced.

**[00137]** It will be apparent to those skilled in the art that various modifications and variations can be made in the present disclosure without departing from the scope of the disclosures. Thus, it is intended that the present invention covers the modifications and variations of this disclosure provided they come within the scope of the appended claims and their equivalents.

The following list provides aspects of the disclosure and forms part of the description. These aspects can be combined in any compatible combination beyond those expressly stated. The aspects can also be combined with any compatible features described herein:

Aspect 1. An electroluminescence display apparatus comprising: a substrate including an active area where a plurality of pixels are provided;

a circuit element layer disposed on the substrate;

a first electrode disposed on the circuit element layer;

an auxiliary electrode disposed on the circuit element layer and spaced apart from the first electrode;

a first light emitting layer disposed on the first electrode;

a buffer layer disposed on the first light emitting layer;

a second light emitting layer disposed on the buffer layer and the auxiliary electrode; and a second electrode disposed on the second light emitting layer.

Aspect 2. The electroluminescence display apparatus of aspect 1, wherein the buffer layer comprises a nonconductive material.

Aspect 3. The electroluminescence display apparatus of aspect 1, wherein the first light emitting layer comprises a blue light emitting material layer, and the buffer layer is disposed on the blue light emitting material layer.

Aspect 4. The electroluminescence display apparatus of aspect 3, wherein the buffer layer has a T1 voltage level higher than a T1 voltage level of the blue light emitting material layer and a highest occupied molecular orbital (HOMO) level value lower than a HOMO level value of the blue light emitting material layer.

Aspect 5. The electroluminescence display apparatus of aspect 1, wherein the buffer layer comprises a polymer, an oligomer, or a monomer having a molecular weight of 800 or more.

Aspect 6. The electroluminescence display apparatus of aspect 1, wherein the buffer layer comprises a material including an alkyl group.

Aspect 7. The electroluminescence display apparatus of aspect 1, wherein the buffer layer comprises a material including carbazole or a material including fluorene or acridine.

Aspect 8. The electroluminescence display apparatus of aspect 1, wherein the buffer layer comprises one or more materials selected from a group including an arylamine-based material, a starburst aromatic amine-based material, and a spiro type material.

Aspect 9. The electroluminescence display apparatus of aspect 1, wherein the buffer layer is formed through an inkjet process.

Aspect 10. The electroluminescence display apparatus of aspect 1, wherein the first light emitting layer is formed through an inkjet process, and the second light emitting layer is formed through a deposition process.

Aspect 11. The electroluminescence display apparatus of aspect 1, wherein the first light emitting layer comprises a hole injecting layer, a hole transporting layer, and a light emitting material layer, and

the second light emitting layer comprises an electron injecting layer.

Aspect 12. The electroluminescence display apparatus of aspect 1, wherein the second light emitting layer comprises a conductive material and is electrically connected to the auxiliary electrode and the second electrode.

Aspect 13. An electroluminescence display apparatus comprising:

a substrate including an active area where a red pixel, a green pixel, and a blue pixel are provided;

a first electrode and an auxiliary electrode disposed on the substrate and spaced apart from each other;

a bank disposed in an edge of each of the first electrode and the auxiliary electrode to define an emission area in the active area;

a first light emitting layer disposed in the emission area provided on the first electrode and a buffer layer disposed on the first light emitting layer;

a second light emitting layer disposed on the buffer layer and the auxiliary electrode; and

a second electrode disposed on the second light emitting layer,

wherein the buffer layer is disposed in the blue pixel.

Aspect 14. The electroluminescence display apparatus of aspect 13, wherein the buffer layer comprises a nonconductive material.

Aspect 15. The electroluminescence display apparatus of aspect 13, wherein

the first light emitting layer comprises a hole injecting layer, a hole transporting layer, and a light emitting material layer,

the second light emitting layer comprises an electron injecting layer, and

the first light emitting layer and the buffer layer are formed through an inkjet process, and the second light emitting layer is formed through a deposition process.

#### WHAT IS CLAIMED IS:

1. An electroluminescence display apparatus comprising:

a substrate including an active area where a plurality of pixels are provided;

a circuit element layer disposed on the substrate;

a first electrode disposed on the circuit element layer;

an auxiliary electrode disposed on the circuit element layer and spaced apart from the first electrode;

a first light emitting layer disposed on the first electrode;

a buffer layer disposed on the first light emitting layer;

a second light emitting layer disposed on the buffer layer and the auxiliary electrode; and

a second electrode disposed on the second light emitting layer.

2. The electroluminescence display apparatus of claim 1, wherein the buffer layer comprises an organic material.

3. The electroluminescence display apparatus of claim 1 or 2, wherein the first light emitting layer comprises a blue light emitting material layer, and the buffer layer is disposed on the blue light emitting material layer.

4. The electroluminescence display apparatus of claim 3, wherein the buffer layer has a T1 voltage level higher than a T1 voltage level of the blue light

emitting material layer and a highest occupied molecular orbital (HOMO) level value lower than a HOMO level value of the blue light emitting material layer.

5. The electroluminescence display apparatus of any one of claims 1 to 4, wherein the buffer layer comprises a polymer, an oligomer, or a monomer having a molecular weight of 800 or more.

6. The electroluminescence display apparatus of any one of claims 1 to 5, wherein the buffer layer comprises a material including an alkyl group.

7. The electroluminescence display apparatus of any one of claims 1 to 6, wherein the buffer layer comprises a material including carbazole or a material including fluorene or acridine.

8. The electroluminescence display apparatus of any one of claims 1 to 7, wherein the buffer layer comprises one or more materials selected from a group including an arylamine-based material, a starburst aromatic amine-based material, and a spiro type material.

9. The electroluminescence display apparatus of any one of claims 1 to 8, wherein the buffer layer is formed through an inkjet process.

10. The electroluminescence display apparatus of any one of claims 1 to 9, wherein the first light emitting layer is formed through an inkjet process, and the second light emitting layer is formed through a deposition process.

11. The electroluminescence display apparatus of any one of claims 1 to 10, wherein the first light emitting layer comprises a hole injecting layer, a hole transporting layer, and a light emitting material layer, and

the second light emitting layer comprises an electron injecting layer.

12. The electroluminescence display apparatus of any one of claims 1 to 11, wherein the second light emitting layer comprises a conductive material and is electrically connected to the auxiliary electrode and the second electrode.

13. The electroluminescence display apparatus of any one of claims 1 to12, wherein the substrate further comprises a dummy area provided at the periphery of the active area.

14. A process of making the electroluminescence display apparatus of any one of claims 1 to 13, wherein the buffer layer is formed through an inkjet process.

15. A process of making the electroluminescence display apparatus of any one of claims 1 to 14, wherein the first light emitting layer is formed through an inkjet process, and the second light emitting layer is formed through a deposition process.

16. An electroluminescence display apparatus comprising:

a substrate including an active area where a red pixel, a green pixel, and a blue pixel are provided;

a first electrode and an auxiliary electrode disposed on the substrate and spaced apart from each other;

a bank disposed at an edge of each of the first electrode and the auxiliary electrode to define an emission area in the active area;

a first light emitting layer disposed in the emission area provided on the first electrode and a buffer layer disposed on the first light emitting layer;

a second light emitting layer disposed on the buffer layer and the auxiliary electrode; and

a second electrode disposed on the second light emitting layer,

wherein the buffer layer is disposed in the blue pixel.

17. The electroluminescence display apparatus of claim 16, wherein the buffer layer comprises an organic material.

18. The electroluminescence display apparatus of claim 16 or 17, wherein the first light emitting layer comprises a hole injecting layer, a hole transporting layer, and a light emitting material layer,

the second light emitting layer comprises an electron injecting layer, and

the first light emitting layer and the buffer layer are formed through an inkjet process, and the second light emitting layer is formed through a deposition process.

19. The electroluminescence display apparatus of any one of claims 16 to18, wherein the substrate further comprises a dummy area provided at the periphery of the active area.

Intellectual Property Office

| Application No:  | GB1820512.0 | Examiner:       | Thomas Britland |

|------------------|-------------|-----------------|-----------------|

| Claims searched: | 1-15        | Date of search: | 29 May 2019     |

# Patents Act 1977: Search Report under Section 17

## Documents considered to be relevant:

| Category | Relevant<br>to claims         | Identity of document and passage or figure of particular relevance |

|----------|-------------------------------|--------------------------------------------------------------------|

| X,E      | 1, 2, 4, 9,<br>11, 12 &<br>14 | WO 2019/071759 A1<br>(TANG) See figure 9 and related text.         |

| X,E      | 1-4, 11 &<br>12               | EP 3480851 A1<br>(CHOI) See figure 8 and related text.             |

| X        | 1-15                          | US 2016/0240810 A1<br>(OH) See figure 1 and related text.          |

| X        | 1-15                          | US 2014/0239262 A1<br>(KIM) See figure 7 and related text.         |

| X        | 1-15                          | US 2016/0126304 A1<br>(CHO) See figure 4 and related text.         |

| X        | 1-15                          | US 2016/0155790 A1<br>(LEE1) See figure 13 and related text.       |

| X        | 1-15                          | US 2017/0110530 A1<br>(LEE2) See figure 2 and related text.        |

#### Categories:

| Cui | egones.                                          |   |                                                               |

|-----|--------------------------------------------------|---|---------------------------------------------------------------|

| X   | Document indicating lack of novelty or inventive | А | Document indicating technological background and/or state     |

|     | step                                             |   | of the art.                                                   |

| Y   | Document indicating lack of inventive step if    | Р | Document published on or after the declared priority date but |

|     | combined with one or more other documents of     |   | before the filing date of this invention.                     |

|     | same category.                                   |   |                                                               |

| &   | Member of the same patent family                 | Е | Patent document published on or after, but with priority date |

|     |                                                  |   | earlier than, the filing date of this application.            |

### Field of Search:

Search of GB, EP, WO & US patent documents classified in the following areas of the  $UKC^{\rm X}$  :

Worldwide search of patent documents classified in the following areas of the IPC H01L

The following online and other databases have been used in the preparation of this search report

# EPODOC, WPI

| International Classification: |          |            |  |

|-------------------------------|----------|------------|--|

| Subclass                      | Subgroup | Valid From |  |

| H01L                          | 0051/52  | 01/01/2006 |  |

| H01L                          | 0027/12  | 01/01/2006 |  |

| H01L                          | 0027/32  | 01/01/2006 |  |

| H01L                          | 0051/50  | 01/01/2006 |  |

| H05B                          | 0033/08  | 01/01/2006 |  |