# (10) **DE 10 2006 025 959 B4** 2010.03.04

(12)

# **Patentschrift**

(21) Aktenzeichen: 10 2006 025 959.9

(22) Anmeldetag: 02.06.2006(43) Offenlegungstag: 13.12.2007

(45) Veröffentlichungstag

der Patenterteilung: 04.03.2010

(51) Int Cl.8: *H01L 23/482* (2006.01)

*H01L 21/60* (2006.01) *H01L 29/772* (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten(§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

| (73) Patentinhaber: Infineon Technologies AG, 81669 München, DE                                                                                             | (56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>(74) Vertreter: Meissner, Bolte &amp; Partner GbR, 80538 München</li> <li>(72) Erfinder: Häberlen, Oliver, Dipl-Phys., Dr., Villach, AT</li> </ul> | DE 10 2004 030042 A1 DE 100 03 671 A1 US 2004/01 04 489 A1 US 2001/00 33 022 A1 US 53 93 697 A US 68 38 735 B1 US 63 13 512 B1 |

(54) Bezeichnung: Leistungshalbleiteranordnung mit vorderseitig aufgelötetem Clip und Verfahren zur Herstellung einer solchen

(57) Hauptanspruch: Leistungshalbleiteranordnung vom FET-Typ, mit vorderseitig aufgelötetem Clip zum externen Ausschließen eines Source-Anschlusses, bei der eine lötfähige vorderseitige Leistungs-Metallisierungsschicht für den Source-Anschluss und eine Gatefinger-Struktur für einen Gate-Anschluss sowie eine strukturierte Passivierungsschicht zur Isolation der Gatefinger von dem aufgelöteten Clip vorgesehen sind, wobei die lötfähige Leistungs-Metallisierungsschicht über der Passivierungsschicht angeordnet ist und die Passivierungsschicht im Bereich des Gatefingers im Wesentlichen vollständig überdeckt.

### **Beschreibung**

**[0001]** Die Erfindung betrifft eine Leistungshalbleiteranordnung mit Vorderseitig aufgelötetem sowie ein Verfahren zur Herstellung einer solchen.

**[0002]** Im Zuge der Entwicklung der Halbleitertechnologie sind unzählige Anordnungen und Verfahren zur externen Kontaktierung der eigentlichen Halbleiterelemente oder -schaltungen entwickelt worden, darunter die bekannten und in mannigfachen Abwandlungen praktizierten Drahtbond- und Die-Bond-Verfahren.

[0003] Speziell auf dem Gebiet der Leistungshalbleiteranordnungen haben in den letzten Jahren zunehmende Leistungsanforderungen zur Etablierung neuer Montagetechniken geführt. Dabei wurde insbesondere das Ziel verfolgt, den Ohmschen Widerstand und die Induktivität der externen Verbindungen zu verringern. Diesem Ziel der Bereitstellung niederohmigerer und niederinduktiverer Chipanbindungen dient die Ersetzung der herkömmlichen Drahtbondverbindungen auf der Chipvorderseite durch gelötete Clip-Verbindungen. Da die herkömmlichen vorderseitigen Metallisierungen auf Al-Basis nicht oder jedenfalls nicht ohne Weiteres lötfähig sind, erfordert diese grundlegende Änderung der Verbindungstechnologie die Ersetzung der herkömmlichen Metallisierung für den Source-Anschluss bzw. Leistungs-Metallisierung durch eine vom Grundaufbau her lötfähige Leistungs-Metallisierung oder die Aufbringung einer lötfähigen Leistungs-Metallisierung auf einer Basismetallisierung des bekannten Al-basierten Typs.

[0004] Es ist bekannt, zum Anschluss Gate-Spannung bei Halbleiteranordnungen – speziell auch Leistungshalbleitern - mit hohen Anforderungen an die Schaltgeschwindigkeit eine Fingerstruktur der Gate-Anschlüsse für ein Transistorzellenfeld vorzusehen, die verkürzt auch als "Gatefinger" bezeichnet wird. Sollen Halbleiteranordnungen mit einer derartigen Gatefinger-Struktur auf die hier in Rede stehende Weise mit gelöteten Clip-Verbindungen extern angeschlossen werden, müssen selbstverständlich die Gatefinger von dem auf Source-Potential liegenden aufgelötetem Clip isoliert sein. Es ist bekannt, hierzu eine Passivierungsschicht über den Gatefingern einzusetzen, die üblicherweise auf Siliziumnitrid (Si<sub>3</sub>N<sub>4</sub>), Siliziumoxid (SiO<sub>2</sub>) oder einem Polymeren, insbesondere einem Imid, basiert. Eine derartige Passivierungsschicht wird üblicherweise nach der Ausbildung der strukturierten lötfähigen Leistungs-Metallisierungsschicht aufgebracht.

[0005] Bei dieser Technik hat sich als nachteilig herausgestellt, dass die Passivierungsschicht beim Auflöten des Clips zum externen Anschluss des Chips vom Lot nicht benetzt wird. Da bei jedem Lötverfahren vor dem Aufbringen des Lotes eine Benetzung

mit einem Flussmittel erfolgt, besteht die reale Gefahr des Verbleibens von Flussmittelresten auf der Passivierungsschicht. Diese chemisch aggressiven Flussmittelreste können, wie sich in der Praxis auch erwiesen hat, zu einer zeitabhängigen Verschlechterung von Eigenschaften der Leistungshalbleiteranordnung, einer sogenannten Degradation, führen.

[0006] Es sind auch Techniken bekannt geworden, mit denen eine Verwendung der bevorzugten Chip-Anbindung durch eine gelötete Clip-Verbindung realisiert und dennoch der nachteilige Effekt des Verbleibens von Flussmittelresten auf einer Passivierungsschicht verhindert werden kann. So ist es bekannt, den aufgelöteten Clip in Anpassung an die vorhandene Gatefinger-Struktur geometrisch derart zu konfigurieren, dass keine vom Clip abgedeckten Bereiche einer Passivierungsschicht existieren.

**[0007]** Durch die Strukturierung des Chips entsteht hier jedoch ein höherer Aufwand.

[0008] Es ist auch bekannt, mittels stromloser Abscheidung eine lötbare Vorderseitenmetallisierung auf eine aluminiumbasierten Leistungsmetallisierung abzuscheiden, die jedoch nicht auf vorher passivierten Bereichen aufwächst. Weiter ist es bekannt geworden, bei bestimmten Leistungshalbleiterstrukturen vom FET-Typ, dem sogenannten DirectFET, die lötbare Chipvorderseite einer gemeinsamen Strukturierung mit einer Basis-Leistungsmetallisierung zu unterziehen und anschließend die Gatefinger mit einem pressmassen-ähnlichen Material abzudecken.

[0009] Die US 6 838 735 B1 beschreibt eine Leistungshalbleiteranordnung (MOSFET) mit mehreren Gräben, die von einem Gate-Oxid gesäumt und die mit leitendem Polysilizium ausgefüllt sind. Die Oberfläche der Polysiliziumschicht wird mit einer Isolierungsschicht (TEOS) gedeckt, um die Gate-Elektrode von der Source-Elektrode (aus Aluminium) zu isolieren.

**[0010]** Die US 6 313 512 B1 beschreibt eine FET-Anordnung mit einer Mehrheit von Drain-, Source- und Gate-Fingerelektroden. Der wesentliche Gedanke dieser Entegegenhaltung sieht eine Anordnung vor, welche das Kreuzen der Drain-Linien mit den Source-Linien vermeiden soll.

**[0011]** Die DE 100 03 671 A1 beschreibt einen Halbleiterpackungsaufbau zur Erniedrigung des elektrischen Widerstands der Halbleiter-Packung ohne Silizium-Chip. Für diesen Zweck wird die Verbindungsoberfläche der ersten und zweiten Elektrode und des ersten und zweiten Metallteils des Halbleiter-Bauelementes mit einer Edelmetallschicht versehen.

[0012] Die US 2001/0 033 022 A1 beschreibt einen

## DE 10 2006 025 959 B4 2010.03.04

Clip für eine Aluminium-Verbindung mit einem Halbleiter-Bauelement. In diesem Dokument ist explizit beschrieben, dass der Clipkörper eine besondere Form hat, um die Verbindung mit der Gate-Elektrode zu verhindern.

**[0013]** Die US 2004/0 104 489 A1 beschreibt eine Halbleiteranordnung, welche einen topfförmigen Clip auf der Drain-Elektrode benutzt, um den gesamten Widerstand bei Hochfrequenz zu erniedrigen. Eine Passivierungsschicht wird in dieser Entgegenhaltung benutzt, um einen Kurzschluss zwischen Gate und Source zu vermeiden.

[0014] Die DE 10 2004 030 042 A1 beschreibt ein in Flip-Chip-Technik hergestelltes Halbleiterbauelement mit einem Halbleiterchip, bei dem die über einen bestimmten Anschlusskontakt abgeführte Wärme auf einen vorgegebenen Wert begrenzt ist. Im Besonderen werden die strukturierte Metallisierungsschicht und optional auch die strukturierte Verbindungsschicht bereits bei der Herstellung des Halbleiterchips erzeugt. Weist dabei die Vorderseite des Halbleiterchips mehrere gegeneinander isolierte Anschlusskontakte auf, ist für jede Anschlusskontakte eine eigene Kontaktschicht vorhanden.

**[0015]** Alle erwähnten Ansätze haben sich jedoch unter bestimmten Gesichtspunkten als nachteilig erwiesen. Insbesondere sind die funktional überzeugenderen dieser Lösungen mit einem erhöhnten Verfahrensaufwand verbunden und führen daher auch zu erhöhten Kosten der erzeugten Halbleiteranordnungen.

**[0016]** Der Erfindung liegt daher die Aufgabe zu Grunde, eine verbesserte Halbleiteranordnung sowie ein verbessertes Verfahren zur Herstellung einer solchen anzugeben, die insbesondere beim Einsatz von lötbaren Clip-Verbindungen Zuverlässigkeitsprobleme sicher ausschließen, ohne zu einem wesentlich erhöhten Herstellungsaufwand und damit höheren Herstellungskosten zu führen.

**[0017]** Diese Aufgabe wird in ihrem Vorrichtungsaspekt durch eine Halbleiteranordnung mit den Merkmalen des Anspruchs 1 und in ihrem Verfahrensaspekt durch ein Verfahren mit den Merkmalen des Anspruchs 10 gelöst. Zweckmäßige Fortbildungen des Erfindungsgedankens sind Gegenstand der jeweiligen abhängigen Ansprüche.

[0018] Die Erfindung schließt den wesentlichen Gedanken ein, in grundlegender Umkehrung des bisherigen Verfahrensablaufes eine lötfähige Leistungs-Metallisierungsschicht nach Aufbringung einer Passivierungsschicht zur Isolierung der Gatefinger auszubilden. Dies hat zur Folge, dass die vorab passivierten Gatefinger im Bereich der Clip-Anbindung, wie auch die übrigen Oberflächenbereiche, mit einer

vom Lot benetzbaren Schicht versehen sind.

[0019] Der entscheidende Vorteil dieser neuen Lösung besteht darin, dass sämtliche Oberflächenbereiche der Chip-Vorderseite bzw. alle Bereiche zwischen dieser und der korrespondierenden Clip-Oberfläche vollständig mit Lot ausgefüllt sein können, es also keine Bereiche mehr gibt, in denen Flussmittelreste verbleiben können. Ein weiterer Vorteil besteht in der gleichmäßigeren Anbindung der durch die Gatefinger-Struktur im Chip elektrisch separierten Bereiche der Transistorzellenfelder.

**[0020]** Erfindungsgemäß wird die Passivierungsschicht von der lötfähigen Leistungs-Metallisierungsschicht im Bereich des Gatefingers im Wesentlichen vollständig überdeckt.

[0021] Weiter bevorzugt ist vorgesehen, dass die lötfähige Leistungs-Metallisierungsschicht eine Mehrschichtstruktur aufweist, wobei eine obere, einem Lot zur Clip-Verbindung benachbarte Schicht Ag oder eine Ag-Legierung aufweist. Hierbei beträgt die Dicke der oberen Schicht insbesondere 100 bis 700 nm, besonders bevorzugt zwischen 150 und 500 nm. Mit einer solchen Dicke wird ein sinnvoller Kompromiss zwischen sicherer Lot-Benetzbarkeit der Metallisierungsschicht und vergleichsweise geringer Schichtdicke erzielt.

[0022] In einer weiteren Ausgestaltung dieser Ausführungsform ist vorgesehen, dass die lötfähige Leistungs-Metallisierungsschicht eine Dreischichtstruktur mit einer unteren Ti- oder Ti-Legierungs-Schicht, einer mittleren Ni- oder Ni-Legierungs-Schicht und einer oberen Ag- oder Ag-Legierungs-Schicht aufweist. Diese Schichtstruktur ist besonders zweckmäßig konfiguriert mit einer Schichtdicke der lötfähigen Leistungs-Metallisierungsschicht im Bereich zwischen 450 und 1750 nm, bevorzugt zwischen 550 und 850 nm und besonders bevorzugt von 700 nm.

[0023] Die Schichtdicken der einzelnen Teilschichten sind bevorzugt wie folgt gewählt: Die Schichtdicke der unteren Ti- oder Ti-Legierungs-Schicht liegt im Bereich zwischen 150 und 450 nm, bevorzugt bei 300 nm, die Dicke der mittleren Ni- oder Ni-Legierungs-Schicht liegt zwischen 100 und 600 nm, bevorzugt zwischen 200 und 400 nm, und die Dicke der oberen Ag- oder Ag-Legierungs-Schicht liegt zwischen 100 und 700 nm, bevorzugt zwischen 150 und 500 nm.

**[0024]** Die hier in Rede stehende lötfähige Leistungs-Metallisierungsschicht ist als zusätzliche Schicht auf einer AlSi-, AlCu- oder AlSiCu-Basismetallisierung vorgesehen. Alternativ hierzu, durchaus im Rahmen der Erfindung, kann aber auch eine andere Basismetallisierung als Grundlage dienen.

[0025] In einer weiteren bevorzugten Ausführungsform der Erfindung ist vorgesehen, dass die lötfähige Leistungs-Metallisierungsschicht auf einer Passivierungsschicht angeordnet ist, die eine dünne SiNoder  ${\rm SiO_2}$ -Haftschichtpassivierung mit einer Dicke im Bereich zwischen 20 und 100 nm, bevorzugt zwischen 30 und 70 nm, und eine Imid-Schicht mit einer Dicke im Bereich zwischen 3 und 10  $\mu$ m, bevorzugt zwischen 5 und 7  $\mu$ m, aufweist. Auch hierzu gibt es Alternativen, so können etwa plasma-unterstützt abgeschiedene Siliziumoxide und/oder -nitride allein als Passivierung dienen.

[0026] Zu den vorstehend erwähnten Merkmalen und bevorzugten Ausführungen der vorgeschlagenen Leistungshalbleiteranordnung vom FET-Typ korrespondieren Merkmale eines entsprechenden Herstellungsverfahrens, sodass diese hier nicht im Einzelnen wiederholt werden müssen. Es sei jedoch darauf hingewiesen, dass der erfindungsgemäße Verfahrensablauf zumindest die folgenden Schritte umfasst: Abscheidung und Strukturierung einer Basismetallisierungsschicht, auf einem Substrat, Ausbildung und Strukturierung einer Passivierungsschicht zur Isolierung einer auf dem Substrat vorliegenden Gatefinger-Struktur und Abscheidung und Strukturierung einer lötfähigen Leistungs-Metallisierungsschicht über der Basismetallisierungsschicht und der strukturierten Passivierungsschicht, wobei die Leistungs-Metallisierungsschicht die Passivierungsschicht im Wesentlichen vollständig überdeckt, und Auflöten eines Clips auf die lötfähige Leistungs-Metallisierungsschicht.

**[0027]** Hierbei weist insbesondere die Strukturierung der Passivierungsschicht ein Ätzen, insbesondere Plasmaätzen, der  $\mathrm{Si_3N_4}$ - bzw.  $\mathrm{SiO_2}$ -Haftschicht unter Maskierung durch die vorab fotochemisch strukturierte Imid-Schicht auf.

**[0028]** In einer weiteren bevorzugten Verfahrensführung ist die Abscheidung der lötfähigen Leistungs-Metallisierungsschicht als Vakuumbedampfungs- oder Sputterverfahren ausgebildet, und es handelt sich hierbei insbesondere um einen mehrschrittigen Prozess, in dessen letzter Stufe, also als lot-benetzbare Oberfläche der Metallisierung, eine Ag- oder Ag-Legierungs-Schicht mit hinreichender Dicke (wie oben erwähnt) abgeschieden wird.

[0029] In einer weiteren bevorzugten Verfahrensführung ist vorgesehen, dass vor der Abscheidung der lötfähigen Leistungs-Metallisierungsschicht eine Fotolackschicht aufgebracht und strukturiert wird und nach dem Abscheiden der lötfähigen Leistungs-Metallisierungsschicht eine Strukturierung derselben durch einen Liftoff-Prozess ausgeführt wird.

[0030] Da die vorgeschlagene Lösung sich insbesondere für Leistungshalbleiteranordnungen in Ge-

stalt dünner Halbleiterchips, mit einer Dicke von 250 µm oder weniger, insbesondere von 175 µm oder weniger, eignet, kann das vorgeschlagene Verfahren durch einen Schritt des Abdünnens der Wafer-Rückseite nach den vorstehend erwähnten Prozessschritten vervollständigt sein. Auf dieses Abdünnen können selbstverständlich – in an sich bekannter Weise – noch Schritte der Rückseitenimplantation und/oder -metallisierung des Wafers folgen.

**[0031]** Vorteile und Zweckmäßigkeiten der Erfindung ergeben sich im Übrigen aus der nachfolgenden Beschreibung eines Ausführungsbeispiels des vorgeschlagenen Verfahrens anhand der Figuren. Von diesen zeigen:

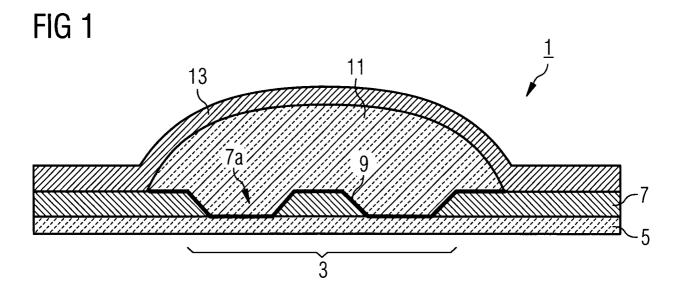

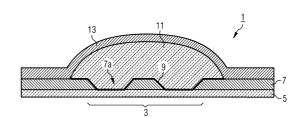

**[0032]** Fig. 1 eine schematische Darstellung eines Ausführungsbeispiels der Erfindung, als Querschnittsdarstellung einer Leistungsmetallisierungs-Schichtfolge einer Leistungshalbleiteranordnung und

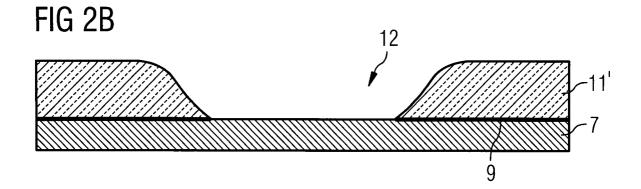

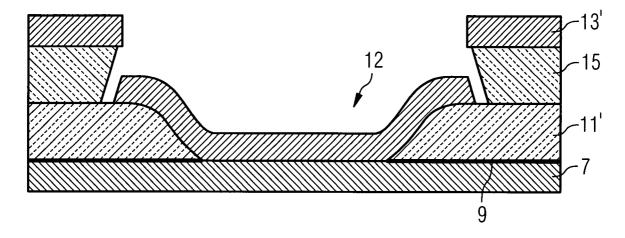

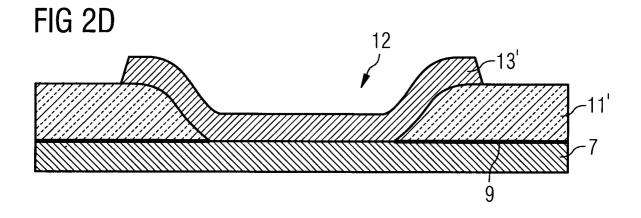

**[0033]** Fig. 2A bis Fig. 2D schematische Querschnittsdarstellungen zur Erläuterung eines Herstellungsverfahrens gemäß einer Ausführung der Erfindung.

[0034] Fig. 1 zeigt einen erfindungsgemäßen Schichtaufbau 1 einer Leistungsmetallisierung über einem Gatefinger-Bereich 3 eines (hier nicht insgesamt dargestellten) Leistungs-FET. Als unterste Schicht dargestellt ist eine auch als Zwischenoxid (ZWOX) bezeichnete Isolationsschicht 5, wie sie typischer Weise auf einer aus Poly-Si bestehenden (hier dargestellten) Gateelektrode des tungs-FET vorgesehen ist. Diese Schicht besteht in der Regel aus bor- und/oder phosphordotiertem Silikatglas (Kurzbezeichnungen BSG, PSG bzw. BPSG). Hierauf ist eine in vorgegebener Weise strukturierte AlSiCu-Basismetallisierungsschicht 7 aufgebracht, in der in der Figur zwei freigelegte Bereiche 7a gezeigt sind. Hierauf ist eine plasmaunterstützt abgeschiedene Siliziumnitridschicht (Kurzbezeichnung SNIT) 9 vorgesehen.

[0035] Erfindungsgemäß ist über dem mit SNIT abgedeckten strukturierten Bereich der Basismetallisierungsschicht 7 eine relativ dicke Imidschicht 11 aufgebracht, deren Haftung auf der Basismetallisierungsschicht 7 durch die SNIT-Schicht 9 verbessert wird. Über der Basismetallisierungsschicht 7 und (wo diese vorgesehen ist) der Imidschicht 11 erstreckt sich schließlich eine lötbare Leistungsmetallisierungs(LVS)-Schicht 13. Durch das Vorsehen der Imidschicht 11 im Gatefinger-Bereich 3 unterhalb der lötbaren Leistungsmetallisierungs(LVS)-Schicht 13 werden die Gatefinger gegenüber dieser auf sichere und vergleichsweise unaufwändige Weise elektrisch isoliert.

[0036] Die Herstellung dieses Schichtaufbaus wird anhand der Fig. 2A bis Fig. 2D etwas näher erläutert, bei denen allerdings gegenüber Fig. 1 die Zwischenoxidschicht 5 fortgelassen ist und die AlSi-Cu-Basismetallisierungsschicht 7 als solche unstrukturiert dargestellt ist. Hierbei zeigt Fig. 2A als (willkürlich angenommenen) Ausgangspunkt einfach eine unstrukturierte, in der Praxis beispielsweise 3,2 μm dicke AlSiCu-Basismetallisierungsschicht 7 als Basismetallisierung mit einer aufgesputterten, 40 nm dicken Schutznitrid-Passivierung, die auch als Haftvermittler für die nachfolgende Schicht wirkt.

[0037] Fig. 2B zeigt den Schichtaufbau mit dieser nachfolgenden Schicht, nämlich einer 6 µm dicken, durch Photolithographie strukturierbaren Imidschicht 11', einem sog. Photoimid oder FT-Imid. Hierin sowie in der Schutznitridschicht 9 wurde durch geeignete Ätzprozesse eine Öffnung 12 gebildet.

[0038] Hierzu wird das nach dem Aufbringen photosensitive Photoimid zunächst über einen herkömmlichen Lithographieschritt strukturiert und anschließend zur mechanischen Stabilisierung vernetzt. Da die unter der Imidschicht 11' liegende Schutznitridschicht 9 mit der strukturierten Imidschicht 11' als Maske geätzt wird, wird die Vernetzung der letzteren in zwei Stufen ausgeführt: Zunächst wird ein sogenanntes "Hardbake" bei 200°C ausgeführt, wodurch der Lösemittelgehalt der Imidschicht drastisch abgesenkt wird, um bei einem nachfolgenden Plasmaätzen der Schutznitridschicht eine Kontaminierung der Vakuumkammer mit Lösemitteldämpfen zu verhindern.

[0039] Nach dem Hardbake wird eine kurze O<sub>2</sub>-Plasmaätzung ausgeführt, durch die etwaige organische Niederschläge auf dem freigelegten Öffnungsbereich 12 entfernt werden sollen. Nach diesem kurzen Plasmaätzschritt wird die eigentliche, vollständige Vernetzung der Imidschicht ausgeführt, die auch als Zyklisieren bezeichnet wird. Dieser Schritt dauert typischer Weise ein bis zwei Stunden und wird als thermische Behandlung im Bereich zwischen 380°C und 420°C in Inertgasatmosphäre ausgeführt. Daran schließt sich ein nochmaliges kurzes Ätzen im Sauerstoffplasma an, um bei dem Zyklisieren gegebenenfalls nochmals gebildete organische Niederschläge von den metallischen Oberflächen zu entfernen.

[0040] Als nächstes wird auf die Imidschicht 11' außerhalb des Öffnungsbereiches 12 unter Einsatz geeigneter Maskierungsmethoden für einen nachfolgenden sogenannten Liftoff-Schritt eine entsprechend auch als FT-Liftoff 15 bezeichnete Photolackschicht derart aufgebracht, dass die Lackkante nahe dem Öffnungsbereich 12 einen negativen Kantenwinkel bzw. "Überhang" hat. Nach der erwähnten Strukturierung dieser Zwischenschicht 15 wird ganzflä-

chig, sowohl auf die lackbedeckten als auch auf die lackfreien Abschnitte, die lötbare Leistungsmetallisierungs(LVS)-Schicht **13'** abgeschieden.

[0041] Es handelt sich hierbei um eine Dreischichtstruktur aus einer im Beispiel 300 nm dicken Ti-Schicht, einer darüber abgeschiedenen 200 nm dicken NiV-Schicht und einer hierüber ebenfalls durch Sputtern aufgebrachten, 200 nm dicken Ag-Schicht. (Die Schichtstruktur ist in den Figuren nicht dargestellt.) Die Verfahrensführung bei den entsprechenden Vakuumbeschichtungsschritten ist konventionell.

[0042] Anschließend wird der gesamte Aufbau einem als solcher seit langem bekannten Liftoff-Prozess unterzogen, bei dem durch Kombination chemischer und mechanischer Einwirkung (Lösungsmittel/Druckstrahl) die Photolackschicht 15 zusammen mit der darauf abgeschiedenen Leistungsmetallisierungsschicht 13' von der Waferoberfläche entfernt wird. Die im Öffnungsbereich 12 auf der AlSiCu-Metallschicht aufliegende Leistungsmetallisierung hat dort eine so große Haftung, dass sie bei diesem Prozess nicht entfernt und auch nicht beschädigt wird. Es ist dann der in Fig. 2D gezeigte Zustand erreicht.

**[0043]** Die Ausführung der Erfindung ist nicht auf dieses Beispiel und die oben hervorgehobenen Aspekte beschränkt, sondern ebenso in einer Vielzahl von Abwandlungen möglich, die im Rahmen fachgemäßen Handelns liegen. Insbesondere sollen Kombinationen sämtlicher Merkmale der abhängigen Ansprüche miteinander als im Bereich der Erfindung liegend angesehen werden.

#### **Patentansprüche**

- 1. Leistungshalbleiteranordnung vom FET-Typ, mit vorderseitig aufgelötetem Clip zum externen Ausschließen eines Source-Anschlusses, bei der eine lötfähige vorderseitige Leistungs-Metallisierungsschicht für den Source-Anschluss und eine Gatefinger-Struktur für einen Gate-Anschluss sowie eine strukturierte Passivierungsschicht zur Isolation der Gatefinger von dem aufgelöteten Clip vorgesehen sind, wobei die lötfähige Leistungs-Metallisierungsschicht über der Passivierungsschicht angeordnet ist und die Passivierungsschicht im Bereich des Gatefingers im Wesentlichen vollständig überdeckt.

- 2. Leistungshalbleiteranordnung nach Anspruch 1, dadurch gekennzeichnet, dass die lötfähige Leistungs-Metallisierungsschicht eine Mehrschichtstruktur aufweist, wobei eine obere, einem Lot zur Clip-Verbindung benachbarte Schicht ein Edelmetall, insbesondere Ag oder eine Ag-Legierung, aufweist.

- 3. Leistungshalbleiteranordnung nach Anspruch 2, dadurch gekennzeichnet, dass die Dicke der oberen Schicht zwischen 100 und 700 nm, bevorzugt

zwischen 150 und 500 nm, liegt.

- 4. Leistungshalbleiteranordnung nach Anspruch 2 oder 3, dadurch gekennzeichnet, dass die lötfähige Leistungs-Metallisierungsschicht eine Dreischichtstruktur mit einer unteren Ti- oder Ti-Legierungs-Schicht, einer mittleren Ni- oder Ni-Legierungs-Schicht und einer oberen Ag- oder Ag-Legierungs-Schicht aufweist.

- 5. Leistungshalbleiteranordnung nach einem der vorangehenden Ansprüche, gekennzeichnet durch eine Schichtdicke der lötfähigen Leistungs-Metallisierungsschicht im Bereich zwischen 450 und 1750 nm, bevorzugt zwischen 550 und 850 nm und besonders bevorzugt von 700 nm.

- 6. Leistungshalbleiteranordnung nach Anspruch 4 und 5, dadurch gekennzeichnet, dass die Schichtdicke der unteren Ti- oder Ti-Legierungs-Schicht im Bereich zwischen 150 und 450 nm, bevorzugt bei 300 nm, die Dicke der mittleren Ni- oder Ni-Legierungs-Schicht zwischen 100 und 600 nm, bevorzugt bei 200 nm, und die Dicke der oberen Ag- oder Ag-Legierungs-Schicht zwischen 100 und 700 nm, bevorzugt bei 200 nm, liegt.

- 7. Leistungshalbleiteranordnung nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass die lötfähige Leistungs-Metallisierungsschicht auf einer AlSi-, AlCu- oder AlSiCu-Basismetallisierung angeordnet ist.

- 8. Leistungshalbleiteranordnung nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass die lötfähige Leistungs-Metallisierungsschicht auf einer Passivierungsschicht angeordnet ist, die eine dünne  $\mathrm{Si}_3\mathrm{N}_4$  oder  $\mathrm{SiO}_2$ -Haftschichtpassivierung mit einer Dicke im Bereich zwischen 20 und 100 nm, bevorzugt zwischen 30 und 70 nm, und eine Imid-Schicht mit einer Dicke im Bereich zwischen 3 und 10 µm, bevorzugt zwischen 5 und 7 µm, aufweist.

- 9. Leistungshalbleiteranordnung nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass der aufgelötete Clip und die zu dieser gehörige Leistungs-Metallisierungsschicht oberhalb einer Die-Bond-Verbindung vorgesehen und die Leitungshalbleiteranordnung mit der Die-Bond-Verbindung und dem Clip in ein Kunststoffgehäuse eingeschlossen ist.

- 10. Verfahren zur Herstellung einer Leistungshalbleiteranordnung vom FET-Typ, mit der Schritten einer Abscheidung und Strukturierung einer Basismetallisierungsschicht auf einem Substrat, Ausbildung und Strukturierung einer Passivierungsschicht zur Isolierung einer auf dem Substrat vorliegenden Gatefinger-Struktur, Abscheidung und Strukturierung einer lötfähigen Leistungs-Metallisierungsschicht

über der Basismetallisierungsschicht und der strukturierten Passivierungsschicht, wobei die Leistungs-Metallisierungsschicht die Passivierungsschicht im Wesentlichen vollständig überdeckt, Auflöten eines Clips auf die lötfähige Leistungs-Metallisierungsschicht.

- 11. Verfahren nach Anspruch 10 dadurch gekennzeichnet, dass die Ausbildung der Passivierungsschicht die Erzeugung einer  $\mathrm{Si}_3\mathrm{N}_4$  oder  $\mathrm{SiO}_2$ -Haftschicht mit einer Dicke im Bereich zwischen 20 und 100 nm, bevorzugt zwischen 30 und 70 nm, und das Aufbringen einer Imid-Schicht mit einer Dicke im Bereich zwischen 3 und 10 µm, bevorzugt zwischen 5 und 7 µm, umfasst.

- 12. Verfahren nach Anspruch 10 oder 11, dadurch gekennzeichnet, dass die Strukturierung der Passivierungsschicht ein Ätzen, insbesondere Plasmaätzen, der  $\mathrm{Si_3N_4}$  bzw.  $\mathrm{SiO_2}$ -Haftschicht unter Maskierung durch die vorab fotochemisch strukturierte Imid-Schicht aufweist.

- 13. Verfahren nach einem der Ansprüche 10 bis 12, dadurch gekennzeichnet, dass das Abscheiden der lötfähigen Leistungs-Metallisierungsschicht als Vakuumbedampfungs- oder Sputter-Verfahren ausgestaltet ist.

- 14. Verfahren nach einem der Ansprüche 10 bis 13, dadurch gekennzeichnet, dass die Abscheidung der lötfähigen Leistungs-Metallisierungsschicht ein mehrschrittiger Prozess ist, in dessen letzter Stufe eine Ag- oder Ag-Legierungs-Schicht mit einer Schichtdicke zwischen 100 und 700 nm, bevorzugt zwischen 150 und 500 nm, abgeschieden wird.

- 15. Verfahren nach einem der Ansprüche 10 bis 14, dadurch gekennzeichnet, dass vor der Abscheidung der lötfähigen Leistungs-Metallisierungsschicht eine Fotolackschicht aufgebracht und strukturiert wird und nach dem Abscheiden der lötfähigen Leistungs-Metallisierungsschicht eine Strukturierung der selben durch einen Liftoff-Prozess ausgeführt wird.

- 16. Verfahren nach einem der Ansprüche von 10 bis 15, gekennzeichnet durch einen Schritt des rückseitigen Dünnschleifens zur Ausbildung eines dünnen Halbleiterchips mit einer Dicke von 250 µm oder weniger.

Es folgen 2 Blatt Zeichnungen

# Anhängende Zeichnungen