심사관 :

이우식

## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

#### **H01L 27/108**(2006.01)

(21) 출원번호 **10-2001-0038167**

(22) 출원일자 **2001년06월29일** 심사청구일자 **2006년03월14일**

(65) 공개번호

10-2003-0002518

공개일자 **2003년01월09일**

(56) 선행기술조사문헌 KR1020010046630 A KR1019970030485 A 전체 청구항 수 : 총 4 항 (45) 공고일자 2007년09월10일

(11) 등록번호 10-0756806

(24) 등록일자 2007년08월31일

(73) 특허권자

#### 주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자

#### 박주온

서울특별시중구신당6동846파라다이스아파트1208호

(74) 대리인

이후동, 특허법인태평양

(54) 반도체소자의 캐패시터 형성방법

#### (57) 요 약

본 발명은 반도체 소자의 캐패시터 형성방법에 관한 것으로, 콘택플러그에 구비되는 층간절연막을 반도체기판 상부에 형성하고 상기 층간절연막 상부에 저장전극용 산화막을 형성한 다음, 상기 저장전극용 산화막에 저장전극 영역을 정의하되, 라인/스페이스 패턴을 갖는 두 개의 마스크를 저장전극 영역에서 중첩되도록 교차 이중 노광시켜 정의하고 상기 전체표면상부를 평탄화시키는 질화막을 형성한 다음, 상기 산화막과의 식각선택비 차이를 이용하여 상기 질화막을 평탄화식각하고 상기 산화막을 노출시켜 제거함으로써 상기 저장전극영역 및 콘택플러그를 노출시키고 상기 콘택플러그에 접속되는 저장전극용 도전층을 전체표면상부에 형성한 다음, 전체표면상부에 감광막을 도포하고 상기 감광막과 저장전극용 도전층을 평탄화식각하여 상기 질화막을 노출시킨 다음, 상기 감광막을 제거하여 콘케이브형 저장전극을 용이하게 형성하되, 해상도 향상, CD 균일성 향상 및 수율을 향상시킬 수 있는 기술이다.

#### 대표도 - 도1a

#### 특허청구의 범위

#### 청구항 1

콘택플러그를 포함하는 층간절연막을 반도체기판 상부에 형성하는 공정과,

상기 층간절연막 상부에 저장전극용 산화막을 형성하는 공정과,

상기 저장전극용 산화막을 부분 식각하되, 두 개의 라인/스페이스 패턴용 마스크를 이용하여 저장전극 영역에서 서로 교차하는 이중 노광 공정을 실시하여 저장전극영역을 정의하는 산화막 패턴을 형성하는 공정과.

상기 전체표면상부를 평탄화시키는 질화막을 형성하는 공정과,

상기 산화막과의 식각선택비 차이를 이용하여 상기 질화막을 평탄화식각하고 상기 산화막 패턴을 노출시켜 제거 함으로써 상기 저장전극영역 및 콘택플러그를 노출시키는 공정과,

상기 콘택플러그에 접속되는 저장전극용 도전층을 전체표면상부에 형성하는 공정과,

전체표면상부에 감광막을 도포하고 상기 감광막과 저장전극용 도전층을 평탄화식각하여 상기 질화막을 노출시키는 공정 및

상기 감광막을 제거하여 콘케이브형 저장전극을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체소자의 캐 패시터 형성방법.

#### 청구항 2

제 1 항에 있어서,

상기 산화막은 TEOS, BPSG 또는 PSG 로 형성하는 것을 특징으로하는 반도체소자의 캐패시터 형성방법.

#### 청구항 3

제 1 항에 있어서,

상기 산화막과 질화막은  $1\sim 30000$  Å 두께로 형성하는 것을 특징으로하는 반도체소자의 캐패시터 형성방법.

#### 청구항 4

제 1 항에 있어서,

상기 산화막의 제거공정은 순수와의 혼합비가 9 : 1 인 BOE 용액을 이용하여 실시하는 것을 특징으로하는 반도 체소자의 캐패시터 형성방법.

### 명세서

#### 발명의 상세한 설명

#### 발명의 목적

### 발명이 속하는 기술 및 그 분야의 종래기술

- <7> 본 발명은 반도체소자의 캐패시터 형성방법에 관한 것으로, 특히 반도체소자의 고집적화에 충분한 정전용량을 확보하는 콘케이브 (concave) 형 캐패시터 형성공정인 수직한 라인/스페이스 패턴과 수평한 라인/스페이스 패 턴을 교차시켜 더블 노광 (double expose) 시킴으로써 미세한 콘케이브형 섬패턴을 형성할 수 있어 리소그래 피 공정 마진을 향상시킬 수 있는 기술에 관한 것이다.

- <8> 반도체소자가 고집적화되어 셀 크기가 감소됨에따라 저장전극의 표면적에 비례하는 정전용량을 충분히 확보하기 가 어려워지고 있다.

- 특히, 단위셀이 하나의 모스 트랜지스터와 캐패시터로 구성되는 디램 소자는 칩에서 많은 면적을 차지하는 캐패시터의 정전용량을 크게 하면서, 면적을 줄이는 것이 디램 소자의 고집적화에 중요한 요인이 된다.

- <10> 그래서,  $(\epsilon_0 \times \epsilon_r \times A)/T$  (단, 상기  $\epsilon_0$ 는 진공유전율, 상기  $\epsilon_r$ 은 유전막의 유전율, 상기 A는 저

장전극의 면적 그리고 상기 T 는 유전막의 두께 ) 로 표시되는 캐패시터의 정전용량 C 를 증가시키기 위하여, 유전상수가 높은 물질을 유전체막으로 사용하거나, 유전체막을 얇게 형성하거나 또는 저장전극의 표면적을 증가 시키는 등의 방법을 사용하였다.

- <11> 상기 저장전극의 표면적을 증가시키는 방법으로 콘케이브 캐패시터 패턴이 있다.

- <12> 상기 콘케이브형 캐패시터는 동일 크기에서 라인/스페이스 패턴보다 잠상 콘트라스트 (aerial image contrast) 가 낮아 미세 패턴을 구현하기 어렵다.

- <13> 가령, 패터닝이 가능하더라고 상대적으로 리소그래피 마진이 부족할 뿐만아니라 요구된 CD ( critical dimension ) 균일성 불량이 캐패시터의 전기적 특성을 저하시켜 소자소자 동작에 막대한 지장을 초래한다.

- <14> 또한, DOF (depth of focus ) 부족은 칩의 가장자리에서 패턴의 일부가 오픈되지 않는 문제점을 유발 할 수도 있어 소자의 안정적 동작이 어렵고 그에 따른 수율 향상을 기대할 수 없다.

- <15> 따라서, 종래에는 이러한 문제점을 해결하기 위하여, 조명 방식을 광원을 마스크상에 경사시킴으로써 0차 광과 +1,-1차 회절광 중에서 한쪽 빔(beam), 즉 2beam만을 사용함으로써 해상력을 향상시키는 이른바 사입사 조명방 법을 사용하고 있으나 리소그래피 마진이 부족하다.

- <16> 다른 방법은, 상대적으로 프로젝션 렌즈 NA ( projection lens numerical aperture ) 가 큰 노광 장비를 적용하는 방법이 있다. 하지만, 이 방법은 추가적으로 노광장비를 구입해야 하는 문제가 있어 원가 상승을 가져오는 원인이 된다.

- <17> 상기한 바와같이 종래기술에 따른 반도체소자의 캐패시터 형성방법은, 콘케이브형 캐패시터를 형성하기 위한 패터닝 공정시 사입사 조명방법을 이용하였으나 CD 균일성이 낮아 적용하기 어려운 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은 상기한 바와 같은 종래기술의 문제점을 해소시키기 위하여, 캐패시터와 같은 섬 패턴보다 잠상 이미지 콘트라스트가 좋은 라인/스페이스 패턴을 적절히 이용하여 리소그래피 마진이 충분한 캐패시터를 형성함으로써 반도체소자의 고집적화에 충분한 정전용량을 확보할 수 있도록 하는 반도체소자의 캐패시터 형성방법을 제공하는데 그 목적이 있다.

#### 발명의 구성 및 작용

<19> 상기 목적 달성을 위해 본 발명에 따른 반도체소자의 캐패시터 형성방법은,

콘택플러그를 포함하는 층간절연막을 반도체기판 상부에 형성하는 공정과,

상기 층간절연막 상부에 저장전극용 산화막을 형성하는 공정과.

상기 저장전극용 산화막을 부분 식각하되, 두 개의 라인/스페이스 패턴용 마스크를 이용하여 저장전극 영역에서 서로 교차하는 이중 노광 공정을 실시하여 저장전극영역을 정의하는 산화막 패턴을 형성하는 공정과,

상기 전체표면상부를 평탄화시키는 질화막을 형성하는 공정과,

상기 산화막과의 식각선택비 차이를 이용하여 상기 질화막을 평탄화식각하고 상기 산화막 패턴을 노출시켜 제거 함으로써 상기 저장전극영역 및 콘택플러그를 노출시키는 공정과,

상기 콘택플러그에 접속되는 저장전극용 도전층을 전체표면상부에 형성하는 공정과,

전체표면상부에 감광막을 도포하고 상기 감광막과 저장전극용 도전층을 평탄화식각하여 상기 질화막을 노출시키는 공정 및

- <20> 상기 감광막을 제거하여 콘케이브형 저장전극을 형성하는 공정을 포함하는 것을 특징으로 한다.

- <21> 삭제

- <22> 삭제

- <23> 삭제

- <24> 삭제

- <25> 삭제

- <26> 삭제

- <27> 삭제

- <28> 한편, 이상의 목적을 달성하기 위한 본 발명의 원리는 다음과 같다.

- 반도체소자의 급속한 발전은 MFS ( minimum pitcher size ) 가 점점 작아지게 되며 리소그래피 공정에서는 해상 도 ( resolution ) 및 CD 균일성 확보를 위해 NA 가 큰 장비에 대한 투자를 필요로 한다. 이러한, 장비투자는 원가 상승의 원인이 되므로 새로운 장비 투자없이 리소그패리 마진을 확보할 수 있는 옵티컬 익스텐션 ( optical extension ) 기술이 필요하다.

- <30> 본 발명은 캐패시터에 관한 것으로서, 종래의 캐패시터 형성방법은 단일 노광 (single expose)에 의한 방법으로 공정 단순화 측면에서는 유리하지만 라인/스페이스 패턴과 같은 타 층에 비하여 잠상 콘트라스트가 낮아해상도 측면에서 불리할 뿐만아니라 CD 균일도 측면에서도 많은 취약점을 가지고 있다.

- <31> 따라서, 라인/스페이스 패턴과 같이 잠상 콘트라스트가 좋은 패턴을 수평방향과 수직 방향으로 교차 중첩 노광하는 방법으로 캐패시터를 형성함으로써 콘케이브형의 저장전극을 용이하게 형성할 수 있다. 이때, 저장전극영역을 정의하는 감광막이 포지티브냐 네가티브냐에 따라 후속 진행공정이 달라질 수 있다.

- <32> 여기서, 잠상 콘트라스트가 좋은 라인/스페이스 패턴의 효과를 증폭시킬 수 있는 익스트림 오프 어식스 (extreme off-axis ) 인 다이폴 (dipole ) 과 같은 어퍼쳐 (aperture )를 이용하면 더욱 미세한 패턴을 얻을 수 있다.

- <33> 라인/스페이스 패턴을 구현하는데 가장 좋은 것으로 알려진 다이폴과 같은 일루미네이션 (illumination) 방법을 라인/스페이스 패턴이 아닌 캐패시터의 저장전극을 구현하는데 잘 이용하면 리소그래피 마진을 극대화 할 수있을 것이다.

- <34> 하지만, 다이폴 일루미네이션 방법은 폴이 장작된 축과 직교하는 패턴은 해상도가 극대화되지만 같은 축선상에 있는 패턴은 기존보다 못한 해상도를 보여준다.

- <35> 따라서, 다이폴 일루미네이션의 방향성을 감안하여 교차 이중 중첩 노광을 하면 보다 극대화된 해상도 한계를 갖는 캐패시터 패턴을 얻을 수 있다.

- <36> 이하, 첨부된 도면을 참고로 하여 본 발명을 상세히 설명하기로 한다.

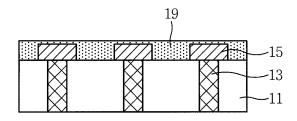

- <37> 도 1a 내지 도 1f 는 본 발명의 실시예에 따른 반도체소자의 캐패시터 형성방법을 도시한 단면도이다.

- <38> 도 1a를 참조하면, 상기 반도체기판(도시안됨)의 소자분리막, 불순물 접합영역, 워드라인, 비트라인 및 저장전 극 콘택플러그(13)를 포함하는 층간절연막(11)을 형성한다.

- <39> 전체표면상부에 저장전극용 산화막(15)을 1 ~ 30000 Å 두께 형성한다.

- <40> 이때, 상기 산화막(15)은 BPSG, PSG 또는 TEOS 로 형성한다.

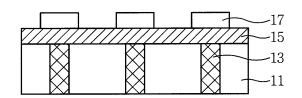

- <41> 그 다음, 상기 저장전극용 산화막(15) 상부에 제1감광막패턴(17)을 형성한다.

- <42> 이때, 상기 제1감광막패턴(17)은 두 개의 라인/스페이스 패턴용 마스크를 이용하여 저장전극 영역에서 서로 직 교하여 교차하는 이중 노광공정후 현상공정을 실시하여 저장전극영역이 차단되는 모양으로 형성한 것이다.

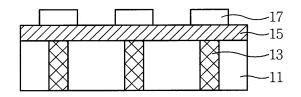

- <43> 도 1b를 참조하면, 상기 제1감광막패턴(17)을 마스크로 하여 상기 저장전극용 산화막(15)을 식각함으로써 산화막(15)패턴을 형성한다. 이때, 상술한 바와 같이 교차 이중 중첩 노광에 의하여 산화막(15)패턴이 사각형 형태로 형성되지 않고 콘케이브형으로 형성된다.

- <44> 그리고, 상기 제1감광막패턴(17)을 제거한다.

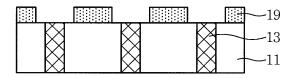

- <45> 도 1c를 참조하면, 상기 산화막(15)패턴 사이를 매립하는 질화막(19)을 전체표면상부에 1 ~ 30000 Å 두께로 형성한다.

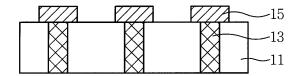

- <46> 도 1d를 참조하면, 상기 산화막(15)패턴이 노출될때 까지 상기 질화막(19)을 CMP 한다.

- <47> 그리고, 상기 질화막(19)과 산화막(15)패턴과의 식각선택비 차이를 이용하여 상기 산화막(15)패턴을 제거하여 상기 저장전극 콘택플러그(13) 및 저장전극 영역을 노출시키는 질화막(19)패턴을 형성한다.

- <48> 여기서, 상기 산화막(15)패턴의 제거공정은 순수와의 혼합비가 9 : 1 인 BOE 용액을 이용하여 실시한다.

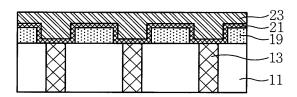

- <49> 도 1e를 참조하면, 상기 저장전극 콘택플러그(13)에 접속되는 저장전극용 도전층(21)을 전체표면상부에 형성한다.

- <50> 그리고, 상기 저장전극 영역을 매립하는 제2감광막(23)을 전체표면상부에 형성한다.

- <51> 그리고, CMP 공정으로 상기 제2감광막(23)과 저장전극용 도전층(21)을 식각하되, 상기 질화막(19)패턴을 노출시킬 때 까지 CMP한다.

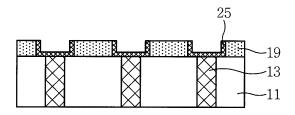

- <52> 그 다음, 상기 제2감광막(23)을 제거함으로써 콘케이브형 캐패시터의 저장전극(25)을 형성한다.

#### 발명의 효과

<53> 이상에서 설명한 바와 같이 본 발명에 따른 반도체소자의 캐패시터 형성방법은, 라인/스페이스 패턴을 갖는 두 개의 마스크를 저장전극 영역에서 서로 교차하게 형성하여 저장전극 영역을 정의함으로써 해상도 및 CD 균일성을 향상시키고 공정을 안정화시키며 디포커스 (defocus)에 의한 패턴 불량을 제거할 수 있어 소자의 수율을향상시킬 수 있는 효과를 제공한다.

#### 도면의 간단한 설명

- <1> 도 1a 내지 도 1f 는 본 발명의 실시예에 따른 반도체소자의 캐패시터 형성방법을 나타낸 단면도.

- <2> < 도면의 주요주분에 대한 부호의 설명>

- <3> 11 : 충간절연막 13 : 콘택플러그

- <4> 17 : 제1감광막패턴 19 : 질화막

- <5> 21 : 저장전극용 도전층 23 : 제2감광막

- <6> 25 : 저장전극

#### 도면

#### 도면1a

## 도면1b

## 도면1c

### *도면1d*

## *도면1e*

## *도면1f*