US006667191B1

US 6,667,191 B1

Dec. 23, 2003

# (12) United States Patent

# McLellan et al.

## (54) CHIP SCALE INTEGRATED CIRCUIT PACKAGE

- (75) Inventors: Neil McLellan, Mid Levels (HK); Wing Him Lau, Yuen Long (HK); Tak Sang Yeung, Tin Shui Wai (HK); Onofre A. Rulloda, Jr., Riviera Gardens (HK)

- (73) Assignee: Asat Ltd., New Territories (HK)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 10/211,567

- (22) Filed: Aug. 5, 2002

- (51) Int. Cl.<sup>7</sup> ..... H01L 21/44; H01L 23/34

- (52) U.S. Cl. ..... 438/121; 438/122; 438/124;

- 438/125; 438/126; 438/127; 257/712; 257/720; 257/777; 257/780; 257/787

## References Cited

(10) Patent No.:

(45) Date of Patent:

### **U.S. PATENT DOCUMENTS**

| 6,392,290 B1 * 5/2002  | Kasem et al 257/774     |

|------------------------|-------------------------|

| 6,429,530 B1 * 8/2002  | Chen 438/126            |

| 6,441,475 B2 * 8/2002  | Zandman et al 257/710   |

| 6,489,557 B2 * 12/2002 | Eskildsen et al 257/788 |

| 6,498,387 B1 * 12/2002 | Yang 257/753            |

| 6,518,089 B2 * 2/2003  | Coyle 438/106           |

\* cited by examiner

(56)

Primary Examiner-Kevin M. Picardat

(74) Attorney, Agent, or Firm-Keating & Bennett, LLP

# (57) ABSTRACT

An integrated circuit package including a silicon wafer, a plate of intermetallic compound fixed to the back surface of the silicon wafer and a plurality of solder ball contacts. The solder ball contacts are in electrical connection with die circuitry on the front surface of the silicon wafer.

## 20 Claims, 2 Drawing Sheets

FIG. 1D

FIG. 1F

25

30

35

45

60

65

# CHIP SCALE INTEGRATED CIRCUIT PACKAGE

#### FIELD OF THE INVENTION

This invention relates in general to integrated circuit packaging, and more particularly to a chip scale integrated circuit package with improved thermo-mechanical properties.

## BACKGROUND OF THE INVENTION

Wafer scale, or chip scale packages offer a high density integrated circuit package in comparison to other integrated circuit (IC) packages. Traditionally, chip scale packages 15 have been the preferred packages for use in electronic devices. This is due to the relatively small size of the chip scale package thereby allowing the use of a small circuit board which contains the IC package in the electronic device.

One typical chip scale package of the prior art includes a flip chip integrated circuit with a redistribution layer on the surface of the die to spread the interconnects over the die surface. The redistribution layer is typically an organic dielectric with copper traces routing to the bump areas on the die. These packages have achieved limited use in the industry because they suffer from disadvantages.

One of these disadvantages is that there exists a thermally induced stress due to the mismatch in coefficients of thermal expansion between the die and the motherboard when the chip is soldered to the system motherboard. More specifically, the silicon die has a low coefficient of thermal expansion, typically in the range of about 3 ppm/° C. compared to the high coefficient of thermal expansion (CTE) of the motherboard. Motherboards are typically made from epoxy resin and have a CTE of about 22 ppm/° C. Silicon is a rigid material with a high modulus of elasticity. During temperature cycling, the CTE mismatch creates stresses and strains concentrated on the interconnects between the die and substrate. In extreme cases fatigue failure occurs in the solder joint after a very small number of thermal cycles. Thus, this flip chip design has achieved limited use in a small number of applications using expensive ceramic substrates in controlled environments.

With the introduction of organic underfill techniques, it was determined that by sealing the interface between the die and the motherboard with a connective layer of epoxy adhesive the stress of the thermal mismatch between die and motherboard is spread across the total area under the die.  $_{50}$ Thus, the stress is spaced across a large area of epoxy rather than concentrated at the weaker solder joints. While this solution is somewhat effective, the implementation of this direct attach technique suffers problems.

One particular problem is that the use of the underfill on 55 the motherboard results in a permanent chip attach. Once a chip is attached, it is extremely difficult to remove or rework it, therefore leading to high scrap rates and other problems. At the time this technique was introduced, technology in motherboard routing could not accommodate the interconnect densities of the direct chip attach. Although motherboard technology has advanced since the introduction of the direct chip attach technique, the use of underfill still suffers disadvantages such as permanent chip attach, which precludes large-scale use of the technique.

Variations to this design have been introduced for a variety of reasons. For example, a discrete ball and array

package, commonly referred to as a flip chip ball grid array package has a flipped chip and is underfilled to a discrete component. This permits testing and more effective placement on the motherboard. These devices have achieved common usage but still suffer from the disadvantage of complex construction and high expense. Further, because of the complex construction, these packages generally require more than one test to ensure quality.

Accordingly, it is an object of an aspect of the present 10 invention to provide a chip scale integrated circuit package with improved thermo-mechanical properties.

#### SUMMARY OF THE INVENTION

In an aspect of the present invention, there is provided an integrated circuit package that includes a silicon wafer, a plate of intermetallic compound fixed to the back surface of the silicon wafer and a plurality of solder ball contacts. The solder ball contacts are in electrical connection with die circuitry on the front surface of the silicon wafer.

In another aspect of the present invention, there is pro-20 vided a process for fabricating an integrated circuit package including backgrinding a silicon water fixing a first surface of the silicon wafer to a plate of intermetallic compound, adding a redistribution layer to a second surface of the silicon wafer, the second surface opposite the first surface, connecting a plurality of solder balls to die circuitry of the silicon wafer to provide a plurality of joined integrated circuit packages, and singulating individual integrated circuit packages from the joined integrated circuit packages.

In yet another aspect of the present invention, there is provided a chip scale integrated circuit package. The chip scale integrated circuit package includes a silicon wafer back ground to a thickness of between about 25 microns and about 250 microns, and a plate of intermetallic compound fixed to a back surface of the silicon wafer. The intermetallic compound has a coefficient of thermal expansion of about 22 ppm/° C. and an elastic modulus greater than the elastic modulus of the silicon wafer. A redistribution layer is disposed on a surface of the silicon wafer and covers die circuitry on the silicon wafer. A plurality of solder ball contacts are fixed to pads of the redistribution layer and are in electrical connection with die circuitry on the front surface of the silicon wafer.

In an aspect of the present invention, the thermomechanical properties of the chip-scale IC package are adapted to approach the temperature induced strain of the motherboard.

Advantageously, the use of an intermetallic compound such as copper aluminide fixed to the silicon wafer provides a hybrid with thermo-mechanical properties that approach that of the motherboard. In one aspect, the coefficient of thermal expansion is close to that of the motherboard and the elastic modulus is high to restrain the silicon.

In another aspect, the package is tested prior to saw singulation. Advantageously, only one test is carried out on each package.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention will be better understood with reference to the drawings, and the following description, in which

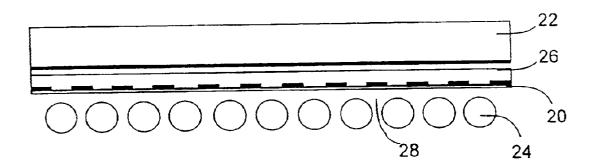

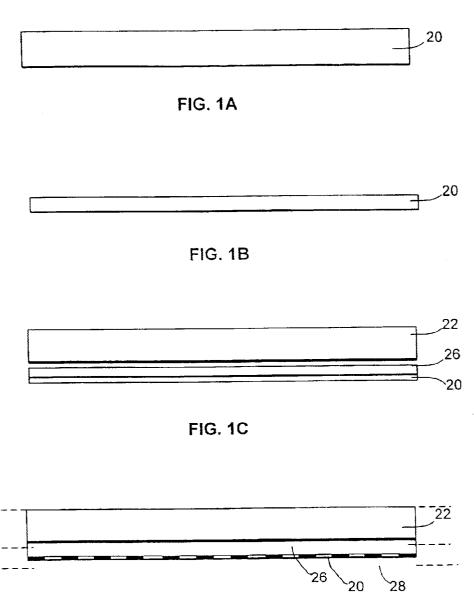

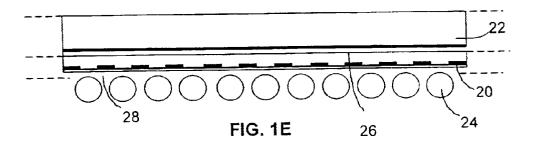

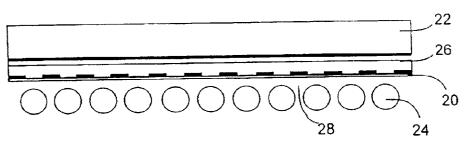

FIGS. 1A to 1F show processing steps for manufacturing an improved chip scale integrated circuit package according to an embodiment of the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Reference is made to FIGS. 1A to 1F to describe a process for the manufacture of an improved chip scale integrated

10

35

45

50

circuit package according to an embodiment of the present invention. FIG. 1A shows an elevation view of a silicon wafer indicated by the numeral 20. It will be understood that the silicon wafer 20 includes the die circuitry or chip patterns on a front surface thereof.

A back surface of the silicon wafer **20** is then ground down using a backgrinding technique (FIG. 1B), as will be understood by those of skill in the art. Preferably the silicon wafer **20** is ground to a thickness between about 25 microns and about 250 microns.

The back surface of the thinned silicon wafer 20 is then fixed to a plate of intermetallic compound 22 using an organic adhesive 26 (FIG. 1C). Intermetallic compounds, also referred to as bulk intermetallics, are chemical compounds based on definite atomic formulas, each with a fixed <sup>15</sup> or narrow range of chemical composition. Thus intermetallic compounds are stoichiometric combinations of metallic ions that form bonded matrices of crystals having desirable thermo-mechanical properties. There are a wide range of 20 intermetallic compounds, the properties of which vary significantly. Preferably, the intermetallic has a CTE in the range of about 18 to about 26 ppm/° C., and more preferably the intermetallic has a CTE of about 22 ppm/° C. Preferably the intermetallic has a high elastic modulus. In the present 25 embodiment, the thinned silicon wafer 20 is laminated to a moderately thicker plate of copper aluminide (CuAl<sub>3</sub>) using the organic adhesive 26. The copper aluminide has a CTE of about 22 ppm/° C. and a modulus of elasticity that is higher than that of silicon. 30

Next, a redistribution layer 28 is added on the front surface of the of the silicon wafer. The redistribution layer 28 is a dieletric layer that includes a coating of polyimide over die circuitry. Holes are etched in the polyimide layer to coincide with peripheral terminals in the die circuitry. Copper is patterned to connect the terminals to an array of solder pads on top of the polyimide layer. The solder pads are then masked with polyimide (FIG. 1D).

Solder balls 24 (or bumps) are then placed on the pads and reflowed using known reflow techniques to fix the solder  $_{40}$  balls 24 to the pads (FIG. 1E). The polyimide masking is used to inhibit solder from wetting down the copper interconnects from the array of pads to the die circuitry.

The package is then tested prior to singulation.

Next, the package is saw singulated (FIG. 1F).

The present invention has been described by way of example. Numerous modifications and variations to the embodiment described herein will occur to those of skill in the art. For example, the thinned silicon wafer **20** can be attached to the intermetallic compound **22** using several other techniques such as by use of liquid epoxy, a B stage film epoxy or a thermoplastic film. Also, other intermetallic compounds can be used. A list of exemplary intermetallic compounds is included below.

| CoAl                            | HfAl <sub>3</sub>               | Nb <sub>3</sub> Al | ZrAl <sub>2</sub>               |

|---------------------------------|---------------------------------|--------------------|---------------------------------|

| FeAl <sub>2</sub>               | $Hf_3Al_2$                      | NiĂl               | $ZrAl_3$                        |

| FeAl <sub>3</sub>               | LiAl                            | TaAl               | $Zr_4Al_3$                      |

| Fe <sub>2</sub> Al <sub>5</sub> | Mo <sub>3</sub> Al              | $TaAl_3$           |                                 |

| HfAl                            | Mo <sub>3</sub> Al <sub>8</sub> | TiAl               |                                 |

| $HfAl_2$                        | NbAl <sub>3</sub>               | TiAl <sub>3</sub>  |                                 |

| CoB                             | $Fe_2B$                         | NiB                | $Ni_4B_3$                       |

| $Co_2B$                         | MnB                             | $Ni_2B$            |                                 |

| FeB                             | $Mn_2B$                         | Ni <sub>3</sub> B  |                                 |

| $CeSi_2$                        | FeSi                            | PdSi               | $TbSi_2$                        |

| CoSi                            | FeSi <sub>2</sub>               | Pd <sub>2</sub> Si | Tb <sub>5</sub> Si <sub>3</sub> |

| -continued |                    |                                 |                                    |                                |  |

|------------|--------------------|---------------------------------|------------------------------------|--------------------------------|--|

| С          | oSi <sub>2</sub>   | Fe <sub>2</sub> Si              | PrSi <sub>2</sub>                  | TiSi <sub>2</sub>              |  |

| C          | $O_2Si$            | GdSi <sub>2</sub>               | PtSi                               | VSi <sub>2</sub>               |  |

|            | Si                 | MnSi                            | $Pt_2Si$                           | V <sub>3</sub> Si              |  |

| Cı         | Si <sub>2</sub>    | MnSi <sub>2</sub>               | ReSi                               | V <sub>5</sub> Si <sub>3</sub> |  |

| Cı         | r₃Si               | Mn <sub>5</sub> Si <sub>3</sub> | ReSi <sub>2</sub>                  | WSi <sub>2</sub>               |  |

| Ct         | 1 <sub>3</sub> Si  | MoSi <sub>2</sub>               | Re <sub>2</sub> Si <sub>5</sub>    | Ysi                            |  |

| Ct         | ı₅Si               | NbSi <sub>2</sub>               | Si <sub>4</sub> Zr <sub>5</sub>    | Y <sub>3</sub> Si <sub>5</sub> |  |

| D          | ySi <sub>2</sub>   | NdSi <sub>2</sub>               | SmSi <sub>2</sub>                  | Y <sub>5</sub> Si <sub>3</sub> |  |

| Er         | Si <sub>2</sub>    | NiSi                            | SrSi <sub>2</sub>                  | Y <sub>5</sub> Si <sub>4</sub> |  |

| Eι         | ıSi <sub>2</sub>   | Ni <sub>2</sub> Si              | TaSi <sub>2</sub>                  | YbSi <sub>2</sub>              |  |

| Co         | oNb                | Fe <sub>2</sub> Ta              | Nb <sub>3</sub> Ir                 | TiAl <sub>3</sub>              |  |

| Co         | oSm <sub>2</sub>   | Fe <sub>2</sub> Ti              | Nd <sub>2</sub> Fe <sub>14</sub> B | TiAu                           |  |

|            | οZr                | Fe <sub>2</sub> Zr              | NiHf                               | TiAu <sub>2</sub>              |  |

| Co         | oZr <sub>2</sub>   | Fe <sub>3</sub> Y               | NiTi                               | TiCo                           |  |

| Co         | $D_2$ Zr           | HfCo                            | NiY                                | TiCu                           |  |

| Ct         | uΥ                 | $HfCo_2$                        | NiZr                               | $TiMn_2$                       |  |

| Ct         | ιZr                | HfCu <sub>3</sub>               | NiZr <sub>2</sub>                  | TiNi <sub>3</sub>              |  |

| Cu         | u₄Zr               | Hf <sub>2</sub> Cu              | Ni <sub>2</sub>                    | TiPd                           |  |

| Fe         | $x_{17}Y_2$        | Hf <sub>2</sub> Cu <sub>3</sub> | Ni <sub>2</sub> Ta                 | TiPd <sub>3</sub>              |  |

| Fe         | ₂ <sub>17</sub> Yb | LaNi                            | Ni <sub>3</sub> Nb                 | TiPt                           |  |

| Fe         | Nb                 | LaNi <sub>2</sub>               | Ni <sub>3</sub> Ta                 | TiSi <sub>2</sub>              |  |

| Fe         | Si                 | LaPt                            | Ni <sub>5</sub> Y                  | $Ti_2N_1$                      |  |

| Fe         | Ta                 | LaPt <sub>5</sub>               | Ni <sub>5</sub> Yb                 | Ti₃Au                          |  |

|            | Ti                 | La <sub>3</sub> Ni              | Ni <sub>7</sub> Hf <sub>2</sub>    | VSi <sub>2</sub>               |  |

| Fe         | 23Tb5              | Mn11Si19                        | Ni <sub>7</sub> Zr <sub>2</sub>    | WSi <sub>2</sub>               |  |

|            | $Y_{23}Y_{6}$      | MnSi <sub>2</sub>               | $Sm_2Co_{17}$                      | ZrCr <sub>2</sub>              |  |

| Fe         | $_{2}Hf$           | $MoSi_2$                        | TaAl <sub>3</sub>                  | $ZrSi_2$                       |  |

| Fe         | $2^{\rm Nb}$       | NbSi <sub>2</sub>               | TaSi <sub>2</sub>                  | Zr <sub>2</sub> Cu             |  |

It will be appreciated that any intermetallic with the desired material properties can be used. All such modifications and variations are believed to be within the scope and sphere of the present invention.

What is claimed is:

**1**. A process for fabricating integrated circuit packages comprising:

backgrinding a silicon wafer;

- fixing a first surface of said silicon wafer to a plate of intermetallic compound;

- adding a redistribution layer to a second surface of said silicon wafer, said second surface opposite said first surface;

- connecting a plurality of solder balls to die circuitry of said silicon wafer to provide a plurality of joined integrated circuit packages; and

- singulating individual integrated circuit packages from said joined integrated circuit packages.

2. The process for fabricating an integrated circuit package according to a claim 1 wherein said integrated circuit packages are tested prior to singulating.

**3**. The process for fabricating an integrated circuit package according to claim **1** wherein said backgrinding includes grinding and polishing said silicon wafer.

4. The process of fabricating an integrated circuit package according to claim 1 wherein said plate of intermetallic compound comprises an intermetallic compound having a 55 coefficient of thermal expansion of from about 18 ppm/° C. to about 26 ppm/° C.

5. The process for fabricating an integrated circuit package according to claim 1 wherein said plate of intermetallic compound comprises an intermetallic compound having a

60 coefficient of thermal expansion of about 22 ppm/° C.

6. The process for fabricating an integrated circuit package according to claim 1 wherein said plate of intermetallic compound is comprised of an intermetallic compound selected from the group consisting of: CoAl, FeAl<sub>2</sub>, FeAl<sub>3</sub>,

65 Fe<sub>2</sub>Al<sub>5</sub>, CuAl<sub>3</sub>, HfAl, HfAl<sub>2</sub>, HfAl<sub>3</sub>, HF<sub>3</sub>Al<sub>2</sub>, LiAl, Mo<sub>3</sub>Al, Mo<sub>3</sub>Al<sub>8</sub>, NbAl<sub>3</sub>, Nb<sub>3</sub>Al, NiAl, TaAl, TaAl<sub>3</sub>, TiAl, TiAl<sub>3</sub>, ZrAl<sub>2</sub>, ZrAl<sub>3</sub>, CoB, Co<sub>2</sub>B, FeB, Fe<sub>2</sub>B, MnB, Mn<sub>2</sub>B, NiB,

Ni<sub>2</sub>B, Ni<sub>3</sub>B, Ni<sub>4</sub>B<sub>3</sub>, CeSi<sub>2</sub>, CoSi, CoSi<sub>2</sub>, Co<sub>2</sub>Si, CrSi, CrSi<sub>2</sub>, Cr<sub>3</sub>Si, Cu<sub>3</sub>Si, Cu<sub>5</sub>Si, DySi<sub>2</sub>, ErSi<sub>2</sub>, EuSi<sub>2</sub>, FeSi, FeSi<sub>2</sub>, Fe<sub>2</sub>Si, GdSi<sub>2</sub>, MnSi, MnSi<sub>2</sub>, Mn<sub>5</sub>Si<sub>3</sub>, MoSi<sub>2</sub>, NbSi<sub>2</sub>, NdSi<sub>2</sub>, NiSi, Ni<sub>2</sub>Si, PdSi, Pd<sub>2</sub>Si, PrSi<sub>2</sub>, PtSi, Pt<sub>2</sub>Si, ReSi, ReSi<sub>2</sub>, Re<sub>2</sub>Si<sub>5</sub>, Si<sub>4</sub>Zr<sub>5</sub>, SmSi<sub>2</sub>, SrSi<sub>2</sub>, TaSi<sub>2</sub>, TbSi<sub>2</sub>, Tb<sub>5</sub>Si<sub>3</sub>, TiSi<sub>2</sub>, 5 VSi<sub>2</sub>, V<sub>3</sub>Si, V<sub>5</sub>Si<sub>3</sub>, WSi<sub>2</sub>, Ysi, Y<sub>3</sub>Si<sub>5</sub>, Y<sub>5</sub>Si<sub>3</sub>, Y<sub>5</sub>Si<sub>4</sub>, CoNb, CoSm<sub>2</sub>, CoZr, CoZr<sub>2</sub>, Co<sub>2</sub>Zr, CuY, CuZr, Cu<sub>4</sub>Zr, Fe<sub>17</sub>Y<sub>2</sub>, Fe<sub>17</sub>Yb, FeNb, FeSi, FeTa, FeTi, Fe<sub>23</sub>Tb<sub>5</sub>, Fe<sub>23</sub>Y<sub>6</sub>, Fe<sub>2</sub>Hf, Fe<sub>2</sub>Nb, Fe<sub>2</sub>Ta, Fe<sub>2</sub>Ti, Fe<sub>2</sub>Zr, Fe<sub>3</sub>Y, HfCo, HfCo<sub>2</sub>, HfCu<sub>3</sub>, Hf<sub>2</sub>Cu, Hf<sub>2</sub>Cu<sub>3</sub>, LaNi, LaNi<sub>5</sub>, LaPt, LaPT<sub>5</sub>, La<sub>3</sub>Ni, 10 Mn<sub>11</sub>Si<sub>19</sub>, MnSi<sub>2</sub>, MoSi<sub>2</sub>, NbSi<sub>2</sub>, Nb<sub>3</sub>Ir, Nd<sub>2</sub>Fe<sub>14</sub>B, NiHf, NiTi, NiY, NiZr, NiZr<sub>2</sub>, Ni<sub>2</sub>Ta, Ni<sub>3</sub>Nb, Ni<sub>3</sub>Ta, Ni<sub>5</sub>Y, Ni<sub>5</sub>Yb, Ni<sub>7</sub>Hf<sub>2</sub>, Ni<sub>7</sub>Zr<sub>2</sub>, Sm<sub>2</sub>Co<sub>17</sub>, TaAl<sub>3</sub>, TaSi<sub>2</sub>, TiAl<sub>3</sub>, TiAu, TiAu<sub>2</sub>, TiCo, TiCu, TiMn<sub>2</sub>, TiNi<sub>3</sub>, TiPd, TiPd<sub>3</sub>, TiPt, TiSi<sub>2</sub>, Ti<sub>2</sub>Ni, Ti<sub>3</sub>Au, VSi<sub>2</sub>, WSi<sub>2</sub>, ZrCr<sub>2</sub>, ZrSi<sub>2</sub> and Zr<sub>2</sub>Cu. 15

7. The process for fabricating an integrated circuit package according to claim 1 wherein said plate of intermetallic compound comprises CuAl<sub>3</sub>.

**8**. The process for fabricating an integrated circuit package according to claim **1** wherein said intermetallic com- 20 pound has a modulus of elasticity at least in the range of the modulus of elasticity of silicon.

**9**. The process for fabricating an integrated circuit package according to claim **3** wherein said silicon wafer is ground to a thickness of between about 50 microns and 25 about 250 microns.

**10.** The process of fabricating an integrated circuit package according to claim **1** wherein said redistribution layer comprises a dieletric layer including polyimide with copper interconnects between terminals of the die circuitry and an 30 array of solder pads on said polyimide.

11. The process of fabricating an integrated circuit package according to claim 10 wherein said solder ball contacts are fixed to said solder pads.

12. An integrated circuit package comprising:

a silicon wafer;

- a plate of intermetallic compound fixed to a back surface of said silicon wafer; and

- a plurality of solder ball contacts in electrical connection 4 with die circuitry on a front surface of said silicon wafer.

**13**. The integrated circuit package according to claim **12** wherein said plate of intermetallic compound comprises an intermetallic compound having a coefficient of thermal expansion of from about 18 ppm/° C. to about 26 ppm/° C.

14. The integrated circuit package according to claim 12 wherein said plate of intermetallic compound comprises an intermetallic compound having a coefficient of thermal expansion of about 22 ppm/° C.

**15**. The integrated circuit package according to claim **12** <sup>50</sup> wherein said plate of intermetallic compound is comprised

6

of an intermetallic compound selected from the group consisting of: CoAl, FeAl<sub>2</sub>, FeAl<sub>3</sub>, Fe<sub>2</sub>Al<sub>5</sub>, CuAl<sub>3</sub>, HfAl, HfAl<sub>2</sub>, HfAl<sub>3</sub>, Hf<sub>3</sub>Al<sub>2</sub>, LiAl, Mo<sub>3</sub>Al, Mo<sub>3</sub>Al<sub>8</sub>, NbAl<sub>3</sub>, Nb<sub>3</sub>Al, NiAl, TaAl<sub>3</sub>, TiAl, TiAl<sub>3</sub>, ZrAl<sub>2</sub>, ZrAl<sub>3</sub>, Zr<sub>4</sub>Al<sub>3</sub>, CoB, Co<sub>2</sub>B, FeB, Fe<sub>2</sub>B, MnB, Mn<sub>2</sub>B, NiB, Ni<sub>2</sub>B, Ni<sub>3</sub>B, Ni<sub>4</sub>B<sub>3</sub>, CeSi<sub>2</sub>, CoSi, CoSi<sub>2</sub>, Co<sub>2</sub>Si, CrSi, CrSi<sub>2</sub>, Cr<sub>3</sub>Si, Cu<sub>3</sub>Si, Cu<sub>5</sub>Si, DySi<sub>2</sub>, ErSi<sub>2</sub>, EuSi<sub>2</sub>, FeSi, FeSi<sub>2</sub>, Fe<sub>2</sub>Si, GdSi<sub>2</sub>, MnSi, MnSi<sub>2</sub>, Mn<sub>5</sub>Si<sub>3</sub>, MoSi<sub>2</sub>, NbSi<sub>2</sub>, NdSi<sub>2</sub>, NiSi, Ni<sub>2</sub>Si, PdSi, Pd<sub>2</sub>Si, PrSi<sub>2</sub>, PtSi, Pt<sub>2</sub>Si, ReSi, ReSi<sub>2</sub>, Re<sub>2</sub>Si<sub>5</sub>, Si<sub>4</sub>Sr<sub>5</sub>, SmSi<sub>2</sub>, SrSi<sub>2</sub>, TaSi<sub>2</sub>, TbSi<sub>2</sub>, Tb<sub>5</sub>Si<sub>3</sub>, TiSi<sub>2</sub>, VSi<sub>2</sub>, V<sub>3</sub>Si, V<sub>5</sub>Si<sub>3</sub>, WSi<sub>2</sub>, Ysi, Y<sub>3</sub>Si<sub>5</sub>, Y<sub>5</sub>Si<sub>3</sub>, Y<sub>5</sub>Si<sub>4</sub>, YbSi<sub>2</sub>, CoNb, CoSm<sub>2</sub>, CoZr, CoZr<sub>2</sub>, Co<sub>2</sub>Sr, CuY, CuZr, Cu<sub>4</sub>Zr, Fe<sub>17</sub>Y<sub>2</sub>, Fe<sub>17</sub>Yb, FeNb, FeSi, FeTa, FeTi, Fe<sub>23</sub>Tb<sub>5</sub>, Fe<sub>23</sub>Y<sub>6</sub>, Fe<sub>2</sub>Hf, Fe<sub>2</sub>Nb, Fe<sub>2</sub>Ta, Fe<sub>2</sub>Ti, Fe<sub>2</sub>Zr, Fe<sub>3</sub>Y, HfCo, HfCo<sub>2</sub>, HfCu<sub>3</sub>, Hf<sub>2</sub>Cu, Hf<sub>2</sub>Cu<sub>3</sub>, LaNi, LaNi<sub>5</sub>, LaPt, LaPt<sub>5</sub>, La<sub>3</sub>Ni, Mn<sub>11</sub>Si<sub>19</sub>, MnSi<sub>2</sub>, MoSi<sub>2</sub>, NbSi<sub>2</sub>, Nb<sub>3</sub>Ir, Nd<sub>2</sub>Fe<sub>14</sub>B, NiHf, NiTi, NiY, NiZr, NiZr<sub>2</sub>, Ni<sub>2</sub>, Ni<sub>2</sub>Ta, Ni<sub>3</sub>Nb, Ni<sub>3</sub>Ta, Ni<sub>5</sub>Y, Ni<sub>5</sub>Yb, Ni<sub>7</sub>Hf<sub>2</sub>, Ni<sub>7</sub>Zr<sub>2</sub>, Sm<sub>2</sub>Co<sub>17</sub>, TaAl<sub>3</sub>, TaSi<sub>2</sub>, TiAl<sub>3</sub>, TiAu, TiAu<sub>2</sub>, TiCo, TiCu, TiMn<sub>2</sub>, TiNi<sub>3</sub>, TiPd, TiPd<sub>3</sub>, TiPt, TiSi<sub>2</sub>, Ti<sub>2</sub>Ni, Ti<sub>3</sub>Au, VSi<sub>2</sub>, WSi<sub>2</sub>, ZrCr<sub>2</sub>, ZrSi<sub>2</sub>, and Zr<sub>2</sub>Cu.

16. The integrated circuit package according to claim 12 wherein said plate of intermetallic compound comprises CuAl<sub>3</sub>.

17. The integrated circuit package according to claim 12 wherein said intermetallic compound has a modulus of elasticity at least in the range of the modulus of elasticity of silicon.

18. The integrated circuit package according to claim 12 further comprising a redistribution layer disposed on a front surface of said silicon wafers, wherein said solder ball contacts are connected to an array of pads which are connected to peripheral terminals of the die circuitry.

19. The integrated circuit package according to claim 12

35 wherein said silicon wafer has a thickness of between about 25 microns and about 200 microns.

20. A chip scale integrated circuit package comprising:

- a silicon wafer back ground to a thickness of between about 25 microns and about 250 microns;

- a plate of intermetallic compound fixed to a back surface of said silicon wafer, the intermetallic compound having a coefficient of thermal expansion of about 22 ppm/° C. and an elastic modulus at least in the range of the elastic modulus of the silicon wafer;

- a redistribution layer on a surface of said silicon wafer and covering die circuitry on said silicon wafer; and

- a plurality of solder ball contacts fixed to pads of said redistribution layer in electrical connection with die circuitry on a front surface of said silicon wafer.

\* \* \* \* \*