US 20140182897A1

### (19) United States

# (12) Patent Application Publication LEE et al.

(10) **Pub. No.: US 2014/0182897 A1**(43) **Pub. Date:**Jul. 3, 2014

### (54) CIRCUIT BOARD AND METHOD OF MANUFACTURING THE SAME

## (71) Applicant: SAMSUNG ELECTRO-MECHANICS CO., LTD., Suwon (KR)

(72) Inventors: **Doo Hwan LEE**, Daejeon (KR); **Yul Kyo CHUNG**, Yongin (KR); **Yee Na SHIN**, Suwon (KR); **Seung Eun LEE**, Sungnam (KR)

(73) Assignee: **SAMSUNG ELECTRO-MECHANICS CO., LTD.**, Suwon (KR)

(21) Appl. No.: 14/143,682

(30)

(22) Filed: Dec. 30, 2013

D 44 4044 (TVD)

Dec. 31, 2012 (KR) ...... 10-2012-0158340

Foreign Application Priority Data

#### **Publication Classification**

(51) Int. Cl. H05K 1/02 (2006.01) H05K 3/30 (2006.01) H05K 3/00 (2006.01)

(52) U.S. Cl.

156/280; 29/832

### (57) ABSTRACT

A circuit board includes an inorganic material insulating layer, a first circuit pattern layer formed on a surface of the inorganic material insulating layer, a first build-up insulating layer formed on the inorganic material insulating layer and formed of an organic material, and a second circuit pattern layer formed on a surface of the first build-up insulating layer.

FIG. 1

FIG. 2

FIG. 3A

FIG. 3B

FIG. 3D

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9A

FIG. 9B

FIG. 9D

### CIRCUIT BOARD AND METHOD OF MANUFACTURING THE SAME

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the foreign priority benefit of Korean Patent Application No. 10-2012-0158340 filed with the Korea Intellectual Property Office on Dec. 31, 2012, the disclosure of which is incorporated herein by reference.

#### BACKGROUND

[0002] 1. Field

[0003] Embodiments of the present invention relate to a circuit board and a method of manufacturing the same.

[0004] 2. Description of the Related Art

[0005] In order to deal with a light weight, a small size, a high speed, a multiple functions, and high performance of electronic appliances, multi-layered substrate techniques in which a plurality of interconnection layers are formed on a printed circuit board (PCB) are developed, and further, a technique of mounting electronic components such as an active device or a passive device into a multi-layered substrate is also developed.

[0006] Meanwhile, one of important tasks in a multi-layered substrate field may be that built-in electronic components effectively transmit and receive a signal including a voltage or current to/from an external circuit or other devices.

[0007] In addition, as tendency for high performance of electronic components, a small size and thinning of electronic components and electronic components-built-in substrate is intensified, in order to mount small electronic components into a smaller and thinner substrate and connect external electrodes of the electronic components to the outside, improvement in integrity of a circuit pattern is necessarily needed.

[0008] Meanwhile, as the electronic components-built-in substrate is further thinned, a bending phenomenon of the substrate becomes a serious problem. Such a bending phenomenon may be referred to as warpage, which becomes serious as the electronic components-built-in substrate is formed of various materials having different thermal expansion coefficients.

[0009] Document 1 cited below discloses a multi-layered substrate constituted by an insulating layer formed on a glass ceramic material only, and Document 2 cited below discloses a conventional multi-layered substrate in which a core substrate is formed by coating or impregnating a glass core or a glass fiber with resin.

[0010] However, when the insulating layer is implemented by the glass ceramic material only like in Document 1, since a process of processing a via and a circuit pattern is very difficult, it is difficult to implement a fine and highly integrated circuit pattern, and it is difficult to secure adhesion reliability between layers.

[0011] In addition, even in the case of a core in which the glass core or glass fiber is impregnated with resin like in Patent Document 2, sufficient strength cannot be secured to cause limitation in reduction of warpage.

### CITATIONS

[0012] (Document 1) Japanese Patent Application Laid-Open No. 1994-232528

[0013] (Document 2) Japanese Patent Application Laid-Open No. 2000-261124

#### SUMMARY

[0014] Embodiments of the present invention have been invented in order to overcome the above-described problems and it is, therefore, an aspect of the present invention is to provide a circuit board and a method of manufacturing the same that are capable of reducing warpage of the circuit board and improving manufacturing efficiency thereof.

[0015] In accordance with one aspect of the present invention to achieve the above mentioned capabilities, there is provided a circuit board including: an inorganic material insulating layer; a first circuit pattern layer formed on a surface of the inorganic material insulating layer; a first build-up insulating layer formed on the inorganic material insulating layer and formed of an organic material; and a second circuit pattern layer formed on a surface of the first build-up insulating layer.

[0016] Here, the inorganic material insulating layer may be a glass sheet or a plate glass.

[0017] In addition, the circuit board may further include a recess section formed at one region of the inorganic material insulating layer, and an electronic component at least partially inserted into the recess section and having an external electrode at at least one surface thereof, wherein the first build-up insulating layer covers the electronic components.

[0018] Here, the first build-up insulating layer may include a first upper build-up insulating layer formed on the inorganic material insulating layer and a first lower build-up insulating layer formed under the inorganic material insulating layer.

[0019] In addition, the number of build-up layers formed on the first upper build-up insulating layer may be different from the number of build-up layers formed on the first lower buildup insulating layer.

**[0020]** Here, the external electrode may be disposed in a direction of the first upper build-up insulating layer, and the number of build-up layers formed on the first upper build-up insulating layer may be larger than that of the build-up layers formed on the first lower build-up insulating layer.

[0021] Meanwhile, the first circuit pattern layers may be formed on both surfaces of the inorganic material insulating layer, and may be electrically connected to each other by a via passing through the inorganic material insulating layer.

[0022] In addition, the circuit board may further include at least one build-up layer on the first build-up insulating layer.

[0023] Further, the inorganic material insulating layer may include a first inorganic material insulating layer having a cavity; an adhesive layer adhered to a lower surface of the first inorganic material insulating layer; and a second inorganic material insulating layer adhered to a lower surface of the adhesive layer.

[0024] Furthermore, the circuit board may further include a cavity passing through the inorganic material insulating layer and formed in one region of the inorganic material insulating layer, and an electronic component at least partially inserted into the cavity and having an external electrode formed at at least one surface thereof, wherein the first build-up insulating layer covers the electronic component.

[0025] Here, the electronic component may be a capacitor. [0026] A circuit board according to an embodiment of the present invention includes an inorganic material insulating layer having a cavity or a recess section; an identification mark formed on a surface of the inorganic material insulating

layer; an electronic component partially inserted into the cavity or the recess section and having an external electrode at at least one surface thereof; a first build-up insulating layer formed on the inorganic material insulating layer and formed of an organic material; and a second circuit pattern layer formed on a surface of the first build-up insulating layer.

[0027] Here, the inorganic material insulating layer may be a glass sheet or plate glass.

[0028] In addition, the first build-up insulating layer may include a first upper build-up insulating layer formed on the inorganic material insulating layer and a first lower build-up insulating layer formed on the inorganic material insulating layer, the second circuit pattern layer may include a second upper circuit pattern layer formed on an upper surface of the first upper build-up insulating layer and a second lower circuit pattern layer formed on an upper surface of the first lower build-up insulating layer, and the second upper circuit pattern layer and the second lower circuit pattern layer may be electrically connected by a via passing through the first build-up insulating layer and the inorganic material insulating layer.

[0029] Further, the via may pass through the identification mark.

[0030] Furthermore, the external electrode may be electrically connected to any one of the second upper circuit pattern layer and the second lower circuit pattern layer by the via.

[0031] In addition, the external electrode may be disposed in a direction of the first upper build-up insulating layer, and the number of build-up layers formed on the first upper build-up insulating layer may be larger than that of build-up layers formed on the first lower build-up insulating layer.

[0032] Here, the electronic component may be a capacitor.

[0033] A method of manufacturing a circuit board according to an embodiment of the present invention includes: forming a first circuit pattern layer on a surface of an inorganic material insulating layer; forming a recess section or a cavity in the inorganic material insulating layer; inserting at least a portion of an electronic component having an external electrode into the recess section or the cavity; forming a first build-up insulating layer formed of an organic material on the inorganic material insulating layer; forming a via-hole passing the first build-up insulating layer and configured to expose a surface of at least one of the first circuit pattern layer and the external electrode; and forming a conductive material in the via-hole and forming a second circuit pattern layer on a surface of the first build-up insulating layer.

[0034] Here, forming a recess section or a cavity in the inorganic material insulating layer may include forming a resist pattern configured to expose a region at which the recess section or the cavity is to be formed on the inorganic material insulating layer; and wet-etching the exposed region to form the recess section or the cavity and then removing the resist pattern.

[0035] In addition, the first build-up insulating layer may include a first upper build-up insulating layer formed on the inorganic material insulating layer and a first lower build-up insulating layer formed under the inorganic material insulating layer, the method may further include forming at least one build-up layer on the first upper build-up insulating layer and the first lower build-up insulating layer, and wherein the number of build-up layers formed on the first upper build-up insulating layer is different from the number of build-up layers formed on the first lower build-up insulating layer.

[0036] Further, inserting at least the portion of the electronic component having the external electrode into the recess

section or the cavity may be performed by making the lower surface of the electronic components in contact with the adhesive layer and adhering an added inorganic material insulating layer to the adhesive layer lower surface in a state in which an adhesive layer is adhered to the lower surface of the inorganic material insulating layer having the cavity.

[0037] Furthermore, the method may further include performing at least one pre-treatment process selected from surface etching, hardening and opaque processing to the inorganic material insulating layer.

[0038] A method of manufacturing a circuit board according to an embodiment of the present invention includes forming an identification mark on a surface of an inorganic material insulating layer; forming a recess section or a cavity in the inorganic material insulating layer; inserting at least a portion of an electronic component having an external electrode into the recess section or the cavity; forming a first build-up insulating layer formed of an organic material on the inorganic material insulating layer; forming a via-hole passing through the first build-up insulating layer and configured to expose a surface of the external electrode; and forming a conductive material in the via-hole and forming a second circuit pattern layer on a surface of the first build-up insulating layer.

[0039] Here, forming the recess section or the cavity in the inorganic material insulating layer may include patterning a predetermined region with respect to the identification mark.

[0040] In addition, inserting at least the portion of the electronic component having the external electrode into the recess section or the cavity may be performed by mounting the

section or the cavity may be performed by mounting the electronic component on a predetermined position with respect to the identification mark.

[0041] Further, forming the via-hole passing through the

[0041] Further, forming the via-hole passing through the first build-up insulating layer and configured to expose a surface of the external electrode may include forming a via-hole passing through the first build-up insulating layer, the identification mark and the inorganic material insulating layer.

[0042] Furthermore, the first build-up insulating layer may include a first upper build-up insulating layer formed on the inorganic material insulating layer and a first lower build-up insulating layer formed under the inorganic material insulating layer, the method may further include forming at least one build-up layer on the first upper build-up insulating layer and the first lower build-up insulating layer, wherein the number of build-up layers formed on the first upper build-up layers formed on the first lower build-up layers formed on the first lower build-up insulating layer.

[0043] In another aspect of the invention, a circuit board includes: a core substrate comprised of a glass sheet or a plate glass; and, on the core substrate, at least one build-up insulating layer formed of organic material and through which a via connecting circuit patterns at opposite respective ends of the via is disposed

### BRIEF DESCRIPTION OF THE DRAWINGS

[0044] These and/or other aspects and advantages of the present general inventive concept will become apparent and more readily appreciated from the following description of the embodiments, taken in conjunction with the accompanying drawings of which:

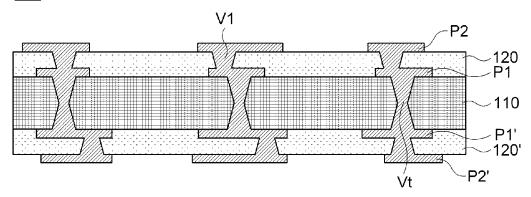

[0045] FIG. 1 is a cross-sectional view schematically showing a circuit board according to an embodiment of the present invention;

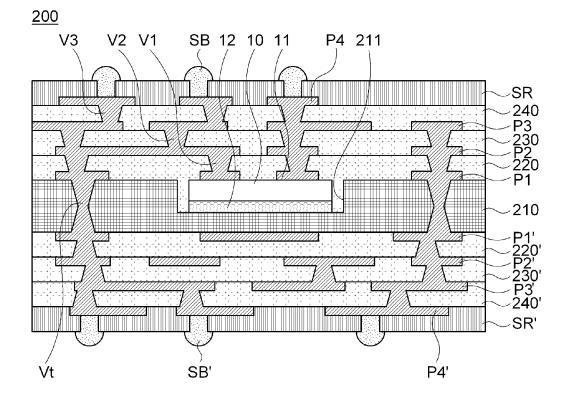

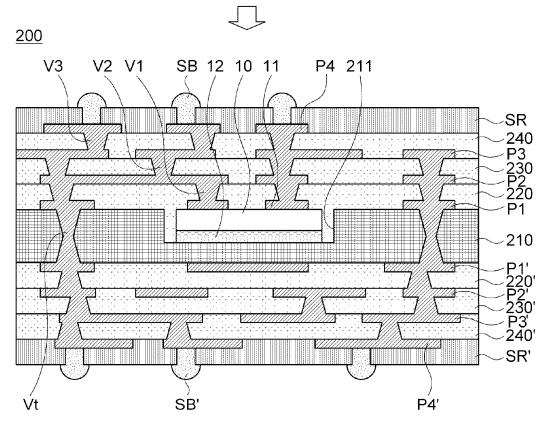

[0046] FIG. 2 is a cross-sectional view schematically showing a circuit board according to another embodiment of the present invention;

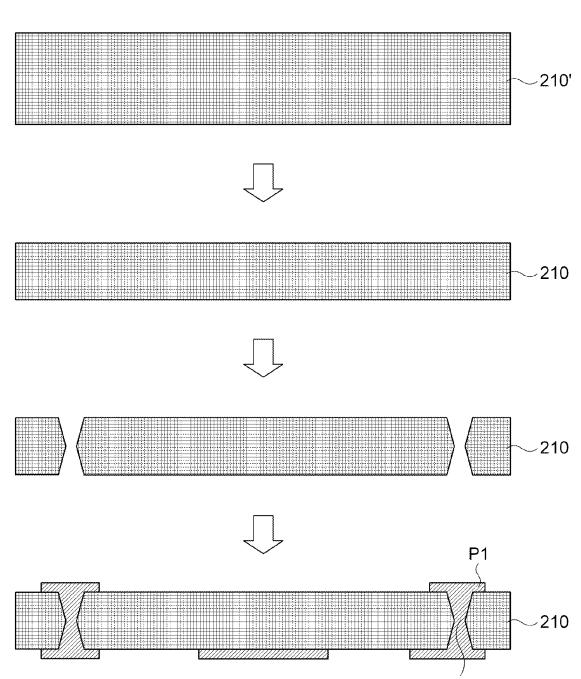

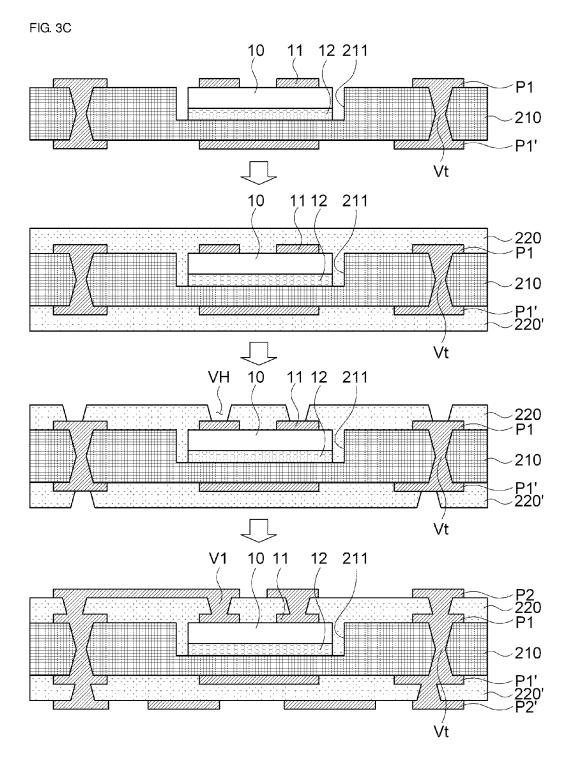

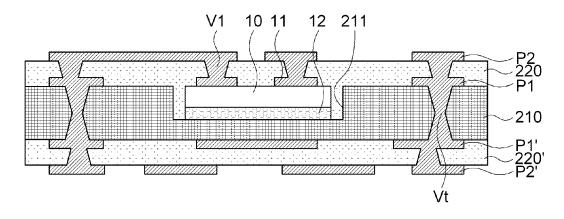

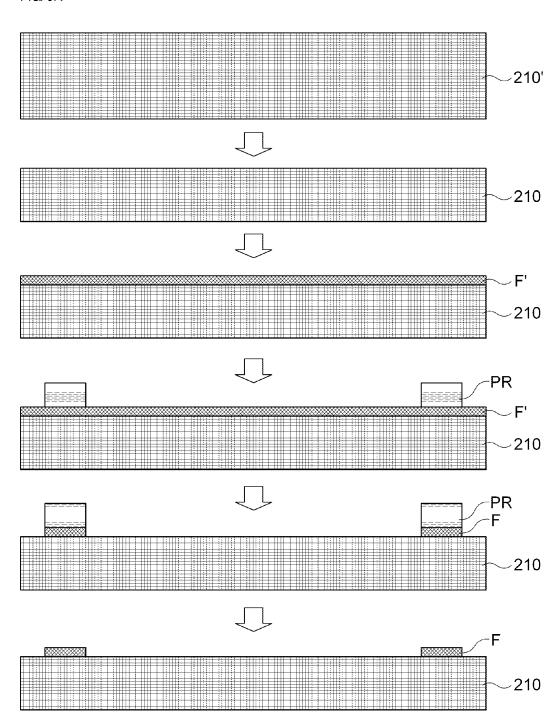

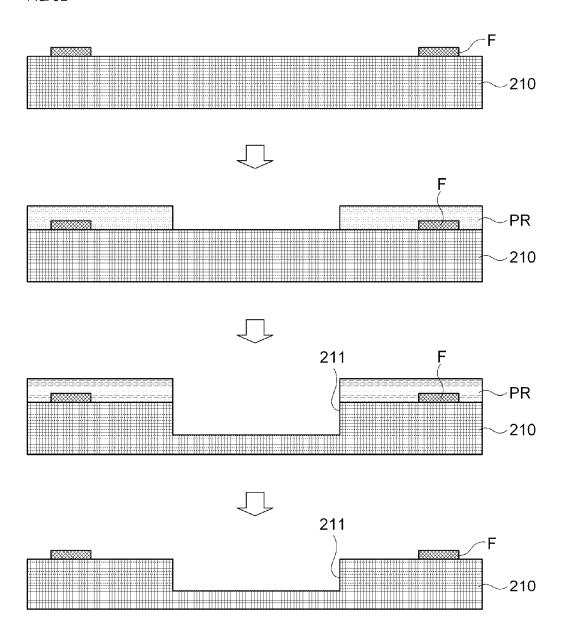

[0047] FIGS. 3A to 3D are cross-sectional process views schematically showing a method of manufacturing the circuit board according to the embodiment also illustrated in FIG. 2, FIG. 3A showing a process of forming a first circuit pattern layer on an inorganic material insulating layer, FIG. 3B showing a process of forming a recess section in the inorganic material insulating layer, FIG. 3C showing a process of mounting electronic components and forming a first build-up insulating layer, and FIG. 3D showing a process of further forming a build-up layer;

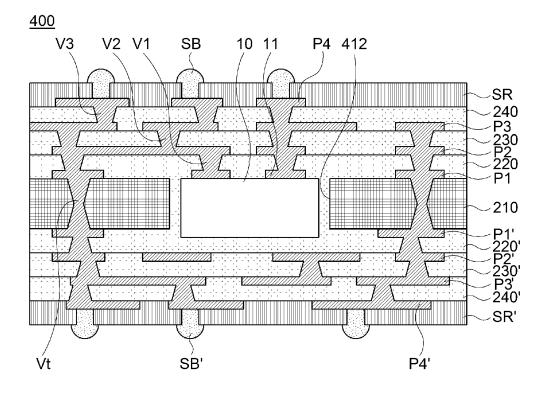

[0048] FIG. 4 is a cross-sectional view schematically showing a circuit board according to another embodiment of the present invention;

[0049] FIG. 5 is a cross-sectional view schematically showing a circuit board according to another embodiment of the present invention;

[0050] FIG. 6 is a cross-sectional view schematically showing a circuit board according to a another embodiment of the present invention;

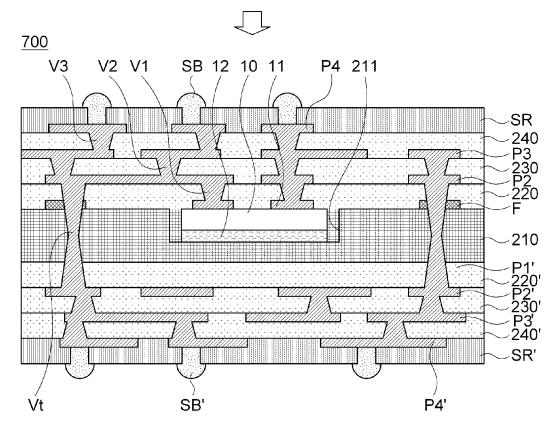

[0051] FIG. 7 is a cross-sectional view schematically showing a circuit board according to another embodiment of the present invention;

[0052] FIG. 8 is a cross-sectional view schematically showing a circuit board according to another embodiment of the present invention; and

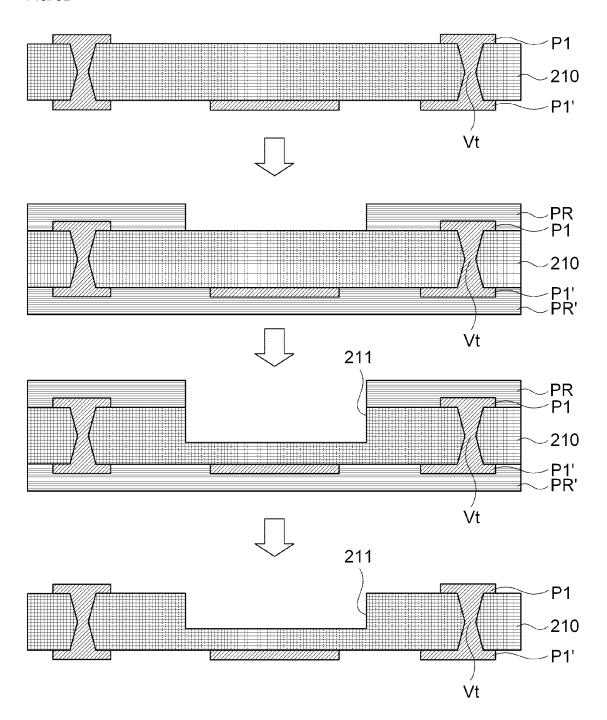

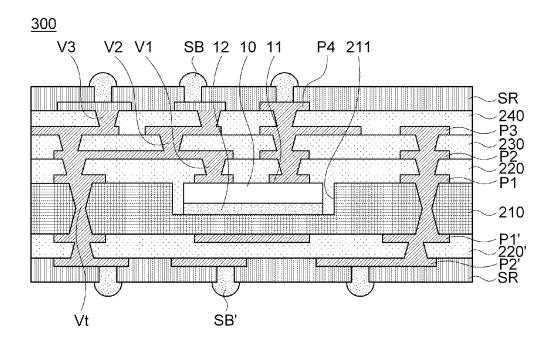

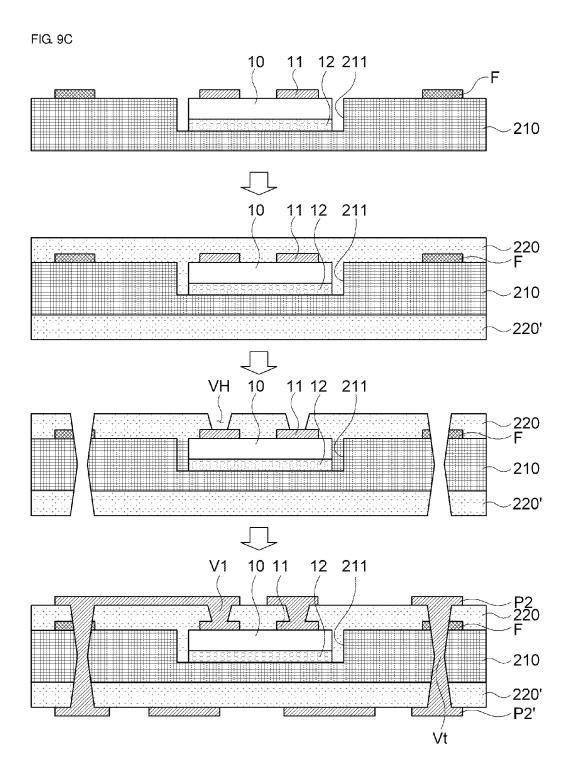

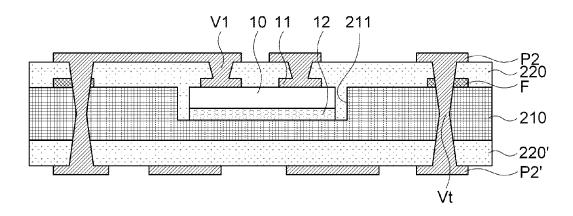

[0053] FIGS. 9A to 9D are cross-sectional process views schematically showing the circuit board according to the embodiment also illustrated in FIG. 8, FIG. 9A showing a process of forming an identification mark on an inorganic material insulating layer, FIG. 9B showing a process of forming a recess section in the inorganic material insulating layer, FIG. 9C showing a process of mounting electronic components and forming a first build-up insulating layer, and FIG. 9D showing a process of further forming a build-up layer.

### DESCRIPTION OF EMBODIMENTS

[0054] Hereinafter, exemplary embodiments of the present invention will be described in detail. However, the present invention is not limited to the embodiments disclosed below but can be implemented in various forms. The following embodiments are described in order to enable those of ordinary skill in the art to embody and practice the present invention. To clearly describe the present invention, parts not relating to the description are omitted from the drawings. Like numerals refer to like elements throughout the description of the drawings.

[0055] Terms used herein are provided for explaining embodiments of the present invention, not limiting the invention. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises" and/or "comprising," when used in this specification, specify the presence of stated components, motions, and/or devices, but do not preclude the presence or addition of one or more other components, motions, and/or devices thereof.

[0056] For the purpose of simplification and clarification of illustration, the drawings show conventional configurations, and known characteristics and detailed description of techniques may be omitted to avoid description of the embodiments from becoming unnecessary unclear. Additionally,

components of the drawings are not necessarily drawn according to their scales. For example, sizes of some components of the drawings may be exaggerated for the convenience of understanding of the present invention. Like reference numerals in different drawings designate like element, and similar reference numerals may designate similar elements, not necessarily so.

[0057] It will be understood that, although the terms "first," "second," "third," "fourth" etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another. For example, a first element could be termed a second element, and, similarly, a second element could be termed a first element, without departing from the scope of the present invention. Similarly, when it is described that a method includes series of steps, a sequence of the steps is not a sequence in which the steps should be performed in the sequence, an arbitrary technical step may be omitted and/or another arbitrary step, which is not disclosed herein, may be added to the method.

[0058] It will be understood that when terms "left," "light," "front," "rear," "on," "under," "over," "beneath" or the like are used, the terms are merely used for the purpose of description, not describing unchangeable relative positions. The terms used herein may be exchangeable to be operated in different directions than shown and described herein under an appropriate environment. It will be understood that when an element is referred to as being "connected" or "coupled" to another element, it can be directly connected or coupled to the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected" or "directly coupled" to another element, there are no intervening elements present. Here, the phrase "in one embodiment" means the same embodiment, not necessarily

[0059] Hereinafter, configurations and effects of the present invention will be described in detail with reference to the accompanying drawings.

[0060] FIG. 1 is a cross-sectional view schematically showing a circuit board 100 according to an embodiment of the present invention.

[0061] Referring to FIG. 1, the circuit board 100 according to an embodiment of the present invention may include an inorganic material insulating layer 110, a first circuit pattern layer P1, a first build-up insulating layer 120 and a second circuit pattern layer P2.

[0062] The inorganic material insulating layer 110 may be formed of glass. Here, the glass may be a glass plate such as a glass sheet or a plate glass produced by a glass manufacturer. For example, the glass may be formed of various kinds of glass materials such as a willow, Gorilla (which are trademarks, manufactured by Corning Corporation), Lime Soda, a plate glass used in a liquid crystal display (LCD), or the like. In exemplary embodiments of the present invention, impurities or additives may be partially mixed with the glass to improve properties.

[0063] According to the exemplary embodiments, the inorganic material insulating layer 110 may function as a core substrate. In this case, since good stiffness, modulus, and tensile strength can be secured in comparison with the case in which a conventional resin or a resin impregnated with glass fiber is used as the core substrate, a warpage phenomenon of the circuit board can be basically solved.

[0064] Here, various kinds of glass materials such as willow, LCD, Gorilla, Lime Soda, or the like, may be applied as the glass.

[0065] Next, the first circuit pattern layer P1 may be directly formed on a surface of the inorganic material insulating layer 110.

[0066] Here, the first circuit pattern layer P1, P1' may be formed at both surfaces of the inorganic material insulating layer 110, and the first circuit pattern layer P1 formed on one surface of the inorganic material insulating layer 110 may be electrically connected to the first circuit pattern layer P1' formed on the other surface of the inorganic material insulating layer 110 through a through-via Vt passing through the inorganic material insulating layer 110.

[0067] Next, the first build-up insulating layer 120 may be formed of an organic material.

[0068] For example, the first build-up insulating layer 120 may be formed of epoxy resin. In one embodiment, the first build-up insulating layer 120 may include ABF. According to the exemplary embodiments of the present invention, the organic material does not exclude that an additive such as filler is included in an organic composition such as resin. And a second circuit pattern layer P2 may be directly formed on a surface of the first build-up insulating layer 120.

[0069] According to the exemplary embodiments, since the warpage of the circuit board 100 is basically blocked by the inorganic material insulating layer 110, even when an insulating material including a core material such as prepreg is not used as a build-up insulating layer, sufficient mechanical and physical characteristics of the circuit board can be secured. Accordingly, as the organic material is used as the build-up insulating layer, a circuit pattern having a finer pitch or line width can be formed.

[0070] Here, the first build-up insulating layer 120, 120' may also be formed on and under the inorganic material insulating layer 110, a layer formed on the inorganic material insulating layer 110 may be referred to as a first upper build-up insulating layer 120, and a layer formed under the inorganic material insulating layer 110 may be referred to as a first lower build-up insulating layer 120'.

[0071] Accordingly, the circuit board 100 according to an embodiment of the present invention includes the inorganic material insulating layer 110 to enable reduction in warpage in comparison with the conventional art and effective implement of a via and circuit pattern on the first build-up insulating layer 120 formed of an organic material.

[0072] Accordingly, while reduction in warpage is limited in the case of the conventional multi-layered substrate formed of the organic material only, the circuit board 100 according to the embodiment of the present invention can solve the problem.

[0073] In addition, when the conventional multi-layered substrate in which the entire substrate is formed of glass, a process of processing the via and circuit pattern is very difficult and adhesion reliability between layers cannot be easily secured, and such problems cannot be solved by the circuit board 100 according to the embodiment of the present invention.

[0074] FIG. 2 is a cross-sectional view schematically showing a circuit board 200 according to another embodiment of the present invention.

[0075] Referring to FIG. 2, the circuit board 200 according to the embodiment includes an electronic component 10 mounted therein.

[0076] Here, a recess section 211 recessed in a groove shape is formed in one region of an inorganic material insulating layer 210 such that the electronic component 10 is seated in the recess section 211. Of course, it will be easily understood to those skilled in the art that the entire electronic component 10 should not be inserted into the recess section 211.

[0077] In addition, the electronic component 10 may be an active device such as a semiconductor chip or a passive device such as a capacitor, and an external electrode 11 is installed at the outside thereof.

[0078] In particular, in the embodiment in which the electronic component 10 is seated in the recess section 211, a surface the electrode 10 at which the external electrode 11 is formed may be disposed in a direction opposite to a bottom surface of the recess section 211 such that the external electrode 11 of the electronic component 10 forms electrical connection to the outside of the circuit board 200.

[0079] Meanwhile, the first build-up insulating layer 220 formed of the organic material may be provided on the inorganic material insulating layer 210 to cover the inorganic material insulating layer 210, the first circuit pattern layer P1 and the electronic component 10.

[0080] As described above, the first build-up insulating layer 220 may be formed only on the inorganic material insulating layer 210 or only under the inorganic material insulating layer 210.

[0081] Here, the second circuit pattern layer P2 may be formed on the surface of the first build-up insulating layer 220, and the second circuit pattern layer P2 may be electrically connected to the first circuit pattern layer P1 and the external electrode 11 via a first via V1.

[0082] The process of implementing the circuit pattern on the first build-up insulating layer 220 formed of the organic material has high process efficiency and a fine circuit pattern in comparison with the process of implementing the circuit pattern on the inorganic material insulating layer 210. In addition, in processing the via passing through the insulating layer, fine vias can be relatively easily and precisely formed.

[0083] In addition, according to the necessity, at least one build-up layer may be further formed on the first build-up insulating layer 220. Here, the build-up layer may include a build-up insulating layer and a circuit pattern layer formed on a surface of the build-up insulating layer.

[0084] As shown in FIG. 2, which illustrates another embodiment of the present invention, a second build-up insulating layer 230, a third circuit pattern layer P3, a third build-up insulating layer 240, a fourth circuit pattern layer P4, and so on, may be further provided in an upward direction of the inorganic material insulating layer 210, and build-up layers may be further provided in a downward direction of the inorganic material insulating layer 210 in a similar manner.

[0085] In addition, as shown, it will be apparent that a solder resist SR and a solder ball SB may be further provided at the outermost side of the circuit board 100.

[0086] Accordingly, the circuit board 200 can effectively implement the fine circuit pattern on the first build-up insulating layer 220 formed of the organic material while sufficiently reducing the warpage using the inorganic material insulating layer 210.

[0087] FIGS. 3A to 3D are process cross-sectional views schematically showing a method of manufacturing the circuit board 200 according to the aforementioned embodiment of the present invention.

[0088] First, referring to FIG. 3A, an inorganic material 210' formed of glass is pre-treated to prepare the inorganic material insulating layer 210. Here, the pre-treatment may be a process of treating surface through a process such as surface etching, or the like, or a process of hardening the surface to further improve strength thereof.

[0089] In addition, in inspecting whether the circuit pattern is appropriately formed in the manufacturing process of the circuit board 200, when the inorganic material insulating layer 210 is transparent, efficiency and precision of the inspection of the circuit pattern disposed on the inorganic material insulating layer 210 may be decreased by the circuit pattern or the like disposed under the inorganic material insulating layer 210. In order to solve the problem, the inorganic material insulating layer 210 may be opaquely treated, and the opaque treatment may also be included in the pre-treatment process.

[0090] Meanwhile, the first circuit pattern layers P1 may be formed on the surface of the inorganic material insulating layer 210. Here, the first circuit pattern layer P1 may be formed at both surfaces of the inorganic material insulating layer 210, and a through-via Vt may be formed to electrically connect the first circuit pattern layers P1, P1' formed on both surfaces thereof.

[0091] That is, after processing a via-hole passing through the inorganic material insulating layer 210 by laser or wet etching, a conductive material may be provided in the via-hole to form the through-via Vt, and the first circuit pattern layers P1, P1' can be electrically connected by the through-via Vt.

[0092] Next, referring to FIG. 3B, the recess section 211 may be formed on the inorganic material insulating layer 210.

[0093] First, a resist pattern PR configured to expose a region in which the recess section 211 is to be formed is formed on the inorganic material insulating layer 210. Here, the resist pattern PR may be a photo resist pattern, but not limited thereto.

[0094] Next, the wet etching is performed using etchant, and as a result, the recess section, which is partially recessed, may be formed in the inorganic material insulating layer 210.

[0095] Here, when the first circuit pattern layers P1 are formed on both surfaces of the inorganic insulating material insulating layer 210, the resist pattern PR may be formed such that the resist pattern PR covers both of the first circuit pattern layers P1 to prevent damage to the first circuit pattern layers P1 due to the etchant.

[0096] Next, when the etching process is completed, all of the resist pattern PR can be removed to provide the recess section 211 in the inorganic material insulating layer 210.

[0097] Next, referring to FIG. 3C, the electronic component 10 is inserted into the recess section 211.

[0098] Here, the electronic component 10 can be relatively securely fixed by applying an adhesive agent 12 to a lower surface of the electronic component 10 or applying the adhesive agent 12 to the upper surface of the recess section 211 and then mounting the electronic component 10.

[0099] Next, a first build-up insulating layer 220 is formed, and a via-hole VH passing through the first build-up insulating layer 220 is formed at a place requiring via connection, for example, an upper region of the external electrode 11 of the electronic component 10 or the first circuit pattern layer P1, by laser or wet etching.

[0100] Next, the via-hole VH may be filled with a conductive material, and the second circuit pattern layer P2 may be formed on a surface of the first build-up insulating layer 220. [0101] Next, referring to FIG. 3D, the plurality of build-up layers, the solder resist SR and the solder ball SB may be formed on the first build-up insulating layer 220 to manufacture the circuit board 200.

[0102] FIG. 4 is a cross-sectional view schematically showing a circuit board 300 according to another embodiment of the present invention.

[0103] Referring to FIG. 4, it will be appreciated that the number of build-up layers provided on the inorganic material insulating layer 210 is larger than that of the build-up layers provided under the inorganic material insulating layer 210.

[0104] For example, as shown, when the external electrode 11 of the electronic component 10 is formed in an upward direction of the inorganic material insulating layer 210, a more complicate interconnection should be formed on the electronic component 10, rather than under the electronic component 10.

[0105] Even in this case, since the inorganic material insulating layer 210 is symmetrically formed at upper and lower sides thereof to reduce the warpage in the conventional multilayered substrate, the interconnection cannot be sufficiently formed on the electronic component 10 to increase an area of the substrate or add unnecessary layers under the electronic component 10, increasing a thickness of the substrate.

[0106] However, as described above, since the circuit board 300 according to the present invention can efficiently implement the fine circuit pattern on the first build-up insulating layer 220 formed of the organic material while sufficiently reducing the warpage using the inorganic material insulating layer 210, the number of build-up layers may be different on and under the inorganic material insulating layer 210 from each other, and thus, the problems of the conventional art can be solved.

[0107] FIG. 5 is a cross-sectional view schematically showing a circuit board 400 according to another embodiment of the present invention.

[0108] Referring to FIG. 5, it will be appreciated that the circuit board 400 according to the embodiment may include a cavity 412 instead of the recess section so that the electronic component 10 is inserted into the cavity 412.

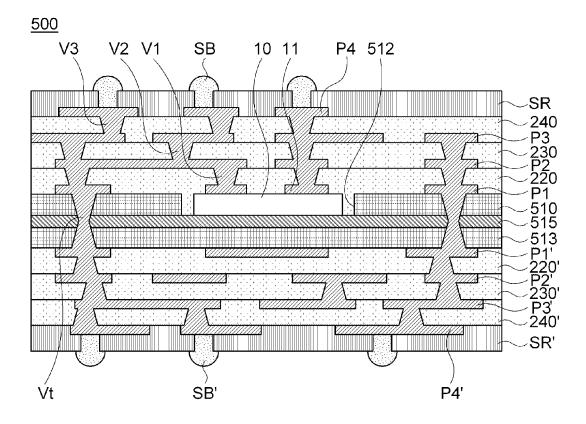

[0109] FIG. 6 is a cross-sectional view schematically showing a circuit board 500 according to a another embodiment of the present invention.

[0110] Referring to FIG. 6, it will be described that the circuit board 500 according to the embodiment may include an inorganic material insulating layer constituted by a first inorganic material insulating layer 510, an adhesive layer 515 and a second inorganic material insulating layer 513.

[0111] That is, in a state in which a cavity 512 is formed in the first inorganic material insulating layer 510, the adhesive layer 515 can be adhered to a lower surface of the first inorganic material insulating layer 510, and in a state in which the electronic component 10 is inserted into the cavity 512 of the first inorganic material insulating layer 510, the lower surface of the electronic component 10 can be securely adhered to the upper surface of the adhesive layer 515.

[0112] In addition, as the second inorganic material insulating layer 513 is further adhered to the lower surface of the adhesive layer 515, strength of the inorganic material insulating layer can be further improved to more stably support the electronic component 10.

[0113] Meanwhile, the first inorganic material insulating layer 510 and the second inorganic material insulating layer 513 are entitled merely for the convenience of description, the first inorganic material insulating layer 510 may be referred to as an inorganic material insulating layer, and the second inorganic material insulating layer 513 may be referred to as an added inorganic material insulating layer.

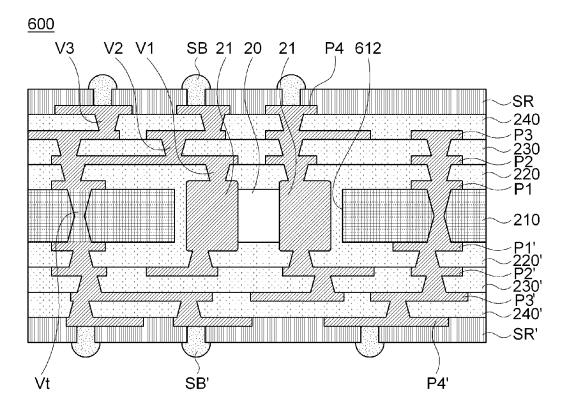

[0114] FIG. 7 is a cross-sectional view schematically showing a circuit board 600 according to another embodiment of the present invention.

[0115] Referring to FIG. 7, it will be appreciated that an electronic component 20 inserted into a cavity 612 is a capacitor such as MLCC or the like.

[0116] When the capacitor is inserted in this manner, vias may be formed at the lower surface of an external electrode 21 as well as the upper surface of the external electrode 21 to be electrically connected to the build-up layers

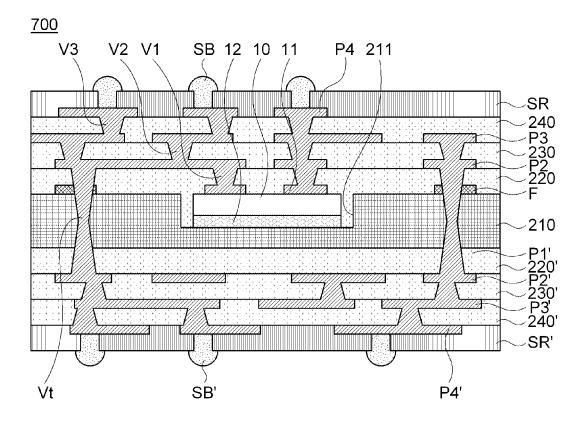

[0117] FIG. 8 is a cross-sectional view schematically showing a circuit board 700 according to another embodiment of the present invention.

[0118] Referring to FIG. 8, the circuit board 700 according to the embodiment may include an inorganic material insulating layer 210, an identification mark F, an electronic component 10, a first build-up insulating layer 220 and a second circuit pattern layer P2.

[0119] Here, similar to the above-mentioned embodiments, the inorganic material insulating layer 210 may be glass.

[0120] Meanwhile, when the first build-up insulating layers 220 are formed on and under the inorganic material insulating layer 210 and the second circuit pattern layers P2 are formed on and under the inorganic material insulating layer 210, the second circuit pattern layer P2 on the inorganic material insulating layer 210 may be needed to be connected to the second circuit pattern layer P2 under the inorganic material insulating layer 210.

[0121] In this case, the through-via Vt passing through the first build-up insulating layer 220 may be formed to electrically connect the second circuit pattern layers P2.

[0122] In addition, the through-via Vt formed at this time can pass through the identification mark F. That is, in forming the through-via Vt, in order to process the via-hole at a precise position, the identification mark F can be used as a kind of reference index.

[0123] In addition, the identification mark F may be used as a reference index in a process of forming the recess section 211 or the cavity in the inorganic material insulating layer 210, and may be used as a reference index in a process of mounting the electronic component 10.

[0124] Accordingly, precision in processing of the viahole, processing of the recess section 211 or the cavity, and mounting of the electronic component 10 can be further improved.

[0125] Unlike the above-mentioned embodiments, in the embodiment, the first circuit pattern layer P1 is not formed on the surface of the inorganic material insulating layer 210.

[0126] In consideration of the current technique, in comparison with the process of forming the circuit pattern or the via in the insulating layer formed of the organic material, the process of forming the circuit pattern or the via on the surface of the inorganic material insulating layer 210 formed of glass has a relatively low yield or process efficiency.

[0127] Of course, while the thickness for forming at least two layers can be reduced by forming the first circuit pattern layer P1 on the surface of the inorganic material insulating layer 210, an effect according to formation of the first circuit pattern layer P1 could be diluted in consideration of the process efficiency and yield.

[0128] Accordingly, in consideration of the above-mentioned aspects, an appropriate one of the above-mentioned embodiment and the present embodiment may be applied to manufacture the circuit board.

[0129] Meanwhile, since the others related to the embodiment are similar to the above-mentioned embodiment, overlapping description will be omitted.

[0130] FIGS. 9A to 9D are cross-sectional process views schematically showing a method of manufacturing the circuit board 700 according to the embodiment illustrated in FIG. 8.

[0131] First, referring to FIG. 9A, the inorganic material 210' formed of glass is pre-treated to prepare the inorganic material insulating layer 210. Here, the pre-treatment may mean that the surface is treated through surface etching, hardened to improve strength thereof, or the inorganic material insulating layer 210 is opaquely treated.

[0132] Meanwhile, the identification mark F is provided at the circuit board 700 according to the embodiment of the present invention.

[0133] Here, the identification mark F may be used as a reference index in the process of forming the recess section 211 or the cavity in the inorganic material insulating layer 210, and it has been described that the identification mark F can be used s a reference index in the process of mounting the electronic component 10.

[0134] The identification mark F may have a groove shape or a protrusion shape, and in the specification, a method of forming the identification mark F in the protrusion shape will be described.

[0135] First, a film F' is formed on one surface of the inorganic material insulating layer 210 through sputtering or plating.

[0136] Next, the resist pattern PR configured to cover a portion at which the identification mark F is to be formed and expose the other portion is formed. Here, the resist pattern PR may be a photo resist pattern.

[0137] Next, after removing the exposed region through etching or the like, the resist pattern PR may be removed to form the identification mark F having the protrusion shape.

[0138] Next, referring to FIG. 9B, the recess section 211 may be formed on the inorganic material insulating layer 210.

[0139] Further, the resist pattern PR configured to expose a region at which the recess section 211 is to be formed is formed on the inorganic material insulating layer 210. Here, the resist pattern PR may be the photo resist pattern PR, but not limited thereto.

[0140] Next, wet etching is performed using etchant, and as a result, the recess section 211, which is partially recessed, may be formed in the inorganic material insulating layer 210.

[0141] Next, when the etching is completed, all of the resist pattern PR may be removed to form the recess section 211 in the inorganic material insulating layer 210.

[0142] Meanwhile, a cavity instead of the recess section 211 may be formed in the inorganic material insulating layer 210, and as described above, the recess section 211 and the cavity may be formed through wet etching or laser drilling.

[0143] Here, a laser is irradiated to a predetermined region with respect to the identification mark F to form the recess section 211 or the cavity, more precisely processing the recess section 211 or the cavity.

- [0144] Next, referring to FIG. 9C, the electronic component 10 is inserted into the recess section 211.

- [0145] Here, after applying the adhesive agent 12 to the lower surface of the electronic component 10 or applying the adhesive agent 12 to the upper surface of the recess section 211, the electronic component 10 may be mounted to relatively securely fix the electronic component 10.

- [0146] Next, the first build-up insulating layer 220 is formed, and the via-hole VH passing through the first build-up insulating layer 220 is formed in a place that requires via connection, for example, an upper region of the external electrode 11 of the electronic component 10, through laser or wet etching.

- [0147] Meanwhile, when the second circuit pattern layers P2 are formed on and under the inorganic material insulating layer 210 and are needed to be electrically connected to each other, a via-hole passing through the first build-up insulating layer 220 and the inorganic material insulating layer 210 may be formed, and in order to precisely process the via-hole, the via-hole may pass through the identification mark F also.

- [0148] That is, the identification mark F may be used as a reference index for processing the via-hole to form the through-via Vt.

- [0149] Next, the via-hole may be filled with a conductive material, and the second circuit pattern layer P2 may be formed on a surface of the first build-up insulating layer 220.

- [0150] Next, referring to FIG. 9D, a plurality of build-up layer, a solder resist SR and a solder ball SB may be formed on the first build-up insulating layer 220 to manufacture the circuit board 700.

- [0151] As can be seen from the foregoing, the present invention includes the inorganic material insulating layer to provide useful effects of reducing the warpage in comparison with the conventional art, and effectively implementing the via and circuit pattern on the first build-up insulating layer formed of the organic material.

- [0152] In addition, since the warpage can be sufficiently reduced, there is no need to symmetrically form the build-up layers formed on and under the inorganic material insulating layer, and thus, degree of design freedom can be increased and the circuit board can be further slimmed.

- [0153] In addition, as the identification mark is used, precision in processing of the via-hole, processing of the recess section or the cavity, and mounting of the electronic component can be further improved.

- [0154] As described above, although multiple embodiments of the present invention have been shown and described, it will be appreciated by those skilled in the art that substitutions, modifications and variations may be made in these embodiments without departing from the principles and spirit of the general inventive concept, the scope of which is defined in the appended claims and their equivalents.

What is claimed is:

- 1. A circuit board comprising:

- an inorganic material insulating layer;

- a first circuit pattern layer formed on a surface of the inorganic material insulating layer;

- a build-up insulating layer formed on the inorganic material insulating layer and formed of an organic material; and

- a second circuit pattern layer formed on a surface of the build-up insulating layers.

- 2. The circuit board according to claim 1, wherein the inorganic material insulating layer is a glass sheet or a plate glass.

- 3. The circuit board according to claim 2, further comprising:

- a recess section formed at one region of the inorganic material insulating layer; and

- an electronic component at least partially inserted into the recess section and having an external electrode at at least one surface thereof,

- wherein the build-up insulating layer covers the electronic components.

- 4. The circuit board according to claim 3, wherein

- the build-up insulating layer is a first upper build-up insulating layer formed on the inorganic material insulating layer, and

- the circuit board further comprises a first lower build-up insulating layer formed under the inorganic material insulating layer.

- 5. The circuit board according to claim 4, further compris-

- at least one further build-up layer formed on at least one layer selected from the first upper build-up insulating layer and the first lower build-up insulating layer, wherein the number of build-up layers formed on the first upper build-up insulating layer is different from the number of build-up layers formed on the first lower build-up insulating layer.

- **6**. The circuit board according to claim **5**, wherein the external electrode is on a surface of the electronic component that is facing the first upper build-up insulating layer, and

- the number of build-up layers formed on the first upper build-up insulating layer is larger than that of the buildup layers formed on the first lower build-up insulating layer.

- 7. The circuit board according to claim 2, further comprising:

- a further first circuit pattern layer on the surface of the inorganic material insulating layer so that the circuit board comprises a pair of first circuit pattern layers, each formed on a respective surface of the inorganic material insulating layer, and each electrically connected to the other by a via passing through the inorganic material insulating layer.

- 8. The circuit board according to claim 2, further comprising, on the build-up insulating layer, at least one further build-up layer.

- 9. The circuit board according to claim 3, wherein the inorganic material insulating layer comprises:

- a first inorganic material insulating layer having a cavity; an adhesive layer adhered to a lower surface of the first inorganic material insulating layer; and

- a second inorganic material insulating layer adhered to a lower surface of the adhesive layer.

- 10. The circuit board according to claim 2, further comprising a cavity passing through the inorganic material insulating layer and formed in one region of the inorganic material insulating layer, and

- an electronic component at least partially inserted into the cavity and having an external electrode formed at at least one surface thereof,

- wherein the build-up insulating layer covers the electronic component.

- 11. The circuit board according to claim 10, wherein the electronic component is a capacitor.

- 12. A circuit board comprising:

- an inorganic material insulating layer having a cavity or a recess section;

- an identification mark formed on a surface of the inorganic material insulating layer;

- an electronic component partially inserted into the cavity or the recess section and having an external electrode at at least one surface thereof;

- a build-up insulating layer formed on the inorganic material insulating layer and formed of an organic material; and

- a second circuit pattern layer formed on a surface of the build-up insulating layer.

- 13. The circuit board according to claim 12, wherein the inorganic material insulating layer is a glass sheet or plate glass.

- 14. The circuit board according to claim 13, wherein

- the build-up insulating layer is a first upper build-up insulating layer formed on the inorganic material insulating layer,

- the circuit board further comprises a first lower build-up insulating layer formed on the inorganic material insulating layer,

- the second circuit pattern layer is a second upper circuit pattern layer formed on an upper surface of the first upper build-up insulating layer,

- the circuit board further comprises a second lower circuit pattern layer formed on an upper surface of the first lower build-up insulating layer, and

- the second upper circuit pattern layer and the second lower circuit pattern layer are electrically connected by a via passing through the build-up insulating layer and the inorganic material insulating layer.

- 15. The circuit board according to claim 14, wherein the via passes through the identification mark.

- 16. The circuit board according to claim 14, wherein the external electrode is electrically connected to any one of the second upper circuit pattern layer and the second lower circuit pattern layer by the via.

- 17. The circuit board according to claim 16, wherein the external electrode is on a surface of the electronic component that is facing the first upper build-up insulating layer, and

- the number of build-up layers formed on the first upper build-up insulating layer is larger than that of build-up layers formed on the first lower build-up insulating layer.

- 18. The circuit board according to claim 16, wherein the electronic component is a capacitor.

- 19. A method of manufacturing a circuit board, comprising:

- forming a first circuit pattern layer on a surface of an inorganic material insulating layer;

- forming a recess section or a cavity in the inorganic material insulating layer;

- inserting at least a portion of an electronic component having an external electrode into the recess section or the cavity;

- forming a build-up insulating layer formed of an organic material on the inorganic material insulating layer;

- forming a via-hole passing through the build-up insulating layer and configured to expose a surface of at least one of the first circuit pattern layer and the external electrode; and

- forming a conductive material in the via-hole and forming a second circuit pattern layer on a surface of the build-up insulating layer.

- 20. The method of manufacturing the circuit board according to claim 19,

- wherein the forming the recess section or cavity in the inorganic material insulating layer comprises:

- forming a resist pattern configured to expose a region at which the recess section or the cavity is to be formed on the inorganic material insulating layer; and

- wet-etching the exposed region to form the recess section or the cavity and then removing the resist pattern.

- 21. The method of manufacturing the circuit board according to claim 19,

- wherein the build-up insulating layer is a first upper buildup insulating layer formed on the inorganic material insulating layer,

- further comprising forming a first lower build-up insulating layer formed under the inorganic material insulating layer,

- further comprising forming at least one further build-up layer on either or both of the first upper build-up insulating layer and the first lower build-up insulating layer, and

- wherein the number of build-up layers formed on the first upper build-up insulating layer is different from the number of build-up layers formed on the first lower build-up insulating layer.

- 22. The method of manufacturing the circuit board according to claim 19, wherein the inserting at least the portion of the electronic component having the external electrode into the recess section or the cavity is performed by making the lower surface of the electronic components in contact with the adhesive layer and adhering an added inorganic material insulating layer to the adhesive layer lower surface in a state in which an adhesive layer is adhered to the lower surface of the inorganic material insulating layer having the cavity.

- 23. The method of manufacturing the circuit board according to claim 19, further comprising performing at least one pre-treatment process selected from surface etching, hardening and opaque processing to the inorganic material insulating layer.

- 24. A method of manufacturing a circuit board, comprising:

- forming an identification mark on a surface of an inorganic material insulating layer;

- forming a recess section or a cavity in the inorganic material insulating layer;

- inserting at least a portion of an electronic component having an external electrode into the recess section or the cavity:

- forming a build-up insulating layer formed of an organic material on the inorganic material insulating layer;

- forming a via-hole passing through the build-up insulating layer and configured to expose a surface of the external electrode; and

- forming a conductive material in the via-hole and forming a second circuit pattern layer on a surface of the build-up insulating layer.

- 25. The method of manufacturing the circuit board according to claim 24, wherein forming the recess section or the cavity in the inorganic material insulating layer comprises patterning a predetermined region with respect to the identification mark.

- 26. The method of manufacturing the circuit board according to claim 24, wherein inserting at least the portion of the electronic component having the external electrode into the recess section or the cavity is performed by mounting the electronic component on a predetermined position with respect to the identification mark.

- 27. The method of manufacturing the circuit board according to claim 24, wherein forming the via-hole passing through the build-up insulating layer and configured to expose a surface of the external electrode comprises forming a via-hole passing through the build-up insulating layer, the identification mark and the inorganic material insulating layer.

- 28. The method of manufacturing the circuit board according to claim 24,

- wherein the build-up insulating layer is a first upper buildup insulating layer formed on the inorganic material insulating layer,

- further comprising forming a first lower build-up insulating layer formed under the inorganic material insulating layer,

- further comprising forming at least one build-up layer on the first upper build-up insulating layer and the first lower build-up insulating layer, and

- wherein the number of build-up layers formed on the first upper build-up insulating layer is different from the number of build-up layers formed on the first lower build-up insulating layer.

- 29. A circuit board comprising:

- a core substrate comprised of a glass sheet or a plate glass;

- on the core substrate, at least one build-up insulating layer formed of organic material and through which a via connecting circuit patterns at opposite respective ends of the via is disposed.

- 30. The circuit board according to claim 29,

- wherein the at least one build-up insulating layer includes:

- a first build-up insulating layer on a first surface the core substrate; and

- a second build-up insulating layer on a second surface of the core substrate opposite to the first surface, further comprising:

- a first circuit pattern layer on a side of the first build-up insulating layer facing toward the core substrate;

- a second circuit pattern layer on a side of the first build-up insulating layer facing away from the core substrate; and

- a first via passing through the first build-up insulating layer and electrically connecting the first and second circuit patterns:

- a third circuit pattern layer on a side of the first build-up insulating layer facing toward the core substrate;

- a fourth circuit pattern layer on a side of the first build-up insulating layer facing away from the core substrate;

- a second via passing through the first build-up insulating layer and electrically connecting the third and fourth circuit patterns; and

- a third via passing through the core substrate electrically connecting the first and third circuit pattern layers.

- 31. The circuit board according to claim 30, wherein the first and second build-up insulating layers are in contact with the core substrate.

- 32. The circuit board according to claim 30,

- wherein the core substrate has a recess section or cavity, further comprising:

- an electronic component at least partially inserted into the recess section or cavity; and

- on each side of the core substrate, at least one further respective build-up insulating layer formed of organic material and through which a via, connecting circuit patterns on opposite respective ends of the via, is disposed.

- 33. The circuit board according to claim 32, wherein the core substrate has a recess section recessed from the first surface, and

- the number of build-up layers formed on the first surface of the core substrate is larger than the number of build-up layers formed on the second surface of the core substrate.

\* \* \* \* \*