### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2017/0104732 A1

Apr. 13, 2017 (43) **Pub. Date:**

#### (54) SECURITY PROCESSING ENGINES. CIRCUITS AND SYSTEMS AND ADAPTIVE PROCESSES AND OTHER PROCESSES

(71) Applicant: TEXAS INSTRUMENTS **INCORPORATED**, Dallas, TX (US)

Inventors: Amritpal Singh Mundra, Allen, TX

(US); Denis Roland Beaudoin,

Rowlett, TX (US)

(21) Appl. No.: 15/387,030

Dec. 21, 2016 (22) Filed:

### Related U.S. Application Data

- (62) Division of application No. 15/205,487, filed on Jul. 8, 2016, which is a division of application No. 15/045,948, filed on Feb. 17, 2016, now Pat. No. 9,503,265, which is a division of application No. 14/712,396, filed on May 14, 2015, now Pat. No. 9,305,184, which is a division of application No. 13/165,190, filed on Jun. 21, 2011, now Pat. No. 9,141,831.

- (60) Provisional application No. 61/362,393, filed on Jul. 8, 2010, provisional application No. 61/362,395, filed on Jul. 8, 2010.

#### **Publication Classification**

(51) Int. Cl. H04L 29/06 (2006.01)G06F 7/58 (2006.01)

| H04L 9/06   | (2006.01) |

|-------------|-----------|

| H04L 12/851 | (2006.01) |

| H04L 9/30   | (2006.01) |

| H04L 9/32   | (2006.01) |

| H04W 12/06  | (2006.01) |

| G06F 21/72  | (2006.01) |

| H04L 9/08   | (2006.01) |

CPC ....... H04L 63/0485 (2013.01); G06F 21/72 (2013.01); G06F 7/588 (2013.01); H04L 63/0428 (2013.01); H04L 63/08 (2013.01); H04L 9/0625 (2013.01); H04L 9/0631 (2013.01); H04L 9/0637 (2013.01); H04L 9/065 (2013.01); H04L 9/0869 (2013.01); H04L 9/3013 (2013.01); H04L 9/3239 (2013.01); H04L 9/3242 (2013.01); H04W 12/06 (2013.01); H04L 47/2441 (2013.01); H04L 2209/125 (2013.01); H04L 2209/38

(2013.01)

#### (57)ABSTRACT

(52) U.S. Cl.

An electronic circuit (200) includes one or more programmable control-plane engines (410, 460) operable to process packet header information and form at least one command, one or more programmable data-plane engines (310, 320, 370) selectively operable for at least one of a plurality of cryptographic processes selectable in response to the at least one command, and a programmable host processor (100) coupled to such a data-plane engine (310) and such a control-plane engine (410). Other processors, circuits, devices and systems and processes for their operation and manufacture are disclosed.

FIG. 6

FIG. 7

FIG. 9

FIG. 19

#### SECURITY PROCESSING ENGINES, CIRCUITS AND SYSTEMS AND ADAPTIVE PROCESSES AND OTHER PROCESSES

## CROSS-REFERENCES TO RELATED APPLICATIONS

[0001] This application is a divisional of application Ser. No. 15/205,487, filed Jul. 8, 2016, currently pending;

[0002] Which was a divisional of prior application Ser. No. 15/045,948, filed Feb. 17, 2016, now U.S. Pat. No. 9,503,265, issued Nov. 22, 2016;

[0003] Which was a divisional of prior application Ser. No. 14/712,396, filed May 14, 2015, now U.S. Pat. No. 9,305,184, issued Apr. 5, 2016;

[0004] Which was a divisional of prior application Ser. No. 13/165,190, filed Jun. 21, 2011, now U.S. Pat. No. 9,141,831, issued Sep. 22, 2015;

[0005] Which is related to provisional U.S. patent application "Security Processing Engines, Circuits and Systems and Adaptive Processes and Other Processes" Ser. No. 61/362,393, (TI-67750PS) filed Jul. 8, 2010, for which priority is claimed under 35 U.S.C. 119(e) and all other applicable law, and which is incorporated herein by reference in its entirety.

[0006] And is also related to provisional U.S. patent application "Mode Control Engine (MCE) For Confidentiality and Other Modes, Circuits and Processes" Ser. No. 61/362,395, (TI-68484PS) filed Jul. 8, 2010, for which priority is claimed under 35 U.S.C. 119(e) and all other applicable law, and which is incorporated herein by reference in its entirety.

[0007] This application is related to U.S. Patent Application Publication 2004/0025036, "Run-time firmware authentication" dated Feb. 5, 2004, (TI-34918), which is incorporated herein by reference in its entirety.

[0008] This application is related to U.S. Patent Application Publication 2007/0294496, "Methods, Apparatus, and Systems for Secure Demand Paging and Other Paging Operations for Processor Devices" dated Dec. 20, 2007, (TI-38213), which is incorporated herein by reference in its entirety.

[0009] This application is related to U.S. Patent Application Publication 2008/0114993, "Electronic Devices, Information Products, Processes of Manufacture And Apparatus For Enabling Code Decryption in a Secure Mode Using Decryption Wrappers and Key Programming Applications, and Other Structures" dated May 15, 2008, (TI-38346), which is incorporated herein by reference in its entirety.

[0010] This application is related to U.S. Patent Application Publication 2007/0110053 "Packet Processors and Packet Filter Processes, Circuits, Devices, and Systems", dated May 17, 2007 (TI-39133), which is incorporated herein by reference in its entirety.

[0011] This application is related to U.S. Patent Application Publication 2007/0226795, "Virtual Cores and Hardware-Supported Hypervisor Integrated Circuits, Systems, Methods and Processes of Manufacture" dated Sep. 27, 2007 (TI-61985), which is incorporated herein by reference in its entirety.

[0012] This application is related to U.S. Patent Application Publication 2010/0138857, "Systems and Methods for Processing Data Packets" dated Jun. 3, 2010 (TI-63830), which is incorporated herein by reference in its entirety.

[0013] This application is related to U.S. Patent Application Publication 2010/0322415, "Multilayer Encryption of a Transport Stream Data and Modification of a Transport Header" dated Dec. 23, 2010 (TI-63831), which is incorporated herein by reference in its entirety.

[0014] This application is related to U.S. patent application Ser. No. 12/815,734 "Slice Encoding and Decoding Processors, Circuits, Devices, Systems and Processes" (TI-67049), filed Jun. 15, 2010, which is incorporated herein by reference in its entirety.

## STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

[0015] Not applicable.

#### COPYRIGHT NOTIFICATION

[0016] Portions of this patent application contain materials that are subject to copyright protection. The copyright owner has no objection to the facsimile reproduction by anyone of the patent document, or the patent disclosure, as it appears in the United States Patent and Trademark Office, but otherwise reserves all copyright rights whatsoever.

#### **BACKGROUND**

[0017] This invention is in the field of information and communications, and is more specifically directed to improved processes, circuits, devices, and systems for information and communication processing and/or protection against unauthorized interception of communications, and processes of operating, protecting and making them. Without limitation, the background is further described in connection with communications processing and wireless and wireline communications, and security processing.

[0018] Wireless communications, of many types, have gained increasing popularity in recent years. The mobile wireless (cellular) telephone has become ubiquitous around the world. Mobile telephony can communicate video and digital data, in addition to voice. Wireless devices, for communicating computer data over a wide area network, using mobile wireless telephone channels and techniques are also available. Ethernet and other wireline broadband technologies support many office systems and home systems.

[0019] Wireless data communications in wireless local area networks (WLAN), such as that operating according to the well-known IEEE 802.11 standard, has become especially popular in a wide range of installations, ranging from home networks to commercial establishments. Short-range wireless data communication according to the Bluetooth technology permits computer peripherals to communicate with a personal computer or workstation within the same room

[0020] Security is essential to protect retail and other commercial transactions in electronic commerce. Security is vital to protect medical data, medical records, and other storage and transfer of personal data, or in any context in which personal privacy is desirable. Security is fundamental for both wireline and wireless communications and at multiple layers in communications, such as transport layer, network layer, and other layers. Added features and increasing numbers of security standards add further processing tasks to communications systems. These potentially involve additional software and hardware in systems that already face cost and power dissipation challenges. Even the ability

of the system itself to keep up with the task load and rate of information flow may be jeopardized.

[0021] Each of the data communication security standards like IPSEC, SRTP, TLS, WiMax, Wireless 3G and Wireless 4G uses its own form of data cryptography and source authentication. (Refer to TABLE 1 Glossary of acronyms.) To make data communication more secure each security standard defines its own additional level of processing beyond standard cryptographic algorithmic processing (AES, 3DES, Kasumi etc). This additional processing called "mode operation" is different for each application and different within a given application depending upon current mode of operation and peer capabilities. This mode processing is sometimes very complex and calls for repeated cryptographic processing for a same data block. Some popular examples of the confidentiality modes that use AES or 3DES cores are CBC, OFB, CFB, CTR, GCM, and CCM which may be used in IPSEC applications. To secure wireless data traffic, transmitted via antenna, Kasumi-F8 and Snow3G-F8 are used in 3GPP technology, for a couple of examples.

[0022] This cryptographic "mode operation" processing presents a huge technological challenge, given that performance and chip area vitally matter, to support so many different types of processing in hardware even though the modes include the basic cryptography AES, 3DES, etc., in the process. Moreover, as security standards evolve, new modes are added continually to overcome or mitigate security issues as and when found in mode processing, thereby leading to a further problem of technologically keeping up with new modes of security processing in hardware.

[0023] If system hardware is to support multiple security standards at extremely high processing speeds and transfer rates (called bit-rates), more cryptography standards must be supported with high performance even though each standard defines its own data cryptography processes, authentication methods and operational encryption modes.

[0024] Hardware implementation of confidentiality modes like CBC, OFB, CFB, CTR, GCM, and CCM, conventionally calls for custom logic for each mode even when they may use the same cryptographic process (AES, 3DES etc). Performance and chip real estate area suffer. Competitive issues and market demands add yet further dimensions of performance, chip area, and QoS (Quality of service) to the challenge of implementing so many security standards. Moreover, as security standards evolve, new modes are invented continually in the industry to overcome or mitigate newly-detected types of attacks.

[0025] Departures for more efficient ways of handling and/or protecting packet and non-packet data, voice, video, and other content are needed for microprocessors, telecommunications apparatus and computer systems.

#### SUMMARY OF THE INVENTION

[0026] Generally, and in one form of the invention, an electronic circuit includes one or more programmable control-plane engines operable to process packet header information and form at least one command, one or more programmable data-plane engines selectively operable for at least one of a plurality of cryptographic processes selectable in response to the at least one command, and a programmable host processor coupled to such a data-plane engine and such a control-plane engine.

[0027] Generally, and in another form of the invention, a security context cache module is for use with a host processor and an external memory. The module includes a local cache memory, a local processor coupled with the local cache memory, an ingress circuit having an input for ingress of a packet stream including an ingress packet having a security context pointer, and an auto-fetch circuit responsive to such ingress packet and operable to automatically fetch a security context from the external memory to the local cache memory using the security context pointer, and to associate the security context in the local cache memory with the packet stream, the auto-fetch circuit operable for multiple such packet streams and ingress packets, whereby to allow simultaneous security connections.

[0028] Generally, and in a further form of the invention, a streaming interface for packet data includes a buffer circuit for a packet stream including a packet having an associated request field for thread identification, the buffer circuit operable to provide a ready signal indicating that the buffer circuit currently has at least a predetermined amount of space to accept data; and a data transfer circuit responsive to the request for thread identification to transfer data to a particular target thread, the data transfer circuit including a control circuit responsive to the ready signal, and responsive to a start-of-packet indicator and an end-of-packet indicator and a drop-packet indicator, and further responsive to a multi-bit thread identification of a thread that is currently occupying the buffer circuit.

[0029] Generally, yet another form of the invention involves a control method for packet processing. The control method includes host-loading a first storage area with a context including control data and processing instructions for processing at least part of a packet, supplying a stream of packets including a particular packet to a packet processing subsystem, the particular packet including a pointer to a context in the first storage area; operating the packet processing subsystem to access the context from the first storage area for use in the packet processing subsystem in accordance with the pointer, and processing the stream of packets in the packet processing subsystem in accordance with the control data and processing instructions in the context.

[0030] Generally, another further form of the invention involves an electronic method of processing packets. The method includes providing a set of accelerator engines and at least one separate control engine, receiving packets from a stream using an electronic interface, electronically chunking the packets into chunks in a memory, the chunks being generally shorter than their packets and at least one of the chunks having associated control information, operating the separate control engine in response to the control information to electronically generate and store a sequence of engine identifications representing a pipelined process by selected ones of the accelerator engines one after another according to the sequence; and coupling and operating the accelerator engines responsive to the stored sequence of engine identifications so that a first accelerator engine having the first engine identification in the sequence processes a series of the chunks to produce resulting chunks, and a second accelerator engine having the second engine identification in the sequence processes the resulting chunks from the first accelerator engine beginning substantially as soon as the first of the resulting chunks comes from the first accelerator engine, whereby the stream of packets is pipeline-processed.

[0031] Generally, and in still another form of the invention, a packet interface circuit includes a control circuit operable to receive packets each having a header and a payload, some of the packets representing a first stream, and some others of the packets representing a second stream, the control circuit operable to assign thread identifications identifying each such stream, a memory, and a chunking circuit operable, when a given such packet has a payload exceeding a predetermined length, to store chunks in the memory so that the chunks have the predetermined length or less, and the chunking circuit operable to load chunk control information into the memory, the control information indicating start of packet (SOP), middle of packet (MOP), and end of packet (EOP), depending on the position in the payload of data in a given stored chunk.

[0032] Generally, a further process form of the invention involves a communication method for control communication between processors. The communication method includes electronically breaking ingress packets into smaller chunks, one of the chunks for a packet being a start-of-packet chunk having associated control information, operating one or more programmable control-plane engines to process such a start of packet chunk and form at least one command to organize a set of data plane engines into a particular pipeline topology, and selectively operating the data-plane engines programmably to process the chunks in accordance with the command, whereby to effectuate at least one of a plurality of packet processing modes.

[0033] Generally, and in a yet further form of the invention, an electronic buffering circuit includes at least three processors each having inputs and outputs and identified by respective engine identifications, and at least one of the processors operable to generate particular engine identifications of at least two of the processors; a plurality of buffers at least equal in number to the plurality of processors; and a selection circuit responsive to controls based on the engine identifications of the processors for any-order interconnection of a selected processor-buffer-processor topology.

[0034] Generally, and in another additional form of the invention, a packet-processing electronic subsystem includes a first data interface for first streaming data, a second data interface for second streaming data, a scheduler circuit coupled to the first and second data interfaces and including a packet memory, a security context cache module coupled for input from, and output to, the scheduler circuit, the security context cache module including a cache controller and a cache storage for at least one security context, a packet header processing module coupled for input from, and output to, the scheduler circuit, an authentication module coupled for input from, and output to, the scheduler circuit; and an encryption module coupled for input from, and output to, the scheduler circuit and the encryption module including control circuitry and encryption accelerators responsive to a security context in the security context cache module to operate the encryption module and the authentication module as specified by the security context and the packet header processing module.

[0035] Other processors, circuits, devices and systems and processes for their operation and manufacture are disclosed and claimed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

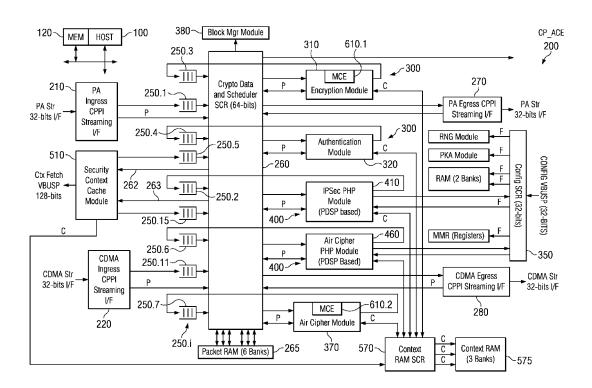

[0036] FIG. 1 is a block diagram of an inventive subsystem for efficient cryptographic acceleration.

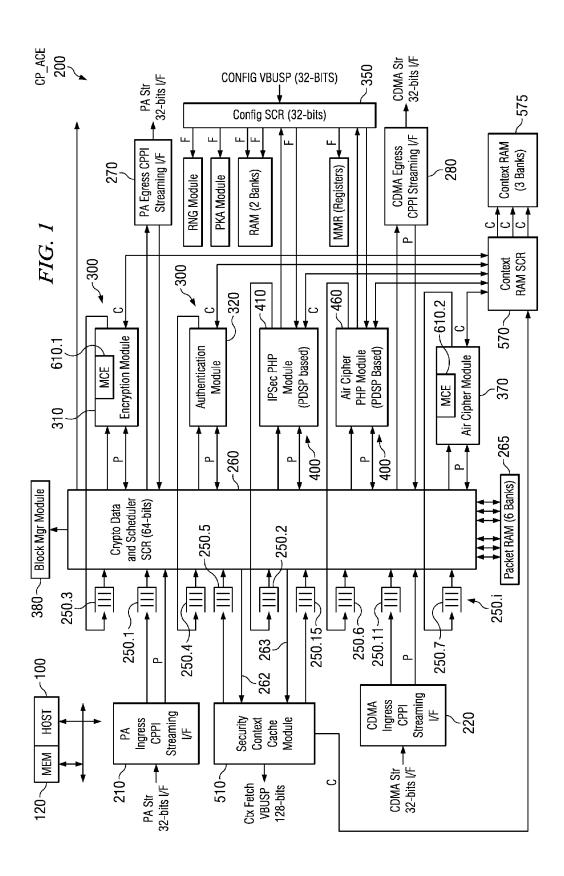

[0037] FIG. 1A is a four-quadrant diagram of processing parallelism of the inventive subsystem of FIG. 1, e.g., in Internet and wireless, and in a control plane and a data plane.

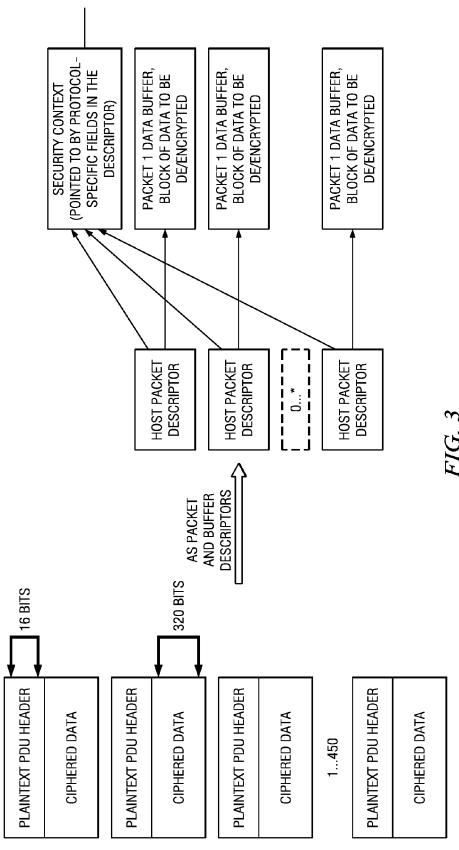

[0038] FIG. 2 is a diagram of memory spaces related by pointers, and including inventive security data structures acting as a data sink receive queue at top and data source transmit queue at bottom which are established or supported by a host processor and the subsystem embodiment of FIG.

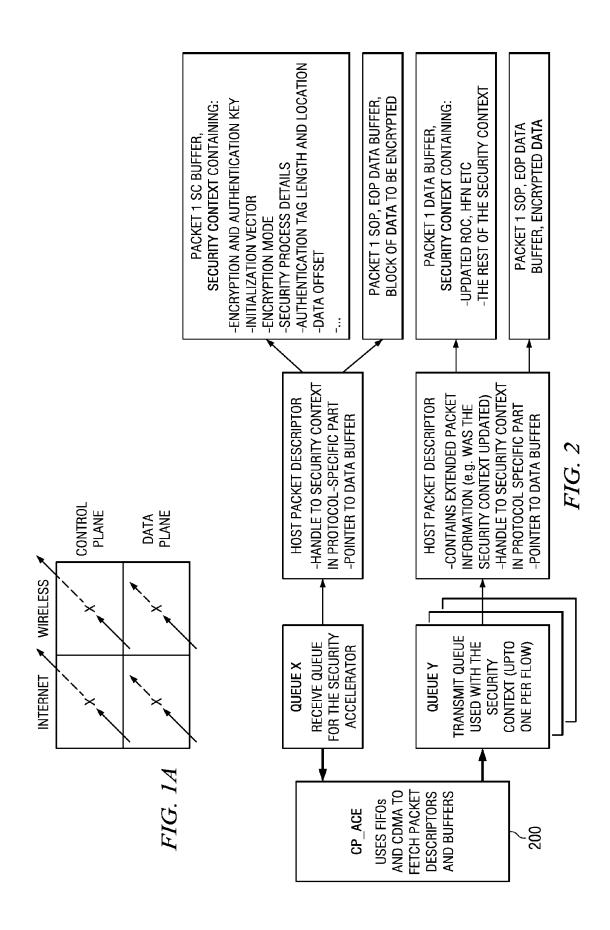

[0039] FIG. 3 is a composite diagram of packets and descriptors therein together with storage spaces for a security context and data buffer space(s) used for the inventive security data structures of FIG. 2.

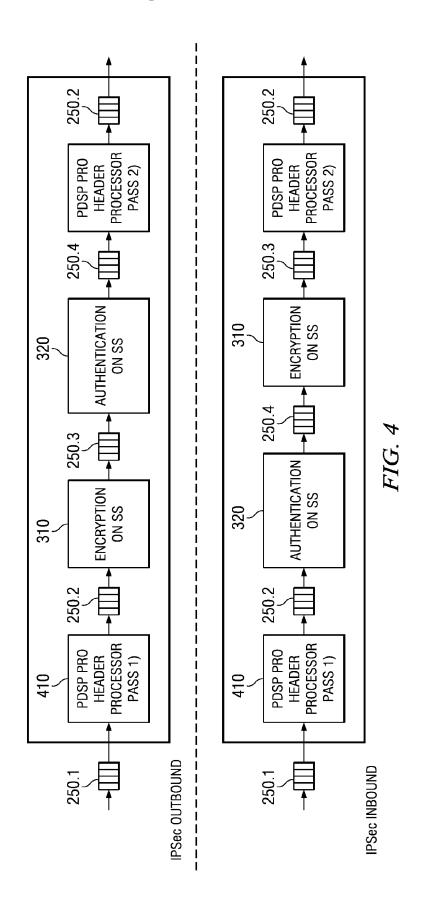

[0040] FIG. 4 is a partially block, partially flow, diagram wherein the inventive subsystem of FIG. 1 adaptively organizes a programmable structure called a logical topology for IPSEC outbound and IPSEC inbound packets.

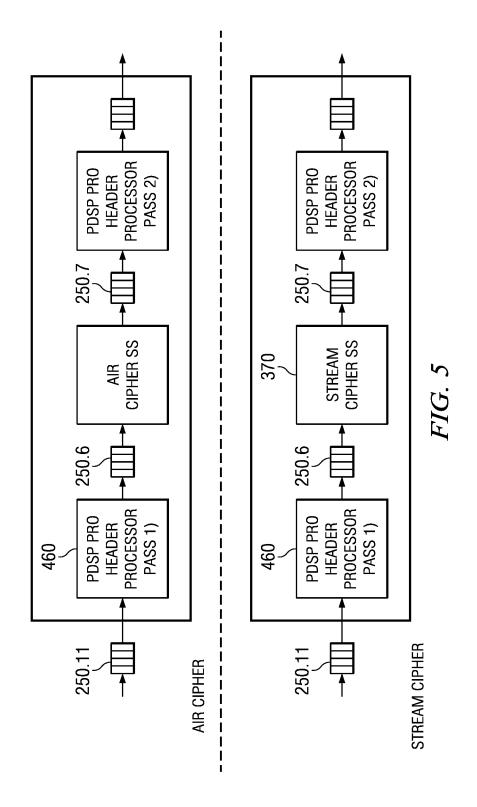

[0041] FIG. 5 is a partially block, partially flow, diagram wherein the inventive subsystem of FIG. 1 adaptively organizes a programmable structure (logical topology) for Air cipher/Stream cipher.

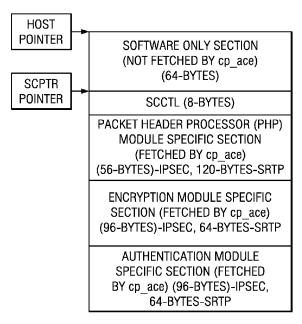

[0042] FIG. 6 is a storage space diagram of an inventive security context data structure for IPSEC in ESP mode, such as to support FIG. 4, or alternatively with an inventive security context for SRTP.

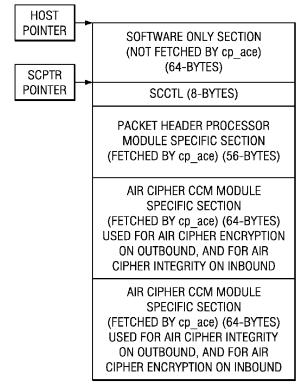

[0043] FIG. 7 is a storage space diagram of an inventive security context data structure that supports FIG. 5 for Air Cipher inbound and outbound. Notice that the order of integrity and encryption in the security context is reversed in this example depending on the Outbound or Inbound operation.

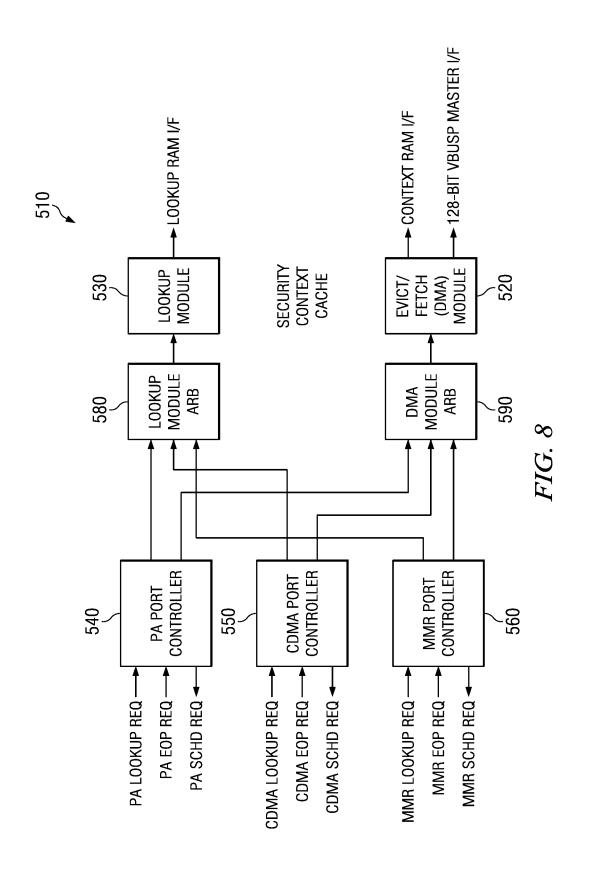

[0044] FIG. 8 is a block diagram of an inventive security context cache for the security context data structures such as those of FIGS. 6 and 7.

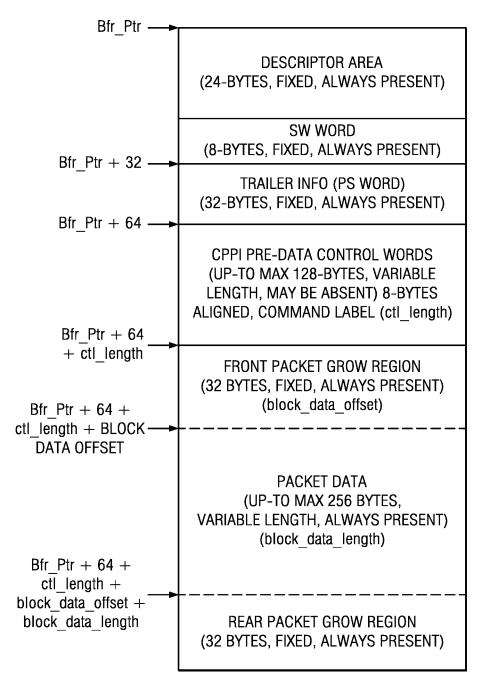

[0045] FIG. 9 is a storage space diagram of an inventive internal buffer format with associated buffer pointer positions and that is provided for an inventive process of chunking packets.

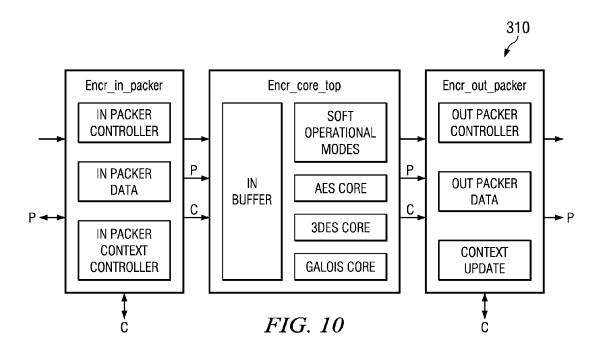

[0046] FIG. 10 is a block diagram of an inventive encryption module in the subsystem embodiment of FIG. 1.

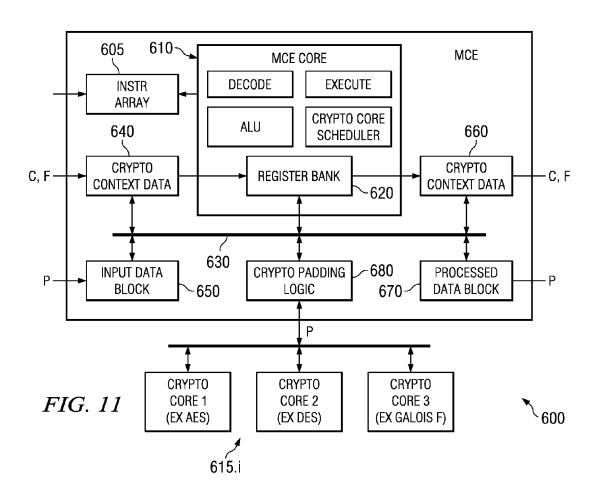

[0047] FIG. 11 is a block diagram of an inventive mode control engine (MCE) for use in the encryption module of FIG. 10 and in the Air Cipher module of FIG. 14.

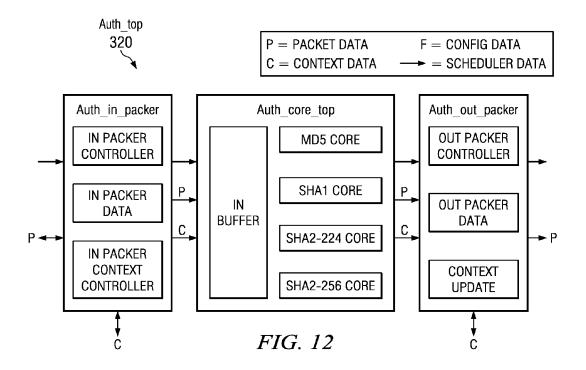

[0048] FIG. 12 is a block diagram of an inventive authentication module in the subsystem embodiment of FIG. 1.

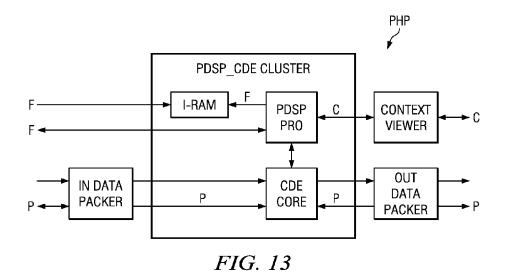

[0049] FIG. 13 is a block diagram of an inventive packet header processing (PHP) module in the subsystem embodiment of FIG. 1.

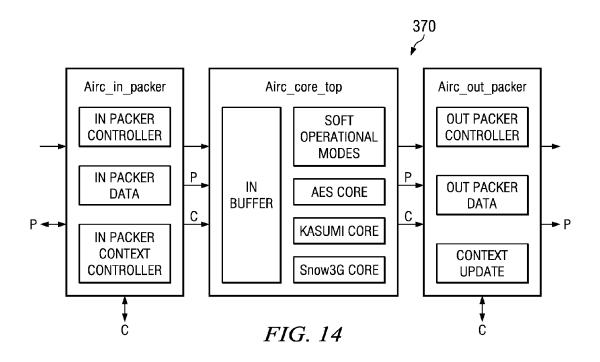

[0050] FIG. 14 is a block diagram of an inventive Air Cipher module in the subsystem of FIG. 1 and that uses the MCE embodiment of FIG. 11.

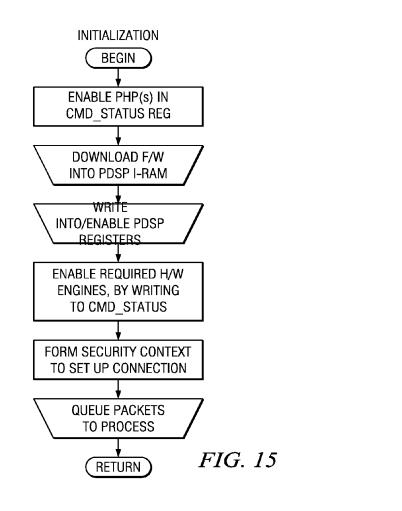

[0051] FIG. 15 is a flow diagram of an inventive process for initialization of the subsystem of FIG. 1.

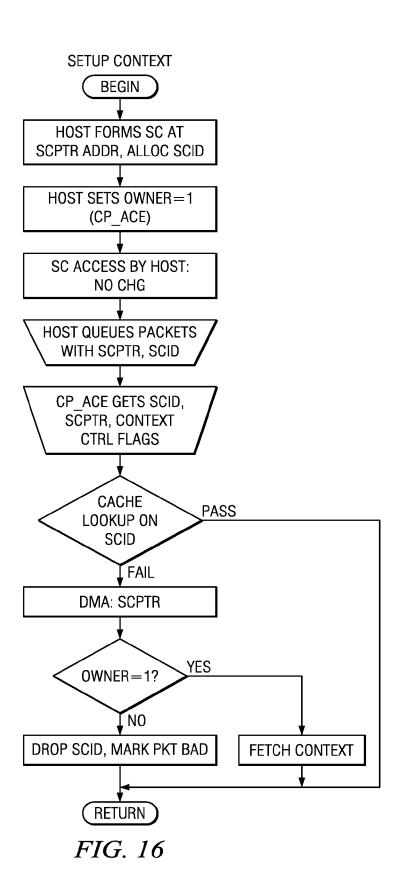

[0052] FIG. 16 is a flow diagram of an inventive process for setting up a security context for the subsystem embodiment of FIG. 1.

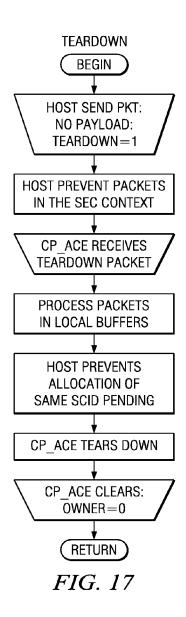

[0053] FIG. 17 is a flow diagram of an inventive process for tearing down a security context for the subsystem embodiment of FIG. 1.

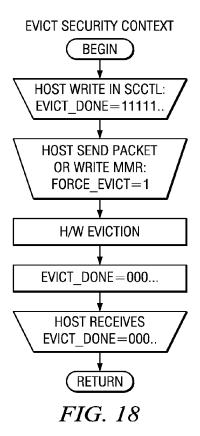

[0054] FIG. 18 is a flow diagram of an inventive process for evicting a security context in FIGS. 1 and 8 for the subsystem embodiment of FIG. 1.

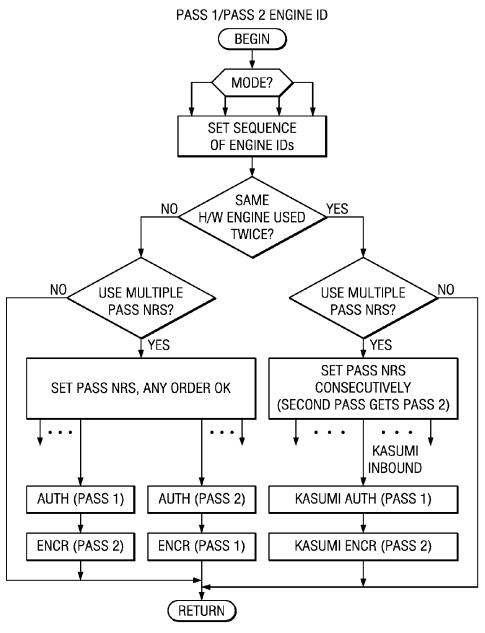

[0055] FIG. 19 is a flow diagram of an inventive process for issuing Engine IDs for multiple execution passes for the subsystem embodiment of FIG. 1.

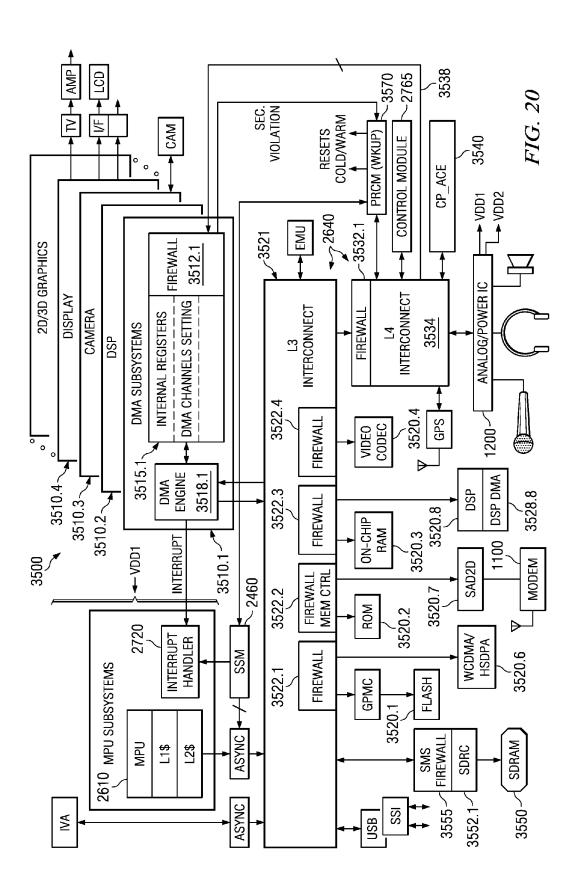

[0056] FIG. 20 is a block diagram of an inventive secure telecommunication and processing system combination with structures and processes as disclosed herein.

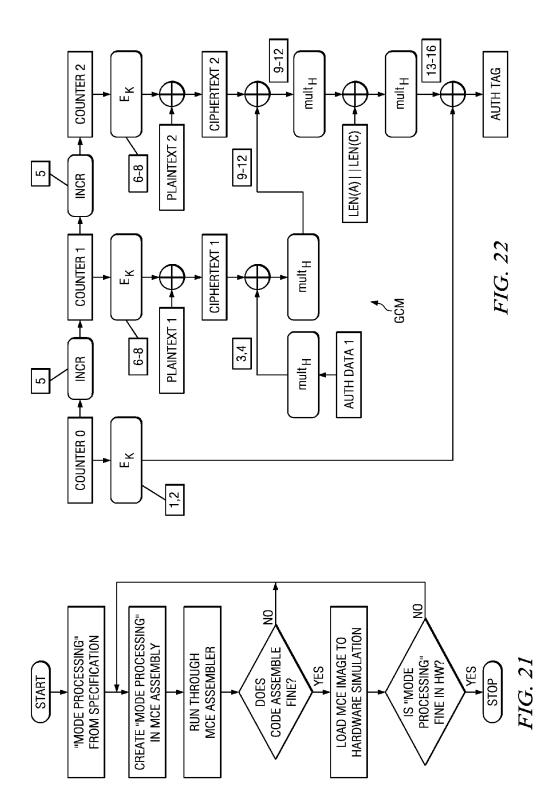

[0057] FIG. 21 is a flow diagram of a process for inventive mode processing code assembly for the FIG. 11 MCE embodiment.

[0058] FIG. 22 is a flow diagram of a process for inventive mode processing in FIGS. 1 and 11 by the MCE embodiment according to assembly code generated according to FIG. 21.

[0059] Corresponding numerals in different Figures indicate corresponding parts except where the context indicates otherwise. A minor variation in capitalization or punctuation or spacing, or lack thereof, for the same thing does not necessarily indicate a different thing. A suffix .i or .j refers to any of several numerically suffixed elements having the same prefix.

#### DETAILED DESCRIPTION OF EMBODIMENTS

[0060] To solve the above noted problems and other problems, smart, scalable high performance, configurable cryptographic engines (occasionally referred to as CP\_ACE herein) provide an example of a remarkable, adaptive subsystem category of embodiments, allowing multiple security standards like IPSEC, SRTP, TLS, WiMax, wireless 3G and wireless 4G to be processed concurrently and efficiently using the same processing engines. The subsystem embodiment of FIG. 1 is adaptive, adapted, or adaptable by allowing firmware-controlled security header processing and hardware-driven, any-order data staging, cipher block formatting and cryptographic processing.

[0061] Such subsystem embodiments can satisfy extremely high bit-rate demands and provide a rich feature set to accommodate industry cryptography standards to carry out content encryption and authenticity validation for wire-side and wireless-side traffic. Moreover, these embodiments can provide anti-replay protection and resist other types of security attacks.

[0062] A form of the subsystem employs multiple engines that primarily process streams of data and controllably separates or segregates them from one or more additional engines that primarily perform control functions and responses to conditions—thereby establishing a data plane and a control plane herein. The separation desirably avoids or obviates blocking effects that might otherwise arise between control plane processing and data plane processing, while the control plane schedules and otherwise controls the data plane. The separable data planes and their independent control avoid stalling of either plane by the other plane. A host processor is also provided that can call the subsystem and further is free to itself selectively use the data plane and bypass the control plane, e.g. without engaging control plane components. Two-way register access between control plane and data plane promotes monitoring, control of blocks and their topology, and controllable separation. The cut-through structure separates the data plane from the control plane, or generally provides a parallel control information transfer path in one circuit half or control plane as compared with a data transfer path in another circuit half or data plane for true pipelined processing. That way, no stall arises even if delays occur in either the control plane or data plane.

[0063] The subsystem preserves and enhances Quality of Service (QoS) by automatically breaking a data packet into small chunks and scheduling these data chunks based on configured or requested QoS level. Such QoS level indicates or represents packet stream priority and is used by the subsystem to control and/or establish subsystem latency (packet throughput delay) and data rate, for instance. This important ability to switch within-a-packet allows QoS preference, such as to give higher priority to packets of another type or QoS level, to be effective immediately. Some modes or packet types may automatically have a particular QoS level associated with them in the configuration.

[0064] The high performance, adaptive, and configurable cut-through embodiments with internal data chunking allow multiple security standards to be processed concurrently at high bit rate and low latency. Mere updates to firmware for the subsystem confer the ability to support new standards in the field. Such subsystem processes packets in data chunks thereby giving ability to switch within-a-packet to a new higher priority packet, thereby preserving and enhancing Quality of Service.

[0065] The subsystem of FIG. 1 hosts a security context cache module of FIG. 8 that fetches and evicts a respective control data structure for each security context that holds information like cryptographic keys and modes from external memory 120 on demand basis. This information is fanned out to the data processing engine(s) automatically by hardware before data is processed. Optionally the control structure itself can be encrypted to safeguard access to keys in external memory 120. Arbitrated port controllers are coupled to a data lookup cache portion and to a security context cache portion, further effectuating the parallelism of control plane and data plane in the cache structure of such subsystem embodiments.

[0066] The subsystem circuitry partially constructs a security context as a control plane operation in the local context cache store by an access to host memory. The circuitry also acts to process an incoming packet into packet chunks each including a portion of data from an incoming packet and to affix control information into at least one such chunk. The subsystem provides a further contribution to the construction of the security context in the local context store from the control information in the packet chunk in the data plane. Interlocked security is thus flexibly provided by operations in both the control plane and the data plane.

[0067] Moreover, the subsystem introduces both control plane/data plane parallelism and cryptographic parallelism such as for Internet and wireless concurrently. This constitutes a two-dimensional streaming parallelism in four quadrants (see FIG. 1A) for control/data and Internet/wireless cryptographic and other processing that can with dramatic efficiency securely handle the real-life applications that users care about now and in the future.

[0068] Cryptography processing is conventionally very expensive and burdensome on a main CPU (or array of CPU's) at least because new security standards require more data and instruction bandwidth and processing in conjunction with the high incoming packet rate. The subsystem embodiments described herein offer tremendous advantage since the process of operation offloads data security related processing from the main CPU (host processor or array, see FIG. 20) and at the same time supports multiple security standards at high performance. The subsystem also provides

a direct mode in which one or more such CPUs can directly engage hardware cryptographic cores to process non-packet (non-standard) data.

[0069] The field of Cryptography processing has numerous acronyms, and TABLE 1A provides a Glossary for some of them. TABLE 1A also illustrates the diversely extensive numerousness of these processing operations demanded for execution at high rates.

TABLE 1

| GLOSSA           | RY OF CRYPTOGRAPHY AND COMMUNICATIONS                         |

|------------------|---------------------------------------------------------------|

| Acronym          | Description                                                   |

| AAD              | Additional authenticated data (for Galois)                    |

| AES              | Advanced Encryption Standard                                  |

| AES-CMAC         | Advanced Encryption Standard Cipher-based Message             |

|                  | Authentic'n Code                                              |

| Air Cipher<br>AH | Cipher to protect wireless over-the-air communications        |

| CBC*             | Authentication Header, part of IPSEC<br>Cipher Block Chaining |

| CBC-MAC          | Cipher Block Chaining - Message Authentication Code           |

| CCM*             | Counter with CBC-MAC                                          |

| CFB*             | Cipher Feedback                                               |

| Cipher           | Procedure for performing encryption or decryption             |

| CTR*             | Counter. An encryption mode.                                  |

| DES              | Data Encryption Standard                                      |

| DFC              | Decorrelated Fast Cipher                                      |

| DSL              | Digital Subscriber Line, type of wired network over           |

|                  | telephone line                                                |

| ECB              | Electronic Code Book                                          |

| Ethernet         | Type of wired network using cabling on premises               |

| nan              | between computers                                             |

| ESP              | Encapsulating Security Payload, part of IPSEC packet          |

| . = (0           | protection                                                    |

| A5/3             | GSM key stream generator                                      |

| F8#              | A confidentiality process in UMTS, uses Kasumi                |

| F9#              | An integrity process in UMTS, uses Kasumi                     |

| ECB              | Electronic Code Book                                          |

| FIPS             | Federal Information Processing System                         |

| GCM*             | Galois Counter Mode                                           |

| GMAC             | Galois Message Authentication Code                            |

| GPRS             | General packet radio service. A wireless standard.            |

| HMAC             | Hashed Message Authentication Code                            |

| IETF             | Internet Engineering Task Force                               |

| IKE              | Internet Key Exchange                                         |

| IPSEC            | Internet Protocol Security                                    |

| Kasumi           | Block cipher in UMTS, GSM, GPRS. An Air Cipher.               |

| LAN              | Local Area Network                                            |

| MACSEC           | Media Access Control Security, IEEE 802.1AE, e.g.,            |

| 100              | for Ethernet                                                  |

| MD5              | Message Digest 5                                              |

| NIST             | National Institute of Standards and Technology                |

| OFB*             | Output Feedback. An encryption mode.                          |

| RFC              | Request for Comment                                           |

| SHA              | Secure Hash Algorithm                                         |

| SnowSG           | Word-oriented stream cipher, an Air Cipher                    |

| SRTP             | Secure Real-time Transport protocol                           |

| SS               | Subscriber Station                                            |

| SSL              | Secure Socket Layer                                           |

| TLS              | Transport Layer Security                                      |

| UMTS             | Universal Mobile Telecommunications System. A                 |

| TIT AND          | wireless standard.                                            |

| WLAN             | Wireless Local Area Network                                   |

| 3DES             | Triple DES                                                    |

| 3GPP             | 3rd Generation Partnership Project                            |

\*Examples of confidentiality modes that use AES or 3DES cores are CBC, OFB, CFB, CTR, GCM, and CCM, which are used in IPSEC applications.

#Kasumi-F8 and Snow3G-F8 are used in 3GPP technology to secure data traffic transmitted via antenna, hence the phrase Air Cipher herein.

[0070] TABLE 1B provides another Glossary for acronyms used to describe the embodiments.

TABLE 1B

| Acronym | Description                                                           |

|---------|-----------------------------------------------------------------------|

| CDMA    | CPPI DMA controller (distinct from wireless CDMA next                 |

| CDMA    | Wireless code division multiplex for telecom                          |

| CMD     | Command                                                               |

| CPPI    | Communication Processor Peripheral Interface                          |

| CP_ACE  | Accelerated Cryptographic Engine. Subsystem example of<br>embodiment. |

| CTR     | Counter                                                               |

| CTX     | Context                                                               |

| ctxcach | Context Cache                                                         |

| DDR     | Double Date Rate, type of RAM                                         |

| DMA     | Direct Memory Access, peripheral circuit                              |

| EMIF    | External Memory Interface                                             |

| EOP     | End of Packet                                                         |

| FW      | Firmware, e.g. software stored in flash non-volatile memory.          |

| HFN     | Hyperframe Number                                                     |

| HW      | Hardware                                                              |

| IV      | Initialization Vector, for key derivation                             |

| LSB     | Least Significant Bit                                                 |

| MCE     | Mode control engine, another type of embodiment                       |

| MMR     | Memory Mapped Register                                                |

| MOP     | Middle of Packet                                                      |

| MSB     | Most Significant Bit                                                  |

| PA      | Packet accelerator                                                    |

| PHP     | Packet header processor                                               |

| PDSP    | Packed Data Structure Processor, another type of                      |

|         | embodiment: programmable engine for parsing a packet                  |

|         | header, trailer, and payload                                          |

| PKA     | Public Key Accelerator                                                |

| RAM     | Random Access Memory                                                  |

| RISC    | Reduced Instruction Set Computing or Computer                         |

| RNG     | Random Number Generator                                               |

| ROC     | Rollover Counter                                                      |

| SC      | Pointer Security context pointer holding data                         |

|         | structure in host memory                                              |

| SCCTL   | Security context control word, TABLES 19, 10.                         |

| SCID    | Security context ID                                                   |

| SCIDX   | Security index                                                        |

| SCPTR   | Security context pointer                                              |

| SOP     | Start Of Packet                                                       |

| sw      | Software or firmware                                                  |

| SW      | Software Word                                                         |

| VBUSP   | VBUS Protocol bus signaling protocol                                  |

[0071] Embodiments exemplified by the subsystems described at length herein are flexible and adaptive thereby allowing new security standards and application-specific encryption operational modes to be updated in the field. Various embodiments provide a high performance, loosely coupled packet engine to encrypt, decrypt and authenticate data on-the-fly thereby maintaining a suitably-specified wire-rate or wireless rate, and to perform a threshold level of security monitoring on inbound traffic to provide sanity and integrity checks to protect host processor 100 from unwanted traffic. Minimal intervention from host 100 is involved to process data, but at same time the host 100 is fully in control of such processing. The subsystem can cache high-speed connections keys and control, thereby promoting efficient high speed execution. Auto-fetch keys and control structures from host memory are provided in secure fashion as and when appropriate, so that the system is secure when caching high-speed connections keys and control. Some embodiments provide direct cryptographic processing acceleration to host 100 to encrypt/authenticate raw data (nonpacket), especially for multi-media applications.

[0072] A public key accelerator (PKA) aids host 100 for key generation/derivation mainly for IKE and other similar

processes. A non-deterministic true random number generator (TRNG) is provided and is host-accessible. A high performance, link-list based, descriptor-driven scattergather CPPI DMA (direct memory access) can queue packets. Firmware is updatable in the field to enhance/support new processing features such as new header processing features and other features.

[0073] The system has a remarkable structure and process to update micro-instructions in the field to support new encryption operation modes like CCM etc.

[0074] High Level protocols supported include 1) transport mode for both AH and ESP processing for IPSEC protocol stack, 2) tunnel mode for both AH and ESP processing, 3) full header parsing and padding checks, 4) Construct initialization vector IV from header, 5) anti-replay attack resistance, 6) SRTP protocol stack to support F8 mode of processing and replay protection, 7) WiMax encryption, 8) 3GPP protocol stack, 9) Wireless Air cipher standard, 10) A5/3 mode, 11) firmware enhancements for SSL and MAC-SEC

TABLE 2

| PERFORMANCE EXAMPLE |              |  |  |

|---------------------|--------------|--|--|

| Protocol            | Mbits/sec    |  |  |

| IPSEC - ESP         | 1400         |  |  |

| IPSEC - AH          | 1400         |  |  |

| 3GPP                | 400          |  |  |

| SRTP                | 400          |  |  |

| Legal co-existence  |              |  |  |

|                     |              |  |  |

| IPSec + SRTP        | 1800 (Total) |  |  |

| IPSec + 3GPP        | 1800 (Total) |  |  |

[0075] In the keys and control structure, host 100 forms a security context under which the hardware encrypts and decrypts keys, provides connection-specific control flags, anti-replay windows, and firmware parameters, and establishes static connection values such as a nonce or a salt. (A nonce is a security string or number used once. A salt is a random value input used along with a password in key derivation.)

[0076] The system in one example supports up to 32,768 (or  $2^{15}$ ) simultaneous connections or more. Setup is as easy as sending packet pertaining to that connection. Host 100 can lock high-speed connections. Any connection can be smoothly torn down.

[0077] A control structure is auto-fetched on a demand basis, as and when requested, to cache up to 64 security contexts or more. A security context is cached permanently if locked by host 100. Also, host 100 is operable to automatically evict old connections to make room for new connections.

[0078] Some embodiments secure the security context itself, and/or fetch the connection in secure mode using secure infrastructure.

[0079] In FIG. 1, hardware 200 in one embodiment has a Two-Plane architecture herein including a data plane 300 and a control plane 400. The data plane 300 supports cryptographic payload processing by providing and utilizing modules for authentication processing 320, encryption processing 310, air ciphering 370, public key acceleration PKA, and a true random number generator TRNG. Further, as shown in FIGS. 1, 10, 11, 12, 13, and 14, the planes cut

through each of the just-noted modules and the packet header processing PHP modules **410** and **460**. The data plane involves the blocks or sub-blocks primarily involved with handling packets "p" (packet data). The control plane involves the sub-blocks primarily involved with handling packets "c" for control data, packets "\_" (unmarked) for scheduler data, and packets "f" for configuration data. PKA and TRNG by having lines marked "f" represent a slight legend exception to the foregoing generalization, and PKA and TRNG partake of data-plane. The basic structure and benefits of the distinction between planes are nonetheless consistent throughout.

[0080] The control plane includes one or more packet header processing PHP modules and provides Ingress header checks and Egress header updating. The special CPPI IO's along with these data and control planes provide a high-performance streaming interface.

[0081] In both control plane and data plane, shared hardware crypto core hardware is provided for IPSec, SRTP and Transport layer, thereby saving integrated circuit real estate expense. The architecture segregates the data plane 300 from the control plane 400 (or generally provides a parallel control information transfer path in upper half as compared with data path in lower half in FIGS. 10, 11, 12, 13, and 14) for true pipelined processing, so no stall arises even if delays occur in either the control plane or data plane. The fully-pipelined engine, or structure e.g. of FIG. 1, supports Encryption and Authentication simultaneously, and also provides any-order staging, such as AES followed by SHA or SHA followed by AES, or AES1 followed by AES2, for some examples.

[0082] In data plane 300 (or cut-through data-related portion in FIGS. 10, 11, 12, 13, and 14), a cryptographic payload processing module provides authentication 320 processing for SHA1 and AES (used for authentication too), MD5, and SHA2, for instance. Keyed HMAC (Hashed Message Authentication Code) operation via hardware core using MD5, SHA1, SHA2-224 and SHA2-256, and support for truncated authentication tag are included.

[0083] Block data encryption is supported via respective hardware cores for processing AES, DES, 3DES, and Galois multiplier, see module 310. Supported Air Ciphers include Kasumi and Snow3G for stream data encryption, see module 370. Security context architecture has on-chip cache (FIG. 8) with auto-fetch and can cache 64 contexts and auto-Evict or auto-Fetch a Security context on a demand basis. A Public Key Accelerator module includes a high performance, public key engine for large vector math operation and supports a modulus size up to 4096-bits or more for public key computations. Further, the Cryptographic Payload processing module(s) in the data plane has a True Random Number Generator TRNG, is non-deterministic and FIPS compliant. Null cipher and null authentication support debugging.

[0084] Further in FIG. 1, the independent control plane and data plane architecture allows host 100 to selectively use only data plane 300 components while bypassing the control plane 400. In a cut-through mode of operation, packets are processed as and when received, without waiting for the complete packet to finish. Packets are processed in chunks thereby ensuring that all the hardware engines are fully engaged. The context cache module 510 is coupled for auto fetch of security context based on current state of an engine, and pre-fetch security context is based on information available from an ingress FIFO. An option allows storage of

security context within an engine for high performance connections. Auto-eviction of security context is based on unavailability of space within the context cache in FIG. 8. Fully pipelined engines for parallel processing allow multiple processing on a same payload by auto-forwarding to next engine.

[0085] To avoid limitlessly accumulating mode-specific hardware cores for multiple modes like CBC, OFB, CFB, CTR, GCM, CCM and other modes, a remarkable programmable Mode Control Engine MCE of FIG. 11 herein sequences various logical and arithmetic operations and other instructions to achieve each desired encryption/authentication operational mode and leverage the speed of associated hardware crypto cores. The sequence of operations is contained in a set of instructions that are stored as part of the security context in the memory. MCE also has registers (e.g., four registers each 128-bit such as in its Register Bank) to store the immediate result after each operation. In addition, the security context of FIG. 2 in memory stores encryption and authentication key and some other security parameters such as Initial Vector (IV), encryption mode, authentication tag length and location, date offset and security process details. Many of the MCE instructions as in TABLE 13 are also specifically set up to have direct access to these parameters.

[0086] In the control plane 400 (or cut-through controlrelated portion in FIGS. 10, 11, 12, 13, and 14), a cryptographic control plane processing module includes two instances 410, 460 of a PHP (Packet header processor) of FIG. 13 and has a 32-bit Low gate count RISC CPU (PDSP) header processing engine for programmable protocol-related packet header and trailer and payload parsing for true 64K bytes packet processing, padding checks, security procedure control and decode, 16K of instruction RAM, and 8K scratch-pad RAM in one set of RAM size parameters for an implementation example. A hardware-accelerated security context viewer module is provided, as well as a hardwareaccelerated packet viewer module. A special data engine designated CDE is beneficial for packet type application and allows hardware accelerated bytes insertion and removal from any packet.

[0087] Software and firmware architecture includes firmware for IPSEC, firmware for SRTP, and firmware for 3GPP, and firmware that schedules the processing for the hardware engines. A driver layer is provided.

[0088] In FIGS. 1 and 2, the subsystem 200 includes and uses FIFOs and CDMA (CPPI DMA Communication Processor Peripheral Interface direct memory access controller) to fetch packet descriptors and buffers contents from a system 3500 such as in FIG. 20. In FIG. 2, subsystem 200 (3540) maintains a receive queue (Queue X) for ingress for the security accelerator. Receive queue holds one or more Host Packet Descriptors that each have 1) a handle to access a security context buffer in a protocol-specific part, and 2) a pointer to a Data Buffer for data or from which to access data. The security context (SC) buffer holds security context information that is collectively called a Security Context. The Security Context includes information such as encryption and authentication key, initialization vector (IV), encryption mode, authentication tag length and location, and data offset and other security process details. The Data Buffer holds SOP (start of packet), EOP (end of packet), and a block of data to be cryptographically processed such as by encryption, decryption, authentication, or otherwise according to the encryption mode.

[0089] In FIG. 2, subsystem 200 also maintains a transmit queue (Queue Y) used for egress with the security context, and multiple transmit queues are established for multiple concurrent security contexts. A transmit queue holds a Host Packet Descriptor that contains 1) a handle to access the security context buffer or an output security context buffer in the protocol-specific part, 2) a pointer to the Data Buffer or to an output data buffer from which to access data, and 3) extended packet information, such as to indicate whether the security context has been updated. The security context (SC) buffer for transmit purposes not only holds the Security Context as already described but also any updated ROC (rollover count), HFN (hyperframe number), etc. The Data Buffer for transmit purposes holds SOP (start of packet), EOP (end of packet), and a block of output data resulting from the cryptographic processing.

[0090] In FIG. 3, receive operations relate to that receive queue of FIG. 2 and involve ingress of a series of packets each having a plaintext PDU (Protocol Data Unit) header and packet payload data arriving for cryptographic processing. Host Packet Descriptors correspond to the packets and have a pointer that points to the data buffer block of data to be decrypted or encrypted. Such Host Packet Descriptor has one or more protocol-specific fields that point to the Security Context or fields therein. These receive operations also relate to the chunking of the packets by subsystem 200, i.e. breaking a data packet on ingress into smaller data chunks. [0091] In FIG. 4, the subsystem 200 of FIG. 1 adaptively organizes a programmable structure called a logical topology for IPSEC outbound and IPSEC inbound packets using its IPSEC PHP 410 in FIG. 1. (See FIG. 13 for a PHP detail that is used in each of the IPSEC PHP and Air Cipher PHP and that uses a processor PDSP.) For IPSEC outbound packets, first pass packet header processing by IPSEC PHP 410 is followed in FIG. 4 by Encryption SS 310, then Authentication SS 320, and then IPSEC PHP pass 2 processing. See also the associated security context of FIG. 6 and FIG. 3. For IPSEC inbound packets, first pass packet header processing by IPSEC PHP 410 is followed in FIG. 4 by Authentication SS 320, then Encryption SS 310 (decryption), and then IPSEC PHP pass 2 processing. If one IPSEC packet stream is outbound while another IPSEC packet stream is inbound, then both forms of processing in FIG. 4 can be set up and executed concurrently. Buffering 250.i supports the logical topology, such as cascade or serial nature of the outbound and inbound processes. Indeed, the subsystem of FIG. 1 not only effectively supports either of those FIG. 4 processes individually but also is or can be relatively evenly loaded while supporting both of those FIG. 4 processes concurrently. This is because the chunks (FIG. 9) are likely to be of similar size, and the differing order of operations for outbound and inbound readily have a FIG. 1 encryption block 310 running for outbound while an authentication block 320 is running for inbound, and vice versa. Notice that the buffers 250.i in FIG. 4 are some of the FIFO buffers at the inputs of Crypto Data and Scheduler SCR 260 of FIG. 1 and any buffers in the blocks or modules themselves. Under the configured or programmably established logical topology, those buffers of FIG. 1 are re-arranged or selectively multiplexed into whatever operational order (such as in the examples of FIGS. 4 and 5) is specified to establish a particular currently-employed process or future process. These processes can be in one security context or in plural security contexts such as represented by any one or more of various forms of FIGS. 6 and 7 and FIGS. 2 and 3. [0092] When FIG. 1 is considered in light of FIGS. 4 and 5, the logical topologies of FIGS. 4 and 5 or otherwise, are recognized as various programmably-helical paths (involving what are called "rounds" herein) that can be established adaptively in and in a sense form the structure of FIG. 1 into one or more coils (rounds) mediated by the Crypto Data and Scheduler SCR 260. Depending on context, the term "round" may also refer to a sequence of operations cycling through a same given subset of the modules among modules 410, 460, 310, 320, 370 and buffers 250.i. Notice the compatible lines for control plane and data plane throughout FIGS. 10-14. Multiple packet flows streaming into the PA and CDMA Ingress CPPI Streaming Interfaces are coiled at any given moment into logical topologies of approximately concurrent data flow and processing, and output data streams emerge out of the PA and CDMA Egress CPPI Streaming Interfaces. The various modules that concurrently participate in the different coils (rounds), and in what order for each coil (round), are established according to the Security Context Cache information and the Configuration SCR information. The operations of the modules are sequenced in a given coil (round). These operations appear to alternate or form other remarkable patterns of operation in space and time, as the remarkable CP\_ACE subsystem 200 is configured and called and does its work.

[0093] In FIG. 5, the inventive CP\_ACE subsystem 200 of FIG. 1 adaptively organizes a programmable structure (logical topology) for Air cipher/Stream cipher. For Air Cipher, first pass packet header processing by PDSP of FIGS. 1, 13 Air Cipher PHP 460 is followed in FIG. 5 by Air Cipher SS processing in the separate Air Cipher module 370 of FIGS. 1 and 14, and then further followed by FIG. 5 Air Cipher PHP 460 pass 2 processing. See also the associated security context of FIG. 7 and FIG. 3 and TABLE 5. Concurrently or otherwise for Stream cipher, first pass packet header processing by PHP 460 is followed in FIG. 5 by Stream Cipher SS in module 370, and then PHP 460 pass 2 processing. Buffering 250.i again supports the logical cascade or serial nature of these parallel processes so that the subsystem of FIG. 1 is relatively evenly loaded.

[0094] Notice that the logical topologies of both FIGS. 4 and 5 can be executed concurrently due to the additional level of parallelism of the subsystem 200. Accordingly, not only can subsystem 200 be characterized by control plane/data plane parallelism but also cryptographic parallelism such as illustrated for supporting Internet and wireless concurrently. Subsystem 200 embodiments thus also remarkably introduce a two-dimensional parallelism in four quadrants for control/data and Internet/wireless cryptographic and other processing to which the advantages commend them.

[0095] As illustrated by examples of FIG. 6 and FIG. 7, each individual security context per-connection accessible via Ctx Fetch VBUSP in FIG. 1 Host memory 120 (3520.3, 3550 in FIG. 20) is made up of three parts: Software-only section, PHP section, and data plane processing section. The Software only section holds the information that is used by software (DSP code) for managing security context and for storing connection-specific data, and this information does not need to be fetched by CP\_ACE subsystem 200. The PHP

section in FIG. 6 or 7 holds PHP control information used by each packet header processing (PHP) module 410 or 460 in subsystem 200 to maintain the current state of the connection along with data used to process packets. This PHP section in FIG. 6 or 7 is fetched and updated as needed using DMA 520 of FIG. 8. The third and fourth sections in FIG. 6 or 7 hold data plane processing (Encryption, Authentication, and/or Air Cipher) module-specific control and state information fetched by subsystem 200 as needed. Subsystem 200 does not need to write/update these data plane processing subsystem sections. To maximize the EMIF (external memory interface) efficiency, each FIG. 6 section starts at a 64-bytes aligned address, for instance. Hardware control structure is aligned to 64-bytes to allow cascading of multiple control structures.

[0096] In FIG. 6, a security context example is shown for IPSEC or SRTP in ESP mode as seen by DSP software. This context uses Authentication (SHA/MD5) and Encryption (AES/3DES). This flow is same for both Inbound and Outbound. A Host pointer points to a 64-bytes Softwareonly section that is not fetched by CP\_ACE. The SCPTR pointer of TABLE 10 points to a section in FIG. 6 that has SCCTL (8-bytes), a Packet Header processor (PHP) modulespecific section, followed by an encryption module-specific section, and further followed by an Authentication modulespecific section. The 56-bytes Packet Header processor (PHP) module specific section is fetched by subsystem 200 and used for IPSEC header processing using PDSP and CDE engine and PHP Pass1/Pass2 Engine ID (TABLE 5). The 96-bytes Encryption module-specific section is fetched by subsystem 200 and used for IPSEC encryption using AES/ 3DES core and Encryption Pass1 Engine ID. See discussion of FIG. 10 and TABLES 11-12 later hereinbelow. The 96-bytes authentication module-specific section is also fetched by CP ACE and used for IPSEC Authentication using SHA/MD5 core and Authentication Pass1 Engine ID. See discussion of FIG. 12 and TABLE 15 also.

[0097] In FIG. 6, for SRTP, the three module-specific sections are used in the same way but have different numbers of bytes than used for IPSEC. Thus, multiple modes for IPSEC and for SRTP respectively are analogously supported by the same FIG. 1 hardware for PHP, encryption, and authentication.

[0098] In FIG. 7, another example of security context is provided for Air cipher Outbound, where encryption (Kasumi-F8) is done first, followed by Authentication (Kasumi-F9). In this case a same hardware engine is used twice. The order of Authentication/Encryption sections is beneficially reversed in FIG. 7 for Air Cipher Inbound. A 56-bytes Packet Header processor (Air Cipher PHP) module-specific section is fetched by subsystem 200 and used for Air cipher header processing using PDSP and CDE engine and PHP Pass1/ Pass2 Engine ID (TABLE 5). A 64-bytes Air cipher module specific section is fetched by subsystem 200 and used for Air cipher encryption using Kasumi/AES/Snow3G core (e.g., Kasumi-F8) and Air Cipher Pass1 Engine ID. A second 64 bytes Air cipher module-specific section is also fetched by CP\_ACE and used for Air cipher integrity protection using Kasumi/AES/Snow3G core (e.g., Kasumi-F9) and Air Cipher Pass2 Engine ID. See discussion of FIG. 14 and TABLES 16-17 also.

[0099] FIG. 7 also is re-used as a Figure to show a separate example of security context (separately-stored in memory) for Air cipher Inbound, where Authentication (Kasumi-F9)

is done first, and followed by Encryption (Kasumi-F8). In this case a same hardware engine is used twice. The order of Authentication/Encryption sections is reversed for Air Cipher Inbound relative to Air Cipher Outbound. In this way, two different Air cipher modes are supported, depending on the configuration or loading of the security context. [0100] In FIG. 7, yet another security context applies analogously to CCM for Inbound or Outbound modes. The control bits track those of the Air Cipher description by analogy, except that for CCM an AES/3DES core is specified.

[0101] FIG. 8 shows a block diagram for the security context cache module 510 that is coupled to context RAM 570 in subsystem 200 of FIG. 1, and the block diagram also illustrates a flow of the security context cache working process. In FIG. 8, the security context cache 510 has a DMA module 520 that interfaces with the context RAM 570 and couples to a master interface with context fetch bus VBUSP to access security contexts (as in FIG. 2, 3, 6 or 7) in host memory 120 in FIG. 1. This portion operates as a control-plane structure. DMA 520 is operable for fetch and eviction operations with context RAM 570. A lookup module 530 interfaces with a storage called Lookup RAM for data read/write. Such storage is suitably provided in the context RAM 575 space in FIG. 1. Note also the FIG. 1 parallel buffers 250.5 and 250.15 which can be coupled to modules 520, 530 in FIG. 8 directly or multiplexer-coupled into the cache structure. Thus the cut-through organization is carried consistently into the cache structure.

[0102] Cache module 510 in FIG. 8 has three cache port controllers: 1) PA CPPI port controller 540, 2) CDMA CPPI port controller 550, and 3) MMR port controller 560. Arbitration logic 580 supports lookup module 530 by arbitrating any lookup contention for module 530 as between any of the port controllers 540, 550, 560. Arbitration logic 590 supports evict/fetch DMA module 520 by arbitrating any contention for DMA 520 as between any of the port controllers 540, 550, 560. Each of these three port controllers has a set of three control lines with a port prefix followed by \_Lookup\_Req to activate a lookup request, \_EOP\_Req to activate an end of packet request, and \_Schd\_Req to return a scheduling response output. (FIG. 1 shows these control lines in abbreviated manner simply by lines 262, 263 coupling crypto data and scheduler SCR 260 with security context cache module 510.) Each triplet of these control lines is designated by a prefix PA, CDMA, or MMR to indicate that it is coupled to PA CPPI, CDMA CPPI, or MMR block in FIG. 1. Each of the three port controllers 540, 550, 560 has two output lines to convey requests to lookup arbitration 580 and DMA arbitration 590. See, among other controls descriptions elsewhere herein: For PA, see TABLES 26, 28. For CDMA, see TABLES 25, 27. For MMR, see TABLES 21-24. For security context cache operations pertaining to setting up, tearing down, and evicting a security context, see FIGS. 16-18 and TABLE 9.

[0103] Turning to FIG. 9, an internal buffer format is depicted. A packet as received from CPPI 210 or 220 as part of ingress flow is chunked into smaller data blocks within subsystem 200 and packed into the buffer, e.g. 265, with the illustrated format. All of the data processing engines in FIG. 1 use and operate on the basis of this FIG. 9 format to access data for their respective processing. Packet data start position is variable and dependent upon length of the CPPI Pre-data Control words section in FIG. 9. If no CPPI

Pre-data Control words are present, then packet data starts at offset of 64-bytes. In this example, CPPI Pre-data Control words as formed by Host 100 or PDSP software are 8-bytes aligned. Padding of zeroes is executed, if need be, to achieve 8-bytes alignment.

[0104] In FIG. 9, this internal buffer format or chunk buffer begins at a pointer address Buf\_Ptr with a Descriptor area (e.g., 24 bytes). Refer also to FIGS. 2 and 3 Host Packet Descriptor discussion. Descriptor area is followed by a SW word area (e.g. 8 bytes, see also TABLE 3 and SW0, SW1). Trailer information called the PS word (32 bytes) and then up-to-128 bytes CPPI pre-data control words such as Command label(s) are next in succession. Then follow a Front Packet Grow region (32 bytes), an up-to-256 bytes chunk of variable length packet data, and a Rear Packet Grow region (32 bytes). (All of the numbers of bytes represent non-limiting examples.)

[0105] Each Grow region provides a guard band of buffer space. The Front Packet Grow region provides a degree of protection of CPPI Pre-data Control Words (e.g., Command label(s)) from an error or attack involving the Packet data section in FIG. 9. The Rear Packet Grow region provides a degree of protection of an adjacent chunk buffer space (beyond FIG. 9) from an error or attack that might affect or run-on the size of the Packet data section.

[0106] Returning to FIG. 1, data processing engines and security contexts are further detailed. The letter-code legends for lines used in FIG. 1 and FIGS. 10 and 12-14 are: p=Packet Data

c=Context Data

f=Configuration Data

(none)=Scheduler Data.

[0107] In FIG. 1, the data planes and their independent control avoid stalling of either plane by the other plane. Also, host 100 is free to selectively use the data plane without engaging control plane components. Control plane processing in subsystem 200 is carried out in a Packet header processing (PHP) subsystem 410, 460 each as in FIG. 13 and equipped with PDSP (RISC CPU) and associated CDE engine to parse packet headers and define routing for the data plane. PHP PDSP thereby sets up any desired logical topology as illustrated in the FIGS. 4-5 examples and frees up Host 100. In some embodiments, the PHP PDSP program accesses and executes an adapted version of software that would otherwise burden the Host, so that PHP 410 or 460 controls the hardware modules 310, 320, 370 instead, based on the packet headers and based on the security context (e.g., FIGS. 6, 7, TABLE 19) and Ingress data (TABLE 31 and FIG. 9).

[0108] Firmware executed on PHP PDSP extracts and inspects security headers as per the security protocol stack (IPSEC/SRTP/3GPP etc) in use to define the action to be carried out on the packet. If the packet passes the header integrity check, then packet header processor PHP subsystem (FIG. 13) sets the route for payload processing within subsystem 200. To set the route for payload processing, PHP adds a Command label CmdLbl in a pre-defined format (e.g. TABLES 4-6) in a data buffer holding a packet or chunk as in FIG. 9. Command label CmdLbl is used by an applicable other hardware module (e.g. Encryption, Authentication, Air Cipher) to forward the packet to the appropriate hardware engine in such module 310, 320 or 370. For instance, the packet can be sent to one of AES, DES, or Galois in Encryption module 310; and/or one of the SHA cores or

MD5 in Authentication module **320**; and/or one of AES, Kasumi or Snow3G core in Air Cipher module **370**. The native processing to which each selected scheduled core is adapted then executes. The results are fed into, between and from modules according to the logical topology or topologies set up by PHP **410** or **460** or both.

[0109] In FIG. 1, Data plane processing is carried out by various data processing subsystems, or modules that are partitioned based on nature of processing done by such subsystem or module. Subsystem 200 has three major data processing subsystems, namely 1) Encryption module 310, 2) Authentication module 320 and 3) Air cipher module 370. Packets or chunks thereof are forwarded to the applicable individual data plane module by decoding the command label prefixed in front of the packet chunk (FIG. 9). The command label is attached by control plane, e.g. PHP 410 or 460. Host 100 also can leverage CP\_ACE 200 flexibility by selectively engaging any data plane components by prefixing a Command label in or from the packet thereby bypassing PDSP based processing of PHP.

[0110] The Encryption module 310 of FIGS. 1 and 10 supports confidentiality by carrying out the task of encrypting/decrypting a payload from desired offset using hardware encryption cryptographic cores. In FIG. 9, such offset is represented by the expression Bfr\_Ptr+64+ctl\_length+block data offset. Buffer pointer Bfr\_Ptr points to the chunk, and the just-given offset expression points to portion of packet data payload in the chunk. Encryption subsystem 310 has an MCE (mode control engine, FIGS. 1, 11), an AES core, 3DES core and Galois multiplier core which are deployed by MCE. Mode control engine MCE in the encryption module 310 implements various confidentiality modes like ECB, CBC, CTR, OFB, GCM etc, see "Soft Operational Modes" block representing MCE operation in FIG. 10.

[0111] The Authentication module 320 of FIGS. 1 and 12 provides integrity protection. Authentication module 320 is equipped with SHA1 core, MD5 core, SHA2-224 core and SHA2-256 core to support keyed (HMAC) and non-keyed hash calculations electronically.

[0112] The Air cipher module 370 of FIGS. 1 and 14 secures data sent to a wireless device (such as modem 1100 in FIG. 20) over the air by using wireless-infrastructure-defined cryptographic cores like Kasumi or Snow3G. This module 370 is also used to decrypt the data as received from air interface modules.

[0113] Further in FIG. 1, the control and data plane processing engines 410, 460, 310, 320, 370 each have lines to context RAM 570 to access or store/update the control information pertaining to each logical connection. Context RAM 570 holds the information like Keys, IV, partial data, etc., for each active security context (e.g., as in FIG. 2, 3, 6, or 7). Cryptographic engine CP ACE provides and can store up to e.g., 64 or more context-identifying numbers on-chip based on the desired performance. Context RAM 570 is coupled with Security Context Cache module 510 (FIG. 8) to fetch the context information from external memory 120 to populate the active context on a real-time demand basis. [0114] In FIG. 1, subsystem 200 accepts packets on respective 32-bit PA and CDMA Streaming buses PA\_Str and CDMA\_Str respectively feeding a PA (packet accelerator) Ingress CPPI Streaming Interface port 210 and a CDMA Ingress CPPI Streaming Interface port 220 as part of ingress flow. Each packet destined to subsystem 200 is prefixed with at least 8-bytes of CPPI Software Word (for FIG. 9) that holds information about security context to uniquely identify security connection and associated security parameters. See TABLE 31. Coherency is maintained by CPPI DMA. Word order of operations is in-order so that each new packet starts after a last (previous) packet is completely fetched by CP\_ACE. Egress is handled by a PA Egress CPPI streaming interface 270 and a CDMA Egress CPPI streaming interface 280 on other side or output side of the Crypto Data and Scheduler SCR 260 that has numerous 64-bit registers.

[0115] Regarding the input side of Crypto Data and Scheduler SCR 260, notice that nine FIFO (first in first out) buffers 250.i or queues support: A) the Security Context Cache module 510 with a pair of such buffers 250.5, 250.15 for important parallelism and control bandwidth, and B) one buffer for each of the two Ingress CPPI Streaming Interfaces for PA and CDMA, C) one buffer each (250.1, 250.11) for IPSEC PHP and Air Cipher PHP, and D) one buffer each (250.3, 250.4, 250.7) for the hardware modules or engines (e.g. Encryption 310, Authentication 320, Air Cipher 370) and buffers 250.2, 250.6 for the IPSEC PHP 410 and Air Cipher PHP 460 respectively.

[0116] Crypto Data and Scheduler SCR 260 has an associated Packet RAM 265 and an associated Block Manager Module 380. Crypto Data and Scheduler SCR 260 has respective outputs coupled to IPSEC PHP 410 and Air Cipher PHP 460, and to the Encryption, Authentication, and Air Cipher hardware modules 310, 320, 370, as well as outputs to the PA Egress CPPI streaming interface 270 and the CDMA Egress CPPI streaming interface 280, and an output line (when included) directly external to CP\_ACE. [0117] Security Context Cache module 510 has inputs for context Ctx Fetch by a 128-bit VBUSP bus, and two 64-bit wide lines 262, 263 from Crypto Data and Scheduler SCR 260. Security Context Cache module 510 has a context data line coupled to Context RAM 570, as do each of IPSEC PHP 410 and Air Cipher PHP 460, and the Encryption, Authentication, and Air Cipher hardware modules 310, 320, 370. Context RAM SCR 570 in turn is coupled to three banks of Context RAM 575.

[0118] A Configuration SCR 350 store receives 32-bits input from a Configuration VBUSP bus. Configuration SCR 350 supplies or is accessed for Configuration data for each of IPSEC PHP 410 and Air Cipher PHP 460, as well as providing Configuration data for each of RNG, PKA, MMR registers and two banks of Configuration RAM.

[0119] Packets are fetched to subsystem 200 via CPPI CDMA using, e.g., two ingress channels and sent out of CP\_ACE via, e.g., 16 egress channels (threads). Crypto Data and Scheduler SCR 260 internally breaks up a received packet on-the-fly from either Ingress port (PA 210 or CDMA 220) into data chunks. Each data chunk can hold maximum of e.g. 256-bytes of packet payload. Six banks of packet RAM 265 support Crypto Data and Scheduler SCR 260. This chunking operation is provided to fully engage the hardware engines in modules 310, 320, 370 and to reduce internal buffer (RAM) spaces 250.i. Chunking also promotes efficient, low-latency cut-through mode operations in subsystem 200 wherein the packet data can thereby be processed and is processed as and when received without waiting for a given whole packet to be completely received and stored.

[0120] The initial route in Ingress flow within subsystem 200 is determined by an Engine ID that is extracted from the CPPI software word SW in FIG. 9 and described hereinbe-

low, see also TABLES 3 and 5. Subsequent sequence processing of the data chunk is determined by the command label prefixed to the chunk (FIG. 9, TABLES 4-6) by Host 100 or PHP (packet header processor) module 410 or 460 of FIG. 13. The command label (TABLE 4) holds the engine select codes of TABLE 5 with optional parameters. Multiple command labels can be cascaded (TABLE 6) to allow a chunk to be routed to multiple engines within subsystem 200 to form a logical processing chain. Optional parameters of a command label provide control information pertaining to each processing engine.

[0121] CP ACE allows processing of interleaved data chunks, but always ensures that chunks of a given packet follow the same route within the system thereby maintaining packet data coherency. Chunks are routed to next engine based on command label, and a chunk can be routed back to a same engine for second stage processing. Once chunks are processed they are queued for Egress to exit subsystem 200. Subsystem 200 has two physical egress ports 270, 280 (PA and CDMA). Internal hardware structure ensures that packets entering PA Ingress port 210 can only exit PA Egress port 270; likewise packets entering CDMA Ingress port 220 can only exit CDMA Egress port 280. As packets internal to subsystem 200 are processed in chunks, chunks belonging to different packets may cross each other in time, i.e. a data chunk of a last received packet may come out first on Egress before a first packet data chunk. Hence, CP\_ACE has 16 Egress CPPI DMA channels, and internal hardware ensures that all data chunks belonging to an individual packet go out on a same Egress CPPI DMA channel (thread). The internal hardware maintains packet data coherency on a given CPPI DMA channel.

[0122] Subsystem 200 also hosts TRNG (True Random Number Generator) and PKA (Public Key Accelerator) modules that can be accessed via Memory mapped registers by IPSEC PHP 410 PDSP, Air Cipher PHP 460 PDSP, or by Host 100 to aid key generation and computation.

[0123] CPPI software words SW are formed and attached to a packet (e.g., chunk in FIG. 9) by a packet queuing entity. SW Word0 and SW Word1 of CPPI hold the information to associate the current packet to a security context. SW Word2 is optionally used to specify destination CPPI queue.

[0124] In TABLE 3, a single bit is sufficient for Present info and each flag, otherwise multiple bits are provided.

TABLE 3

| CPPI SW Wo                                                                                                                           | rd0                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Field                                                                                                                                | Width                                                    |

| CPPI Destination Info Present Command Label Present Command Label Offset Engine ID Evict, Tear, NoPayload Security Context ID (SCID) | Multiple bits<br>Multiple bits<br>Flags<br>Multiple bits |

[0125] In TABLE 3, the CPPI Destination Info Present flag indicates that SW word2 is holding CPPI destination queue information thereby detailing the flow index on ingress and free queue number or thread to be used on egress when sending this packet out to CPPI after processing. (Compare also with TABLE 21 and with TABLES 25-28