# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2019/0115260 A1 Hsiao et al.

### Apr. 18, 2019 (43) **Pub. Date:**

CPC .. H01L 21/823425 (2013.01); H01L 29/0607

(2013.01); H01L 27/0251 (2013.01); H01L

(2013.01)

29/4925 (2013.01); H01L 29/7832 (2013.01);

### (54) TRANSISTOR STRUCTURE

(71) Applicant: United Microelectronics Corp.,

Hisnchu (TW)

(72) Inventors: Shih-Yin Hsiao, Chiayi County (TW);

Ching-Chung Yang, Hsinchu City (TW); Kuan-Liang Liu, Hsinchu

County (TW)

(73) Assignee: United Microelectronics Corp.,

Hsinchu (TW)

Appl. No.: 15/813,945 (21)

(22)Filed: Nov. 15, 2017

(30)Foreign Application Priority Data

Oct. 13, 2017 (TW) ...... 106135221

### **Publication Classification**

(51) Int. Cl.

H01L 21/8234 (2006.01)H01L 29/06 (2006.01)

H01L 27/02 (2006.01)H01L 29/78 (2006.01)H01L 21/8249 (2006.01)H01L 29/49 (2006.01)

H01L 21/8249 (2013.01); H01L 29/7835

(52) U.S. Cl.

(57)

A transistor structure includes a source region and a drain region disposed in a substrate, extending along a first direction. A polysilicon layer is disposed over the substrate, extending along a second direction perpendicular to the first direction, wherein the polysilicon layer includes a first edge region, a channel region and a second edge region formed as a gate region between the source region and the drain region in a plane view. The polysilicon layer has at least a first opening pattern at the first edge region having a first portion overlapping with the gate region; and at least a second opening pattern at the second edge region having a second portion overlapping with the gate region.

ABSTRACT

FIG. 2

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

### TRANSISTOR STRUCTURE

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims the priority benefit of Taiwan patent application serial no. 106135221, filed on Oct. 13, 2017. The entirety of the above-mentioned patent application is hereby incorporated by reference herein and made a part of the specification.

### BACKGROUND OF THE INVENTION

### Field of the Invention

[0002] The invention relates to a semiconductor manufacturing technology and more particularly to a transistor structure.

### Description of Related Art

[0003] In the integrated circuit of a semiconductor, the field effect transistor is a major component. A field effect transistor is basically the structure of the metal-oxide-semiconductor (MOS), including a gate structure and a source region and a drain region located at two sides of the gate structure and on the substrate. Besides, a gate insulation layer is disposed between the substrate and the gate structure. Generally, a thickness of gate insulation layer determines a threshold voltage when the transistor starts operating. Since the gate insulation layer is formed by performing a thermal oxidation process to the substrate, the thickness of the gate insulation layer on the edge region thereof is thinner, and the threshold voltage of the transistor is influenced.

[0004] Besides, if the thickness of the gate insulation layer is excessively thin and the operational voltage is excessively high, for example, is within an operating range of medium voltage (MV) or high voltage (HV), a leakage may occur. [0005] The above problems occur more significantly when the transistor has a smaller size. Therefore, in the design and manufacturing processes, factors affecting the quality of transistors needs to be eliminated to as few as possible.

### SUMMARY OF THE INVENTION

**[0006]** The invention relates to a transistor structure, wherein an opening is disposed at an edge region for at least eliminating the occurrence of kink effect or that of gate-induced drain leakage (GIDL) caused by a gate.

[0007] According to an embodiment, the invention provides a transistor structure including a source region and a drain region, and the source region and the drain region are disposed in a substrate and extend along a first direction. A polysilicon layer is disposed over the substrate and extends along a second direction perpendicular to the first direction. The polysilicon layer includes a first edge region, a channel region and a second edge region. The first edge region, the channel region and the second edge region are formed as a gate region located between the source region and the drain region. The polysilicon layer includes at least a first opening pattern at the first edge region and at least a second opening pattern at the second edge region, the first opening pattern has a first portion overlapping the gate region, and the second opening pattern has a second portion overlapping the gate region.

[0008] In an embodiment, the transistor structure further includes a gate insulation layer disposed on the substrate and between the source region and the drain region, wherein the polysilicon layer is located on the gate insulation layer.

[0009] In the transistor structure according to an embodiment, the gate insulation layer has a thickness at the first edge region and the second edge region equal to or smaller than 70% of a thickness of the gate insulation layer in the middle of the channel region.

[0010] In the transistor structure according to an embodiment, the substrate has a channel region located under the polysilicon layer and between the source region and the drain region.

[0011] In the transistor structure according to an embodiment, the first opening pattern includes at least a first opening, and the second opening pattern includes at least a second opening.

[0012] In the transistor structure according to an embodiment, a bottom portion of the first opening pattern and the second opening pattern is covered by a dielectric layer.

[0013] In the transistor structure according to an embodiment, the dielectric layer is a spacer on a sidewall of the first opening pattern and the second opening pattern.

[0014] In the transistor structure according to an embodiment, the first opening pattern and the second opening pattern is identical or different.

[0015] In the transistor structure according to an embodiment, at least one of the first opening pattern and the second opening pattern includes an opening located between the source region and the drain region without overlapping the source region and the drain region.

[0016] In the transistor structure according to an embodiment, at least one of the first opening pattern and the second opening pattern disposes over and is adjacent to the source region and the drain region.

[0017] In an embodiment, the transistor structure further includes a lightly doped region in the substrate, the lightly doped region is located on two sides of the polysilicon layer correspondingly to the source region and the drain region.

[0018] In the transistor structure according to an embodiment, two sidewalls of the polysilicon layer do not have a spacer on the lightly doped region, or two sidewalls of the polysilicon layer have a spacer on the lightly doped region.

[0019] In the transistor structure according to an embodiment, the first edge region and the second edge region equal to or are smaller than 1 nm on the second direction.

[0020] In the transistor structure according to an embodiment, each of the first opening pattern and the second opening pattern has a single opening or a plurality of openings.

[0021] In the transistor structure according to an embodiment, the first opening pattern has a first opening on a center line between the source region and the drain region, and the second opening pattern has a second opening on the center line between the source region and the drain region.

[0022] In the transistor structure according to an embodiment, the first opening includes a portion other than the first portion and extending outward from a first edge line formed by a first edge of the source region and of the drain region, and the second opening includes a portion other than the first portion and extending outward from a second edge line formed by a second edge of the source region and of the drain region.

[0023] In the transistor structure according to an embodiment, the first opening pattern includes a first opening and a second opening, the first opening disposing over and adjacent to the source region, the second opening disposing over and adjacent to the source region, and the second opening pattern includes a third opening and a fourth opening, the third opening disposing over and adjacent to the source region and the fourth opening disposing over and adjacent to the source region.

[0024] In the transistor structure according to an embodiment, each of the first opening and the second opening includes a portion other than the first portion and extending outward from a first edge line formed by a first edge of the source region and of the drain region, and each of the third opening and the fourth opening includes a portion other than the first portion and extending outward from a second edge line formed by a second edge of the source region and of the drain region.

[0025] In the transistor structure according to an embodiment, a cross-sectional structure taken along the first direction of the first edge region and/or the second edge region includes the source region and the drain region in the substrate. The gate insulation layer is disposed on the substrate and between the source region and the drain region. The polysilicon layer is disposed on the gate insulation layer and has an opening in between the source region and the drain region exposing the gate insulation layer.

[0026] In the transistor structure according to an embodiment, a cross-sectional structure taken along the second direction of the gate region includes a gate insulation layer disposed on the substrate and between the source region and the drain region. The polysilicon layer is disposed on the gate insulation layer. The polysilicon layer has a first opening at a first edge region for at least exposing a first edge of the gate insulation layer and has a second opening at a second edge region for at least exposing a second edge of the gate insulation layer.

[0027] To make the above features and advantages of the invention more comprehensible, several embodiments accompanied with drawings are described in detail as follows.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0028] The accompanying drawings are included to provide a further understanding of the invention, and are incorporated in and constitute a part of this specification. The drawings illustrate exemplary embodiments of the invention and, together with the description, serve to explain the principles of the invention.

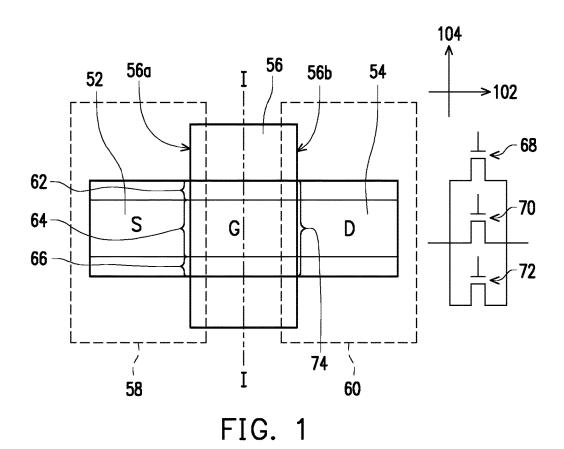

[0029] FIG. 1 is a schematic top view of a transistor structure including two edge transistors and a main channel transistor according to an embodiment of the invention.

[0030] FIG. 2 is a schematic cross-sectional view of a transistor structure along a polysilicon layer according to an embodiment of the present invention.

[0031] FIG. 3 is a schematic top view of a transistor structure according to an embodiment of the present invention.

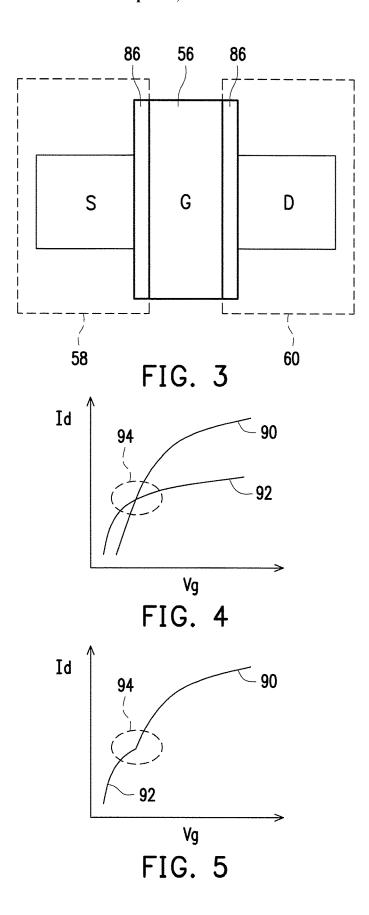

[0032] FIG. 4 is a schematic view of an I-V curve corresponding to a conduction current and a gate voltage of an edge transistor and a main channel transistor of a transistor structure according to an embodiment of the invention.

[0033] FIG. 5 is a schematic view of a kink effect of an I-V curve due to an effect of a transistor structure including an edge transistor according to an embodiment of the invention.

[0034] FIG. 6 is a schematic view of a GIDL mechanism due to an edge effect of a gate insulation layer of a transistor structure according to an embodiment of the invention.

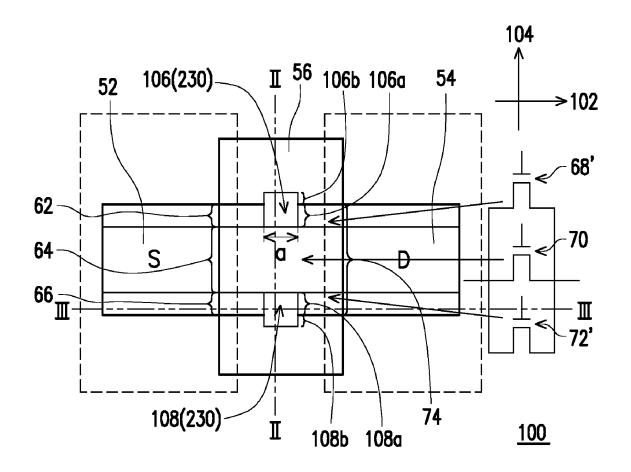

[0035] FIG. 7 is a schematic top view of a transistor structure including two edge transistors and a main channel transistor according to an embodiment of the invention.

[0036] FIG. 8 is a cross-sectional view of a part of a transistor structure taken along line II-II of FIG. 7 according to an embodiment of the invention.

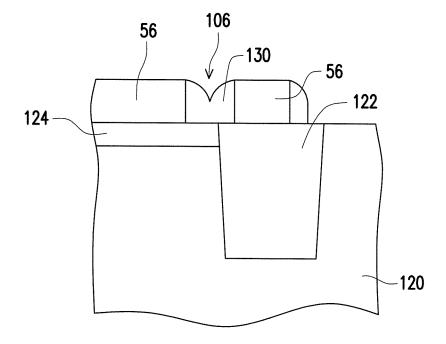

[0037] FIG. 9 is a cross-sectional view of a part of a transistor structure taken along line of FIG. 7 according to an embodiment of the invention.

[0038] FIG. 10 is a schematic top view of a transistor structure including two opening patterns of edge transistor according to an embodiment of the invention.

[0039] FIG. 11 is a schematic top view of a transistor structure including two opening patterns of edge transistor according to an embodiment of the invention.

[0040] FIG. 12 is a schematic top view of a transistor structure including two opening patterns of edge transistor according to an embodiment of the invention.

[0041] FIG. 13 is a schematic top view of a transistor structure including two opening patterns of edge transistor according to an embodiment of the invention.

[0042] FIG. 14 is a schematic cross-sectional view of an opening of an edge transistor according to an embodiment of the present invention.

### DESCRIPTION OF THE EMBODIMENTS

[0043] Some other embodiments of the invention are provided as follows. It should be noted that the reference numerals and part of the contents of the previous embodiment are used in the following embodiments, in which identical reference numerals indicate identical or similar components, and repeated description of the same technical contents is omitted. Please refer to the description of the previous embodiment for the omitted contents, which will not be repeated hereinafter.

[0044] The performance of transistors may be affected by many factors, and the conditions of a gate insulation layer may also affect the operating performance of transistors. For example, generally speaking, a gate insulation layer decreases in thickness on the edge after being formed by a thermal oxidation process. As for a gate between a source region and a drain region, through more meticulous observation, a center region and two edge regions may be viewed as three sub-transistors among which the center region sub-transistor is the major one. Therefore, under general performance requirements, the edge region sub-transistors are ignorable. However, if higher performance is required, the effects of the edge region sub-transistors become significant. The effects of the edge region sub-transistors become significant when the size of component is small, for example, or when the transistor is operated at MV or HV, for example.

[0045] The current kink effect caused by the gate insulation layer occurs because the gate insulation layer of edge region sub-transistor has a thinner thickness and a lower threshold voltage (Vt), and the starting speed is thereby faster. The gate insulation layer of center region sub-transistor has a thickness in accordance with the design and has

a higher threshold voltage, and the starting speed is thereby lower. | Therefore, the current kink effect is as illustrated in FIG. 4 and FIG. 5 to be provided in the following. In addition, the occurrence of GIDL is as illustrated in FIG. 6 to be provided in the following.

[0046] The following will describe some embodiments as examples of the invention;

[0047] however, the invention is not limited by the embodiments.

[0048] FIG. 1 is a schematic top view of a transistor structure including two edge transistors and a main channel transistor according to an embodiment of the invention. Referring to FIG. 1, the invention looks into the structure of a transistor and qualitatively divides the transistor into two edge transistors 68 and 72 and a main channel transistor 70 based on a thickness of a gate insulation layer.

[0049] Taking MV transistor for example, when viewing from the top, a general transistor structure includes a source region (S) 52 and a drain region (D) 54, disposed in a substrate such as substrate 80 illustrated in FIG. 2 and substrate 120 illustrated in FIG. 8. The source region 52 and the drain region 54 extend along a first direction 102. A polysilicon layer 56 is disposed over the substrate and extends along a second direction 104 perpendicular to the first direction 102. The polysilicon layer 56 includes a first edge region 62, a channel region 64 and a second edge region 66 formed as a gate region 74 located between the source region 52 and the drain region 54. A part of the polysilicon layer 56 in the gate region 74 functions as a gate structure (G). The transistor structure may be divided into two edge transistors 68 and 72 and a main channel transistor 70 corresponding to the first edge region 62, the channel region 64 and the second edge region 66.

[0050] MV transistor is taken as an example in the embodiment herein, wherein a plurality of lightly doped regions 58 and 60 corresponding to the source region 52 and the drain region 54 are formed on the substrate in advance and overlap the polysilicon layer 56. A spacer may not be required to form on a sidewall of the polysilicon layer 56. However, the transistor of the invention is not limited to MV transistors. Low voltage transistors or HV transistors, for example, are also applicable. Alternatively, transistors of other structures, such as fin field-effect transistors (Fin FET), are also applicable.

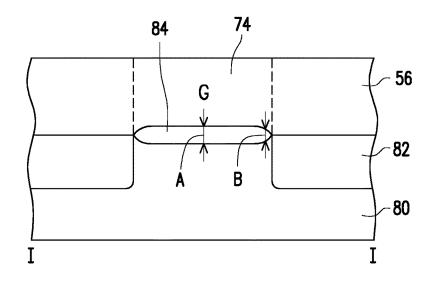

[0051] FIG. 2 is a schematic cross-sectional view of a transistor structure along a polysilicon layer according to an embodiment of the present invention. Referring to FIG. 2, the invention inspects the change of thickness of the gate insulation layer. For example, viewing from the crosssectional structure taken along line I-I of FIG. 1, on the substrate 80 is a region where a gate insulation layer 84 is expected to form, which is generally determined by two insulation structures 82. A surface of the substrate 80, for example, is oxidized to form the gate insulation layer 84 by a thermal oxidation process. A thickness B on the edge region of the gate insulation layer 84 formed by the thermal oxidation process gradually shrinks and the gate insulation layer 84 finally merges with the insulation structure 82. As most of a thickness A on the center region of the gate insulation layer 84 may be maintained at a predetermined thickness and the thickness B on the edge region shrinks, the invention qualitatively divides the transistor into two edge regions 62 and 66. For example, the thickness B equals to or is smaller than 70% of the thickness A.

[0052] FIG. 3 is a schematic top view of a transistor structure according to an embodiment of the present invention. Referring to FIG. 3, a transistor in the embodiment is, for example, a LV transistor, wherein a plurality of lightly doped regions 58 and 60 are generally formed by a polysilicon 56 providing a gate (G). Then, a spacer 86, a source region (S) and a drain region (D) are formed on a sidewall of the polysilicon layer 56. The plurality of lightly doped regions 58 and 60 and the polysilicon layer 56 are not required to substantially overlap herein.

[0053] Provided as follows is the problem investigated by the invention. FIG. 4 is a schematic view of an I-V curve corresponding to a conduction current and a gate voltage of an edge transistor and a main channel transistor of a transistor structure according to an embodiment of the invention. Referring to FIG. 4, since the gate insulation layer 84 has a relative thinner thickness at the edge regions 62 and 66 than on the center region, an I-V curve 92 of the gate insulation layer 84 relating the gate voltage Vg to the drain voltage Id is different from an I-V curve 90 of the channel region 64. The I-V curve 92 and the I-V curve 90 intersect at a region 94.

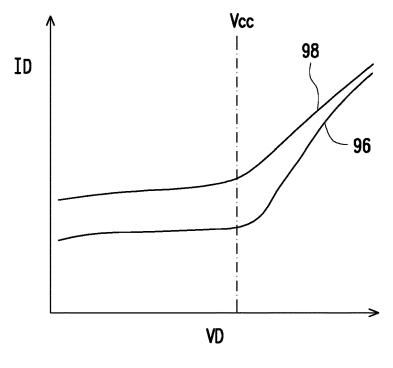

[0054] Since the gate insulation layer 84 has a thinner thickness on the edge regions 62 and 66 and also has a lower threshold voltage, the transistor starts conducting in an unexpectedly faster speed and results in the occurrence of kink effect. According to an embodiment of the invention, FIG. 5 is a schematic view of a kink effect of an I-V curve due to an effect of a transistor structure including an edge transistor. Referring to FIG. 5, in practical operations, the combination of the two I-V curves 90 and 92 of FIG. 4 results in the occurrence of kink effect at the region 94.

[0055] In addition, the thickness of the gate insulation layer 84 would cause GIDL effect as well. According to an embodiment of the invention, FIG. 6 is a schematic view of a GIDL mechanism due to an edge effect of a gate insulation layer of a transistor structure. Referring to FIG. 6, a curve 98 shows a general condition of an edge transistor effect by relating a drain voltage VD to a drain current ID. On the other hand, a curve 96 shows an improved transistor structure provided by the invention. In a current where the transistor has not started yet, the curve 98 has a relative greater leakage than the curve 96.

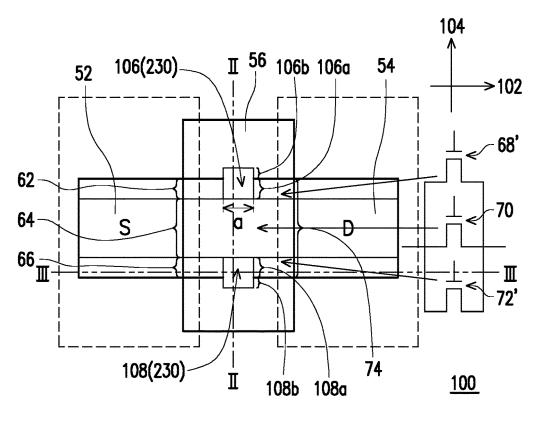

[0056] Based on researches on the effects generated by the gate insulation layer 84 on the edge regions, the invention provides an improved transistor structure. FIG. 7 is a schematic top view of a transistor structure including two edge transistors and a main channel transistor according to an embodiment of the invention.

[0057] Referring to FIG. 7, the invention qualitatively divides the transistor into two edge transistors 68 and 72 and a main channel transistor 70 based on researches on the thickness of the gate insulation layer.

[0058] Taking MV transistor for example, when viewing from the top of a transistor structure 100, a general transistor structure includes a source region (S) 52 and a drain region (D) 54, disposed in a substrate such as substrate 80 illustrated in FIG. 2 or substrate 120 illustrated in FIG. 8. The source region 52 and the drain region 54 extend along a first direction 102. A polysilicon layer 56 is disposed over the substrate and extends along a second direction 104 perpendicular to the first direction 102. The polysilicon layer 56 includes a first edge region 62, a channel region 64 and a second edge region 66. The first edge region 62, the channel

region 64 and the second edge region 66 are formed as a gate region 74 located between the source region 52 and the drain region 54. A part of the polysilicon layer 56 in the gate region 74 functions as a gate structure (G). The transistor structure may be divided into two edge transistors 68 and 72 and a main channel transistor 70 corresponding to the first edge region 62, the channel region 64 and the second edge region 66.

[0059] In this embodiment, the invention provides the polysilicon layer 56 forming an opening 106 and an opening 108 respectively at the first edge region 62 and the second edge region 64 of the gate region 74. The opening 106 and the opening 108 are single openings, for example, but generally speaking, the opening 106 and the opening 108 may be an opening pattern 230 and an opening pattern 232, wherein the location and number of openings are not limited and may be designed according to practical requirements. Embodiments of the variations will be provided in the following FIG. 10 to FIG. 13.

[0060] Regarding the disposition of the opening pattern 230 and the opening pattern 232, the opening 106 and the opening 108 are taken as examples of the opening pattern 230 and the opening pattern 232 in this embodiment. The polysilicon layer 56 includes at least a first opening pattern 230 at the first edge region 62 and at least a second opening pattern 232 at the second edge region 66. The first opening pattern 230 has a first opening portion 106a overlapping the gate region 74; and the second opening pattern 232 has a second opening portion 108a overlapping the gate region 74. [0061] An opening portion 106b of the opening 106 other than the first opening portion 106a is located outside from the first edge region 62. In other words, the opening portion 106b extends outward from a first edge line formed by a first edge of the source region 52 and of the drain region 54. Similarly, the second opening 108 includes the opening portion 108b other than the second opening portion 108a extends outward from a second edge line formed by a second edge of the source region 52 and of the drain region 54. In an embodiment, a thickness of the opening 106 and the opening 108 on the first direction 102 is not specifically limited.

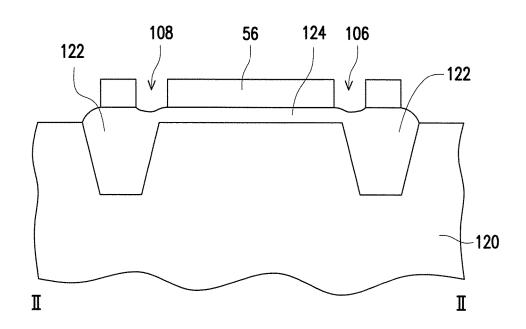

[0062] According to an embodiment of the invention, FIG. 8 is a cross-sectional view of a part of a transistor structure taken along line II-II of FIG. 7. Referring to FIG. 8, in the cross-section of FIG. 7, the cross-sectional structure includes a gate insulation layer 124 disposed on a substrate 120 and between the source region 52 and the drain region 54. Viewing along the second direction 104, the gate insulation layer 124 is connected to an isolation structure 122. The polysilicon layer 56 is located on the gate insulation layer 124 and the isolation structures 122. Only a part of structure related to the openings is illustrated in the polysilicon layer 56 in FIG. 8.

[0063] In addition, the polysilicon layer 56 is disposed on the gate insulation layer 124 and has a first opening 106 at the first edge region 62 for at least exposing a first edge of the gate insulation layer 124. A second opening 108 is located at the second edge region 66 for at least exposing a second edge of the gate insulation layer 124.

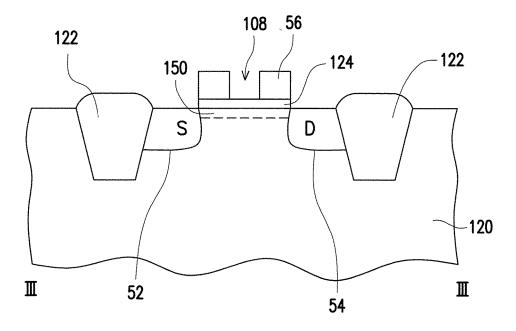

[0064] According to an embodiment of the invention, FIG. 9 is a cross-sectional view of a part of a transistor structure taken along line of FIG. 7. Referring to FIG. 9, a cross-sectional structure taken along the first direction 102 of the first edge region 62 and/or the second edge region 66

includes, for example, a source region and a drain region in the substrate 120. The gate insulation layer 124 is disposed on the substrate 120 and between the source region 52 and the drain region 54. Moreover, the polysilicon layer 56 is disposed on the gate insulation layer 124 and has a first opening 108 in between the source region 52 and the drain region 54 for exposing the gate insulation layer 124. The substrate 120 has a channel 150 under the gate insulation layer 56 and between the source region 52 and the drain region 54. The cross-section line may also be on the first edge region 62 and/or the second edge region 66 herein.

[0065] The aforementioned opening 106 and opening 108 increases a threshold voltage of edge transistors 68' and 72' and thus eliminates the occurrence of kink effects. In addition, the opening of the opening pattern 230 and the opening pattern 232 may also be adjusted with regard to the occurrence of GIDL.

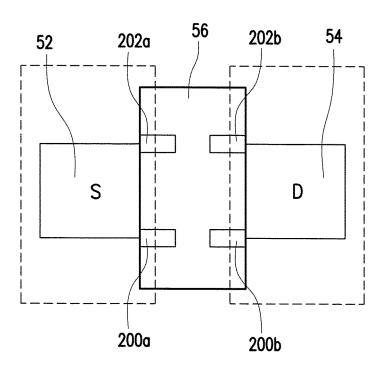

[0066] According to an embodiment of the invention, FIG. 10 is a schematic top view of a transistor structure including two opening patterns of edge transistor. Referring to FIG. 10, a first opening pattern 230, for example, includes a first opening 202a disposing over and adjacent to the source region 52 and a second opening 202b disposing over and adjacent to the drain region 54. A second opening pattern 232, for example, includes a third opening 200a disposing over and adjacent to the source region 52 and a fourth opening 200b disposing over and adjacent to the drain region 54.

[0067] Similar to FIG. 7, each of the first opening 202a and the second opening 202b of FIG. 10 extends outward from a first edge line formed by a first edge of the source region 52 and of the drain region 54, which is similar to the opening portion 106b of the opening 106 of FIG. 7 other than the first opening portion 106a. Each of the third opening 200a and the fourth opening 200b extends outward from a second edge line formed by a second edge of the source region 52 and of the drain region 54, similar to the opening portion 108b of the opening 108 of FIG. 7 other than the first opening portion 108a.

**[0068]** The opening 200a, opening 200b, opening 202a and opening 202b in FIG. 10 not only eliminate the occurrence of kink effect but also reduce GIDL phenomenon. However, the invention is not limited to particular implementation of opening patterns.

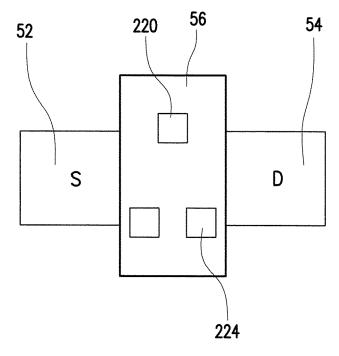

[0069] According to an embodiment of the invention, FIG. 11 is a schematic top view of a transistor structure including two opening patterns of edge transistor. Referring to FIG. 11, in an embodiment, a number of an opening 220 at an edge region is one, as a number of an opening 224 at another edge region is more than one, such as two.

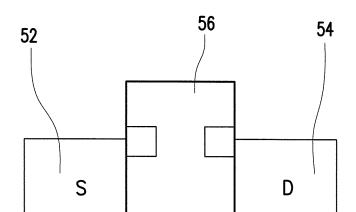

[0070] According to an embodiment of the invention, FIG. 12 is a schematic top view of a transistor structure including two opening patterns of edge transistor. Referring to FIG. 2, in an embodiment, an opening at an edge region may adapt the opening 202a and opening 202b of FIG. 10, as an opening at another edge region may adapt the opening 108 of FIG. 7.

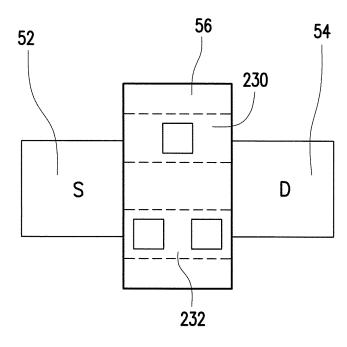

[0071] According to an embodiment of the invention, FIG. 13 is a schematic top view of a transistor structure including two opening patterns of edge transistor. Referring to FIG. 13, generally speaking, a number and location of the opening 230 and the opening 232 may be modified properly, and the opening 230 and the opening 232 may be of identical or different pattern.

[0072] FIG. 14 is a schematic cross-sectional view of an opening of an edge transistor according to an embodiment of the present invention. Referring to FIG. 14, taking the opening 106 of FIG. 8 as an example, a bottom portion of an opening of a transistor structure is covered by a dielectric layer 130. In other words, a bottom portion of an opening pattern is covered by the dielectric layer 130. The dielectric layer 130 is, for example, a spacer left on the sidewall by other manufacturing process and may not require to be applied by an additional process.

[0073] Regarding the transistor structure, the invention provides a polysilicon layer including at least a first opening pattern at the first edge region and at least a second opening pattern at the second edge region. The first opening pattern has a first portion overlapping the gate region, and the second opening pattern has a second portion overlapping the gate region. The opening increases the threshold voltage of the sub-transistor at the edge region and at least eliminates the occurrence of kink effect or that of GIDL.

[0074] It will be apparent to those skilled in the art that various modifications and variations can be made to the disclosed embodiments without departing from the scope or spirit of this invention. In view of the foregoing, it is intended that the invention covers modifications and variations provided that they fall within the scope of the following claims and their equivalents.

- 1. A transistor structure, comprising:

- a source region and a drain region disposed in a substrate and extend along a first direction; and

- a polysilicon layer, disposed over the substrate and extending along a second direction perpendicular to the first direction, wherein the polysilicon layer comprises a first edge region, a channel region and a second edge region, the first edge region, the channel region and the second edge region formed as a gate region between the source region and the drain region in a plane view,

- wherein the polysilicon layer comprises at least a first opening pattern at the first edge region and at least a second opening pattern at the second edge region, the first opening pattern has a first portion overlapping with the gate region, and the second opening pattern has a second portion overlapping with the gate region,

- wherein a portion of the substrate right under the source region, the drain region and the gate region is a single conductivity type.

- 2. The transistor structure according to claim 1, further comprising a gate insulation layer disposed on the substrate and between the source region and the drain region, wherein the polysilicon layer is located on the gate insulation layer, the gate insulation layer is exposed by the first opening pattern and the second opening pattern in the polysilicon layer.

- 3. The transistor structure according to claim 1, wherein the gate insulation layer has a central region, a first edge region and a second edge region, the central region is between the first edge region and the second edge region, wherein a thickness at the first edge region and the second edge region equal to or smaller than 70% of a thickness of the gate insulation layer at a center of the central region.

- **4**. The transistor structure according to claim **1**, wherein the substrate has a channel located under the polysilicon layer and between the source region and the drain region.

- 5. The transistor structure according to claim 1, wherein the first opening pattern comprises at least a first opening and the second opening pattern comprises at least a second opening.

- **6**. The transistor structure according to claim **1**, wherein a bottom portion of the first opening pattern and the second opening pattern is covered by a dielectric layer.

- 7. The transistor structure according to claim 6, wherein the dielectric layer is a spacer of a sidewall of the first opening pattern and the second opening pattern.

- **8**. The transistor structure according to claim **1**, wherein the first opening pattern and the second opening pattern are identical or different.

- 9. The transistor structure according to claim 1, wherein at least one of the first opening pattern and the second opening pattern comprises an opening located between the source region and the drain region without overlapping the source region and the drain region.

- 10. The transistor structure according to claim 1, wherein at least one of the first opening pattern and the second opening pattern disposes over and is adjacent to the source region and the drain region.

- 11. The transistor structure according to claim 1, further comprising a lightly doped region in the substrate, the lightly doped region is located on two sides of the polysilicon layer in the plane view corresponding to the source region and the drain region.

- 12. The transistor structure according to claim 11, wherein the lightly doped region overlaps with or not overlap with the polysilicon layer.

- 13. The transistor structure according to claim 1, wherein the first edge region and the second edge region equal to or are smaller than 1 nm in the second direction.

- 14. The transistor structure according to claim 1, wherein each of the first opening pattern and the second opening pattern has a single opening.

- 15. The transistor structure according to claim 1, wherein the first opening pattern has a first opening on a center line between the source region and the drain region, the second opening pattern has a second opening on the center line between the source region and the drain region.

- 16. The transistor structure according to claim 15, wherein the first opening includes a portion other than the first portion of the first opening pattern and extending outward from a first edge line formed by a first edge of the source region and of the drain region, and the second opening includes a portion other than the first portion and extending outward from a second edge line formed by a second edge of the source region and of the drain region.

- 17. The transistor structure according to claim 1, wherein the first opening pattern includes a first opening and a second opening, the first opening disposing over and adjacent to the source region, the second opening disposing over and adjacent to the source region, and the second opening pattern includes a third opening and a fourth opening, the third opening disposing over and adjacent to the source region and the fourth opening disposing over and adjacent to the source region.

- 18. The transistor structure according to claim 17, wherein each of the first opening and the second opening includes a portion other than the first portion and extending outward from a first edge line formed by a first edge of the source region and of the drain region, and each of the third opening and the fourth opening include a portion other than

the first portion and extending outward from a second edge line formed by a second edge of the source region and of the drain region.

- 19. The transistor structure according to claim 1, wherein a cross-sectional structure taken along the first direction of the first edge region and/or the second edge region comprises:

- the source region and the drain region disposed in the substrate;

- the gate insulation layer disposed on the substrate and between the source region and the drain region in the plane view; and

- the polysilicon layer disposed on the gate insulation layer, wherein the polysilicon layer has an opening between the source region and the drain region in the plane view exposing the gate insulation layer.

- 20. The transistor structure according to claim 1, wherein a cross-sectional structure taken along the second direction of the gate region at the first edge region and the second edge region, comprises:

- a gate insulation layer disposed on the substrate at a region between the source region and the drain region in the plane view; and

- a polysilicon layer disposed on the gate insulation layer, wherein the polysilicon layer has a first opening at the first edge region and a second opening at the second edge region for at least exposing of the gate insulation layer.

\* \* \* \* \*