# (11) EP 1 420 415 B1

(12)

## **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent:

06.01.2016 Bulletin 2016/01

(51) Int Cl.: **G11C 16/30** (2006.01)

G11C 16/10 (2006.01)

(21) Application number: 03104130.4

(22) Date of filing: 10.11.2003

(54) A circuit for programming a non-volatile memory device with adaptive program load control Programmierschaltung für nichtflüchtige Speicheranordnung mit adaptiver Programmladesteuerung Circuit de programmation pour dispositif de mémoire non volatile avec commande de chargement de programme adaptative

(84) Designated Contracting States: **DE FR GB IT**

(30) Priority: 12.11.2002 IT MI20022387

(43) Date of publication of application: 19.05.2004 Bulletin 2004/21

(73) Proprietor: STMicroelectronics Srl 20864 Agrate Brianza (IT)

(72) Inventors:

Micheloni, Rino 22078 TURATE (CO) (IT) Ravasio, Roberto

24030 CARVICO (BG) (IT)

(74) Representative: Manley, Nicholas Michael et al WP Thompson 8th Floor

1 Mann Island Liverpool L3 1BP (GB)

(56) References cited:

WO-A-97/16831 JP-A- 2000 163 323 US-A- 5 930 168 US-B1- 6 418 059

EP 1 420 415 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

25

35

40

45

50

#### Description

**[0001]** The present invention relates to a circuit for programming a non-volatile memory device.

1

[0002] Non-volatile memory devices are commonly used for storing information that must be preserved even when a power supply feeding the memory device is off. A particular type of non-volatile memory device (such as a flash E²PROM) is programmable electrically. A flash memory is typically formed by a matrix of cells, each one consisting of a floating gate MOS transistor; the transistor is programmed injecting an electric charge into its floating gate; conversely, the transistor is erased discharging its floating gate. The electric charge in the floating gate of the transistor modifies its threshold voltage, so as to define different logic values.

[0003] The writing of a block of data on selected memory cells is accomplished through a series of program steps, each one followed by a verification of the values actually stored in the memory cells. During the program step, a voltage pulse is applied to each memory cell that needs to be programmed (in order to cause the injection of electric charge into its floating gate); the program pulse is commonly applied through a driving element (referred to as program load), which is supplied by a charge pump. [0004] Each memory cell absorbs a significant amount of current during the program step; therefore, the number of memory cells that can be programmed at the same time is limited by the capacity of the charge pump.

**[0005]** A solution known in the art for improving the speed of the writing operation is that of providing multiple banks of program-loads. This structure allows more program steps to be carried out in succession without any interposed verification. Therefore, the corresponding time required for switching the flash memory (between a program mode and a reading mode of operation) is saved.

**[0006]** However, the problem of the constraint imposed by the capacity of the charge pump remains unresolved. In other words, in the flash memories known in the art it is not possible to improve the speed of the program step without either increasing the capacity of the charge pump or reducing the current absorbed by the memory cells.

**[0007]** A further example of a prior art arrangement is disclosed in US 5,930,168. US 5,930,168 discloses a flash memory which includes circuitry which receives an external input voltage and generates a voltage  $V_{pp}$  used to program memory cells. US 5,930,168 adjusts memory write operations according to actual voltage conditions present to supply power to the memory cells.

**[0008]** It is an object of the present invention to overcome the above-mentioned drawbacks. In order to achieve this object, a circuit as set out in the first claim is proposed.

**[0009]** In accordance with a first aspect of the invention there is provided a circuit for programming a non-volatile memory device having a plurality of memory cells and a timing unit to provide a clock signal (CLK) which is used

to synchronize all circuits of the non-volatile memory device, the circuit including a plurality of driving elements, each of the plurality of driving elements for applying a program pulse to a selected memory cell to be programmed, the driving elements being suitable to be supplied by a power supply unit, and control means for controlling the driving elements, wherein

the control means includes means for determining a residual capacity of the power supply unit, and selecting means for selectively enabling ones of the plurality of driving elements at each cycle of the clock signal (CLK) according to the residual capacity of the power supply unit for supplying the programming of the plurality of memory cells, the control means to monitor an actual load placed on a charge pump within the power supply unit to determine the residual capacity, the selecting means being configured to enable at least one driving element in succession during a program step of the selected memory cells, the selecting means further including means for disabling each driving element after a predetermined delay from the enabling of the driving element, the delay corresponding to the length of the program pulse, the control means further including means for signaling a completion of the program step when all the driving elements have been disabled.

**[0010]** In accordance with a second aspect of the invention there is provided a method of programming a non-volatile memory device including a plurality of memory cells and a plurality of driving elements each one for applying a program pulse to a selected memory cell to be programmed, the non-volatile memory device further including a timing unit to provide a clock signal (CLK) which is used to synchronize all circuits of the non-volatile memory device, the method including the steps of:

supplying the plurality of driving elements by a power supply unit;

determining a residual capacity of the power supply unit by monitoring an actual load placed on a charge pump within the power supply unit to determine the residual capacity;

selectively enabling ones of the plurality of the driving elements at each cycle of the clock signal (CLK) according to the residual capacity of the power supply unit for supplying the programming of selected ones of the plurality of memory cells;

enabling at least one driving element in succession during a program step of the selected memory cells; disabling each driving element after a predetermined delay from the enabling of the driving element, the delay corresponding to the length of the program pulse; and

signaling a completion of the program step when all the driving elements have been disabled.

**[0011]** Further features and the advantages of the solution according to the present invention will be made clear by the following description of a preferred embod-

iment thereof, given purely by way of a non-restrictive indication, with reference to the attached figures, in which:

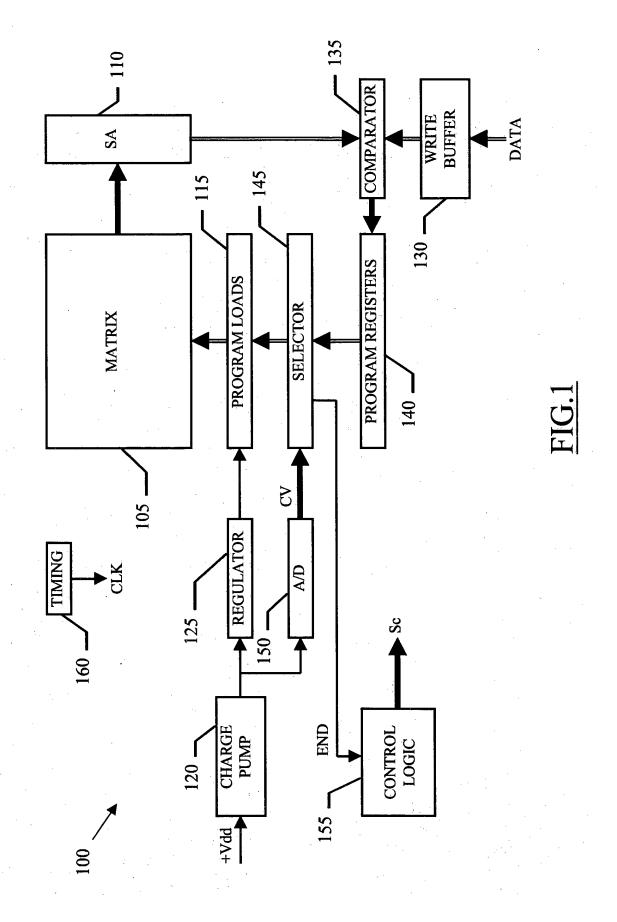

Figure 1 is a schematic block diagram of a writing section of a non-volatile memory device in which the circuit of the invention can be used;

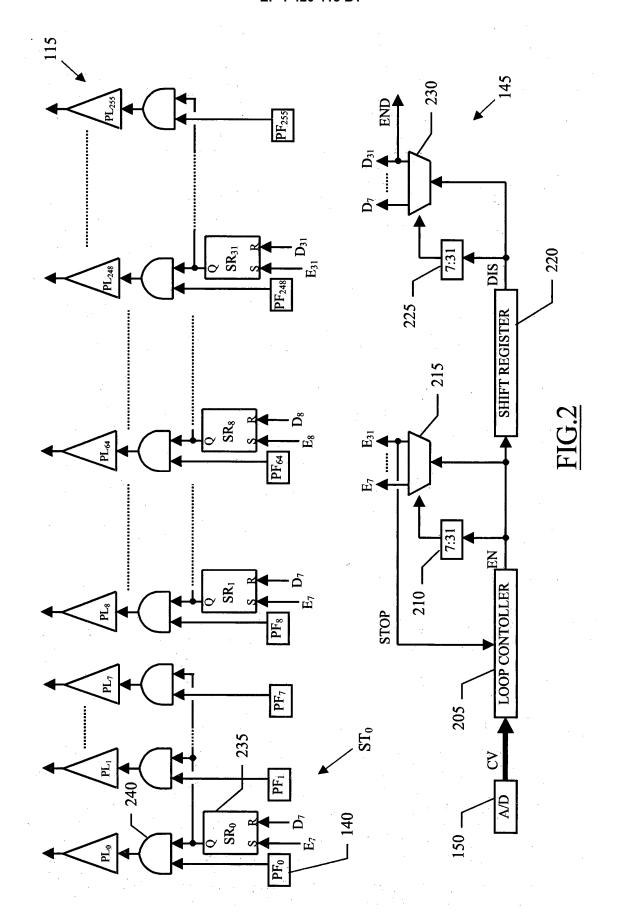

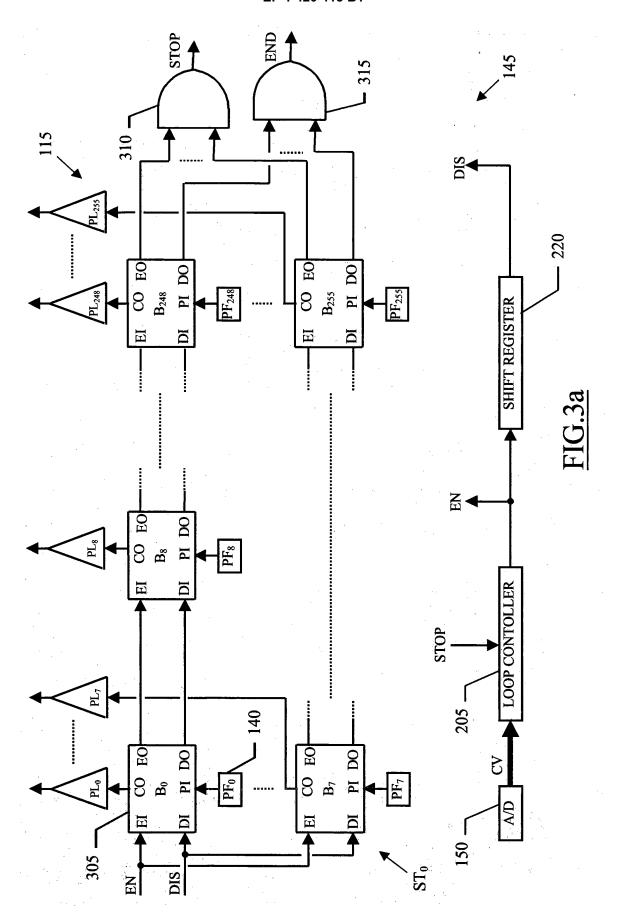

Figure 2 shows a first embodiment of the circuit; Figure 3a shows a different embodiment of the circuit; and

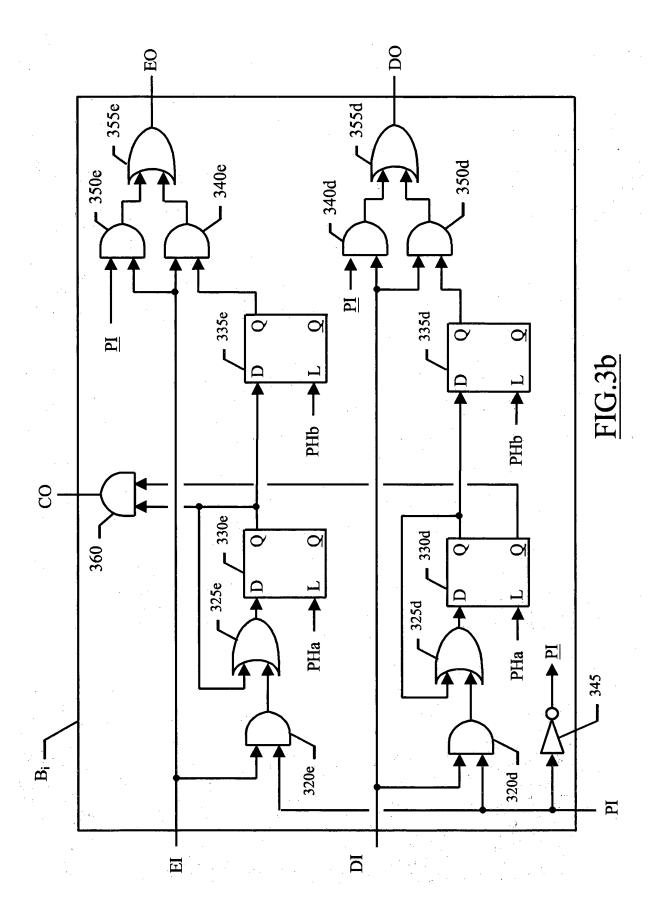

Figure 3b is a representation of a logic block included in the circuit of Figure 3a.

**[0012]** With reference in particular to Figure 1, a writing section of a multilevel flash E<sup>2</sup>PROM 100 is illustrated. The flash 100 includes an array 105 of memory cells (for example, with a so-called NOR architecture). The matrix 105 further includes a column decoder and a row decoder, which are used to select the memory cells (such as 64) of a page consisting of 8 words that are simultaneously processed by the flash 100 (in response to a corresponding address).

**[0013]** Each memory cell consists of a floating gate MOS transistor. The memory cell in a non-programmed (or erased) condition features a low threshold voltage. The memory cell is programmed by injecting electric charge into its floating gate; the memory cell may be programmed to multiple levels, each one associated with a corresponding range of its threshold voltage. Each level represents a different logic value; for example, the flash 100 supports 4 levels so that each memory cell stores a value consisting of 2 bits of information (11, 10, 01 and 00 for increasing threshold voltages).

[0014] A bank of sense amplifiers 110 (64 in the example at issue) is used to read the values stored in the memory cells of a selected page. A bank of program loads 115 is instead used to program the memory cells of multiple selected pages; for example, the flash 100 includes 256 program loads (for programming the memory cells of 4 pages). Each program load 115 drives a memory cell; the program load 115 applies a program pulse providing sufficient energy to some of the electrons (hot electrons) flowing through a channel of the transistor to cause their injection into the floating gate. As a consequence, the threshold voltage of the memory cell is increased.

[0015] A charge pump 120 receives an external power supply voltage +Vdd (for example, 3V relative to a reference voltage or ground); the charge pump 120 generates an internal power supply voltage of higher value (for example, up to 8.5V). The internal power supply voltage is provided to a regulator 125, which maintains the internal power supply voltage substantially constant under changing load conditions. The regulator 125 directly supplies the program loads 115.

**[0016]** A buffer 130 latches a block of data (256 x 2 bits in the example at issue) to be written on the selected memory cells of the matrix (previously erased). A module 135 compares the values stored in the selected memory

cells (read by the sense amplifiers 110 in succession) with the block of data (latched in the buffer 130). For each selected memory cell, the comparator 135 controls a flag PFi (with i=0...255) that is asserted when the memory cell requires a program pulse for approaching the value to be written (i.e., when the value stored in the memory cell is higher than the desired one); the program flags are stored in a bank of registers 140.

[0017] A module 145 accesses the registers 140. The module 145 also interfaces with an analog-to-digital (A/D) converter 150; the A/D converter 150 provides a signal CV indicative of the voltage currently generated by the charge pump 120. The module 145 operates as a selector for enabling the program loads 115; the selector 145 also generates a signal END, which is asserted as soon as a program step on the selected memory cells has been completed.

[0018] The signal END is provided to a control logic 155. The control logic 155 manages operation of the flash 100 by means of a sequence of control signals (denoted as a whole with Sc). A timing unit 160 provides a clock signal CLK, which is used to synchronize all the circuits of the flash 100.

[0019] A writing operation consists of a sequence of program steps and verify steps. Particularly, the block of data to be written on the selected memory cells is compared with the values that are currently stored, and the program flags are set accordingly. As described in detail in the following, a program pulse is then applied to the drain terminals of the memory cells to be programmed (while their gate terminals are kept at a predetermined voltage); the drain/gate voltage has a value such as to increase the threshold voltage of the memory cells of a small amount (for example, 300mV). As soon as the program step has been completed (signal END asserted), the new content of the selected memory cells is compared again with the block of data to be written. The steps described above are repeated changing the voltage at the gate terminals of the memory cells (so as to approximate a trapezoidal wave shape providing a constant electric field at an oxide layer thereof). The writing operation is completed when all the selected memory cells reach the desired values (or the writing operation is aborted after a predetermined number of program steps); typically, a series of 8 program pulses are requested to reduce the value stored in each memory cell of one unit (from 11 to 10, from 10 to 01, or from 01 to 00).

**[0020]** The number of program loads 115 that can be enabled at the same time is limited by the capacity of the charge pump 120 (due to the current absorbed by the memory cells being programmed). For example, a charge pump supplying a maximum current of 5mA cannot program more than about 64 memory cells.

**[0021]** The inventors have discovered that the structures known in the art do not exploit the capacity of the charge pump 120 at its best.

[0022] First of all, the current absorbed by each memory cell (to which the program pulse is applied) is not

40

steady. In fact, the current decreases during the program step while the electric charge is injected into the floating gate of the transistor (and then its threshold voltage is increased).

[0023] Moreover, the charge pump 120 is dimensioned so as to ensure the correct operation of the flash 100 in the worst operative condition; for example, the charge pump 120 can supply the maximum required current (5mA) even when the power supply voltage +Vdd is low (down to 2.7V) and when the environment temperature is high (up to 90°C). Therefore, in a standard operative condition (power supply voltage +Vdd equal to 3V and environment temperature equal to 27°C) the charge pump 120 can supply a higher current (for example, up to 7mA).

**[0024]** At the end, the program pulses are applied only to a portion of the selected memory cells. In fact, at the beginning of the writing operation each memory cell stores the value 11 (having being erased). If the same value 11 must be written on the memory cell, no program pulse is required; one, two or three series of program pulses are instead required to write the values 10, 01 and 00, respectively. Assuming that the values to be written are uniformly distributed among the four possible values 00-11, it results that only 50% of the memory cells must be programmed on the average.

**[0025]** In sharp contrast to the solutions known in the art, the circuit described in the following monitors the actual load of the charge pump 120, so as to estimate a residual capacity thereof. At every clock signal, the program loads 115 are selectively enabled according to the residual capacity of the charge pump 120 (in addition to information about the selected memory cells to be programmed). In this way, the program loads 115 are enabled as soon as possible; in any case, the total current required to the charge pump 120 at any time never exceeds its capacity.

[0026] However, the concepts of the present invention are also applicable when the flash has a different architecture or is replaced with another (electrically programmable) non-volatile memory device (such as an E<sup>2</sup>PROM), when each memory cell stores a different number of bits (down to a single one) or is programmable to another number of levels (even different from a power of 2), when the memory cells are programmed with an alternative procedure, or when a different number of sense amplifiers and/or program loads is provided. Similar considerations apply if the flash has multiple banks of program loads (wherein more program steps are carried out in succession without any interposed verification), if the charge pump and the regulator are replaced with equivalent means, if the program registers store other information, if different means is used for monitoring the current load of the charge pump, and the like. Alternatively, the flash is also suitable to be programmed using an external power supply unit, which is coupled with the program loads through an alternative path; this procedure is typically used by a manufacturer for test purposes or it is available to a user for a fast programming of the flash

**[0027]** In a particular embodiment of the present invention, as shown in Figure 2, the program loads 115 are grouped into multiple subsets; for example, the program loads (individually denoted with  $PL_i$ ) are grouped into 32 subsets  $ST_j$  (with j=0...31), each one of 8 program loads (from  $ST_0$ = $L_0$ - $L_7$  to  $ST_{31}$ = $L_{248}$ - $L_{255}$ ). Each subset of program loads  $ST_j$  is individually enabled as soon as possible.

**[0028]** For this purpose, the signal CV output by the A/D converter 150 is supplied to a loop controller 205. The loop controller 205 generates a global enabling signal EN, which is asserted (at every clock signal) when the residual capacity of the charge pump allows the supplying of a further subset of program loads ST<sub>j</sub>. For example, the loop controller 205 compares the signal CV with a predetermined threshold value; in a more sophisticated structure, the loop controller 205 implements an algorithm that estimates the position of the charge pump on its actual load line.

[0029] The global enabling signal EN is provided to a circuit 210 operating as a counter from 7 to 31, and to a demultiplexer 215 having 31-7=24 output terminals (each one providing a corresponding local enabling signal E<sub>7</sub>-E<sub>31</sub>). The starting number (7) is chosen so as to ensure that the charge pump can always supply the corresponding first subsets of program loads (from ST<sub>0</sub> to ST<sub>7</sub> in the example at issue), even in the worst operative condition. The number stored in the counter 210 controls the demultiplexer 215, thereby transferring the global enabling signal EN to the corresponding output terminal; in this way, the local enabling signals E<sub>7</sub>-E<sub>31</sub> are asserted in succession every time the global enabling signal EN is asserted. The last local enabling signal  $E_{31}$  also defines a suspend signal STOP, which is returned to the loop controller 205.

**[0030]** The global enabling signal EN is also provided to a shift register 220, which outputs a global disabling signal DIS after a predetermined delay. The delay of the shift register 220 is set to a value (for example, 15-30 clock periods) corresponding to the length of the program pulse.

**[0031]** The global disabling signal DIS is provided to a counter 225 (from 7 to 31) and to a demultiplexer 230 (having 24 output terminals each one providing a corresponding local disabling signal  $D_7$ - $D_{31}$ ). The number stored in the counter 225 controls the demultiplexer 230, so as to transfer the global disabling signal DIS to the corresponding output terminal. The last local disabling signal  $D_{31}$  also defines the signal END (for the control logic of the flash).

**[0032]** The selector 145 further includes 32 SR latches 235; each latch (denoted with  $SR_j$ ) is associated with a subset of program loads  $ST_j$ . The first 8 latches  $SR_0$ - $SR_7$  are controlled by the same local enabling signal  $E_7$  and by the same local disabling signal  $D_7$ ; particularly, all the latches  $SR_0$ - $SR_7$  receive the local enabling signal  $E_7$  and

the local disabling signal  $D_7$  at their set terminals (S) and reset terminals (R), respectively. The local enabling signals  $E_8$ - $E_{31}$  and the local disabling signals  $D_8$ - $D_{31}$  are applied to the set terminals and to the reset terminals, respectively, of each one of the remaining latches  $SR_8$ - $SR_{31}$ .

**[0033]** For each program load  $PL_i$  of a generic subset  $ST_j$ , the value provided by a main output terminal (Q) of the latch  $SR_j$  and the program flag  $PF_i$  (stored in the associated register 140) are applied to respective input terminals of an AND gate 240. The signal output by the AND gate 240 directly controls the program load  $PL_i$ .

**[0034]** At the beginning of a program step all the latches  $SR_j$  are in a reset state, and both the counters 210 and 225 store the last number 31. As soon as the control logic enables the loop controller 205, the global enabling signal EN is asserted (since the charge pump always has a sufficient residual capacity). The counter 210 then switches to the starting number 7, so as to assert the local enabling signal  $E_7$ ; in response thereto, the first 8 latches  $SR_0$ - $SR_7$  are set. As a consequence, all the program loads of the subsets  $ST_0$ - $ST_7$  associated with the memory cells to be programmed (program flags  $PF_i$  asserted) are enabled thereby applying a program pulse to the corresponding memory cells.

**[0035]** At the next clock signal, the A/D converter 150 detects the current voltage of the charge pump again. If the loop controller 205 determines that the residual capacity of the charge pump allows the supplying of a further subset of program loads  $ST_j$ , the global enabling signal EN is asserted. The counter 210 is incremented (to the number 8), so as to assert the local enabling signal  $E_8$  and then to set the latch  $SR_8$ . As a consequence, all the program loads of the subset  $ST_8$  associated with memory cells to be programmed are enabled. Conversely, if the limit defined by the capacity of the charge pump has been reached the global enabling signal EN is deasserted; therefore, no further subset of program loads  $ST_j$  is enabled. The same operations described above are continually repeated at every clock signal.

[0036] In the meanwhile, the global enabling signal EN goes through the shift register 220. The global disabling signal DIS is asserted after the corresponding delay from the assertion of the local enabling signal E7. The counter 225 then switches to the starting number 7, so as to assert the local disabling signal D<sub>7</sub>; in response thereto, the first 8 latches SR<sub>0</sub>-SR<sub>7</sub> are reset. As a consequence, all the program loads of the subsets ST<sub>0</sub>-ST<sub>7</sub> are disabled. In this way, the load of the charge pump is reduced allowing the enabling of further subsets of program loads ST; (if necessary). Likewise, the global disabling signal DIŚ is asserted again after the same delay from the assertion of every next local enabling signal E<sub>i</sub>. The counter 225 is then incremented in succession, so as to assert the corresponding local disabling signal D<sub>i</sub> (thereby resetting the latch SR<sub>i</sub> and disabling the subset of program loads

[0037] As soon as the last subset of program loads

$\mathrm{ST}_{31}$  has been enabled (signal  $\mathrm{E}_{31}$  asserted), the signal STOP is asserted; in response thereto, the loop controller 205 is disabled. After the delay defined by the shift register 220, the same subset of program loads  $\mathrm{ST}_{31}$  is disabled (signal  $\mathrm{D}_{31}$  asserted). As a consequence, the signal END is asserted as well (for signaling the completion of the program step to the control logic of the flash).

**[0038]** However, the concepts of the present invention are also applicable when the program loads are grouped into a different number of subsets, when the residual capacity of the charge pump is determined in another way, or when equivalent means is provided for controlling the program loads. Similar considerations apply if a different number of subsets are simultaneously enabled at the beginning of the program step, if the shift register provides a different delay or it is replaced with equivalent means, and the like.

**[0039]** A further embodiment of the present invention is illustrated in Figure 3a (the elements corresponding to the ones shown in Figure 2 are denoted with the same references and their explanation is omitted for the sake of simplicity); in this case, the selector only takes into consideration the program loads associated with memory cells actually to be programmed.

**[0040]** For this purpose, the selector 145 includes a matrix of logic blocks 305; each logic block (denoted with  $B_i$ ) is associated with a program load  $PL_i$ . The logic block  $B_i$  has an enabling input terminal EI, a disabling input terminal DI and a program flag input terminal PI; the logic block  $B_i$  also has an enabling output terminal EO, a disabling output terminal DO and a control output terminal CO.

[0041] Each program flag PF; (stored in the associated register 140) is supplied to the input terminal PI of the block B<sub>i</sub>; the signal provided by the output terminal CO directly controls the associated program load PLi. All the blocks B<sub>0</sub>-B<sub>7</sub> of the first subset ST<sub>0</sub> receive the global enabling signal EN and the global disabling signal DIS at their input terminals EI and at their input terminals DI, respectively. The input terminal EI and the input terminal DI of each one of the other blocks Bi are connected to the output terminal EO and to the output terminal DO, respectively, of the corresponding block of the previous subset ST<sub>i</sub> (for example, the block B<sub>0</sub> is cascade connected to the block B<sub>8</sub>, which in turn is connected to the block B<sub>16</sub>, and so on until the block B<sub>248</sub>); in this way, the blocks Bi result logically arranged into 8 parallel channels. The signals provided by the output terminals EO of all the blocks  $B_{248}$ - $B_{255}$  of the last subset  $ST_{31}$  are applied to respective input terminals of an AND gate 310; the AND gate 310 outputs the signal STOP, which is returned to the loop controller 205. The signals provided by the output terminals DO of the same blocks  ${\rm B_{248}\text{-}B_{255}}$  are likewise applied to respective input terminals of a further AND gate 315; the AND gate 315 outputs the signal END (for the control logic of the flash).

**[0042]** The structure of a generic block  $B_i$  is illustrated in Figure 3b. The block  $B_i$  consists of two legs for enabling

40

45

25

30

35

40

45

50

and for disabling, respectively, the associated program load.

9

[0043] Particularly, the signal at the input terminal El and the signal at the input terminal PI are AND-ed by a logic gate 320e. An OR gate 325e receives (at respective input terminals) the signal provided by the AND gate 320e and the signal provided by a main output terminal (Q) of a D latch 330e. The output terminal of the OR gate 325e is connected to a set terminal (D) of the latch 330e. An enabling terminal (L) of the latch 330e receives a control signal PHa, which is generated applying a predetermined phase displacement to the clock signal CLK. The signal provided by the main output terminal of the latch 330e is also applied to the set terminal of a further D latch 335e; the enabling terminal of the latch 330e receives a different control signal PHb, which is generated applying a further phase displacement to the control signal PHa; the control signals PHa and PHb are disoverlapped, so that they are never asserted at the same time. The signal at the main output terminal of the latch 335e and the signal at the input terminal EI are AND-ed by a logic gate 340e; a further AND gate 350e is supplied with the same signal at the input terminal EI and with a signal PI, which is output by an inverter 345 connected to the input terminal PI. The signal provided by the AND gate 340e and the signal provided by the AND gate 350e are applied to respective input terminals of an OR gate 355e; the output terminal of the OR gate 355e is directly connected to the output terminal EO.

[0044] The disabling leg of the block  $B_i$  processes the signal at the input terminal DI in a similar manner. The elements of the disabling leg are denoted with the same references of the corresponding elements in the enabling leg, simply replacing the suffix "d" for the suffix "e". The structure of the disabling leg is exactly the same as the one of the enabling leg, so that its explanation is omitted for the sake of simplicity.

[0045] The signal at the main output terminal of the latch 330e and the signal at an inverted output terminal (Q) of the latch 330d are supplied to an AND gate 360. The output terminal of the AND gate 360 is directly connected to the output terminal CO.

[0046] In a rest condition, all the latches 330e, 335e, 330d and 335d are reset (in response to the completion of a previous program step); therefore, the signals at the output terminals EO, DO and CO are deasserted. Let us assume now that the signal at the input terminal EI is asserted at a generic clock signal.

**[0047]** If the corresponding memory cell is to be programmed, the signal at the input terminal PI is asserted and the inverted signal  $\underline{PI}$  is deasserted. In this case, the signal at the output terminal EO remains deasserted (irrespective of the signal at the input terminal EI). The signal at the set terminal of the latch 330e is instead asserted. After a delay defined by the phase displacement of the control signal PHa, the latch 330e is then set. This results in the assertion of the signal at the output terminal CO. After a further delay defined by the phase displace-

ment of the control signal PHb, the latch 335e is set as well. From now on, the signal at the set terminal of the latch 330e is always asserted (irrespective of the signal at the input terminal EI); as a consequence, the latch 330e remains set. The signal at the output terminal EO is instead asserted or deasserted according to the signal at the input terminal EI.

[0048] Conversely, if the corresponding memory cell is not to be programmed the signal at the input terminal PI is deasserted and the inverted signal PI is asserted. The latches 330e and 335e then remain reset (irrespective of the signal at the input terminal EI); as a consequence, the signal at the output terminal CO is always deasserted. In this case, however, the signal at the output terminal EO is asserted or deasserted (at every clock signal) according to the signal at the input terminal EI.

**[0049]** In a similar manner, let us assume that the signal at the input terminal DI is asserted at a generic clock signal.

[0050] If the corresponding memory cell has been programmed, the signal at the input terminal PI is asserted and the inverted signal PI is deasserted. In this case, the signal at the output terminal DO remains deasserted (irrespective of the signal at the input terminal DI). The signal at the set terminal of the latch 330d is instead asserted. After a delay defined by the phase displacement of the control signal PHa, the latch 330d is then set. This results in the deassertion of the signal at the output terminal CO. After a further delay defined by the phase displacement of the control signal PHb, the latch 335d is set as well. From now on, the signal at the set terminal of the latch 330d is always asserted (irrespective of the signal at the input terminal DI); as a consequence, the latch 330d remains set. The signal at the output terminal DO is instead asserted or deasserted according to the signal at the input terminal DI.

[0051] Conversely, if the corresponding memory cell has not been programmed the signal at the input terminal PI is deasserted and the inverted signal PI is asserted. The latches 330d and 335d then remain reset (irrespective of the signal at the input terminal DI); as a consequence, the signal at the output terminal CO is not affected by the signal at the input terminal DI. In this case, however, the signal at the output terminal DO is asserted or deasserted (at every clock signal) according to the signal at the input terminal DI.

**[0052]** In other words, the signal applied to the input terminal EI and the signal applied to the input terminal DI of the block  $B_i$  are managed as tokens (which are either used when necessary or passed to the next block otherwise).

**[0053]** Referring back to Figure 3a, at the beginning of a program step the signals at the output terminals CO of all the blocks  $B_i$  are deasserted. As soon as the control logic enables the loop controller 205, the global enabling signal EN is asserted. The global enabling signal EN is supplied to the input terminals EI of the first blocks  $B_0$ - $B_7$  in all the channels. For each channel, if the first block is

20

25

30

40

associated with a memory cell to be programmed (signal at the input terminal PI asserted) the signal at the output terminal CO is asserted (so as to enable the corresponding program load), while the signal at the output terminal EO remains deasserted. On the contrary (signal at the input terminal PI deasserted), the signal at the output terminal EO is asserted (so as to pass the global enabling signal EN to the next corresponding block), while the signal at the output terminal CO remains deasserted. The same operations described above are executed until a block associated with a memory cell to be programmed is reached.

[0054] At the next clock signal, the A/D converter 150 detects the current voltage of the charge pump again. If the loop controller 205 determines that the residual capacity of the charge pump allows the supplying of a further subset of program loads ST<sub>j</sub>, the global enabling signal EN is asserted. For each channel, the global enabling signal EN goes through all the blocks that are associated with either a memory cell not to be programmed or a program load already enabled (until a block associated with a memory cell still to be programmed is reached); when the global enabling signal EN crosses the whole channel, the signal at the corresponding input terminal of the AND gate 310 is asserted.

**[0055]** Conversely, if the limit defined by the capacity of the charge pump has been reached the global enabling signal EN is deasserted; as a consequence, no further subset of program loads ST<sub>i</sub> is enabled.

**[0056]** The same operations described above are continually repeated at every clock signal.

[0057] In the meanwhile, the global enabling signal EN goes through the shift register 220. The global disabling signal DIS is then asserted after the corresponding delay from the (first) assertion of the global enabling signal EN. The global disabling signal DIS is supplied to the input terminals DI of the first blocks B<sub>0</sub>-B<sub>7</sub> in all the channels. For each channel, if the first block is associated with a program load that has been enabled (signal at the input terminal PI asserted) the signal at the output terminal CO is deasserted (so as to disable the corresponding program load), while the signal at the output terminal DO remains deasserted. On the contrary, the signal at the output terminal DO is asserted (so as to pass the global disabling signal DIS to the next corresponding block), while the signal at the output terminal CO remains deasserted. The same operations described above are executed until a block associated with an enabled program load is reached.

**[0058]** Likewise, the global disabling signal DIS is asserted again after the same delay from the next assertion of the global enabling signal EN. For each channel, the global disabling signal DIS goes through all the blocks that are associated with either a memory cell not to be programmed or a program load already disabled (until a block associated with a program load still enabled is reached); when the global disabling signal crosses the whole channel, the signal at the corresponding input ter-

minal of the AND gate 315 is asserted.

[0059] As soon as all the program loads PL<sub>i</sub> associated with the memory cells to be programmed have been enabled, the global enabling signal EN crosses all the channels; therefore, the signal STOP is asserted. In response thereto, the loop controller 205 is disabled. After the delay defined by the shift register 220 also the global disabling signal DIS will cross all the channels. As a consequence, the signal END is asserted as well.

**[0060]** However, the concepts of the present invention are also applicable when the logic blocks are arranged in another way, when the logic blocks have a different structure, or when the latches are replaced with equivalent means. Similar considerations apply if the control signals for the latches are generated in another way, if different components are used for signaling the completion of the program step, and the like.

[0061] More generally, the present invention proposes a circuit for programming a non-volatile memory device (having a plurality of memory cells). The circuit includes multiple driving elements, each one used to apply a program pulse to a selected memory cell to be programmed; the driving elements are suitable to be supplied by a power supply unit. Control means is provided for controlling the driving elements. In the circuit of the invention, the control means includes means for determining a residual capacity of the power supply unit; selecting means is used for selectively enabling the driving elements according to the residual capacity.

**[0062]** The solution of the invention strongly reduces the time required for programming the selected memory cells.

**[0063]** The proposed architecture self-adapts to the actual capacity of the power supply unit. In other words, the devised structure makes it possible to exploit the capacity of the power supply unit that is available but unused in the memory devices known in the art.

**[0064]** Therefore, more memory cells may be programmed concurrently at any time, never exceeding the capacity of the power supply unit. This solution strongly improves the speed of the program step without requiring either the capacity of the power supply unit to be increased or the current absorbed by the memory cells to be reduced.

45 [0065] The preferred embodiment of the invention described above offers further advantages.

**[0066]** Particularly, the program loads are enabled in succession during a program step; each program load is disabled after a delay corresponding to the program pulse. The program step is completed as soon as all the program loads have been disabled.

**[0067]** In this way, operation of the program loads is out of phase; therefore, as soon as one or more program loads are disabled, the load of the charge pump is reduced allowing the enabling of other program loads.

**[0068]** Advantageously, the program loads are grouped into subsets that are enabled individually.

[0069] This structure is very simple, but at the same

15

20

25

30

35

40

time effective.

**[0070]** However, the solution according to the present invention leads itself to be implemented managing the completion of the program step in another way, enabling as many program loads as possible only at the beginning of the program step (for example, according to the residual capacity of the charge pump detected periodically), or even enabling the program loads individually.

**[0071]** In a particular embodiment of the invention, the subsets of program loads are enabled in succession.

**[0072]** This structure is very simple, even if it is not optimal (since it does not enable the maximum number of program loads actually supported by the capacity of the charge pump).

**[0073]** A way to improve the structure is to enable a predetermined number of subsets at the beginning of the program step.

**[0074]** The proposed feature makes it possible to save the time required for reaching the maximum capacity of the charge pump.

**[0075]** Advantageously, each subset of program loads is disabled after a predetermined delay.

**[0076]** This feature ensures the correct operation of the circuit in a very simple manner.

**[0077]** Alternatively, the subsets of program loads are enabled with different algorithms, only a single subset is enabled at every time, or the program loads are disabled in another way.

**[0078]** In a different embodiment of the invention, the program loads to be enabled are selected only among the ones associated with the memory cells actually to be programmed.

**[0079]** In this way, the capacity of the charge pump is used at its best.

**[0080]** As a further enhancement, this result is achieved by means of a matrix of logic blocks arranged in multiple channels; each channel exploits the global enabling signal as a token.

[0081] The proposed implementation is simple and modular.

**[0082]** Advantageously, the same structure is also used for disabling the program loads.

**[0083]** In this way, the correct operation of the circuit is achieved with a very compact structure.

**[0084]** However, the solution of the present invention is also suitable to be implemented selecting the program loads to be enabled only according to the residual capacity of the charge pump, exploiting a different structure for managing the program loads, or even disabling the program loads in another way.

**[0085]** Naturally, in order to satisfy local and specific requirements, a person skilled in the art may apply to the solution described above many modifications and alterations all of which, however, are included within the scope of protection of the invention as defined by the following claims.

#### Claims

- 1. A circuit (115, 145, 150) for programming a non-volatile memory device (100) having a plurality of memory cells (105) and a timing unit (160) to provide a clock signal (CLK) which is used to synchronize all circuits of the non-volatile memory device (100), the circuit including a plurality of driving elements (115), each of the plurality of driving elements (115) for applying a program pulse to a selected memory cell to be programmed, the driving elements being suitable to be supplied by a power supply unit (120,125), and control means (145,150) for controlling the driving elements, characterized in that

- the control means includes means (150,205) for determining a residual capacity of the power supply unit, and selecting means (145) for selectively enabling ones of the plurality of driving elements at each cycle of the clock signal (CLK) according to the residual capacity of the power supply unit for supplying the programming of the plurality of memory cells, the control means to monitor an actual load placed on a charge pump (120) within the power supply unit (120, 125) to determine the residual capacity, the selecting means (145) being configured to enable at least one driving element in succession during a program step of the selected memory cells, the selecting means further including means (220-230) for disabling each driving element (115) after a predetermined delay from the enabling of the driving element, the delay corresponding to the length of the program pulse, the control means further including means (230) for signaling a completion of the program step when all the driving elements have been disabled.

- 2. The circuit (115, 145, 150) according to claim 1, wherein the driving elements (115) are grouped into a plurality of subsets each one consisting of a predetermined number of driving elements, the selecting means (145) including means (205) for providing an enabling signal when the power supply unit (120,125) is in a condition to supply the driving elements of a further subset.

- 45 3. The circuit (115,143,150) according to claim 2, wherein the selecting means (145) further includes means (210,215,235) responsive to the enabling signal for individally enabling the subsets in succession.

- 4. the circuit (115,145,150) according to claim 2, wherein the selecting means (145) further includes means (210,215,235) responsive to a first enabling signal at the beginning of the program step for enabling a predetermined plurality of subsets, and means (210,215,235) responsive to each next enabling signal for individually enabling the remaining subsets in succession.

15

25

35

40

45

50

55

- 5. The circuit (115,145,160) according to claim 3 or 4, wherein the selecting means (145) further includes means (220) for providing a disabling signal after the predetermined delay from the provision of the enabling signal, means (225,230,235) responsive to the disabling signal for disabling the subset enabled by the corresponding enabling signal, and means (230) for providing a signal indicative of the completion of the program step in response to the disabling signal corresponding to a last one oi the subsets.

- 6. The circuit (115,145,150) according to claim 2, wherein the selecting means (145) further includes means (305) responsive to the enabling signal for enabling at most the predetermined number of driving elements (115) selected only among the driving elements associated with memory cells (105) to be programmed

- 7. The circuit (115,145,150) according to claim 6, wherein the selecting means (145) includes a logic block (305) for each driving element (115), the logic blocks being grouped into a plurality of further subsets corresponding to the subsets of the driving elements, each logic block including means (330e,335e) for storing an indication of whether the corresponding driving element has been enabled, means (360) for enabling the corresponding driving element in response to the enabling signal when the corresponding memory cell (105) is to be programmed and the corresponding driving element has not been enabled, and means (340e-355e) for transmitting the enabling signal to a corresponding logic block of a next further subset otherwise.

- 8. The circuit (115,145,150) according to claim 7, wherein the selecting means (145) further includes means (220) for providing a disabling signal after the predetermined delay from the provision of the enabling signal, each logic block (305) further including means (330d,335d) for storing an indication of whether the corresponding driving element has been disabled, means (360) for disabling the corresponding driving element in response to the disabling signal when the corresponding memory cell is to be programmed and the corresponding driving element has not been disabled, and means (340d-355d) for transmitting the disabling signal to the corresponding logic block of the next further subset otherwise, and wherein the selecting means further includes means (315) for providing a signal indicative of the completion of the program step in response to the disabling signal transmitted by all the logic blocks of a last further subset.

- 9. A non-volatile memory device (100) including a plurality of memory cells (105) and the circuit (115,145,150) according to any claim from 1 to 8 for

programming the memory cells.

10. A method of programming a non-volatile memory device (100) including a plurality of memory cells (105) and a plurality of driving elements each one for applying a program pulse to a selected memory cell to be programmed, the non-volatile memory device further including a timing unit (160) to provide a clock signal (CLK) which is used to synchronize all circuits of the non-volatile memory device (100), the method including the steps of:

supplying the plurality of driving elements by a power supply unit, and being characterise by:

determining a residual capacity of the power supply unit by monitoring an actual load placed on a charge pump (120) within the power supply unit (124, 125) to determine the residual capacity;

selectively enabling ones of the plurality of the driving elements at each cycle of the clock signal (CLK) according to the residual capacity of the power supply unit for supplying the programming of selected ones of the plurality of memory cells;

enabling at least one driving element in succession during a program step of the selected memory cells;

disabling each driving element (115) after a predetermined delay from the enabling of the driving element, the delay corresponding to the length of the program pulse; and signaling a completion of the program step when all the driving elements have been disabled.

### Patentansprüche

Schaltung (115, 145, 150) zum Programmieren eines nichtflüchtigen Speichergeräts (100) mit mehreren Speicherzellen (105) und einer Zeitsteuereinheit (160) zum Erzeugen eines Taktsignals (CLK), das zum Synchronisieren aller Schaltungen des nichtflüchtigen Speichergeräts (100) verwendet wird, wobei die Schaltung mehrere Ansteuerungselemente (115) aufweist, wobei jedes der mehreren Ansteuerungselemente (115) zum Anlegen eines Programmpulses an eine gewählte zu programmierende Speicherzelle dient, wobei die Ansteuerungselemente zum Zuführen von einer Stromversorgungseinheit (120, 125) geeignet sind, und Steuermittel (145, 150) zum Steuern der Ansteuerungselemente,

### dadurch gekennzeichnet, dass

das Steuermittel Mittel (150, 205) zum Ermitteln einer Restkapazität der Stromversorgungseinheit und Auswahlmittel (145) zum selektiven Freigeben von

35

40

45

einigen der mehreren Ansteuerungselemente bei jedem Zyklus des Taktsignals (CLK) gemäß der Restkapazität der Stromversorgungseinheit zum Zuführen der Programmierung der mehreren Speicherzellen beinhaltet, wobei das Steuermittel zum Überwachen einer tatsächlichen Last auf einer Ladungspumpe (120) innerhalb der Stromversorgungseinheit (120, 125) dient, um die Restkapazität zu ermitteln, wobei das Auswahlmittel (145) zum Freigeben wenigstens eines Ansteuerungselements in Folge während eines Programmschritts der gewählten Speicherzellen dient, wobei das Auswahlmittel ferner Mittel (220-230) zum Sperren jedes Ansteuerungselements (115) nach einer vorbestimmten Verzögerung nach dem Freigeben des Ansteuerungselements beinhaltet, wobei die Verzögerung der Länge des Programmpulses entspricht, wobei das Steuermittel ferner Mittel (230) zum Signalisieren des Abschlusses des Programmschritts beinhaltet, wenn alle Ansteuerungselemente gesperrt sind.

- 2. Schaltung (115, 145, 150) nach Anspruch 1, wobei die Ansteuerungselemente (115) zu mehreren Teilsätzen gruppiert sind, die jeweils aus einer vorbestimmten Anzahl von Ansteuerungselementen bestehen, wobei das Auswahlmittel (145) Mittel (205) zum Bereitstellen eines Freigabesignals beinhaltet, wenn die Stromversorgungseinheit (120, 125) in einem Zustand zum Versorgen der Ansteuerungselemente eines weiteren Teilsatzes ist.

- Schaltung (115, 145, 150) nach Anspruch 2, wobei das Auswahlmittel (145) ferner Mittel (210, 215, 235) beinhaltet, die auf das Freigabesignal mit dem individuellen Freigeben der Teilsätze in Folge ansprechen.

- 4. Schaltung (115, 145, 150) nach Anspruch 2, wobei das Auswahlmittel (145) ferner Mittel (210, 215, 235), die auf ein erstes Freigabesignal zu Beginn des Programmschritts mit dem Freigeben einer vorbestimmten Mehrzahl von Teilsätzen ansprechen, und Mittel (210, 215, 235) beinhaltet, die auf jedes nächste Freigabesignal mit dem individuellen Freigeben der verbleibenden Teilsätze in Folge ansprechen.

- 5. Schaltung (115, 145, 150) nach Anspruch 3 oder 4, wobei das Auswahlmittel (145) ferner Mittel (220) zum Bereitstellen eines Sperrsignals nach der vorbestimmten Verzögerung nach dem Bereitstellung des Freigabesignals, Mittel (225,230,235), die auf das Sperrsignal mit dem Sperren des von dem entsprechenden Freigabesignal freigegebenen Teilsatzes ansprechen, und Mittel (230) zum Bereitstellen eines Signals beinhaltet, das den Abschluss des Programmschritts als Reaktion auf das Sperrsignal entsprechend einem letzten der Teilsätze anzeigt.

- 6. Schaltung (115, 145, 150) nach Anspruch 2, wobei das Auswahlmittel (145) ferner Mittel (305) beinhaltet, die auf das Freigabesignal zum Freigeben von höchstens der vorbestimmten Anzahl von Ansteuerungselementen (115) ansprechen, die nur aus den mit zu programmierenden Speicherzellen (105) assoziierten Ansteuerungselementen ausgewählt sind.

- Schaltung (115, 145, 150) nach Anspruch 6, wobei das Auswahlmittel (145) einen Logikblock (305) für jedes Ansteuerungselement (115) beinhaltet, wobei die Logikblöcke zu mehreren weiteren Teilsätzen entsprechend den Teilsätzen der Ansteuerungsele-15 mente gruppiert sind, wobei jeder Logikblock Mittel (330e, 335e) zum Speichern einer Anzeige, ob das entsprechende Ansteuerungselement freigegeben wurde, Mittel (360) zum Freigeben des entsprechenden Ansteuerungselements als Reaktion auf das 20 Freigabesignal, wenn die entsprechende Speicherzelle (105) programmiert werden soll und das entsprechende Ansteuerungselement nicht freigegeben wurde, und Mittel (340e-355e) beinhaltet, um ansonsten das Freigabesignal zu einem entspre-25 chenden Logikblock eines nächsten weiteren Teilsatzes zu übertragen.

- Schaltung (115, 145, 150) nach Anspruch 7, wobei das Auswahlmittel (145) ferner Mittel (220) zum Bereitstellen eines Sperrsignals nach der vorbestimmten Verzögerung nach dem Bereitstellen des Freigabesignals beinhaltet, wobei jeder Logikblock (305) ferner Mittel (330d, 335d) zum Speichern einer Anzeige, ob das entsprechende Ansteuerungselement gesperrt wurde, Mittel (360) zum Sperren des entsprechenden Ansteuerungselements als Reaktion auf das Sperrsignal, wenn die entsprechende Speicherzelle programmiert werden soll und das entsprechende Ansteuerungselement nicht gesperrt wurde, und Mittel (340d-355d) beinhaltet, um ansonsten das Sperrsignal zu dem entsprechenden Logikblock des nächsten weiteren Teilsatzes zu übertragen, und wobei das Auswahlmittel ferner Mittel (315) zum Bereitstellen eines Signals beinhaltet, das den Abschluss des Programmschritts als Reaktion darauf anzeigt, dass das Sperrsignal von allen Logikblöcken eines letzten weiteren Teilsatzes übertragen wurde.

- 50 9. Nichtflüchtiges Speichergerät (100) mit mehreren Speicherzellen (105) und Schaltung (115, 145, 150) nach einem der Ansprüche 1 bis 8 zum Programmieren der Speicherzellen.

- 55 10. Verfahren zum Programmieren eines nichtflüchtigen Speichergeräts (100) mit mehreren Speicherzellen (105) und mehreren Ansteuerungselementen, jedes zum Anlegen eines Programmpulses an eine zu pro-

15

20

25

30

35

40

45

50

55

grammierende gewählte Speicherzelle, wobei das nichtflüchtige Speichergerät ferner eine Zeitsteuereinheit (160) zum Bereitstellen eines Taktsignals (CLK) aufweist, das zum Synchronisieren aller Schaltungen des nichtflüchtigen Speichergeräts (100) benutzt wird, wobei das Verfahren die folgenden Schritte beinhaltet:

Zuführen der mehreren Ansteuerungselemente durch eine Stromversorgungseinheit, und **gekennzeichnet durch**:

Ermitteln einer Restkapazität der Stromversorgungseinheit **durch** Überwachen einer tatsächlichen Last auf einer Ladungspumpe (120) in der Stromversorgungseinheit (120, 125), um die Restkapazität zu ermitteln;

selektives Freigeben von einigen der mehreren Ansteuerungselemente bei jedem Zyklus des Taktsignals (CLK) gemäß der Restkapazität der Stromversorgungseinheit zum Zuführen der Programmierung von ausgewählten der mehreren Speicherzellen;

Freigeben von wenigstens einem Ansteuerungselement in Folge während eines Programmschritts der gewählten Speicherzellen;

Sperren jedes Ansteuerungselements (115) nach einer vorbestimmten Verzögerung nach dem Freigeben des Ansteuerungselements, wobei die Verzögerung der Länge des Programmpulses entspricht; und

Signalisieren des Abschlusses des Programmschritts, wenn alle Ansteuerungselemente gesperrt sind.

#### Revendications

Un circuit (115, 145, 150) destiné à la programmation d'un dispositif à mémoire non volatile (100) possédant une pluralité de cellules à mémoire (105) et une unité de synchronisation (160) destinée à fournir un signal d'horloge (CLK) qui est utilisé de façon à synchroniser tous les circuits du dispositif à mémoire non volatile (100), le circuit comprenant une pluralité d'éléments d'excitation (115), chacun des éléments de la pluralité d'éléments d'excitation (115) étant destiné à l'application d'une impulsion de programme à une cellule à mémoire sélectionnée à programmer, les éléments d'excitation étant adaptés de façon à être fournis par une unité d'alimentation électrique (120, 125), et un moyen de commande (145, 150) destiné à la commande des éléments d'excitation, caractérisé en ce que

le moyen de commande comprend un moyen (150, 205) de détermination d'une capacité résiduelle de l'unité d'alimentation électrique et un moyen de sélection (145) destiné à l'activation de manière sélective d'éléments de la pluralité d'éléments d'excitation à chaque cycle du signal d'horloge (CLK) selon la capacité résiduelle de l'unité d'alimentation électrique de façon à fournir la programmation de la pluralité de cellules à mémoire, le moyen de commande étant destiné à surveiller une charge réelle placée sur une pompe à charge (120) à l'intérieur de l'unité d'alimentation électrique (120,125) de façon à déterminer la capacité résiduelle, le moyen de sélection (145) étant configuré de façon à activer au moins un élément d'excitation en succession au cours d'une opération de programme des cellules à mémoire sélectionnées, le moyen de sélection comprenant en outre un moyen (220-230) de désactivation de chaque élément d'excitation (115) après un délai prédéterminé à partir de l'activation de l'élément d'excitation, le délai correspondant à la longueur de l'impulsion de programme, le moyen de commande comprenant en outre un moyen (230) de signalement d'un achèvement de l'opération de programme lorsque tous les éléments d'excitation ont été désactivés.

- 2. Le circuit (115, 145, 150) selon la Revendication 1, où les éléments d'excitation (115) sont groupés en une pluralité de sous-ensembles, chacun d'eux se composant d'un nombre prédéterminé d'éléments d'excitation, le moyen de sélection (145) comprenant un moyen (205) de fourniture d'un signal d'activation lorsque l'unité d'alimentation électrique (120, 125) est en état de fournir les éléments d'excitation d'un autre sous-ensemble.

- 3. Le circuit (115, 145, 150) selon la Revendication 2, où le moyen de sélection (145) comprend en outre un moyen (210, 215, 235) réactif au signal d'activation destiné à activer individuellement les sous-ensembles en succession.

- 4. Le circuit (115, 145, 150) selon la Revendication 2, où le moyen de sélection (145) comprend en outre un moyen (210, 215, 235) réactif à un premier signal d'activation au début de l'opération de programme destiné à l'activation d'une pluralité prédéterminée de sous-ensembles, et un moyen (210, 215, 235) réactif à chaque signal d'activation suivant destiné à activer individuellement les sous-ensembles restants en succession.

- 5. Le circuit (115, 145, 150) selon la Revendication 3 ou 4, où le moyen de sélection (145) comprend en outre un moyen (220) de fourniture d'un signal de désactivation après le délai prédéterminé à partir de la fourniture du signal d'activation, un moyen (225,

15

20

25

40

45

230, 235) réactif au signal de désactivation destiné à la désactivation du sous-ensemble activé par le signal d'activation correspondant, et un moyen (230) de fourniture d'un signal indicatif de l'achèvement de l'opération de programme en réponse au signal de désactivation correspondant à un dernier des sous-ensembles.

- 6. Le circuit (115, 145, 150) selon la Revendication 2, où le moyen de sélection (145) comprend en outre un moyen (305) réactif au signal d'activation de façon à activer au plus le nombre prédéterminé d'éléments d'excitation (115) sélectionnés uniquement parmi les éléments d'excitation associés à des cellules à mémoire (105) à programmer.

- 7. Le circuit (115, 45, 150) selon la Revendication 6, où le moyen de sélection (145) comprend un bloc logique (305) pour chaque élément d'excitation (115), les blocs logiques étant groupés en une pluralité d'autres sous-ensembles correspondant aux sous-ensembles des éléments d'excitation, chaque bloc logique comprenant un moyen (330e, 335e) de conservation en mémoire d'une indication si l'élément d'excitation correspondant a été activé, un moyen (360) d'activation de l'élément d'excitation correspondant en réponse au signal d'activation lorsque la cellule à mémoire correspondante (105) est à programmer et l'élément d'excitation correspondant n'a pas été activé, et un moyen (340e-355e) de transmission du signal d'activation à un bloc logique correspondant d'un autre sous-ensemble suivant dans le cas contraire.

- 8. Le circuit (115,145,150) selon la Revendication 7, où le moyen de sélection (145) comprend en outre un moyen (220) de fourniture d'un signal de désactivation après le délai prédéterminé à partir de la fourniture du signal d'activation, chaque bloc logique (305) comprenant en outre un moyen (330d, 335d) de conservation en mémoire d'une indication si l'élément d'excitation correspondant a été désactivé, un moyen (360) de désactivation de l'élément d'excitation correspondant en réponse au signal de désactivation lorsque la cellule à mémoire correspondante est à programmer et l'élément d'excitation correspondant n'a pas été désactivé, et un moyen (340d, 355d) de transmission du signal de désactivation au bloc logique correspondant de l'autre sous-ensemble suivant dans le cas contraire, et où le moyen de sélection comprend en outre un moyen (315) de fourniture d'un signal indicatif de l'achèvement de l'opération de programme en réponse au signal de désactivation transmis par tous les blocs logiques d'un dernier autre sous-ensemble.

- 9. Un dispositif à mémoire non volatile (100) comprenant une pluralité de cellules à mémoire (105) et le

circuit (115, 145, 150) selon l'une quelconque des Revendications 1 à 8, destiné à la programmation des cellules à mémoire.

10. Un procédé de programmation d'un dispositif à mémoire non volatile (100) comprenant une pluralité de cellules à mémoire (105) et une pluralité d'éléments d'excitation, chacun d'eux étant destiné à l'application d'une impulsion de programme à une cellule à mémoire sélectionnée à programmer, le dispositif à mémoire non volatile comprenant en outre une unité de synchronisation (160) destinée à fournir un signal d'horloge (CLK) qui est utilisé de façon à synchroniser tous les circuits du dispositif à mémoire non volatile (100), le procédé comprenant les opérations suivantes :

la fourniture de la pluralité d'éléments d'excitation par une unité d'alimentation électrique, et étant **caractérisé par** :

la détermination d'une capacité résiduelle de l'unité d'alimentation électrique par la surveillance d'une charge réelle placée sur une pompe à charge (120) à l'intérieur de l'unité d'alimentation électrique (120, 125) de façon à déterminer la capacité résiduelle.

l'activation sélective de certains éléments de la pluralité d'éléments d'excitation à chaque cycle du signal d'horloge (CLK) selon la capacité résiduelle de l'unité d'alimentation électrique de façon à fournir la programmation des cellules sélectionnées de la pluralité de cellules à mémoire,

l'activation d'au moins un élément d'excitation en succession au cours d'une opération de programme des cellules à mémoire sélectionnées.

la désactivation de chaque élément d'excitation (115) après un délai prédéterminé à partir de l'activation de l'élément d'excitation, le délai correspondant à la longueur de l'impulsion de programme, et

le signalement d'un achèvement de l'opération de programme lorsque tous les éléments d'excitation ont été désactivés.

55

# EP 1 420 415 B1

## REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Patent documents cited in the description

• US 5930168 A [0007]