# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0123011 A1

## May 3, 2018 (43) **Pub. Date:**

# (54) EUTECTIC ELECTRODE STRUCTURE OF FLIP-CHIP LED CHIP AND FLIP-CHIP LED

(71) Applicant: XIAMEN SANAN **OPTOELECTRONICS**

TECHNOLOGY CO., LTD., Xiamen

(72) Inventors: Anhe HE, Xiamen (CN); Suhui LIN,

Xiamen (CN); Jiansen ZHENG, Xiamen (CN); Kangwei PENG, Xiamen (CN); Xiaoxiong LIN, Xiamen

(CN); Chenke HSU, Xiamen (CN)

(73) Assignee: XIAMEN SANAN **OPTOELECTRONICS** TECHNOLOGY CO., LTD., Xiamen

(21) Appl. No.: 15/853,845

(22) Filed: Dec. 24, 2017

#### Related U.S. Application Data

(63) Continuation of application No. PCT/CN2016/ 097758, filed on Sep. 1, 2016.

#### (30)Foreign Application Priority Data

Oct. 13, 2015 (CN) ...... 201510655970.X

#### **Publication Classification**

(51) Int. Cl. H01L 33/62 (2006.01)H01L 25/075 (2006.01)H01L 25/00 (2006.01)H01L 33/40 (2006.01)

(52) U.S. Cl.

CPC ........... H01L 33/62 (2013.01); H01L 25/0753 (2013.01); H01L 2924/12041 (2013.01); H01L 33/40 (2013.01); H01L 2225/06513 (2013.01); H01L 25/50 (2013.01)

#### (57)ABSTRACT

A Flip-chip LED chip includes: a substrate; a first semiconductor layer; a second semiconductor layer; a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer; a first metal layer over part of the first semiconductor layer; a second metal layer over part of the second semiconductor layer; an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, with opening structures over the first metal layer and the second metal layer respectively; an eutectic electrode structure over the insulating layer, including a first eutectic layer and a second eutectic layer at vertical direction, and a first-type electrode region and a second-type electrode region at horizontal direction. Poor packaging caused by high eutectic void content during eutectic bonding process can therefore be reduced.

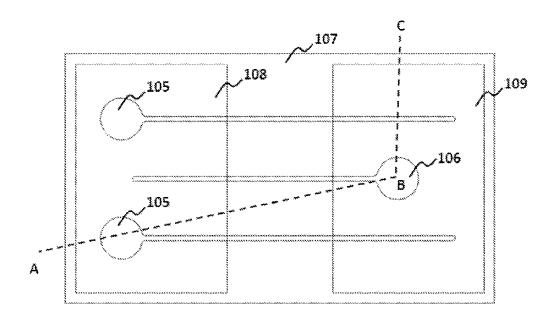

FIG. 1 (PRIOR ART)

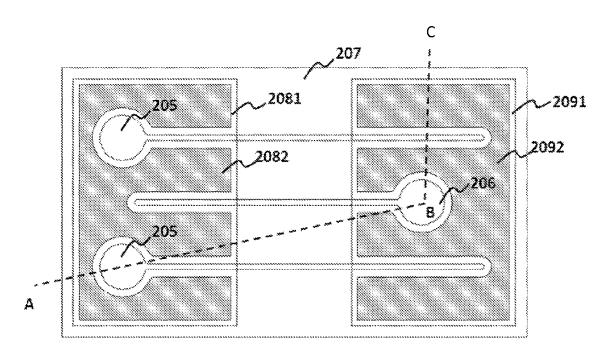

FIG. 2 (PRIOR ART)

FIG. 3 (PRIOR ART)

FIG. 4

FIG. 5

FIG. 7

FIG. 8

#### EUTECTIC ELECTRODE STRUCTURE OF FLIP-CHIP LED CHIP AND FLIP-CHIP LED CHIP

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a continuation of, and claims priority to, PCT/CN2016/097758 filed on Sep. 1, 2016, which claims priority to Chinese Patent Application No. 201510655970.X filed on Oct. 13, 2015. The disclosures of these applications are hereby incorporated by reference in their entirety.

#### BACKGROUND

[0002] Flip-chip LED chips (FCs for short) have been applied in mass production due to proven excellent heat dissipation characteristics and good light extraction efficiency. However, the flip-chip LED chip is different from existing light emitting diode in packaging process. Therefore, chip design, packaging process and material matching have become one of the important topics in the flip-chip packaging technology. The packaging of flip-chip LED chip is mainly divided into two types: The first type is Au-stub bumping process. In this process, an Au-stub bumping is firstly planted over the package substrate, wherein, the relative position of the Au-stub bumping on the substrate is same as that of the chip electrode. Later, through ultrasound pressing, the chip electrode is electrically connected to the Au-stub bumping over the package substrate; this method has the advantages of low requirements for the package substrate and flexible process.

#### **SUMMARY**

[0003] The inventors of the present disclosure have recognized that the ultrasound pressing involves expensive equipment, poor production efficiency due to large consumption and high cost of Au-stub bumping and high precision of chip alignment, resulting in high cost of the entire production; the second type is eutectic bonding process, wherein, the selected eutectic metal is fabricated over the chip through evaporating or sputtering; the chip is pre-fit over the package substrate through low-temperature scaling powder, and reflowed at melting point higher than that of the eutectic metal layer so that the chip is connected to the package substrate. With low metal cost and fast production, this method has low precision requirement of machine. But it has high requirements for flatness of the eutectic metal layer over the flip-chip LED chip surface. If height difference appears over the metal layer surface, the eutectic void ratio is high, which causes poor eutectic quality and influences the package yield.

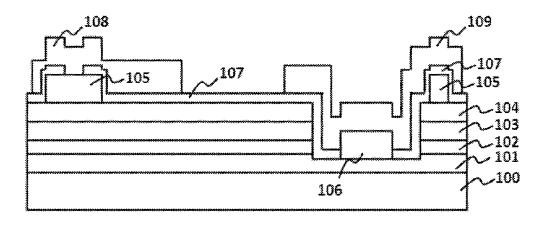

[0004] FIGS. 1 and 2 show an existing LED flip-chip structure, which is fabricated by epitaxial growth of a first semiconductor layer, a light emitting layer and a second semiconductor layer over an epitaxial substrate; depositing a transparent conducting layer; etching and exposing part of the first semiconductor layer; evaporating a metal layer (including the spreading finger); depositing an insulating layer and evaporating an AuSn eutectic electrode. However, when this structure is applied in eutectic package, as shown in FIG. 3, a bumping structure appears over the AuSn eutectic electrode surface due to the bumping metal layer (including the metal spreading finger). For example, the

upper surface of the AuSn eutectic electrode of the second metal layer (including the metal spreading finger) is highest, which is available for eutectic bonding with the package substrate; however, the AuSn eutectic electrodes in other regions are low, and is difficult for eutectic bonding with the package substrate; therefore, the flatness of the eutectic electrode upper surface cannot be guaranteed, which may cause high eutectic void ratio and poor eutectic quality.

[0005] Various embodiments of the present disclosure provide an eutectic electrode structure of flip-chip LED chip and a flip-chip LED chip, which solves low package yield due to high eutectic void ratio during eutectic bonding process of the existing flip-chip LED chip structure without changing the package substrate.

[0006] According to a first aspect of the present disclosure, an eutectic electrode structure of flip-chip LED chip is provided, wherein, the eutectic electrode structure is composed of a first eutectic layer and a second eutectic layer from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction, wherein, the upper surface and lower surface of the first eutectic layer are not flat, and the upper surface of the second eutectic layer is flat.

[0007] In some embodiments, the lower surface of the first eutectic layer contacts with the flip-chip LED chip for current conduction.

[0008] In some embodiments, the upper surface of the second eutectic layer is higher than or is of equal height with the upper surface of the first eutectic layer to form a flat eutectic plane.

[0009] According to a second aspect of the present disclosure, a flip-chip LED chip is provided, which includes: a substrate; a first semiconductor layer over the substrate; a light emitting layer over the first semiconductor layer; a second semiconductor layer over the light emitting layer; a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer; a first metal layer over part of the first semiconductor layer; a second metal layer over part of the second semiconductor layer; an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, wherein, the insulating layer has opening structures over the first metal layer and the second metal layer respectively; an eutectic electrode structure over the insulating layer with openings, wherein, the eutectic electrode structure is composed of a first eutectic layer and a second eutectic layer from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction; wherein, a upper surface and a lower surface of the first eutectic layer are not flat, and a upper surface of the second eutectic layer is flat.

[0010] In some embodiments, the lower surface of the first eutectic layer contacts with the first metal layer and the second metal layer respectively for current conduction.

[0011] In some embodiments, the second eutectic layer is not overlapped with the first metal layer and the second metal layer at vertical direction.

[0012] In some embodiments, the upper surface of the second eutectic layer is higher than or is of equal height with the upper surface of the first eutectic layer to form a flat eutectic plane.

[0013] In some embodiments, the second eutectic layer in the first-type electrode region is of same height with the second eutectic layer in the second-type electrode region.

[0014] In some embodiments, the first metal layer and the second metal layer are composed of metal bodies and metal spreading fingers, or the first metal layer and the second metal layer are metal bodies.

[0015] In some embodiments, the opening structure of the insulating layer is only over the metal body.

[0016] In some embodiments, the first-type electrode region and the second-type electrode region are of equivalent area and in symmetrical positions.

[0017] In some embodiments, a transparent conducting layer is formed over the second semiconductor layer, and the material can be ITO, ZnO, CTO, InO, In-doped ZnO, Al-doped ZnO or Ga-doped ZnO or any of their combinations

[0018] In some embodiments, the metal layer material is Cr, Ti, Pt, Au, Ag, Ni, Cu, TiW or any of their combinations. [0019] In some embodiments, the insulating layer material is SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiN<sub>X</sub>, TiO<sub>2</sub> or any of their combinations.

[0020] In some embodiments, the eutectic electrode structure material is Ti, Ni, Cu, Au, AuSn, SnCu, SnBi or any of their combinations.

[0021] In another aspect of the present disclosure, a lightemitting diode including a flip-chip LED chip is provided, in which the flip-chip LED chip further includes a substrate; a first semiconductor layer over the substrate; a light emitting layer over the first semiconductor layer; a second semiconductor layer over the light emitting layer; a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer; a first metal layer over part of the first semiconductor layer; a second metal layer over part of the second semiconductor layer; an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, wherein, the insulating layer has opening structures over the first metal layer and the second metal layer respectively; an eutectic electrode structure over the insulating layer with openings, wherein, the eutectic electrode structure is composed of a first eutectic layer and a second eutectic layer from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction; wherein, a upper surface and a lower surface of the first eutectic layer are not flat, and a upper surface of the second eutectic layer is flat.

[0022] In another aspect of the present disclosure, a lightemitting system including a plurality of light-emitting diodes (LEDs) is provided, in which each LED includes a flip-chip LED chip. The flip-chip LED chip further includes: a substrate; a first semiconductor layer over the substrate; a light emitting layer over the first semiconductor layer; a second semiconductor layer over the light emitting layer; a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer; a first metal layer over part of the first semiconductor layer; a second metal layer over part of the second semiconductor layer; an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, wherein, the insulating layer has opening structures over the first metal layer and the second metal layer respectively; an eutectic electrode structure over the insulating layer with openings, wherein, the eutectic electrode structure is composed of a first eutectic layer and a second eutectic layer from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction; wherein, a upper surface and a lower surface of the first eutectic layer are not flat, and a upper surface of the second eutectic layer is flat. The light-emitting system can be used in the fields of lighting, display, signage, etc.

[0023] Through a dual-layer eutectic electrode structure, the electrode structure design of the flip-chip LED chip of the present disclosure solves the problem of low package yield due to high eutectic void ratio during eutectic bonding process of existing chip structures, without changing the package substrate.

[0024] The other features and advantages of the present disclosure will be described in detail in the following specification, and it is believed that such features and advantages will become more obvious in the specification or through implementations of the present disclosure. The purposes and other advantages of the present disclosure can be realized and obtained in the structures specifically described in the specifications, claims and drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0025] The accompanying drawings, which are included to provide a further understanding of the present disclosure and constitute a part of this specification, together with the embodiments, are therefore to be considered in all respects as illustrative and not restrictive. In addition, the drawings are merely illustrative, which are not drawn to scale.

[0026] FIG. 1 illustrates a top view of an existing flip-chip LED chip structure.

[0027] FIG. 2 illustrates a sectional view along A-B-C direction in FIG. 1.

[0028] FIG. 3 illustrates a sectional view of an eutectic package of an existing flip-chip LED chip structure.

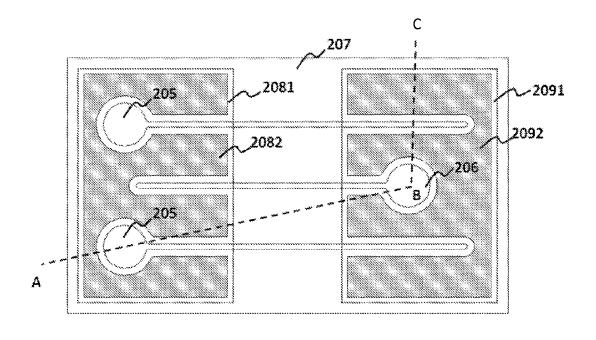

[0029] FIG. 4 illustrates a top view of a flip-chip LED chip structure according to Embodiment 1.

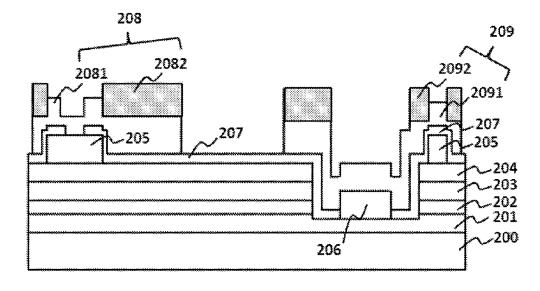

[0030] FIG. 5 illustrates a sectional view of the flip-chip LED chip in FIG. 4 along A-B-C direction.

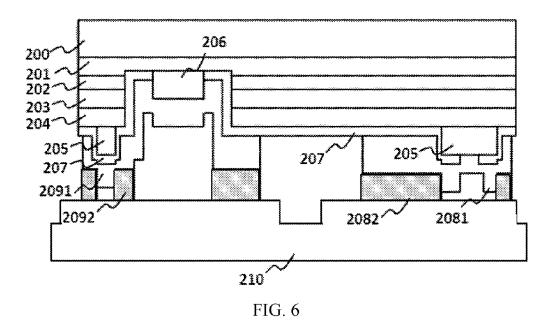

[0031] FIG. 6 illustrates a sectional view of eutectic package of a flip-chip LED chip structure according to Embodiment 1.

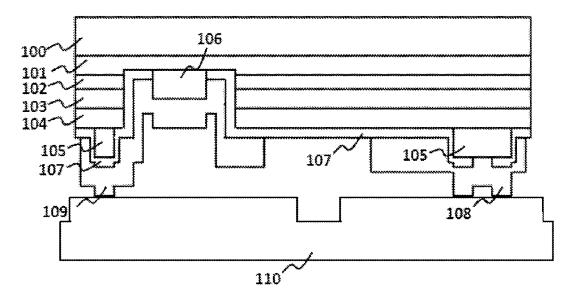

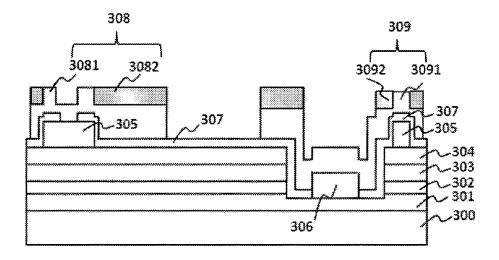

[0032] FIG. 7 illustrates a top view of a flip-chip LED chip structure according to Embodiment 2.

[0033] FIG. 8 illustrates a sectional view of eutectic package of a flip-chip LED chip structure according to Embodiment 2.

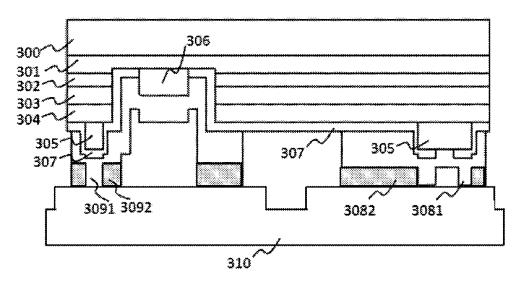

[0034] In the drawings: 100, 200, 300: substrate; 101, 201, 301: first semiconductor layer; 102, 202, 302: light emitting layer; 103, 203, 303: second semiconductor layer; 104, 204, 304: transparent conducting layer; 105, 205, 305: second metal layer; 106, 206, 306: first metal layer; 107, 207, 307: insulating layer; 108, 208, 308: second-type electrode region; 109, 209, 309: first-type electrode region; 110, 210, 310: package substrate; 2081, 2091, 3081, 3091: first eutectic layer; 2082, 2092, 3082, 3092: second eutectic layer.

## DETAILED DESCRIPTION

[0035] Detailed steps and compositions will be described below for a better understanding of the present disclosure. In addition, it should be noted that well-known compositions or

steps are not included to avoid unnecessary limitation to the present disclosure. Preferred embodiments of the present disclosure will be described in detail below. However, in addition to these details, the present disclosure can be widely applied to other embodiments. The scope of the present disclosure is not limited and is as defined by the appended claims.

[0036] To solve the problem of existing flip-chip LED chip during eutectic bonding process, the present disclosure provides a dual-layer eutectic electrode design applicable to the flip-chip LED chip, which solves the problem of low package yield due to high eutectic void ratio during eutectic bonding process of existing chip structures, without changing the package substrate. Various embodiments of the eutectic electrode structure and the flip-chip LED chip of the present disclosure will be described in detail with reference to the accompanying drawings.

#### Embodiment 1

[0037] With reference to FIGS. 4 and 5, a flip-chip LED chip of this embodiment, comprises: a substrate 200; a first semiconductor layer 201 over the substrate 200; a light emitting layer 202 over the first semiconductor layer 201; a second semiconductor layer 203 over the light emitting layer 202; a local defect region over part of the second semiconductor layer 203, which extends downward to the first semiconductor layer 201; a transparent conducting layer 204 over part of the second semiconductor layer 203; a first metal layer 206 over part of the first semiconductor layer 201; a second metal layer 205 over the transparent conducting layer 204; an insulating layer 207 over the first metal layer 206, the second metal layer 205, the transparent conducting layer 204 and the first semiconductor layer 201 in the local defect region, wherein, the insulating layer has opening structures over the first metal layer 206 and the second metal layer 205 respectively; an eutectic electrode structure over the insulating layer 207 with openings, wherein, the eutectic electrode structure is composed of a first eutectic layer 2081 and 2091 and a second eutectic layer 2082 and 2092 from bottom to up at vertical direction, and is divided into a first-type electrode region 209 and a second-type electrode region 208 at horizontal direction; wherein, the first-type electrode region 209 and the secondtype electrode region 208 are of equivalent area and in symmetrical positions.

[0038] In some embodiments, the substrate 200 can be a sapphire, SiC, silicon, GaN, AlN, ZnO or other substrates suitable for epitaxial growth; in this embodiment, sapphire is preferred; the first semiconductor layer 201, the second semiconductor layer 202 and the light emitting layer 203 are GaN-based materials or other materials; the transparent conducting layer 204 can be ITO, ZnO, CTO, InO, In-doped ZnO, Al-doped ZnO or Ga-doped ZnO or any of their combinations; in this embodiment, ITO is preferred.

[0039] In some embodiments, the first metal layer and the second metal layer are composed of metal bodies and metal spreading fingers, or the first metal layer and the second metal layer are metal bodies; to improve current spreading uniformity, in this embodiment, the first metal layer 206 and the second metal layer 205 prefer to be composed of circular metal bodies and strip metal spreading fingers, and the metal layer material is Cr, Ti, Pt, Au, Ag, Ni, Cu, TiW or any of their combinations or other materials.

[0040] In some embodiments, the opening structure of the insulating layer 207 can be over the circular metal bodies and the strip metal spreading fingers, or only over the circular metal bodies. In this embodiment, preferably, the insulating layer 207 is over the strip metal spreading finger, and the opening structure of the insulating layer is only over the circular metal body; In some embodiments, the insulating layer material is SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, SiN<sub>x</sub>, TiO<sub>2</sub> or any of their combinations; in this embodiment, a distributed Bragg reflective layer alternatively stacked by low-refractivity SiO<sub>2</sub> and high-refractivity TiO<sub>2</sub> is preferred to facilitate light reflection from the light emitting layer and increase light emitting.

[0041] The first eutectic layer 2081 is formed over the insulating layer 207 with openings, such that the lower surface of the first eutectic layer 2081 contacts with the second metal layer 205 for current conduction; the first eutectic layer 2091 is formed over the insulating layer 207 with openings such that the lower surface of the first eutectic layer 2091 contacts with the first metal layer 206 for current conduction. As the first eutectic layer 2081 and 2091 has bumping metal layers 205 and 206 at bottom, the upper and lower surfaces of the first eutectic layer 2081 and 2091 are not flat, appearing in concave-convex shape.

[0042] The second eutectic layer 2082 and 2092 are formed over the first eutectic layers 2081 and 2091 respectively, and are not overlapped with the first metal layer 205 and the second metal layer 206 at vertical direction, i.e., the second eutectic layers avoid metal electrode bodies and metal spreading fingers; the second eutectic layer is over the flat bottom region of the concave-convex upper surface of the first eutectic layer to obtain a second eutectic layer with flat upper surface; the second eutectic layer 2092 in the first-type electrode region 209 is of same height with the second eutectic layer 2082 in the second-type electrode region 208, thus forming a complete eutectic plane.

[0043] With reference to FIG. 6, when the flip-chip LED chip of this embodiment is used for eutectic package, the upper surface of the second eutectic layer is higher than the upper surface of the first eutectic layer, and the upper surface of the second eutectic layer are flat with same height, thus forming a complete eutectic plane, which effectively reduces void ratio during eutectic bonding of the package substrate 210. In addition, the second eutectic layer 2082 and 2092 are much larger than the first metal layer 205 and the second metal layer 206 to increase effective eutectic area and to make eutectic bonding stronger, so as to improve package yield of the flip-chip LED chip and increase current stability and uniformity.

### Embodiment 2

[0044] With reference to FIGS. 7 and 8, the difference from Embodiment 1 is that: the upper surface of the second eutectic layer 3082 and 3092 are of same height with the upper surface of the first eutectic layer 3081 and 3091, which further enlarges the flat upper surface of the eutectic electrode structure to make eutectic bonding stronger, and to improve package yield and current spreading uniformity.

[0045] According to the embodiments of the present disclosure, when the dual-layer eutectic electrode according to the present disclosure is applied, i.e., the first eutectic layer

is used for current conduction with the semiconductor

bottom layer, and the second eutectic layer avoids the

bumping region of the metal layer (which may include the

metal spreading finger). This solves the problem of eutectic failure due to high void ratio from electrode height difference (flatness difference) during eutectic process of existing eutectic electrode designs, so as to improve the package yield of flip-chip LED chips and current spreading uniformity.

[0046] Although specific embodiments have been described above in detail, the description is merely for purposes of illustration. It should be appreciated, therefore, that many aspects described above are not intended as required or essential elements unless explicitly stated otherwise. Various modifications of, and equivalent acts corresponding to, the disclosed aspects of the exemplary embodiments, in addition to those described above, can be made by a person of ordinary skill in the art, having the benefit of the present disclosure, without departing from the spirit and scope of the disclosure defined in the following claims, the scope of which is to be accorded the broadest interpretation so as to encompass such modifications and equivalent structures.

- 1. An eutectic electrode structure of a flip-chip LED chip, comprising a first eutectic layer and a second eutectic layer from bottom to up in a vertical direction, and having a first-type electrode region and a second-type electrode region in a horizontal direction, wherein a upper surface and a lower surface of the first eutectic layer are not flat, and a upper surface and a lower surface of the second eutectic layer are flat.

- 2. The eutectic electrode structure of flip-chip LED chip of claim 1, wherein the lower surface of the first eutectic layer contact with the flip-chip LED chip for current conduction.

- 3. The eutectic electrode structure of flip-chip LED chip of claim 1, wherein the upper surface of the second eutectic layer is higher than or is of equal height with the upper surface of the first eutectic layer to form a flat eutectic plane.

- 4. A flip-chip LED chip, comprising:

- a substrate;

- a first semiconductor layer over the substrate;

- a light emitting layer over the first semiconductor layer;

- a second semiconductor layer over the light emitting layer;

- a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer;

- a first metal layer over part of the first semiconductor layer:

- a second metal layer over part of the second semiconductor layer;

- an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, wherein, the insulating layer has opening structures over the first metal layer and the second metal layer respectively;

- an eutectic electrode structure over the insulating layer with openings, wherein the eutectic electrode structure comprises a first eutectic layer and a second eutectic layer from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction;

- wherein an upper surface and a lower surface of the first eutectic layer are not flat, and an upper surface and a lower surface of the second eutectic layer are flat.

- **5**. The flip-chip LED chip of claim **4**, wherein, the lower surface of the first eutectic layer contacts with the first metal layer and the second metal layer respectively for current conduction.

- **6**. The flip-chip LED chip of claim **4**, wherein, the second eutectic layer do not overlap with the first metal layer and the second metal layer at vertical direction.

- 7. The flip-chip LED chip of claim 4, wherein, the upper surface of the second eutectic layer is higher than or is of equal height with the upper surface of the first eutectic layer to form a flat eutectic plane.

- **8**. The flip-chip LED chip of claim **4**, wherein, the second eutectic layer in the first-type electrode region is of same height with the second eutectic layer in the second-type electrode region.

- 9. The flip-chip LED chip of claim 4, wherein, the first metal layer and the second metal layer are composed of metal bodies and metal spreading fingers, or the first metal layer and the second metal layer are metal bodies.

- 10. The flip-chip LED chip of claim 9, wherein: the opening structure of the insulating layer is only over the metal body.

- 11. The flip-chip LED chip of claim 4, wherein: a transparent conducting layer is formed over the second semiconductor layer.

- 12. A light-emitting system comprising a plurality of flip-chip LED chips each including:

- a substrate;

- a first semiconductor layer over the substrate;

- a light emitting layer over the first semiconductor layer;

- a second semiconductor layer over the light emitting layer;

- a local defect region over part of the second semiconductor layer, which extends downward to the first semiconductor layer;

- a first metal layer over part of the first semiconductor

- a second metal layer over part of the second semiconductor layer;

- an insulating layer covering the first metal layer, the second metal layer, the second semiconductor layer and the first semiconductor layer in the local defect region, wherein, the insulating layer has opening structures over the first metal layer and the second metal layer respectively;

- an eutectic electrode structure over the insulating layer with openings, wherein, the eutectic electrode structure is composed of first eutectic layers and second eutectic layers from bottom to up at vertical direction, and is divided into a first-type electrode region and a second-type electrode region at horizontal direction;

- wherein upper surfaces and lower surfaces of the first eutectic layers are not flat, and upper surfaces and lower surfaces of the second eutectic layers are flat.

- 13. The light-emitting system of claim 12, wherein the lower surfaces of the first eutectic layers contact with the first metal layer and the second metal layer respectively for current conduction.

- 14. The light-emitting system of claim 12, wherein the second eutectic layers do not overlap with the first metal layer and the second metal layer at vertical direction.

- 15. The light-emitting system of claim 12, wherein the upper surface of the second eutectic layer is higher than or

is of equal height with the upper surface of the first eutectic layer to form a flat eutectic plane.

- 16. The light-emitting system of claim 12, wherein the second eutectic layer in the first-type electrode region is of same height with the second eutectic layer in the second-type electrode region.

- 17. The light-emitting system of claim 12, wherein the first metal layer and the second metal layer are composed of metal bodies and metal spreading fingers, or the first metal layer and the second metal layer are metal bodies.

- 18. The light-emitting system of claim 17, wherein the opening structure of the insulating layer is only over the metal body.

- 19. The light-emitting system of claim 12, wherein a transparent conducting layer is formed over the second semiconductor layer.

\* \* \* \* :