#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 30 September 2021 (30.09.2021)

(10) International Publication Number WO 2021/192562 A1

(51) International Patent Classification:

G01R 31/28 (2006.01) G01N 3/32 (2006.01) G01R 31/26 (2020.01) B06B 1/06 (2006.01) G01R 29/22 (2006.01)

(21) International Application Number:

PCT/JP2021/002118

(22) International Filing Date:

15 January 2021 (15.01.2021)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

20165967.9

26 March 2020 (26.03.2020)

20) EP

- (71) Applicant (for all designated States except JP): MITSUBISHI ELECTRIC CORPORATION [JP/JP]; 7-3, Marunouchi 2-chome, Chiyoda-ku, Tokyo, 1008310 (JP).

- (71) Applicant (for JP only): MITSUBISHI ELECTRIC R&D CENTRE EUROPE B.V. [NL/NL]; Capronilaan 46, NS Schiphol Rijk, 1119 (NL).

- (72) Inventors: DEGRENNE, Nicolas; c/o Mitsubishi Electric R&D Centre Europe, 1 allée de Beaulieu CS 10806, 35708 Rennes Cedex 7 (FR). OUHAB, Merouane; c/o Mitsubishi Electric R&D Centre Europe, 1 allée de Beaulieu CS 10806, 35708 Rennes Cedex 7 (FR). MOLLOV, Stefan; c/o Mitsubishi Electric R&D Centre Europe, 1 allée de Beaulieu CS 10806, 35708 Rennes Cedex 7 (FR).

- (74) Agent: SOGA, Michiharu et al.; S. Soga & Co., 2nd Floor, Keihanshin Onarimon Building, 16-12, Shimbashi 6-chome, Minato-ku, Tokyo 1050004 (JP).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, IT, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

(54) Title: SYSTEM AND METHOD FOR ACCELERATING AGEING OF INTERCONNECTIONS USED FOR INTERCONNECTING POWER SEMICONDUCTORS

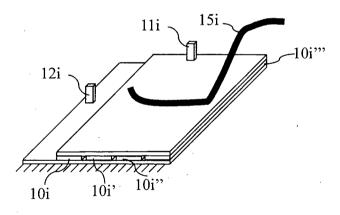

Fig. 5

(57) **Abstract:** The present invention concerns a system for accelerating the ageing of interconnections used for interconnecting power semiconductors. The system comprises: a piezoelectric material, at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material, means for applying an electric field between the top and the bottom of the piezoelectric material using a first electrode disposed on the top of the piezoelectric material and a second electrode disposed on the bottom of the piezoelectric material, means for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[DESCRIPTION]

[Tile of Invention]

SYSTEM AND METHOD FOR ACCELERATING AGEING OF INTERCONNECTIONS USED FOR INTERCONNECTING POWER SEMICONDUCTORS

[Technical Field]

[0001]

The present invention relates generally to a system for accelerating the ageing of interconnections used for interconnecting power semiconductors.

[Background Art]

[0002]

Understanding the effect of mechanical stress on the strength and the lifetime of interconnections in power semiconductor devices is necessary to face the high requirements in terms of reliability level. Mechanical testing plays an important role in the design stage of power semiconductors and even after the manufacturing of the power semiconductor. Mechanical testing of interconnections enables to measure and improve reliability and robustness of the interconnection, reduce qualification tests, optimize designs for specific performances and develop physics-based lifetime models.

[0003]

Wire bond lift-off and die solder cracking are pointed out as the most recurrent degradation processes under field conditions due to thermomechanical fatigue.

[0004]

The dissipated losses during operation flow through the multi-layers of the power semiconductor assembly and are extracted by means of the heatsink.

[0005]

This causes temperature gradients inside the multi-layered structure. The mismatch in the Coefficient of Thermal Expansion (CTE) of the stacked layers generates high shear stresses at interfaces, which induce voids formation and cracks propagation in wire bonds and die solder joints. Consequently, the losses increase and the thermal path degrades causing an overheating in the power semiconductor zone leading to more accumulated damage over the time until the device failure. [0006]

Thermal cycling is a testing method, where the temperature of the whole device under test package is isothermally cycled using a climatic room temperature. The applied thermal cycle lasts usually for many minutes. This test emulates the variation of ambient temperature.

[Summary of Invention]

[0007]

The present invention aims to provide a system for accelerating the ageing of interconnections used for interconnecting power semiconductors.

[0008]

To that end, the present invention concerns a system for accelerating the ageing of interconnections used for interconnecting power semiconductors, characterized in that the system comprises:

- a piezoelectric material,

- at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material,

- means for applying an electric field between the top and the bottom of the piezoelectric material using a first electrode disposed on the top of the piezoelectric material and a second electrode disposed on the bottom of the piezoelectric material. Since the electrodes will not be tested for ageing, they must be more reliable compared to the interconnections used for interconnecting power semiconductors. To achieve it:

- means for measuring the behaviour of the least one interconnection used for interconnecting power semiconductors.

[0009]

Thus, the interconnection(s) can be subjected to an ageing process by electromechanical dilatation using a cyclic electric field instead of using power cycling tests that are energy consuming and present high cost.

[0010]

According to a particular feature, the interconnection used for interconnecting power semiconductors is composed of a metallization on which a wire or a foil or a ribbon is bonded.

[0011]

Thus, it is possible to replicate the wire/foil/ribbon-metallization structure found in standard power devices, and therefore to generate similar interface stress profile. Moreover, the metallization allows to apply a uniform electric field within the piezoelectric material.

[0012]

According to a particular feature, it further comprises a third electrode that is connected to the wire or the foil or the ribbon and means for monitoring the resistance between the first and third electrodes.

[0013]

Thus, the third electrode allows an on-line measurement of the interconnection resistance that is correlated to the degradation level of the contact between the

wire/foil/ribbon and the metallization. [0014]

According to a particular feature, the interconnection used for interconnecting power semiconductors is a solder or a sintering joint.

[0015]

Thus, standard solders (Sn-Ag-Cu alloys) or advanced die attaches based on sintering can be tested to measure their reliability, since they are considered as critical regions in standard power devices.

[0016]

According to a particular feature, it further comprises a third electrode that is connected to the solder or the sintering joint and means for monitoring the resistance between the second and third electrodes.

[0017]

Thus, it allows to monitor the degradation of the solder or the sintering joint based on the resistance as an electrical indicator.

[0018]

According to a particular feature, the system comprises two interconnections used for interconnecting power semiconductors. A first interconnection located on the top of the piezoelectric element is composed of a metallization on which a wire or a foil or a ribbon is bonded and a second interconnection located on the bottom of the piezoelectric element is a solder or a sintering joint.

[0019]

Thus, it is possible to conduct an ageing test for both critical interconnections in power devices at the same time, i.e. top and bottom interconnections. Here, it is possible to study under which conditions one of the interconnections is more prone to degradation and failure (or lifetime limited) than the other.

[0020]

According to a particular feature, the system comprises:

- at least two piezoelectric materials having the same properties,

- at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric materials,

- means for applying an electric field between the top and the bottom of each piezoelectric material separately, the electric field being different of the electric field applied between the top and the bottom of at least one other piezoelectric material,

- means for measuring the behaviour of the least one interconnection used for interconnecting power semiconductors.

[0021]

According to a particular feature, no electric field is applied between the first

and second electrodes of one piezoelectric material during a given time and the first and second electrodes are used for measuring the voltage across said piezoelectric material in order to estimate the local effective strain during the given time. [0022]

Thus, it is possible to control fully the strain-stress profile generated over the surface of the piezoelectric material. Therefore, a specific ageing profile can be applied to test the targeted interconnection(s).

[0023]

According to a particular feature, the system comprises:

- at least two piezoelectric materials having different properties,

- at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric materials,

- means for applying an electric field between the top and the bottom of each piezoelectric material using one electrode disposed on the top of the piezoelectric materials and the electrode disposed on the bottom of the piezoelectric materials,

- means for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[0024]

According to a particular feature, the system is further mounted on a ceramic base plate.

[0025]

Thus, it would be possible to reproduce the same multi-layered stack that can be found in standard power devices and modules. In addition, the ceramic offers an electrical isolation and a mechanical stability.

[0026]

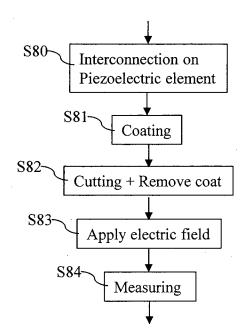

The present invention concerns also a method for accelerating the ageing of interconnections used for interconnecting power semiconductors, characterized in that the method comprises the steps of:

- disposing one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of a piezoelectric material,

- applying an electric field between the top and the bottom of the piezoelectric material using a first electrode disposed on the top of the piezoelectric material and a second electrode disposed on the bottom of the piezoelectric material,

- measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[0027]

Thus, the interconnection(s) can be subjected to an ageing process by electromechanical dilatation using a cyclic electric field instead of using power

cycling tests that are energy consuming and present high cost. [0028]

According to a particular feature, the method further comprises the steps of:

- coating, prior applying the electrical field, in a resin the interconnection used for interconnecting power semiconductors located on the top and/or the bottom of a piezoelectric material and the piezoelectric material,

- cutting, prior applying the electrical field, on a vertical axis the interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material and the piezoelectric material,

- removing the resin prior applying the electrical field, and the measuring of the behaviour of the at least one interconnection used for interconnecting power semiconductors is performed using a Digital Image Correlation method, Scanning Acoustic Microscopy or crystallography. [0029]

Thus, this technique allows a close monitoring of crack propagation in the interconnections from one side based on a cross-section that preserves its electrical functionality. Crack conditions might be monitored using for example a Digital Image Correlation (DIC) method, Scanning Acoustic Microscopy (SAM) or crystallography to analyse the microstructure change with the ageing process.

[Brief Description of Drawings] [0030]

The characteristics of the invention will emerge more clearly from a reading of the following description of example embodiments, the said description being produced with reference to the accompanying drawings.

[0031]

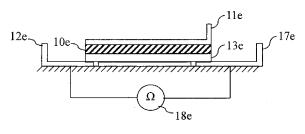

[Fig. 1]

Figure 1 represents a first example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

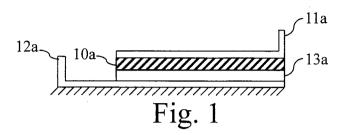

[Fig. 2]

Figure 2 represents a second example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

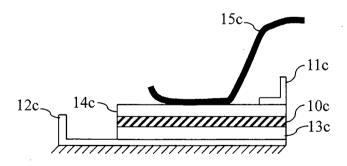

[Fig.3]

Figure 3 represents a third example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

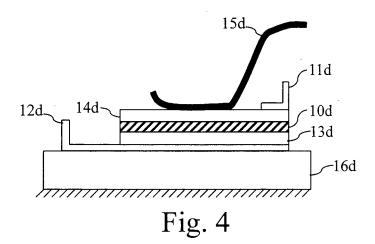

[Fig. 4]

Figure 4 represents a fourth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[Fig. 5]

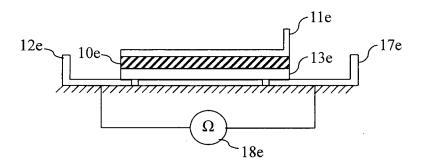

Figure 5 represents a fifth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[Fig. 6]

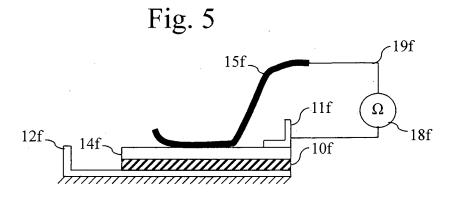

Figure 6 represents a sixth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[Fig. 7]

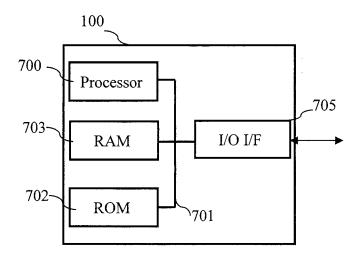

Figure 7 represents a device that is able to execute the method disclosed in reference of Fig. 8.

[Fig. 8]

Figure 8 represents an example of an algorithm for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

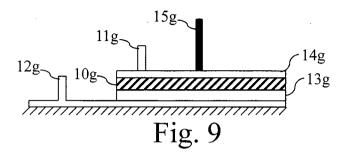

[Fig. 9]

Figure 9 represent an example of views of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors provided by the algorithm of Fig. 8.

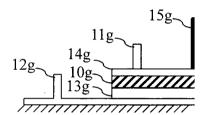

[Fig. 10]

Figure 10 represent an example of views of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors provided by the algorithm of Fig. 8.

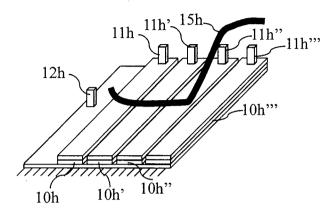

[Fig. 11]

Figure 11 represents a seventh example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[Fig. 12]

Figure 12 represents an eighth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[Description of Embodiments]

[0032]

Fig. 1 represents a first example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0033]

The system comprises a piezoelectric material 10a, an interconnection 13a used for interconnecting power semiconductors located on the bottom of the piezoelectric material 10a. The interconnection 13a used for interconnecting power semiconductors is a solder or a sintered joint.

[0034]

In one example of implementation, the interconnection 13a is a conductive joint including at least a Sn-Ag-Cu (SAC) alloy with a thickness comprised between 10  $\mu$ m and 500  $\mu$ m.

[0035]

The system comprises a first electrode 11a disposed on the top of the piezoelectric material 10a and a second electrode 12a disposed on the bottom of the piezoelectric material 10a that are used for applying an electric field between the top and the bottom of the piezoelectric material 10a.

[0036]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material.

[0037]

The electric field is for example a square, triangular sinusoidal or a sawtooth waveform.

[0038]

The electric field may be also a time dependent profile which reproduces complex mechanical loading.

[0039]

Fig. 2 represents a second example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0040]

The system comprises a piezoelectric material 10b, an interconnection used for interconnecting power semiconductors located on the top of the piezoelectric material 10b. The interconnection used for interconnecting power semiconductors is composed of a metallization 14b on which a wire or a foil or a ribbon 15b is bonded.

[0041]

The interconnection is for example composed of a cylindrical aluminium wire with a diameter comprised between 50  $\mu m$  and 800  $\mu m$ . The wire is bonded onto the metallization that is made of aluminium with a thickness less than 10  $\mu m$ . [0042]

The system comprises a first electrode 11b disposed on the top of the metallization 14b and a second electrode 12b disposed on the bottom of the piezoelectric material 10b that are used for applying an electric field between the top and the bottom of the piezoelectric material 10b.

[0043]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may be also be spring-loaded in order to provide a reliable contact with the piezoelectric material. [0044]

The electric field is for example a square, triangular, sinusoidal or a sawtooth waveform.

[0045]

The electric field may be also a time dependent profile which reproduces complex mechanical loading.

[0046]

Fig. 3 represents a third example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0047]

The system comprises a piezoelectric material 10c and two interconnections 13c and 15b used for interconnecting power semiconductors.

[0048]

The interconnection 13c is used for interconnecting power semiconductors located on the bottom of the piezoelectric material 10c. The interconnection 13c used for interconnecting power semiconductors is a solder or a sintering joint.

[0049]

The interconnection 13c is a conductive joint including at least a Sn-Ag-Cu (SAC) alloy with a thickness comprised between 10  $\mu$ m and 500  $\mu$ m. [0050]

The system comprises a first electrode 11c disposed on the top of the piezoelectric material 10c and a second electrode 12c disposed on the bottom of the piezoelectric material 10c that are used for applying an electric field between the top

and the bottom of the piezoelectric material 10c. [0051]

In order to improve the reliability of the first, second and third electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material. [0052]

The electric field is for example a square, triangular, sinusoidal or a sawtooth waveform.

[0053]

The electric field may be also a time dependent profile which reproduces complex mechanical loading.

[0054]

The interconnection used for interconnecting power semiconductors is composed of a metallization 14c on which a wire or a foil or a ribbon 15c is bonded and is disposed on the top of the piezoelectric material 10c.

[0055]

The interconnection 15c is for example composed of a cylindrical aluminium wire with a diameter comprised between 50  $\mu m$  and 800  $\mu m$ . The wire is bonded onto the metallization that is made of aluminium with a thickness less than 10  $\mu m$ . [0056]

Fig. 4 represents a fourth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0057]

The system comprises a piezoelectric material 10d, an interconnection 13d used for interconnecting power semiconductors located on the bottom of the piezoelectric material 10d. The interconnection 13d used for interconnecting power semiconductors is a solder or a sintering joint.

[0058]

The interconnection 13d is a conductive joint including at least a Sn-Ag-Cu (SAC) alloy with a thickness comprised between 10  $\mu$ m and 500  $\mu$ m. [0059]

The system comprises a first electrode 11d disposed on the top of the piezoelectric material 10d and a second electrode 12d disposed on the bottom of the piezoelectric material 10d that are used for applying an electric field between the top and the bottom of the piezoelectric material 10d.

[0060]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material.

[0061]

The electric field is for example a square, triangular, sinusoidal or a sawtooth waveform.

[0062]

The electric field may also be a time dependent profile which reproduces complex mechanical loading.

[0063]

The system further comprises a ceramic base plate (16d) on which the second electrode 12d is mounted. The baseplate is made of Alumina (Al2O3)- or Aluminium Nitride (AlN)-based ceramic with a thickness higher than 700 um. [0064]

The ceramic baseplate is used to provide a mechanical stability for the assembly during the fatigue test, it reproduces more accurately the structure of a power module, and thus, the strain/stress is also more realistically reproduced on the wire and/or the solder/sintered layer.

[0065]

It has to be noted here that the ceramic baseplate may be replaced by a direct bonded copper (DBC) substrate.

[0066]

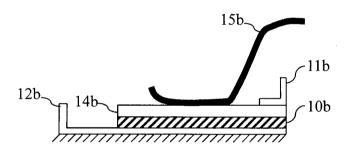

Fig. 5 represents a fifth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[0067]

The system comprises a piezoelectric material 10e, an interconnection 13e used for interconnecting power semiconductors located on the bottom of the piezoelectric material 10e. The interconnection 13e used for interconnecting power semiconductors is a solder or a sintering joint.

[0068]

The interconnection 13e is a conductive joint including at least a Sn-Ag-Cu (SAC) alloy with a thickness comprised between 10  $\mu$ m and 500  $\mu$ m. [0069]

The system comprises a first electrode 11e disposed on the top of the piezoelectric material 10e, a second electrode 12e disposed on the bottom of the

piezoelectric material 10e that are used for applying an electric field between the top and the bottom of the piezoelectric material 10e.

[0070]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material.

[0071]

The electric field is for example a square, triangular, sinusoidal or a sawtooth waveform.

[0072]

The electric field may be also a time dependent profile which reproduces complex mechanical loading.

[0073]

The system further comprises a third electrode 17e that is connected to the solder or the sintering joint and means 18e for monitoring the resistance between the second and third electrodes.

[0074]

Fig. 6 represents a sixth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[0075]

The system comprises a piezoelectric material 10f, an interconnection 13f used for interconnecting power semiconductors located on the top of the piezoelectric material 10f. The interconnection used for interconnecting power semiconductors is composed of a metallization 14f on which a wire or a foil or a ribbon 15f is bonded.

[0076]

The interconnection is for example composed of a cylindrical aluminium wire with a diameter comprised between 50  $\mu m$  and 800  $\mu m$ . The wire is bonded onto the metallization that is made of aluminium with a thickness less than 10  $\mu m$ . [0077]

The system comprises a first electrode 11f disposed on the top of the metallization 14b and a second electrode 12f disposed on the bottom of the piezoelectric material 10f that are used for applying an electric field between the top and the bottom of the piezoelectric material 10f.

[0078]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material. [0079]

The electric field is for example a square, triangular, sinusoidal or a sawtooth waveform.

[0800]

The electric field may be also a time dependent profile which reproduces complex mechanical loading.

[0081]

The system further comprises a third electrode 19f that is connected to the wire or the foil or the ribbon 15f and means 18f for monitoring the resistance between the first and third electrodes.

[0082]

Fig. 7 represents a device that is able to execute the method disclosed in reference of Fig. 8.

[0083]

The device 100 has, for example, an architecture based on components connected together by a bus 701 and a processor 700 controlled by a program.

[0084]

The bus 701 links the processor 700 to a read only memory ROM 702, a random access memory RAM 703, and an input output I/O interface I/F 705. [0085]

The memory 703 contains registers intended to receive variables and the instructions of the program related to the algorithm disclosed in Fig. 8. [0086]

The read-only memory, or possibly a flash memory 702, contains instructions of the program related to the algorithm disclosed in Fig. 8.

[0087]

When the device 100 is powered on, the instructions stored in the memory 702 are transferred to the random access memory 703.

[0088]

In other words, the device 100 includes circuitry enabling the estimation module 107 to perform the program as disclosed in Fig. 8.

[0089]

Fig. 8 represents an example of an algorithm for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the

present invention and for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

[0090]

At step S80, the device 100 commands through the input output I/O interface I/F 705 the disposing of two interconnections used for interconnecting power semiconductors located on the tops 14g and 15g and on the bottom 13g of the piezoelectric material 10g.

[0091]

At step S81, the device 100 commands through the input output I/O interface I/F the coating in a resin of the interconnections 13g and 15g used for interconnecting power semiconductors located on the top and the bottom of a piezoelectric material and the piezoelectric material 10g as shown in Fig. 9.

[0092]

At step S82, the device 100 commands through the input output I/O interface I/F to perform a micro-section of the interconnection used for interconnecting power semiconductors as disclosed in Fig. 10. For that, the device 100 commands through the input output I/O interface I/F to cut on a vertical axis the interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material and the piezoelectric material. At the same step, the device 100 commands through the input output I/O interface I/F the removing of the resin using, for example, dedicated chemicals.

[0093]

At step S83, the device 100 commands through the input output I/O interface I/F the applying, during a predetermined period, of an electric field between the top and the bottom of the piezoelectric material using a first electrode 11g disposed on the top of the piezoelectric material and a second electrode 12g disposed on the bottom of the piezoelectric material 10g.

[0094]

At step S84, the device 100 commands through the input output I/O interface I/F a Digital Image Correlation system and/or a Scanning Acoustic Microscopy system or crystallography analysis system in order to measure the behaviour of the least one interconnection used for interconnecting power semiconductors.

[0095]

Fig. 11 represents a seventh example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0096]

The system comprises plural piezoelectric materials 10h, 10h', 10h'' and

10h'", one interconnection used for interconnecting power semiconductors located on the top of the piezoelectric materials 10h, 10h', 10h' and 10h'". The piezoelectric materials have the same piezoelectric property. The interconnection used for interconnecting power semiconductors is composed of metallization 14h, 14h' and 14h'" on which a wire or a foil or a ribbon 15h is bonded. [0097]

The system comprises for each piezoelectric material a first electrode 11h, 11h', 11h'' and 11h''' disposed on the top of the metallization 14h, 14h', 14h'' and 14h''' and a second electrode 12h disposed on the bottom of the piezoelectric material 10h that are used for applying an electric field between the top and the bottom of the piezoelectric materials 10h, 10h', 10h'' and 10h'''.

[0098]

In order to improve the reliability of the electrodes, each electrode metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The electrodes may also be spring-loaded in order to provide a reliable contact with the piezoelectric material.

[0099]

In the example of Fig. 11, the electric field between the top and the bottom of each piezoelectric material is different of the electric field applied between the top and the bottom of at least one other piezoelectric materials.

[0100]

It has to be noted here that, in a particular mode of realization, no electric field is applied between the first and second electrodes of one piezoelectric material during a given time and the first and second electrodes are used for measuring the voltage across said piezoelectric material in order to estimate the local effective strain during the given time.

[0101]

Fig. 12 represents an eighth example of a system for accelerating the ageing of interconnections used for interconnecting power semiconductors according to the present invention.

[0102]

The system comprises plural piezoelectric materials 10i, 10i', 10i'' and 10i''', one interconnection used for interconnecting power semiconductors located on the top of the piezoelectric materials 10h, 10h', 10h'' and 10h'''. The piezoelectric materials have different piezoelectric properties. The interconnection used for interconnecting power semiconductors is composed of a metallization on which a wire or a foil or a ribbon 15i is bonded.

[0103]

WO 2021/192562 PCT/JP2021/002118

15

The system comprises for the piezoelectric materials a first electrode 11i disposed on the top of the metallization and a second electrode 12i disposed on the bottom of the piezoelectric material 10i that are used for applying an electric field between the top and the bottom of the piezoelectric materials 10i, 10i', 10i' and 10i''.

[0104]

In order to improve the reliability of the first and second electrodes, the electrodes metallization can be designed using a specific material (Nickel, Silver ...etc.), thickness and/or pattern. The first and second electrodes may also be springloaded in order to provide a reliable contact with the piezoelectric material.

[0105]

In the example of Fig. 12, the electric field between the top and the bottom of each piezoelectric material is the same as the electric field applied between the top and the bottom of the other piezoelectric materials.

[0106]

Naturally, many modifications can be made to the embodiments of the invention described above without departing from the scope of the present invention.

# [CLAIMS] [Claim 1]

A system for accelerating the ageing of interconnections used for interconnecting power semiconductors, characterized in that the system comprises:

- a piezoelectric material,

- at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material,

- means for applying an electric field between the top and the bottom of the piezoelectric material using a first electrode disposed on the top of the piezoelectric material and a second electrode disposed on the bottom of the piezoelectric material,

- means for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

## [Claim 2]

The system according to claim 1, characterized in that the interconnection used for interconnecting power semiconductors is composed of a metallization layer on which a wire or a foil or a ribbon is bonded.

# [Claim 3]

The system according to claim 2, characterized in that it further comprises a third electrode that is connected to the wire or the foil or the ribbon and means for monitoring the resistance between the first and third electrodes.

# [Claim 4]

The system according to claim 1, characterized in that the interconnection used for interconnecting power semiconductors is a solder or a sintered joint.

[Claim 5]

The system according to claim 4, characterized in that it further comprises a third electrode that is connected to the solder or the sintered joint and means for monitoring the resistance between the second and third electrodes.

# [Claim 6]

The system according to claim 1, characterized in that the system comprises two interconnections used for interconnecting power semiconductors, a first interconnection located on the top of the piezoelectric element is composed of a metallization on which a wire or a foil or a ribbon is bonded and a second interconnection located on the bottom of the piezoelectric element is a solder or a sintered joint.

# [Claim 7]

The system according to claim 1, characterized in that the system comprises:

- at least two piezoelectric materials having the same properties,

- at least one interconnection used for interconnecting power semiconductors located

on the top and/or the bottom of the piezoelectric materials,

- means for applying an electric field between the top and the bottom of each piezoelectric material, the electric field being different of the electric field applied between the top and the bottom of the at least one other piezoelectric material,

- means for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

### [Claim 8]

The system according to claim 7, characterized in that no electric field is applied between the first and second electrodes of one piezoelectric material during a given time and the first and second electrodes are used for measuring the voltage across said piezoelectric material in order to estimate the local effective strain during the given time.

## [Claim 9]

The system according to claim 1, characterized in that the system comprises:

- at least two piezoelectric materials having different properties,

- at least one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric materials,

- means for applying an electric field between the top and the bottom of each piezoelectric material using one electrode disposed on the top of the piezoelectric materials and one electrode disposed on the bottom of the piezoelectric materials,

- means for measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

## [Claim 10]

The system according to any of the claims 1 to 4, characterized in that the system is further mounted on a ceramic base plate.

# [Claim 11]

A method for accelerating the ageing of interconnections used for interconnecting power semiconductors, characterized in that the method comprises the steps of:

- disposing one interconnection used for interconnecting power semiconductors located on the top and/or the bottom of a piezoelectric material,

- applying an electric field between the top and the bottom of the piezoelectric material using a first electrode disposed on the top of the piezoelectric material and a second electrode disposed on the bottom of the piezoelectric material,

- measuring the behaviour of the at least one interconnection used for interconnecting power semiconductors.

# [Claim 12]

The method according to claim 11, characterized in that the method further

WO 2021/192562 PCT/JP2021/002118

18

comprises the steps of:

- coating, prior applying the electrical field, in a resin the interconnection used for interconnecting power semiconductors located on the top and/or the bottom of a piezoelectric material and the piezoelectric material,

- cutting, prior applying the electrical field, on a vertical axis the interconnection used for interconnecting power semiconductors located on the top and/or the bottom of the piezoelectric material and the piezoelectric material,

- removing the resin prior applying the electrical field, and the measuring a Digital Image Correlation system and/or a Scanning Acoustic Microscopy system or crystallography analysis system.

WO 2021/192562 PCT/JP2021/002118

Fig. 2

Fig. 3

Fig. 6

Fig. 7

Fig. 8

Fig. 10

WO 2021/192562 PCT/JP2021/002118

Fig. 11

Fig. 12

#### INTERNATIONAL SEARCH REPORT

International application No PCT/JP2021/002118

A. CLASSIFICATION OF SUBJECT MATTER INV. G01R31/28 G01R31/26

G01R29/22

G01N3/32

B06B1/06

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G01R G01N B06B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                       | Relevant to claim No. |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| X         | EP 3 226 014 A1 (MITSUBISHI ELECTRIC R&D<br>CT EUROPE BV [NL] ET AL.)<br>4 October 2017 (2017-10-04)<br>paragraphs [0007], [0008], [0034] -<br>[0063]; figures 1,4,2a-2d | 1-12                  |  |

| А         | US 2013/037395 A1 (HORI HISAO [JP] ET AL) 14 February 2013 (2013-02-14) paragraphs [0007], [0016] - [0047], [0066] - [0069]; figures 1-4, 6                              | 1-12                  |  |

| A         | US 2003/047006 A1 (SELIGER NORBERT [DE]) 13 March 2003 (2003-03-13) paragraphs [0015] - [0062]; figures 1-4                                                              | 1-12                  |  |

| X Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family |  |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date of mailing of the international search report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 13 April 2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21/04/2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Name and mailing address of the ISA/  European Patent Office, P.B. 5818 Patentlaan 2  NL - 2280 HV Rijswijk  Tel. (+31-70) 340-2040,  Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                       | Authorized officer  Maric, Viktor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

1

#### **INTERNATIONAL SEARCH REPORT**

International application No

PCT/JP2021/002118

|           | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                             |                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                     | Relevant to claim No. |

| A         | GORECKI CHRISTOPHE ET AL: "Interferometry of AlN-based microcantilevers to determine the material properties and failure mechanisms",  OPTICAL MICRO- AND NANOMETROLOGY IV, SPIE, 1000 20TH ST. BELLINGHAM WA 98225-6705 USA, vol. 8430, no. 1, 3 May 2012 (2012-05-03), pages 1-16, XP060002266, DOI: 10.1117/12.922887 abstract; figure 1 paragraphs [0001] - [0002] | 1-12                  |

| A         | US 2018/188309 A1 (DEGRENNE NICOLAS [FR] ET AL) 5 July 2018 (2018-07-05) paragraphs [0049] - [0079]; figures 1a-1b                                                                                                                                                                                                                                                     | 1-12                  |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                        |                       |

1

#### INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/JP2021/002118

| Patent document cited in search report | Publication<br>date | Patent family<br>member(s)                                                                                  | Publication<br>date                                                              |

|----------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| EP 3226014 <i>F</i>                    | 1 04-10-2017        | CN 108885231 A<br>EP 3226014 A1<br>JP 6552737 B2<br>JP 2018535553 A<br>US 2019331729 A1<br>WO 2017169313 A1 | 23-11-2018<br>04-10-2017<br>31-07-2019<br>29-11-2018<br>31-10-2019<br>05-10-2017 |

| US 2013037395 A                        | 1 14-02-2013        | JP 4796657 B1<br>JP 2012119595 A<br>US 2013037395 A1                                                        | 19-10-2011<br>21-06-2012<br>14-02-2013                                           |

| US 2003047006 A                        | 1 13-03-2003        | AU 4637401 A<br>EP 1268114 A1<br>US 2003047006 A1<br>WO 0174524 A1                                          | 15-10-2001<br>02-01-2003<br>13-03-2003<br>11-10-2001                             |

| US 2018188309 A                        | 1 05-07-2018        | EP 3141893 A1<br>JP 6619450 B2<br>JP 2018515771 A<br>US 2018188309 A1<br>WO 2017043346 A1                   | 15-03-2017<br>11-12-2019<br>14-06-2018<br>05-07-2018<br>16-03-2017               |