(12) United States Patent

# Chapman

#### (54) USING A CHANGE IN DOPING OF POLY GATE TO PERMIT PLACING BOTH HIGH VOLTAGE AND LOW VOLTAGE TRANSISTORS ON THE SAME CHIP

- (75) Inventor: Richard A. Chapman, Dallas, TX (US)

- (73) Assignce: Texas Instruments Incorporated, Dallas, TX (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1440 days.

- (21) Appl. No.: 08/698,251

- (22) Filed: Aug. 14, 1996

## **Related U.S. Application Data**

- (60) Continuation of application No. 08/475,245, filed on Jun. 7, 1995, now abandoned, which is a division of application No. 08/055,099, filed on Apr. 29, 1993, now Pat. No. 5,468,666.

- (51) Int. Cl.<sup>7</sup> ..... H01L 29/76

- (58) Field of Search ...... 257/412, 369,

- 257/407, 392

## (56) **References Cited**

## **U.S. PATENT DOCUMENTS**

| 4,472,871 A | * 9/1984  | Green et al  | 257/392 |

|-------------|-----------|--------------|---------|

| 4,559,694 A | * 12/1985 | Yoh et al    | 257/412 |

| 5,214,298 A | * 5/1993  | Yuan et al   | 257/195 |

| FORE        | IGN PATE  | NT DOCUMENTS |         |

US 6,348,719 B1

Feb. 19, 2002

## JP 4056354 \* 2/1992 ..... 257/392 \* cited by examiner

(10) Patent No.:

(45) Date of Patent:

Primary Examiner-Mark V. Prenty

(74) Attorney, Agent, or Firm—Gary C. Honeycutt; Fred Telecky; Arthur I. Navarro

### (57) **ABSTRACT**

A semiconductor device having high and low voltage transistors on the same chip. High voltage NMOS transistor 76 comprises a polysilicon gate 40 doped at first dopant level. Low voltage NMOS transistor comprises a polysilicon gate 44 doped at a second dopant level. The second dopant level is higher than the first. High voltage PMOS transistor 84 comprises a polysilicon gate 48 doped at a third dopant level. Low voltage PMOS transistor comprises a polysilicon gate 52 doped at a fourth dopant level. The fourth dopant level is higher than the third.

#### 2 Claims, 7 Drawing Sheets

,0

10

## USING A CHANGE IN DOPING OF POLY GATE TO PERMIT PLACING BOTH HIGH VOLTAGE AND LOW VOLTAGE TRANSISTORS ON THE SAME CHIP

This application is a continuation of application Ser. No. 08/475,245 filed Jun. 7, 1995 and now abandoned, which is a divisional of application Ser. No. 08/055,099 filed Apr. 29, 1993 and now U.S. Pat. No. 5,468,666.

#### FIELD OF THE INVENTION

This invention generally relates to semiconductor processing and more specifically to using a change in doping of the polysilicon gate to permit placing both high voltage and low voltage transistors on the same chip.

#### BACKGROUND OF THE INVENTION

As the density of integrated circuits increases, it becomes necessary to shrink the dimensions of NMOS and PMOS 20 transistors. Proper scaling of NMOS and PMOS transistors typically requires that the operating voltage be decreased as the gate oxide thickness is shrunk. Otherwise, the electric field will become too large in the gate oxide and, consequently, the gate oxide will eventually fail. 25

On the other hand, if the operating voltage is decreased, the device will no longer be compatible with most of the current packaged integrated circuits which operate at a standard voltage. For, instance, most circuits using CMOS transistors with gate lengths of 0.8 microns or more operate 30 at 5.0V. When the gate length in decreased to 0.5 microns and the gate oxide thickness to 90-120 Å, the voltage is lowered to 3.3V in order to maintain reliability of the gate oxide. Thus, a device is needed that has input/output peripheral sections that operate at 5.0 V so that the device may be 35 used in systems using other chips operating at 5.0 V while allowing other portions of the device to operate at 3.3 V. The same problem occurs when the gate length is reduced from 0.5  $\mu$ m to 0.35  $\mu$ m or 0.25  $\mu$ m. At 0.35  $\mu$ m, the voltage is reduced to 2.5V or lower in order to maintain the integrity 40 of the gate oxide.

One method that has been used to overcome this problem uses longer gate lengths in the input/output CMOS transistors in order to minimize the hot carrier stress problem. However, gate insulator reliability may still be a problem due to the large electric field in the gate insulator.

Another method uses a thicker gate oxide for the input/ output sections. This lowers the electric field in the high voltage CMOS transistors. However, this method requires a resist to be patterned on the gate oxide to remove the oxide from one portion of the chip and then strip the resist and grow the second gate oxide of a different thickness. As a result, defects and contamination may occur in the gate oxide.

Another approach uses two polysilicon layers. One polysilicon layer is placed over a first gate of one thickness. Next, a second gate oxide is grown and another polysilicon layer is deposited over the second gate oxide. This process however, adds to many additional process steps.

#### SUMMARY OF THE INVENTION

Generally, and in one form of the invention, a method for forming a semiconductor device having a semiconductor body is disclosed. A gate oxide is formed over a surface of 65 the semiconductor body and a layer of polysilicon is deposited over the gate oxide. The polysilicon layer is patterned to 2

expose the area where low voltage NMOS transistors are to be formed. The low voltage NMOS region is implanted with an n-type dopant at a first dopant level. The polysilicon layer may then be patterned to expose the ares where low voltage PMOS transistors are to be formed. The low voltage PMOS

region may then be implanted with a p-type dopant at a second dopant level. The polysilicon layer and gate oxide are then etched to form at least one high voltage NMOS gate, at least one low voltage NMOS gate, and, optionally, at least one low voltage PMOS gate, and at least one high voltage

<sup>10</sup> PMOS gate. Note that the low voltage NMOS and PMOS transistor gates will already comprise doped polysilicon. The n+ source/drain regions, the high voltage NMOS gate and the low voltage NMOS gate are implanted with the n-type dopant at a third dopant level. The p+ source/drain regions, the high voltage PMOS gate and the low voltage PMOS gate may then be implanted with the p-type dopant at a fourth dopant level.

An advantage of the invention is in providing a semiconductor device comprising both high and low voltage transistors.

A further advantage of the invention is in providing a semiconductor device having both high and low voltage transistors that avoids gate insulator reliability problems.

A further advantage of the invention is in providing a 25 semiconductor device having both high and low voltage transistors that does not require longer gate lengths in the high voltage transistors.

A further advantage of the invention is in providing a semiconductor device having high voltage transistor gates at one dopant level and low voltage transistor gates at a higher dopant level.

These and other advantages will be apparent to those skilled in the art having reference to this specification, in conjunction with the drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings:

45

50

60

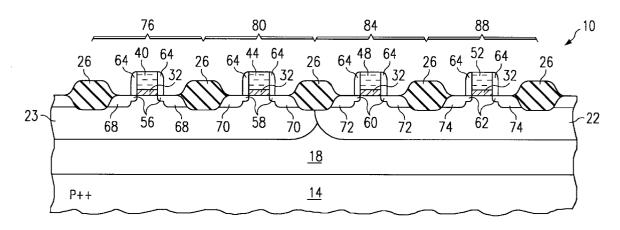

FIG. 1 is a cross-sectional view of the preferred embodiment of the invention;

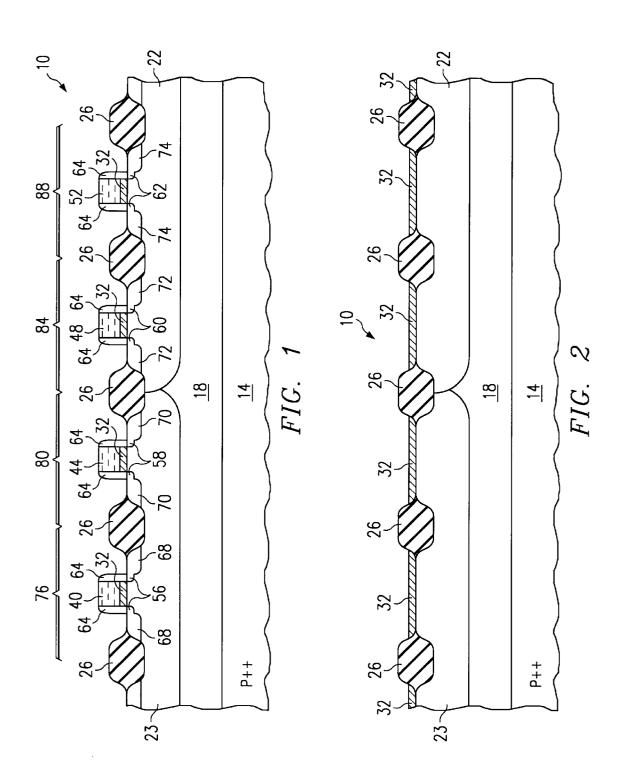

FIG. **2** is a cross-sectional view of semiconductor body used as the starting point for the fabrication of the preferred embodiment of the invention;

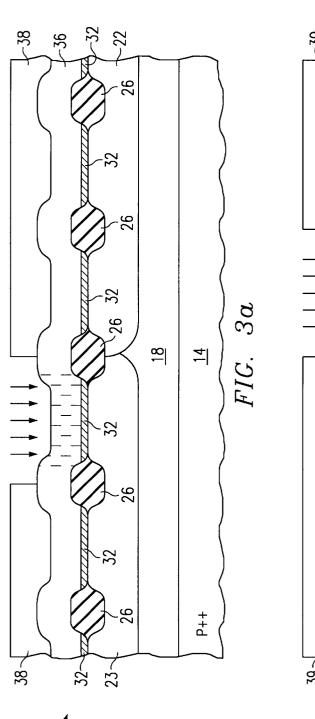

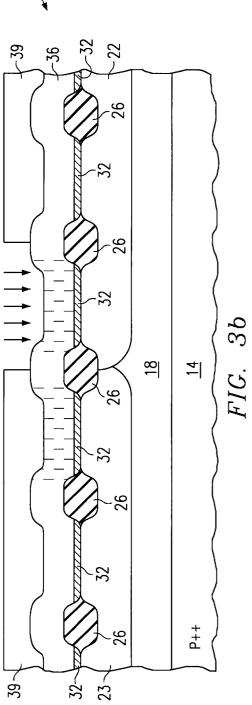

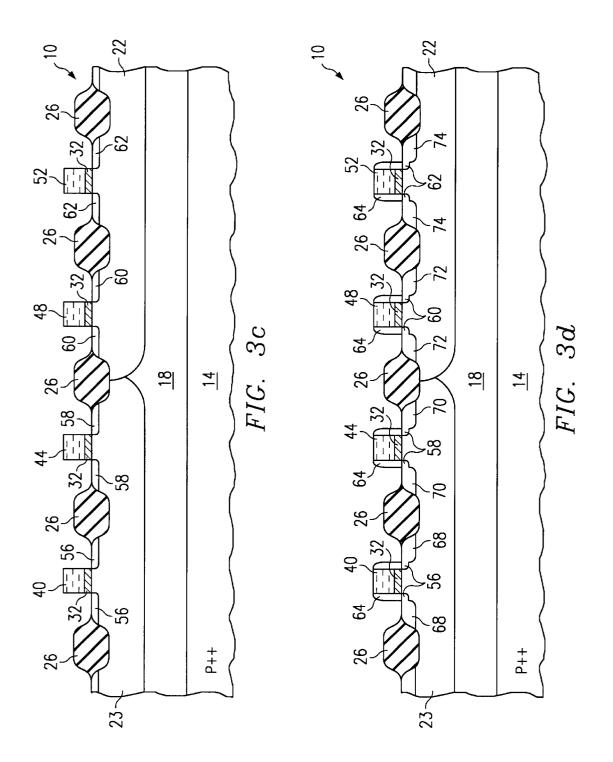

FIGS. 3a-d are cross-sectional views of the preferred embodiment of the invention during various fabrication steps;

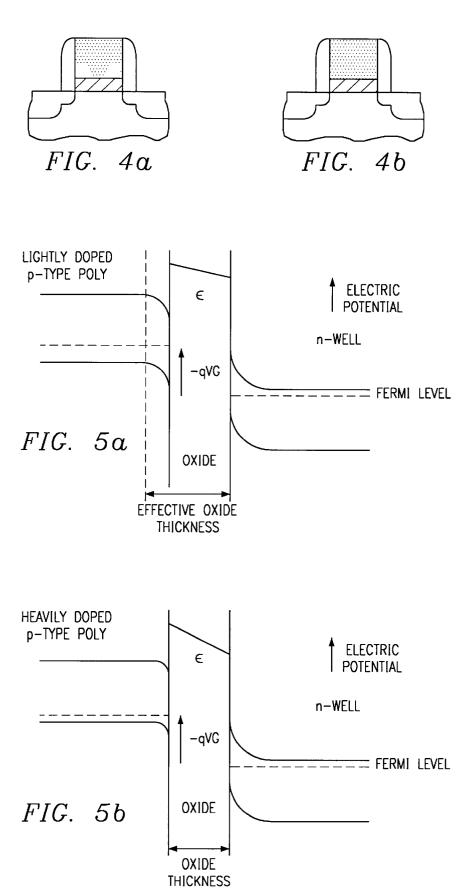

FIGS. 4*a*–*b* are cross-sectional views of lightly and heavily doped poly gates, respectively;

FIGS. **5***a*–*b* are band diagrams over the active channel of PMOS transistors having lightly and heavily doped poly gates, respectively;

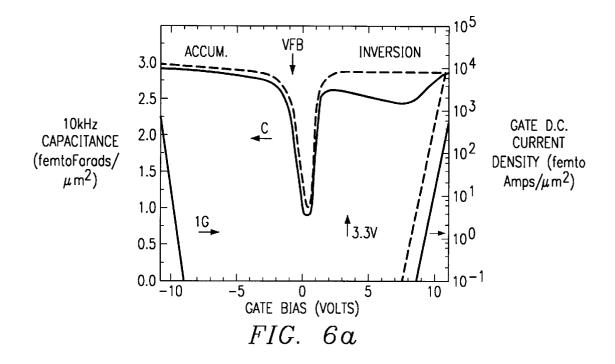

FIGS. 6a-b are C-V diagrams of NMOS and PMOS transistors, respectively, having a gate oxide of 120 Å;

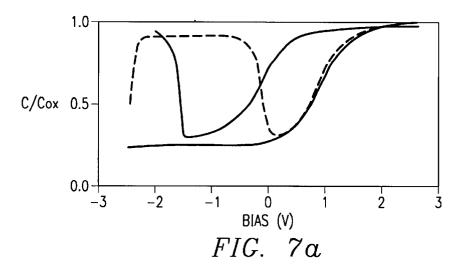

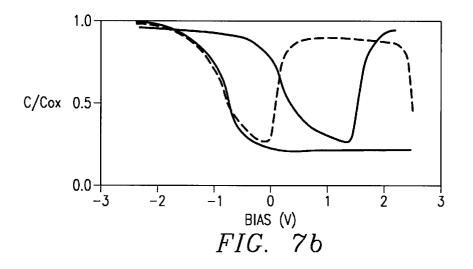

FIGS. 7*a*–*b* are C-V diagrams of NMOS and PMOS transistors, respectively, having poly gates doped once dur-55 ing the source/drain implant;

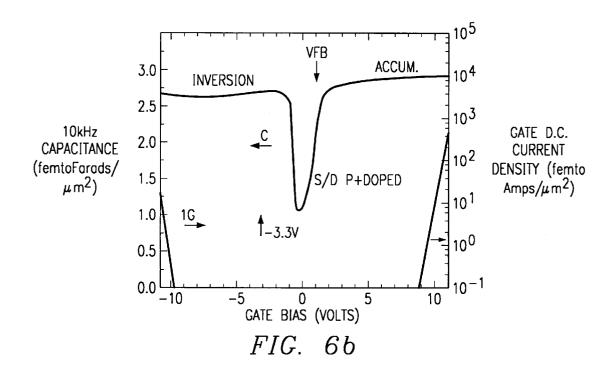

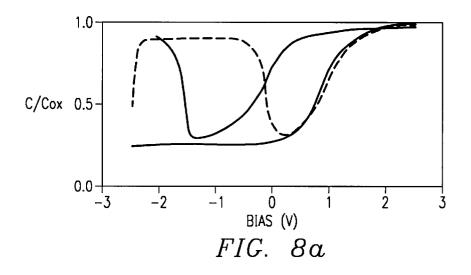

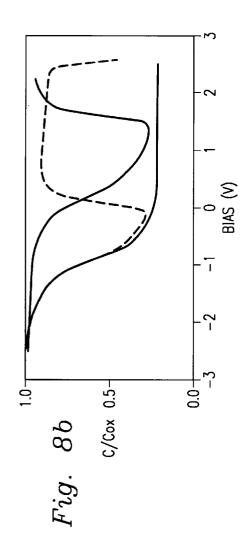

FIGS. **8***a*–*b* are C-V diagrams of NMOS and PMOS transistors, respectively, having extra poly gate doping; and

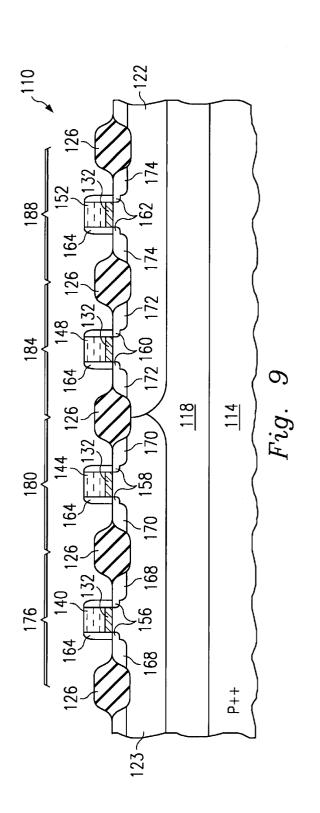

FIG. 9 is cross-sectional view of an alternate preferred embodiment of the invention.

Corresponding numerals and symbols in the different figures refer to corresponding parts unless otherwise indicated.

#### DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

The preferred embodiment of the invention will be described in conjunction with CMOS transistors using n+

15

20

25

35

polysilicon for NMOS gates and p+ polysilicon for PMOS gates. It will be apparent to those skilled in the art that other processes and devices, such as CMOS, BiCMOS, and BiN-MOS devices, can also realize the benefits of this invention.

For high voltage performance and packing density, the lavout and thickness dimensions of CMOS transistors need to be decreased. This usually results in a decreased operating voltage in order to avoid reliability problems caused by increasing the electric field in the gate insulator. Currently, however, most integrated circuits still need to interact with 10 other circuits using a standard higher voltage. Thus, there is a need for higher voltage input/output sections and lower voltage sections on the same chip. There is also a need to place higher voltage non-volatile memory on the same chip with high density lower voltage CMOS.

The preferred embodiment of the invention provides high and low voltage CMOS on the same chip by means of using lower doping of the polysilicon gates in the high voltage portions of the circuit. In the low doping areas, the electric field from the gate insulator penetrates into the lower portion of the gate and decreases the peak electric field in the gate insulator. In other words, the high voltage CMOS transistors will behave as if they had a thicker gate oxide. Accordingly, the operating voltage can be increased to a higher voltage (e.g., back to 5.0 V) without causing an electric field sufficient to cause gate insulator reliability problems.

The preferred embodiment of the invention is shown in FIG. 1. Substrate 14 of device 10 is shown as a p++ substrate. It will be apparent to those skilled in the art that other substrates may alternatively be used. Optional epitaxial layer 18 is p-type into which a patterned p-well 23 may be implanted and which will contain the high voltage NMOS transistor 76 and low voltage NMOS transistor 80. N-well 22 is located in epitaxial layer 18. Field insulating regions 26 may comprise oxide and serve to isolate transistors 76, 80, 84, and 88 from each other. Gate oxide regions 32 and sidewall oxides 64 insulate polysilicon gates 40, 44, and 52.

High voltage NMOS transistor **76** is located in p-well **23** and comprises gate 40 and source/drain regions 68. Transistor 76 may also comprise lightly doped drains (LDDs) 56. Low voltage NMOS transistor 80 is also located in p-well 23 and comprises gate 44, source/drain regions 70, and gate insulator 32. Transistor 80 may also comprise LDDs 58. Low voltage PMOS transistor 84 and high voltage PMOS transistor 88 are located in n-well 22. Low voltage PMOS transistor 84 comprises a gate 48, gate insulator 32 source/ drain regions 72, and optionally LDDs 60. High voltage PMOS transistor 88 comprises a gate 52, source/drain 50 regions 74, and optionally LDDs 62.

FIG. 2 shows semiconductor body 12 after the formation of p-type epitaxial layer 18, n-well 22, p-well 23, field insulating regions 26, and gate oxide 32. The preferred method for forming device 10 in the structure of FIG. 2 will 55 now be described with reference to FIGS. 3a-d.

Referring to FIG. 3a, a layer of polysilicon 36 is deposited over the gate oxide 32 covering the surface of semiconductor body 12. Polysilicon layer 36 may have a thickness in the range of 0.2 to 0.4 microns, preferably 0.25 microns. For the 60 low voltage transistors, the thickness of polysilicon layer 36 determined by the depth of the source/drain junctions. Polysilicon layer 36 may be thicker than the source/drain junctions so that when the source/drain junctions are implanted, the dopant does not extend to the bottom of the 65 polysilicon gates. Masking layer 38, for example photoresist, is deposited on the surface of polysilicon layer

36 as shown in FIG. 3a. Masking layer 38 masks portions of polysilicon layer 36 where high voltage NMOS transistor 76 and both high and low voltage PMOS transistors 84 and 88 are to be formed. The exposed portion of polysilicon layer 36 is implanted with phosphorous (e.g., 5E15 P/cm<sup>2</sup>) and annealed. Typically, the implant will be a high energy implant in the range of 1E15 to 1E16 P or As/cm<sup>2</sup>.

Masking layer 38 is then removed and a second masking layer **39** is deposited, as shown in FIG. **3***b*. Masking layer **39** masks portions of polysilicon layer 36 where both high and low voltage NMOS transistors 76 and 80 and high voltage PMOS transistor 88 are to be formed. The exposed portion of polysilicon layer 36 is then implanted with boron (e.g., 7E15 B/cm<sup>2</sup>) and annealed. Typically, the implant will be a high energy implant in the range of 1E15 B/cm<sup>2</sup> to 1E16 B/cm<sup>2</sup>. An anneal is used to anneal implant damage before gate etch and to drive both the n-type and p-type dopant material to the bottom of polysilicon layer 36. Masking layer **39** is then removed.

Referring to FIG. 3c, polysilicon layer 36 is then patterned by microlithography and etched, along with gate oxide 32 to form gates 40, 44, 48, and 52. At this point, LDDs 56, 58, 60, and 62 may optionally be formed. N+ LDDs 56 and 58 are patterned and implanted in p-type epitaxial layer 18 by conventional techniques. Then, p+ LDDs 60 and 62 are patterned and implanted into n-well 22 by conventional techniques.

As shown in FIG. 3d, sidewall oxides 64 are now formed on the vertical edges of gates 40, 44, 48, and 52 as is well known in the art (e.g., CVD deposition of silicon dioxide and followed by an anisotropic etch). Following the formation of sidewall oxides 64, n+ source/drain regions 68 and 70 are patterned and implanted (e.g., 2E15 As/cm<sup>2</sup> at 80 keV plus 4E14 P/cm<sup>2</sup> at 60 keV), as shown in FIG. 3d. Other dopant concentrations will be apparent to those skilled in the art. However, typically the doping implant dose will be in the range  $1E15/cm^2$  to  $5E 15/cm^2$ . It will also be apparent to those skilled in the art that an implant of either arsenic or phosphorous or a combination thereof may be used. Finally, p+ source/drain regions 72 and 74 are patterned and imprinted (e.g., 1.5E15 B/cm<sup>2</sup>). Typically, the doping implant dose will be in the range of 1E15/cm<sup>2</sup> to 5E15/cm<sup>2</sup> and the dopant species may, for example, be boron or  $BF_2$ .

Because polysilicon layer 36, and thus gates 40, 44, 48, and 52, are at least as thick as source/drain regions 56, 58, 60, and 62, the implants forming the source/drain regions 45 56-62, will only partially dope the polysilicon gates 40 and 52, as shown in FIG. 4a with only a small amount of dopant reaching the bottom surface of the polisilicon. The high energy implant and anneal performed prior to the gate etch combined with the source/drain implants, completely dope polysilicon gates 44 and 48, as shown in FIG. 4b. The light doping at the bottom of high voltage NMOS and PMOS gates 40 and 52, enables the electric field to penetrate into the bottom of the polysilicon gate. FIG. 5a shows an electric potential band diagram for a high voltage PMOS transistor, such as transistor 88, having a lightly doped gate according to the invention. The electric field extends from the oxide into the polysilicon gate making the effective oxide thickness greater than the actual oxide thickness. FIG. 5b shows a band diagram for a low voltage PMOS transistor, such as transistor 84, having a highly doped gate. The electric field will not penetrate into the low voltage areas because of the heavy doping at the bottom of the low voltage gates. The electric field remains within the oxide region.

FIGS. 5a and 5b are for the case of PMOS transistors with p-type poly. The case for NMOS transistors with n-type poly would have similar band diagrams but with the opposite polarity.

4.5E17 4.6E17 4.2E17

An experiment was performed using three different gate oxide thicknesses: 45 Å, 55 Å, and 65 Å. Table I shows the Capacitance-Voltage test results for the experiment. The nomenclature PG12 indicates that these wafers had extra patterned implants of 7E15-P/cm2 over NMOS and 7E15-B/cm2 over PMOS. These implants are in addition to the source/drain implants that are patterned after gate etch (and go into both the poly gate and the source/drains). The NMOS source/drain implant is 2E15-As/cm2 @ 80 keV plus 4E14-P/cm2 @ 60keV. The PMOS source/drain implant is 1.5E15-10 B/cm2 @ 20 keV. The polysilicon thickness is 2500A in all cases. The column tOX ACC indicates the effective oxide thickness derived from the maximum capacitance at [3.5V] in accumulation. The column tOX INV gives the effective oxide thickness derived from the maximum inversion capacitance measured by Quasi-Static techniques at [3.5]V in inversion. Note for wafer 09 without the extra implant, that the effective NMOS capacitance in inversion is 73A in comparison to 59.7A in accumulation. Even larger differences can be obtained between cases "S/D" and S/D+PG12" 20 by increasing the poly thickness or decreasing the S/D dose.

03 S/D

09 S/D

TABLE 1

the capacitance is low because the Debye length or depletion depth in the poly is comparable with the gate oxide thickness-minority carriers in the poly are not involved.

FIGS. 7a, 7b, 8a, and 8b show the Capacitance-Voltage characteristics corresponding to wafers 14 and 15 in Table I. Each figure shows the measured high frequency C-V, the theoretical high frequency C-V, and the measured Quasi-Static C-V. FIG. 7a shows the PMOS C-V with source/drain implant alone. FIG. 7b shows the NMOS C-V with source/ drain implant alone. FIG. 8a shows the PMOS C-V with extra dopant and FIG. 8b shows the NMOS C-V with extra dopant. Note the difference is capacitance in channel inversion with and without the added 7E15/cm<sup>2</sup> implant for NMOS and PMOS. For example, the difference between 15 tOX INV for the source/drain implant alone, as shown in FIG. 7a and tOX INV for wafer 16 with the added implant, as shown in FIG. 8b is on the order of 10 Å.

An alternate preferred embodiment of the invention is shown in FIG. 9. Device 110 is identical to device 10 except that all transistors are high voltage. Thus, the fabrication of device 110 is identical to that described above for device 10

|                                                          | 66.6<br>60.0<br>60.6 |

|----------------------------------------------------------|----------------------|

| 14 S/D 52.3 1.06 61.7 3.6E17 53.3 11.03 6                |                      |

| (+ 3/D) $52.5$ $-1.00$ $01.7$ $5.017$ $55.5$ $+1.05$ $0$ | 60.6                 |

| 6 S/D + PG12 51.7 -1.00 52.7 3.6E17 52.6 +1.12 6         |                      |

ANALYSIS OF C-V DATA FOR LOT-9628 NMOS PMOS tOX VFB tOX SUBST tOX VFB tOX SUB Wafer/implant ACC INV CONC. ACC volts INV CONC. volts 40.8 A -1.03 V 53 A 3.5E17 42.5 A +1.04 V 51 A 4.9E17/cm3 04 S/D + PG1241.1 -1.0043 3.6E17 42.9 +1.13 47.8 4.2E17 59.7 4.9E17 -1.07 73 3.5E17 60.4 +1.0569.6

> except that the implants and anneals done prior to the polysilicon etch are omitted. Device 110 has a substrate 114, which may for example be p++, and an optional epitaxial layer 118, which may be p-type. N-well 122 is located in epitaxial layer 118. Field insulating regions 126 may comprise oxide and serve to isolate transistors 176, 180, 184, and 188 from each other. Gate oxide regions 132 and sidewall oxides 164 insulate polysilicon gates 140, 144, 148, and 152. NMOS transistors 176 and 180 both operate at a higher voltage and are located p-well 123. NMOS transistor 176 comprises gate 140 and source/drain regions 168. Transistor 176 may also comprise lightly doped drains (LDDs) 156. NMOS transistor 180 comprises gate 144 and source/drain regions 170. Transistor 180 may also comprise LDDs 158. PMOS transistors 184 and 188 are located in n-well 122. PMOS transistor 184 comprises a gate 148, source/drain regions 172, and optionally LDDs 160. High voltage PMOS transistor 188 comprises a gate 152, source/drain regions 174, and optionally LDDs 162.

An important aspect of the preferred embodiments is that the poly thickness may be chosen thicker than in the usual design. Generally for CMOS using patterned n+/p+ poly gates, the poly gate thickness is adjusted relative to the depth of the source/drain junctions such that the source/drain implants also sufficiently dope the bottom of the poly gate but the poly thickness should not be so thin that the source/drain implants penetrate the gate oxide and compensate the channel. In this invention, the poly gate thickness may be chosen relatively thick so that those transistors for high voltage operation that are doped by the source/drain

15

implants alone will not be heavily doped on the bottom surface of the poly gate: in this way, the electric field will penetrate into the poly. Since the patterned implants to dope the poly for the low voltage transistors are implanted before gate etch, higher implant energies and doses can be used to adequately dope the bottom of the poly without regard to the requirements for the source/drain doping profiles.

It should be noted that if BiNMOS input/output drivers are used, then only the added implant for the NMOS transistors would be performed. If the input/output circuits <sup>10</sup> are NMOS only, then obviously only the added pattern for NMOS would be performed.

It should also be noted that the low voltage transistors can be built with an unpatterned n+ implant thus producing low-voltage buried channel PMOS transistors using  $n^+$  poly rather than  $p^+$  poly and high voltage surface channel transistors.

The foregoing description of the electric field penetration into the bottom of the polysilicon gate has been explained by reference to FIGS. **5**, **6**, **7**, and **8**(*a* and *b*) which describe the situation over the active channel of the transistor. It should be noted that the electric field will also penetrate into the lightly doped polysilicon over the edges of the gate where the gate passes over the LDD or source drain. In fact, the penetration of the electric field into the lightly doped polysilicon is even greater than over the active channel because the electric field current cannot penetrate into the silicon underneath the gate oxide because the LDD or S/D is more heavily doped. 30

A few preferred embodiments have been described in detail hereinabove. It is to be understood that the scope of the invention also comprehends embodiments different from those described, yet within the scope of the claims. While this invention has been described with reference to illustrative embodiments, this description is not intended to be construed in a limiting sense. Various modifications and combinations of the illustrative embodiments, as well as other embodiments of the invention, will be apparent to persons skilled in the art upon reference to the description. It is therefore intended that the appended claims encompass any such modifications or embodiments.

#### What is claimed is:

1. A semiconductor device having a semiconductor body, comprising:

- a) at least one high voltage NMOS transistor having a high voltage NMOS gate; and

- b) at least one low voltage NMOS transistor having a low voltage NMOS gate;

- wherein said low voltage NMOS gate is more heavily doped than said high voltage NMOS gate, and wherein the bottom of said high voltage gate is more lightly doped than the top of said high voltage gate.

**2**. A semiconductor device having a semiconductor body, comprising:

- a) at least one low voltage PMOS transistor having a low voltage PMOS gate; and

- b) at least one high voltage PMOS transistor having a high voltage PMOS gate,

- wherein said low voltage PMOS gate is more heavily doped than said high voltage PMOS gate, and wherein the bottom of said high voltage gate is more lightly doped than the top of said high voltage gate.

\* \* \* \* \*