# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2021/0193685 A1 ZHU et al.

Jun. 24, 2021 (43) **Pub. Date:**

### (54) ARRAY SUBSTRATE AND MANUFACTURING METHOD THEREOF, DISPLAY PANEL AND DISPLAY DEVICE

(71) Applicants: BOE TECHNOLOGY GROUP CO.. LTD., Beijing (CN); BEIJING BOE DISPLAY TECHNOLOGY CO.,

LTD., Beijing (CN)

(72) Inventors: Ning ZHU, Beijing (CN); Qiujie SU, Beijing (CN); Chongyang ZHAO,

Beijing (CN)

(73) Assignees: **BOE TECHNOLOGY GROUP CO.,** LTD., Beijing (CN); BEIJING BOE DISPLAY TECHNOLOGY CO., LTD., Beijing (CN)

(21) Appl. No.: 15/779,222

(22) PCT Filed: Sep. 29, 2017

(86) PCT No.: PCT/CN2017/104162

§ 371 (c)(1),

(2) Date: May 25, 2018

### (30)Foreign Application Priority Data

Mar. 17, 2017 (CN) ...... 201710159841.0

### **Publication Classification**

(51) Int. Cl. H01L 27/12 (2006.01)

U.S. Cl. (52)CPC .......... H01L 27/124 (2013.01); H01L 27/127 (2013.01)

#### (57)**ABSTRACT**

An array substrate and a manufacturing method thereof, a display panel and a display device are provided. The array substrate includes common electrodes, multiple first common electrode lines and multiple second common electrode lines. The multiple first common electrode lines intersect with the multiple second common electrode lines to form grids. The multiple first common electrode lines are connected with the common electrodes through first via-holes and the multiple second common electrode lines are connected with the common electrodes through second viaholes.

Fig. 1

Fig. 2

## ARRAY SUBSTRATE AND MANUFACTURING METHOD THEREOF, DISPLAY PANEL AND DISPLAY DEVICE

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] The present application claims a priority to Chinese Patent Application No. 201710159841.0 filed on Mar. 17, 2017, the disclosure of which is incorporated in its entirety by reference herein.

### TECHNICAL FIELD

[0002] The present disclosure relates to the field of displaying technology, and more particularly, to an array substrate and a manufacturing method thereof, a display panel and a display device.

### BACKGROUND

[0003] For an array substrate including a common electrode in related technology, a metallic common electrode line, also referred as a gate layer common electrode line, may be provided in a gate metal layer and arranged in parallel with a gate line in order to reduce a resistance of a transparent common electrode and transmit a signal for the common electrode. The gate layer common electrode line is connected with the transparent common electrode through a via-hole.

## **SUMMARY**

[0004] The present disclosure provides an array substrate and a manufacturing method thereof, a display panel and a display device, to reduce resistances of transparent common electrodes and to transmit signals for the common electrodes. Metallic common electrode lines (also referred as gate layer common electrode lines) may be provided in a gate metal layer and in parallel with gate lines. The gate layer common electrode lines are connected with the transparent common electrodes through via-holes.

[0005] In view of the above, the present disclosure provides an array substrate, including transparent common electrodes, multiple first common electrode lines and multiple second common electrode lines. The multiple first common electrode lines intersect with the multiple second common electrode lines to form grids. The multiple first common electrode lines are connected with the common electrodes through first via-holes and the multiple second common electrode lines are connected with the common electrodes through second via-holes.

[0006] Optionally, the multiple first common electrode lines are arranged in a different layer from the multiple second common electrode lines.

[0007] Optionally, the array substrate further includes multiple gate lines. The first common electrode lines are arranged in an identical layer to and in parallel with the gate lines

[0008] Optionally, the array substrate further includes multiple data lines. The second common electrode lines are arranged in an identical layer to and in parallel with the data lines

[0009] Optionally, the array substrate is a double-gate-line type array substrate. Two gate lines are provided between two adjacent rows of subpixels. One data line is provided every two adjacent columns of subpixels. Each second

common electrode line is provided between two columns of subpixels where no data line is provided.

[0010] Optionally, the common electrodes for respective subpixels are arranged separately. The common electrodes at an identical row are connected with each other through the first common electrode line, and the common electrodes at an identical column are connected with each other through the second common electrode line.

[0011] Optionally, the first via-hole is deeper than the second via-hole.

[0012] Optionally, the array substrate further includes a base substrate, a gate insulating layer, a pixel electrode and an insulating layer. The first common electrode lines are arranged on the base substrate. The gate insulating layer is arranged on the base substrate and covers the multiple first common electrode lines. The pixel electrode and the multiple second common electrode lines are arranged on the gate insulating layer. The insulating layer is arranged on the gate insulating layer and covers the pixel electrode and the multiple second common electrode lines. The transparent common electrodes are arranged on the insulating layer. The first via-holes extend through the insulating layer and the gate insulating layer and the second via-holes extend through the insulating layer.

[0013] The present disclosure further provides a display panel, including the above array substrate.

[0014] The present disclosure further provides a display device, including the above display panel.

[0015] The present disclosure further provides a method for manufacturing an array substrate, including: forming grids by intersecting multiple first common electrode lines with multiple second common electrode lines; and forming transparent common electrodes, the multiple first common electrode lines and the multiple second common electrode lines in a way that the multiple first common electrode lines are connected with the transparent common electrodes through first via-holes and the multiple second common electrode lines are connected with the transparent common electrodes through second via-holes.

[0016] Optionally, the multiple first common electrode lines are arranged in a different layer from the multiple second common electrode lines.

[0017] Optionally, the forming the transparent common electrodes, the multiple first common electrode lines and the multiple second common electrode lines includes: forming the multiple first common electrode lines and multiple gate lines in parallel with the multiple first common electrode lines through one patterning process.

[0018] Optionally, the forming the transparent common electrodes, the multiple first common electrode lines and the multiple second common electrode lines includes: forming the multiple second common electrode lines and multiple data lines in parallel with the multiple second common electrode lines through one patterning process.

### BRIEF DESCRIPTION OF THE DRAWINGS

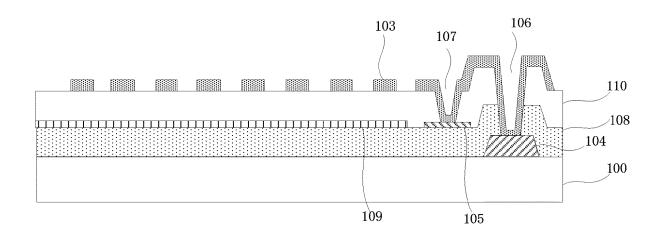

[0019] FIG. 1 is a top view of an array substrate according to an embodiment of the present disclosure; and

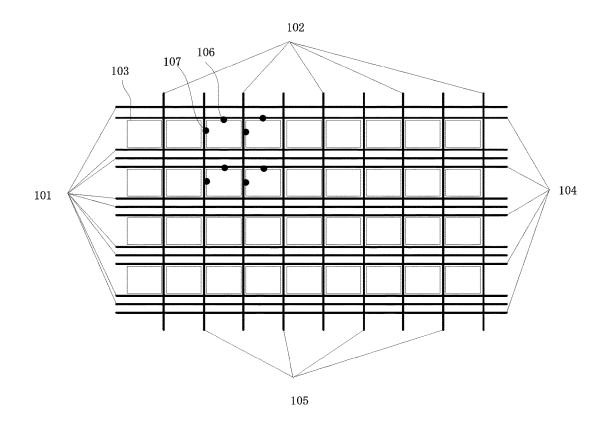

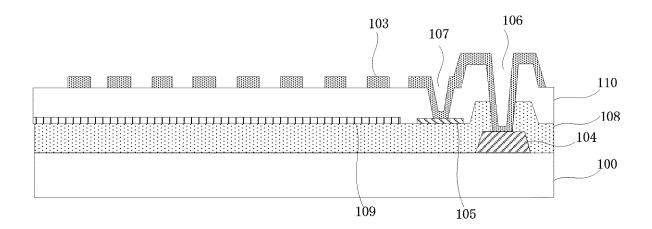

[0020] FIG. 2 is a sectional view of an array substrate according to another embodiment of the present disclosure.

### DETAILED DESCRIPTION

[0021] To further clarify objects, technical solutions and advantages of embodiments of the present disclosure, the technical solutions in the embodiments of the present disclosure are to be described in a clear and complete way in conjunction with drawings for the embodiments of the present disclosure. Apparently, described embodiments are a part of rather than all of the embodiments of the present disclosure. Any other embodiments obtained by the ordinary skilled in the art based on the described embodiments of the present disclosure shall fall within scope of protection of the present disclosure.

[0022] For an array substrate in related technology, a gate layer common electrode line is merely provided in a horizontal direction, hence, a common voltage for a whole panel is of relatively un-uniform distribution and the common voltage is not stable, resulting in poor displaying performance. An array substrate is provided according to an embodiment of the present disclosure, including: a transparent common electrode, multiple first common electrode lines and multiple second common electrode lines. The multiple first common electrode lines intersect with the multiple second common electrode line is connected with the common electrode through a first via-hole and each second common electrode line is connected with the common electrode line is connected with the common electrode through a second via-hole.

[0023] According to the embodiment of the present disclosure, a resistance of the common electrode can be effectively reduced by providing, for the common electrode of the array substrate, the common electrode lines forming the grids and connected with the common electrode. In addition, by distributing the common electrode lines in grids instead of arranging the gate layer common electrode line only in the horizontal direction, the whole panel can be ensured with a stable and uniform common voltage. Furthermore, since the resistance of the common electrode can be effectively reduced with the common electrode lines in grids, a line width of each common electrode line can be accordingly reduced, thereby improving aperture ratio.

[0024] Usually, the common electrode is made of a transparent conductive material such as ITO.

[0025] Optionally, the first common electrode lines and the second common electrode lines may be made of a metallic conductive material, to facilitate reduction of the resistance of the common electrode.

[0026] However according to some other embodiments of the present disclosure, it is not excluded that the first common electrode lines and the second common electrode lines are made of a transparent conductive material to improve aperture ratio.

[0027] Optionally, a grid structure formed by the first common electrode lines and the second common electrode lines covers an area where the common electrode is located.

[0028] According to embodiments of the present disclosure, the first common electrode lines may be arranged at an identical layer to the second common electrode lines, or may be arranged at a different layer from the second common electrode lines.

[0029] In a case that the first common electrode lines are arranged at an identical layer to the second common electrode lines, the first common electrode lines are connected to the second common electrode lines. In this case, the first common electrode lines and the second common electrode

lines usually needs to be arranged at an independent layer to avoid interfering with patterns on other functional film layers of the array substrate.

[0030] In a case that the first common electrode lines are arranged at a different layer from the second common electrode lines, at least one of the first common electrode lines and the second common electrode lines may be arranged at an identical layer to other functional film layer of the array substrate, to reduce a thickness of the film layers. Optionally, at least one of the first common electrode lines and the second common electrode lines may be arranged at an identical layer to other conductive functional film layer and can be formed together with the conductive functional film layer through one pattering process, which decreases a quantity of mask(s) and reduces the cost.

[0031] The array substrate further includes multiple gate lines. Optionally, the first common electrode lines and the gate lines may be arranged at an identical layer to decrease a quantity of mask and reduce the cost. Furthermore, optionally, the first common electrode lines may be arranged in parallel with the gate lines. Obviously according to some other embodiments of the present disclosure, it is not excluded that the first common electrode lines are arranged at an identical layer to the gate lines and perpendicular to the gate lines; in this case, each first common electrode line needs to be disconnected at intersections with the gate lines are

[0032] In the case that the first common electrode lines are arranged at an identical layer to the gate lines and in parallel with the gate lines, one row of subpixels may correspond to one first common electrode line or multiple rows of subpixels may correspond to one first common electrode line.

[0033] The array substrate further includes multiple data lines. Optionally, the second common electrode lines and the data lines may be arranged at an identical layer to decrease a quantity of mask and reduce the cost. Furthermore, optionally, the second common electrode lines may be arranged in parallel with the data lines. Obviously according to some other embodiments of the present disclosure, it is not excluded that the second common electrode lines are arranged at an identical layer to the data lines and perpendicular to the data lines; in this case, each second common electrode line needs to be disconnected at intersections with the data lines.

[0034] In the case that the second common electrode lines are arranged at an identical layer to the data lines and in parallel with the data lines, one column of subpixels may correspond to one second common electrode line or multiple columns of subpixels may correspond to one second common electrode line.

[0035] Referring to the drawings, FIG. 1 is a top view of an array substrate according to an embodiment of the present disclosure. The array substrate according to the embodiment of the present disclosure is a double-gate-line type array substrate. The array substrate includes multiple gate lines 101 and multiple data lines 102. Two gate lines 101 are provided between two adjacent rows of subpixels. One data line 102 is provided every two adjacent columns of subpixels and two columns of subpixels are located between every two data lines. Common electrodes 103 for respective subpixels are arranged separately. The array substrate further includes multiple first common electrode lines 104 and multiple second common electrode lines 105. The first common electrode lines 104 are arranged at an identical layer to and in parallel with the gate lines 101. The second

common electrode lines 105 are arranged at an identical layer to and in parallel with the data lines. Each of the second common electrode lines 105 is provided between two columns of subpixels where no data line 102 is provided. The first common electrode lines 104 and the second common electrode lines 105 form grids. The first common electrode lines 104 are connected to the common electrodes 103 through first via-holes 106. The second common electrode lines 105 are connected to the common electrodes 103 through second via-holes 107.

[0036] According to the embodiment of the present disclosure, the double-gate-line type array substrate has a specific structure that two columns of subpixels are located between every two data lines, such that the second common electrode lines are provided between columns of subpixels where no date line is provided and form grids together with the first common electrode lines, thereby ensuring a stable and uniform common voltage for a whole panel. In addition, since resistances of the common electrodes can be effectively decreased due to the common electrode lines in grids, a line width of each common electrode line can be reduced accordingly to improve aperture ratio.

[0037] According to the embodiment of the present disclosure, the common electrodes 103 for respective subpixels are arranged separately, an identical row of common electrodes 103 is connected with each other through the first common electrode line 104 and an identical column of common electrodes 103 is connected with each other through the second common electrode line 105. Hence, all common electrodes 103 of a whole face are connected with each other.

[0038] In related technology, in the case that common electrodes for respective subpixels of the array substrate are arranged separately, connection between common electrodes for adjacent subpixels should be achieved by bridge wires through via-holes and an upper metal layer (such as a source and drain metal layer or a common electrode layer), thereby achieving connection among all common electrodes of the whole face. With this design, not only additional wires are necessary but also capacitances between the additional wires and other electrodes (such as source or drain electrodes, gate electrodes) overlapping the additional wires or located at lateral sides of the additional wires are introduced. The introduced capacitances may result in increasing load and may further affect subpixel charging.

[0039] According to the embodiment of the present disclosure, there is no need to provide the bridge wires. In a horizontal direction, an identical row of common electrodes can be connected through the first common electrode line, in a vertical direction, an identical column of common electrodes can be connected through the second common electrode line; hence, the structure is simple. In addition, capacitances between the common electrodes and electrodes located at a periphery of the common electrodes are effectively reduced, which facilitates subpixel charging.

[0040] Reference can be made to FIG. 2, which is a sectional view of an array substrate according to another embodiment of the present disclosure. The array substrate according to the embodiment differs from that according to the embodiment of FIG. 1 in that, the common electrode 103 here is a strip common electrode while the common electrode 103 according to the embodiment of FIG. 1 is a block common electrode. In FIG. 2, a numeral reference 100 represents a base substrate, a numeral reference 108 repre-

sents a gate insulating layer, a numeral reference 109 represents a pixel electrode and a numeral reference 110 represents an insulating layer.

[0041] As clearly reflected in FIG. 2, the common electrode 103 can be connected with a first common electrode line 104 in a gate metal layer and a second common electrode line 105 in a source and drain metal layer respectively through a first via-hole 106 and a second via-hole 107. The first via-hole 106 is a deep via-hole and the second via-hole 107 is a shallow via-hole.

[0042] The array substrate according to the embodiment of the present disclosure may be an HADS array substrate, an IPS array substrate or other array substrate including common electrodes.

[0043] A display panel is further provided according to an embodiment of the present disclosure, including the array substrate according to any foregoing embodiment.

[0044] A display device is further provided according to an embodiment of the present disclosure, including the above display panel.

[0045] The display device according to the embodiment of the present disclosure may further include a driving chip. The driving chip may be connected to the first common electrode lines and/or the second common electrode lines and used to transmit a common voltage signal to the common electrodes through the first common electrode lines and/or the second electrode lines.

[0046] A method for manufacturing an array substrate is provided according to an embodiment of the present disclosure. The method includes a step of forming transparent common electrodes and a step of forming multiple first common electrode lines and multiple second common electrode lines. The multiple first common electrode lines intersect with the multiple second common electrode lines to form grids. The first common electrode lines are connected with the common electrodes through first via-holes and the second common electrode lines are connected with the common electrodes through second via-holes.

[0047] Optionally, the first common electrode lines are arranged at a different layer from the second common electrode lines.

[0048] The method for manufacturing the array substrate further includes a step of forming multiple gate lines. Optionally, the first common electrode lines and the gate lines are formed through one patterning process, and the first common electrode lines are in parallel with the gate lines.

[0049] The method for manufacturing the array substrate further includes a step of forming multiple data lines. Optionally, the second common electrode lines and the data lines are formed through one patterning process, and the second common electrode lines are in parallel with the data lines.

[0050] Unless otherwise defined, technical terms or scientific terms used in the present disclosure shall be understood as common meanings by those ordinary skilled in the art to which the present disclosure relates. Terms such as "first" and "second" in the present disclosure are merely to distinguish different components rather than to indicate any sequence, quantity or importance. Similarly, terms such as "a" or "an" merely intends to indicate there exists at least one rather than to limit the quantity. Terms such as "connected to" or "coupled to" are not limited to physical or mechanical connections and may further include either direct electrical connections or indirect electrical connec-

tions. Terms such as "above", "below", "left" and "right" merely indicate relative position relationships, and in a case that an absolute position of a described object changes, the relative position relationships with respect to the described object change accordingly.

[0051] Optional embodiments of the present disclosure are described hereinabove. It should be noted that the ordinary skilled in the art can make various improvements and polishment without departing from the principle of the disclosure, and those improvements and polishment all fall within the protection scope of the present disclosure.

- 1. An array substrate, comprising: transparent common electrodes;

- a plurality of first common electrode lines; and

- a plurality of second common electrode lines;

wherein the plurality of first common electrode lines intersects with the plurality of second common electrode lines to define grids, the plurality of first common electrode lines is connected with the common electrodes through first viaholes and the plurality of second common electrode lines is connected with the common electrodes through second via-holes.

- 2. The array substrate according to claim 1, wherein the plurality of first common electrode lines are in a different layer from the plurality of second common electrode lines.

- 3. The array substrate according to claim 2, further comprising a plurality of gate lines, wherein the plurality of first common electrode lines are in an identical layer to and in parallel with the plurality of gate lines.

- **4.** The array substrate according to claim **3**, further comprising a plurality of data lines, wherein the plurality of second common electrode lines are in an identical layer to and in parallel with the plurality of data lines.

- 5. The array substrate according to claim 4, wherein the array substrate is a double-gate-line type array substrate, two of the plurality of gate lines are between every two adjacent rows of subpixels, one of the plurality of data lines is provided every two adjacent columns of subpixels, and one of the plurality of second common electrode lines is between every two columns of subpixels where no data line is provided.

- 6. The array substrate according to claim 2, wherein the common electrodes for respective subpixels are arranged separately, the common electrodes at an identical row are connected with each other through one of the plurality of first common electrode lines, and the common electrodes at an identical column are connected with each other through one of the plurality of second common electrode lines.

- 7. The array substrate according to claim 1, wherein each of the plurality of first via-holes is deeper than each of the plurality of second via-hole.

- 8. The array substrate according to claim 1, further comprising a base substrate, a gate insulating layer, a pixel electrode and an insulating layer; wherein

the plurality of first common electrode lines are on the base substrate;

the gate insulating layer is on the base substrate and covers the plurality of first common electrode lines; the pixel electrode and the plurality of second common electrode lines are on the gate insulating layer;

- the insulating layer is on the gate insulating layer and covers the pixel electrode and the plurality of second common electrode lines;

- the transparent common electrodes are on the insulating laver:

- the plurality of first via-holes extend through the insulating layer and the gate insulating layer; and

- the plurality of second via-holes extend through the insulating layer.

- 9. A display panel, comprising the array substrate according to claim 1.

- 10. A display device, comprising the display panel according to claim 9.

- 11. A method for manufacturing an array substrate, comprising:

forming grids by intersecting a plurality of first common electrode lines with a plurality of second common electrode lines; and

forming transparent common electrodes, the plurality of first common electrode lines and the plurality of second common electrode lines in a way that the plurality of first common electrode lines are connected with the transparent common electrodes through first via-holes and the plurality of second common electrode lines are connected with the transparent common electrodes through second via-holes.

- 12. The method for manufacturing the array substrate according to claim 11, wherein the plurality of first common electrode lines are in a different layer from the plurality of second common electrode lines.

- 13. The method for manufacturing the array substrate according to claim 12, wherein the forming the transparent common electrodes, the plurality of first common electrode lines and the plurality of second common electrode lines comprises: forming the plurality of first common electrode lines and a plurality of gate lines in parallel with the plurality of first common electrode lines through one patterning process.

- 14. The method for manufacturing the array substrate according to claim 13, wherein the forming the transparent common electrodes, the plurality of first common electrode lines and the plurality of second common electrode lines comprises: forming the plurality of second common electrode lines and a plurality of data lines in parallel with the plurality of second common electrode lines through one patterning process.

- 15. The array substrate according to claim 2, further comprising a plurality of data lines, wherein the plurality of second common electrode lines are in an identical layer to and in parallel with the plurality of data lines.

- 16. The method for manufacturing the array substrate according to claim 12, wherein the forming the transparent common electrodes, the plurality of first common electrode lines and the plurality of second common electrode lines comprises: forming the plurality of second common electrode lines and a plurality of data lines in parallel with the plurality of second common electrode lines through one patterning process.

\* \* \* \* \*