US011769738B2

# (12) United States Patent Kirby et al.

#### (54) APPARATUSES EXHIBITING ENHANCED STRESS RESISTANCE AND PLANARITY, AND RELATED MICROELECTRONIC DEVICES AND MEMORY DEVICES

(71) Applicant: **Micron Technology, Inc.**, Boise, ID

(72) Inventors: **Kyle K. Kirby**, Boise, ID (US); **Chao Wen Wang**, Central Taiwan Science

Park (TW)

(73) Assignee: **Micron Technology, Inc.**, Boise, ID

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 101 days.

(21) Appl. No.: 17/339,560

(22) Filed: Jun. 4, 2021

(65) Prior Publication Data

US 2021/0296289 A1 Sep. 23, 2021

#### Related U.S. Application Data

- (62) Division of application No. 16/554,986, filed on Aug. 29, 2019, now Pat. No. 11,056,443.

- (51) Int. Cl. H01L 23/00 (2006.01) H01L 23/528 (2006.01) (Continued)

- (52) **U.S. Cl.**CPC ....... *H01L 23/562* (2013.01); *H01L 21/4875* (2013.01); *H01L 21/56* (2013.01); (Continued)

# (10) Patent No.: US 11,769,738 B2

(45) **Date of Patent:** Sep. 26, 2023

## (58) Field of Classification Search

CPC ...... H01L 23/562; H01L 2225/06513 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

7,531,407 B2 5/2009 Clevenger et al. 7,615,411 B2 11/2009 Jobetto (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 109994446 A 7/2019 CN 110137144 A 8/2019

#### OTHER PUBLICATIONS

Chinese First Office Action for Application No. 202010870053.4, dated Aug. 16, 2021, 16 pages with English Translation.

Primary Examiner — Farun Lu (74) Attorney, Agent, or Firm — TraskBritt

#### (57) ABSTRACT

An apparatus comprises conductive segments comprising an uneven topography comprising upper surfaces of the conductive segments protruding above an upper surface of underlying materials, a first passivation material substantially conformally overlying the conductive segments, and a second passivation material overlying the first passivation material. The second passivation material is relatively thicker than the first passivation material. The apparatus also comprises structural elements overlying the second passivation material. The second passivation material has a thickness sufficient to provide a substantially flat surface above the uneven topography of the underlying conductive segments at least in regions supporting the structural elements. Microelectronic devices, memory devices, and related methods are also disclosed.

#### 20 Claims, 10 Drawing Sheets

# US 11,769,738 B2 Page 2

| (51) | Int. Cl.                                                 |           | (56)                               | References Cited |                               |

|------|----------------------------------------------------------|-----------|------------------------------------|------------------|-------------------------------|

|      | H01L 23/31                                               | (2006.01) | II C                               | DATENIT          | DOCUMENTS                     |

|      | H01L 23/29                                               | (2006.01) | 0.3                                | o. PAIENI        | DOCUMENTS                     |

|      | H01L 25/065                                              | (2023.01) | 7,750,483 B1                       |                  | Lin et al.                    |

|      | H01L 21/74                                               | (2006.01) | 7,811,863 B1<br>7,923,304 B2       |                  | Lin et al.<br>Choi et al.     |

|      | H01L 21/56                                               | (2006.01) | 8,158,508 B2                       |                  | Lin et al.                    |

|      | H01L 21/48                                               | (2006.01) | 8,461,601 B2<br>8,999,816 B1       |                  | Herrmann<br>Holden et al.     |

|      | H01L 23/492                                              | (2006.01) | 9,269,646 B2                       |                  | Luo et al.                    |

|      | H01L 23/532                                              | (2006.01) | 9,460,966 B2                       |                  | Lei et al.                    |

|      | H01L 23/538                                              | (2006.01) | 9,773,719 B2<br>10,714,438 B2      |                  | Meinhold et al.<br>Ahn et al. |

|      | 11012 23/330                                             | (2000.01) | 10,847,447 B2                      | 11/2020          | Kim et al.                    |

|      |                                                          |           | 2011/0221057 A1                    | * 9/2011         | Lin H01L 21/78<br>438/114     |

| (52) | U.S. Cl.                                                 |           | 2013/0256878 A1                    | * 10/2013        | Hsu H01L 24/08                |

| ( )  | CPC H01L 21/743 (2013.01); H01L 23/291                   |           |                                    |                  | 257/737                       |

|      | (2013.01); <b>H01L 23/293</b> (2013.01); <b>H01L</b>     |           | 2014/0103520 A1<br>2015/0162346 A1 |                  | Kirby et al.<br>Choi et al.   |

|      | <b>23/3192</b> (2013.01); <b>H01L 23/4924</b> (2013.01); |           | 2017/0102340 A1<br>2017/0125369 A1 |                  |                               |

|      | H01L 23/528 (2013.01); H01L 23/5385                      |           | 2017/0372961 A1                    |                  |                               |

|      | (2013.01); <b>H01L 23/5386</b> (2013.01); <b>H01L</b>    |           | 2018/0164698 A1                    |                  |                               |

|      | 23/53214 (2013.01); H01L 23/53228                        |           | 2018/0342475 A1                    |                  |                               |

|      | (2013.01); <b>H01L</b> 25/0657 (2013.01); H01L           |           | 2019/0172725 A1                    | 6/2019           | Fay et al.                    |

|      | <i>2225/06513</i> (2013.01)                              |           | * cited by examin                  | ner              |                               |

FIG. 2A

FIG. 2B

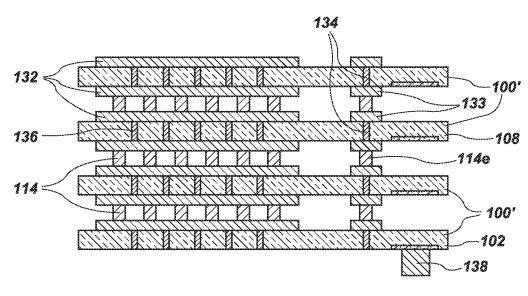

FIG. 5A

FIG. 5B

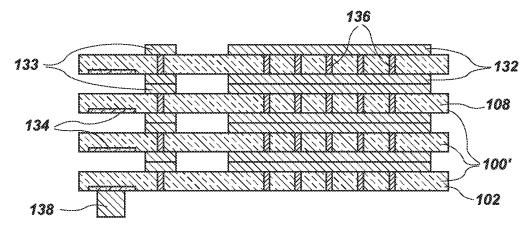

FIG. 5C

FIG. 5D

FIG. 6A

FIG. 68

FIG. 7A

FIG. 7B

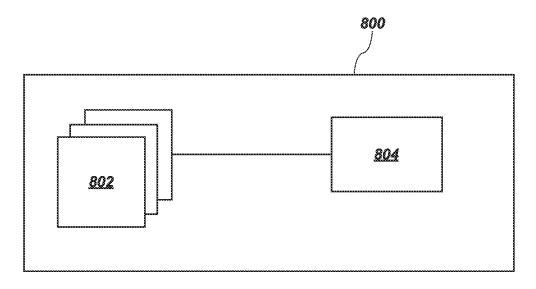

FIG. 8

FIG. 9

FIG. 10

### APPARATUSES EXHIBITING ENHANCED STRESS RESISTANCE AND PLANARITY, AND RELATED MICROELECTRONIC DEVICES AND MEMORY DEVICES

# CROSS-REFERENCE TO RELATED APPLICATION

This application is a divisional of U.S. patent application Ser. No. 16/554,986, filed Aug.  $29,\,2019$ , the disclosure of  $^{10}$  which is hereby incorporated herein in its entirety by this reference.

#### TECHNICAL FIELD

Embodiments of the disclosure relate to microelectronic devices and microelectronic device fabrication. More particularly, embodiments of the disclosure relate to an apparatus exhibiting enhanced stress resistance and planarity, and to related methods, memory devices, and electronic systems. <sup>20</sup>

#### BACKGROUND

Increased circuit density is an ongoing goal of manufacturers of microelectronic devices. One favored configuration 25 is three-dimensional (3D) assembly of vertically stacked semiconductor dice, at least some of which are interconnected electrically and the stacked die assembly being mechanically and electrically connected to higher level packaging, such as an interposer or other base material (e.g., 30 substrate) bearing conductive traces.

One configuration employing stacked dice is a Micropillar Grid Array Package ("MPGA"). Such a package comprises a stack of (for example four (4)) dynamic random access (DRAM) semiconductor memory dice vertically intercon- 35 nected with conductive pillars from an uppermost die to a lowermost die, and conductive pillars extending from the underside of the lowermost memory die for connection to a logic die or a System on a Chip (SoC) die. The provider of the logic die or the SoC die conventionally mounts their 40 device to an interposer, such as a ball grid array (BGA) substrate, the logic or SoC die including conductive pads for connection to the conductive pillars on the underside of the MPGA and through vias for connecting to the substrate. The MPGA is mounted to the logic die or SoC die on the 45 interposer and the assembly is then overmolded with an encapsulant into a finished Ball Grid Array (BGA) package. which configuration may be implemented as a so-called "Wide I/O" memory device, enabling fast memory access and reduced power requirements.

Further, as the MPGA die assembly incorporates a highspeed logic die below a vertical stack of DRAM dice interconnected with through-silicon vias (TSVs), the DRAM dice are configured specifically to only handle data, while the logic die provides all DRAM control within the die 55 assembly. The design reduces latency, and greatly improves bandwidth and speed, while offering significantly reduced power demand and physical space requirements and providing flexibility for multiple platforms and application through use of different logic dice. One such implementation of a die 60 assembly as described above may be characterized as a Memory Cube DRAM (MCDRAM) comprising a thermally conductive overmold over the DRAM dice and in contact with the logic die where it extends peripherally beyond the stack of DRAM dice. DRAM memory stacks may also 65 include double data rate (DDR) type synchronous DRAM (SDRAM) devices, such as double data rate type four

2

(DDR4), double data rate type five (DDR5), double data rate type six (DDR6), etc. Additional implementations of similar die assemblies may include Hybrid Memory Cube (HMC) and High Bandwidth Memory (HBM), the latter of which associates device logic with the DRAM die stack and separate host logic with a processor.

One significant concern with regard to implementation of such 3D semiconductor die assemblies is the issue of providing adequate stress distribution between base material (i.e., semiconductor dice) and overlying structures, often in the form of pillars protruding from active surfaces of the semiconductor dice and used to provide mechanical connections, thermal connections, or both, to another semiconductor die, interposer or other structure above or below semiconductor dice in a stack and to provide mechanical support between the various components in the stack. Further, design of mutually spaced metallization structures (e.g., conductive traces and pads) on the active surface and underlying the pillars is commonly governed by structural design and/or electrical performance of circuitry of a semiconductor die, without regard to subsequent placement of the pillars that overlie a passivation material between the metallization structures and the pillars. The spacing of such metallization structures results in an uneven topography on the active surface. In conventional devices, a substantially conformal and relatively thin passivation material located over the metallization structures for environmental protection and electrical isolation conforms to the uneven topography of the metallization structures and, so, may not be adequate to withstand stress applied by the pillars when a die stack is formed and electrically conductive elements thereof interconnected by, for example, thermocompression bonding. The thermocompression bonding process also applies force, and thus stress, to the pillars perpendicular to the major planes of the semiconductor dice in the stack and, thus, to the passivation material. In particular, random misalignment of the pillars relative to the underlying metal structures and consequent uneven stress distribution on the passivation material by the pillars may cause stress points, resulting in cracking of the passivation material and compromise integrity of the semiconductor die.

### BRIEF DESCRIPTION OF THE DRAWINGS

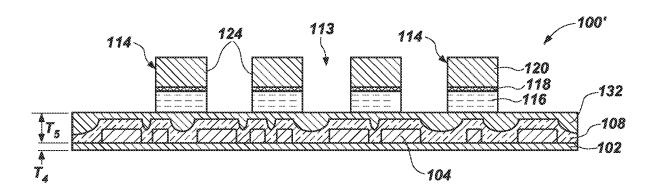

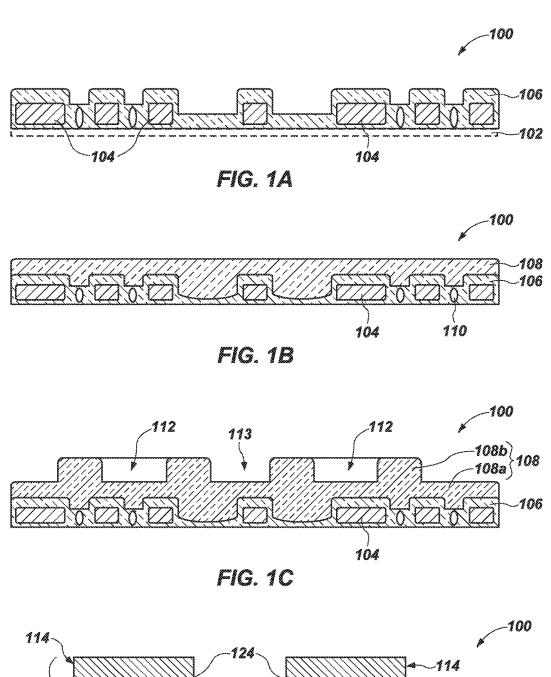

FIGS. 1A-1D are simplified, partial cross-sectional views illustrating various stages of forming a microelectronic device in accordance with embodiments of the disclosure:

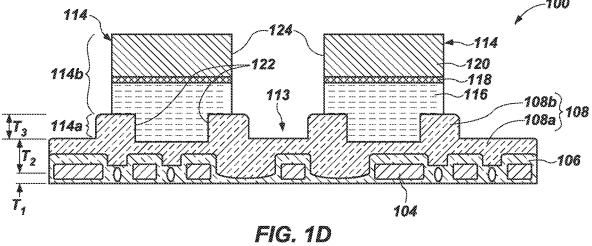

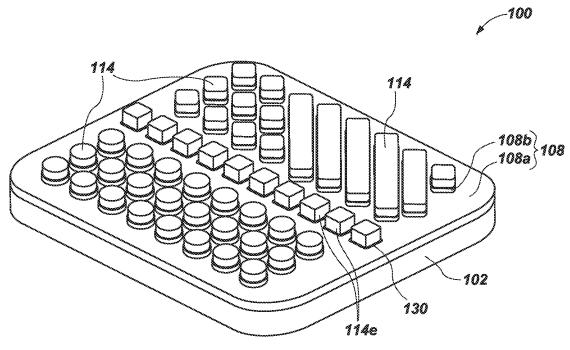

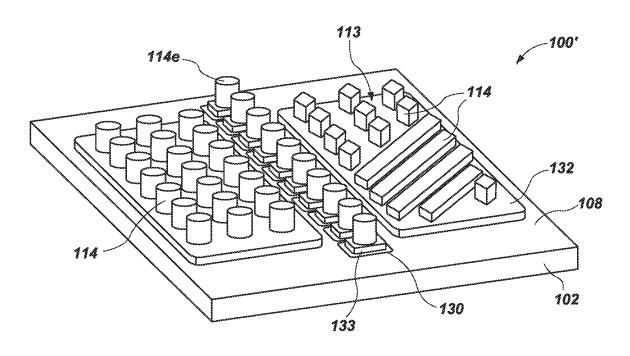

FIGS. **2**A-**2**B are simplified, perspective views illustrating various stages of forming the microelectronic device of FIG. **1**D in accordance with embodiments of the disclosure;

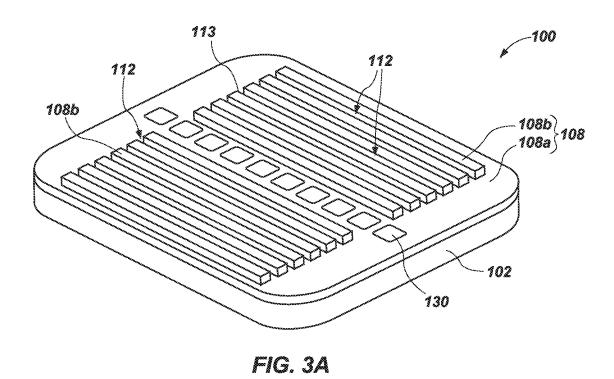

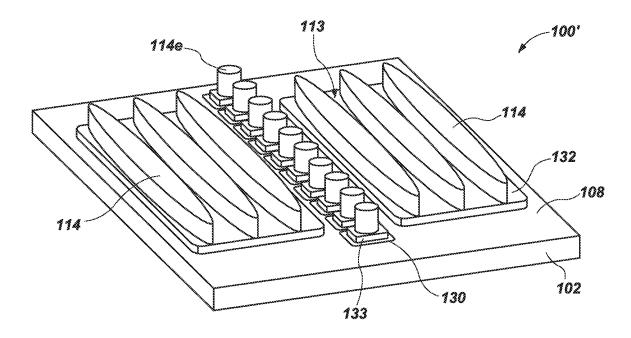

FIGS. 3A-3B are simplified, perspective views illustrating various stages of forming the microelectronic device of FIG. 1D in accordance with additional embodiments of the disclosure;

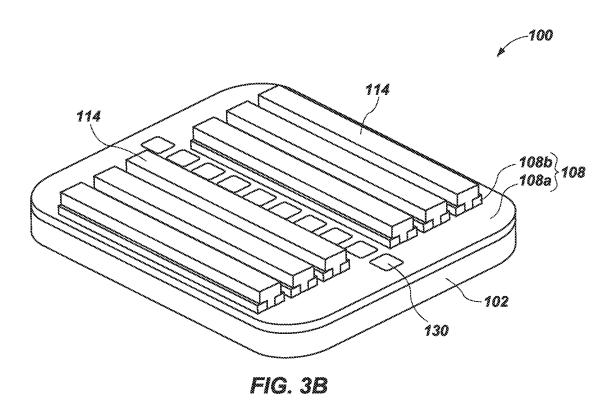

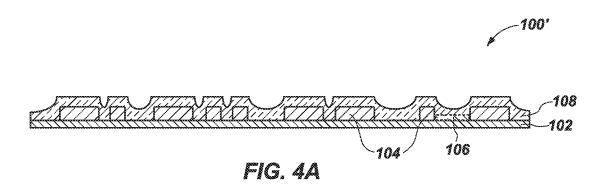

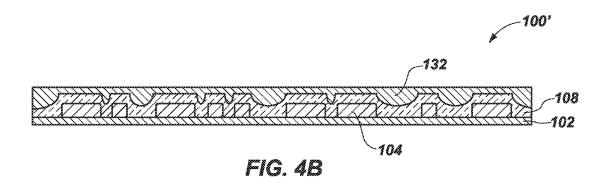

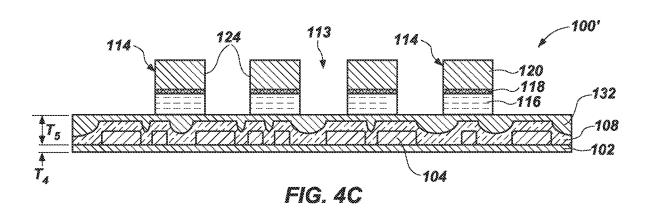

FIGS. 4A-4C are simplified, partial cross-sectional views illustrating various stages of forming a microelectronic device in accordance with additional embodiments of the disclosure:

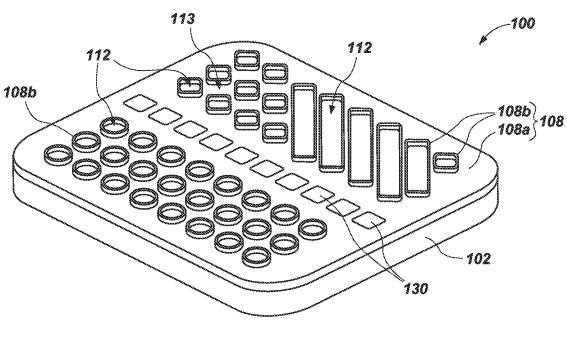

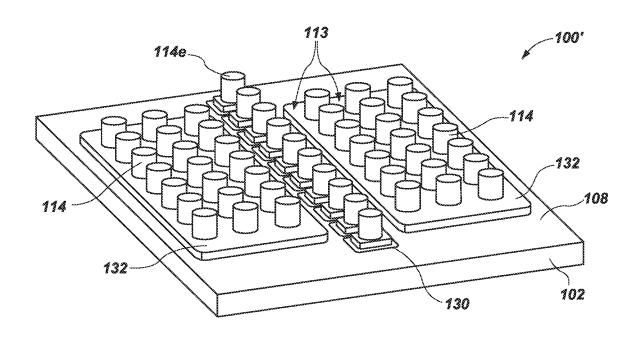

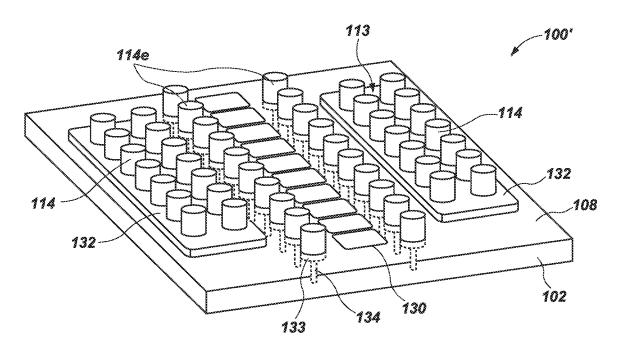

FIGS. 5A-5D are simplified, perspective views of the microelectronic device of FIG. 4C in accordance with additional embodiments of the disclosure;

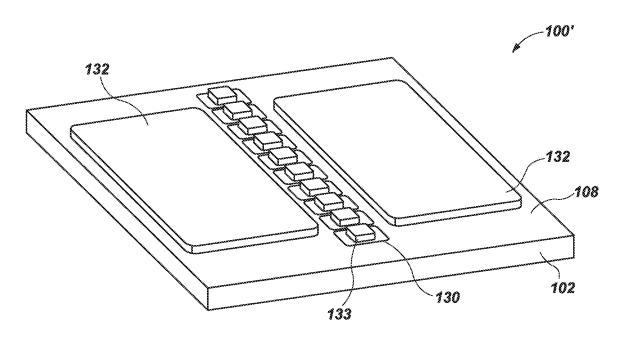

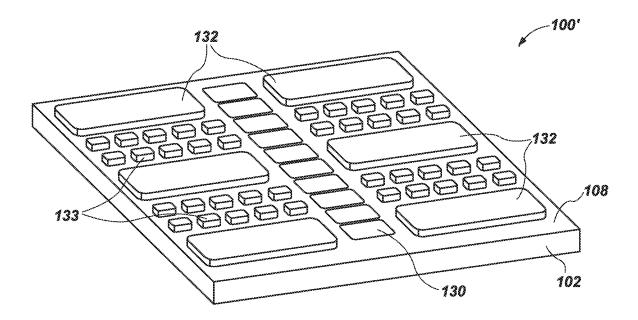

FIGS. 6A-6B are simplified, perspective views of the microelectronic device of FIG. 4C in accordance with additional embodiments of the disclosure;

FIGS. 7A-7B are simplified, partial cross-sectional views of the microelectronic device of FIG. 4C in accordance with additional embodiments of the disclosure;

FIG. 8 is a schematic block diagram illustrating a memory device including one or more of the microelectronic devices in accordance with embodiments of the disclosure:

FIG. 9 is a schematic block diagram of an electronic system, in accordance with embodiments of the disclosure; 5

FIG. 10 is a simplified, partial cross-sectional view of an exemplary microelectronic device.

#### DETAILED DESCRIPTION

A microelectronic device (e.g., an apparatus) includes conductive segments comprising an uneven topography comprising upper surfaces of the conductive segments protruding above an upper surface of underlying materials, a 15 dielectric material (e.g., a first passivation material) substantially conformally overlying the conductive segments, and another dielectric material (e.g., a second passivation material) overlying the first passivation material. The microelectronic device also includes protruding structural elements 20 overlying the second passivation material. The second passivation material may have a thickness sufficient to provide a substantially flat surface above an uneven topography of the underlying conductive segments at least in designated regions supporting the structural elements (e.g., regions 25 proximate to, immediately adjacent to, and/or directly underlying the structural elements) so as to distribute stress applied to the first passivation material, second passivation material and the underlying conductive segments by the structural elements. In some embodiments, the second pas- 30 sivation material may include a lower region and upper regions comprising support structures. Further, support structures (e.g., annular rings) of the upper regions of the second passivation material may comprise discrete portions in direct physical contact with portions of the structural 35 tions of one or more of the associated listed items. elements extending above the lower region. Alternatively, the structural elements may include one or more base plates overlying the passivation material and, optionally, protrusions from the base plates. The base plates may conform to the topography of the underlying passivation material yet 40 have a thickness sufficient to provide a substantially flat surface above the underlying conductive segments and to distribute stress applied by the protrusions, if present.

The following description provides specific details, such as material types, material thicknesses, and process condi- 45 tions in order to provide a thorough description of embodiments described herein. However, a person of ordinary skill in the art will understand that the embodiments disclosed herein may be practiced without employing these specific details. Indeed, the embodiments may be practiced in con- 50 junction with conventional fabrication techniques employed in the semiconductor industry. In addition, the description provided herein does not form a complete description of a microelectronic device or a complete process flow for manufacturing the microelectronic device and the structures 55 described below do not form a complete microelectronic device. Only those process acts and structures necessary to understand the embodiments described herein are described in detail below. Additional acts to form a complete microelectronic device may be performed by conventional tech- 60 niques.

The materials described herein may be formed by conventional techniques including, but not limited to, spin coating, blanket coating, chemical vapor deposition (CVD), atomic layer deposition (ALD), plasma enhanced ALD, 65 physical vapor deposition (PVD), electroplating, electroless plating, or furnace growth (e.g., diffusion). Further, forma-

tion processes may be performed continuously or as a batch process. Alternatively, the materials may be grown in situ. Depending on the specific material to be formed, the technique for depositing or growing the material may be selected by a person of ordinary skill in the art. The removal of materials may be accomplished by any suitable technique including, but not limited to, dry etching, wet etching, wet cleaning, abrasive planarization (e.g., chemical-mechanical planarization), or other known methods unless the context indicates otherwise.

Drawings presented herein are for illustrative purposes only, and are not meant to be actual views of any particular material, component, structure, device, or system. Variations from the shapes depicted in the drawings as a result, for example, of manufacturing techniques and/or tolerances, are to be expected. Thus, embodiments described herein are not to be construed as being limited to the particular shapes or regions as illustrated, but include deviations in shapes that result, for example, from manufacturing. For example, a region illustrated or described as box-shaped may have rough and/or nonlinear features, and a region illustrated or described as round may include some rough and/or linear features. Moreover, sharp angles that are illustrated may be rounded, and vice versa. Thus, the regions illustrated in the figures are schematic in nature, and their shapes are not intended to illustrate the precise shape of a region and do not limit the scope of the present claims. The drawings are not necessarily to scale. Additionally, elements common between figures may retain the same numerical designation.

As used herein, the singular forms "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise.

As used herein, "and/or" includes any and all combina-

As used herein, "about" or "approximately" in reference to a numerical value for a particular parameter is inclusive of the numerical value and a degree of variance from the numerical value that one of ordinary skill in the art would understand is within acceptable tolerances for the particular parameter. For example, "about" or "approximately" in reference to a numerical value may include additional numerical values within a range of from 90.0 percent to 110.0 percent of the numerical value, such as within a range of from 95.0 percent to 105.0 percent of the numerical value, within a range of from 97.5 percent to 102.5 percent of the numerical value, within a range of from 99.0 percent to 101.0 percent of the numerical value, within a range of from 99.5 percent to 100.5 percent of the numerical value, or within a range of from 99.9 percent to 100.1 percent of the numerical value.

As used herein, spatially relative terms, such as "beneath," "below," "lower," "bottom," "above," "upper," "top," "front," "rear," "left," "right," and the like, may be used for ease of description to describe one element's or feature's relationship to another element(s) or feature(s) as illustrated in the figures. Unless otherwise specified, the spatially relative terms are intended to encompass different orientations of the materials in addition to the orientation depicted in the figures. For example, if materials in the figures are inverted, elements described as "below" or "beneath" or "under" or "on bottom of" other elements or features would then be oriented "above" or "on top of" the other elements or features. Thus, the term "below" can encompass both an orientation of above and below, depending on the context in which the term is used, which will be evident to one of ordinary skill in the art. The materials may

be otherwise oriented (e.g., rotated 90 degrees, inverted, flipped) and the spatially relative descriptors used herein interpreted accordingly.

As used herein, the terms "vertical," "longitudinal," "horizontal," and "lateral" are in reference to a major plane 5 of a structure and are not necessarily defined by Earth's gravitational field. A "horizontal" or "lateral" direction is a direction that is substantially parallel to the major plane of the structure, while a "vertical" or "longitudinal" direction is a direction that is substantially perpendicular to the major 10 plane of the structure. The major plane of the structure is defined by a surface of the structure having a relatively large area compared to other surfaces of the structure.

As used herein, the term "configured" refers to a size, shape, material composition, and arrangement of one or 15 more of at least one structure and at least one apparatus facilitating operation of one or more of the structure and the apparatus in a pre-determined way.

As used herein, reference to an element as being "on" or "over" another element means and includes the element 20 being directly on top of, directly adjacent to (e.g., directly laterally adjacent to, directly vertically adjacent to), directly underneath, or in direct contact with the other element. It also includes the element being indirectly on top of, indirectly adjacent to (e.g., indirectly laterally adjacent to, 25 indirectly vertically adjacent to), indirectly underneath, or near the other element, with other elements present therebetween. In contrast, when an element is referred to as being "directly on" or "directly adjacent to" another element, there are no intervening elements present.

As used herein, the term "microelectronic device" includes without limitation a memory device, as well as other microelectronic devices which may or may not incorporate memory, such as a logic device, a processor device, or a radiofrequency (RF) device. Further, a microelectronic 35 device may incorporate memory in addition to other functions such as, for example, a so-called "system on a chip" (SoC) including a processor and memory, or a microelectronic device including logic and memory. As used herein, the term "memory device" means and includes a microelectronic device exhibiting memory functionality but not necessarily only memory functionality.

As used herein, the term "substantially" in reference to a given parameter, property, or condition means and includes to a degree that one of ordinary skill in the art would 45 understand that the given parameter, property, or condition is met with a degree of variance, such as within acceptable tolerances. By way of example, depending on the particular parameter, property, or condition that is substantially met, the parameter, property, or condition may be at least 90.0 percent met, at least 95.0 percent met, at least 99.0 percent met, at least 99.9 percent met, or even 100.0 percent met.

As used herein, the term "substrate" means and includes a material (e.g., a base material) or construction upon which additional materials are formed. The substrate may be a semiconductor substrate, a base semiconductor material on a supporting structure, a metal electrode, or a semiconductor substrate having one or more materials, layers, structures, or regions formed thereon. The materials on the semiconductor substrate may include, but are not limited to, semiconductive materials, insulating materials, conductive materials, etc. The substrate may be a conventional silicon substrate or other bulk substrate comprising a layer of semiconductive material. As used herein, the term "bulk substrate" means and includes not only silicon wafers, but also silicon-oninsulator ("SOT") substrates, such as silicon-on-sapphire ("SOS") substrates and silicon-on-glass ("SOG") substrates,

6

epitaxial layers of silicon on a base semiconductor foundation, and other semiconductor or optoelectronic materials, such as silicon-germanium, germanium, gallium arsenide, gallium nitride, and indium phosphide. The substrate may be doped or undoped.

FIGS. 1A through 1D illustrate a method of forming a microelectronic device in accordance with embodiments of the disclosure.

An apparatus 100 including mutually spaced conductive segments 104 is shown in FIG. 1A. The conductive segments 104 may be located adjacent (e.g., on or over) a base material 102 (e.g., a semiconductor die), as depicted in broken lines. More specifically, the conductive segments 104 may reside on the active surface of the semiconductor die. In some embodiments, the conductive segments 104 may be formed adjacent (e.g., on or over) the base material 102, if present. In other embodiments, the conductive segments 104 may be formed adjacent (e.g., on, directly on) underlying materials (e.g., metal materials and/or insulative materials). The conductive segments 104 may include, for example, conductive traces and pads overlying metal materials (not shown) including routing lines or electrical circuitry. Such materials underlying the conductive segments 104 may include various metal materials (e.g., copper) and insulative materials formed in one or more damascene processes, such as a single-damascene process or a dualdamascene process. Upper surfaces of metal materials and insulative materials formed by such a damascene process are coplanar. Thus, the materials underlying the conductive segments 104 may exhibit a substantially flat upper surface, over which the conductive segments 104 are formed.

The conductive segments 104 may be formed to exhibit any suitable thickness (e.g., a height of a top surface of the conductive segments 104 above a top surface of the underlying materials). By way of non-limiting example, at least some of the conductive segments 104 may be formed to a thickness of between about 5000 Angstroms (Å) and about 7000 Å, in some embodiments. In other embodiments, the conductive segments 104 may include metal portions within a redistribution layer (RDL). In other words, the conductive segments 104 may be embedded within insulative materials (e.g., a dielectric material) forming an RDL. In such embodiments, a total thickness of the RDL, including the conductive segments 104, may be between about 1 µm and about 10 μm, for example. Further, the conductive segments 104 may be mutually spaced from one another resulting in an uneven topography. The conductive segments 104 may be formed of a material including a metal, a metal alloy, or a metal-containing material. By way of example and not limitation, the conductive segments 104 may include aluminum or an alloy thereof.

A first passivation material 106 may be formed adjacent to (e.g., over) at least a portion of the conductive segments 104 and the base material 102. The first passivation material 106 may adapt to the uneven topography of the underlying conductive segments 104 in a substantially conformal manner. In some embodiments, one or more intermediate materials may, optionally, be formed between the first passivation material 106 and the conductive segments 104, such as anti-reflective coatings, barrier materials, etc., as is known in the art. In other embodiments, the first passivation material 106 may be in direct physical contact with the conductive segments 104.

In embodiments, a thickness of the first passivation material **106** may be sufficient to electrically isolate the conductive segments **104** from one another and provide environmental protection and electrical isolation from the

environment to the conductive segments. By way of non-limiting example, the first passivation material **106** may be formed to a thickness (e.g., average thickness) of between about 0.8  $\mu$ m and about 3  $\mu$ m, such as between about 0.8  $\mu$ m and about 2.3  $\mu$ m. In some embodiments, the first passivation material **106** may be formed to a thickness of about 2.3  $\mu$ m.

The first passivation material 106 may be formed of and include at least one dielectric material including, but not limited to, an oxide, a nitride, or an oxynitride. In particular, the first passivation material 106 may include, but is not limited to, an oxide material (e.g., a silicon oxide material) in some embodiments. Further, the first passivation material 106 may include one or more (e.g., two) portions of materials adjacent one another. For example, the first passivation material 106 may include a first portion (e.g., an oxide material) and a second portion (e.g., a silicon nitride material) overlying the first portion. By way of example and not limitation, the first portion may be formed to a thickness of about 1.5  $\mu$ m. In other embodiments, the first passivation material 106 may be a polyimide material.

The first passivation material **106** may be formed using one or more conventional deposition processes, such as one or more of a conventional ALD process and a conventional CVD process. The passivation material may be blanket deposited, and portions of the first passivation material **106** may then be removed (e.g., as by etching) to expose bond pads on the active surface of the semiconductor die by one or more of conventional etching processes, such as one or more of anisotropic dry etching and anisotropic wet etching, as is known in the art.

As shown in FIG. 1B, a second passivation material 108 may be formed adjacent (e.g., on or over) exposed surfaces of the first passivation material 106. As shown in FIG. 1B, the second passivation material 108 may substantially fill in and smooth an uneven topography defined by the surfaces (e.g., upper surfaces, side surfaces) of the first passivation 40 material 106 upon which the second passivation material 108 is formed. In other words, the second passivation material 108 may extend from and between side surfaces (e.g., sidewalls) of the first passivation material 106 as well as over upper, horizontal surfaces of the first passivation 45 material 106. In some embodiments, the second passivation material 108 may be in direct physical contact with the first passivation material 106. Further, the second passivation material 108 may be of sufficient thickness to form a substantially continuous, flat material surface over at least a 50 portion of the first passivation material 106. In other words, an upper surface of the second passivation material 108 may be substantially smooth and even, without marked (e.g., pronounced) protrusions and/or indentations. By way of non-limiting example, the upper surface of the second 55 passivation material 108 may have a surface roughness between about 15 nm and about 100 nm, such as between about 50 nm and about 100 nm, or between about 25 nm and about 50 nm, root mean square (RMS). One or more air gaps 110 may reside within portions of the first passivation 60 material 106. The air gaps 110 may laterally intervene between laterally-neighboring conductive segments 104 and serve as insulators (i.e., having a dielectric constant (k) of about 1). The air gaps 110 may limit capacitance (e.g., parasitic capacitance, stray capacitance) and increase shorts 65 margin between laterally-neighboring conductive segments 104, and may reduce cross-talk therebetween. However, the

8

air gaps 110 also comprise structural weak points in the first passivation material 106 which are particularly susceptible to stress cracking.

The second passivation material 108 may be formed to exhibit any suitable thickness. By way of non-limiting example, the second passivation material 108 may be formed to a thickness (e.g., average thickness) of between about 0.5 µm and about 10 µm, such as between about 0.8  $\mu$ m and about 2.3  $\mu$ m, between about 2.3  $\mu$ m and about 5  $\mu$ m, or between about 5 µm and about 10 µm. In some embodiments, the second passivation material 108 may be formed to a thickness of about 2.3 µm. Further, a combined thickness of the first passivation material 106 and the second passivation material 108 may be between about 1 µm and about 13 µm, for example. In some embodiments, the thickness (e.g., average thickness) of the second passivation material 108 may be relatively greater than the thickness (e.g., average thickness) of the first passivation material 106. In particular, the thickness of the second passivation material 108 may be between about 3 and 15 times (e.g., an order of magnitude) greater than the thickness of the first passivation material 106.

In some embodiments, the second passivation material 108 may be formed of and include at least one dielectric material including, but not limited to, an oxide, a nitride, or an oxynitride. In other embodiments, the second passivation material 108 may be formed of a polyimide material. Further, the second passivation material 108 may be formed of the same material as or formed of a different material from the first passivation material 106. By way of non-limiting example, the second passivation material 108 may be a nitride material (e.g., a silicon nitride or silicon oxynitride material) and the first passivation material 106 may be an oxide material (e.g., a silicon oxide material). In other words, the material of the second passivation material 108 may be formed of a different material having a different etch selectivity than that of the first passivation material 106. In other embodiments, each of the first passivation material 106 and the second passivation material 108 may be formed of the same material, such that there is no easily discernable physical interface therebetween. In yet other embodiments the conductive segments 104 may be covered to a desired thickness with a single passivation material, such as the second passivation material 108, for example. In such embodiments, the second passivation material 108 may be in direct physical contact with the conductive segments 104 and the base material 102 and be of a thickness to extend between, above and over the conductive segments 104 to a great enough height to comprise a substantially planar upper surface in designated regions.

The second passivation material 108 may be formed using conventional processes (e.g., conventional deposition processes, conventional material removal processes) and conventional processing equipment, which are not described in detail herein. For example, the second passivation material 108 may be formed on or over portions of the exposed surfaces of the apparatus 100 using one or more conventional deposition processes (e.g., a conventional CVD or PVD process, or by spin or blanket coating if a polyimide). In some embodiments, the second passivation material 108 may be subjected to at least one conventional planarization process (e.g., at least one conventional CMP process) after formation to facilitate or enhance the planarity of an upper boundary (e.g., upper surface) of the second passivation material 108. In such embodiments, portions of the second passivation material 108 may exhibit a substantially planar upper boundary (e.g., upper surface), and a non-planar lower

boundary substantially defined by the topography of the surface (e.g., upper surface) of the first passivation material 106

As shown in FIG. 1C, the second passivation material 108 may be formed to include separate portions including, for 5 example, a first portion (e.g., a lower region 108a) and a second portion (e.g., upper regions 108b). In some embodiments, the lower region 108a of the second passivation material 108 may be formed in one or more conventional processes, as discussed with reference to FIG. 1B, followed 10 by formation of the upper regions 108b in one or more subsequent conventional processes (e.g., additional conventional deposition processes and/or material removal processes). In other words, the lower region 108a may be formed in a first process and the upper regions 108b may be 15 formed in a second, separate process.

In other embodiments, the lower region 108a and the upper regions 108b may be formed in one or more conventional processes including a single deposition process and a single material removal process. In such embodiments, the 20 second passivation material 108 may be formed, following which portions thereof may be removed (e.g., patterned) using one or more conventional material removal processes (e.g., conventional photolithography processes, conventional etching processes). For example, a dielectric material 25 may be formed over the first passivation material 106 and may be patterned by conventional photolithography techniques to form the lower region 108a and the upper regions 108b of the second passivation material 108. For instance, a photoresist material (not shown) may be formed over the 30 dielectric material and patterned by conventional techniques, with the pattern in the photoresist material subsequently transferred to the dielectric material. A dry etch process may, for example, be used to form the upper regions **108**b. Alternatively, the upper regions **108**b may be formed 35 using a photosensitive polyimide material that may be patterned and developed. Such formation and removal processes may result in formation of support structures (e.g., protrusions, ridges, lips, collars, etc.) of the upper regions **108***b* extending above (e.g., substantially transverse to) an 40 upper surface of the lower region 108a of the second passivation material 108.

As shown in FIG. 1C, the upper regions 108b of the second passivation material 108 may be patterned and configured (e.g., sized, shaped, etc.) to facilitate placement 45 of structures to be formed thereon. In particular, the upper regions 108b may include openings 112 configured to receive structures (e.g., structural elements) therein, to be discussed in greater detail with reference to FIG. 1D. Further, the upper regions 108b may be separated by intermediary regions 113 comprising an upper surface of lower region 108a and located between adjacent structures of the upper regions 108b. In other words, adjacent portions of the upper regions 108b of the second passivation material 108 may be spaced apart by the intermediary regions 113, as 55 shown in FIG. 1C.

As shown in FIG. 1D, the apparatus 100 comprises one or more structural elements 114 in the form of a pillar, for example. The structural elements 114 may comprise thermally conductive elements and, incidentally, comprise an 60 electrically conductive material, for example, a metal material. The structural elements 114 may be formed within at least some of the openings 112 in the second passivation material 108 and defined by upper regions 108b. In particular, the structural elements 114 may be vertically and laterally supported by the upper regions 108b of the second passivation material 108. As shown in FIG. 1D, lower

10

portions 114a of the structural elements 114 may be positioned within (e.g., substantially laterally surrounded by) the upper regions 108b of the second passivation material 108, while upper portions 114b of the structural elements 114 may extend above an upper surfaces of the surrounding upper regions 108b without being laterally surrounded by the upper regions 108b. In other words, sidewalls 122 of the lower portions 114a of the structural elements 114 may be in direct physical contact with inner surfaces of the upper regions 108b, while sidewalls 124 of the upper portions 114b are entirely free of the second passivation material 108. Further, the upper portions 114b may exhibit a greater lateral extent than that of the lower portions 114a in some embodiments. In other words, the sidewalls 124 of the upper portions 114b may extend laterally beyond the sidewalls 122 of the lower portions 114a, such that the upper portions 114b overlay and are vertically supported by the upper regions 108b. In other embodiments, the lower portions 114a may have substantially the same diameter as that of the upper portions 114b, such that the sidewalls 122, 124 are substantially coplanar with one another and the upper portions 114bare laterally adjacent the upper regions 108b without overlying portions thereof. In either case, any stress applied by structural elements 114 is substantially distributed over the lower region 108a and the upper regions 108b of the second passivation material 108.

As discussed in greater detail with reference to FIG. 1C, portions of the second passivation material 108 may exhibit a substantially planar upper boundary, and a non-planar lower boundary partially defined by the topography of the surface of the first passivation material 106 and separated from the upper boundary. Thus, the lower region 108a of the second passivation material 108 may have a thickness sufficient to substantially smooth out the underlying uneven topography of the conductive segments 104 (e.g., smooth out abrupt topography changes between adjacent portions of the underlying conductive segments 104). In other words, portions of the lower region 108a of the second passivation material 108 may intervene between laterally adjacent portions of the conductive segments 104 and fill (e.g., substantially completely fill) recessed regions between the laterally adjacent portions of the first passivation material 106 over conductive segments 104.

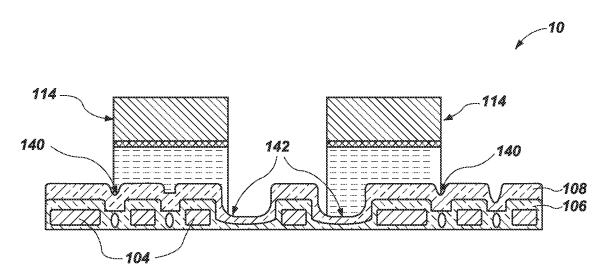

FIG. 10 shows a simplified, partial cross-sectional view of a conventional apparatus 10. In contrast to the apparatus 100 of FIG. 1D, the apparatus 10 of FIG. 10 shows the second passivation material 108 (if present) being formed conformally over the first passivation material 106 and the underling conductive segments 104 using conventional deposition processes and durations. In such embodiments, the second passivation material 108 is not formed to a thickness sufficient to provide a flat surface above topography of the conductive segments 104 and distribute regions of high stress applied to the first passivation material 106 and the second passivation material 108 by the structural elements 114. In particular, lateral sidewalls of the structural elements 114 of the embodiment of FIG. 10 may be randomly aligned with the uneven topography of the second passivation material 108 such that high stress points develop within recessed regions (e.g., small valleys 140 and large valleys 142) between laterally adjacent portions of the conductive segments 104. Such random misalignment of the structural elements 114 relative to the conductive segments 104 may result in passivation cracking due to inadequate support of the structural elements 114 occasioned by lack of sufficient stress distribution. FIG. 10 and the accompanying description thereof in this specification are provided to enhance an

understanding by one of ordinary skill in the art of embodiments of the disclosure, and are not admitted by the applicant as prior art for any purpose.

Returning to FIG. 1D, the second passivation material 108 of the apparatus 100, in contrast to that of the apparatus 10, 5 may have a thickness sufficient to more evenly distribute (e.g., spread out) stress applied to the second passivation material 108 by the structural elements 114 to provide adequate support to the structural elements 114. For example, high stress points along the base of the structural 10 elements 114 may be reduced (e.g., minimized) by increasing an effective surface area between the second passivation material 108 and the lower portions 114a of the structural elements 114 using the relatively thicker lower region 108a as well as the upper regions 108b. In particular, the first 15 passivation material 106 may be formed to a first thickness  $T_1$ , the lower region 108a may be formed to a second thickness  $T_2$  greater than the first thickness  $T_1$ , and the upper regions 108b may be formed to a third thickness T<sub>3</sub>, as shown in FIG. 1D. In some embodiments, the second 20 thickness T<sub>2</sub> may be greater than each of the first thickness  $T_1$  and the third thickness  $T_3$ . In other embodiments, the third thickness T<sub>3</sub> may be greater than each of the first thickness T<sub>1</sub> and the second thickness T<sub>2</sub>. Further, the second thickness T2 of the lower region 108a and/or the third 25 thickness T<sub>3</sub> of the upper regions 108b of the second passivation material 108 may be formed to be independent (e.g., entirely independent) or, alternatively, at least partially dependent on sizes and shapes of the conductive segments 104 (e.g., heights, widths, and/or lateral distances therebe- 30 tween).

In some embodiments, the structural elements 114 may include solder bumps or solder balls. In other embodiments, the structural elements 114 may be individual pillars including a single conductive material, such as copper, or a 35 conductive material capped by solder. For example, the structural elements 114 may comprise a conductive material 116 (e.g., copper), a barrier material 118 (e.g., a nickel material) thereover, and a solder material 120, such as a SnAg solder, over the barrier material 118, as shown in FIG. 40 1D. The conductive material 116 may be formed using a conventional electroplating process, for example, to a thickness (e.g., height) of between about 5 µm and about 15 µm. Further, the barrier material 118 may be formed (e.g., electroplated) to a thickness of between about 3 µm and 45 about 5 µm. The barrier material 118 may be employed, in some embodiments, as a barrier layer to prevent formational of intermetallic compounds between the conductive material 116 and the tin of solder material 120. The solder material 120 may be formed (e.g., electroplated) to a thickness of 50 between about 12 µm and about 15 µm, for example. Further, thicknesses of materials may be expressed relative to one another. By way of non-limiting example, a combined thickness of the first passivation material 106 and the second passivation material 108 may be between about 15 percent 55 and about 70 percent of a thickness of the structural elements 114, such as between about 20 percent and about 50 percent. Stated another way, a combined thickness of the first passivation material 106 and the second passivation material 108 may be between about 1 μm and about 4 μm less than 60 a thickness of the structural elements 114, for example.

One of ordinary skill in the art will appreciate, however, that respective thicknesses of each of the conductive material 116, the barrier material 118 and the solder material 120 of the structural elements 114 may correspond to the materials employed in fabrication of conductive elements to electrically interconnect stacked, TSV-equipped semicon-

12

ductor dice and a substrate so that the conductive elements and structural elements may be formed using the same processes. The relative thicknesses of various materials employed in structural elements 114 are not limiting of implementation of embodiments of the disclosure, nor is it a requirement that structural elements 114 must necessarily be fabricated at the same time as the aforementioned structural elements.

The structural elements 114 may comprise a substantially circular cross-sectional (e.g., cylindrical) shape having a diameter of between about 10  $\mu$ m and about 40  $\mu$ m, such as between about 15  $\mu$ m and about 30  $\mu$ m, for example. In some embodiments, the structural elements 114 may have a diameter of about 20  $\mu$ m. Further, specific requirements (e.g., materials, thicknesses, diameter, etc.) of the structural elements 114 may vary between structures of differing microelectronic devices. For example, semiconductor dice configured for use in a High Bandwidth Memory (HBM) device may include materials and/or dimensions of structural elements 114, as well as support structures (e.g., upper regions 108b of the second passivation material 108) designed to accommodate such memory devices.

While two structural elements 114 are shown in FIG. 1D for clarity, any number of structural elements 114 may be formed in a repeating pattern (e.g., an array). While each of the two structural elements 114 is shown as having a substantially circular cross-sectional shape, the structural elements 114 may have any suitable transverse cross-sectional shape such as, for example, a square cross-sectional shape, an elliptical cross-sectional shape, or a triangular cross-sectional shape. In some embodiments, the structural elements 114 may have a rectangular cross-sectional shape, such as slash marks or elongated bars, for example.

Alternatively or additionally, the conductive segments 104 may be configured (e.g., sized, shaped, and/or located) in predetermined patterns within the apparatus 100. In particular, while design of the conductive segments 104 (e.g., conductive traces and pads) is commonly governed by structural design and/or electrical performance of an individual circuit, the conductive segments 104 may be intentionally designed so as to be arranged in predetermined patterns within designated locations that are based, at least in part, on subsequent placement of the structural elements 114. In other words, a desired topography suitable for placement of the structural elements 114 may be obtained by selectively arranging the underlying conductive segments 104, such that the resulting topography provides enhanced structural support to the structural elements 114 by reducing or eliminating potential high stress points. By way of example and not limitation, regions that are more densely packed with the conductive segments 104 may be suitable locations for subsequent placement of at least some of the structural elements 114. In particular, the conductive segments 104 may be configured to be positioned under (e.g., in direct vertical alignment with) the structural elements 114 upon formation thereof to provide additional stability to the structural elements 114 and to avoid stress points between the conductive segments 104 that may result in cracking of the first passivation material 106 and/or the second passivation material 108. Further, the conductive segments 104 may be configured such that recessed regions between laterally adjacent portions of the conductive segments 104 are not in vertical alignment with lateral side surfaces of the structural elements 114. In addition, portions of the conductive segments 104 may be strategically positioned to be vertically aligned with the structural elements 114 for enhanced thermal conductivity therebetween, in addition to

providing increased structural stability. In other words, at least some of the structural elements 114 may comprise thermal elements that are in direct vertical alignment with the underlying conductive segments 104 (e.g., cell plates). Further, thicknesses of the second passivation material 108 including the upper regions 108b thereof may be based, at least in part, on placement of the underlying conductive segments 104.

FIGS. 2A through 3B show the apparatus 100 after multiple process acts described above have been conducted. 10 For example, the apparatus 100 includes the lower region 108a of the second passivation material 108 having a thickness sufficient to substantially smooth out underlying topography of the conductive segments 104 as well as patterned regions of the upper regions 108b thereof to 15 provide adequate support to the structural elements 114. In particular, the differing thicknesses of the passivation materials, including the lower region 108a and the upper regions 108b of the second passivation material 108, provides an optimized thickness of the passivation materials such that 20 stress points are reduced along the margins, for example, along an outer perimeter of bases of the structural elements 114 with minimal reduction in thermal conductivity. Further, as noted above, placement of the conductive segments 104 in predetermined patterns may be based at least in part on 25 subsequent placement of the structural elements 114 in order to further reduce occurrences of passivation cracking.

As shown in FIG. 2A in combination with FIG. 2B, the apparatus 100 comprises the second passivation material 108 overlying the base material 102. For clarity and convenience, the conductive segments 104 and the first passivation material 106 have been removed from the perspective views of FIGS. 2A and 2B (as well as from the perspective views of FIGS. 3A and 3B) although it is to be understood that the conductive segments 104 and the first passivation 35 material 106 may be included in a fully assembled apparatus 100. Conductive pads 130 (e.g., probe pads, through-silicon via (TSV) pads, micro pad interconnect regions, etc.) may be formed on or over the base material 102 in one or more rows. As discussed above, portions of the materials (e.g., the 40 second passivation material 108) may be removed (e.g., recessed) to expose portions of the conductive pads 130.

As shown in FIG. 2A, the lower region 108a of the second passivation material 108 may be of sufficient thickness to cover (e.g., substantially entirely cover) and smooth out the 45 underlying uneven topography, such that portions of the second passivation material 108 may exhibit a substantially planar upper boundary (e.g., upper surface). As best shown in the perspective views of FIGS. 2A and 2B, the upper regions 108b of the second passivation material 108 may be 50 patterned to accommodate placement of the structural elements 114. For example, the openings 112 may be defined within portions of the upper regions 108b that are configured (e.g., sized and shaped) to receive the structural elements 114, as shown in FIG. 2B. Further, the upper regions 108b 55 may be separated by the intermediary regions 113 located between adjacent portions thereof. Further, placement of the structural elements 114 may be based, at least in part, on placement of features within the apparatus 100. For example, at least some of the structural elements 114 may 60 include thermal pillars as well as substantially mechanical support pillars positioned flanking a central region (e.g., spine) of the base material 102 to provide one or more of enhanced thermal conductivity, uniform support, and bond line linearity when components are stacked. In other words, 65 an increased number (e.g., higher concentrations) of the structural elements 114 may be positioned within or proxi14

mate to regions prone to excessive heat generation, warpage, or both. At least some of the structural elements 114 may include thermal pillars overlying (e.g., in direct vertical alignment with) the conductive segments 104 while being electrically isolated from circuitry (e.g., upper metal portions, bond pads, etc.) thereof. In embodiments, the structural elements 114 are of the same height and comprise the same material or materials as conductive elements 114e (e.g., electrical pillars) positioned on or over the conductive pads 130 to provide electrical connection to circuitry of the apparatus 100, as shown in FIG. 2B.

In some embodiments, the upper regions 108b may each be formed to comprise a substantially circular cross-sectional (e.g., annular) shape, as shown in the lower, left-hand portion of the perspective view of FIG. 2A. In such embodiments, an inner diameter of the upper regions 108b may be sized and shaped to correspond to an outer diameter of the lower portions 114a (FIG. 1D) of the structural elements 114 having a substantially cylindrical cross-sectional shape with an outer diameter of the structural element being between the inner and outer diameters of the upper regions 108b, for example. In other embodiments, the upper regions 108b may be formed to comprise a substantially square outer crosssectional shape, as shown in the upper, right-hand portion of FIG. 2A. In such embodiments, individual portions of the upper regions 108b may be discrete and separated by the intermediary regions 113 or, alternatively, individual portions of the upper regions 108b may be continuous (e.g., without separation) in a lattice-shaped structure, for example. In yet other embodiments, the upper regions 108b may be formed to comprise a substantially rectangular cross-sectional shape in the form of an elongated bar, as shown in the lower, right-hand portion of FIG. 2A. Further, a longitudinal axis of such elongated bars may be oriented at an acute angle (e.g., a 45-degree angle) with respect to a longitudinal axis of one or more rows of the conductive pads 130, as shown in FIG. 2A. While the apparatus 100 is illustrated in FIGS. 2A and 2B as comprising an assortment of shapes and sizes of the upper regions 108b, it may be understood that such an assortment is shown for illustrative purposes only and that any configuration of the apparatus 100 including patterns of the upper regions 108b may include uniform sizes and shapes.

Further, the features and feature configurations (e.g., shapes) described above in relation to FIGS. 2A and 2B may be adapted to design needs of specific microelectronic devices (e.g., memory devices). In particular, FIGS. 3A and 3B show simplified, perspective views of the apparatus 100 having a different configuration than that depicted in FIGS. 2A and 2B.

As shown in FIG. 3A in combination with FIG. 3B, the apparatus 100 similarly comprises the second passivation material 108 overlying the base material 102 and the conductive pads 130 formed thereover in one or more rows. Similarly, the lower region 108a of the second passivation material 108 may be of sufficient thickness to cover (e.g., substantially entirely cover) and smooth out the underlying uneven topography, such that portions of the second passivation material 108 may exhibit a substantially planar upper boundary (e.g., upper surface). As shown in the perspective views of FIGS. 3A and 3B, the upper regions 108b may also be patterned to accommodate placement of the structural elements 114. In particular, the upper regions 108b may be formed to comprise a substantially rectangular cross-sectional shape. In such embodiments, pairs of parallel elongated bars of the rectangular-shaped portions of the upper regions 108b may be separated by the intermediary regions

113 located between adjacent pairs and having the openings 112 between two adjacent elongated bars of the upper regions 108b. In other words, elongated bars of the structural elements 114 may be supported on opposing sides by elongated segments of the second passivation material 108. 5 Further, a longitudinal axis of the elongated bars of the upper regions 108b may be oriented substantially parallel to the longitudinal axis of the one or more rows of the conductive pads 130, as shown in FIG. 3A. Alternatively, the longitudinal axis of the elongated bars of the structural elements 10 114 may be oriented substantially transverse (e.g., perpendicular) to the longitudinal axis of the one or more rows of the conductive pads 130 or oriented at an acute angle thereto. As in the previous embodiments, the structural elements 114 may be formed within the openings 112 of the 15 upper regions 108b and extend above the openings 112 and at least partially laterally over the adjacent elongated bars of the upper regions 108b, as shown in the perspective view of FIG. 3B. Thus, the structural elements 114 may be elongated, continuous portions in the embodiment of FIGS. 3A 20 and 3B. To complete formation of the apparatus 100 including the patterned regions of the second passivation material 108, additional materials may be formed on or over the second passivation material 108, the structural elements 114, and/or the conductive pads 130 by conventional techniques, 25 which are not described in detail herein.

Numerous advantages are achieved by utilizing the process described above to form the apparatus 100. By utilizing patterned support structures of the upper regions 108b of the second passivation material 108, increased reliability may be achieved by providing enhanced adhesion of and support for the structural elements 114 as well as by reducing passivation cracking. For example, stress risers (e.g., locations of concentrated stress) along the base of the structural elements 114, may be reduced by increasing an effective 35 surface area between the second passivation material 108 and the lower portions 114a of the structural elements 114 using the upper regions 108b. Thus, force may be more evenly distributed (e.g., equalized) around a perimeter and along sidewalls of the structural elements 114, resulting in 40 potential stress points being raised well above a potentially damaging level. In addition, thermal performance may be improved by enabling placement of the structural elements 114 (e.g., thermal pillars) over designated locations within the apparatus 100 (e.g., over cell plates) without consider- 45 ation of underlying topography. Alternatively or additionally, the conductive segments 104 may be positioned in predetermined patterns based at least in part on subsequent placement of the structural elements 114 in order to further reduce occurrences of passivation cracking. Further, forma- 50 tion of materials (e.g., the second passivation material 108) having specific thicknesses to provide a planar surface above base material 102 of apparatus 100 may provide simplified fabrication processes to enhance the planarity among the structural elements 114, for example. In particular, structural 55 elements 114 may be more repeatably processed (e.g., electroplated) at the same time to reliably achieve a coplanar profile, resulting in a more linear bondline.

Accordingly, a method of forming a microelectronic device is disclosed. The method comprises forming mutually spaced conductive segments, forming a first passivation material having a first thickness adjacent the conductive segments, and forming a second passivation material having a second, greater thickness adjacent the first passivation material. The second passivation material may have a thickness sufficient to provide a substantially flat surface above at least a portion of an uneven topography associated with the

16

mutually spaced conductive segments protruding above an upper surface of underlying materials. The method also comprises forming a patterned surface structure in upper regions of the second passivation material, and forming structural elements adjacent the second passivation material. The structural elements may be vertically and laterally supported by the patterned surface structure of the second passivation material.

Accordingly, an apparatus comprises conductive segments comprising an uneven topography comprising upper surfaces of the conductive segments protruding above an upper surface of underlying materials, a first passivation material substantially conformally overlying the conductive segments, and a second passivation material overlying the first passivation material. The second passivation material is relatively thicker than the first passivation material. The apparatus also comprises structural elements overlying the second passivation material. The second passivation material has a thickness sufficient to provide a substantially flat surface above the uneven topography of the underlying conductive segments at least in regions supporting the structural elements.

One of ordinary skill in the art will appreciate that, in accordance with additional embodiments of the disclosure, the features and feature configurations described above in relation to FIGS. 1A through 3B may be adapted to design needs of different microelectronic devices (e.g., different memory devices). By way of non-limiting example, in accordance with additional embodiments of the disclosure, FIGS. 4A through 7B show simplified, partial cross-sectional views and simplified, perspective views of an apparatus having a different configuration than the previous apparatus 100. Throughout the remaining description and the accompanying figures, functionally similar features (e.g., structures, devices) are referred to with similar reference numerals. To avoid repetition, not all features shown in the remaining figures (including FIGS. 4A through 7B) are described in detail herein. Rather, unless described otherwise below, a feature designated by a reference numeral of a previously-described feature (whether the previously described feature is first described before the present paragraph, or is first described after the present paragraph) will be understood to be substantially similar to the previously described feature.

Formation of an apparatus 100' including conductive segments 104 formed adjacent (e.g., on or over) the base material 102 (e.g., a semiconductor die) is shown in FIG. 4A. In some embodiments, the first passivation material 106 may, optionally, be formed adjacent to (e.g., vertically adjacent to and/or laterally adjacent to) at least a portion of the conductive segments 104 and the base material 102, similar to the apparatus 100 described above and depicted in FIG. 1A. Further, the second passivation material 108 may be formed adjacent the first passivation material 106, if present. In such embodiments, each of the first passivation material 106 and the second passivation material 108 may be formed of and include at least one dielectric material including, but not limited to, an oxide, a nitride, or an oxynitride or, alternatively, may be formed of a polyimide material. The second passivation material 108 may be formed of the same material as or formed of a different material from the first passivation material 106. By way of non-limiting example, the second passivation material 108 may be a nitride material (e.g., a silicon nitride or silicon oxynitride material) and the first passivation material 106 may be an oxide material (e.g., a silicon oxide material).

As in the previous embodiment, the second passivation material 108 may be formed adjacent (e.g., on or over) exposed surfaces of the first passivation material 106 in some embodiments. A thickness of the second passivation material 108 may be greater (e.g., substantially greater) than 5 a thickness of the underlying first passivation material 106, as discussed above in greater detail with reference to FIGS. 1B and 1D. In particular, the second passivation material 108 may at least partially (e.g., substantially) cover upper surfaces of the first passivation material 106 and extend from and between side surfaces (e.g., sidewalls) of the first passivation material 106 as well as over horizontal surfaces of the first passivation material 106. In such embodiments, the second passivation material 108 may be of a sufficient thickness to cover (e.g., substantially entirely cover) and 15 smooth out the underlying topography, such that portions of the second passivation material 108 may exhibit a substantially planar upper boundary (e.g., a substantially flat upper surface) at least in regions supporting the structural elements 114, such as, for example, in regions proximate to, imme- 20 diately adjacent to, or directly underlying the structural elements 114.

Alternatively, as shown in FIG. 4A, the second passivation material 108 of the present embodiment may be formed to have a lesser thickness, similar to that of the first 25 passivation material 106. In other words, the second passivation material 108 of the apparatus 100' may be formed using one or more conventional deposition processes, such as one or more of a conventional ALD process and a conventional CVD process. Further, the second passivation 30 material 108 may not include upper and lower regions (e.g., patterned regions) thereof in such embodiments. Rather, upper surfaces of the second passivation material 108 may exhibit a topography generally or in part similar to (e.g., based at least in part on) the underlying topography of the 35 conductive segments 104, as shown in FIG. 4A. In yet other embodiments, the apparatus 100' may include only one (e.g., a single) passivation material (e.g., the first passivation material 106 or the second passivation material 108) shown in subsequent figures, for illustrative purposes, as the second 40 passivation material 108.

As shown in FIG. 4B, a base plate 132 may be formed adjacent (e.g., on or over) exposed surfaces of the passivation materials (e.g., the first passivation material 106 and/or the second passivation material 108) of the apparatus 100'. 45 As shown in FIG. 4B, the base plate 132 may at least partially (e.g., substantially) fill in and smooth a topography defined by the surfaces (e.g., upper surfaces, side surfaces) upon which the base plate 132 is formed. In some embodiments, the base plate 132 may be formed over the first 50 passivation material 106 and may be used in lieu of the second passivation material 108 to fill in and smooth the underlying topography. In other words, the base plate 132 may at least partially (e.g., substantially) cover upper surfaces of the first passivation material 106 and extend from 55 and between side surfaces (e.g., sidewalls) of the first passivation material 106 as well as over horizontal surfaces of the first passivation material 106. In some embodiments, the base plate 132 may be in direct physical contact with the first passivation material 106. In other embodiment, inter- 60 vening materials (e.g., barrier materials, seed materials, etc.) may be located between the first passivation material 106 and the base plate 132. Further, the base plate 132 may form a substantially continuous, flat material surface over designated regions of the first passivation material 106 or the 65 second passivation material 108, if present. In other words, an upper surface of the base plate 132 may be substantially

smooth and even, without marked (e.g., pronounced) protrusions and/or indentations. By way of non-limiting example, the upper surface of the base plate 132 may have a surface roughness between about 15 nm and about 100 nm, such as between about 50 nm and about 100 nm, or between about 25 nm and about 50 nm, root mean square (RMS).

18

The base plate 132 may be formed to exhibit any desirable thickness. By way of non-limiting example, the base plate 132 may be formed to a thickness (e.g., average thickness) of between about 0.5 μm and about 2.5 μm, such as between about 0.75 µm and about 2 µm, or between about 1 µm and about 1.5 µm. In some embodiments, the base plate 132 may be formed to a thickness of about 1 µm or about 2 µm. Further, a combined thickness of the first passivation material 106, if present, the second passivation material 108, and the base plate 132 may be between about 1 µm and about 5 μm, for example. In some embodiments, the thickness (e.g., average thickness) of the second passivation material 108 may be relatively less than the thickness (e.g., average thickness) of the base plate 132. In particular, the second passivation material 108 may be formed to a fourth thickness T<sub>4</sub> and the base plate 132 may be formed to a fifth thickness T<sub>5</sub>, as shown in FIG. 4C. In some embodiments, the fifth thickness T<sub>5</sub> may be greater than the fourth thickness T<sub>4</sub>. In other embodiments, the fourth thickness T<sub>4</sub> may be greater than the fifth thickness T<sub>5</sub>. Further, the fourth thickness T<sub>4</sub> of the second passivation material 108 and/or the fifth thickness T<sub>5</sub> of the base plate 132 may be formed to be independent (e.g., entirely independent) or, alternatively, at least partially dependent on sizes and shapes of the conductive segments 104, including, for example, heights, widths, and lateral distances between laterally adjacent portions thereof.

The base plate 132 may be formed of and include a metal, a metal alloy, or a metal-containing material. The base plate 132 may include, but is not limited to, aluminum, copper, gold, iridium, iridium oxide, molybdenum, molybdenum nitride, nickel, platinum, ruthenium, ruthenium oxide, ruthenium titanium nitride, silver, tantalum, tantalum nitride, tantalum silicide, titanium, titanium nitride, titanium silicide, titanium aluminum nitride, titanium silicon nitride, tungsten, tungsten nitride, tungsten silicide, alloys thereof, or combinations thereof.

The base plate 132 may be formed using conventional processes (e.g., conventional deposition processes, conventional material removal processes) and conventional processing equipment, which are not described in detail herein. For example, the base plate 132 may be formed (e.g., electroplated) on a seed material located on or over portions of the exposed surfaces of the apparatus 100'. In some embodiments, the base plate 132 may be subjected to at least one conventional material removal process. For instance, a photoresist material (not shown) may be formed over the conductive material as deposited, and patterned by conventional techniques, with the pattern in the photoresist material subsequently transferred to the conductive material and the remainder removed. Alternatively, a photoresist material may be formed over the seed material and patterned to expose areas to be electroplated, the photoresist and seed material then subsequently being removed. In such embodiments, portions of the base plate 132 may exhibit a substantially planar upper boundary (e.g., upper surface), and a non-planar lower boundary partially defined by the topography of the surface (e.g., upper surface) of the second passivation material 108.

As shown in FIG. 4C, the apparatus 100' comprises one or more (e.g., an array) of the structural elements 114 in the

form of a pillar or a solder bump, for example. As in the previous embodiments, the structural elements 114 may comprise electrically conductive elements, thermally conductive elements, mechanical structures, or a combination thereof. In some embodiments, at least some of the structural 5 elements 114 may be a pillar comprising the conductive material 116, the barrier material 118, and/or the solder material 120, for example, as discussed in greater detail with reference to FIG. 1D. Further, the structural elements 114 may be formed of the same material as or formed of a 10 different material from the base plate 132. By way of non-limiting example, the structural elements 114 may comprise the conductive material 116 (e.g., a copper material) underlying the barrier material 118 and the solder material 120 and the base plate 132 may comprise the same conduc- 15 tive material (e.g., the copper material) as that of the lowermost material of the structural elements 114. Alternatively, the structural elements 114 may comprise a first conductive material (e.g., a copper material) and the base plate 132 may comprise a second, different conductive 20 material (e.g., a nickel material). Further, the structural elements 114 may be physically connected to the base plate 132. In some embodiments, the structural elements 114 may be in direct physical contact with the base plate 132. In other embodiments, one or more intervening materials (e.g., bar- 25 rier materials) may be located between a bottom surface of the structural elements 114 and an upper surface of the base plate 132.

In some embodiments, the base plate 132 may be formed in one or more conventional processes followed by forma- 30 tion of the structural elements 114 in one or more additional processes (e.g., conventional deposition processes and/or material removal processes). In other words, the base plate 132 may be formed in a first process and the structural elements 114 may be formed in a second, separate process, 35 for example, concurrently with the formation of conductive elements to electrically interconnect the semiconductor die with other components. Alternatively, the base plate 132 and the structural elements 114 may be formed in one or more conventional processes including a single deposition process 40 followed by one or more material removal processes, for example. In such embodiments, a conductive material may be formed at an initial thickness that is greater than a final combined thickness of the base plate 132 and the structural elements 114. Thereafter, portions of the conductive material 45 may be removed (e.g., patterned) using one or more conventional material removal processes (e.g., conventional photolithography processes, conventional etching processes). Such formation and/or removal processes (e.g., patterning and etching processes) may result in formation of 50 the base plate 132 underlying the structural elements 114 extending above (e.g., substantially transverse to) an upper surface of the base plate 132. Alternatively, the base plate 132 may be formed, as by electroplating, and then masked to selectively expose portions of the base plate 132 for 55 additional electroplating. In some embodiments, a thickness (e.g., average thickness) of the structural elements 114 may be relatively greater than a thickness (e.g., average thickness) of the base plate 132. In other embodiments, the thickness (e.g., average thickness) of the structural elements 60 114 may be relatively less than or, alternatively, equal to the thickness (e.g., average thickness) of the base plate 132.

As in the previous embodiment, the structural elements 114 may comprise a substantially circular cross-sectional shape or, alternatively, the structural elements 114 may 65 comprise any one of, or a combination of, a square cross-sectional shape, an elliptical cross-sectional shape, a trian-

20

gular cross-sectional shape, or a rectangular cross-sectional shape (e.g., slash marks or elongated bars). Further, the structural elements 114 located adjacent one another may be separated by the intermediary regions 113. However, rather than being adjacent to and being supported by portions of the second passivation material 108, the structural elements 114 may be adjacent to and be only supported by the base plate 132.