## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2022/0310515 A1

Sep. 29, 2022 (43) **Pub. Date:**

### (54) SEMICONDUCTOR DEVICE AND A DATA STORAGE SYSTEM INCLUDING THE SAME

(71) Applicant: SAMSUNG ELECTRONICS CO., LTD., Suwon-si (KR)

Inventors: Jaeshin LEE, Hwaseong-si (KR); Sunil SHIM, Seoul (KR); Juyoung LIM,

Seoul (KR)

(21) Appl. No.: 17/701,097

Filed: Mar. 22, 2022 (22)

(30)Foreign Application Priority Data

(KR) ..... 10-2021-0038071

#### **Publication Classification**

(51) **Int. Cl.** H01L 23/535 (2006.01)(2006.01)H01L 23/532 H01L 27/11582 (2006.01)H01L 27/11573 (2006.01)

## (52) U.S. Cl.

CPC ...... H01L 23/535 (2013.01); H01L 23/5329  $(2013.01); \textit{H01L 27/11582} \ (2013.01); \textit{H01L}$ 27/11573 (2013.01)

#### (57)ABSTRACT

A semiconductor device includes a structure including a stack structure including a first stack structure and a second stack structure on the first stack structure; a memory vertical structure penetrating the structure; a support vertical structure including a portion penetrating the structure and including an air gap; and a peripheral contact plug, wherein the first and second stack structures includes interlayer insulating layers and gate layers alternately stacked, a side of the memory vertical structure includes a slope changing portion, the peripheral contact plug includes an upper region disposed on a level higher than an upper surface of an uppermost gate layer, the upper region of the peripheral contact plug includes a first region, a second region and a connection region between the first and second regions, and the connection region has a slope different from a slope of at least one of the first and second regions.

FIG. 2C

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 3D

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 8A

FIG. 8B

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 11A

FIG. 11B

FIG. 12

FIG. 13

FIG. 15

FIG. 16C

FIG. 17

FIG. 19

# SEMICONDUCTOR DEVICE AND A DATA STORAGE SYSTEM INCLUDING THE SAME

## CROSS TO REFERENCE TO RELATED APPLICATION(S)

[0001] This application claims priority under 35 U.S.C. 119 to Korean Patent Application No. 10-2021-0038071 filed on Mar. 24, 2021 in the Korean intellectual Property Office, the disclosure of which is incorporated by reference herein in its entirety.

### TECHNICAL FIELD

[0002] Example embodiments of the present disclosure relate to a semiconductor device and a data storage system including the same.

#### DISCUSSION OF RELATED ART

[0003] There is increasing demand for a semiconductor device that offers higher-capacity storage potential than a semiconductor device including cells arranged two-dimensionally. Accordingly, a semiconductor device including memory cells arranged three-dimensionally, has been developed.

### **SUMMARY**

[0004] An example embodiment of the present disclosure is to provide a semiconductor device which may increase integration density and reliability.

[0005] An example embodiment of the present disclosure is to provide a data storage system including a semiconductor device.

[0006] According to an example embodiment of the present disclosure, a semiconductor device includes: a first structure; a second structure including a stack structure including a first stack structure on the first structure and a second stack structure on the first stack structure, and an intermediate insulating layer covering at least a portion of the stack structure; an insulating structure on the second structure; a memory vertical structure penetrating the second structure; a support vertical structure penetrating the second structure and including an air gap and a support layer defining at least a lower portion and a sidewall of the air gap; a peripheral contact plug penetrating the second structure; and gate contact plugs, wherein each of the first and second stack structures includes interlayer insulating layers and gate layers alternately stacked, wherein the gate layers are spaced apart from each other in a vertical direction in a first region and include gate pads arranged in a second region adjacent to the first region, wherein the gate contact plugs are electrically connected to the gate pads, wherein the memory vertical structure penetrates the stack structure in the first region, wherein the memory vertical structure includes a slope changing portion between an uppermost gate layer among the gate layers of the first stack structure and a lowermost gate layer among the gate layers of the second stack structure, wherein the support vertical structure penetrates at least a portion of the gate layers in the second region, wherein the air gap of the support vertical structure includes a portion disposed on the same level as the slope changing portion of the memory vertical structure, wherein the peripheral contact plug is spaced apart from the gate layers, wherein the peripheral contact plug includes an upper region disposed on a level higher than an upper surface of an uppermost gate layer among the gate layers of the stack structure and a lower region disposed on a level lower than the upper surface of the uppermost gate layer among the gate layers of the stack structure, wherein the upper region of the peripheral contact plug includes a first portion, a second portion and a connection portion disposed between the first portion and the second portion, and wherein the connection portion has a slope different from a slope of at least one of the first portion and the second portion.

[0007] According to an example embodiment of the present disclosure, a semiconductor device includes: a pattern structure including a silicon layer; a stack structure including a first stack structure and a second stack structure on the first stack structure on the pattern structure, wherein each of the first and second stack structures includes interlayer insulating layers and gate layers alternately stacked, and in the first and second stack structures, the gate layers are vertically stacked and spaced apart from each other in a first region, and include gate pads arranged in a staircase shape in a second region adjacent to the first region; an insulating structure on the stack structure; separation structures penetrating the stack structure and extending in the insulating structure in the first region and the second region; a memory vertical structure penetrating the stack structure between the separation structures in the first region; a support vertical structure penetrating the stack structure and including an air gap between the separation structures in the second region; gate contact plugs in contact with the gate pads; a peripheral contact plug spaced apart from the gate layers; and bit line contact plugs on the memory vertical structure, wherein the peripheral contact plug includes an upper region disposed on a level higher than an upper surface of an uppermost gate layer among the gate layers of the stack structure and a lower region disposed on a level lower than the upper surface of the uppermost gate layer among the gate layers of the stack structure, wherein the upper region of the peripheral contact plug includes a first portion, a connection portion disposed below the first portion, and a second portion disposed below the connection portion, wherein a side of the connection portion has a slope different from a slope of at least one of a side of the first portion and the second portion, wherein a side of the memory vertical structure includes a slope changing portion in which a slope of the side of the memory vertical structure changes on a level between an uppermost gate layer among the gate layers of the first stack structure and a lowermost gate layer among the gate layers of the second stack structure, and wherein a side of the lower region of the peripheral contact plug is substantially vertical on the level between the uppermost gate layer among the gate layers of the first stack structure and the lowermost gate layer among the gate layers of the second stack structure.

[0008] According to an example embodiment of the present disclosure, a data storage system includes: a main board; a semiconductor device on the main board; and a controller electrically connected to the semiconductor device on the main board, wherein the semiconductor device includes: a pattern structure including a silicon layer; a stack structure including a first stack structure and a second stack structure on the first stack structure on the pattern structure, wherein each of the first and second stack structures includes interlayer insulating layers and gate layers alternately stacked, and in the first and second stack structures, the gate layers are vertically stacked and spaced apart from each other in a first region, and include gate pads arranged in a staircase

shape in a second region adjacent to the first region an insulating structure on the stack structure; separation structures penetrating the stack structure and extending into the insulating structure in the first region and the second region; a memory vertical structure penetrating the stack structure between the separation structures in the first region; a support vertical structure penetrating the stack structure and including an air gap between the separation structures in the second region; gate contact plugs in contact with the gate pads; a peripheral contact plug spaced apart from the gate layers; and bit line contact plugs on the memory vertical structure, wherein the peripheral contact plug includes an upper region disposed on a level higher than an upper surface of an uppermost gate layer among the gate layers of the stack structure and a lower region disposed on a level lower than the upper surface of the uppermost gate layer the gate layer among of the stack structure, wherein the upper region of the peripheral contact plug includes a first portion, a connection portion disposed below the first portion, and a second portion disposed below the connection portion, wherein a side of the connection portion has a slope different from a slope of at least one of a side of the first portion and a side of the second portion, wherein a side of the memory vertical structure includes a slope changing portion on a level between an uppermost gate layer among the gate layers of the first stack structure and a lowermost gate layer among the gate layers of the second stack structure, and wherein a side of the lower region of the peripheral contact plug is substantially vertical on the level between the uppermost gate layer among the gate layers of the first stack structure and the lowermost gate layer among the gate layers of the second stack structure.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0009] The above and other features of the present disclosure will be more clearly understood from the following detailed description, taken in conjunction with the accompanying drawings, in which:

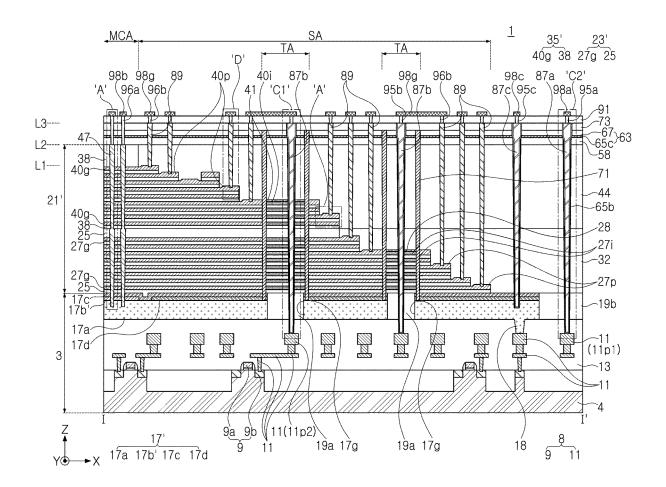

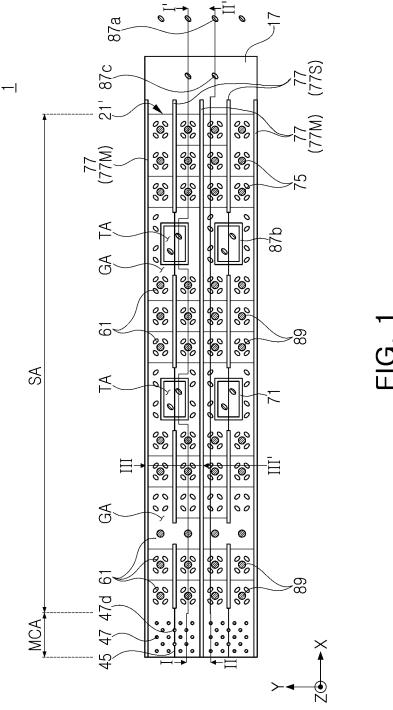

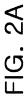

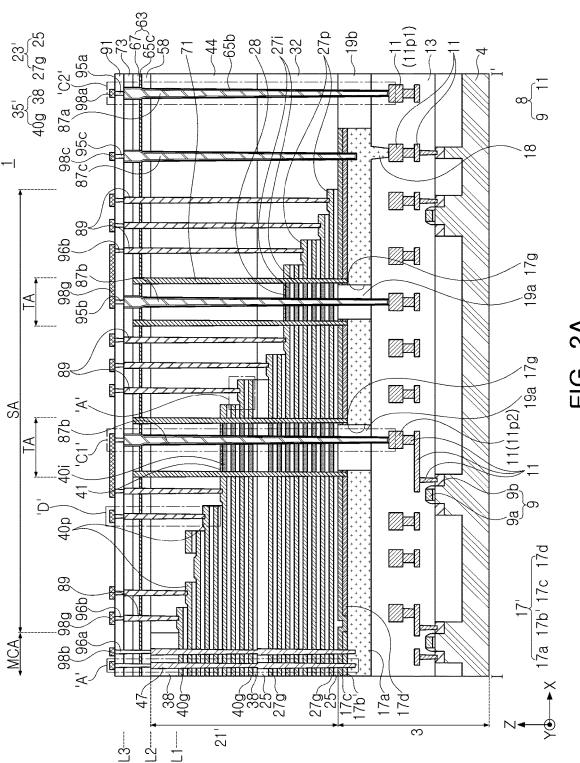

[0010] FIGS. 1, 2A, 2B, 2C, 3A, 3B, 3C and 3D are diagrams illustrating a semiconductor device according to an example embodiment of the present disclosure;

[0011] FIG. 4A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0012] FIG. 4B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0013] FIG. 5A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0014] FIG. 5B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0015] FIG. 6A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0016] FIG. 6B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a por-

tion of the semiconductor device according to an example embodiment of the present disclosure;

[0017] FIG. 7A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0018] FIG. 7B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0019] FIG. 7C is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0020] FIG. 8A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0021] FIG. 8B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0022] FIG. 9A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0023] FIG. 9B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0024] FIG. 10A is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0025] FIG. 10B is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

[0026] FIGS. 11A, 11B, and 12 are diagrams illustrating a modified example of a semiconductor device according to an example embodiment of the present disclosure;

[0027] FIG. 13 is an enlarged diagram illustrating a modified example of a semiconductor device, illustrating a portion of the semiconductor device according to an example embodiment of the present disclosure;

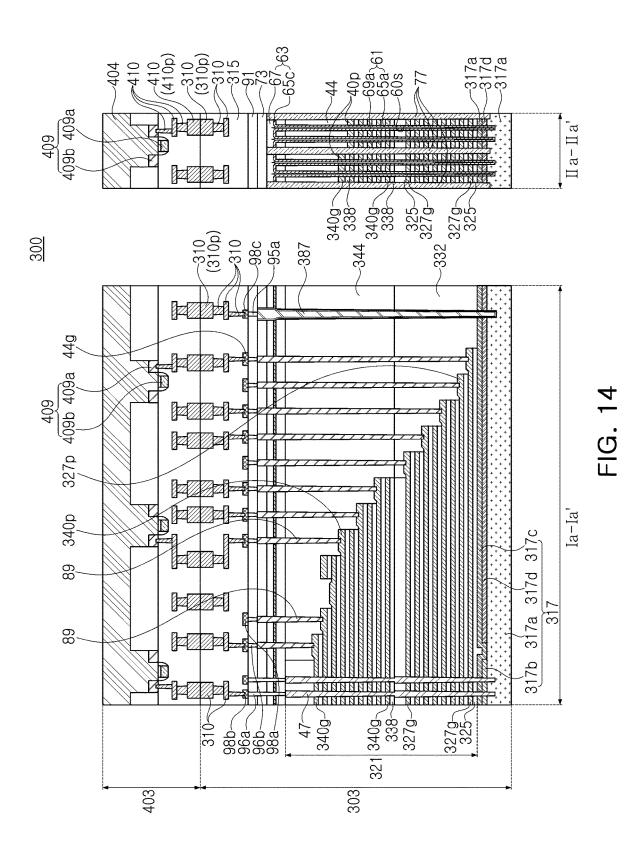

[0028] FIG. 14 is a diagram illustrating a modified example of a semiconductor device according to an example embodiment of the present disclosure;

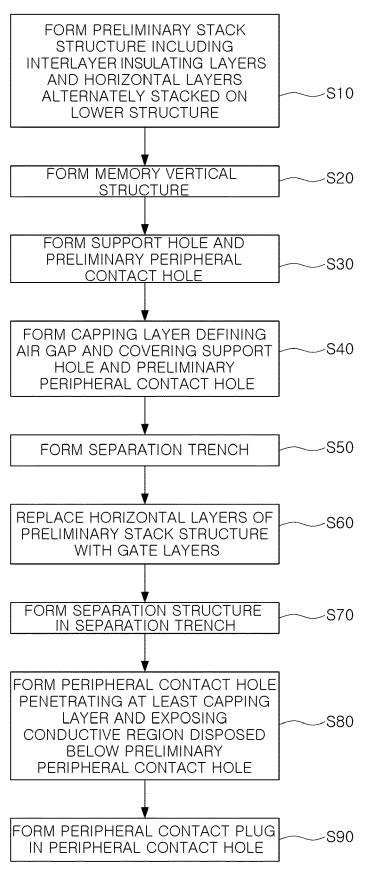

[0029] FIG. 15 is a flowchart illustrating a method of manufacturing a semiconductor device according to an example embodiment of the present disclosure;

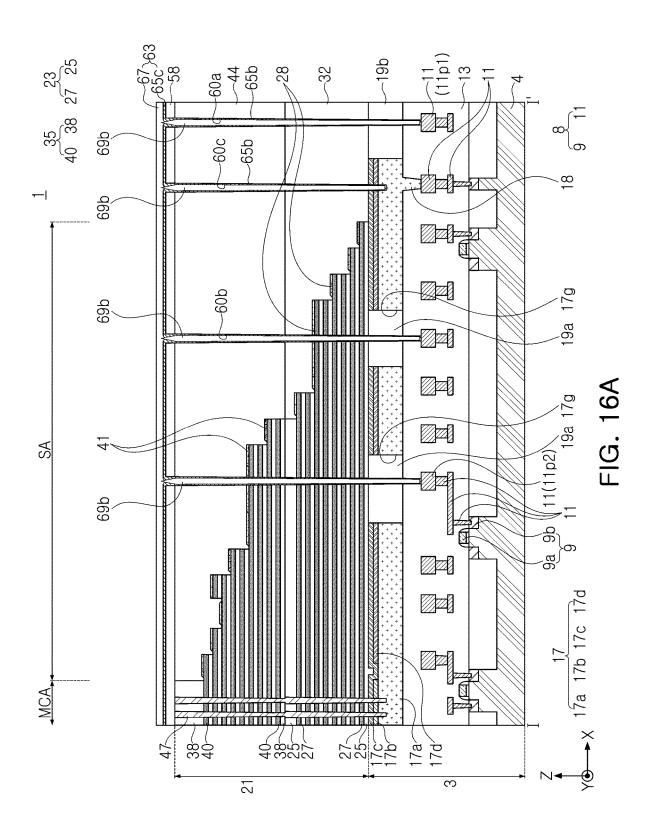

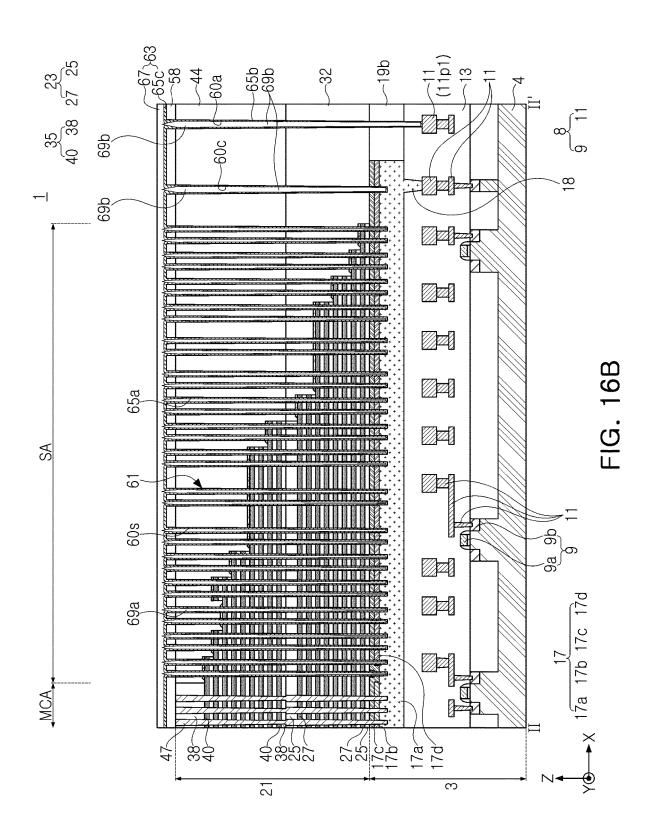

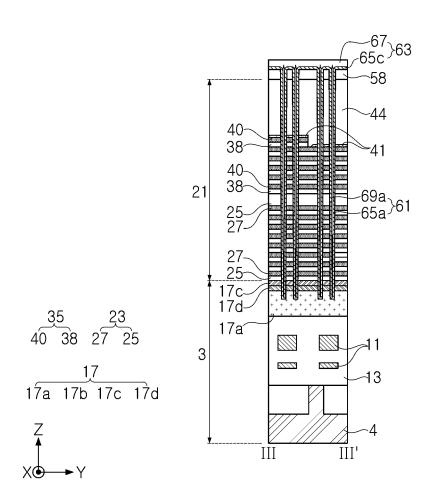

[0030] FIGS. 16A, 16B and 16C are cross-sectional diagrams illustrating a method of manufacturing a semiconductor device according to an example embodiment of the present disclosure;

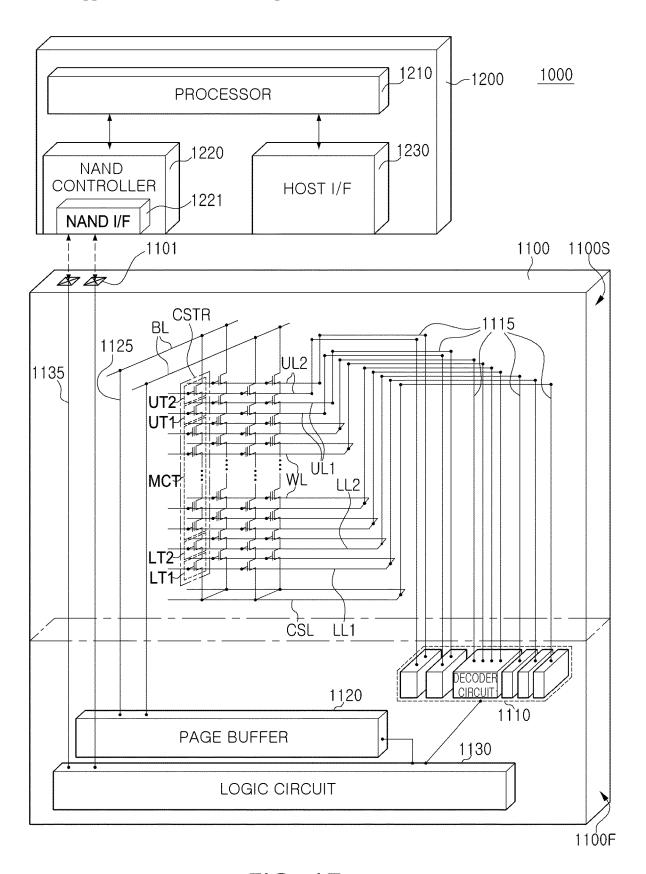

[0031] FIG. 17 is a diagram illustrating a data storage system including a semiconductor device according to an example embodiment of the present disclosure;

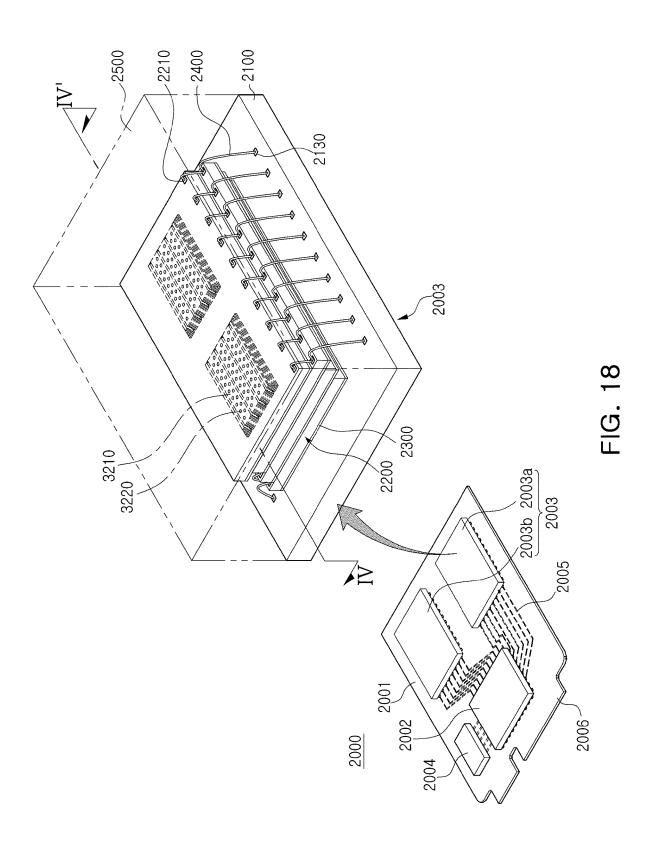

[0032] FIG. 18 is a perspective diagram illustrating a data storage system including a semiconductor device according to an example embodiment of the present disclosure; and

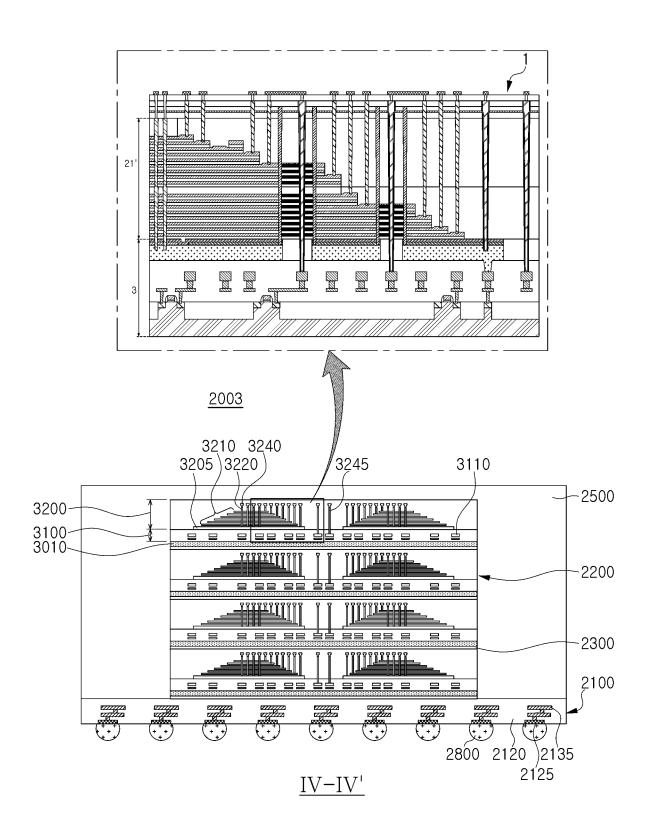

[0033] FIG. 19 is a cross-sectional diagram illustrating a data storage system including a semiconductor device according to an example embodiment of the present disclosure.

# DETAILED DESCRIPTION OF THE EMBODIMENTS

[0034] Hereinafter, example embodiments of the present disclosure will be described with reference to the accompanying drawings. In the drawings, like reference numerals may refer to like elements.

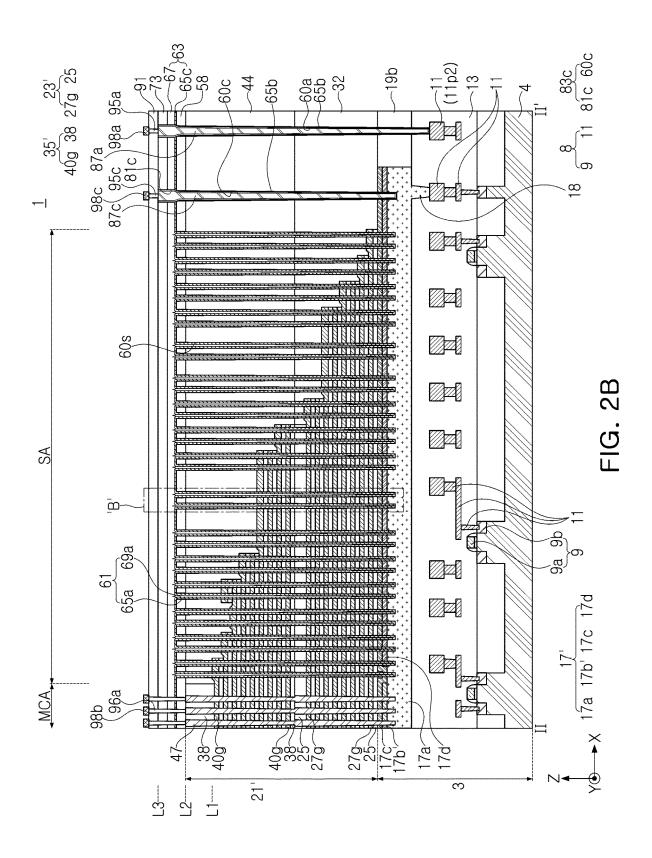

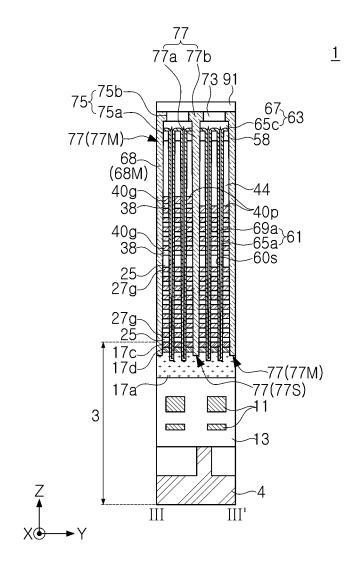

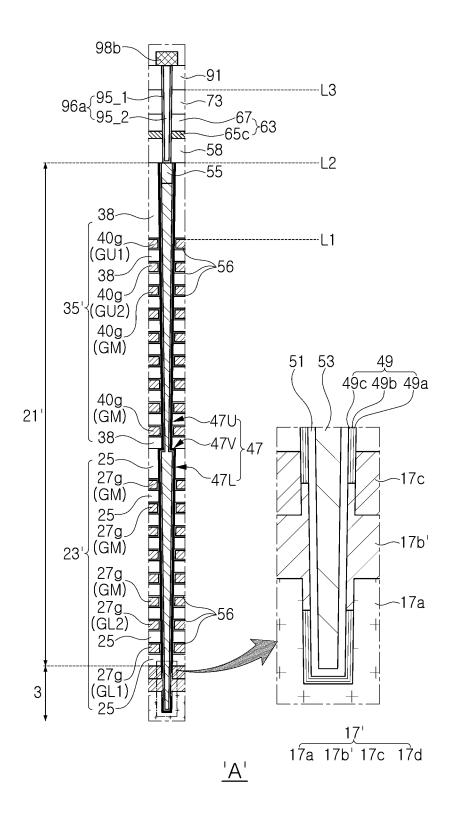

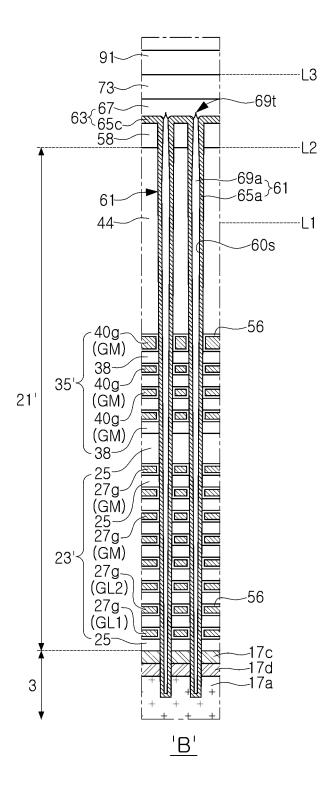

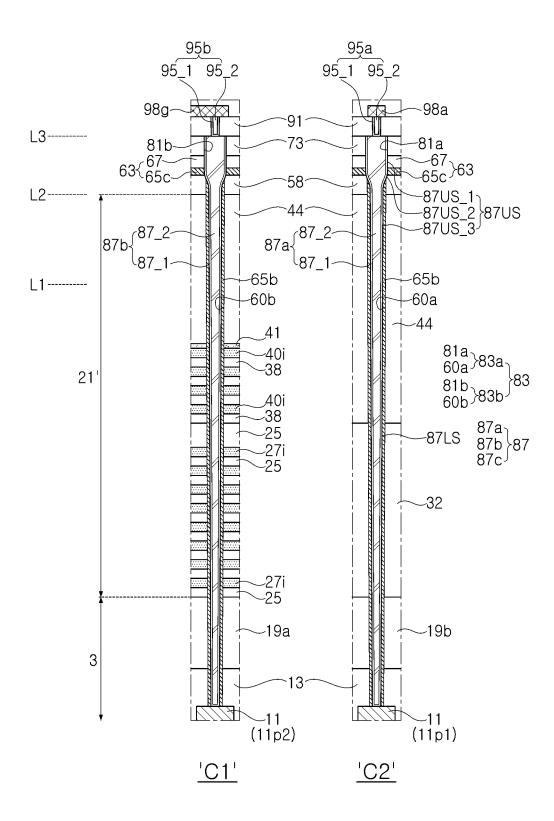

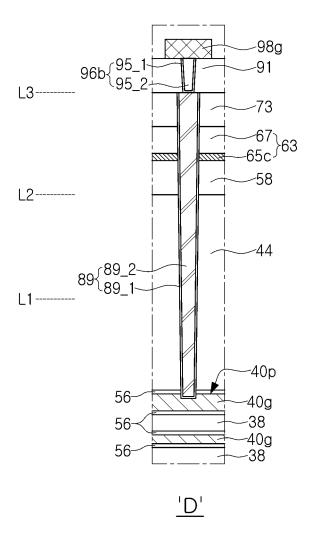

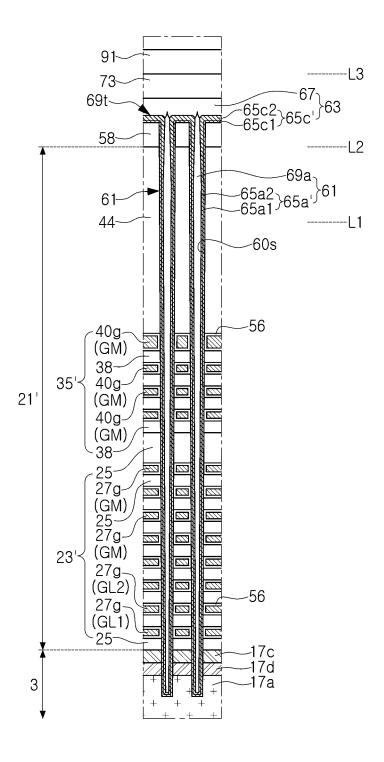

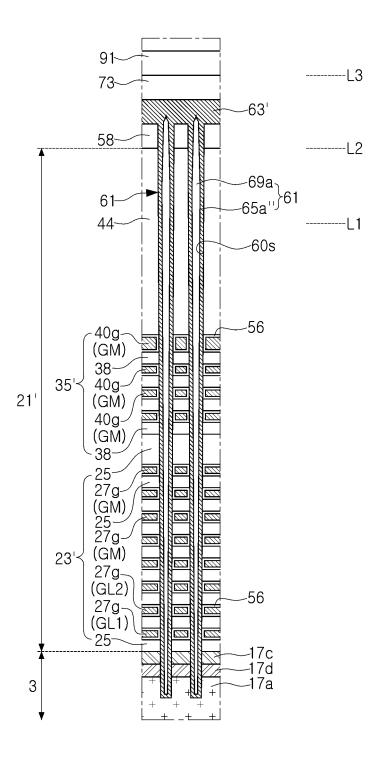

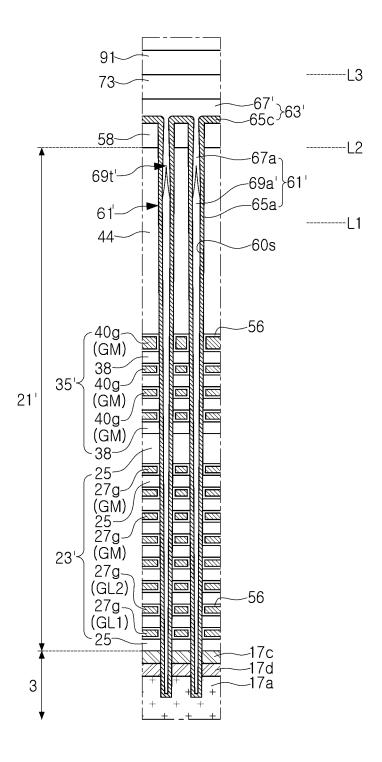

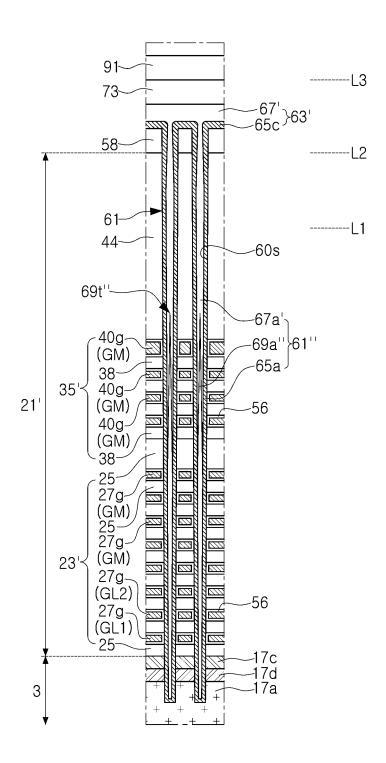

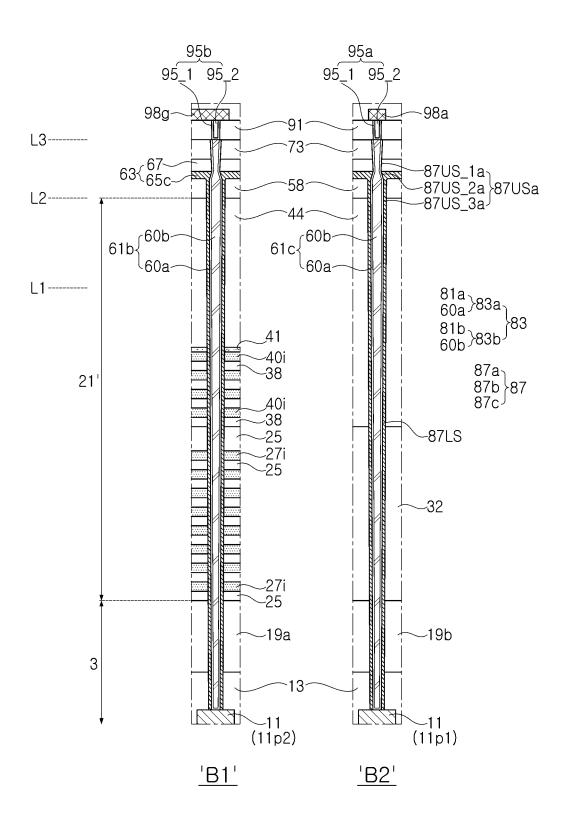

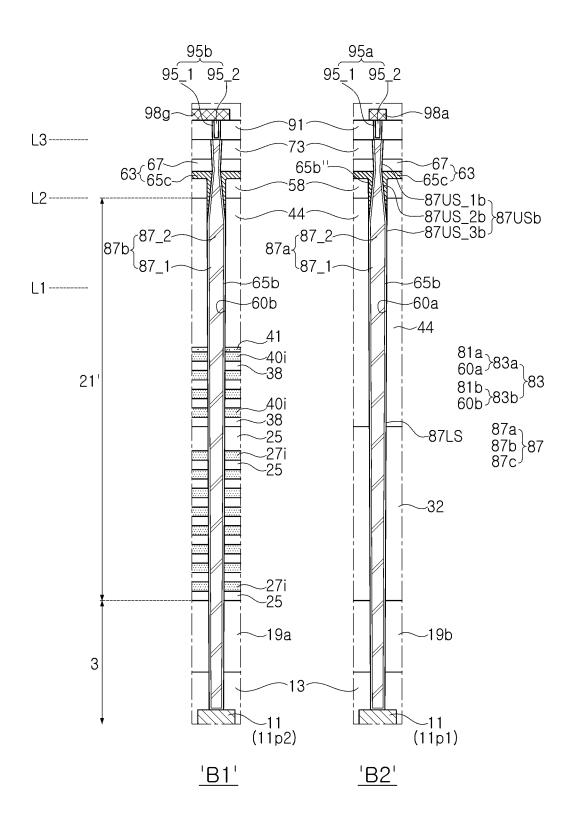

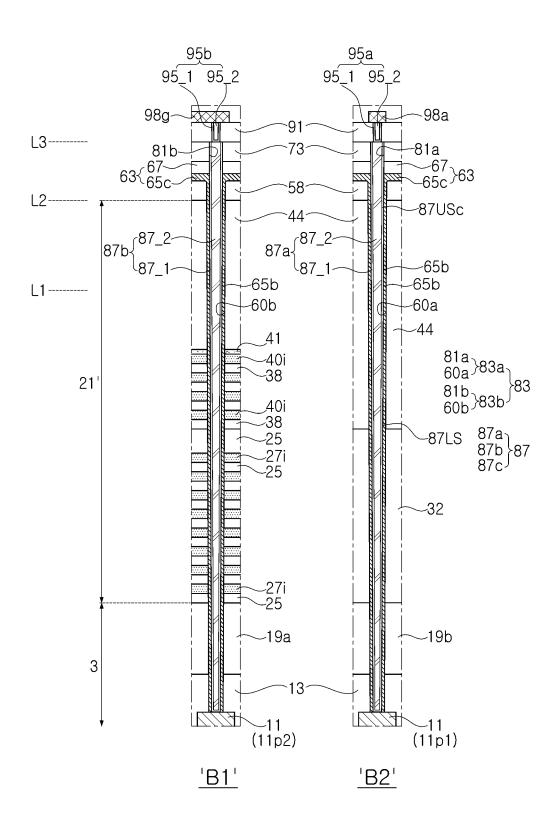

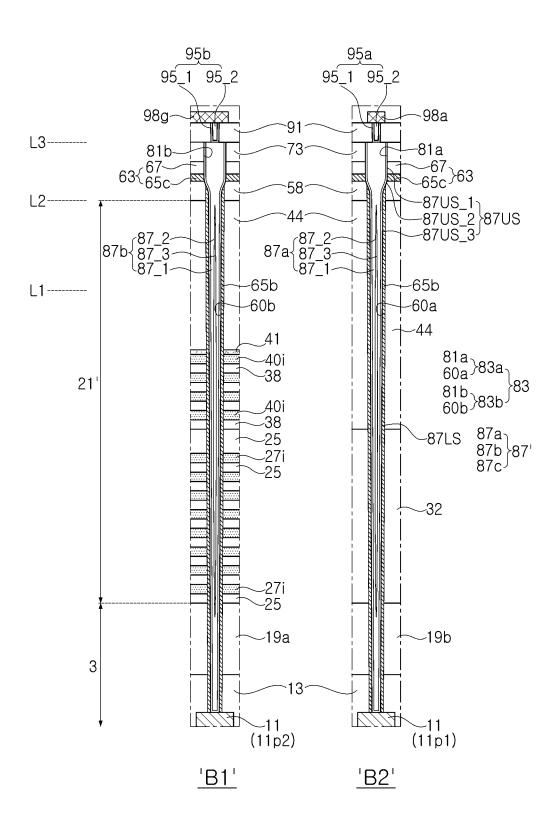

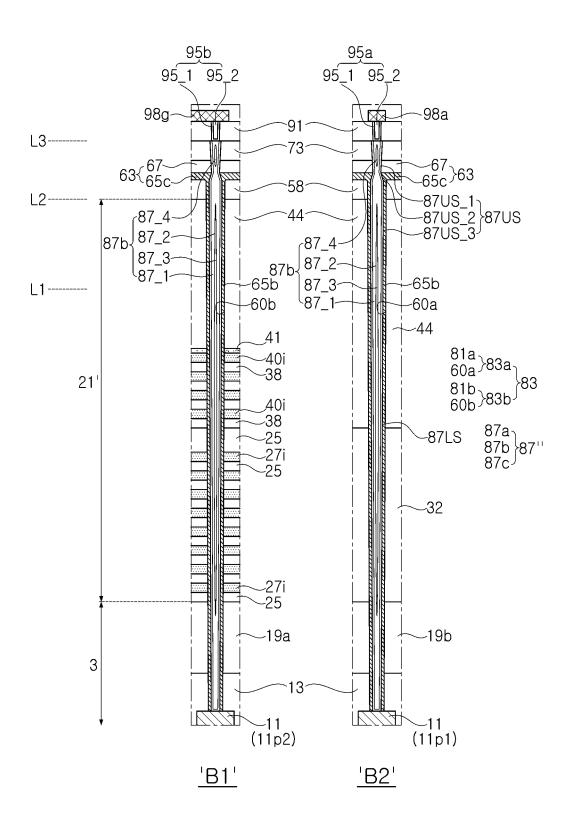

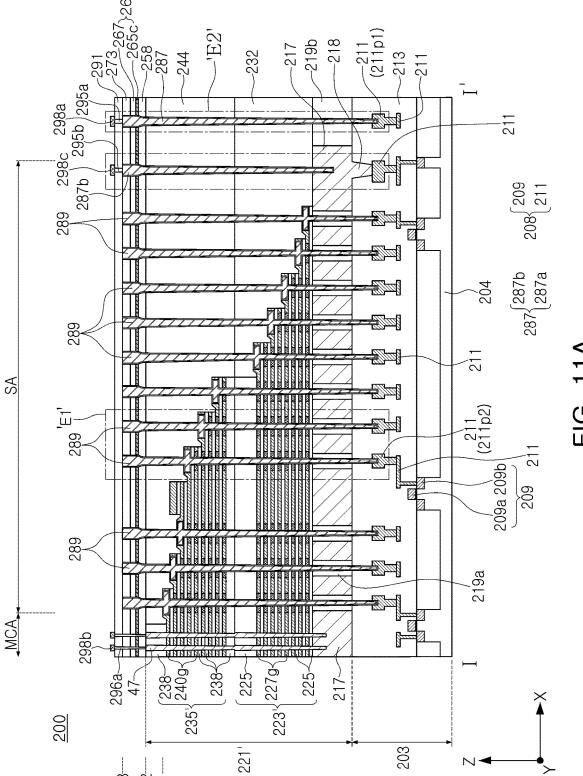

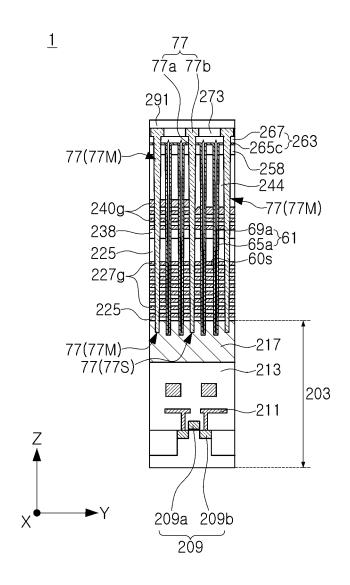

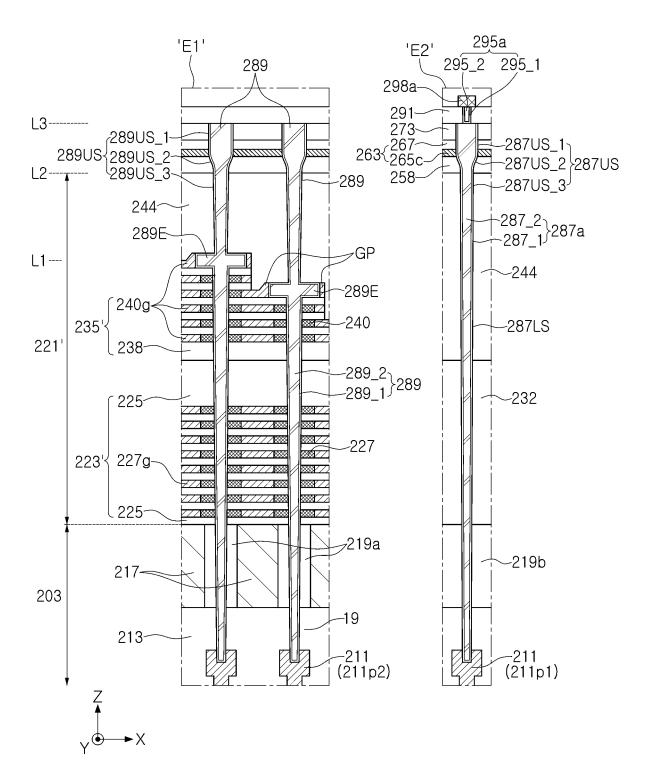

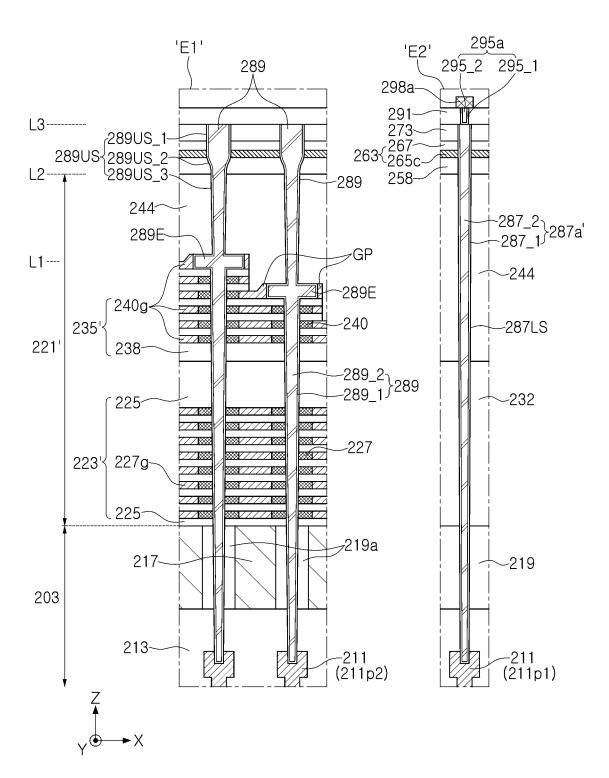

[0035] An example of a semiconductor device according to an example embodiment of the present disclosure will be described with reference to FIGS. 1 to 2C. FIG. 1 is a plan diagram illustrating a semiconductor device according to an example embodiment of the present disclosure, FIG. 2A is a cross-sectional diagram illustrating the region taken along line I-I' in FIG. 1. FIG. 2B is a cross-sectional diagram illustrating the region taken along line II-II' in FIG. 1, and FIG. 2C is a cross-sectional diagram illustrating the region taken along line III-III' in FIG. 1.

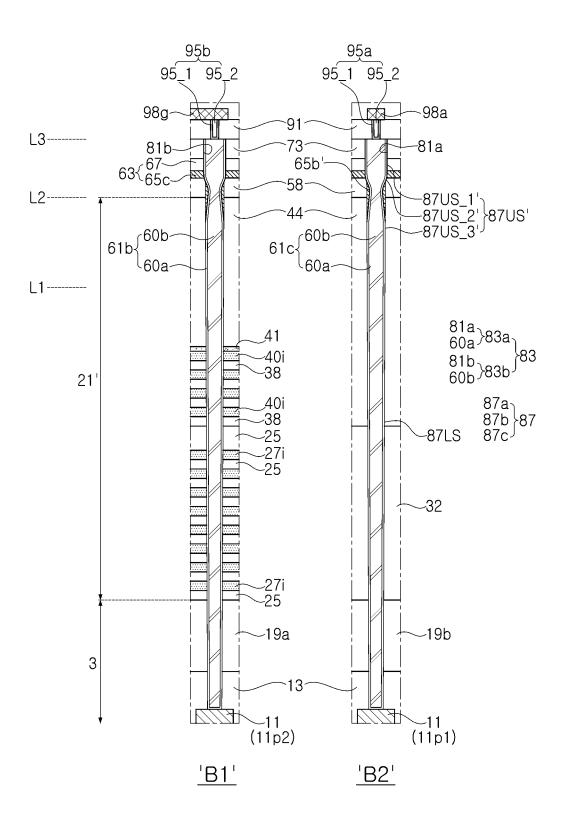

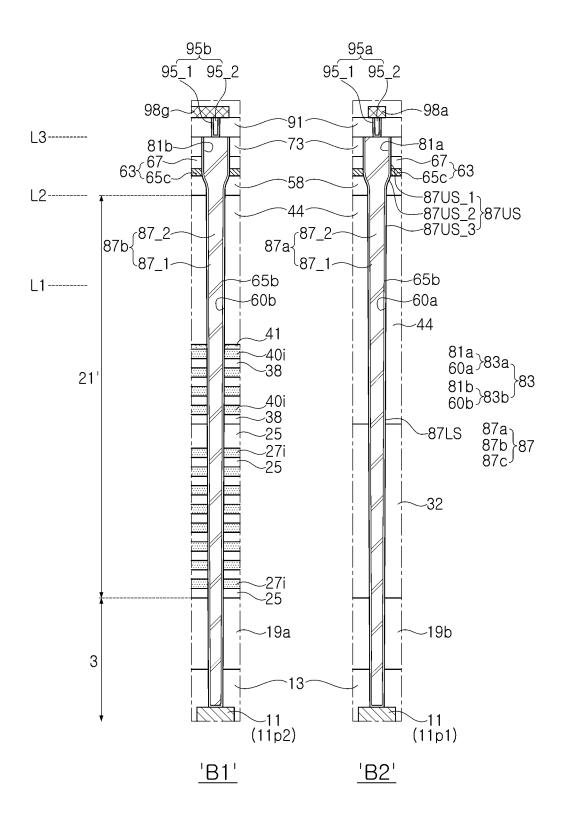

[0036] Referring to FIGS. 1 to 2C, a semiconductor device 1 according to an example embodiment of the present disclosure may include a first structure 3 and a second structure 21' overlapping the first structure 3 in the vertical direction Z.

[0037] The first structure 3 may include a pattern structure 17'. The pattern structure 17' may include at least one silicon layer.

The pattern structure 17' may include a first pattern layer 17a, a second pattern layer 17b', a third pattern layer 17c, and a fourth pattern layer 17d. The second pattern layer 17b' and the fourth pattern layer 17d may be spaced apart from each other on the first pattern layer 17a. In other words, the second pattern layer 17b' and the fourth pattern layer 17d may be disposed on the first pattern layer 17a. The third pattern layer 17c may cover the second pattern layer 17b' and the fourth pattern layer 17d on the first pattern layer 17a. The third pattern layer 17c may contact the first pattern layer 17a between the second and fourth pattern layers 17b' and 17d. The first pattern layer 17a may have a thickness greater than a thickness of each of the second pattern layer 17b', the third pattern layer 17c, and the fourth pattern layer 17d. At least one of the first pattern layer 17a, the second pattern layer 17b', the third pattern layer 17c, and the fourth pattern layer 17d may include a silicon layer. For example, the first pattern layer 17a, the second pattern layer 17b', and the third pattern layer 17c may include a silicon layer, such as, for example, a silicon layer having N-type conductivity, and the fourth pattern layer 17d may include a material different from that of the silicon layer. For example, the fourth pattern layer 17d may include a plurality of layers stacked in order, a silicon oxide layer, a silicon nitride layer, and a silicon oxide layer, for example.

[0039] The first structure 3 may include a semiconductor substrate 4, a peripheral circuit 8 on the semiconductor substrate 4, and a lower insulating layer covering the peripheral circuit 8 on the semiconductor substrate 4. The peripheral circuit 8 may include a circuit device 9 such as a transistor including a peripheral gate 9a and a peripheral source/drain 9b, and a circuit interconnection 11 electrically connected to the circuit device 9. A portion of the circuit interconnection 11 may be first and second peripheral circuit pads 11p1 and 11p2.

[0040] The pattern structure 17' may be disposed on a lower insulating layer 13.

[0041] The pattern structure 17' may further include a ground pattern 18. For example, the ground pattern 18 may be disposed below the first pattern layer 17a and may be grounded to the semiconductor substrate 4 through a portion of the circuit interconnection 11. The ground pattern 18 may extend from the first pattern layer 17a. For example, when the first pattern layer 17a is formed of a silicon layer, the ground pattern 18 may be formed of a silicon layer extending from the silicon layer.

[0042] The pattern structure 17' may have gaps 17g. Each of the gaps 17g may be implemented as a slit or an opening penetrating the pattern structure 17'.

[0043] The first structure 3 may further include an internal insulating layer 19a filling the gaps 17g and an external insulating layer 19b disposed on an external side of the pattern structure 17'.

[0044] The second structure 21' may include a first region MCA and a second region SA. The second structure 21' may include stack structures 23' and 35' disposed in the first region MCA and extending from the first region MCA into the second region SA.

[0045] In example embodiments of the present disclosure, the first region MCA may be a memory cell region, and the second region SA may be a staircase region, an extension region, or a contact region. Hereinafter, for ease of description, the first region MCA will be referred to as a memory cell region and the second region SA will be referred to as a staircase region.

[0046] The stack structures 23' and 35' may include a first stack structure 23' and a second stack structure 35' on the first stack structure 23'. The first stack structure 23' may include first interlayer insulating layers 25 and first gate layers 27g alternately stacked in the vertical direction Z. The vertical direction Z may be disposed in a direction perpendicular to an upper surface of the pattern structure 17'. The first gate layers 27g may have first gate pads 27p arranged in a staircase shape in the staircase region SA.

[0047] The second stack structure 35' may include second interlayer insulating layers 38 and second gate layers 40g alternately stacked in the vertical direction Z. The second gate layers 40g may have second gate pads 40p arranged in a staircase shape in the staircase region SA.

[0048] The first interlayer insulating layers 25 and the second interlayer insulating layers 38 may form interlayer insulating layers 25 and 38, and the first gate layers 27g and the second gate layer 40g may form gate layers 27g and 40g. Accordingly, the first and second stack structures 23' and 35' may include the interlayer insulating layers 25 and 38 and the gate layers 27g and 40g alternately stacked in the vertical direction Z. The gate layers 27g and 40g may have the first and second gate pads 27g and 40g arranged in a staircase shape in the staircase region SA.

[0049] In example embodiments of the present disclosure, the "gate pad" may be a region of the gate layer of which an upper portion is not covered by another gate layer disposed thereon in the staircase region SA.

[0050] In example embodiments of the present disclosure, the first and second gate pads 27p and 40p may be arranged in the staircase shape illustrated in the drawings, and also in various staircase shapes.

[0051] Each of the first and second gate pads 27p and 40p may have a thickness greater than a thickness of each of the

first and second gate layers 27g and 40g disposed in the memory cell array region MCA.

[0052] The first and second gate layers 27g and 40g may include a conductive material. For example, each of the first and second gate layers 27g and 40g may be formed of two or more materials among a doped polysilicon, a metal-semiconductor compound (e.g., TiSi, TaSi, CoSi, NiSi, WSi, or the like), a metal nitride (e.g., TiN, TaN or WN, or the like) or a metal (e.g., Ti or W, or the like). The interlayer insulating layers 25 and 38 may be formed of an insulating material such as silicon oxide.

[0053] The first and second stack structure or multi layer structures 23' and 35' may further include one or a plurality of through regions TA. Each of the through regions TA may further include insulating horizontal layers 27i and 40i disposed on the same level as a level of first and second gate layers 27g and 40g adjacent to the through regions TA among the first and second gate layers 27g and 40g. For example, among the through regions TA, a portion of the through region TA adjacent to the first gate layers 27g may include first insulating horizontal layers 27i disposed on the same level as a level of the first gate layers 27g, and a portion of the through region TA adjacent to the second gate layers 40g may include second insulating horizontal layers 40i disposed on the same level as a level of the second gate layers 40g.

[0054] In an example embodiment of the present disclosure, each of the through regions TA may further include reinforcing horizontal layers 28 and 41 in contact with an uppermost insulating horizontal layer on an uppermost insulating horizontal layer among the insulating horizontal layers 27i and 40i. For example, the through region TA in a position spaced apart from the second stack structure 35' may include a first reinforcing horizontal layer 28 in contact with the uppermost first insulating horizontal layer among the first insulating horizontal layers 27i. For example, the first reinforcing horizontal layer 28 may cover the uppermost first insulating horizontal layer among the first insulating horizontal layers 27i. The through region TA disposed in the first and second stack structures 23' and 35' may include a second reinforcing horizontal layer 41 in contact with an uppermost second insulating horizontal layer among the second insulating horizontal layers 40i. For example, the second reinforcing horizontal layer 41 may cover the uppermost second insulating horizontal layer among the second insulating horizontal layers 40i.

[0055] The first and second insulating horizontal layers 27i and 40i may be formed of an insulating material different from that of the first and second interlayer insulating layers 25 and 38. For example, the first and second insulating horizontal layers 27i and 40i may be formed of first silicon nitride, and the first and second interlayer insulating layers 25 and 28 may be formed of silicon oxide.

[0056] The first and second reinforcing horizontal layers 28 and 41 may be formed of a second silicon nitride having an etch rate different from that of the first silicon nitride of the first and second insulating horizontal layers 27*i* and 40*i*. The second silicon nitride may be a material having an etch rate higher than that of the first silicon nitride.

[0057] When viewed in on the same plane as in FIG. 1, in the stack structures 23' and 35', each of the through regions TA may be surrounded by a gate region GA (in FIG. 1). In the gate region GA, the first and second gate layers 27g and 40g may be disposed. Accordingly, each of the through

regions TA may be surrounded by adjacent first and second gate layers 27g and 40g. The second structure 21' may further include intermediate insulating layers 32 and 44. The intermediate insulating layers 32 and 44 may include a first intermediate insulating layer 32 and a second intermediate insulating layer 44. The first intermediate insulating layer 32 may include the first gate pads 27p, a portion of the pattern structure 17' not covered by the first stack structure 23', and the external insulating layer 19b. The second intermediate insulating layer 44 may cover the second gate pads 40p and the first intermediate insulating layer 32. The first and second intermediate insulating layers 32 and 44 may be formed of an insulating material such as silicon oxide.

[0058] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a memory vertical structure 47 including a portion penetrating the second structure 21'. The memory vertical structure 47 may include a portion penetrating the first and second stack structures 23' and 35' in the memory cell array region MCA. The memory vertical structure 47 may extend into the pattern structure 17' from a portion penetrating the second structure 21' and may be in contact the pattern structure 17'. For example, the memory vertical structure 47 may penetrate the third pattern layer 17c and the second pattern layer 17b' in order and may extend into the first pattern layer 17a. The memory vertical structure 47 may be in contact with at least one of the first to third pattern layers 17a, 17b', and 17c formed as a silicon layer.

[0059] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a string separation pattern 45 penetrating one or a plurality of upper gate layers disposed thereon among the second gate layers 40g. The string separation pattern 45 may be formed of silicon oxide. The string separation pattern 45 may be disposed on a level higher than a second gate layer, which may be a word line, among the second gate layers 40g.

[0060] The semiconductor device 1 according to all example embodiment of the present disclosure may include a dummy vertical structure 47d penetrating the string separation pattern 45 and also penetrating the second structure 21', and in contact with the pattern structure 17'. The dummy vertical structure 47d may have the same cross-sectional structure as that of the memory vertical structure 47 and may be formed of the same material as that of the memory vertical structure 47.

[0061] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a first upper insulating layer 58 on the second structure 21'. The first upper insulating layer 58 may include silicon oxide.

[0062] The semiconductor device 1 according to an example embodiment of the present disclosure may further include support holes 60s penetrating the first upper insulating layer 58 and the second structure 21' and exposing a portion of the pattern structure 17', and support vertical structures 61 disposed in the support holes 60s. Each of the support vertical structures 61 may include a portion penetrating at least a portion of the first and second gate layers 27g and 40g of the second structure 21' in the staircase region SA. When viewed on the plane, each of the support vertical structures 61 may have a circular shape or an elliptical shape.

[0063] At least a portion of the support vertical structures 61 may penetrate the third pattern layer 17c and the fourth pattern layer 17d of the pattern structure 17 in order, and may extend into the first pattern layer 17a. One of the support vertical structures 61 may be spaced apart from the fourth pattern layer 17d, may penetrate the third pattern layer 17c, and may extend into the first pattern layer 17a.

[0064] Hereinafter, a single support hole 60s and a single support vertical structure 61 will be mainly described for ease of description.

[0065] An upper surface of the support vertical structure 61 may be disposed on a level higher than the upper surface of the memory vertical structure 47.

[0066] In example embodiments, "level" may refer to a level when viewed with respect to the upper surface of the pattern structure 17' or a level when viewed with respect to the upper surface of the semiconductor substrate 4.

[0067] The support vertical structure 61 may include an air gap 69a and a support layer 65a defining at least a portion of the air gap 69a.

[0068] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a capping layer 63 disposed on the first upper insulating layer 58 and covering the support vertical structure 61.

[0069] The capping layer 63 may include a lower capping layer 65c and an upper capping layer 67 on the lower capping layer 65c.

[0070] The semiconductor device 1 according to an example embodiment of the present disclosure may further include dam structures 71. Each of the dam structures 71 may penetrate the capping layer 63, the first upper insulating layer 58, and the second structure 21', and may surround each of the through regions TA. Accordingly, when viewed on the plane, each of the darn structures 71 may be disposed between the gate region GA (in FIG. 1) and each of the through regions TA (in FIG. 1).

[0071] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a second upper insulating layer 73 on the capping layer 63. The second upper insulating layer 73 may be in direct contact with the upper capping layer 67.

[0072] The semiconductor device 1 according to an example embodiment of the present disclosure may further include separation structures 77 penetrating the second upper insulating layer 73, the capping layer 63, the first upper insulating layer 58, and the second structure 21'. Each of the separation structures 77 may be formed of silicon oxide or silicon oxide having a void therein. In another example, each of the separation structures 77 may include a conductive pattern in contact with the pattern structure 17' and an insulating layer covering a side surface of the conductive pattern.

[0073] Each of the separation structures 77 may include a lower separation portion 77a penetrating the capping layer 63, the first upper insulating layer 58 and the second structure 21' and an upper separation portion 77b penetrating the second upper insulating layer 73. The lower separation portion 77a and the upper separation portion 77b may be integrated with each other.

[0074] In at least one of the separation structures 77, the upper separation portion 77b may have a width different from a width of the lower separation portion 77a. For example, in at least one of the separation structures 77, the

upper separation portion 77b may have a width greater than a width of the lower separation portion 77a.

[0075] In at least one of the separation structures 77, at least a portion of a side surface of the upper separation portion 77b may not be vertically aligned with at least a portion of a side surface of the lower separation portion 77a. [0076] The separation structures 77 may include a plurality of main separation structures 77M parallel to each other, and auxiliary separation structures 77S disposed between the main separation structures 77M. Each of the separation structures 77 may include a line portion extending in the first horizontal direction X. The first horizontal direction X may be parallel to an upper surface of the pattern structure 17'. The first horizontal direction X may be a direction from the memory cell array region MCA toward the staircase region SA. Each of the auxiliary separation structures 77S may have a length shorter than that of each of the main separation structures 77M. For example, a plurality of the auxiliary separation structures 77S may be arranged in the first direction X next to a single main separation structure 77M arranged in the first direction X. The main separation structures 77M may penetrate the second structure 21' and may separate the first and second stack structures 23' and 35' in the second horizontal direction Y. The second horizontal direction Y may be parallel to the upper surface of the pattern structure 17' and may be perpendicular to the first horizontal direction X. Each of the separation structures 77 may be in contact with the first and second gate layers 27g and 40g adjacent to the separation structure 77.

[0077] The separation structures 77 may extend downwardly from a portion penetrating the second structure 21' and may be in contact the pattern structure 17'. At least one of the separation structures 77 may be in contact with the first pattern layer 17a.

[0078] The semiconductor device 1 according to an example embodiment of the present disclosure may further include peripheral contact plugs 87. The peripheral contact plugs 87 may include a first peripheral contact plug 87a, a second peripheral contact plug 87b, and a third peripheral contact plug 87c. The peripheral contact plugs 87 may penetrate the second upper insulating layer 73, the capping layer 63, the first upper insulating layer 58, and the second structure 21', and may extend into the lower structure 3.

[0079] The first peripheral contact plug 87a may be spaced apart from the first and second gate layers 27g and 40g, may penetrate the first and second intermediate insulating layers 32 and 44, may be in contact with the first peripheral circuit pad 11p1, and may be electrically connected to the first peripheral circuit pad 11p1.

[0080] The second peripheral contact plug 87b may be spaced apart from the first and second gate layers 27g and 40g, may penetrate the first and second insulating horizontal layers 27i and 40i of the through regions TA, may be in contact with the second peripheral circuit pad 11p2, and may be electrically connected to the second peripheral circuit pad 11p2.

[0081] The third peripheral contact plug 87c may be spaced apart from the first and second gate layers 27g and 40g, may penetrate the first and second intermediate insulating layers 32 and 44, and may be in contact with the first pattern layer 17a, and may be electrically connected to the first pattern layer 17a. In the pattern structure 17', the first pattern layer 17a, which may be formed as a polysilicon layer having N-type conductivity, may be a common source,

and the third peripheral contact plug **87***c* may be a common source contact plug electrically connected to the common source.

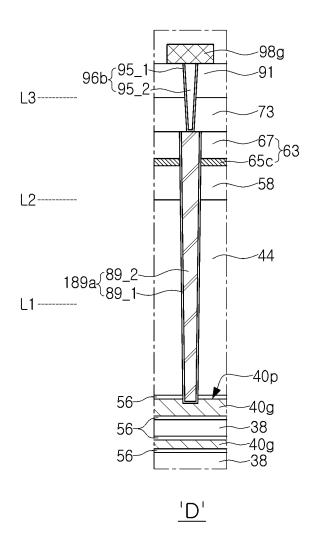

[0082] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a spacer layer 65b covering a side surface of each of the first to third peripheral contact plugs 87a, 87b, and 87c. [0083] The semiconductor device 1 according to an example embodiment of the present disclosure may further include gate contact plugs in contact with the first and second gate pads 27p and 40p and electrically connected to the first and second gate pads 27p and 40p. Gate contact plugs 89 may penetrate the second upper insulating layer 73, the capping layer 63 and the first upper insulating layer 58, may extend into the second structure 21', and may be in contact with the first and second gate pads 27p and 40p.

[0084] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a third upper insulating layer 91 disposed on the second upper insulating layer 73. The first, second, and third upper insulating layers 58, 73, and 91 may include silicon oxide.

[0085] The semiconductor device 1 according to an example embodiment of the present disclosure may further include peripheral upper plugs 95a, 95b, and 95c penetrating the third upper insulating layer 91. The peripheral upper plugs 95a, 95b, and 95c may further include a first peripheral upper plug 95a electrically connected to the first peripheral contact plug 87a, a second peripheral upper plug 95b electrically connected to the second peripheral contact plug 87b, and a third peripheral upper plug 95c electrically connected to the third peripheral contact plug 87c.

[0086] The first peripheral upper plug 95a may include a side surface not vertically aligned with the side surface of the first peripheral contact plug 87a. The second peripheral upper plug 95b may include a side surface not vertically aligned with a side surface of the second peripheral contact plug 87b. The third peripheral upper plug 95c may include a side surface not vertically aligned with a side surface of the third peripheral contact plug 87c.

[0087] A width of each of the first to third peripheral upper plugs 95a, 95b, and 95c may be different from a width of each of the first to third peripheral contact plugs 87a, 87b, and 87c. In one example, a width of each of the first to third peripheral upper plugs 95a, 95b, and 95c may be smaller than a width of each of the first to third peripheral contact plugs 87a, 87b, and 87c. In another example, a width of each of the first to third peripheral upper plugs 95a, 95b and 95c may be greater than a width of each of the first to third peripheral contact plugs 87a, 87b and 87c. The semiconductor device 1 according to an example embodiment of the present disclosure may further include a bit line contact plug 96a penetrating the first to third upper insulating layers 58, 73, and 71 and the capping layer 63, and electrically connected to the memory vertical structure 47.

[0088] The semiconductor device 1 according to an example embodiment of the present disclosure further may include gate upper plugs 96b penetrating the third upper insulating layer 91 and electrically connected to the gate contact plugs 89.

[0089] The semiconductor device 1 according to an example embodiment of the present disclosure may further include wirings 98b, 98g, 98a, and 98c disposed on the third upper insulating layer 91. The wirings 98b, 98g, 98a, and

98c may include bit lines 98b electrically connected to the bit line contact plugs 96a, gate connection wirings 98g electrically connecting each of the gate upper plugs 96b to the plurality of second peripheral upper plugs 95b, a first peripheral wiring 98a electrically connected to the first peripheral upper plug 95a, and a second peripheral wiring 98c electrically connected to the third peripheral upper plug 95c

[0090] Hereinafter, a level on which the upper surface of the uppermost gate layer among the first and second gate layers 27g and 40g is disposed may be referred to as a first level L1, a level on which the upper surface of the memory vertical structure 47 is disposed may be referred to as a second level L2, and a level on which the upper surface of the second upper insulating layer 73 is disposed may be referred to as a third level L3.

[0091] In the description below, examples of the first and second gate layers 27g and 40g and the memory vertical structure 47 described in the aforementioned example embodiment will be described with reference to FIG. 3A. FIG. 3A is an enlarged diagram illustrating region "A" in FIG. 2A.

[0092] Referring to FIGS. 2A and 3A, the first and second gate layers 27g and 40g also just referred to as the gate layers may include one or a plurality of lower gate layers GL1 and GL2, one or the plurality of upper gate layers GW1 and GU2, and plurality of intermediate gate layers GW1 disposed between the one or the plurality of lower gate layers GL1 and GL2 and the one or the plurality of upper gate layers GU1 and GU2. The one or the plurality of upper gate layers GU1 and GU2 may be spaced apart from each other in the vertical direction Z. For example, the plurality of upper gate layers GU1 and GU2 may include a first upper gate layer GU1 and a second upper gate layer GU2 disposed below the first upper gate layer GU1.

[0093] The one or the plurality of lower gate layers GL1 and GL2 may be spaced apart from each other in the vertical direction Z. For example, the plurality of lower gate layers GL1 and GL2 may include a first lower gate layer GL1 and a second lower gate layer GL2 disposed on the first lower gate layer GL1.

[0094] A portion of the plurality of intermediate gate layers GM may be word lines.

[0095] In one example, the first lower gate layer GL1 may be a ground select gate line of a ground select transistor, and the second lower gate layer GL2 may be a dummy gate line.

[0096] In another example, the first lower gate layer  ${\rm GL1}$  may be an erase control gate line of an erase control transistor which may be used for an erase operation for removing data stored in memory cells using a gate induce drain leakage (GIDL) phenomenon, and the second lower gate layer GL2 may be a ground select gate line of a ground select transistor.

[0097] In an example, the plurality of upper gate layers GU1 and GU2 may be string select gate lines of string select transistors

[0098] In another example, the first upper gate layer GU1 of the plurality of upper gate layers GU and GU2 may be an erase control gate line of an erase control transistor, and the second upper gate layer can of the plurality of upper gate layers GU1 and GU2 may be a string select gate line of the string select transistor.

[0099] The memory vertical structure 47 may include a lower vertical portion 47L penetrating the first stack structure 23' and an upper vertical portion 47U penetrating the second stack structure 35'.

[0100] A width of an upper region of the lower vertical portion 47L may be different from a width of a lower region of the upper vertical portion 47U. For example, a width of an upper region of the lower vertical portion 47L may be greater than a width of a lower region of the upper vertical portion 47U. In other words, the width of the lower vertical portion 47L where the lower vertical portion 47L and the upper vertical portion 47U meet may be greater than that of the upper vertical portion 47U.

[0101] A side surface of the lower vertical portion 47L and a side surface of the upper vertical portion 47U, adjacent to each other, may not be aligned in the vertical direction Z.

[0102] A middle side surface of the memory vertical structure 47 disposed on a level between an uppermost first gate layer among the first gate layers 27g of the first stack structure 23' and a lowermost second gate layer of the second gate layers 40g of the second stack structure 35' may include a slope changing portion 47V in which a slope may change.

[0103] In example embodiments of the present disclosure, the "slope changing portion" may be a side-surface portion of the memory vertical structure 47 having a third slope different from a first slope and a second slope between an upper side-surface portion having the first slope and a lower side-surface portion having the second slope. The third slope may be gentler (e.g., not as steep) than the first slope and the second slope, and the first slope and the second slope may be a vertical slope or an almost vertical slope. Therefore, the "slope changing portion" may be a portion having a gentle slope between the upper portion and the lower portion. For example, in the memory vertical structure 47, the lower vertical portion 47L may have a side surface having the first slope which may be vertical or almost vertical, the upper vertical portion 47U may have a side surface having the second slope which may be vertical or almost vertical, and the slope changing portion 47V may have a slope gentler than the first slope and the second slope.

[0104] On the same level as a level of the slope changing portion 47V of the middle side surface of the memory vertical structure 47, a side surface of each of the support vertical structure 61, the first to third peripheral contact plugs 87a, 87b, and 87c, the separation structures 77, and the dam structure 71, described above, may have a substantially linear shape or a monotonically changing shape with regularity.

[0105] The memory vertical structure 47 may include an insulating gap-fill layer 53, a channel layer 51 covering an external side surface and a bottom surface of the insulating gap-fill layer 53, a data storage structure 49 covering an external side surface and a bottom surface of the channel layer 51, and a pad material layer 55 on the insulating gap-fill layer 53.

[0106] The data storage structure 49 may include a first dielectric layer 49c covering the external side surface and the bottom surface of the channel layer 51, a data storage material layer 49b covering the external side surface and the bottom surface of the first dielectric layer 49c, and a second dielectric layer 49c covering the external side surface and the bottom surface of the storage material layer 49c. The first dielectric layer 49c may be in contact with the channel layer

51, and the data storage material layer 49b may be spaced apart from the channel layer 51. The insulating gap-fill layer 53 may include silicon oxide, such as for example, silicon oxide formed by an atomic layer deposition process, or silicon oxide having voids formed therein. The first dielectric layer 49a may include silicon oxide or silicon oxide doped with impurities. The second dielectric layer 49c may include at least one of silicon oxide and a high-k dielectric. The data storage material layer 49b may include a material for trapping charges and storing data, such as, for example, silicon nitride.

[0107] The data storage material layer 49b of the data storage structure 49 of the memory vertical structure 47 may include regions for storing data in a semiconductor device such as a flash memory device. The channel layer 51 may include polysilicon. The pad material layer 55 may include at least one of doped polysilicon, metal nitride (e.g., TiN, or the like), a metal (e.g., W, or the like), and a metal-semiconductor compound (e.g., TiSi, or the like). The pad material layer 55 may be electrically connected to and in contact with the bit line contact plug 96a.

[0108] The memory vertical structure 47 may penetrate the third pattern layer 17c and the second pattern layer 17b of the pattern structure 17 in order, and may extend into the first pattern layer 17a. In the pattern structure 17, the second pattern layer 17b may penetrate the data storage structure 49 and may be in contact with the channel layer 51.

[0109] The semiconductor device 1 according to an example embodiment of the present disclosure may further include a dielectric layer 56 covering an upper surface and a lower surface of each of the first and second gate layers 27g and 40g and disposed between a side surface of the memory vertical structure 47 and a side surface of each of the first and second gate layers 27g and 40g. The dielectric layer 56 may include a high-k dielectric having a dielectric constant higher than that of silicon oxide. For example, the dielectric layer 56 may be formed of a high-k dielectric such as aluminum oxide, lanthanum oxide, or hafnium oxide.

[0110] In the description below, with reference to FIG. 3B, an example of the support vertical structure 61 and the capping layer 63 described above will be described. FIG. 3B is an enlarged diagram illustrating region "B" in FIG. 2B.

[0111] Referring to FIGS. 2B and 3B, as described above, the support vertical structure 61 may include the air gap 69a and the support layer 65a defining at least a portion of the air gap 69a, and the capping layer 63 may include the lower capping layer 65c and the upper capping layer 67. For example, the support layer 65a may limit at least a lower portion and a sidewall of the air gap 69a.

[0112] The support layer 65a may extend continuously from the lower capping layer 65c. The upper capping layer 67 may limit an upper portion of the air gap 69a.

[0113] The lower capping layer 65c and the support layer 65a may be formed of the same material. The lower capping layer 65c and the support layer 65a may be integrated with each other. For example, the lower capping layer 65c and the support layer 65a may be formed of a material layer continuously extending without a boundary surface. For example, the lower capping layer 65c and the support layer 65a may include an insulating material layer.

[0114] In an example, the lower capping layer 65c and the support layer 65a may be formed of a silicon oxide layer.

[0115] In another example, the lower capping layer 65cand the support layer 65a may be formed of a silicon nitride

[0116] In another example, the lower capping layer 65cand the support layer 65a may be formed in a multilayer structure, such as, for example, a multilayer structure of a silicon oxide layer and a silicon nitride layer.

[0117] A maximum thickness of the lower capping layer **65**c may be greater than a minimum thickness of the support layer 65a. The support layer 65a may have a maximum thickness in a portion adjacent to the lower capping layer 65c. be support layer 65a may have a minimum thickness in a portion far from the lower capping layer 65c.

[0118] The upper capping layer 67 may include a material layer formed by a method different from a method of forming the lower capping layer 65c. For example, the lower capping layer 65c may include a silicon oxide layer formed by an atomic layer deposition process (ALD), and the upper capping layer 67 may include a silicon oxide layer formed by a chemical vapor deposition process (CVD).

[0119] In one example, an upper end of the air gap 69a may be disposed on a level higher than a level of the upper surface of the memory vertical structure 47. In one example, the air gap 69a may extend upwardly from a portion disposed in the support hole 60s, and an upper end 69t of the air gap 69a may be disposed on a level higher than a level of the upper surface of the first upper insulating layer 58. The upper end 69t of the air gap 69a may come to point and be narrower than other portions of the air gap 69a therebe-

[0120] In an example, the upper end 69t of the air gap 69amay be disposed on a level higher than a level of the upper surface of the lower capping layer 65c.

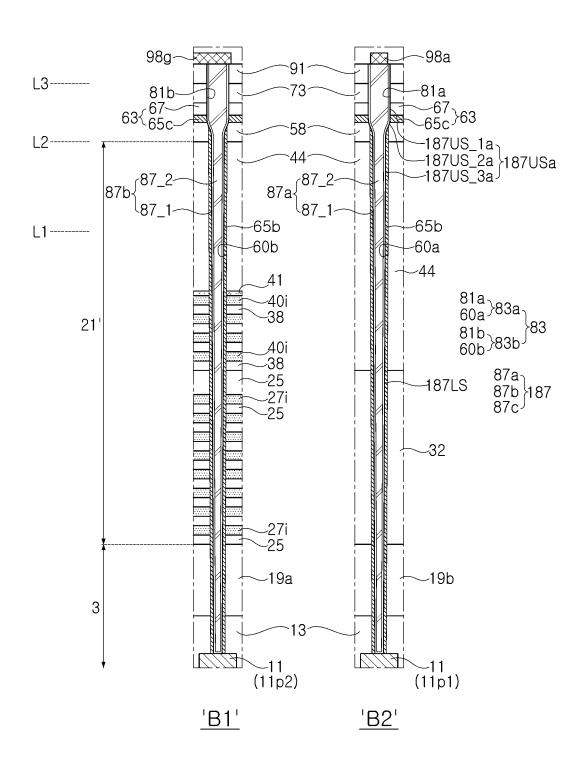

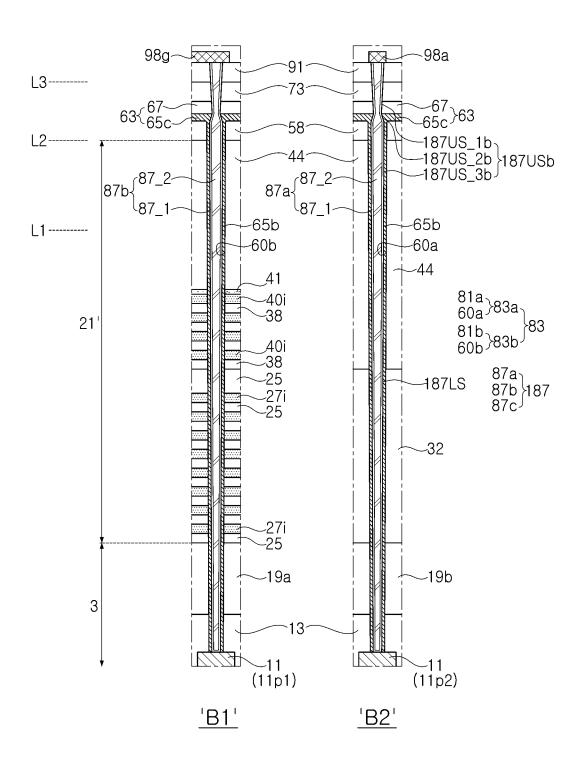

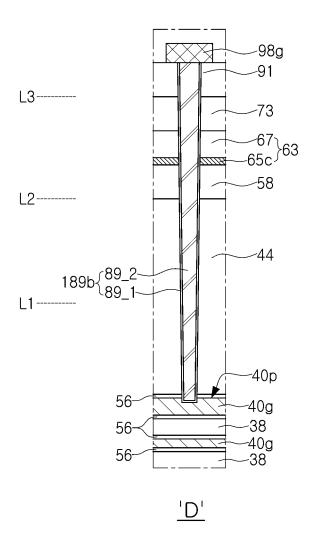

[0121] In the description below, examples of the peripheral contact plugs 87, the first to third peripheral upper plugs 95a, 95b, and 95c, and the spacer layer 65b, and the gate contact plugs 89, described above, will be described with reference to FIGS. 3C and 3D. FIG. 3C is an enlarged diagram illustrating regions "C1" and "C2" in FIG. 2A, and FIG. 3D is an enlarged diagram illustrating region "D" in FIG. **2**A.

[0122] Referring to FIGS. 2A, 3C and 3D, each of the peripheral contact plugs 87 may include a lower region 87LS disposed below a first level L1 and an upper region 87US disposed above the first level L1. For example, in each of the peripheral contact plugs 87, the upper region 87US may be disposed on a level higher than a level of the upper surface of the uppermost gate layer 40g among the first and second gate layers 27g and 40g, the lower region 87LS may be disposed on a level lower than a level of the upper surface of the uppermost gate layer 40g.

[0123] In the description below, the lower region 87LS and the upper region 87US of one of the peripheral contact plugs 87 will be mainly described.

[0124] A side-surface profile of the lower region 87LS may be different from a side-surface profile of the upper region 87US. For example, the lower region 87LS may have a substantially vertical side surface, and the upper region 87US may have at least one curved side surface. For example, the upper region 87US may include a first region 87US\_1, a connection region 87US\_2 disposed below the first region 87US\_1, and a second region 87US\_3 disposed below the connection region 87US\_2. A side surface of the connection region 87US\_2 may have a slope different from at least one of a side surface of the first region 87US\_1 and a side surface of the second region 87US\_2. For example, a side surface of the connection region 87US\_2 may have a slope different from a side surface of the first region 87US\_1 having a first slope and a side surface of the second region 87US 2 having a second slope. For example, the side surface of the first region 87US\_1 and the side surface of the second region 87US\_2 may have a vertical slope or an almost vertical slope which may be steep, and the side surface of the connection region 87US\_2 may have a gentle slope. In example embodiments of the present disclosure, the expression "substantially perpendicular" may indicate the configuration of being substantially perpendicular to the upper surface of the lower structure 3 or the upper surface of the semiconductor substrate 4. For example, forming the plug may include forming a hole by an anisotropic etching process and forming a plug in the hole, and the side surface profile of the plug may be a side-surface profile of the hole formed by the anisotropic etching process. The side surface of the hole formed by the anisotropic etching process may be perpendicular to or may be almost perpendicular to the upper surface of the semiconductor substrate 4. Accordingly, the expression "substantially perpendicular" may indicate the configuration of being perpendicular to the upper surface of the semiconductor substrate 4, but the present disclosure is not limited thereto, and the expression may refer to a shape of a side surface of the hole formed within a range of a process margin of an anisotropic etching process, which may be, for example, a shape almost perpendicular to the upper surface of the semiconductor substrate 4, such as a shape almost perpendicular to the upper surface of the semiconductor substrate 4 and having a constant slope or a shape almost perpendicular to the upper surface of the semiconductor substrate 4 and having a slope that changes. [0125] At least a portion of the first region 87US\_1 may be in contact with the second upper insulating layer 73 and the

upper capping layer 67.

[0126] The first region 87US\_1 may be in contact with the second upper insulating layer 73, the upper capping layer 67, and the lower capping layer 65c. The first region 87US\_1 may extend from the connection region 87US\_2 and contact the lower capping layer 65c, the upper capping 67 and the second upper insulating layer 73 in sequence.

[0127] The side surface of the first region 87US 1 and the side surface of the second region 87US 3 may not be aligned in the vertical direction Z.

[0128] At least a portion of the connection region 87US\_2 may be disposed on a level lower than that of the lower capping layer 65c.

[0129] At least a portion of the connection region  $87 \mathrm{US}\_2$ may be disposed on a level higher than that of the second level L2.

[0130] A maximum width of the upper region 87US may be greater than a maximum width of the lower region 87LS. [0131] In the upper region S7US, the first region 87US\_1 may have a minimum width greater than a minimum width of the connection region 87US\_2, and the second region 87US\_3 may have a maximum width less than a maximum width of the connection region 87US\_2.

[0132] The gate contact plugs 89 disposed on the same level as a level of the upper region 87US may have a side-surface profile different from that of the upper region 87US. For example, each region of the gate contact plugs 89 disposed on the same level as a level of the upper region

**87**US of the peripheral contact plug **87** may have a side surface having a substantially vertical slope.

[0133] The spacer layer 65b may surround a side surface of the lower region 87LS, may extend upwardly, and may cover a portion of a side surface of the upper region 87US. For example, the spacer layer 65b may cover a side surface of the second region 87US\_3 of the upper region 87US, and may be disposed on a level lower than the first region 87US\_1 of the upper region 87US and may be spaced apart from the first region 87US\_1.

[0134] The spacer layer 65b may cover at least a portion of the connection region 87US\_2 of the upper region 87US. For example, the spacer layer 65b may cover a side surface of a lower portion of the connection region 87US\_2 and may not cover a side surface of an upper portion of the connection region 87US\_2.

[0135] Each of the first to third peripheral upper plugs 95*a*, 95*b*, and 95*c* may have a width different from each of the peripheral contact plugs 87. For example, a width of each of the first to third peripheral upper plugs 95*a*, 95*b* and 95*c* may be smaller than a width of each of the peripheral contact plugs 87.

[0136] Each of the peripheral contact plugs 87 may include a plug pattern 87\_2 and a conductive liner 87\_1 covering a side surface and a bottom surface of the plug pattern 87\_2. Each of the gate contact plugs 89 may include a plug pattern 89\_2 and a conductive liner 89\_1 covering a side surface and a bottom surface of the plug pattern 89\_2. [0137] In an example, the peripheral contact plugs 87 and the gate contact plugs 89 may be simultaneously formed. Accordingly, the peripheral contact plugs 87 and the gate contact plugs 89 may be formed of the same material.

[0138] In an example, upper surfaces of the peripheral contact plugs 87 may be coplanar with upper surfaces of the gate contact plugs 89. For example, the upper surfaces of the peripheral contact plugs 87 and the gate contact plugs 89 may be disposed on the third level L3.

[0139] In example embodiments of the present disclosure, the bit line contact plug 96a, the gate upper plugs 96b, and the first to third peripheral upper plugs 95a, 95b, and 95c may be formed simultaneously and may include the same material. For example, each of the bit line contact plug 96a, the gate upper plugs 96b, and the first to third peripheral upper plugs 95a, 95b and 95c may include a plug pattern 95\_2 and a conductive liner 95\_1 covering a bottom surface and a side surface of the plug pattern 95\_2. The conductive line 95\_1 may be in direct contact with the peripheral contact plug 87 or the gate contact plug 89 therebelow. The bit line contact plug 96a, the gate upper plugs 96b, and the first to third peripheral upper plugs 95a, 95b, and 95c may have upper surfaces coplanar with each other.

[0140] In the description below, various modifications of the support vertical structure 61 and the capping layer 63 described above will be described with reference to FIGS. 4A, 4B, 5A and 5B. FIGS. 4A, 4B, 5A and 5B are enlarged diagrams illustrating a modified portion of the example in the enlarged diagram in FIG. 3B. Various modified structures described below with reference to FIGS. 4A, 4B, 5A, and 5B may replace the structure in FIG. 3B.

[0141] In a modified example, referring to FIG. 4A, the lower capping layer 65c described with reference to FIG. 3B may be replaced with a lower capping layer 65c' including a first layer 65c1 and a second layer 65c2 on the first layer 65c1. The support layer 65a described with reference to FIG.

3B may be replaced with a support layer  $65a^{1}$  including a first layer 65a1 and a second layer 65a2 on the first layer 65a1. The first layer 65a1 of the support layer  $65a^{1}$  and the first layer  $65c^{1}$  of the lower capping layer  $65c^{1}$  may be integrated with each other, and the second layer  $65a^{2}$  of the support layer  $65a^{1}$  and the second layer  $65c^{2}$  of the lower capping layer  $65c^{1}$  may be integrated with each other.

[0142] In an example, the first layers 65a1 and 65c1 and the second layers 65a2 and 65c2 may be formed as material layers having different step coverages. For example, one of the first layers 65a1 and 65c1 and the second layers 65a2 and 65c2 may have a step coverage higher than the other. For example, one of the first layers 65a1 and 65c1 and the second layers 65a2 and 65c2 may be formed to have a uniform thickness as compared to a thickness of the other layer.

[0143] In an example, the first layers 65a1 and 65c1 and the second layers 65a2 and 65c2 may be formed of the same type of material. For example, the first layers 65a1 and 65c1 may be formed of a silicon oxide layer having a uniform thickness as compared to that of the second layers 65a2 and 65c2, and the second layers 65a2 and 65c2 may be formed of silicon oxide layer having a non-uniform thickness as compared to that of the first layers 65a1 and 65c1. In another example, the first layers 65a1 and 65c1 and the second layers 65a2 and 65c2 may be formed of different materials. For example, the first layers 65a1 and 65c1 may be formed of a silicon oxide layer, and the second layers 65a2 and 65c2may be formed of a different material from the silicon oxide layer, such as, for example, a silicon nitride layer, a silicon oxynitride layer, or a silicon nitride layer including carbon. The spacer layer 65b (in FIG. 3C) described above may be formed of the same material as that of the support layer 65a'. Accordingly, the spacer layer 65b (in FIG. 3C) may be modified to include the same first layer and the second layer as those of the support layer 65a'.

[0144] In another modified example, referring to FIG. 4B, the capping layer 63 including the lower capping layer 65c and the upper capping layer 67 described with reference to FIG. 3B, and the support layer 65a may be replaced by a capping layer 63' and a support layer 65a", which may limit the air gap 69a by a single material layer. For example, the support layer 65a" may be integrated with the capping layer 63'. For example, in FIG. 3B, the upper capping layer 67 formed by a process different from the process of forming the support layer 65a may limit an upper portion of the air gap 69a, but in FIG. 4B, the capping layer 63' formed by the same process as the process of forming the support layer 65a" may limit an upper portion of the air gap 69a.

[0145] In another modified example, referring to FIG. 5A, the support vertical structure 61 described with reference to FIG. 3B may be replaced with a support vertical structure 61' including an air gap 69a', a support layer 65a defining a portion of the air gap 69a', and an upper gap-fill layer 67a defining an upper portion of the air gap 69a'. The capping layer 63 including the lower capping layer 65c and the upper capping layer 67 described with reference to FIG. 3B may be replaced with a capping layer 63' including an upper capping layer 67' extending from the upper gap-fill layer 67a.

[0146] In an example, the upper end 69t of the air gap 69 may be lower than the second level L2, and may be higher than the first level L1. In this case, the upper gap-fill layer

67a may be provided on the upper end 69t' of the air gap 69' between the first level L1 and the second level L2.

[0147] In another modified example, referring to FIG. 5B, the support vertical structure 61' described with reference to FIG. 3A may be replaced with a support vertical structure 61" including an air gap 69a" having an upper end 69t" lower than the first level L1, a support layer 65a defining a portion of the air gap 69a", and an upper gap-fill layer 67a' defining an upper portion of the air gap 69a".

[0148] In the description below, various modified examples of the peripheral contact plug 87 and/or the spacer layer 65b described above will be described with reference to FIGS. 6A, 6B, 7A and 7B. FIGS. 6A, 6B, 7A and 7B are enlarged diagrams illustrating a modified portion of the example in the enlarged diagram in FIG. 3C. Various modified structures described below with reference to FIGS. 6A, 6B, 7A and 7B may replace the structure in FIG. 3C.

[0149] In a modified example, referring to FIG. 6A, in the peripheral contact plug 87 including the lower region 87LS and the upper region 87US described with reference to FIG. 3C, the upper region 87US may be replaced with the same shape as that of the upper region 87US' in FIG. 6A.

[0150] The upper region 87US' may include a second region 87US\_3', a connection region 87US\_2' on the second region 87US\_3', and a first region 87US\_1' on the connection region 87US\_2'. The connection region 87US\_2' may have a concave side surface. For example, in the upper region 87U', the connection region 87US\_2' may have a concave side surface in a direction toward a center of the upper region 87U' as compared to the first and second regions 87US\_1' and 87US\_3'. In the upper region 87U', a minimum width of the connection region 87US\_2' may be smaller than a width of the second region 87US\_3' adjacent to the connection region 87US\_2'.

[0151] In the upper region 87US', a minimum width of the connection region 87US\_2' may be smaller than a minimum width of the first region 87US\_1'.

[0152] In the upper region 87US', a width of the first region 87US\_1' may be greater than a width of the second region 87US\_3'.

[0153] The spacer layer 65b described with reference to FIG. 3C may be replaced with a spacer layer 65b' which may not cover the lower region 87LS and may cover the side surface of the connection region 87US\_2'. For example, the spacer layer 65b' may fill the concave side surface of the connection region 87US\_2'.

[0154] In a modified example, referring to FIG. 6B, the spacer layer 65b describes with reference to FIG. 3C may not be provided. For example, the peripheral contact plugs 87 may include a portion in direct contact with the second structure 21'.

[0155] In a modified example, referring to FIG. 7A, in the peripheral contact plug 87 including the lower region 87LS and the upper region 87US described with reference to FIG. 3C, the upper region 87US may be replaced with the same shape as that of the upper region 87USa in FIG. 7A.

[0156] The upper region 87USa may include a second region 87US\_3a, a connection region 87US\_2a on the second region 87US\_3a, and a first region 87US\_1a on the connection region 87US\_2a.

[0157] In the upper region 87USa, a minimum width of the first region 87US\_1a may be smaller than a maximum width of the connection region 87US\_2a, a maximum width of the second region 87US\_3a may be greater than a minimum

width of the connection region 87US\_2a, and the maximum width of the second region 87US\_3a may be greater than the maximum width of the first region 87US\_1a. The spacer layer 65b described with reference to FIG. 3C may be continuously connected to and integrated with the capping layer 65c.

[0158] In a modified example, referring to FIG. 7B, in the peripheral contact plug 87 including the lower region 87LS and the upper region 87US described with reference to FIG. 3C, the upper region 87US may be replaced with the same shape as that of the upper region 87USb in FIG. 7B, and the spacer layer 65b described with reference to FIG. 3C may be replaced by a spacer layer 65b" as in FIG. 7B.

[0159] The upper region 87USb may include a second region 87US\_3b, a connection region 87US\_2b on the second region 87US\_3b, and a first region 87US\_1b on the connection region 87US\_2b, and a width of the first region 87US\_1b may be smaller than a width of the second region 87US\_3b. The connection region 87US\_2b may have a tapered shape that narrows as it approaches the first region 87US\_1b.

[0160] The spacer layer 65b" may cover at least a portion of the side surface of the connection region 87US\_2b. The spacer layer 65b" may not cover an entire side surface of the second region 87US\_3b or may not cover a portion of the side surface of the second region 87US\_3b. The peripheral contact plug 87 disposed below the spacer layer 65b" may include a portion in contact with the second structure 21'. The spacer layer 65b" may be continuously connected to and integrated with the lower capping layer 65c.

[0161] In a modified example, referring to FIG. 7C, in the peripheral contact plug 87 including the lower region 87LS and the upper region 87US described with reference to FIG. 3C, the upper region 87US may be replaced with the upper region 87USc extending from the lower region 87LS to have a constant width or to have a monotonically changing width. For example, the side surface of the peripheral contact plug 87 including the lower region 87LS and the upper region 87USc may have a substantially linear shape or a monotonically changing shape with regularity.

[0162] In the description below, a modified example of the peripheral contact plug 87 described above will be described with reference to FIG. 8A. FIG. 8A is an enlarged diagram illustrating a modified portion of the example in the enlarged diagram in FIG. 3C. The modified structure of the peripheral contact plug 87 described below with reference to FIG. 8A may replace the structure of the peripheral contact plug 87 in FIG. 3C and also the structure of the peripheral contact plug 87 described with reference to FIGS. 6A to 7C.

[0163] In the modified example, referring to FIG. 8A, the peripheral contact plug 87 described with reference to FIG. 3C or the peripheral contact plug 87 described with reference to FIGS. 6A to 7C may be replaced with a peripheral contact plug 87' further including an air gap 87\_3. For example, the peripheral contact plug 87' may include a plug pattern 87\_2, a conductive liner 87\_1 covering a side surface and a bottom surface of the plug pattern 87\_2, and an air gap 87\_3 in the plug pattern 87\_2.

[0164] In the peripheral contact plug 87, an upper end of the air gap  $87\_3$  may be lower than the second level L2.

[0165] In the peripheral contact plug 87', an upper end of the air gap 87\_3 may be higher than the first level L1.

[0166] In the description below, a modified example of the peripheral contact plug 87 described above will be described

with reference to FIG. 8B. FIG. 8B is an enlarged diagram illustrating a modified portion of the example in the enlarged diagram in FIG. 7A. The modified structure of the peripheral contact plug 87 described below with reference to FIG. 8B may replace the structure of the peripheral contact plug 87 in FIG. 7A, and also the structure of the peripheral contact plug 87 described with reference to FIGS. 3C, 6A, 6B, 7B, and 7C.

[0167] In a modified example, referring to FIG. 8B, the peripheral contact plug 87 described with reference to FIG. 7A or the peripheral contact plug 87 described with reference to FIGS. 3A, 6A, 6B, 7B and 7C may be replaced with a peripheral contact plug 87" further including a lower air gap 87\_3 and an upper air gap 87\_4. For example, the peripheral contact plug 87" may include a plug pattern 87\_2, a conductive liner 87\_1 covering a side surface and a bottom surface of the plug pattern 87\_2, and the lower air gap 87\_3 and the upper air gap 87\_4 disposed in the plug pattern 87\_2 and spaced apart from each other. In other words, the lower air gap 87\_3 and the upper air gap 87\_4 constitute two separate air gaps.

[0168] In the peripheral contact plug 87", an upper end of the lower air gap 87\_3 may be lower than the second level 1.2.

[0169] In the peripheral contact plug 87", the upper end of the lower air gap 87\_3 may be higher than the first level L1. [0170] In the peripheral contact plug 87", the upper air gap 87\_4 may be higher than the second level L2. An upper end of the upper air gap 87\_4 may be lower than the third level L3. In the alternative, the upper end of the upper air gap 87\_4 may be higher than the third level L3.

[0171] In the description below, a modified example of the above-described peripheral contact plug 87 will be described with reference to FIGS. 9A and 9B. FIG. 9A is an enlarged diagram illustrating a modified portion of the example in the enlarged diagram in FIG. 3C, and FIG. 9B is an enlarged diagram illustrating a modified portion of the example in the enlarged diagram in FIG. 7A. The modified structure of the peripheral contact plug 87 described below with reference to FIGS. 9A and 9B, a structure in which the level of the upper surface is increased, for example, may be reflected in the structure of the peripheral contact plug 87 in FIGS. 3C and 7A and also in the peripheral contact plugs 87, 87' and 87" described with reference to FIGS. 6A, 6B, 7B, 7C, 8A, and 8B. For example, the level of the upper surfaces of the peripheral contact plugs 87, 87', and 87" described with reference to FIGS. 6A, 6B, 7B, 7C, 8A, and 8B may be modified to increase.

[0172] In a modified example, referring to FIG. 9A, the peripheral contact plug 87 including the upper region 87US described with reference to FIG. 3C may be replaced with a peripheral contact plug 187 including an upper region 187USa including an upper surface disposed on a higher level than previously described peripheral contact plugs. The peripheral contact plug 187 may include a lower region 187LS substantially the same as the lower region 87LS described with reference to FIG. 3C.

[0173] The upper region 187USa may include a second region 187US\_3a and a connection region 187US\_2a substantially the same as the second region 87US\_3 and the connection region 87US\_2 described with reference to FIG. 3C, and may include a first region 187US\_1a disposed on a level higher than a level of the first region 87US\_1 described with reference to FIG. 3C.

[0174] The upper region 187USa may have an upper surface coplanar with the upper surface of the third upper insulating layer 91. The upper surface of the upper region 187USa of the peripheral contact plug 187 may be higher than the third level L3.

[0175] The peripheral contact plug 187 may have upper surfaces disposed on a level higher than upper surfaces of the gate contact plugs 89 (in FIG. 2A).

[0176] In a modified example, referring to FIG. 9B, the peripheral contact plug 87 including the upper region 87USa described with reference to FIG. 7A may be replaced with a peripheral contact plug 187 including an pp region 187USb having an upper surface disposed on a higher level than some of the previously described peripheral contact plugs.

[0177] Similarly to the upper region 187USa described with reference to FIG. 9A, the upper region 187USb may include a second region 187US\_3b and a connection region 187US\_2b, which may be substantially the same as the second region 87US\_3a and the connection region 87US\_2a described with reference to FIG. 7A, and may include a first region 187US\_1b disposed on a level higher than a level of the first region 87US\_1a described with reference to FIG. 7A. The first region 187US\_1b of FIG. 9B may be narrower than the first region 187US\_1a of FIG. 9A.

[0178] In the description below, a modified example of the gate contact plug 89 described above will be described with reference to FIGS. 10A and 10B. FIGS. 10A and 10B are enlarged diagrams illustrating a modified portion of the example in the enlarged diagram in FIG. 3D.

[0179] In a modified example, referring to FIG. 10A, the gate contact plug 89 described with reference to FIG. 3D may be replaced with a gate contact plug 189a having an upper surface disposed on a lower level than the gate contact plug 89. The gate contact plug 189a may have an upper surface coplanar with the upper surface of the capping layer 63. In other words, the upper surface of the gate contact plug 189a may not extend beyond the second upper insulating layer 73. Accordingly, the upper surface of the gate contact plug 189a may be disposed on a level lower than a level of the upper surfaces of the peripheral contact plugs 87, 87', 87", and 187 of the various examples described in FIGS. 3C, 6A, 6B, 7A, 7B, 7C, 8A, 8B, 9A, and 9B.

[0180] In a modified example, referring to FIG. 10B, the gate contact plug 89 described with reference to FIG. 3D may be replaced with a gate contact plug 189b having an upper surface disposed on a higher level than the gate contact plug 89. The gate contact plug 189b may have an upper surface coplanar with an upper surface of the third upper insulating layer 91. In this case, the upper surface of the gate contact plug 189a may extend beyond the second upper insulating layer 73. For example, the gate contact plug 189b may have an upper surface coplanar with the upper surface of the peripheral contact plug 187 of the various examples described with reference to FIGS. 9A and 9B.