#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/116867 A1

- (43) International Publication Date 31 July 2014 (31.07.2014)

- (51) International Patent Classification: *H03K 17/12* (2006.01) *H02J 1/00* (2006.01) *H02M 1/00* (2007.01)

- (21) International Application Number:

PCT/US2014/012804

(22) International Filing Date:

23 January 2014 (23.01.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/752,267 28 January 2013 (28.01.2013)

US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

- (72) Inventor: RUTKOWSKI, Joseph D.; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: WALSH, Chad R.; 900 Lafayette St., Ste. 301, Santa Clara, California 95050 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV,

[Continued on next page]

#### (54) Title: DYNAMIC SWITCH SCALING FOR SWITCHED-MODE POWER CONVERTERS

(57) Abstract: Techniques for optimizing the trade-off between minimizing switching losses and minimizing conduction losses in a buck converter. In an aspect, each of a high-side switch and a low-side switch may be implemented as a plurality of parallel-coupled transistors, each transistor having an independently controllable gate voltage, allowing adjustment of the effective transistor size. In response to the target voltage of the buck converter corresponding to a relatively high voltage range, more high-side switch transistors and fewer low-side switch transistors may be selected. Similarly, in response to the target voltage corresponding to a relatively low voltage range, more low-side switch transistors and fewer high-side switch transistors may be selected. In an aspect, the techniques may be applied during a pulse-frequency modulation mode.

FIG 3

##

MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, Published: SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

# DYNAMIC SWITCH SCALING FOR SWITCHED-MODE POWER CONVERTERS

#### CROSS REFERENCE TO RELATED APPLICATIONS

[0001] The present disclosure claims priority to U.S. Nonprovisional App. No. 13/752,267 filed January 28, 2013, the content of which is incorporated herein by reference in its entirety for all purposes.

#### **BACKGROUND**

#### **Field**

[0002] The disclosure relates to techniques for increasing power efficiency in a switched-mode power converter.

#### **Background**

[0003] Buck converters are a type of switched-mode power converter designed to efficiently step down a supply voltage, e.g., a battery voltage of a system, from a first level to a second lower level. A buck converter typically includes a high-side switch and a low-side switch configured to alternately couple an inductor to an output voltage or ground. The high-side and low-side switches may be configured to drive the output voltage to a predetermined target output voltage using a plurality of schemes known in the art, e.g., pulse-width modulation (PWM), pulse-frequency modulation (PFM), etc.

[0004] In a PFM mode of operation, the high-side and low-side switches are configured to vary the frequency of a train of pulses that charge and discharge the inductor. In PFM, there are at least two sources of power losses affecting the efficiency of the buck converter circuit. First, turning the switches on and off to generate the train of pulses leads to "switching losses," due to the current required to charge and discharge various capacitances in the switches. Second, sinking or sourcing DC current through the switches leads to "conduction losses," arising from the finite on-resistance of the switches themselves. Together, such losses undesirably decrease the power efficiency of the buck converter circuit as well as other types of switched-mode power converters.

[0005] It would be desirable to provide techniques for optimizing the operation of a switched-mode power converter such as a buck converter employing high-side and/or low-side switches to improve the overall power efficiency of the circuit.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

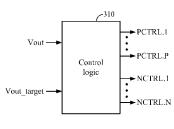

[0006] FIG 1 illustrates a prior art implementation of a buck converter.

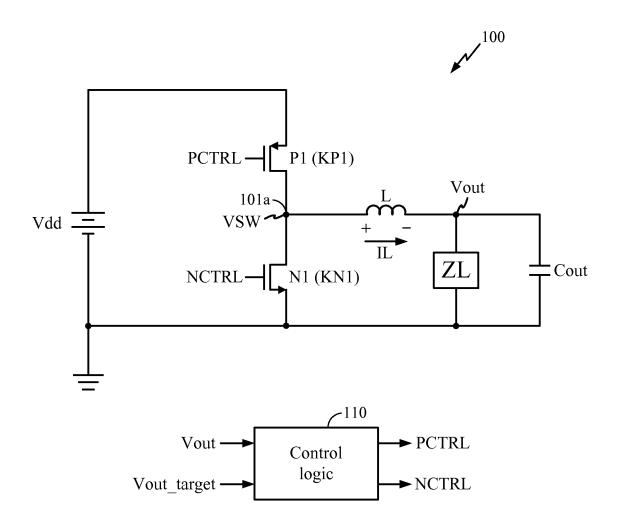

[0007] FIG 2 illustrates exemplary signaling waveforms for PCTRL and NCTRL showing certain aspects of the present disclosure.

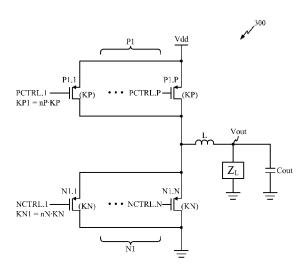

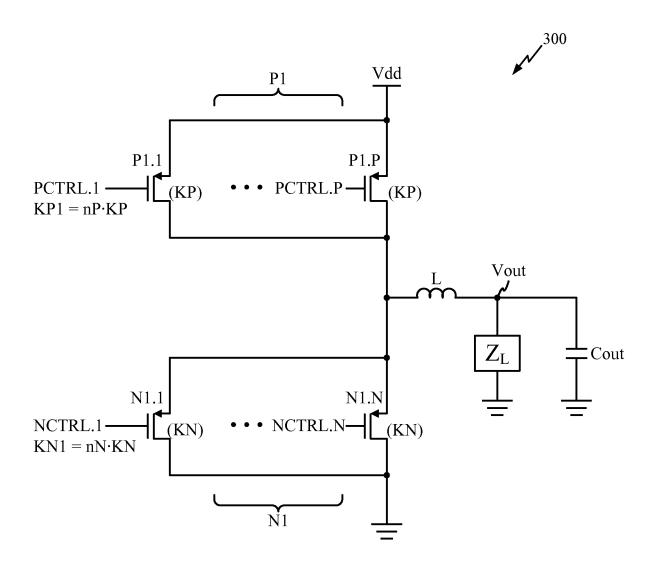

[0008] FIG 3 illustrates an exemplary embodiment of a dynamic switch size adjustment apparatus according to the present disclosure.

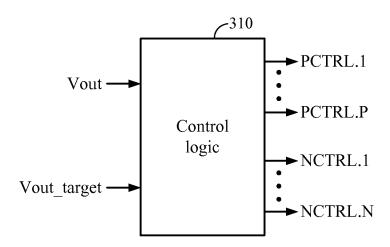

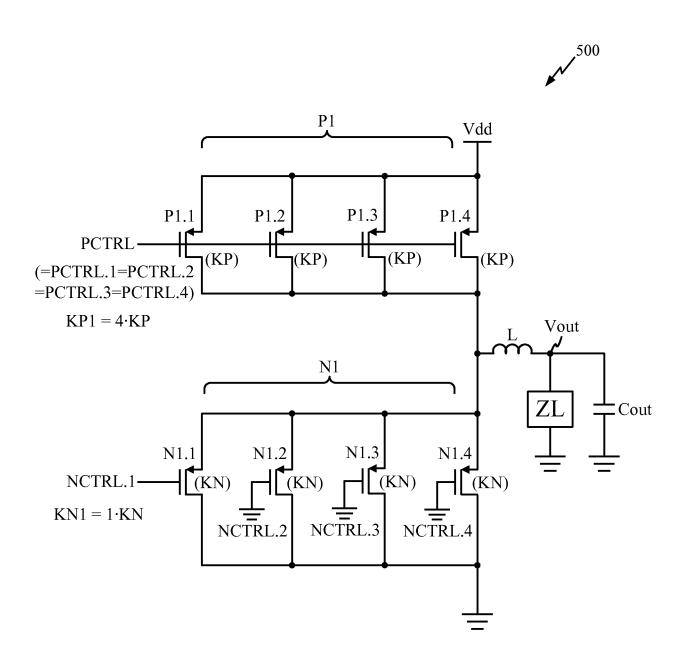

[0009] FIG 4 illustrates an exemplary embodiment of a method that may be implemented by the control logic block.

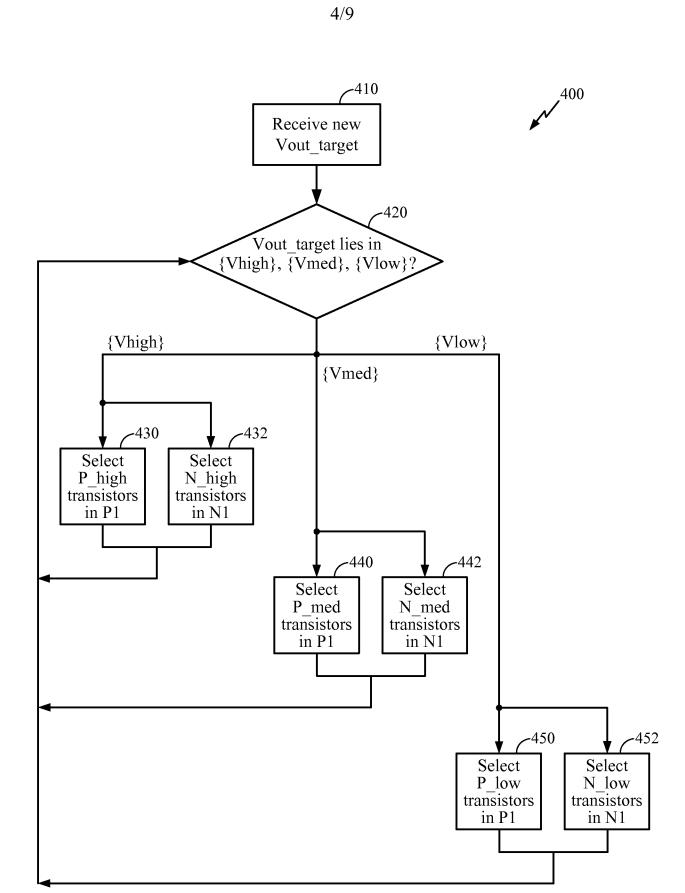

[0010] FIG 5 illustrates an exemplary configuration of transistors according to the present disclosure, wherein the target output voltage lies in the high range {Vhigh}.

[0011] FIG 6 illustrates an exemplary configuration of transistors according to the present disclosure, wherein the target output voltage lies in the medium range {Vmed}.

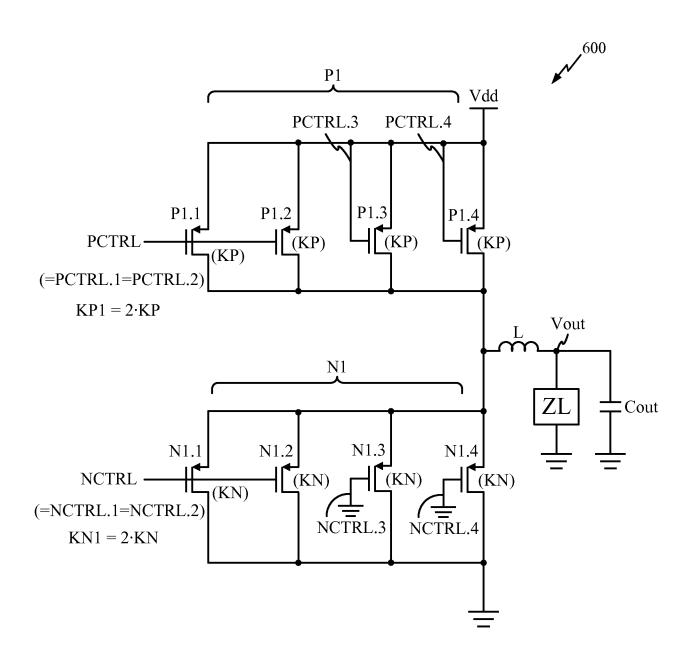

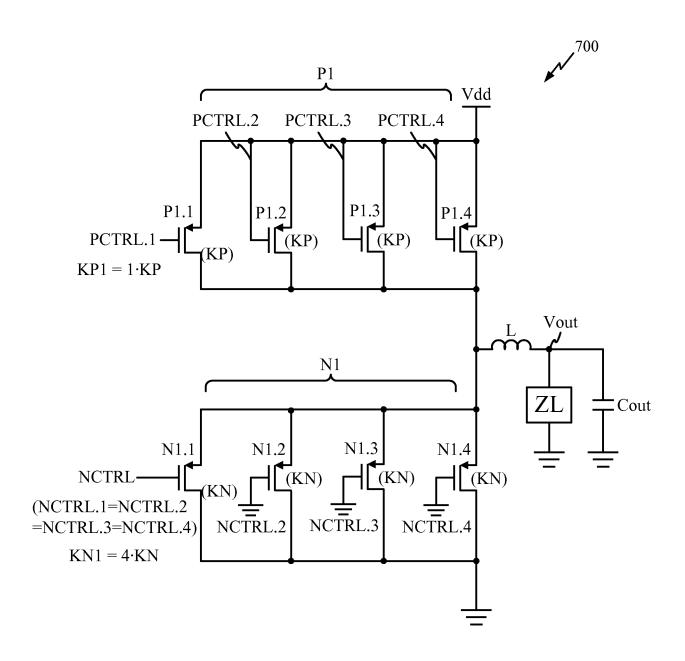

[0012] FIG 7 illustrates an exemplary configuration of transistors according to the present disclosure, wherein the target output voltage lies in the low range {Vlow}.

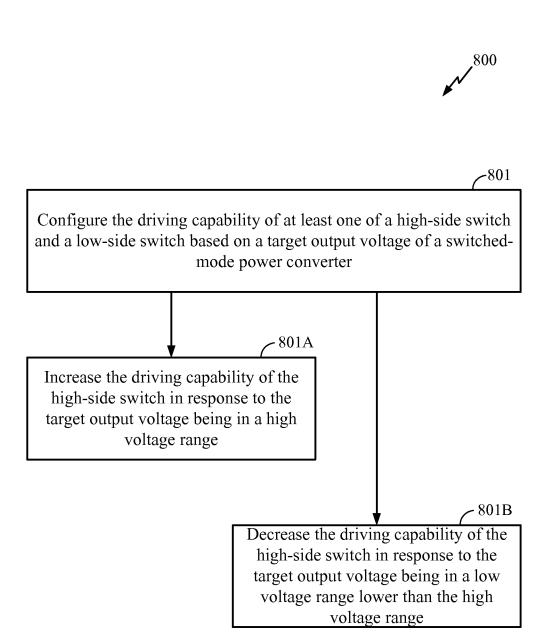

[0013] FIG 8 illustrates an exemplary embodiment of a method according to the present disclosure.

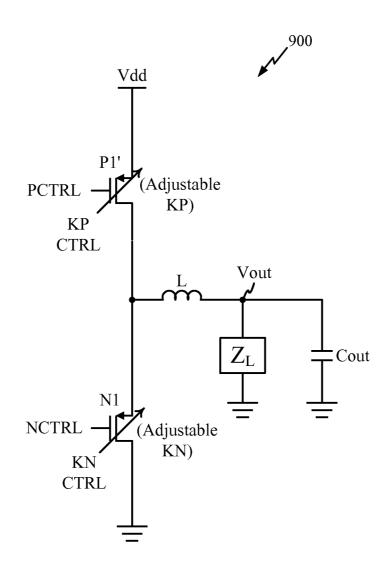

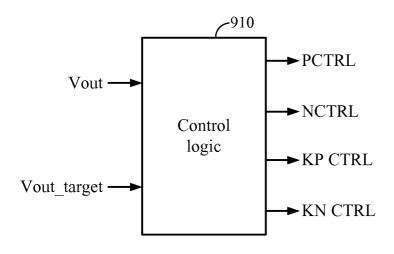

[0014] FIG 9 illustrates an alternative exemplary embodiment according to the present disclosure, wherein the switch sizes are generally adjustable without limitation to any particular technique for switch size adjustment.

#### **DETAILED DESCRIPTION**

[0015] Various aspects of the disclosure are described more fully hereinafter with reference to the accompanying drawings. This disclosure may, however, be embodied in many different forms and should not be construed as limited to any specific structure or function presented throughout this disclosure. Rather, these aspects are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the disclosure to those skilled in the art. Based on the teachings herein one skilled in the art should appreciate that the scope of the disclosure is intended to cover any aspect of the disclosure disclosed herein, whether implemented independently of or combined with any other aspect of the disclosure. For example, an apparatus may be implemented or a method may be practiced using any number of the aspects set forth herein. In addition, the scope of the disclosure is intended to cover such an apparatus or method which is practiced using other structure, functionality, or structure and functionality in addition to or other than the various

aspects of the disclosure set forth herein. It should be understood that any aspect of the disclosure disclosed herein may be embodied by one or more elements of a claim.

[0016] The detailed description set forth below in connection with the appended drawings is intended as a description of exemplary aspects of the invention and is not intended to represent the only exemplary aspects in which the invention can be practiced. The term "exemplary" used throughout this description means "serving as an example, instance, or illustration," and should not necessarily be construed as preferred or advantageous over other exemplary aspects. The detailed description includes specific details for the purpose of providing a thorough understanding of the exemplary aspects of the invention. It will be apparent to those skilled in the art that the exemplary aspects of the invention may be practiced without these specific details. In some instances, well-known structures and devices are shown in block diagram form in order to avoid obscuring the novelty of the exemplary aspects presented herein. In this specification and in the claims, the terms "module" and "block" may be used interchangeably to denote an entity configured to perform the operations described.

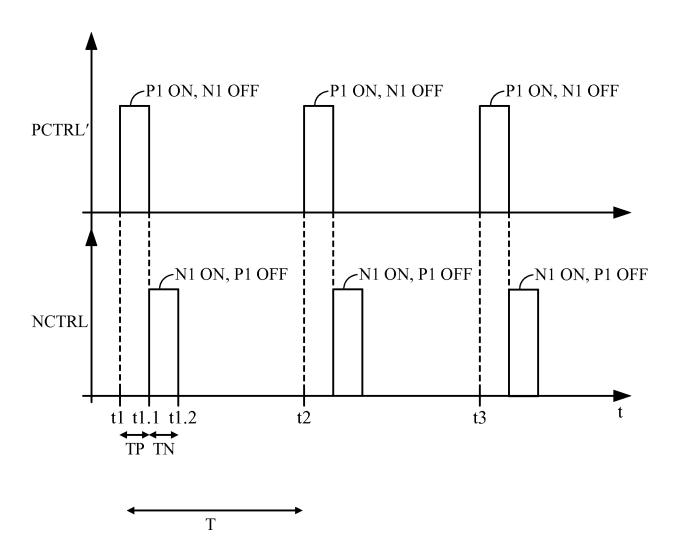

[0017] FIG 1 illustrates a prior art implementation of a buck converter 100. Note FIG 1 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular buck converter topology shown. In this specification and in the claims, the term "switch" may include a "transistor switch," or it may include other types of switches, e.g., scaling relays etc.

[0018] In FIG 1, the buck converter 100 includes switching transistors P1 (also denoted the "high-side switch") and N1 (also denoted the "low-side switch") coupled to an inductor L at a switching node 101a, at which a switching voltage VSW is present. The inductor L is coupled to a load ZL and capacitor Cout, which support an output voltage Vout. Per normal buck converter operation, during a charging phase (e.g., of duration TP) of a cycle (e.g., of duration T), P1 is on and N1 is off, and the switching node 101a couples the inductor L to Vdd through P1. During a discharging phase (e.g., of duration TN) of the cycle, N1 is on and P1 is off, and the switching node 101a thereby couples the inductor L to ground.

[0019] P1 and N1 are coupled to gate control voltages PCTRL and NCTRL, respectively. To configure PCTRL and NCTRL, a control logic block 110 may implement a scheme known as pulse-frequency modulation (PFM) under relatively light load conditions, e.g., low load current or large ZL. According to one implementation of PFM, block 110 may turn on P1 to cause the inductor current IL to ramp up to a pre-defined level, and then turn

off P1. Subsequently, block 110 may turn on N1 to allow the inductor current IL to ramp down to zero, and then turn off N1. Block 110 may repeat this sequence with varying frequency until Vout is above a predefined regulation point. Once Vout exceeds the regulation point, block 110 may stop the pulses (e.g., keep both P1 and N1 off) until Vout falls below the regulation point again.

[0020] Note while one implementation of PFM is described hereinabove, one of ordinary skill in the art will appreciate that other PFM control schemes for P1 and N1 are known in the art. For example, alternative PFM control schemes may vary the frequency of the switching based on other parameters of the circuitry, e.g., load current, inductor current, switch current, etc. It will be appreciated that the techniques of the present disclosure may readily be adapted to support such alternative implementations as well.

[0021] FIG 2 illustrates exemplary signaling waveforms for PCTRL and NCTRL showing certain aspects of the present disclosure. Note FIG 2 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular signaling waveforms, e.g., any particular duty cycles or frequencies for the waveforms shown. Further note that in FIG 2, the inverse of PCTRL, or PCTRL', is shown and described for ease of illustration due to the operating principles of a PMOS transistor. In particular, a low voltage for PCTRL turns P1 on, and therefore a high voltage for PCTRL' turns P1 on, etc.

[0022] In FIG 2, from time t1 to t1.1 (corresponding to a duration TP), P1 is turned on and N1 is turned off. From t1.1 to t1.2 (corresponding to a duration TN), N1 is turned on and P1 is turned off. From t1.2 to t2, both N1 and P1 are off, and the cycle re-commences at t2. The time from t1 to t2 corresponds to the cycle duration T, which determines the frequency f = 1/T. In a typical implementation of PFM, the pulse frequency f may be varied over time to adjust the output voltage Vout and load current. Note in alternative implementations of PFM, multiple groups of pulses may be provided every cycle, e.g., N1 and P1 may be turned on in more than one "cluster" throughout the duration of each cycle.

[0023] It will be appreciated that power dissipation in the switches may arise from at least two factors. First, "switching losses" arise from the finite amount of charge that needs to be transferred to switch each transistor, e.g., to turn a transistor on or off, during each cycle. In general, the switching losses are due to various capacitances of the transistor, e.g., the gate-to-source capacitance, gate-to-drain capacitance, etc. Switching losses occur every time a device is enabled or disabled, and are generally independent of the duration of time for which such device is enabled. It will be appreciated that, all else being equal, larger

transistors (e.g., transistors having a large width-to-length ratio) will generally experience greater switching losses, since larger transistors are generally associated with larger capacitances.

[0024] Second, "conduction losses" or "DC losses" arise from the finite resistance (e.g., RDSon, or drain-to-source on-resistance) present when current flows from the drain to the source of each transistor. The drain-to-source current causes a voltage drop across the device, and corresponding DC power dissipation. Conduction losses are proportional to the time the device is conducting, i.e., when the device is supporting current flow between its drain and source. It will be appreciated that larger transistors will generally experience less conduction losses, since larger transistors are generally associated with less RDSon.

[0025] In view of the nature of switching losses and conduction losses described hereinabove, it will be appreciated that selecting an optimal size for the transistors (e.g., P1 and N1) of a buck converter, and generally any switched-mode power converter, requires balancing the competing considerations of lowering switching losses (e.g., by decreasing transistor size) and lowering conduction losses (e.g., by increasing transistor size).

[0026] For a buck converter operating in PFM mode, the switching and conduction losses are further related to the output voltage Vout of the buck converter as follows. In particular, it will be appreciated that the rate of increase in the inductor current IL is related to (Vdd - Vout) / L, wherein L is the inductance. For a given L, the rate of current increase (e.g., when P1 is turned on and N1 is turned off) is largest when Vout is smallest, since the rate of increase is (Vdd – Vout) / L during charging. Conversely, the rate of current decrease (i.e., when P1 is turned off and N1 is turned on) is largest when Vout is largest, since the rate of increase is -Vout / L during discharging.

[0027] Accordingly, when Vout is low, then the high-side switch (or P1) will be enabled for a relatively short period of time. During this short period of time, the conduction losses through P1 will be relatively smaller compared to the switching losses. On the other hand, when Vout is high, P1 will be enabled for a relatively long period of time, and therefore the conduction losses will be relatively greater compared to the switching losses. Note the low-side switch (or N1) will experience the opposite behavior. In particular, when Vout is low, N1 will be enabled for a relatively long period of time, and the conduction losses will be relatively greater compared to the switching losses. When Vout is high, the inductor current IL ramps down quickly, so N1 will only be enabled for a short period of time. Thus, for

low Vout the conduction losses for N1 will be relatively less compared to the switching losses.

[0028] It would be desirable to provide improved techniques for optimizing the operation of buck converters and other type of switched-mode power converters to reduce switching and conduction losses and thereby increase efficiency. According to the present disclosure, in a low-current mode such as PFM mode, the size of the switches may be dynamically adjusted based on a target output voltage to optimize the trade-offs between switching and conduction losses.

[0029] FIG 3 illustrates an exemplary embodiment 300 of a dynamic switch size adjustment apparatus according to the present disclosure. Note FIG 3 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure. For example, one of ordinary skill in the art will appreciate that switch size adjustment may be accomplished using other techniques besides turning on or off a plurality of transistors coupled in parallel. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0030] In FIG 3, the high-side switch P1 is shown implemented as a plurality P of parallel-coupled PMOS transistors P1.1 through P1.P. Each of P1.1 through P1.P is coupled to a corresponding gate control voltage PCTRL.p, wherein p is an index from 1 to P, such that any or all of the P PMOS transistors may be selectively enabled or disabled at any time. In FIG 3, each of the P transistors P1.1 through P1.P has an identical size KP, such that if, e.g., a subset  $nP \le P$  of the PMOS transistors are enabled, then the overall effective PMOS size KP1 would be  $nP \cdot KP$ . Note in alternative exemplary embodiments, not all of the transistors P1.1 through P1.P need to have the same size, and alternative sizing schemes may be readily utilized, e.g., a binary-weighted scheme wherein the transistors may be sized as KP,  $2 \cdot KP$ ,  $4 \cdot KP$ , etc. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0031] Similarly, N1 is shown implemented as a plurality N of parallel-coupled NMOS transistors N1.1 through N1.N. Note the plurality N corresponding to the number of parallel-coupled NMOS transistors need not be the same as the plurality P corresponding to the number of parallel-coupled PMOS transistors, although in certain exemplary embodiments, N may be equal to P. In FIG 3, each of N1.1 through N1.N is coupled to a corresponding gate control voltage NCTRL.n, wherein n is an index from 1 to N, such that any or all of the N NMOS transistors may be selectively enabled or disabled at any time. In

FIG 3, each of the N transistors N1.1 through N1.N has an identical size KN, such that, if, e.g., a subset nN <= N of the NMOS transistors are enabled, then the overall effective NMOS size KN1 would be nN · KN. Note in alternative exemplary embodiments, not all of the transistors N1.1 through N1.N need to have the same size, and alternative sizing schemes may be readily utilized. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0032] Further shown in FIG 3 is a control logic block 310 for generating the control voltages PCTRL.1 through PCTRL.P and NCTRL1 through NCTRL.N for each of the NMOS and PMOS transistors shown. Block 310 determines the gate control voltages for the parallel-coupled transistors based on receiving the target output voltage Vout\_target for the buck converter 300. In an exemplary embodiment, block 310 may include logical circuitry for controlling the effective sizes of switches P1 and N1 based on the target output voltage, as further described hereinbelow with reference to FIG 4.

[0033] FIG 4 illustrates an exemplary embodiment 400 of a method that may be implemented by the control logic block 310. Note FIG 4 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular exemplary embodiment of a method shown.

[0034] In FIG 4, at block 410, the target output voltage Vout\_target is received. In an exemplary embodiment, the target output voltage Vout\_target may be digitally programmed, e.g., by a microprocessor (not shown) writing to a register (not shown).

[0035] At block 420, it is determined whether Vout\_target lies within a high voltage range {Vhigh}, a medium voltage range {Vmed}, or a low voltage range {Vlow}. In an exemplary embodiment, Vout\_target may be determined to lie within the high voltage range if Vout\_target > Vhigh\_thresh, wherein Vhigh\_thresh is a predetermined high-voltage threshold. Similarly, Vout\_target may be determined to lie within the medium voltage range if Vmed\_thresh1 < Vout\_target < Vmed\_thresh2, and Vout\_target may be determined to lie within the low voltage range if Vout\_target < Vlow thresh.

[0036] In an exemplary embodiment, Vlow\_thresh <= Vmed\_thresh1 < Vmed\_thresh2 <= Vhigh. Note the threshold relationships and classification schemes for Vout\_target are described for illustrative purposes only, and are not meant to limit the scope of the present disclosure to any particular thresholds. In alternative exemplary embodiments, fewer or more than the three voltage ranges described with reference to FIG 4 (e.g., an arbitrary number N of ranges) may be provided, and the techniques disclosed herein may readily be

adapted thereto. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0037] In an exemplary embodiment, Vout\_target may be specified in a K-bit register, and the target output voltage range, and corresponding switch size(s), may be determined by simply referring to the most significant bits (MSB's) of the register. For example, in an exemplary embodiment wherein four voltage ranges are defined, the 2 MSB's may be mapped to voltage ranges as follows:  $00 \Rightarrow \{Vlow\}$ ,  $01 \Rightarrow \{Vmed1\}$ ,  $10 \Rightarrow \{Vmed2\}$ , and  $11 \Rightarrow \{Vhigh\}$ , wherein a medium voltage range is split into two ranges  $\{Vmed1\}$ ,  $\{Vmed2\}$ . Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0038] At block 420, depending on whether Vout\_target lies within {Vhigh}, {Vmed}, or {Vlow}, the method proceeds to block 430 / 432, 440 / 442, or 450 / 452, respectively.

[0039] At block 430, a plurality P\_high of PMOS transistors in P1 is selected. In an exemplary embodiment, P\_high = P. In an exemplary embodiment, control voltages PCTRL.1 through PCTRL.P may be configured to enable a plurality P\_high of PMOS transistors (and disable the remaining N – P\_high PMOS transistors) of P1 whenever P1 is to be enabled, and to disable the P\_high PMOS transistors whenever P1 is to be disabled, during the PFM switching cycles when Vout\_target lies within {Vhigh}.

[0040] At block 432, a plurality N\_high of NMOS transistors in N1 is selected. In an exemplary embodiment, N\_high = 1. In an exemplary embodiment, control voltages NCTRL.1 through NCTRL.N may be configured to enable only a plurality N\_high of NMOS transistors (and disable the remaining N - N\_high NMOS transistors) of N1 whenever N1 is to be enabled, and to disable the N\_high NMOS transistors (along with the remaining N - N\_high NMOS transistors) whenever N1 is to be disabled, during the PFM switching cycles when Vout\_target lies within {Vhigh}.

[0041] Note in FIG 4, blocks 430 and 432 are shown as being implemented in conjunction or in parallel, e.g., P\_high transistors of P1 may be selected and N\_high transistors of N1 may be selected whenever Vout\_target lies within {Vhigh}. In alternative exemplary embodiments, however, only one of blocks 430 and 432 need be implemented, e.g., the dynamic switch size techniques of the present disclosure may be applied to only one of P1 and N1. These comments apply also to blocks 440 / 442, and 450 / 452 further described hereinbelow. For example, in an exemplary embodiment (not shown), P\_high transistors of P1 may be selected while all N transistors of N1 are selected whenever Vout\_target lies

within Vhigh. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0042] Upon the number of PMOS and/or NMOS transistors being selected for {Vhigh} according to blocks 430 and/or 432, the method returns to block 410.

[0043] At block 440, a plurality P\_med of PMOS transistors in P1 is selected. In an exemplary embodiment, 1 < P\_med < P\_high. In an exemplary embodiment, control voltages PCTRL.1 through PCTRL.P may be configured to enable only a plurality P\_med of PMOS transistors (and disable the remaining P – P\_med PMOS transistors) whenever P1 is to be enabled, and to disable the P\_med PMOS transistors (along with the remaining P – P\_med PMOS transistors) whenever P1 is to be disabled, during the PFM switching cycles when Vout target lies within {Vmed}.

[0044] At block 442, a plurality N\_med of NMOS transistors in N1 is selected. In an exemplary embodiment,  $N > N_med > N_high$ . In an exemplary embodiment, control voltages NCTRL.1 through NCTRL.N may be configured to enable only a plurality N\_med of NMOS transistors (and disable the remaining N - N\_high NMOS transistors) whenever N1 is to be enabled, and to disable the N\_med NMOS transistors (along with the remaining N - N\_high NMOS transistors) whenever N1 is to be disabled, during the PFM switching cycles when Vout target lies within {Vmed}.

[0045] Upon the number of PMOS and/or NMOS transistors being selected for {Vmed} according to blocks 440 and/or 442, the method returns to block 410.

[0046] At block 450, a plurality P\_low of PMOS transistors in P1 is selected. In an exemplary embodiment, P\_low < P\_med. In an exemplary embodiment, control voltages PCTRL.1 through PCTRL.P may be configured to enable only a plurality P\_low of PMOS transistors (and disable the remaining P – P\_low PMOS transistors) whenever P1 is to be enabled, and to disable the P\_low PMOS transistors (along with the remaining P – P\_low PMOS transistors) whenever P1 is to be disabled, during the PFM switching cycles when Vout target lies within {Vlow}.

[0047] At block 452, a plurality N\_med of NMOS transistors in N1 is selected. In an exemplary embodiment,  $N \ge N_low > N_low > N_low$ . In an exemplary embodiment, control voltages NCTRL.1 through NCTRL.N may be configured to enable a plurality N\_low of NMOS transistors (and disable the remaining N - N\_low NMOS transistors, if any) whenever N1 is to be enabled, and to disable the N med NMOS transistors whenever

N1 is to be disabled, during the PFM switching cycles when Vout\_target lies within {Vlow}.

[0048] Upon the number of PMOS and/or NMOS transistors being selected for {Vlow} according to blocks 450 and/or 452, the method returns to block 410.

[0049] FIG 5 illustrates an exemplary configuration 500 of transistors according to the present disclosure, wherein the target output voltage lies in the high range {Vhigh}. Note FIG 5 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular values for the variables shown. Further note that the configuration 500 shown in FIG 5 is not meant to imply that the PMOS and NMOS transistors are ever to be simultaneously enabled during buck converter operation; rather, FIG 5 will be understood to illustrate only the number of possible transistors that may be enabled when either P1 is on or N1 is on.

[0050] In FIG 5, P = 4, N = 4, P\_high = 4, and N\_high = 1. Accordingly, when P1 is enabled, all 4 of the PMOS transistors P1.1, P1.2, P1.3, P1.4 are turned on. Similarly, when N1 is enabled, only 1 NMOS transistor N1.1 is turned on. Thus, it will be appreciated that when Vout\_target is in the high range, then a relatively large size (i.e., width-to-length ratio) for the PMOS transistor is provided to minimize RDSon of the high-side switch. Conversely, a relatively small size for the NMOS transistor is provided to minimize the switching capacitance of the low-side switch.

[0051] FIG 6 illustrates an exemplary configuration 600 of transistors according to the present disclosure, wherein the target output voltage lies in the medium range {Vmed}. Note FIG 6 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular values for the variables shown.

[0052] In FIG 6, P = 4, N = 4, P\_med = 2, and N\_med = 2. Accordingly, when P1 is enabled, 2 PMOS transistors P1.1, P1.2 are turned on, while P1.3, P1.4 are kept off. When N1 is enabled, 2 NMOS transistors N1.1, N1.2 are turned on, while N1.3, N1.4 are kept off. [0053] FIG 7 illustrates an exemplary configuration 700 of transistors according to the present disclosure, wherein the target output voltage lies in the low range {Vlow}. Note FIG 7 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular values for the variables shown.

[0054] In FIG 7, P = 4, N = 4,  $P_low = 1$ , and  $N_low = 4$ . Accordingly, when N1 is enabled, all 4 of the NMOS transistors N1.1, N1.2, N1.3, N1.4 are turned on. When P1 is enabled, only 1 PMOS transistor P1.1 is turned on. Thus, it will be appreciated that when

Vout\_target is in the low range, then a relatively large size for the NMOS transistor N1 is provided to minimize RDSon of the low-side switch. Conversely, a relatively small size for the PMOS transistor P1 is provided to minimize the switching capacitance of the high-side switch.

[0055] Note alternative exemplary embodiments may adjust drive voltages for the transistor switches (rather than switch sizes) based on the output voltage, to reduce power losses and increase efficiency. In particular, energy stored in the gate of a transistor may be expressed as ½ CV², wherein V is the driving voltage of a transistor. As a high-to-low, or low-to-high transition in the transistor driving voltage will therefore be accompanied by corresponding power dissipation, it would be advantageous to, e.g., increase the driving voltage for the high-side switch when the target output voltage is higher, and decrease the driving voltage for the high-side switch when the target output voltage is lower. Similarly, it may be advantageous to increase the driving voltage for the low-side switch when the target output voltage is lower, and decrease the driving voltage for the low-side switch when the target output voltage is lower, and decrease the driving voltage for the low-side switch when the target output voltage is higher. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0056] It will thus be appreciated that dynamically adjusting the driving capability of the switches based on the target output voltage as described hereinabove advantageously optimizes the trade-offs between minimizing switching losses and minimizing conduction losses for the buck converter.

[0057] FIG 8 illustrates an exemplary embodiment of a method 800 according to the present disclosure. Note FIG 8 is shown for illustrative purposes only, and is not meant to limit the scope of the present disclosure to any particular method.

[0058] In FIG 8, at block 801 during a low-current mode, the driving capability of at least one of a high-side switch and a low-side switch is configured based on a target output voltage of a switched-mode power converter. In an exemplary embodiment, the switched-mode power converter may be a buck converter. In an alternative exemplary embodiment, the switched-mode power converter may be a boost converter. In an exemplary embodiment, the driving capability may correspond to the size of the switch. In an alternative exemplary embodiment, the driving capability may correspond to the magnitude of the drive voltage applied to the switch.

[0059] The block 801 may include, at block 801A, increasing the driving capability of the high-side switch in response to the target output voltage being in a high voltage range.

[0060] The block 801 may further include, at block 801B, decreasing the driving capability of the high-side switch in response to the target output voltage being in a low voltage range lower than the high voltage range.

[0061] In an exemplary embodiment, the contents of a register holding the digital value of Vout\_target may be provided to the control logic block 310 in FIG 3 to dynamically determine the size of the high-side and low-side transistors for each voltage range (e.g., low, medium, high, etc.). For example, a decode table may be provided storing the preferred sizes for the PMOS and NMOS transistors for each of four specific voltage ranges, and such sizes may determine the particular settings for the control voltages PCTRL, NCTRL (e.g., the number of parallel-coupled transistors that will be enabled when the high-side or low-side transistor is enabled) for each range.

[0062] Note while exemplary embodiments of the present disclosure have been described wherein switch size is selected based on a buck converter output voltage, it will be appreciated that a boost converter may also utilize the techniques of the present disclosure. In particular, the high- and low-side switch sizes may be similarly adjusted based on a boost converter output voltage, for optimizing boost converter operation to reduce the losses and thereby increase efficiency.

[0063] Note while exemplary embodiments have been described hereinabove wherein a PMOS transistor is used as the high-side switch coupling the inductor L to Vdd, the techniques described may readily be utilized in alternative exemplary embodiments employing elements other than a PMOS transistor for the high-side switch. For example, in an alternative exemplary embodiment (not shown), an NMOS switch may also be utilized, and the size of the NMOS (high-side) switch may be adjusted based on target output voltage per the techniques described herein. Such alternative exemplary embodiments are contemplated to be within the scope of the present disclosure.

[0064] While exemplary embodiments have described hereinabove wherein size of a transistor switch is adjusted by increasing or decreasing the number of transistors coupled in parallel, it will be appreciated that alternative exemplary embodiments may adjust transistor size using other techniques, e.g., increasing or decreasing the number of transistors coupled in series, or any other network configuration wherein transistor size may be adjusted. For example, FIG 9 illustrates an alternative exemplary embodiment 900 according to the present disclosure, wherein the switch sizes are generally adjustable without limitation to any particular technique for switch size adjustment. In FIG 9, control logic block 910

generates switch on-off control signals PCTRL, NCTRL, and further switch size adjustment control signals KP CTRL, KN CTRL for switches P1', N1', respectively. KP CTRL and KN CTRL are applied to control the sizes of switches P1' and N1' having adjustable sizes. In an exemplary embodiment, the switch sizes of KP and/or KN may be mapped according to the target output voltage Vout\_target input to block 910, according to the techniques of the present disclosure.

[0065] In this specification and in the claims, the term "driving capability" may denote any parameter that affects the driving capability of a high-side or low-side switch. For example, an increased driving capability for a transistor may include an increased size for the transistor, or an increased gate driving voltage for the transistor, either of which will be understood to increase the driving capability of a transistor.

[0066] In this specification and in the claims, it will be understood that when an element is referred to as being "connected to" or "coupled to" another element, it can be directly connected or coupled to the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected to" or "directly coupled to" another element, there are no intervening elements present. Furthermore, when an element is referred to as being "electrically coupled" to another element, it denotes that a path of low resistance is present between such elements, while when an element is referred to as being simply "coupled" to another element, there may or may not be a path of low resistance between such elements.

[0067] Those of skill in the art would understand that information and signals may be represented using any of a variety of different technologies and techniques. For example, data, instructions, commands, information, signals, bits, symbols, and chips that may be referenced throughout the above description may be represented by voltages, currents, electromagnetic waves, magnetic fields or particles, optical fields or particles, or any combination thereof.

[0068] Those of skill in the art would further appreciate that the various illustrative logical blocks, modules, circuits, and algorithm steps described in connection with the exemplary aspects disclosed herein may be implemented as electronic hardware, computer software, or combinations of both. To clearly illustrate this interchangeability of hardware and software, various illustrative components, blocks, modules, circuits, and steps have been described above generally in terms of their functionality. Whether such functionality is implemented as hardware or software depends upon the particular application and design constraints

imposed on the overall system. Skilled artisans may implement the described functionality in varying ways for each particular application, but such implementation decisions should not be interpreted as causing a departure from the scope of the exemplary aspects of the invention.

[0069] The various illustrative logical blocks, modules, and circuits described in connection with the exemplary aspects disclosed herein may be implemented or performed with a general purpose processor, a Digital Signal Processor (DSP), an Application Specific Integrated Circuit (ASIC), a Field Programmable Gate Array (FPGA) or other programmable logic device, discrete gate or transistor logic, discrete hardware components, or any combination thereof designed to perform the functions described herein. A general purpose processor may be a microprocessor, but in the alternative, the processor may be any conventional processor, controller, microcontroller, or state machine. A processor may also be implemented as a combination of computing devices, e.g., a combination of a DSP and a microprocessor, a plurality of microprocessors, one or more microprocessors in conjunction with a DSP core, or any other such configuration.

[0070] The steps of a method or algorithm described in connection with the exemplary aspects disclosed herein may be embodied directly in hardware, in a software module executed by a processor, or in a combination of the two. A software module may reside in Random Access Memory (RAM), flash memory, Read Only Memory (ROM), Electrically Programmable ROM (EPROM), Electrically Erasable Programmable ROM (EPROM), registers, hard disk, a removable disk, a CD-ROM, or any other form of storage medium known in the art. An exemplary storage medium is coupled to the processor such that the processor can read information from, and write information to, the storage medium. In the alternative, the storage medium may be integral to the processor. The processor and the storage medium may reside in a user terminal. In the alternative, the processor and the storage medium may reside as discrete components in a user terminal.

[0071] In one or more exemplary aspects, the functions described may be implemented in hardware, software, firmware, or any combination thereof. If implemented in software, the functions may be stored on or transmitted over as one or more instructions or code on a computer-readable medium. Computer-readable media includes both computer storage media and communication media including any medium that facilitates transfer of a computer program from one place to another. A storage media may be any available media

that can be accessed by a computer. By way of example, and not limitation, such computer-readable media can comprise RAM, ROM, EEPROM, CD-ROM or other optical disk storage, magnetic disk storage or other magnetic storage devices, or any other medium that can be used to carry or store desired program code in the form of instructions or data structures and that can be accessed by a computer. Also, any connection is properly termed a computer-readable medium. For example, if the software is transmitted from a website, server, or other remote source using a coaxial cable, fiber optic cable, twisted pair, digital subscriber line (DSL), or wireless technologies such as infrared, radio, and microwave, then the coaxial cable, fiber optic cable, twisted pair, DSL, or wireless technologies such as infrared, radio, and microwave are included in the definition of medium. Disk and disc, as used herein, includes compact disc (CD), laser disc, optical disc, digital versatile disc (DVD), floppy disk and Blu-Ray disc where disks usually reproduce data magnetically, while discs reproduce data optically with lasers. Combinations of the above should also be included within the scope of computer-readable media.

[0072] The previous description of the disclosed exemplary aspects is provided to enable any person skilled in the art to make or use the invention. Various modifications to these exemplary aspects will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other exemplary aspects without departing from the spirit or scope of the invention. Thus, the present disclosure is not intended to be limited to the exemplary aspects shown herein but is to be accorded the widest scope consistent with the principles and novel features disclosed herein.

#### **CLAIMS**

#### 1. An apparatus comprising:

a high-side switch coupling a source voltage to an inductor, wherein the inductor is further coupled to an output voltage, and wherein the size of the high-side switch is configurable;

a low-side switch coupling the inductor to ground, wherein the size of the low-side switch is configurable;

wherein the driving capability of at least one of the high-side switch and the lowside switch is configured based on a target output voltage to which the output voltage is driven.

- 2. The apparatus of claim 1, wherein the driving capability of a switch comprises the size of said switch.

- 3. The apparatus of claim 1, wherein the driving capability of a switch comprises the magnitude of a driving voltage of said switch.

- 4. The apparatus of claim 2, wherein the sizes of both the high-side switch and the low-side switch are configured based on a target output voltage to which the output voltage is driven.

- 5. The apparatus of claim 2, the high-side and low-side switches being configured to operate according to pulse frequency modulation (PFM), wherein the size of the high-side switch is increased in response to the target output voltage being in a high voltage range, and the size of the high-side switch is decreased in response to the target output voltage being in a low voltage range lower than the high voltage range.

- 6. The apparatus of claim 2, wherein the size of the low-side switch is increased in response to the target output voltage being in a low voltage range, and the size of the low-side switch is increased in response to the target output voltage being in a high voltage range lower than the high voltage range.

7. The apparatus of claim 2, wherein the size of the high-side switch is configurable by selectively enabling a plurality of parallel-coupled PMOS transistors, and the size of the low-side switch is configurable by selectively enabling a plurality of parallel-coupled NMOS transistors.

- 8. The apparatus of claim 7, further comprising a control logic block configured to generate a plurality of gate control voltages for controlling each of the plurality of parallel-coupled transistors, wherein more of the parallel-coupled PMOS transistors are selected in response to the target output voltage being increased, wherein more of the parallel-coupled NMOS transistors are selected in response to the target output voltage being decreased.

- 9. The apparatus of claim 8, the control logic block comprising a decode table storing a mapping between each of a plurality of voltage ranges and corresponding gate control voltages specifying a size for the PMOS transistor, the decode table further storing a mapping between each of the plurality of voltage ranges and corresponding gate control voltages specifying a size for the NMOS transistor.

- 10. The apparatus of claim 2, wherein the size of the high-side switch is increased in response to the target output voltage being in a higher voltage range, and the size of the high-side switch is decreased in response to the target output voltage being in a lower voltage range.

- 11. The apparatus of claim 2, wherein the size of the at least one of the high-side switch and the low-side switch is configured based on the target output voltage during a low-current mode of the apparatus.

- 12. The apparatus of claim 11, the low-current mode of the apparatus corresponding to operation of a buck converter in a pulse-frequency modulation mode.

#### 13. A method comprising:

during a low-current mode, configuring the driving capability of at least one of a high-side switch and a low-side switch based on a target output voltage of a boost

converter, the high-side switch coupling a source voltage to an inductor, the low-side switch coupling the inductor to ground, the configuring comprising:

increasing the driving capability of the high-side switch in response to the target output voltage being in a high voltage range; and

decreasing the driving capability of the high-side switch in response to the target output voltage being in a low voltage range lower than the high voltage range.

- 14. The method of claim 13, wherein the driving capability of a switch comprises the size of the switch.

- 15. The method of claim 13, wherein the driving capability of a switch comprises the magnitude of a driving voltage of the switch.

- 16. The method of claim 14, the low-current mode corresponding to a pulse-frequency modulation mode of operation in a buck converter, the method further comprising:

increasing the size of the low-side switch in response to the target output voltage being in a low voltage range; and

decreasing the size of the of the low-side switch in response to the target output voltage being in a high voltage range higher than the high voltage range.

- 17. The method of claim 14, the high-side switch comprising a plurality of parallel-coupled PMOS transistors, the low-side switch comprising a plurality of parallel-coupled NMOS transistors, the increasing the size of a switch comprising selecting more parallel-coupled PMOS or NMOS transistors, and the decreasing the size of a switch comprising selecting fewer parallel-coupled PMOS or NMOS transistors.

- 18. The method of claim 13, further comprising:

using a control logic block, mapping a target output voltage to a driving capability for the high-side or low-side switch.

19. The method of claim 18, the mapping comprising classifying the target output voltage into a voltage range associated with a size for the high-side or low-side switch.

#### 20. An apparatus comprising:

means for, during a low-current mode, configuring the driving capability of at least one of a high-side switch and a low-side switch based on a target output voltage of a boost converter, the high-side switch coupling a source voltage to an inductor, the low-side switch coupling the inductor to ground, the configuring comprising:

means for increasing the driving capability of the high-side switch in response to the target output voltage being in a high voltage range; and

means for decreasing the driving capability of the high-side switch in response to the target output voltage being in a low voltage range lower than the high voltage range.

(PRIOR ART) FIG 1

FIG 2

FIG 3

FIG 4

Vout\_target => {Vhigh}

FIG 5

Vout target => {Vmed}

FIG 6

Vout\_target => {Vlow}

FIG 7

8/9

FIG 8

FIG 9

#### INTERNATIONAL SEARCH REPORT

International application No PCT/US2014/012804

A. CLASSIFICATION OF SUBJECT MATTER

INV. H03K17/12 H02M1/00 H02J1/00

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H03K H02M H02J

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category*                                                                                                                                                                                                                                                                                                                                                                          | Citation of document, with indication, where appropriate, of the re                                                               | levant passages                                                                                                                                                                                                                                                                                                                                                                                                                                          | Relevant to claim No. |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| Х                                                                                                                                                                                                                                                                                                                                                                                  | US 2003/038615 A1 (ELBANHAWY ALA<br>27 February 2003 (2003-02-27)<br>the whole document                                           | N [US])                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-20                  |  |

| X                                                                                                                                                                                                                                                                                                                                                                                  | US 2009/080281 A1 (HASHIBA YOSHI<br>26 March 2009 (2009-03-26)<br>paragraphs [0003], [0008], [00<br>[0043], [0053]<br>figures 2-7 | AKI [JP])<br>009],                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1,13,20               |  |

| X                                                                                                                                                                                                                                                                                                                                                                                  | US 6 404 173 B1 (TELEFUS MARK D<br>11 June 2002 (2002-06-11)<br>paragraphs [0005], [0008], [00<br>[0034]<br>figures 2-8           | [US])<br>021],<br>-/                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,13,20               |  |

| X Furt                                                                                                                                                                                                                                                                                                                                                                             | her documents are listed in the continuation of Box C.                                                                            | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |

| <ul> <li>"A" document defining the general state of the art which is not considered to be of particular relevance</li> <li>"E" earlier application or patent but published on or after the international filing date</li> <li>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other</li> </ul> |                                                                                                                                   | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be |                       |  |

| special reason (as specified) "O" document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                                                                                                                         |                                                                                                                                   | considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family                                                                                                                                                                                                                                |                       |  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                             |                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |  |

| Date of the                                                                                                                                                                                                                                                                                                                                                                        | actual completion of the international search                                                                                     | Date of mailing of the international sea                                                                                                                                                                                                                                                                                                                                                                                                                 | rch report            |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                  | 7 June 2014                                                                                                                       | 26/06/2014                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |  |

| Name and r                                                                                                                                                                                                                                                                                                                                                                         | nailing address of the ISA/ European Patent Office, P.B. 5818 Patentlaan 2                                                        | Authorized officer                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |  |

Krasser, Bernhard

NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016

### **INTERNATIONAL SEARCH REPORT**

International application No

PCT/US2014/012804

| C(Continua | ation). DOCUMENTS CONSIDERED TO BE RELEVANT                                        |                             |

|------------|------------------------------------------------------------------------------------|-----------------------------|

| Category*  | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.       |

|            |                                                                                    | Relevant to claim No.  1-20 |

|            |                                                                                    |                             |

|            |                                                                                    |                             |

#### **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2014/012804

| Patent document cited in search report |    | Publication<br>date | Patent family<br>member(s)       |                                                                        | Publication<br>date |                                                                                  |

|----------------------------------------|----|---------------------|----------------------------------|------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------|

| US 2003038615                          | A1 | 27-02-2003          | CN<br>DE<br>JP<br>TW<br>US<br>WO | 1568568<br>10297140<br>2005501497<br>1261960<br>2003038615<br>03019761 | T5<br>A<br>B<br>A1  | 19-01-2005<br>02-09-2004<br>13-01-2005<br>11-09-2006<br>27-02-2003<br>06-03-2003 |

| US 2009080281                          | A1 | 26-03-2009          | JP<br>JP<br>US                   | 4660526<br>2009074973<br>2009080281                                    | A                   | 30-03-2011<br>09-04-2009<br>26-03-2009                                           |

| US 6404173                             | B1 | 11-06-2002          | US<br>US                         | 6404173<br>2002130644                                                  |                     | 11-06-2002<br>19-09-2002                                                         |

| EP 1608066                             | A1 | 21-12-2005          | NONE                             |                                                                        |                     |                                                                                  |