US011139382B2

### (12) United States Patent

### Yang et al.

### (54) SEMICONDUCTOR DEVICE

- (71) Applicant: Samsung Electronics Co., Ltd., Suwon-si (KR)

- Inventors: Jung Gil Yang, Suwon-si (KR); Seung Min Song, Suwon-si (KR); Soo Jin Jeong, Suwon-si (KR); Dong Il Bae, Suwon-si (KR); Bong Seok Suh, Suwon-si (KR)

- (73) Assignee: SAMSUNG ELECTRONICS CO., LTD., Suwon-si

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 16/732,520

- (22) Filed: Jan. 2, 2020

### (65) **Prior Publication Data**

US 2020/0373402 A1 Nov. 26, 2020

### (30) Foreign Application Priority Data

May 22, 2019 (KR) ..... 10-2019-0059798

(51) Int. Cl.

| H01L 27/088 | (2006.01)   |

|-------------|-------------|

| H01L 27/092 | (2006.01)   |

| H01L 29/06  | (2006.01)   |

| H01L 29/423 | (2006.01)   |

| H01L 29/49  | (2006.01)   |

| H01L 29/51  | (2006.01)   |

| H01L 29/775 | (2006.01)   |

|             | (Continued) |

- (52) U.S. Cl.

- CPC .... H01L 29/42392 (2013.01); H01L 27/0886 (2013.01); H01L 27/0924 (2013.01); H01L 27/1211 (2013.01); H01L 29/0642 (2013.01);

### (10) Patent No.: US 11,139,382 B2

### (45) **Date of Patent:** Oct. 5, 2021

*H01L 29/4983* (2013.01); *H01L 29/51* (2013.01); *H01L 29/785* (2013.01); *H01L 29/7851* (2013.01); *H01L 29/78696* (2013.01)

(58) Field of Classification Search CPC ... H01L 29/42392; H01L 29/785–7851; H01L 29/78696; H01L 29/66439; H01L 29/66795; H01L 29/66469; H01L 27/0924; H01L 27/0886; H01L 21/823431; H01L 21/823821; H01L 21/823878; H01L 21/823481; H01L 29/0642–0649

See application file for complete search history.

#### (56) **References Cited**

### U.S. PATENT DOCUMENTS

7,402,483 B2 7/2008 Yun et al. 9,608,062 B1\* 3/2017 Tseng ...... H01L 29/66545 (Continued)

Primary Examiner — Errol V Fernandes

Assistant Examiner — Jeremy J Joy

(74) Attorney, Agent, or Firm - Muir Patent Law, PLLC

### (57) **ABSTRACT**

A semiconductor device having a gate-all-around structure includes a first fin pattern and a second fin pattern separated by a first trench and extending in a first direction, a first nanosheet on the first fin pattern, a second nanosheet on the second fin pattern, a first fin liner extending along at least a portion of a sidewall and a bottom surface of the first trench, a first field insulation layer disposed on the first fin liner and filling a portion of the first trench, and a first gate structure overlapping an end portion of the first fin pattern and including a first gate spacer. A height from the bottom surface of the first trench to a lower surface of the first gate spacer is greater than a height from the bottom surface of the first trench to an upper surface of the first field insulation layer.

### 19 Claims, 19 Drawing Sheets

(51) Int. Cl. *H01L 29/78*

| (2006.01) |

|-----------|

| (2006.01) |

| (2006.01) |

|           |

#### (56) **References** Cited

### U.S. PATENT DOCUMENTS

| 9,620,590    | B1   | 4/2017  | Bergendahl et al.    |

|--------------|------|---------|----------------------|

| 9,818,875    | B1 * | 11/2017 | Bi H01L 29/0653      |

| 9,847,391    | B1   | 12/2017 | Zang et al.          |

| 9,905,468    | B2   | 2/2018  | Kim et al.           |

| 9,972,701    | B2   | 5/2018  | Kim et al.           |

| 9,984,893    | B2   | 5/2018  | Cheng et al.         |

| 2015/0214341 | A1*  | 7/2015  | Shin H01L 29/7851    |

|              |      |         | 257/401              |

| 2016/0163604 | A1*  | 6/2016  | Xie H01L 27/0924     |

|              |      |         | 257/401              |

| 2017/0025540 | A1*  | 1/2017  | Liou H01L 29/66545   |

| 2017/0141211 | A1*  | 5/2017  | Xie H01L 29/785      |

| 2017/0200738 | A1*  | 7/2017  | Kim H01L 21/845      |

| 2018/0033699 | A1*  | 2/2018  | Zhu H01L 21/76232    |

| 2018/0090493 | A1*  | 3/2018  | Kwak H01L 21/823481  |

| 2018/0212035 | A1   | 7/2018  | Cheng et al.         |

| 2018/0374791 | A1   | 12/2018 | Smith et al.         |

| 2019/0035633 | A1*  | 1/2019  | Jha H01L 21/475      |

| 2019/0097015 | A1*  | 3/2019  | Zang H01L 29/66795   |

| 2019/0139831 | A1*  | 5/2019  | Zhu H01L 21/762      |

| 2019/0221469 | A1*  | 7/2019  | Hsu H01L 21/823431   |

|              | A1*  | 11/2019 | Maeda H01L 21/823821 |

|              | A1*  | 5/2020  | Zang H01L 21/823431  |

| 2020/0168607 | A1*  | 5/2020  | Yang H01L 29/78696   |

\* cited by examiner

FIG. 5A

FIG. 5C

Z1

### SEMICONDUCTOR DEVICE

### CROSS-REFERENCE TO RELATED APPLICATION

This application claims priority under 35 U.S.C. § 119 to Korean Patent Application No. 10-2019-0059798, filed on May 22, 2019, in the Korean Intellectual Property Office, the disclosure of which is hereby incorporated by reference in its entirety.

### TECHNICAL FIELD

Example embodiments of the present disclosure relate to a semiconductor device, and more specifically, to a semi-<sup>15</sup> conductor device having a gate-all-around structure.

### DISCUSSION OF RELATED ART

To increase the integration of a semiconductor device, a <sup>20</sup> transistor having a gate-all-around structure including a gate surrounding a silicon body of a nanowire shape formed on a substrate has been proposed.

Since a transistor of a gate-all-around structure can utilize a three-dimensional channel, it can be scaled. Further, its <sup>25</sup> current control capability can be improved without increasing a gate length thereof. A short channel effect (SCE) in which the electrical potential of the channel region is affected by the drain voltage can be effectively reduced and/or suppressed in the transistor with the gate-all-around <sup>30</sup> structure.

### SUMMARY

According to example embodiments of the inventive 35 concepts, a semiconductor device may include a first fin pattern and a second fin pattern separated by a first trench, each of the first fin pattern and the second fin pattern extending lengthwise in a first direction, a first nanosheet on the first fin pattern, a second nanosheet on the second fin 40 pattern, a first fin liner extending along at least a portion of a sidewall and a bottom surface of the first trench, a first field insulation layer disposed on the first gate structure overlapping an end portion of the first fin pattern and including a 45 first gate spacer. A height from the bottom surface of the first trench to a lower surface of the first gate spacer may be greater than a height from the bottom surface of the first trench to an upper surface of the first field insulation layer.

According to example embodiments of the inventive 50 concepts, a semiconductor device may include a first fin pattern and a second fin pattern separated by a first trench, each of the first fin pattern and the second fin pattern extending lengthwise in a first direction, a first nanosheet on the first fin pattern, a second nanosheet on the second fin 55 pattern, a first field insulation layer filling at least a portion of the first fin pattern, a first fin pattern, a first fin liner disposed between a sidewall of the first fin pattern and the first field insulation layer and extending along at least a portion of a 60 sidewall and a bottom surface of the first trench, and a first insulation layer surface of the first field insulation layer and extending along a sidewall of the first gate structure and an upper surface of the first field insulation layer and contacting the first fin liner.

According to example embodiments of the inventive 65 concepts, a semiconductor device may include a first fin pattern and a second fin pattern separated by a trench, each

of the first fin pattern and the second fin pattern extending lengthwise in a first direction, a first nanosheet on the first fin pattern, a second nanosheet on the second fin pattern, a fin liner extending along a portion of a sidewall and a bottom surface of the trench and defining a liner trench, a field insulation layer disposed on the fin liner and filling at least a portion of the trench, and a gate structure overlapping an end portion of the first fin pattern. Each of the first fin pattern, the second fin pattern, the first nanosheet and the second nanosheet may include a group IV-IV compound semiconductor or a group III-V compound semiconductor.

### BRIEF DESCRIPTION OF THE DRAWINGS

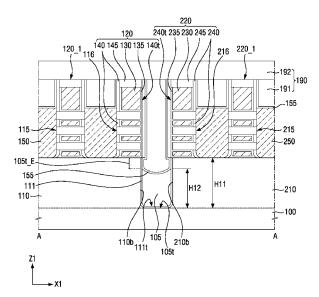

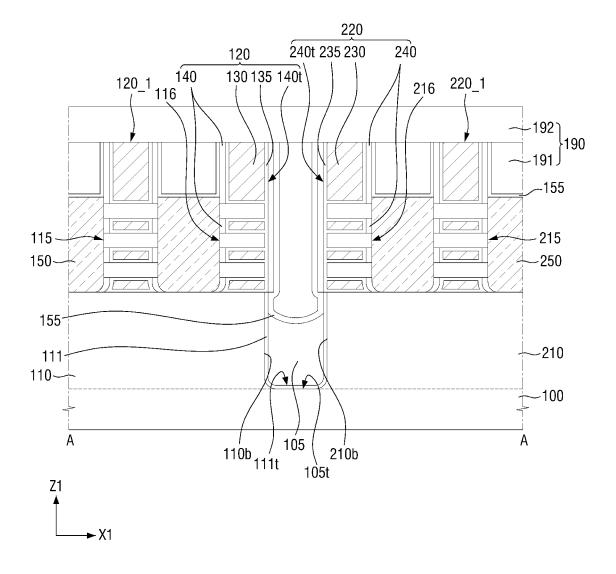

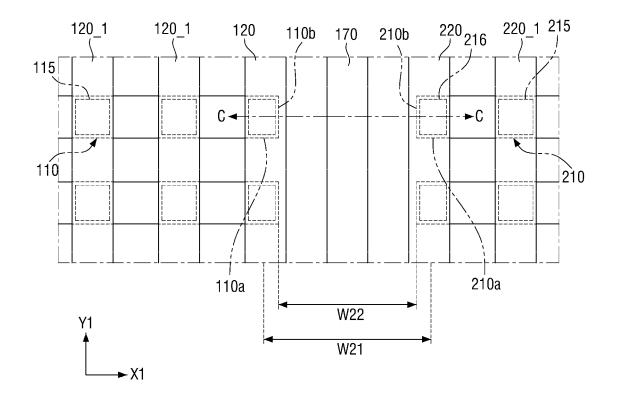

FIG. **1** is a plan view illustrating a semiconductor device, according to example embodiments of the inventive concept.

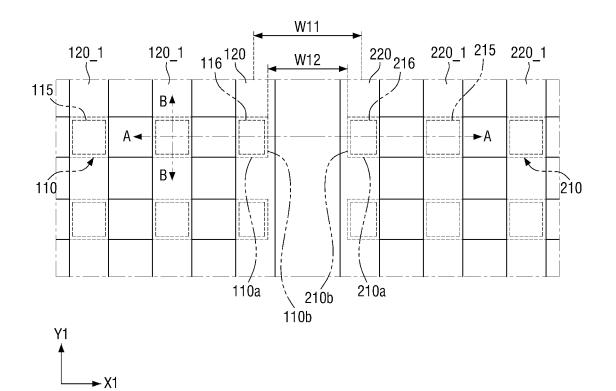

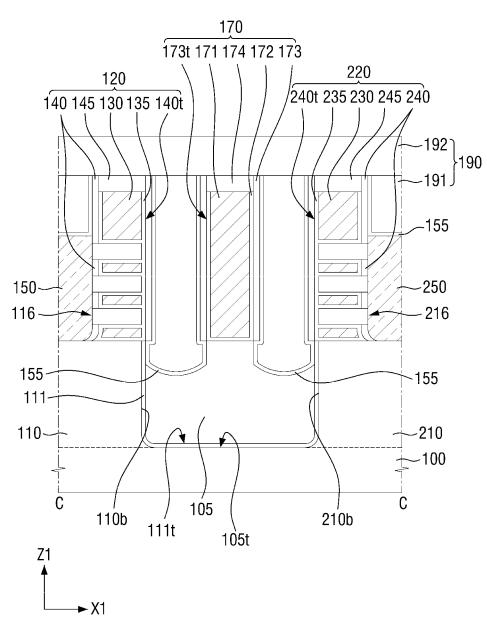

FIG. **2** is a cross-sectional view taken along line A-A of FIG. **1**.

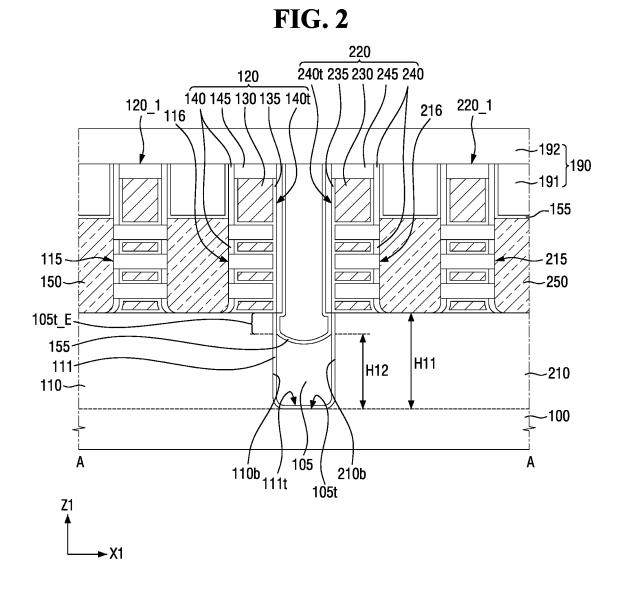

FIG. 3 is a cross-sectional view taken along line B-B of FIG. 1.

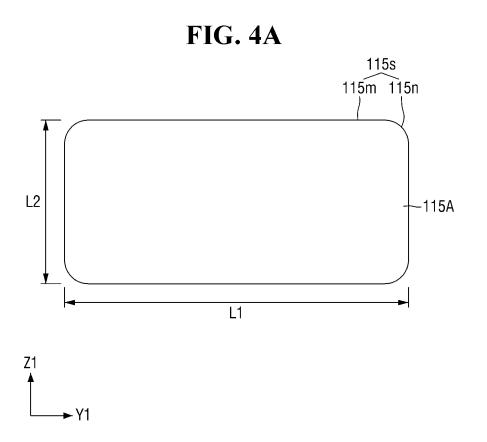

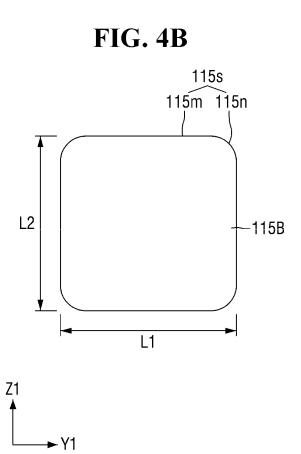

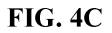

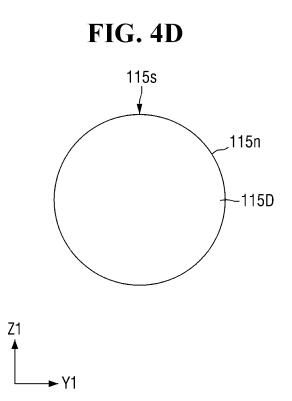

FIGS. 4A, 4B, 4C, and 4D are cross-sectional views taken along line B-B of a nanosheet of FIG. 1.

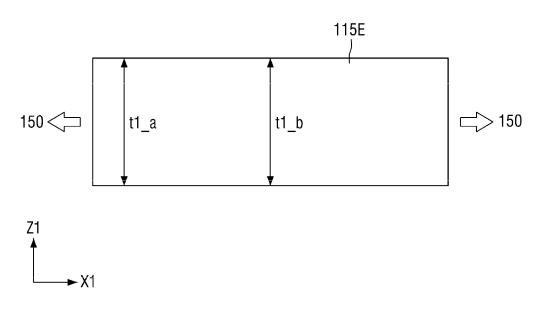

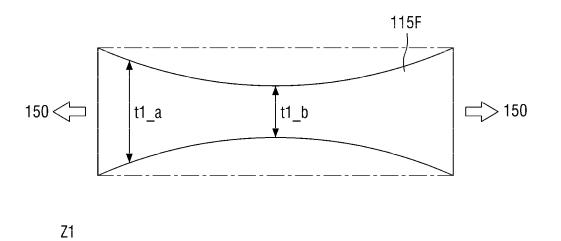

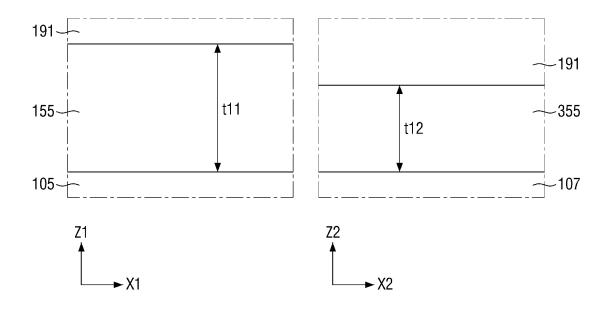

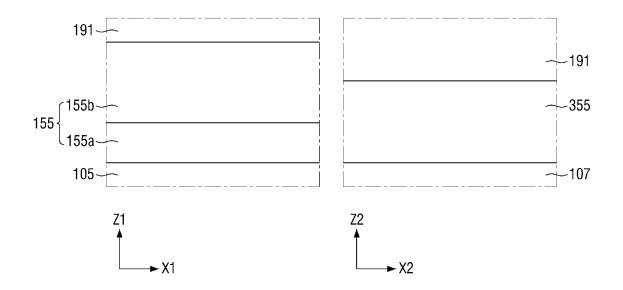

FIGS. 5A, 5B, and 5C are cross-sectional views taken along line A-A of a nanosheet of FIG. 1.

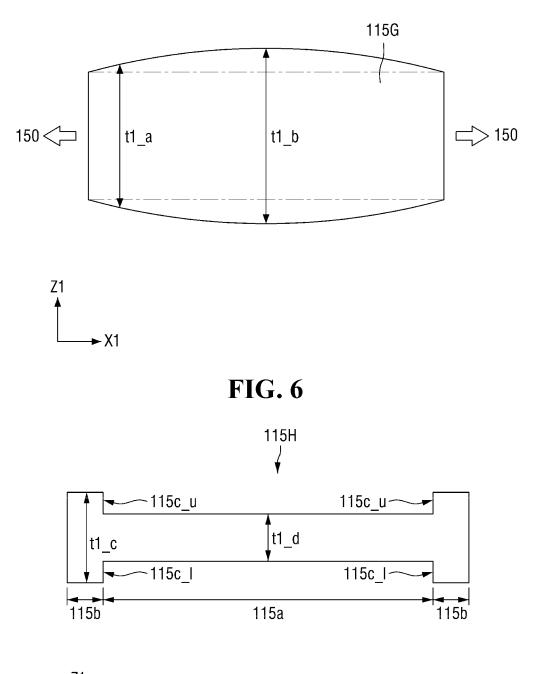

FIG. 6 is a cross-sectional view taken along line A-A of a nanosheet of FIG. 1.

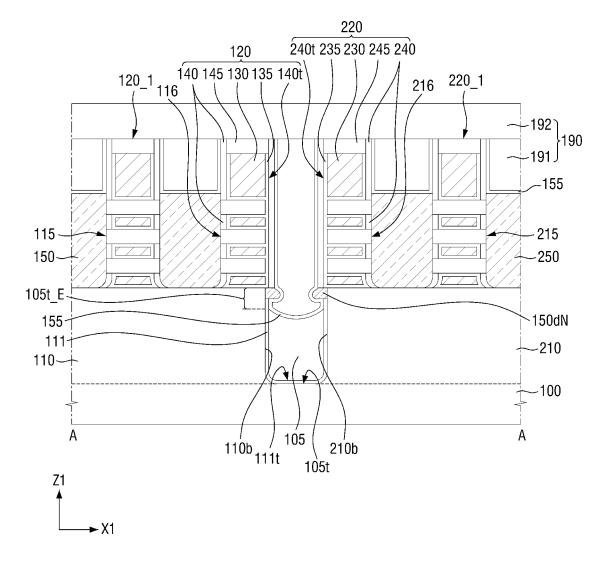

FIG. 7 is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

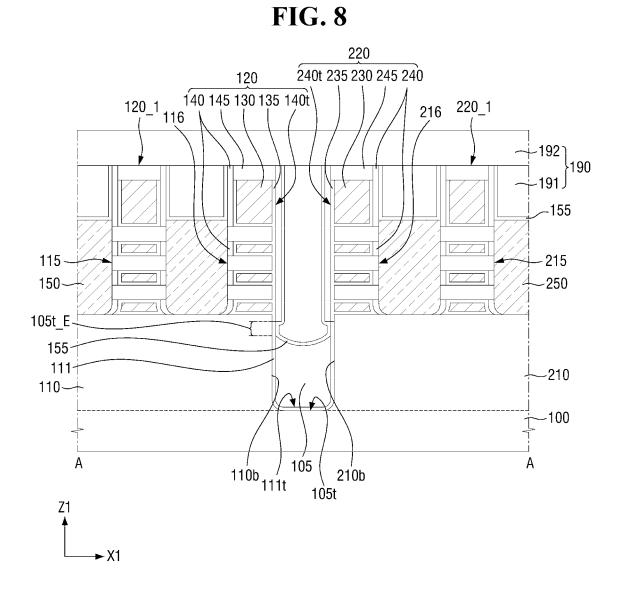

FIG. 8 is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

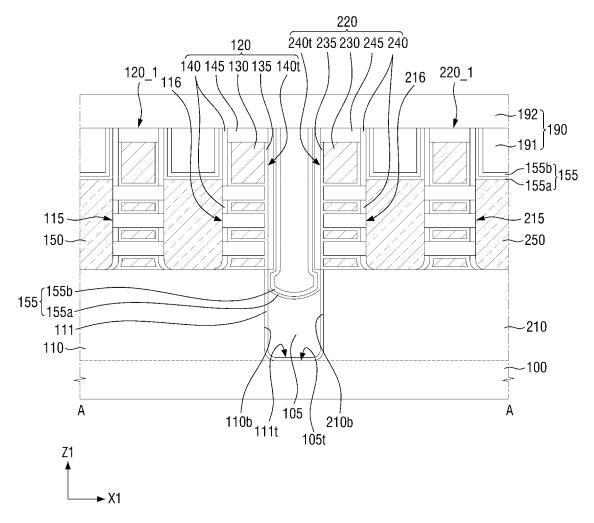

FIG. **9** is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

FIG. **10** is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

FIG. 11 is a plan view illustrating a semiconductor device, according to example embodiments of the inventive concept.

FIG. **12** is a cross-sectional view taken along line C-C of FIG. **11**.

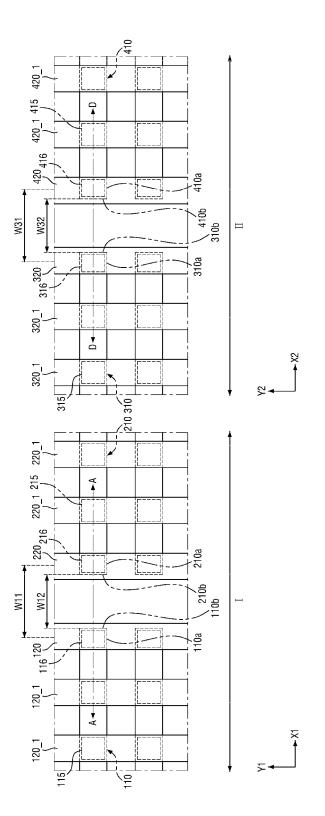

FIG. **13** is a plan view illustrating a semiconductor device, according to example embodiments of the inventive concept.

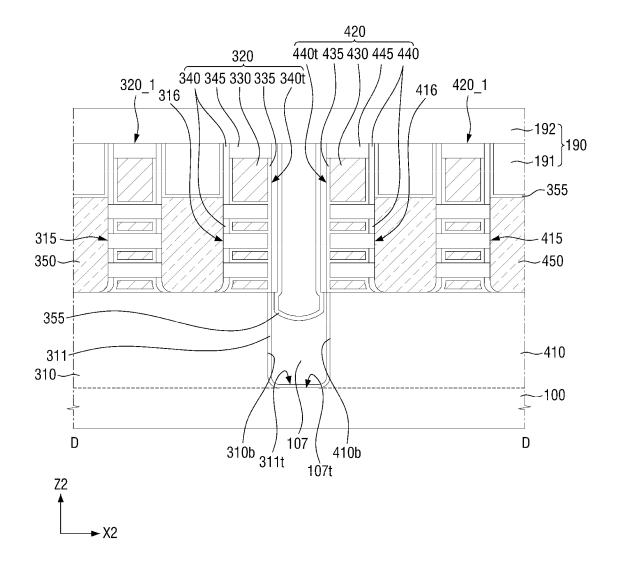

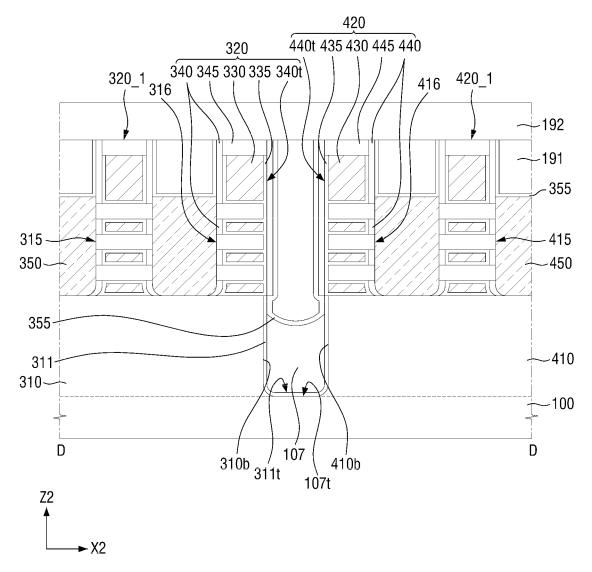

FIG. **14** is a cross-sectional view taken along line D-D of FIG. **13**.

FIG. **15** is a view for comparing a thickness of a first insulation liner in a first region I of FIG. **13** with a thickness of a second insulation liner in a second region II of FIG. **13**.

FIG. **16** is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

FIG. **17** is a view illustrating a semiconductor device, according to example embodiments of the inventive concept.

#### DETAILED DESCRIPTION

Various example embodiments will now be described more fully with reference to the accompanying drawings in which some example embodiments are shown. However, the inventive concepts may be embodied in many alternate forms and should not be construed as limited to only example embodiments set forth herein.

In the drawings of the semiconductor device according to example embodiments of the inventive concept, a gate-allaround transistor including a nanowire-shaped channel or nanosheet-shaped channel is illustrated, but the inventive concept is not limited thereto. The semiconductor device 5 according to example embodiments of the inventive concept may include a tunneling transistor, a three dimensional transistor, or a transistor having a fin-shaped channel. The semiconductor device according to embodiments of the inventive concept may include a bipolar junction transistor, 10 a lateral double diffused transistor (LDMOS), or the like.

FIG. 1 is a plan view illustrating a semiconductor device according to example embodiments of the inventive concept. FIG. 2 is a cross-sectional view taken along line A-A of FIG. 1. FIG. 3 is a cross-sectional view taken along line 15 B-B of FIG. 1. FIGS. 4A, 4B, 4C, and 4D are cross-sectional views taken along line B-B of a nanosheet of FIG. 1. FIGS. 5A, 5B, 5C, and 6 are cross-sectional views taken along line A-A of a nanosheet of FIG. 1. For convenience of explanation, an interlayer insulation layer 190 is not illustrated in 20 FIG. 1.

Referring to FIGS. 1 to 3, a semiconductor device according to example embodiments of the inventive concept may include a substrate 100, a first fin pattern 110, a second fin pattern 210, first normal nanosheets 115, first dummy 25 nanosheets 116, second normal nanosheets 215, second dummy nanosheets 216, first gate structures 120 and 120\_1, second gate structures 220 and 220\_1, a first fin liner 111, and a first insulation liner 155. The semiconductor device may have a gate-all-around structure.

The substrate 100 may be a bulk silicon substrate or a silicon-on-insulator (SOI) substrate. In some embodiments, the substrate 100 may include for example, silicon germanium, silicon germanium on insulator (SGOI), indium antimonide, lead tellurium compound, indium arsenide, indium 35 phosphide, gallium arsenide or gallium antimonide, but it is not limited thereto.

The first fin pattern 110 and the second fin pattern 210 may protrude from the substrate 100 (e.g., in a third direction Z1, which is perpendicular to a first direction X1 and a 40 may include the same material. In some embodiments, each second direction Y1). The first fin pattern 110 and the second fin pattern 210 may respectively extend lengthwise along the first direction X1 parallel to an upper surface of the substrate 100. As used herein, an item, layer, or portion of an item or layer described as extending "lengthwise" in a particular 45 direction has a length in the particular direction and a width perpendicular to that direction, where the length is greater than the width.

For example, the first fin pattern 110 may have a long sidewall 110a extending in the first direction X1 and a short 50 sidewall 110b extending in the second direction Y1, and the second fin pattern 210 may have a long sidewall 210a extending in the first direction X1 and a short sidewall 210b extending in the second direction Y1. The second direction Y1 may be perpendicular to the first direction X1 and may 55 be parallel to the upper surface of the substrate 100. Each of the first fin pattern 110 and the second fin pattern 210 may be defined by a fin trench 106t. For example, each of the long sidewall 110a of the first fin pattern 110 and the long sidewall 210a of the second fin pattern 210 may be defined 60 by the fin trench 106t.

The first fin pattern 110 and the second fin pattern 210 may be aligned in the first direction X1 that is a length direction thereof, and may be spaced apart from each other in the first direction X1. For example, the first fin pattern 110 65 and the second fin pattern 210 may be arranged in a row in the first direction X1. Upper surfaces of the first fin pattern

4

110 and the second fin pattern 210 may be coplanar with one another. Terms such as "same," "equal," "planar," "coplanar," or "uniform," as used herein when referring to orientation, layout, location, shapes, sizes, amounts, or other measures do not necessarily mean an exactly identical orientation, layout, location, shape, size, amount, or other measure, but are intended to encompass nearly identical orientation, layout, location, shapes, sizes, amounts, or other measures within acceptable variations that may occur, for example, due to manufacturing processes.

The short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210 may face each other. The first fin pattern 110 and the second fin pattern 210 may be separated from each other by a first fin-cut trench 105t. The short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210 may be defined by the first fin-cut trench 105t.

Each of the first fin pattern 110 and the second fin pattern 210 may be formed by etching a portion of the substrate 100 or may include an epitaxial layer grown from the substrate 100. Each of the first fin pattern 110 and the second fin pattern 210 may include a semiconductor material, for example, silicon (Si) or germanium (Ge). In some embodiments, each of the first fin pattern 110 and the second fin pattern 210 may include a compound semiconductor, for example, a group IV-IV compound semiconductor or a group III-V compound semiconductor.

The group IV-IV compound semiconductor may include a binary compound or a ternary compound including at least two of carbon (C), silicon (Si), germanium (Ge), and tin (Sn), or a compound doped with a group IV element. The group III-V compound semiconductor may include a binary compound, a ternary compound, or a quaternary compound, each of which is formed by combination of a group III element, for example, at least one of aluminum (Al), gallium (Ga), and indium (In), and a group V element, for example, at least one of phosphorus (P), arsenic (As), and antimony (Sb).

The first fin pattern 110 and the second fin pattern 210 of the first fin pattern 110 and the second fin pattern 210 may be a silicon fin pattern including silicon.

The first fin liner **111** may extend along at least a portion of a sidewall and a bottom surface of the fin trench 106t. The first fin liner 111 may extend along at least a portion of a sidewall and a bottom surface of the first fin-cut trench 105t.

In some embodiments, the first fin liner 111 may be disposed on the whole sidewall of the fin trench 106t and on the whole sidewall of the first fin-cut trench 105t.

The first fin liner 111 may have a lower surface facing the first fin pattern 110 and the second fin pattern 210 and an upper surface opposite to the lower surface. For example, the lower surface of the first fin liner 111 may contact the first fin pattern 110 and the second fin pattern 210, and the upper surface of the first fin liner 111 may contact the first field insulation layer 105. Since the first fin liner 111 extends along the surface of the fin trench 106t and the surface of the first fin-cut trench 105t, a first liner trench 111t may be defined by the upper surface of the first fin liner 111. It will be understood that when an element is referred to as being "connected" or "coupled" to, or "on" another element, it can be directly connected or coupled to, or on the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected," "directly coupled," in or "directly on" another element, there are no intervening elements present. Other words used to describe the relationship between elements should be inter-

preted in a like fashion (e.g., "between" versus "directly between," "adjacent" versus "directly adjacent," etc.). However, the term "contact," as used herein, refers to a direct connection (i.e., touching) unless the context indicates otherwise.

The first fin liner **111** may include, for example, silicon oxynitride, silicon nitride, and/or silicon oxide.

A first field insulation layer 105 may fill a portion of the first fin-cut trench 105t. The first field insulation layer 105 may be disposed on the short sidewall 110b of the first fin 10 pattern 110 and on the short sidewall 210b of the second fin pattern 210. The first field insulation layer 105 may not cover a portion of the sidewall of the first fin pattern 110 and a portion of the sidewall of the second fin pattern 210. In some embodiments, the first fin liner 111 may be disposed 15 between the first field insulation layer 105 and the first fin pattern 110 and between the first field insulation layer 105 and the second fin pattern 210. For example, the first fin liner 111 may contact the short sidewall 110b of the first fin pattern 110, the short sidewall 210b of the second fin pattern 20 210, and an upper surface of the substrate 100, and the first field insulation layer 105 may contact the first fin liner 111.

An upper surface of the first fin pattern **110** and an upper surface of the second fin pattern **210** may be at a higher vertical level (e.g., in the third direction Z1) than an upper 25 surface of the first field insulation layer **105** with respect to the bottom surface of the first fin-cut trench **105***t*. For example, the upper surface of the first field insulation layer **105** may be at a lower vertical level (e.g., in the third direction Z1) than the upper surfaces of the first fin pattern 30 **110** and the second fin pattern **210**.

The first field insulation layer **105** may fill a portion of the first liner trench **111***t*. Since the first field insulation layer **105** fills the portion of the first liner trench **111***t*, the first field insulation layer **105** may not cover a portion of the first fin 35 liner **111** extending along the sidewall of the first fin-cut trench **105***t*. For example, the first field insulation layer **105** may not cover upper portions of the first fin liner **111** that are nearer to the upper surfaces of the first fin pattern **110** and the second fin pattern **210**.

A portion of the first fin liner 111 may protrude above the upper surface of the first field insulation layer 105 with respect to the bottom surface of the first fin-cut trench 105t (e.g., in the third direction Z1).

The first fin-cut trench 105t may include an exposed 45 region  $105t_E$ . The exposed region  $105t_E$  of the first fin-cut trench 105t may be a region not covered by the first field insulation layer 105. For example, the exposed region  $105t_E$  may be exposed with respect to the first field insulation layer 105. The exposed region  $105t_E$  of the first 50 fin-cut trench 105t may be a region not covered by a first gate spacer 140 and a second gate spacer 240.

The first fin liner **111** may be disposed to extend along a portion of the exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t. In some embodiments, the first fin liner **111** may 55 be disposed to extend along the entirety of the exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t.

A second field insulation layer **106** may fill at least a portion of the fin trench **106***t*. The second field insulation layer **106** may fill at least a portion of the first liner trench <sup>60</sup> **111***t*. In some embodiments, an upper surface of the second field insulation layer **106** may be coplanar with an upper surface of the first fin pattern **110** and an upper surface of the second fin pattern **210**.

The second field insulation layer **106** may be disposed on 65 the long sidewall **110***a* of the first fin pattern **110** and the long sidewall **210***a* of the second fin pattern **210**. The second field

insulation layer 106 may cover the entirety of the long sidewall 110a of the first fin pattern 110 and the entirety of the second fin pattern 210, but the inventive concept is not limited thereto.

The first field insulation layer **105** and the second field insulation layer **106** may include, for example, an oxide layer, a nitride layer, an oxynitride layer, or a combination thereof.

First nanosheets **115** and **116** may be disposed on the substrate **100**. The first nanosheets **115** and **116** may be disposed on the first fin pattern **110**. The first nanosheets **115** and **116** may include the first normal nanosheets **115** and the first dummy nanosheets **116**.

The first nanosheets 115 and 116 that are spaced apart from each other in the first direction X1 may be arranged on the upper surface of the first fin pattern 110. A first epitaxial pattern 150 may be disposed between the first nanosheets 115 and 116, which are spaced apart from each other in the first direction X1.

The first dummy nanosheets 116 may be disposed adjacent to the short sidewall 110b of the first fin pattern 110(e.g., on an end portion of the first fin pattern 110). The first dummy nanosheets 116 may be connected to one first epitaxial pattern 150. For example, the first dummy nanosheets 116 may be disposed next to one first epitaxial pattern 150 and may contact the one first epitaxial pattern 150. The first normal nanosheets 115 may be connected to two first epitaxial patterns 150 disposed at opposite sides of the first normal nanosheets 115 in the first direction X1.

Second nanosheets **215** and **216** may be disposed on the substrate **100**. The second nanosheets **215** and **216** may be disposed on the second fin pattern **210**. The second nanosheets **215** and **216** may include the second normal nanosheets **215** and the second dummy nanosheets **216**.

The second nanosheets 215 and 216 that are spaced apart from each other in the first direction X1 may be arranged on the upper surface of the second fin pattern 210. A second epitaxial pattern 250 may be disposed between the second nanosheets 215 and 216, which are spaced apart from each other in the first direction X1.

The second dummy nanosheets **216** may be disposed adjacent to the short sidewall **210***b* of the second fin pattern **210** (e.g., on an end portion of the second fin pattern **210**). The second dummy nanosheets **216** may be connected to one second epitaxial pattern **250**. For example, the second dummy nanosheets **216** may be disposed adjacent to one second epitaxial pattern **250** and may contact the one second epitaxial pattern **250**. The second normal nanosheets **215** may be connected to two second epitaxial patterns **250** disposed at opposite sides of the second normal nanosheets **215** in the first direction X1. For example, the second epitaxial patterns **250** and may contact the two second epitaxial patterns **250** and may contact the two second epitaxial patterns **250** and may contact the two second epitaxial patterns **250** and may contact the two second epitaxial patterns **250**.

Each of the first nanosheets **115** and **116** and the second nanosheets **215** and **216** may include a plurality of nanosheets sequentially arranged in a thickness direction of the substrate **100** (e.g., the third direction Z1). A plurality of first nanosheets **115** and **116** may be sequentially arranged on the first fin pattern **110**. For example, each of the pluralities of first nanosheets **115** and **116** may be stacked on the first fin pattern **110** in the third direction Z1. A plurality of second nanosheets **215** and **216** may be sequentially arranged on the second fin pattern **210**. For example, each of the pluralities of second nanosheets **215** and **216** may be sequentially arranged on the second fin pattern **210**. For example, each of the pluralities of second nanosheets **215** and **216** may be stacked on the second fin pattern **210** in the third direction Z1.

In FIGS. 2 and 3, it is illustrated that each of the first nanosheets 115 and 116 and the second nanosheets 215 and 216 includes three nanosheets stacked in the thickness direction of the substrate 100 (e.g., the third direction Z1), but the inventive concept is not limited thereto. For example, 5 the first nanosheets 115 and 116 may include one first nanosheet 115 and one first nanosheet 116, and the second nanosheets 215 and 216 may include one second nanosheet 215 and one second nanosheet 216. As another example, the first nanosheets 115 and 116 may include more than three 10 first nanosheets 115 and more than three first nanosheets 115 and more than three first nanosheets 116, and the second nanosheets 215 and 216 may include more than three second nanosheets 215 and 216 may include more than three second nanosheets 215 and 216 may include more than three second nanosheets 215 and 216 may include more than three second nanosheets 216.

The first fin pattern **110** and the first nanosheets **115** and 15 **116** may be formed by selectively etching a portion of a fin structure including the first fin pattern **110** and the first nanosheets **115** and **116**. Thus, a width of each of the first nanosheets **115** and **116** in the second direction Y1 may be equal to or less than a width of the first fin pattern **110** in the 20 second direction Y1. A sidewall of the first dummy nanosheets **116** may be aligned with the short sidewall **110***b* of the first fin pattern **110**. For example, a sidewall of the first dummy nanosheets **116** may be on a same plane in the third direction Z1 as the short sidewall **110***b* of the first fin pattern 25 **110**.

Likewise, the second fin pattern **210** and the second nanosheets **215** and **216** may have the same relationship with one another as that described above with respect to the first fin pattern **110** and the first nanosheets **115** and **116**.

Each of the first nanosheets **115** and **116** and the second nanosheets **215** and **216** may include a semiconductor material, for example, silicon or germanium. In some embodiments, each of the first nanosheets **115** and **116** and the second nanosheets **215** and **216** may include a compound 35 semiconductor, for example, a group IV-IV compound semiconductor.

The first nanosheets **115** and **116** may include the same material as corresponding ones of the second nanosheets **215** and **216** at the same height level (e.g., vertical level in the 40 third direction Z1).

The first normal nanosheets **115** and the second normal nanosheets **215** may be used as channel regions of respective ones of transistors including the first normal nanosheets **115** and the second normal nanosheets **215**. The first normal 45 nanosheets **115** including the plurality of nanosheets that are stacked in the thickness direction of the substrate **100** and the second normal nanosheets **215** including the plurality of nanosheets that are stacked in the thickness direction of the substrate **100** may include the same material or different 50 materials. For example, a lowermost one of the plurality of nanosheets of the first normal nanosheets **115** adjacent to the first fin pattern **110** and a next lowermost one of the plurality of nanosheets of the first normal nanosheets **115** adjacent to the first fin pattern **110** may have the same material or 55 different materials.

The first nanosheets **115** and **116** may include the same material as, or a different material from, the first fin pattern **110**.

Each of the first gate structures **120** and **120\_1** may extend <sup>60</sup> lengthwise in the second direction Y1. The first gate structures **120** and **120\_1** may cross the first fin pattern **110**. The first gate structures **120** and **120\_1** may include a first end gate structure **120** and a first normal gate structure **120\_1**. The first end gate structure **120** may overlap the end portion <sup>65</sup> of the first fin pattern **110**. The first end gate structure **120** may overlap the short sidewall **110***b* of the first fin pattern

8

110. For example, the first end gate structure 120 may extend beyond the short sidewall 110b of the first fin pattern 110 in the first direction X1.

The first gate structures 120 and 120\_1 may traverse the first nanosheets 115 and 116, respectively, and may be spaced apart from each other in the first direction X1. The first normal gate structure 120\_1 may surround each of the first normal nanosheets 115. The first end gate structure 120 may surround each of the first dummy nanosheets 116.

Each of the second gate structures **220** and **220\_1** may extend lengthwise in the second direction Y1. Each of the second gate structures **220** and **220\_1** may cross the second fin pattern **210**. The second gate structures **220** and **220\_1** may include a second end gate structure **220** and a second normal gate structure **220\_1**. The second end gate structure **220** may overlap the end portion of the second fin pattern **210**. The second end gate structure **220** may overlap the short sidewall **210***b* of the second fin pattern **210**. For example, the second end gate structure **220** may extend beyond the short sidewall **210***b* of the second fin pattern **210** in the negative first direction X1.

The second gate structures 220 and 220\_1 may traverse the second nanosheets 215 and 216, respectively, and may be spaced apart from each other in the first direction X1. The second normal gate structure 220\_1 may surround each of the second normal nanosheets 215. The second end gate structure 220 may surround each of the second dummy nanosheets 216.

In some embodiments, the first end gate structure **120** and the second end gate structure **220** may contact the first fin liner **111** extending along the sidewall of the first fin-cut trench **105***t*. For example, the first and second end gate structures **120** may contact upper surfaces of the first fin liner **111**.

The first end gate structure **120** and the second end gate structure **220** may be spaced apart from the upper surface of the first field insulation layer **105** in a height direction of the first fin pattern **110** and a height direction of the second fin pattern **210**. For example, lower surfaces of the first end gate structure **120** and the second end gate structure **220** may be at a higher vertical level (e.g., in the third direction Z1) than an upper surface of the first field insulation layer **105**.

A portion of the first fin liner **111** may not be covered by the first field insulation layer **105** between the lower surface of the first end gate structure **120** and the upper surface of the first field insulation layer **105**. A portion of the first fin liner **111** may not be covered by the first field insulation layer **105** between the lower surface of the second end gate structure **220** and the upper surface of the first field insulation layer **105**.

In some embodiments, the first end gate structure 120 and the second end gate structure 220 may not contact the first field insulation layer 105 between the short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210, whereas the first end gate structure 120 and the second end gate structure 220 may contact the second field insulation layer 106 disposed on the long sidewall 110a of the first fin pattern 110 and the long sidewall 210a of the second fin pattern 210.

A distance from a center line of the first end gate structure **120** to a center line of the second end gate structure **220** may be a first distance W11. A distance between the first fin pattern **110** and the second fin pattern **210** separated by the first fin-cut trench **105**t may be a second distance W12. In some embodiments, the second distance W12 may be the distance between the short sidewall **110**b of the first fin pattern **110** and the short sidewall **210**b of the second fin

60

65

pattern 210. For example, the second distance W12 may be defined based on the upper surface of the first fin pattern 110 and the upper surface of the second fin pattern 210. In some embodiments, the second distance W12 may be a distance between the first dummy nanosheets 116 and the second 5 dummy nanosheets 216.

In some embodiments, the first distance W11 may be greater than the second distance W12. For example, a pitch between adjacent ones of the first gate structures 120 and 120\_1 and the second gate structures 220 and 220\_1 may be 10 greater than a separation width between the first fin pattern 110 and the second fin pattern 210 that are adjacent to each other.

Each of the first gate structures 120 and 120\_1 may include a first gate electrode 130, a first gate insulation layer 15 135, first gate spacers 140, a first gate trench 140t, and a first capping pattern 145. Each of the second gate structures 220 and 220\_1 may include a second gate electrode 230, a second gate insulation layer 235, second gate spacers 240, a second gate trench 240t, and a second capping pattern 245. 20

Hereinafter, it will be described with respect to the first gate structures 120 and 120\_1. Descriptions of the second gate structures 220 and 220\_1 will be understood through descriptions of the first gate structures 120 and 120\_1. For example, descriptions of the second gate electrode 230, the 25 second gate insulation layer 235, the second gate spacers 240, the second gate trench 240t, and the second capping pattern 245 may be the same as descriptions of the first gate electrode 130, the first gate insulation layer 135, the first gate spacers 140, the first gate trench 140t, and the first capping 30 pattern 145, respectively.

The first gate spacers 140 may extend lengthwise in the second direction Y1. The first gate spacers 140 may cross the first nanosheets 115 and 116. The first gate spacers 140 may define the first gate trench 140t traversing the first 35 nanosheets 115 and 116. For example, the interior sidewalls of the first gate spacers 140 may define the first gate trench 140t.

The first gate spacers 140 may be disposed on opposite end portions, respectively, of the first normal nanosheets 115 40 oxide, silicon oxynitride, silicon nitride, and/or a high-k extending in the first direction X1. For example, the first gate spacers 140 may be disposed on opposite sides of the first normal nanosheets 115. The first gate spacers 140 may each include a through portion through which the first normal nanosheets 115 pass. 45

Each nanosheet of the first normal nanosheets 115 may pass through the first gate spacers 140. The first gate spacers 140 may contact entire circumferential surfaces of end portions of each nanosheet of the first normal nanosheets 115.

However, the first dummy nanosheets 116 may pass through one of the first gate spacers 140. The first gate spacer 140 through which the first dummy nanosheets 116 pass may contact entire circumferential surfaces of one end portion of each nanosheet of the first dummy nanosheets 55 116.

The first gate spacers 140 may be disposed between the first fin pattern 110 and the lowermost nanosheet of each of the first nanosheets 115 and 116 and between respective nanosheets of the first nanosheets 115 and 116.

The first gate spacer 140 disposed on the end portion of the first fin pattern 110 may not contact the upper surface of the first field insulation layer 105 between the short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210.

A portion of the first fin liner 111 not covered by the first field insulation layer 105 may be disposed between the first

gate spacer 140 and the upper surface of the first field insulation layer 105. For example, the first gate spacer 140 may be above the portion of the first fin liner 111 that is not covered by the first field insulation layer 105.

A height H11 from the bottom surface of the first fin-cut trench 105t to a lower surface of the first gate spacer 140 may be greater than a height H12 from the bottom surface of the first fin-cut trench 105t to the upper surface of the first field insulation layer 105. In some embodiments, the bottom surface of the first fin-cut trench 105t may be on the same plane as the upper surface of the substrate 100, and the height H11 may be the distance between the upper surface of the substrate 100 and the upper surface of the first fin pattern 110 or the second fin pattern 210.

The first gate spacers 140 may include, for example, silicon nitride (SiN), silicon oxynitride (SiON), silicon oxide (SiO<sub>2</sub>), silicon oxycarbonitride (SiOCN), silicon boron nitride (SiBN), silicon oxyboronitride (SiOBN), silicon oxycarbide (SiOC), or a combination thereof.

The first gate insulation layer 135 may be disposed along the circumferential surfaces of the first nanosheets 115 and 116. The first gate insulation layer 135 may surround each nanosheet of the first nanosheets  $\mathbf{115}$  and  $\mathbf{116}.$  The first gate insulation layer 135 may be disposed on the upper surface of the second field insulation layer 106 and on the first fin pattern 110. The first gate insulation layer 135 may extend along inner surfaces of the first gate spacers 140.

The first gate insulation layer 135 may extend along a sidewall and a bottom surface of the first gate trench 140t and along the circumferential surface of each nanosheet of the first nanosheets 115 and 116.

An interfacial layer (not shown) may be disposed between the first gate insulation layer 135 and each nanosheet of the first nanosheets 115 and 116 and between the first gate insulation layer 135 and the first fin pattern 110. Depending on a method of forming the interfacial layer, the interfacial layer may be formed with the same profile as the first gate insulation layer 135.

The first gate insulation layer 135 may include silicon dielectric material having a higher dielectric constant than silicon oxide. The first gate insulation layer 135 may include the high-k dielectric material, for example, hafnium oxide, hafnium silicon oxide, hafnium aluminum oxide, lanthanum oxide, lanthanum aluminum oxide, zirconium oxide, zirconium silicon oxide, tantalum oxide, titanium oxide, barium strontium titanium oxide, barium titanium oxide, strontium titanium oxide, yttrium oxide, aluminum oxide, lead scandium tantalum oxide, and/or lead zinc niobate.

The first gate electrode 130 may traverse the first fin pattern 110 and the first nanosheets 115 and 116. The first gate electrode 130 may surround the circumferential surface of each nanosheet of the first nanosheets 115 and 116. The first gate electrode 130 may be disposed in a space between the first fin pattern 110 and the lowermost nanosheet of each of the first nanosheets 115 and 116. The first gate electrode 130 may be disposed between the first gate spacers 140. The first gate electrode 130 may fill a portion of the first gate trench 140t and may extend lengthwise in the second direction Y1.

The first gate electrode 130 may include, for example, titanium nitride (TiN), tantalum carbide (TaC), tantalum nitride (TaN), titanium silicon nitride (TiSiN), tantalum silicon nitride (TaSiN), tantalum titanium nitride (TaTiN), titanium aluminum nitride (TiAlN), tantalum aluminum nitride (TaAlN), tungsten nitride (WN), ruthenium (Ru). titanium aluminum (TiAl), titanium aluminum carbonitride

(TiAlC—N), titanium aluminum carbide (TiAlC), titanium carbide (TiC), tantalum carbonitride (TaCN), tungsten (W), aluminum (Al), copper (Cu), cobalt (Co), titanium (Ti), tantalum (Ta), nickel (Ni), platinum (Pt), nickel platinum (Ni—Pt), niobium (Nb), niobium nitride (NbN), niobium 5 carbide (NbC), molybdenum (Mo), molybdenum nitride (MoN), molybdenum carbide (MoC), tungsten carbide (WC), rhodium (Rh), palladium (Pd), iridium (Ir), osmium (Os), silver (Ag), gold (Au), zinc (Zn), vanadium (V), or a combination thereof. The first gate electrode **130** may 10 include conductive metal oxide or conductive metal oxynitride. The first gate electrode **130** may include an oxidized form of the above-mentioned material.

The first gate electrode **130** may be formed by a replacement process or a gate last process, but it is not limited 15 thereto.

The first capping pattern 145 may be disposed on the first gate electrode 130. The first capping pattern 145 may fill the remainder of first gate trench 140*t* having the first gate electrode 130. In some embodiments, an upper surface of the 20 first capping pattern 145 may be coplanar with upper surfaces of the first gate spacers 140.

Although the first gate insulation layer **135** is shown not to be disposed between the first gate spacers **140** and the first capping pattern **145**, it is for convenience of explanation, 25 and the inventive concept is not limited thereto. For example, in some embodiments, the first gate insulation layer **135** may be disposed between the first gate spacers **140** and the first capping pattern **145**.

In FIG. 2, the first capping pattern 145 is shown to be 30 disposed between the inner sidewalls of the first gate spacers 140, but the inventive concept is not limited thereto. Upper surfaces of the first gate spacers 140 may be recessed lower than an upper surface of a lower interlayer insulation layer 191 disposed between the adjacent ones of the first and 35 second gate structures 120, 120\_1, 220, and 220\_1, like the first gate electrode 130. For example, in some embodiments, the upper surfaces of the first gate spacers 140 may be coplanar with upper surfaces of the first gate electrode 130. As such, the first capping pattern 145 may be disposed on the 40 upper surfaces of the first gate spacers 140 and an upper surface of the first gate electrode 130.

An upper surface of the first capping pattern **145** may be coplanar with the upper surface of the lower interlayer insulation layer **191**. The first capping pattern **145** may 45 include a material having an etch selectivity with respect to a material of the lower interlayer insulation layer **191**. The first capping pattern **145** may include, for example, silicon nitride (SiN), silicon oxynitride (SiON), silicon oxide (SiO<sub>2</sub>), silicon carbonitride (SiCN), silicon oxycarbonitride 50 (SiOCN), or a combination thereof.

A first epitaxial pattern 150 may be disposed between the adjacent first gate structures 120 and 120\_1. The first epitaxial pattern 150 may be disposed on the first fin pattern 110. The first epitaxial pattern 150 may be disposed at the 55 opposite sides of the first normal nanosheets 115. The first epitaxial pattern 150 may be disposed at one side of the first dummy nanosheets 116. For example, the first epitaxial pattern 150 may be disposed between the first normal nanosheets 115 and the first dummy nanosheets 116. The 60 first epitaxial pattern 150 may be connected to the first nanosheets 115 and 116. For example, the first epitaxial pattern 150 may be disposed to the first nanosheets 115 and 116. For example, the first epitaxial pattern 150 may contact the first nanosheets 115 and 116.

A second epitaxial pattern **250** may be disposed between the adjacent second gate structures **220** and **220\_1**. The 65 second epitaxial pattern **250** may be disposed on the second fin pattern **210**. The second epitaxial pattern **250** may be

disposed at the opposite sides of the second normal nanosheets **215**. The second epitaxial pattern **250** may be disposed at one side of the second dummy nanosheets **216**. For example, the second epitaxial pattern **250** may be disposed between the second normal nanosheets **215** and the second dummy nanosheets **216**. The second epitaxial pattern **250** may be connected to the second nanosheets **215** and **216**. For example, the second epitaxial pattern **250** may contact the second nanosheets **215** and **216**.

The first epitaxial pattern **150** and the second epitaxial pattern **250** may be formed by an epitaxial growth process.

The first epitaxial pattern **150** may be included in a source/drain of the transistor utilizing the first normal nanosheets **115** as the channel region. The second epitaxial pattern **250** may be included in a source/drain of the transistor utilizing the second normal nanosheets **215** as the channel region.

The first epitaxial pattern 150 and the second epitaxial pattern 250 may be included in source/drains of the transistors of the same conductive type. When each of the first epitaxial pattern 150 and the second epitaxial pattern 250 is included in a source/drain of a PMOS transistor, each of the first epitaxial pattern 150 and the second epitaxial pattern 250 may include a compressive stress material. The compressive stress material may be a material having a larger lattice constant than silicon. For example, the compressive stress material may be silicon germanium (SiGe). When each of the first epitaxial pattern 150 and the second epitaxial pattern 250 is included in a source/drain of an NMOS transistor, each of the first epitaxial pattern 150 and the second epitaxial pattern 250 may include a tensile stress material. For example, the tensile stress material may be silicon (Si) or silicon carbide (SiC).

The first insulation liner 155 may extend along a profile of the first epitaxial pattern 150, a profile of the second epitaxial pattern 250, outer sidewalls of the first gate spacers 140, outer sidewalls of the second gate spacers 240, and the upper surface of the first field insulation layer 105. For example, the first insulation liner 155 may contact top surfaces of the first and second epitaxial patterns 150 and 250, outer sidewalls of the first and second gate spacers 140 and 240, and the upper surface of the first field insulation layer 105.

The first insulation liner **155** may contact the first fin liner **111** between the first gate spacer **140** and the first field insulation layer **105** and between the second gate spacer **240** and the first field insulation layer **105**. For example, the first insulation liner **155** may contact the first fin liner **111** between the first end gate structure **120** and the first field insulation layer **105** and between the second end gate structure **220** and the first field insulation layer **105**.

A portion of the first insulation liner 155 may be disposed between the first gate spacer 140 and the upper surface of the first field insulation layer 105, such that the first gate spacer 140 may not contact the first field insulation layer 105. A portion of the first insulation liner 155 may be disposed between the second gate spacer 240 and the upper surface of the first field insulation layer 105, such that the second gate spacer 240 may not contact the first field insulation layer 105.

The first insulation liner 155 may be disposed along at least a portion of the exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t. The first insulation liner 155 may be disposed on a portion of the first liner trench 111t defined by the first fin liner 111.

The first insulation liner **155** may include, for example, silicon nitride (SiN), silicon oxynitride (SiON), silicon oxide

(SiO<sub>2</sub>), silicon carbonitride (SiCN), silicon oxycarbonitride (SiOCN), or a combination thereof. The first insulation liner **155** may include a material having an etch selectivity with respect to the lower interlayer insulation layer **191**.

The interlayer insulation layer **190** may be disposed on 5 the first insulation liner **155**. The interlayer insulation layer **190** may cover the outer sidewalls of the first gate spacers **140** and the outer sidewalls of the second gate spacers **240**.

The interlayer insulation layer **190** may include the lower interlayer insulation layer **191** and an upper interlayer insulation layer **192** on the lower interlayer insulation layer **191**. The lower interlayer insulation layer **191** may be disposed between the adjacent ones of the first and second gate structures **120**, **120\_1**, **220**, and **220\_1**. For example, the lower interlayer insulation layer **191** may be disposed on the 15 first insulation liner **155**, and may contact the first insulation liner **155**. The upper interlayer insulation layer **192** may be disposed on the first gate structures **120** and **120\_1** and the second gate structures **220** and **220\_1**. The lower interlayer insulation layer **191** and the upper interlayer insulation layer 20 **192** may include, for example, silicon oxide, silicon nitride, and/or silicon oxynitride.

A cross-section of example first normal nanosheets **115** taken in the second direction Y1 will be described with reference to FIGS. **4**A to **4**D.

Referring to 4A, a cross-section 115s of the first normal nanosheet 115A may be a shape formed by combination of four straight lines 115m and four curved lines 115n. For example, the cross-section 115s of the first normal nanosheet 115A may be a quadrilateral with rounded corners. In the 30 cross-section 115s of the first normal nanosheet 115A, a width L1 of the first normal nanosheet 115A may be different from a height L2 of the first normal nanosheet 115A. For example, the cross-section 115s of the first normal nanosheet 115A. For example, the cross-section 115s of the first normal nanosheet 115A. For example, the cross-section 115s of the first normal nanosheet 115A. For example, the cross-section 115s of the first normal nanosheet 115A may be a rectangle with rounded corners, but it is not 35 limited thereto.

Referring to FIG. 4B, in the cross-section 115s of the first normal nanosheet 115B, the width L1 of the first normal nanosheet 115B and the height L2 of the first normal nanosheet 115B may be the same. For example, the cross- 40 section 115s of the first normal nanosheet 115B may be a square with rounded corners, but it is not limited thereto.

Referring to FIG. 4C, in the cross-section 115s of the first normal nanosheet 115C, a width L11 of one of opposite sides of the first normal nanosheet 115C may be different from a 45 width L12 of the other of the opposite sides of the first normal nanosheet 115C. For example, the cross-section 115s of the first normal nanosheet 115C may be a trapezoid with rounded corners, but it is not limited thereto.

Referring to FIG. 4D, the cross-section 115s of the first 50 normal nanosheet 115D may be a shape formed by combination of curved lines 115n, for example, a circle.

In some embodiments, unlike those shown in FIG. 4A to 4D, the cross-section 115s of the first normal nanosheet 115 may be a shape formed by a combination of straight lines 55 (e.g., a polygon). For example, the cross-section 115s of the first normal nanosheet 115 may be a shape formed by four linear segments that intersect one another (e.g., a quadrilateral without rounded corners). As another example, the cross-section 115s of the first normal may be a shape formed 60 by three linear segments that intersect one another (e.g., a triangle).

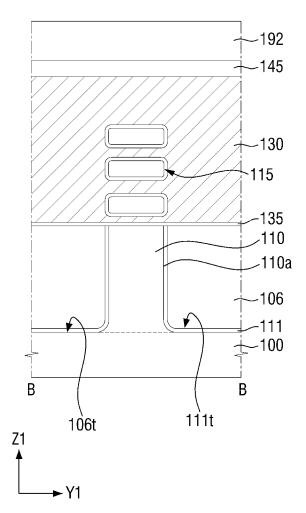

A cross-section of example first normal nanosheets **115** taken in the first direction X1 will be described with reference to FIGS. **5**A to **5**C.

65

Referring to FIG. 5A, a thickness of the first normal nanosheet 115E may be substantially constant in a direction

extending away from the first epitaxial pattern **150** and the first gate spacers **140** (e.g., in the first direction X1). For example, a thickness  $t1_a$  of the end portion of the first normal nanosheet **115**E adjacent to the first epitaxial pattern **150** may be equal to a thickness  $t1_b$  of a central portion of the first normal nanosheet **115**E. Thickness may refer to the thickness or height measured in a direction perpendicular to a top surface of the substrate **100** (e.g., the third direction Z1).

Referring to FIG. 5B, the thicknesses of the first normal nanosheet 115F may decrease in the direction extending away from the first epitaxial pattern 150 and the first gate spacers 140. For example, the thickness  $t1_a$  of the opposite end portions of the first normal nanosheet 115F adjacent to the first epitaxial pattern 150 may be greater than the thickness  $t1_b$  of the central portion of the first normal nanosheet 115F. In some embodiments, the upper surface of the first normal nanosheet 115F may have a concave shape with respect to a top surface of the substrate 100, and the lower surface of first normal nanosheet 115F may have a convex shape with respect to the top surface of the substrate 100.

Referring to FIG. 5C, the thickness of the first normal nanosheet 115G may increase in the direction extending 25 away from the first epitaxial pattern 150 and the first gate spacers 140. For example, the thicknesses t1\_a of the opposite end portions of the first normal nanosheet 115G adjacent to the first epitaxial pattern 150 may be smaller than the thickness t1\_b of the central portion of the first normal nanosheet 115G. In some embodiments, the upper surface of the first normal nanosheet 115G may have a convex shape with respect to a top surface of the substrate 100, and the lower surface of first normal nanosheet 115G may have a concave shape with respect to the top surface of the substrate 35 100.

In FIGS. **5**B and **5**C, the thicknesses of the first normal nanosheets **115**F and **115**G may continuously change in the direction extending away from the first epitaxial pattern **150** and the first gate spacers **140**. For example, the thickness of the first normal nanosheet **115**F may gradually and continuously decrease in directions toward the middle of the first normal nanosheet **115**F, and the thickness of the first normal nanosheet **115**F.

A cross-section of example first normal nanosheet **115**H taken in the first direction X1 will be described with reference to FIG. **6**.

The first normal nanosheet **115**H may be a trimmed sheet pattern. The first normal nanosheet **115**H may include a first portion **115***a* and second portions **115***b*. The second portions **115***b* of the first normal nanosheet **115**H may be disposed at opposite sides of the first portion **115***a* of the first normal nanosheet **115**H. The second portions **115***b* of the first normal nanosheet **115**H. The second portions **115***b* of the first normal nanosheet **115**H may be overlapped with the first gate spacers **140**. The first portion **115***a* of the first normal nanosheet **115**H may be overlapped with the first gate insulation layer **135** and the first gate electrode **130**.

Thicknesses  $t1_c$  of the second portions 115b of the first normal nanosheet 115 may be greater than a thickness  $t1_d$ of the first portion 115a of the first normal nanosheet 115. The change from the thicknesses  $t1_c$  to the thickness  $t1_d$ (and vice versa) may be abrupt, such that inner vertical sidewalls may be formed in the first normal nanosheet 115H. The inner vertical sidewalls may include upper inner vertical sidewalls  $115c_u$  and lower inner vertical sidewalls  $115c_l$ of the second portions 115b. The upper inner vertical side

10

45

55

walls  $115c_u$  may connect planar upper surfaces of the second portions 115b to a planar upper surface of the first portion 115a, and the lower inner vertical sidewalls  $115c_l$  may connect planar lower surfaces of the second portions 115b to a planar lower surface of the first portion 115a.

Unlike that shown in FIG. 6, in some embodiments, a connection portion between the second portion 115b of the first normal nanosheet 115H and the first portion 115a of the first normal nanosheet 115H may be rounded. In FIG. 6, although the thickness of the first portion 115a of the first normal nanosheet 115H is shown to be constant regardless of its location, it is for convenience of explanation, and the inventive concept is not limited thereto. For example, the thickness of the first portion 115a of the first normal nanosheet 115H may change as shown in FIG. 5B or 5C.

FIG. 7 is a view illustrating a semiconductor device according to example embodiments of the inventive concept. In FIG. 7, main differences between the present embodiment and the embodiments of FIGS. 1 to 6 will be  $_{20}$  described.

Referring to FIG. 7, a semiconductor device according to example embodiments of the inventive concept may further include a semiconductor nodule 150 dN protruding from the short sidewall 110b of the first fin pattern 110 toward the <sup>25</sup> second fin pattern 210.

The semiconductor nodule 150dN may also be disposed on the short sidewall 210b of the second fin pattern 210. The semiconductor nodule 150dN may be formed on the region (s) of the first fin pattern 110 and/or the second fin pattern 210 corresponding to the exposed region  $105t_E$  of the first fin-cut trench 105t.

The semiconductor nodule 150dN may be disposed on the short sidewall 110b of the first fin pattern 110 between the lower surface of the first end gate structure 120 and the upper surface of the first field insulation layer 105. In addition, the semiconductor nodule 150dN may be disposed on the short sidewall 210b of the second fin pattern 210 between the lower surface of the first field insulation layer 40 220 and the upper surface of the first field insulation layer 105.

In some embodiments, the semiconductor nodule 150dN may be disposed on one of the first fin pattern 110 and the second fin pattern 210.

The first fin liner **111** may be partly disposed on the exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t. For example, the first fin liner **111** may be disposed on a portion of the exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t and may not be disposed on the remainder of the exposed 50 region 105t E of the first fin-cut trench 105t.

The exposed region  $105t_{\rm E}$  of the first fin-cut trench 105t on which the first fin liner 111 is not disposed may not be covered by the first field insulation layer 105, the first gate spacer 140, and the second gate spacer 240.

The semiconductor nodule **150***d*N may be disposed on the short sidewall **110***b* of the first fin pattern **110** and/or the short sidewall **210***b* of the second fin pattern **210** that are not covered by the first fin liner **111**, the first field insulation layer **105**, the first gate spacer **140**, and the second gate <sup>60</sup> spacer **240**. In some embodiments, the semiconductor nodule **150***d*N formed on the first fin liner **111** and a lower surface of the first gate spacer **140**, and the semiconductor nodule **150***d*N formed on the second fin pattern **210** may contact an upper surface of the first fin liner **111** and a lower surface of the first gate spacer **140**, and the semiconductor nodule **150***d*N formed on the second fin pattern **210** may contact an 65 upper surface of the first fin liner **111** and a lower surface of the second gate spacer **240**.

The semiconductor nodule 150dN may include the material included in the first epitaxial pattern 150 and the second epitaxial pattern 250.

The first insulation liner 155 may extend along a profile of the semiconductor nodule 150dN. For example, the first insulation liner 155 may contact the semiconductor nodule 150dN.

As shown in FIG. 7, the semiconductor nodule 150dN may be disposed between the first gate spacer 140 and the first fin liner 111 and between the second gate spacer 240 and the first fin liner 111, but the inventive concept is not limited thereto.

In some embodiments, a portion of the first fin liner **111** may remain between the semiconductor nodule **150***d*N and the first gate spacer **140**, and/or between the semiconductor nodule **150***d*N and the second gate spacer **240**.

In some embodiments, the semiconductor nodule 150dN protruding from the first fin pattern 110 may contact the semiconductor nodule 150dN protruding from the second fin pattern 210.

FIG. 8 is a view illustrating a semiconductor device according to example embodiments of the inventive concept. In FIG. 8, main differences between the present embodiment and the embodiments of FIGS. 1 to 6 will be described.

Referring to FIG. 8, in a semiconductor device according to example embodiments of the inventive concept, a portion of the first gate spacer 140 and a portion of the second gate spacer 240 may be disposed along the sidewall of the first fin-cut trench 105t. For example, a lower surface of the first gate spacer 140 and a lower surface of the second gate spacer 240 may be at lower vertical levels than upper surfaces of the first and second fin patterns 110 and 210.

The first fin liner 111 may be disposed on the short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210 defining a portion of the sidewall of the first fin-cut trench 105t. The first end gate structure 120 and the second end gate structure 220 may respectively be disposed on the short sidewall 110b of the first fin pattern 110 and the short sidewall 210b of the second fin pattern 210 defining the remainder of the sidewall of the first fin-cut trench 105t. In some embodiments, the first gate insulation layer 135 of the first end gate structure 120 may be disposed on the short sidewall 110b of the first fin pattern 110, and the second gate insulation layer 235 of the second end gate structure 220 may be disposed on the short sidewall 210b of the second fin pattern 210. In some embodiments, the first gate insulation layer 135 may be disposed between the first gate spacer 140 and the short sidewall 110b of the first fin pattern 110, and the second gate insulation layer 235 may be disposed between the second gate spacer 240 and the short sidewall 210b of the second fin pattern 210.

The first end gate structure **120** and the second end gate structure **220** may contact the first fin liner **111** disposed along the sidewall of the first fin-cut trench **105***t*.

FIG. 9 is a view illustrating a semiconductor device according to example embodiments of the inventive concept. In FIG. 9, main differences between the present embodiment and the embodiments of FIGS. 1 to 6 will be described.

Referring to FIG. 9, in a semiconductor device according to example embodiments of the inventive concept, the first insulation liner 155 may include a first lower insulation liner 155a and a first upper insulation liner 155b.

The first lower insulation liner 155a may contact the first fin liner 111 along the portion of the exposed region  $105t_{\text{E}}$

of the first fin-cut trench 105*t*. In addition, the first lower insulation liner 155*a* may contact an upper surface of the first field insulation layer 105, upper surfaces of the first epitaxial pattern 150 and the second epitaxial pattern 250, and side surfaces of the first gate spacers 140 and the second 5 gate spacers 240. The first upper insulation liner 155*b* may be disposed on the first lower insulation liner 155*a*.

The first lower insulation liner 155a may include, for example, silicon oxycarbonitride (SiOCN). The first upper insulation liner 155b may include, for example, silicon 10 nitride (SiN), silicon oxynitride (SiON), silicon oxide (SiO<sub>2</sub>), or a combination thereof.

FIG. 10 is a view illustrating a semiconductor device according to example embodiments of the inventive concept. In FIG. 10, main differences between the present 15 embodiment and the embodiments of FIGS. 1 to 6 will be described.

Referring to FIG. 10, in a semiconductor device according to example embodiments of the inventive concept, each of the first gate structures 120 and 120\_1 and the second gate 20 structures 220 and 220\_1 may not include the capping pattern on the first and second gate electrodes 130 and 230.

In FIG. 10, since the first capping pattern (see, e.g., the first capping pattern 145 of FIG. 2) is not disposed on the first gate electrode 130 and the second capping pattern (see, 25 e.g., the second capping pattern 245 of FIG. 2) is not disposed on the second gate electrode 230, an upper surface of the first gate electrode 130 and an upper surface of the second gate electrode 230 may be coplanar with the upper surface of the lower interlayer insulation layer 191. 30

FIG. **11** is a plan view illustrating a semiconductor device according to example embodiments of the inventive concept. FIG. **12** is a cross-sectional view taken along line C-C of FIG. **11**. In FIGS. **11** and **12**, main differences between the present embodiment and the embodiments of FIGS. **1** to **6** 35 will be described.

Referring to FIGS. 11 and 12, a semiconductor device according to example embodiments of the inventive concept may further include a dummy gate structure 170 disposed between the first end gate structure 120 and the second end 40 gate structure 220, extending lengthwise in the second direction Y1. The lower interlayer insulation layer 191 may be disposed between the first end gate structure 120 and the dummy gate structure 170 and between the second end gate structure 220 and the dummy gate structure 170. 45

The dummy gate structure 170 may pass between the short sidewall 110*b* of the first fin pattern 110 and the short sidewall 210*b* of the second fin pattern 210. The dummy gate structure 170 may not cross the first fin pattern 110 and the second fin pattern 210. The dummy gate structure 170 may 50 not overlap the first fin pattern 110 and the second fin pattern 210. For example, the dummy gate structure 170 may maintain a constant distance in the first fin pattern 110 and a constant distance in the first fin pattern 110 and a sidewall 210*b* of the second fin pattern 210.

The dummy gate structure 170 may be disposed on the first field insulation layer 105 in the first fin-cut trench 105t. The dummy gate structure 170 may be disposed on the upper surface of the first field insulation layer 105. The dummy <sup>60</sup> gate structure 170 may be disposed on the first field insulation layer 105 between the first fin pattern 110 and the second fin pattern 210.

The dummy gate structure **170** may contact the upper surface of the first field insulation layer **105**.

65

Since the dummy gate structure **170** does not cross the first fin pattern **110** or the second fin pattern **210**, the first fin

liner 111 extending along the sidewall and the bottom surface of the first fin-cut trench 105t may not contact the dummy gate structure 170.

An upper surface of a portion of the first field insulation layer 105 contacting the dummy gate structure 170 may be higher than an upper surface of another portion of the first field insulation layer 105 contacting the first fin liner 111 on the sidewall of the first fin-cut trench 105t. In the process of forming the first epitaxial pattern 150 and the second epitaxial pattern 250, the first field insulation layer 105 below the first end gate structure 120 and the second end gate structure 220 may partly be removed. Accordingly, a height of the upper surface of the first field insulation layer 105 below the dummy gate structure 170 may be greater than a height of the upper surface of the first field insulation layer 105 below the first end gate structure 120 and the second end gate structure 220 with respect to the upper surface of the substrate 100. In some embodiments, the upper surface of the first field insulation layer 105 below the dummy gate structure 170 may be at the same vertical level (e.g., in the third direction Z1) as upper surfaces of the first fin pattern 110 and the second fin pattern 210.

A distance between the center line of the first end gate structure 120 and the center line of the second end gate structure 220 with the dummy gate structure 170 therebetween may be a third distance W21. A distance between the first fin pattern 110 and the second fin pattern 210 with the dummy gate structure 170 therebetween may be a fourth distance W22. In some embodiments, the fourth distance W22 may be the distance between the short sidewall 110*b* of the first fin pattern 110 and the short sidewall 210*b* of the second fin pattern 210. As an example, the third distance W21 may be greater than the fourth distance W22.

The dummy gate structure 170 may include a dummy gate electrode 171, a dummy gate insulation layer 172, dummy gate spacers 173, a dummy gate trench 173t, and a dummy capping pattern 174.

The dummy gate spacers 173 may extend lengthwise in the second direction Y1. The dummy gate spacers 173 may define the dummy gate trench 173t.

The dummy gate insulation layer **172** may extend along a bottom surface and a sidewall of the dummy gate trench **173***t*. The dummy gate insulation layer **172** may contact the upper surface of the first field insulation layer **105** below the dummy gate structure **170**.

The dummy gate electrode 171 may be disposed between the dummy gate spacers 173. The dummy gate electrode 171may be disposed on the dummy gate insulation layer 172. An upper surface of the dummy gate electrode 171 may be coplanar with an upper surface of the dummy gate insulation layer 172. The dummy gate electrode 171 may partly fill the dummy gate trench 173t.

The dummy capping pattern 174 may be disposed on the dummy gate electrode 171. The dummy capping pattern 174 may contact the upper surface of the dummy gate insulation layer 172. The dummy capping pattern 174 may fill the remainder of the dummy gate trench 173*t* having the dummy gate electrode 171. An upper surface of the dummy capping pattern 174 may be coplanar with upper surfaces of the dummy gate spacers 173 and the lower interlayer insulation layer 191.

FIG. **13** is a plan view illustrating a semiconductor device according to example embodiments of the inventive concept. FIG. **14** is a cross-sectional view taken along line D-D of FIG. **13**. FIG. **15** is a view for comparing a thickness of

a first insulation liner in a first region I of FIG. 13 with a thickness of a second insulation liner in a second region II of FIG. 13.

A cross-sectional view taken along line A-A of FIG. 13 may be substantially the same as one of the views of FIGS. 5 2, 7, and 8.

In addition, the first fin pattern 110, the second fin pattern 210, the first normal nanosheets 115, the first dummy nanosheets 116, the second normal nanosheets 215, the second dummy nanosheets **216**, the first gate structures **120** and 120 1, the second gate structures 220 and 220 1, the first fin liner 111, and the first insulation liner 155 as shown in a first region I of FIG. 13 and the cross-sectional view taken along line A-A of FIG. 13 may be substantially the same as described with reference to FIGS. 1 to 8. Accord- 15 ingly, descriptions of FIGS. 13 to 15 will be mainly made with reference to contents shown in a second region II.

Referring to FIGS. 13 to 15, a semiconductor device according to example embodiments of the inventive concept may include the first fin pattern 110, the second fin pattern 20 210, a third fin pattern 310, a fourth fin pattern 410, the first normal nanosheets 115, the first dummy nanosheets 116, the second normal nanosheets 215, the second dummy nanosheets 216, third normal nanosheets 315, third dummy nanosheets 316, fourth normal nanosheets 415, fourth 25 may include the same material. In some embodiments, each dummy nanosheets 416, the first gate structures 120 and 120\_1, the second gate structures 220 and 220\_1, third gate structures 320 and 320\_1, fourth gate structures 420 and 420 1, the first fin liner 111, a second fin liner 311, the first insulation liner 155, and a second insulation liner 355.

The substrate 100 may include the first region I and the second region II. The first region I may be a PMOS region. The second region II may be an NMOS region.

Each of the first normal nanosheets 115 and the second normal nanosheets 215 in the first region I may be utilized 35 as a channel region of a PMOS transistor. For example, the first normal nanosheets 115 may be utilized as one channel region of a PMOS transistor, and the second normal nanosheets 215 may be utilized as another channel region of a PMOS transistor. Each of the third normal nanosheets 315 40 and the fourth normal nanosheets 415 in the second region II may be utilized as a channel region of an NMOS transistor. For example, the third normal nanosheets 315 may be utilized as one channel region of an NMOS transistor, and the fourth normal nanosheets 415 may be utilized as another 45 channel region of an NMOS transistor.

The third fin pattern 310 and the fourth fin pattern 410 may protrude from the substrate 100 (e.g., in a sixth direction Z2, which is perpendicular to a fourth direction X2 and a fifth direction Y2). Each of the third fin pattern 310 and the 50 fourth fin pattern 410 may extend lengthwise in the fourth direction X2. For example, the third fin pattern 310 and the fourth fin pattern 410 may have long sidewalls 310a and 410a, respectively, extending in the fourth direction X2, and short sidewalls 310b and 410b, respectively, extending in the 55 fifth direction Y2. The fourth direction X2 and the fifth direction Y2 may be perpendicular to each other and may be parallel to the upper surface of the substrate 100. In some embodiments, the first direction X1, the second direction Y1, and the third direction Z1 may be the same directions as 60 the fourth direction X2, the fifth direction Y2, and the sixth direction Z2, respectively. In other embodiments, the first direction X1, the second direction Y1, and the third direction Z1 may be different from the fourth direction X2, the fifth direction Y2, and the sixth direction Z2, respectively. 65

The third fin pattern 310 and the fourth fin pattern 410 may be arranged in the fourth direction X2 that is a length direction thereof. The third fin pattern 310 may be spaced apart from the fourth fin pattern 410 in the fourth direction X2. For example, the third fin pattern 310 and the fourth fin pattern 410 may be arranged in a row in the fourth direction X2. Upper surfaces of the third fin pattern 310 and the fourth fin pattern 410 may be coplanar with one another.

The short sidewall 310b of the third fin pattern 310 may face the short sidewall 410b of the fourth fin pattern 410. The third fin pattern **310** and the fourth fin pattern **410** may be separated by a second fin-cut trench 107t. The short sidewall 310b of the third fin pattern 310 and the short sidewall 410b of the fourth fin pattern 410 may be defined by the second fin-cut trench 107t.

Each of the third fin pattern **310** and the fourth fin pattern 410 may be formed by etching a portion of the substrate 100 or may include an epitaxial layer grown from the substrate 100. Each of the third fin pattern 310 and the fourth fin pattern 410 may include a semiconductor material, for example, silicon (Si) or germanium (Ge). In some embodiments, each of the third fin pattern 310 and the fourth fin pattern 410 may include a compound semiconductor, for example, a group IV-IV compound semiconductor or a group III-V compound semiconductor.

The third fin pattern 310 and the fourth fin pattern 410 of the third fin pattern 310 and the fourth fin pattern 410 may be a silicon fin pattern including silicon.

The second fin liner 311 may extend along at least a portion of a sidewall and a bottom surface of the second 30 fin-cut trench 107t. In some embodiments, the second fin liner 311 may be disposed on the whole sidewall of the second fin-cut trench 107t.