| UK Patent Appli                                                                                                                                                                                 |                         | (43) Date of A Publication                                                                                       |                            |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| (21) Application No:<br>(22) Date of Filing:                                                                                                                                                    | 1817759.2<br>31.10.2018 | (51) INT CL:<br><i>G06F 7/02</i> (2006.01)<br>(56) Documents Cited:                                              | <b>G06F 7/24</b> (2006.01) |  |  |  |

| (71) Applicant(s):<br>Imagination Technologies Limited<br>(Incorporated in the United Kingdom)<br>Imagination House, Home Park Estate,<br>KINGS LANGLEY, Hertfordshire, WD4 a<br>United Kingdom |                         | US 20130007419 A US 20080288565 A<br>(58) Field of Search:<br>INT CL G06F<br>Other: EPODOC, WPI, Patent Fulltext |                            |  |  |  |

| (72) Inventor(s):<br>Thomas Michael Rose                                                                                                                                                        |                         |                                                                                                                  |                            |  |  |  |

| (74) Agent and/or Address for Service:<br>CMS Cameron McKenna Nabarro Olsw<br>Cannon Place, 78 Cannon Street, Lond<br>United Kingdom                                                            | •                       |                                                                                                                  |                            |  |  |  |

- (54) Title of the Invention: Selecting an ith largest or a pth smallest number from a set of n m-bit numbers. Abstract Title: Method of selecting the ith largest or pth smallest number form a set of n numbers.

- <sup>(57)</sup> A method of hardware logic selecting the i<sup>th</sup> largest or the p<sup>th</sup> smallest number from a set of n m-bit numbers is described. The method is performed iteratively and in the rth iteration, of the method, each of the  $(m-r)^{th}$  bits from the m-bit numbers is summed to generate a summation result, the result is then compared to a threshold value. Depending upon the outcome of the comparison, the  $r^{^{th}}$ bit of the selected number is determined and the (m-r-1)<sup>th</sup> bit of each of the m-bit numbers is selectively updated based on the outcome of the comparison and the value of the (m-r)<sup>th</sup> bit in the m-bit number. In the first iteration, the most significant bit from each of the m-bit numbers is summed and each subsequent iteration sums bits occupying successive bit positions in the numbers. Finally data indicative of the selected number is output, which may be the number or the position within the n numbers of the selected number. The updating may be done by setting a flag for each m-bit number to one or zero, the flag is then used to change or not change the relevant bit in the associated m-bit number.

1 of 13

200

FIG. 2

FIG. 3D

2

FIG. 3F

<u>П</u> С. 3 Ш

INPUT

тах

mìn

×

$\circ$

$\circ$

**4**----

0

0

0

*Acces*

$\circ$

~~~

**19**1111

$\circ$

$\circ$

$\circ$

Kun

s...

$\circ$

\*\*\*\*

$\circ$

FIG. 5

FIG. 9

|                                                                                                                                                                                                                                                         |  | 0 | 0 | 0 | 0        | 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|---|---|----------|---|

| 0                                                                                                                                                                                                                                                       |  | 0 | 0 | 0 | 0        | 0 |

|                                                                                                                                                                                                                                                         |  | 0 | 0 | 0 | <i>4</i> | o |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, _, |  |   |   |   |          |   |

| 80%          |      |   |   |   |   |  |

|--------------|------|---|---|---|---|--|

| ∞ ∕ <b>*</b> |      | 0 | 0 | o | ò |  |

|              | 0    | 0 | 0 | 0 | 0 |  |

| 1            | free | 0 | 0 | đ | 0 |  |

k

8 Ю. 8

FIG. 11B

FIG. 11C

# l

# SELECTING AN I<sup>TH</sup> LARGEST OR A P<sup>TH</sup> SMALLEST NUMBER FROM A SET OF N M-BIT NUMBERS

### Background

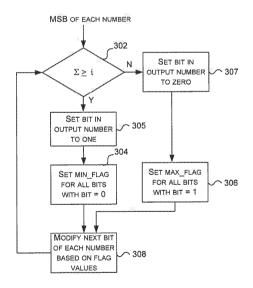

[0001] There are many situations where hardware is required to sort two or more input binary numbers, i.e. to arrange them in order of size. Such sorters are typically constructed from a number of identical logic blocks as shown in FIG. 1. FIG. 1 shows a schematic diagram of an example hardware arrangement 100 for sorting 4 inputs,  $x_1, x_2, x_3, x_4$  into size order, i.e. such that  $output_1 \ge output_2 \ge output_3 \ge output_4$ . It can be seen that this sorter 100 comprises 5 identical logic blocks 102 each of which outputs the largest and smallest (i.e. max and min) values of two inputs (which may be denoted *a* and *b*).

[0002] Each of the logic blocks 102 receives two n-bit integer inputs (a, b) and comprises a comparator that returns a Boolean that indicates whether a > b. The output of the comparator, which may be referred to as the 'select' signal, is then used to control a plurality of n-bit wide multiplexers that each choose between n-bits from a or n-bits from b. If the logic block 102 outputs both the maximum and minimum values (from a and b, as shown in the examples in FIG. 1), the select signal is used to control the multiplexing of 2n-bits (e.g. in the form of 2n 1-bit wide multiplexers or two n-bit wide multiplexers). Alternatively, if the logic block has only one output (which is either the maximum or minimum of a and b), the select signal is used to control the form of a and b), the select signal is used to control multiplexers). Alternatively, if the logic block has only one output (which is either the maximum or minimum of a and b), the select signal is used to control multiplexers). Alternatively, if the logic block has only one output (which is either the maximum or minimum of a and b), the select signal is used to control the multiplexers or one n-bit wide multiplexers or one n-bit wide multiplexers or one n-bit wide multiplexers.

[0003] In the arrangement described above, the select signal is used to power a plurality of logic elements (e.g. logic gates) within a logic block 102 and this results in a large propagation delay. This effect of a delay is caused by a single gate output wire having to charge the transistors in a large number of gates (before these latter gates can propagate their outputs) and may be referred to as 'fanout'. Whilst this delay may be acceptable when only sorting two input numbers, where these logic blocks 102 are concatenated (e.g. as in the sorter 100 shown in FIG. 1 or larger sorters for more than 4 inputs) the resulting delay of the sorting circuit increases which may seriously impact performance (e.g. it may result in the sorting process taking more than a single clock cycle).

[0004] A solution to this delay is to include a large number of buffers (e.g. at least n buffers, which may be arranged in a tree structure) with each of the buffers being driven by the select signal; however, this results in a hardware arrangement that is significantly larger (e.g. in terms of area of logic).

[0005] The embodiments described below are provided by way of example only and are not limiting of implementations which solve any or all of the disadvantages of known hardware and methods for sorting numbers and/or selecting a number from a set of numbers based on its ordered position in the set.

#### Summary

[0006] This Summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This Summary is not intended to identify key features or essential features of the claimed subject matter, nor is it intended to be used to limit the scope of the claimed subject matter.

[0007] A method of selecting, in hardware logic, an i<sup>th</sup> largest or a p<sup>th</sup> smallest number from a set of n m-bit numbers is described. The method is performed iteratively and in the r<sup>th</sup> iteration, where r is between 1 and m, the method comprises: summing the  $(m-r)^{th}$  bit, where the  $(m-1)^{th}$  bit is the most significant bit, from each of the m-bit numbers to generate a summation result and comparing the summation result to a threshold value. Depending upon the outcome of the comparison, the  $(m-r)^{th}$  bit of the selected number is determined and output and additionally the  $(m-r-1)^{th}$  bit of each of the m-bit numbers is selectively updated based on the outcome of the comparison and the value of the  $(m-r)^{th}$  bit in the m-bit number. In a first iteration, r=1 and the most significant bit from each of the m-bit numbers is summed and the most significant bit of the selected number is output. Each subsequent iteration sums the most significant bits of the numbers yet to be summed, which are the bits occupying successive bit positions in their respective numbers (for r=2 bits in position m-2, for r=3 bits in position m-3, etc.) and outputs the next bit of the selected number. There are examples of this method which also output the index of the i<sup>th</sup> largest or a p<sup>th</sup> smallest number.

[0008] A first aspect provides a method of selecting, in hardware logic, a number from a set of n m-bit numbers, wherein the selected number is either an i<sup>th</sup> largest or a p<sup>th</sup> smallest number from the set of n m-bit numbers, where i, p, m and n are integers, the method comprising a plurality of iterations and each of the iterations comprising: summing a bit from each of the m-bit numbers to generate a summation result, wherein all the bits being summed occupy an identical bit position within their respective number; comparing the summation result to a threshold value, wherein the threshold value is calculated based on i or p; setting, based on an outcome of the comparison, a bit of the selected number; and for each of the m-bit numbers, based on the outcome of the comparison and a value of the bit from the m-bit number, selectively updating a bit in the m-bit number occupying a next bit position, wherein in a first iteration, a most significant bit from each of the m-bit numbers is summed and a most significant bit of the selected numbers and sets a next bit of the selected number, and wherein the method comprises outputting data indicative of the selected number.

[0009] Outputting data indicative of the selected number may comprise either: outputting the selected number; or outputting an indication of the position, within the n m-bit numbers, of the selected number.

[0010] Setting, based on an outcome of the comparison, a bit of the selected number may comprise: in response to determining that the summation result exceeds the threshold value, setting the bit of the selected number to one; and in response to determining that the summation result is less than the threshold value, setting the bit of the selected number to zero.

[0011] In a r<sup>th</sup> iteration, summing a bit from each of the m-bit numbers to generate a summation result, may comprise summing a bit having a bit index m-r from each of the m-bit numbers to generate a summation result, wherein each bit is either an original bit from one of the m-bit numbers or an updated bit from a previous iteration.

[0012] The selected number may be the i<sup>th</sup> largest number from the set of n m-bit numbers and the threshold value may be equal to i. In other examples, the selected number may be the p<sup>th</sup> smallest number from the set of n m-bit numbers and the threshold value is equal to (n-p) or (n-p+1).

[0013] Selectively updating a bit in the m-bit number occupying a next bit position based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: selectively setting a flag associated with the m-bit number based on the outcome of the comparison and a value of the bit from the m-bit number; and selectively updating a bit in the m-bit number occupying a next bit position based on values of one or more flags associated with the m-bit number.

[0014] Selectively setting a flag associated with the m-bit number based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, setting a min flag associated with the m-bit number; and in response to determining that the summation result is less than the threshold value and that the value of the bit is one, setting a max flag associated with the m-bit number, and wherein selectively updating a bit in the m-bit number occupying a next bit position based on values of one or more flags associated with the m-bit number is set, setting the bit in the m-bit number occupying the next bit position to one; in response to determining that the min flag associated with the m-bit number is set, setting the bit in the min flag associated with the m-bit number is set, setting the bit in the min flag associated with the m-bit number is set, setting the bit in the min flag associated with the min minimum that the min flag associated with the minimum that neither the max flag nor the min flag associated with the minimum that number is set, leaving the bit in the minimum that number is set, leaving the bit in the minimum that neither the max flag nor the min flag associated with the minimum that number is set, leaving the bit in the minimum that number is set.

[0015] Selectively setting a flag associated with the m-bit number based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, setting a particular flag associated with the m-bit number; and in response to determining that the summation result is less than the threshold value and that the value of the bit is one, setting the particular flag associated with the m-bit number and updating the threshold value by an amount equal to the summation result, and wherein selectively updating a bit in the m-bit number occupying a next bit position based on values of one or more flags associated with the m-bit number to a predefined value; and in response to determining that the particular flag associated with the m-bit position to a predefined value; and in response to determining that the particular flag associated flag associated with the m-bit number is not set, leaving the bit in the m-bit number occupying the next bit position unchanged. The predefined value may be zero.

[0016] Selectively setting a flag associated with the m-bit number based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, setting a particular flag associated with the m-bit number and updating the threshold value by an amount equal to n minus the summation result; and in response to determining that the summation result is less than the threshold value and that the value of the bit is one, setting the particular flag associated with the m-bit number, and wherein selectively updating a bit in the m-bit number occupying a next bit position based on values of one or more flags associated with the m-bit number comprises: in response to determining that the particular flag is set, setting the bit in the m-bit number occupying the next bit position to a predefined value; and in response to determining that the particular flag associated with the particular flag associated with the m-bit number occupying the next bit position to a predefined value; and in response to determining that the particular flag associated with the m-bit number occupying the next bit position to a predefined value; and in response to determining that the particular flag associated with the m-bit number is not set,

leaving the bit in the m-bit number occupying the next bit position unchanged. The predefined value may be one.

[0017] The method may further comprise: determining how many of the m-bit numbers have an associated flag that is set; and in response to determining that n-1 of the m-bit numbers have an associated flag set, outputting data indicative of the m-bit number without an associated flag set.

[0018] Selectively updating a bit in the m-bit number occupying a next bit position based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, updating all bits in the m-bit number to zero; and in response to determining that the summation result does not exceed the threshold value and that the value of the bit is one, updating all bits in the m-bit number to one.

[0019] Selectively updating a bit in the m-bit number occupying a next bit position based on the outcome of the comparison and a value of the bit from the m-bit number may comprise: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, updating all bits in the m-bit number to zero; and in response to determining that the summation result does not exceed the threshold value and that the value of the bit is one, updating all bits in the m-bit number to zero; and that the value of the bit is one, updating all bits in the m-bit number to zero and reducing the threshold value by an amount equal to the summation result.

[0020] The method may comprise m iterations and in the m<sup>th</sup> iteration, a least significant bit from each of the m-bit numbers is summed and a least significant bit of the selected number is set.

[0021] A second aspect provides a hardware logic unit arranged to select an i<sup>th</sup> largest or p<sup>th</sup> smallest number from a set of n m-bit numbers, where i, p, m and n are integers, the hardware logic unit being arranged to operate iteratively and comprising: summation logic arranged to, in each iteration, sum a bit from each of the m-bit numbers to generate a summation result, wherein all the bits being summed occupy an identical bit position within their respective number such that in a first iteration, a most significant bit from each of the m-bit numbers is summed and each subsequent iteration sums bits occupying successive bit positions in their respective numbers; comparison logic arranged to, in each iteration, compare the summation result generated by the summation logic in that iteration to a threshold value and set a bit of the selected number based on an outcome of the comparison, wherein the threshold value is calculated based on i or p; updating logic arranged to, in each iteration and for each of the m-bit numbers, selectively update a bit in the m-bit number occupying a next bit position based on the outcome of the comparison and a value of the bit from the m-bit number; and an output arranged to output data indicative of the selected number.

[0022] The hardware logic unit may further comprise: flag control logic arranged to selectively set a flag associated with the m-bit number based on the outcome of the comparison and a value of the bit from the m-bit number; and wherein the updating logic is arranged to selectively update a bit in the m-bit number occupying a next bit position based on values of one or more flags associated with the m-bit number.

[0023] The flag control logic may comprise: a min flag logic block arranged to, in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, set a min flag associated with the m-bit number; and a max flag logic block arranged to, in response to determining that the summation result is less than the threshold value and that the value of the bit is one, set a max flag associated with the m-bit number, and wherein the updating logic is arranged to: in response to determining that the max flag associated with the m-bit number, and wherein the m-bit number is set, set the bit in the m-bit number occupying the next bit position to one; in response to determining that the min flag associated with the m-bit number is set, set the bit in the m-bit position to zero; and in response to determining that neither the max flag nor the min flag associated with the m-bit number is set, leave the bit in the m-bit number occupying the next bit position to zero; and in response to determining that min flag associated with the m-bit number is set, leave the bit in the m-bit number occupying the next bit position to zero; and in response to determining that min flag associated with the m-bit number is set, leave the bit in the m-bit number occupying the next bit position to zero; and in response to determining that neither the max flag nor the min flag associated with the m-bit number is set, leave the bit in the m-bit number occupying the next bit position unchanged.

[0024] The flag control logic may be arranged to: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, set a particular flag associated with the m-bit number; and in response to determining that the summation result is less than the threshold value and that the value of the bit is one, set the particular flag associated with the m-bit number and updating the threshold value by an amount equal to the summation result, and wherein the updating logic is arranged to: in response to determining that the particular flag is set, set the bit in the m-bit number occupying the next bit position to a predefined value; and in response to determining that the particular flag is not set, leave the bit in the m-bit number occupying the next bit position unchanged. The predefined value may be zero.

[0025] The flag control logic may be arranged to: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, set a particular flag associated with the m-bit number and updating the threshold value by an amount equal to n minus the summation result; and in response to determining that the summation result is less than the threshold value and that the value of the bit is one, set the particular flag associated with the m-bit number, and wherein the updating logic is arranged to: in response to determining that the particular flag is set, set the bit in the m-bit number occupying the next bit position to a predefined value; and in response to determining that the particular flag is not set, leave the bit in the m-bit number occupying the next bit position unchanged. The predefined value may be one.

[0026] The hardware logic unit may further comprise: an early exit hardware logic block arranged to determine how many of the m-bit numbers have an associated flag that is set; and in response to determining that n-1 of the m-bit numbers have an associated flag set, to output the m-bit number without an associated flag set as the selected number.

[0027] The updating logic may be arranged to: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, update all bits in the mbit number to zero; and in response to determining that the summation result does not exceed the threshold value and that the value of the bit is one, update all bits in the m-bit number to one.

[0028] The updating logic may be arranged to: in response to determining that the summation result exceeds the threshold value and that the value of the bit is zero, update all bits in the mbit number to zero; and in response to determining that the summation result does not exceed the threshold value and that the value of the bit is one, update all bits in the m-bit number to zero and reduce the threshold value by an amount equal to the summation result.

[0029] A third aspect provides a hardware logic unit configured to perform the method described above.

[0030] A fourth aspect provides a method of manufacturing, using an integrated circuit manufacturing system, a hardware logic unit as detailed above.

[0031] A fifth aspect provides an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the integrated circuit manufacturing system to manufacture a hardware logic unit as detailed above.

[0032] A sixth aspect provides a computer readable storage medium having stored thereon a computer readable description of an integrated circuit that, when processed in an integrated circuit manufacturing system, causes the integrated circuit manufacturing system to manufacture a hardware logic unit as detailed above.

[0033] A seventh aspect provides an integrated circuit manufacturing system comprising: a computer readable storage medium having stored thereon a computer readable description of an integrated circuit that describes a hardware logic unit as detailed above; a layout processing system configured to process the integrated circuit description so as to generate a circuit layout description of an integrated circuit embodying the hardware logic unit; and an integrated circuit generation system configured to manufacture the hardware logic unit according to the circuit layout description.

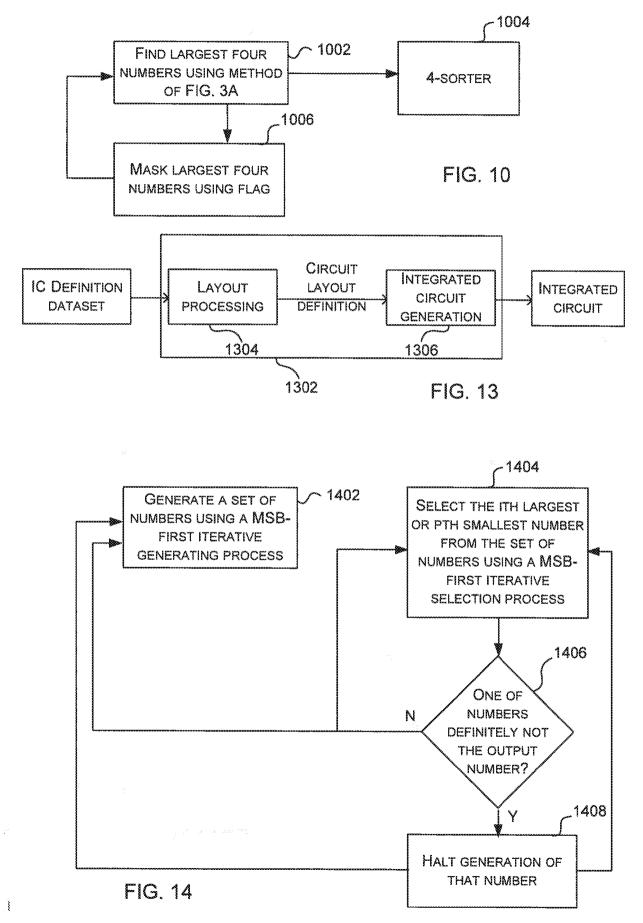

[0034] An eighth aspect provides a method, implemented in hardware logic, for generating and selecting a number, the method comprising: performing a MSB-first (most significant bit first) iterative generating process for generating a set of n numbers; concurrently with performing the MSB-first iterative generating process for generating the set of n numbers, performing a MSB-first iterative selection process to select either an i<sup>th</sup> largest or a p<sup>th</sup> smallest number from the set of n numbers, where i, p and n are integers; and in response to the MSB-first iterative selection process determining that a particular one of the numbers of said set of n numbers will not be the selected number, halting the generation of said particular number by said MSB-first iterative generated and before all of the bits of said particular number have been generated, wherein the method comprises outputting data indicative of the selected number.

[0035] The MSB-first iterative generating process may be a CORDIC (Coordinate Rotation Digital Computer) process or an Online Arithmetic process.

[0036] Performing the MSB-first iterative selection process may comprise performing a plurality of iterations, wherein each of the iterations may comprise: summing a bit from each of the numbers of the set to generate a summation result, wherein all the bits being summed occupy an identical bit position within their respective number; comparing the summation result to a threshold value, wherein the threshold value is calculated based on i or p; setting, based on an outcome of the comparison, a bit of the selected number; and for each of the numbers of the set, based on the outcome of the comparison and a value of the bit from the number, selectively updating a bit in the number occupying a next bit position. In a first iteration, a most significant bit from each of the numbers of the set may be summed and a most significant bit of the selected number may be set and each subsequent iteration sums bits occupying successive bit positions in their respective numbers and sets a next bit of the selected number.

[0037] The selected number may be the i<sup>th</sup> largest number from the set of n numbers and the threshold value is equal to i. In other examples, the selected number may be the p<sup>th</sup> smallest number from the set of n numbers and the threshold value is equal to (n-p) or (n-p+1).

[0038] Each of the n numbers of the set, if fully generated, may be m-bit numbers.

[0039] Outputting data indicative of the selected number may comprise either: outputting the selected number; or outputting an indication of the position, within the set of n numbers, of the selected number.

[0040] A ninth aspect provides a processing unit configured to generate and select a number, the processing unit comprising: a generation logic unit, implemented in hardware, configured to perform a MSB-first iterative generating process for generating a set of n numbers; a selection logic unit, implemented in hardware, configured to operate concurrently with the generation logic unit, and configured to perform a MSB-first iterative selection process to select either an i<sup>th</sup> largest or a p<sup>th</sup> smallest number from the set of n numbers, where I, p and n are integers; and an output arranged to output data indicative of the selected number, wherein the processing unit is configured to, in response to the selection logic unit determining that a particular one of the numbers of said set of n numbers will not be the selected number, cause the generation logic unit to halt the generation of said particular number by said MSB-first iterative generating process after at least one of the bits of said particular number has been generated and before all of the bits of said particular number have been generated.

[0041] The selection logic may comprise: summation logic arranged to, in each iteration, sum a bit from each of the numbers to generate a summation result, wherein all the bits being summed occupy an identical bit position within their respective number; comparison logic arranged to, in each iteration, compare the summation result generated by the summation logic in that iteration to a threshold value and set a bit of the selected number based on an outcome of the comparison, wherein the threshold value is calculated based on i or p; and updating logic arranged to, in each iteration and for each of the numbers, selectively update a bit in the number occupying a next bit position based on the outcome of the comparison in that iteration and a value of the bit from the number. The summation logic may be arranged such that in a first iteration, a most significant bit from each of the numbers is summed and each subsequent iteration sums bits occupying successive bit positions in their respective numbers.

[0042] A tenth aspect provides a processing unit configured to perform the method for generating and selecting a number, as detailed above.

[0043] An eleventh aspect provides a method of manufacturing, using an integrated circuit manufacturing system, a processing unit as detailed above.

[0044] A twelfth aspect provides an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the integrated circuit manufacturing system to manufacture a processing unit as detailed above.

[0045] A thirteenth aspect provides a computer readable storage medium having stored thereon a computer readable description of an integrated circuit that, when processed in an integrated

circuit manufacturing system, causes the integrated circuit manufacturing system to manufacture a processing unit as detailed above.

[0046] A fourteenth aspect provides an integrated circuit manufacturing system comprising: a computer readable storage medium having stored thereon a computer readable description of an integrated circuit that describes a processing unit as detailed above; a layout processing system configured to process the integrated circuit description so as to generate a circuit layout description of an integrated circuit embodying the processing unit; and an integrated circuit generation system configured to manufacture the processing unit according to the circuit layout description.

[0047] The number sorting hardware logic unit and/or processor comprising hardware logic configured to perform one of the methods as described herein may be embodied in hardware on an integrated circuit. There may be provided a method of manufacturing, at an integrated circuit manufacturing system, a number sorting hardware logic unit and/or a processor comprising hardware logic configured to perform one of the methods as described herein. There may be provided an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the system to manufacture an number sorting hardware logic unit and/or a processor comprising hardware logic configured to perform one of the methods as described herein. There may be provided a non-transitory computer readable storage medium having stored thereon a computer readable description of an integrated circuit that, when processed, causes a layout processing system to generate a circuit layout description used in an integrated circuit manufacturing system to manufacture a number sorting hardware logic unit and/or a processor comprising hardware logic configured to perform one of the methods as described herein. There may be provided a non-transitory computer readable storage medium having stored thereon a computer readable description of an integrated circuit that, when processed, causes a layout processing system to generate a circuit layout description used in an integrated circuit manufacturing system to manufacture a number sorting hardware logic unit and/or a processor comprising hardware logic configured to perform one of the methods as described herein.

[0048] There may be provided an integrated circuit manufacturing system comprising: a nontransitory computer readable storage medium having stored thereon a computer readable integrated circuit description that describes the number sorting hardware logic unit and/or processor comprising hardware logic configured to perform one of the methods as described herein; a layout processing system configured to process the integrated circuit description so as to generate a circuit layout description of an integrated circuit embodying the number sorting hardware logic unit and/or processor comprising hardware logic configured to perform one of the methods as described herein; and an integrated circuit generation system configured to manufacture the number sorting hardware logic unit and/or processor comprising hardware logic configured to perform one of the methods as described herein according to the circuit layout description.

[0049] There may be provided computer program code for performing any of the methods described herein. There may be provided non-transitory computer readable storage medium having stored thereon computer readable instructions that, when executed at a computer system, cause the computer system to perform any of the methods described herein.

[0050] The above features may be combined as appropriate, as would be apparent to a skilled person, and may be combined with any of the aspects of the examples described herein.

9

## **Brief Description of the Drawings**

[0051] Examples will now be described in detail with reference to the accompanying drawings in which:

[0052] FIG. 1 is a schematic diagram of an example hardware arrangement for sorting 4 inputs;

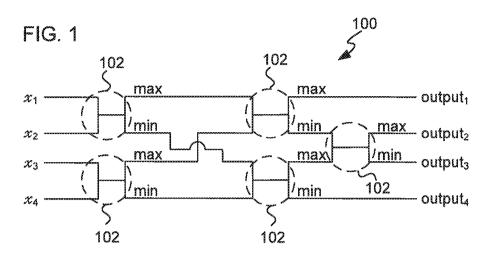

[0053] FIG. 2 shows a graphical representation of the set of n m-bit numbers which are input to the methods and hardware described herein;

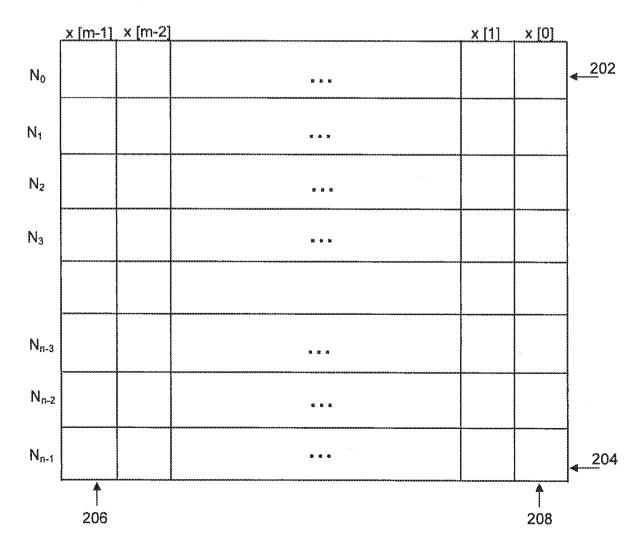

[0054] FIG. 3A is a flow diagram showing a first example method of calculating the i<sup>th</sup> largest number from the input set of n m-bit numbers;

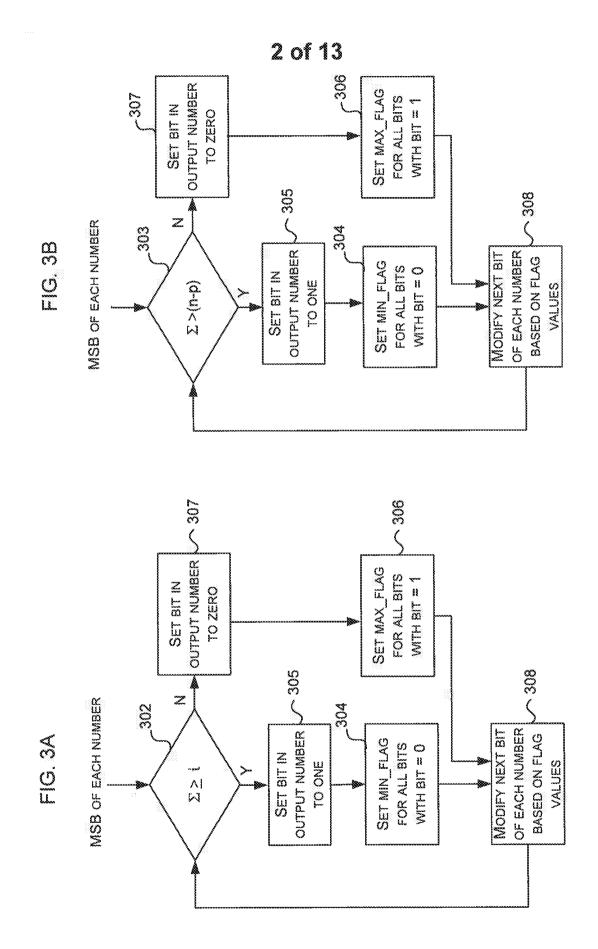

[0055] FIG. 3B is a flow diagram showing a first example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers;

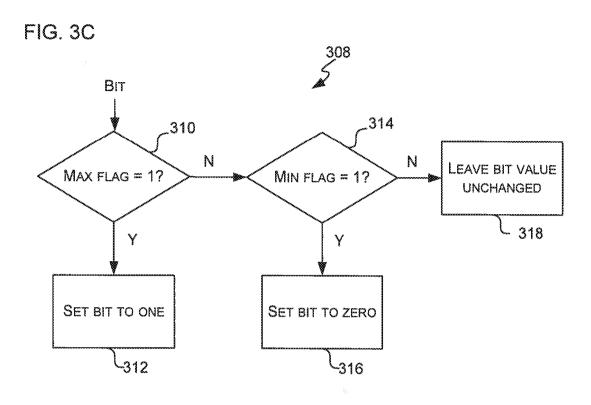

[0056] FIG. 3C is a flow diagram showing an operation from the methods of FIGs. 3A and 3B in more detail;

[0057] FIG. 3D is a circuit diagram of an example hardware implementation of the operation shown in FIG. 3C;

[0058] FIG. 3E shows a truth table for the hardware arrangement shown in FIG. 3D;

[0059] FIG. 3F shows a schematic diagram of an example hardware arrangement that implements an operation in the method of FIG. 3A;

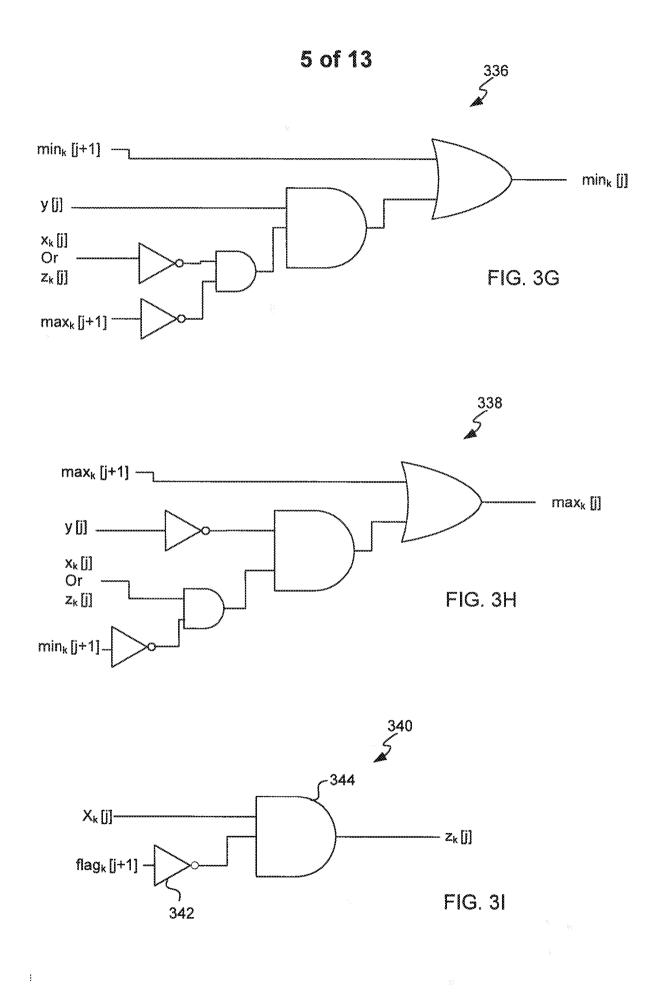

[0060] FIG. 3G and 3H show schematic diagrams of two different example hardware arrangements that implements an operation in the methods of FIGs. 3A and 3B;

[0061] FIG. 3I shows a schematic diagram of an example hardware arrangement that implements an operation in the method of FIG. 9;

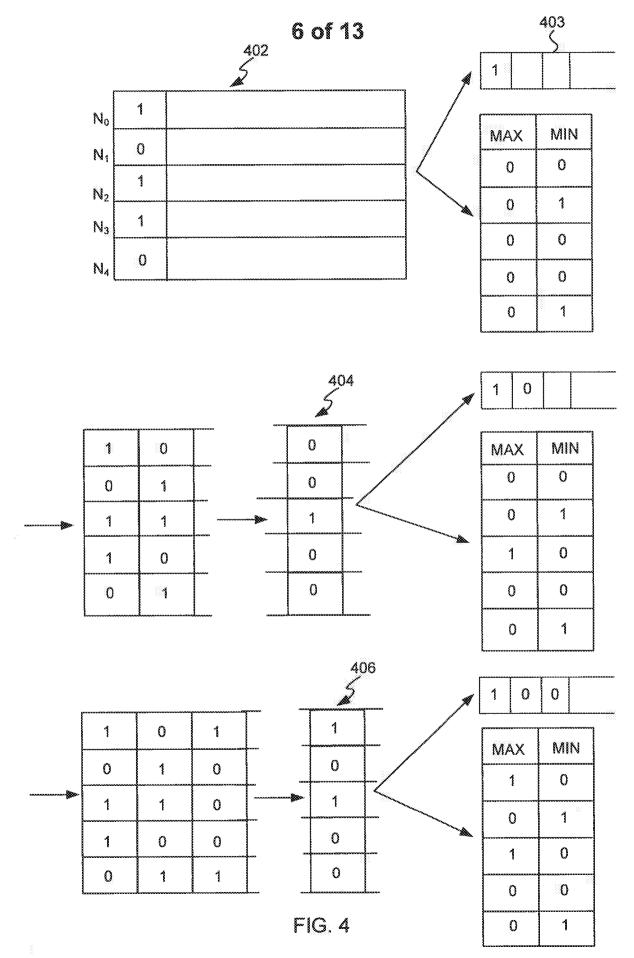

[0062] FIG. 4 illustrates an example of the operation of the method of FIG. 3A;

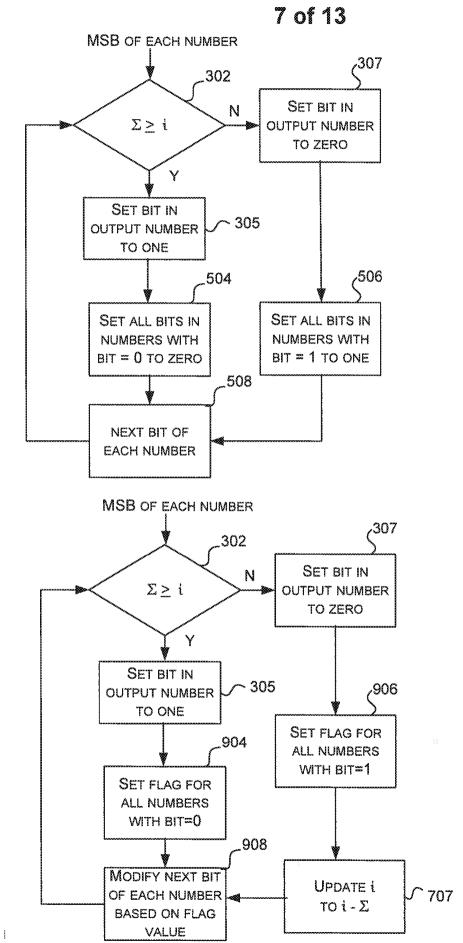

[0063] FIG. 5 is a flow diagram showing a second example method of calculating the i<sup>th</sup> largest number from the input set of n m-bit numbers;

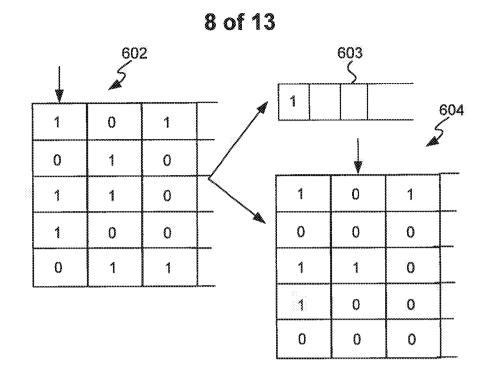

[0064] FIG. 6 illustrates an example of the operation of the method of FIG. 5;

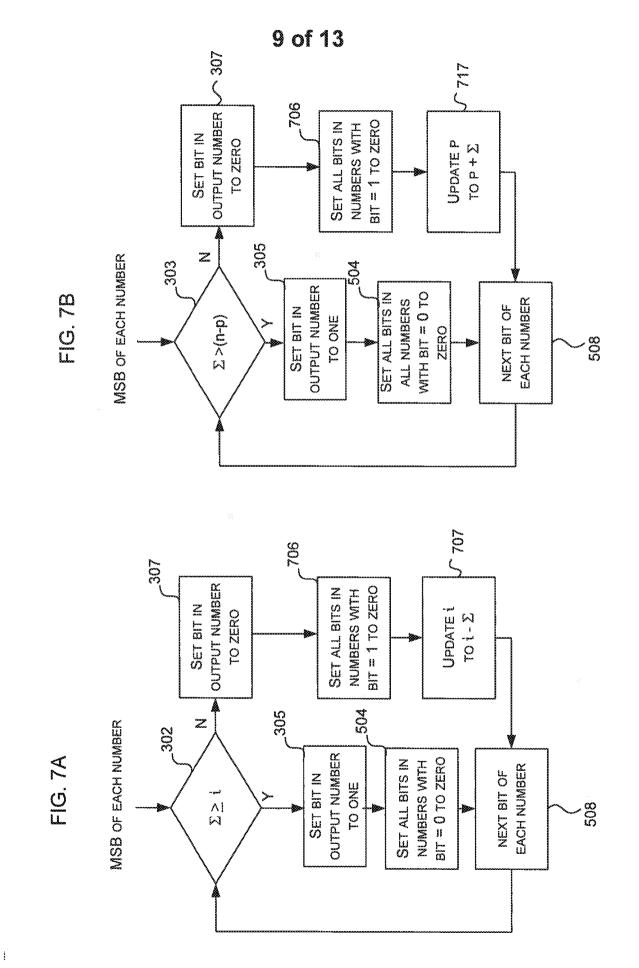

[0065] FIG. 7A is a flow diagram showing a third example method of calculating the i<sup>th</sup> largest number from the input set of n m-bit numbers;

[0066] FIG. 7B is a flow diagram showing a further example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers;

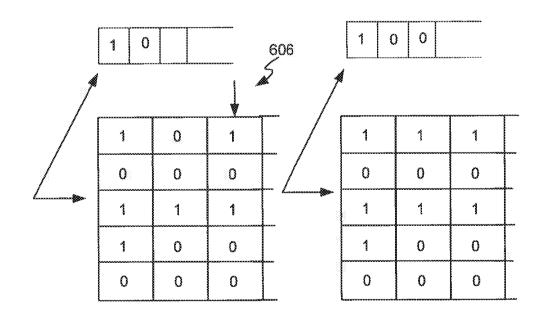

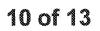

[0067] FIG. 8 illustrates an example of the operation of the method of FIG. 7A;

[0068] FIG. 9 is a flow diagram showing a fourth example method of calculating the i<sup>th</sup> largest number from the input set of n m-bit numbers;

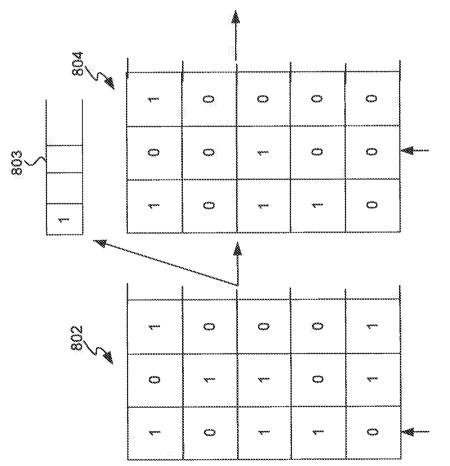

[0069] FIG. 10 is a schematic diagram showing the use of the method of FIG. 3A to perform sorting;

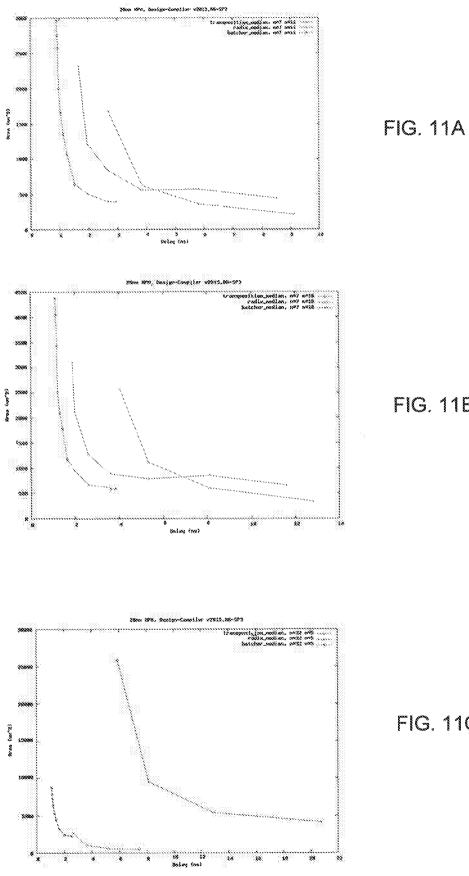

[0070] FIGs. 11A, 11B and 11C are graphs showing synthesis results for the methods described herein;

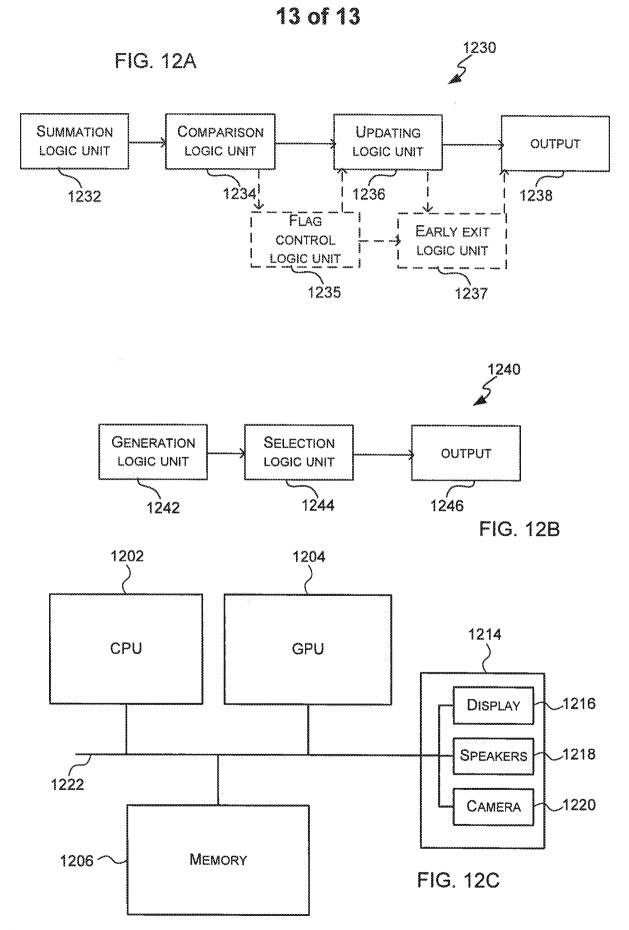

[0071] FIG. 12A is a schematic diagram of a hardware logic unit arranged to select the i<sup>th</sup> largest number or the p<sup>th</sup> smallest number from an input set of n m-bit numbers;

[0072] FIG. 12B is a schematic diagram of a processing unit arranged to generate and select a number;

[0073] FIG. 12C shows a computer system in which a graphics processing system is implemented;

[0074] FIG. 13 shows an integrated circuit manufacturing system for generating an integrated circuit embodying a graphics processing system; and

[0075] FIG. 14 is a flow diagram of an example method of generating and selecting a number from a set of n numbers that are generated iteratively, starting with the MSB.

[0076] The accompanying drawings illustrate various examples. The skilled person will appreciate that the illustrated element boundaries (e.g., boxes, groups of boxes, or other shapes) in the drawings represent one example of the boundaries. It may be that in some examples, one element may be designed as multiple elements or that multiple elements may be designed as one element. Common reference numerals are used throughout the figures, where appropriate, to indicate similar features.

## **Detailed Description**

[0077] The following description is presented by way of example to enable a person skilled in the art to make and use the invention. The present invention is not limited to the embodiments described herein and various modifications to the disclosed embodiments will be apparent to those skilled in the art.

[0078] Embodiments will now be described by way of example only.

[0079] There are many applications where it is useful to select the i<sup>th</sup> largest or p<sup>th</sup> smallest integer from a set of integers. Typically this is implemented using a sorting algorithm, or sorting network (e.g. as described above with reference to FIG. 1) to sort the integers into an ordered list and then the relevant integer from the list can be output. However, the size of the resulting hardware can be large, even if redundant logic (which doesn't affect the required output) is removed as part of the synthesis of the hardware.

[0080] Described herein is a method and hardware for selecting the i<sup>th</sup> largest or p<sup>th</sup> smallest number from a set of n m-bit numbers without first sorting the set of numbers. Using the methods described herein, the hardware is smaller than a sorting network, e.g. it scales in area as  $O(n^*m)$  rather than  $O(m^*n^*(ln(n)^2))$ . Furthermore, as the method is iterative, the area of the hardware used to implement the method can be made even smaller by trading performance / throughput (e.g. by synthesizing only one iteration or less than m iterations and then reusing the hardware logic over multiple cycles). Additionally, the method enables performance / throughput to be increased at a cost of additional area (e.g. by increasing the number of bits that are assessed in each iteration above 1).

[0081] The methods described herein may be adapted to apply to numbers represented in signed or unsigned fixed point format, floating point format and signed or unsigned normalised format. For example, for signed and floating point numbers, the top bit of each number is

negated on both input to the method and output from the method. For unsigned fixed point numbers, no changes are required to the methods. For normalised formats, the bit string is treated as a normal unsigned (or signed) number. In various examples, the numbers may be integers. In various examples, the numbers may be binary approximations of values with no finite binary representation in the standard fixed point format (e.g. 1/3 or the square root of 2), where the binary approximations are generated one bit at a time.

[0082] The method involves examining the most significant bit (MSB) from each of the numbers in the set and based on the outcome of the analysis setting one or more flags or mask bits. The method is then repeated, selecting the next bit from each of the numbers in the set, adjusting the bit values dependent upon the flags or mask bits and then performing the same analysis (or very similar analysis) as was performed on the MSB. As with the first iteration (that involved the MSBs), based on the outcome of the analysis, one or more flags or mask bits may be set. The method may iterate through each of the m bits in the numbers in order to determine which of the numbers is the i<sup>th</sup> largest or p<sup>th</sup> smallest number. In each iteration, a bit from the output number (i.e. the i<sup>th</sup> largest or p<sup>th</sup> smallest number) is set and the output from the method may be either the output number itself or other data that identifies (or indicates) the output number from within the set of n m-bit numbers (e.g. in the form of an index of the output number within the set of n numbers).

[0083] In describing the various embodiments and examples below, the following notation is used, which can be described with reference to FIG. 2:

- n is the number of numbers in the set 200,

- k is the number index and ranges between 0 and (n-1),

- $N_k$  are the numbers in the set 200, such that the first number 202 in the set 200 is  $N_0$  and the last number 204 in the set 200 is  $N_{n-1}$ .

- m is the number of bits in each of the numbers in the set and each number in the set comprises the same number of bits,

- j is the bit index and ranges between (m-1) for the MSB 206 and 0 for the least significant bit (LSB) 208 in each number, and in examples where the method analyses a single bit from each number in the set in each iteration (from the MSB to the LSB), j may also be referred to as the iteration index,

- r is the iteration number that ranges between one (for the first iteration, where j=m-1) and m (for the last iteration, where j=0), hence j=m-r in examples in which one bit position is considered per iteration.

- xk[j] refers to bit j of the number Nk, where j=m-1 for the MSB and j=0 for the LSB,

- z<sub>k</sub>[j] refers to the modified bit j of the number N<sub>k</sub>,

-- --------

- i and p are integers in the range 1 to n and the methods described herein identify the i<sup>th</sup> largest or p<sup>th</sup> smallest number from the set of numbers, and the desired number, i.e. the i<sup>th</sup> largest or p<sup>th</sup> smallest number, is referred to herein as the output number,

- min<sub>k</sub>[j] is the minimum flag (or min\_flag) for the number N<sub>k</sub> following analysis of the j<sup>th</sup> bit of the number N<sub>k</sub>,

- min<sub>k</sub>[m] is the initial (i.e. starting) value of the minimum flag for the number N<sub>k</sub>,

- max<sub>k</sub>[j] is the maximum flag (or max\_flag) for the number N<sub>k</sub> as set following analysis of the j<sup>th</sup> bit of the number N<sub>k</sub>,

- max<sub>k</sub>[m] is the initial (i.e. starting) value of the maximum flag for the number N<sub>k</sub>,

- flag<sub>k</sub>[j] is the flag for the number  $N_k$  as set following analysis of the j<sup>th</sup> bit of the number  $N_k$  in examples where a single flag is used, and

- flag<sub>k</sub>[m] is the initial (i.e. starting) value of the single flag for the number N<sub>k</sub>.

[0084] FIG. 2 shows a graphical representation of the set 200 of n m-bit numbers which are input to the methods and hardware described herein. The numbers within the set are not in any particular order and hence the value of k only identifies the position of the number in the set (and hence is used to refer to a particular number  $N_k$ ) and does not provide any information about the relative size of the number  $N_k$  compared to other numbers in the set 200.

[0085] The methods and hardware described herein may be used to find the i<sup>th</sup> largest or p<sup>th</sup> smallest number from the set 200 of n m-bit numbers without first sorting the set of numbers.

[0086] FIG. 3A is a flow diagram of a first example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers. In various examples the value of i is fixed and in other examples, the value of i is an input variable. As shown in FIG. 3A, the method is iterative and uses two flags per number: min\_flag and max\_flag (i.e. 2n flag bits in total). The minimum flag, min\_flag or min<sub>k</sub>[], when set indicates that the particular number is smaller than the output number (the i<sup>th</sup> largest number) and the maximum flag, max\_flag or max<sub>k</sub>[], when set indicates that the particular or max<sub>k</sub>[], when set indicates that the particular number is larger than the output number. Initially (when j=m), the flags may all be unset (e.g. set to zero) unless some pre-masking has been performed (as described below). As described below, the method builds up the output number, one bit per iteration.

[0087] In the first iteration (r=1, j=m-1) the MSBs 206 of each number are summed and if the sum of the MSBs is greater than or equal to i ('Yes' in block 302) then this means that the MSB of the i<sup>th</sup> largest number from the input set (i.e. the MSB of the output number) is a one and the MSB of the output number may be set to one (block 305). However, if the sum of the MSBs is less than i ('No' in block 302), then this means that the MSB of the i<sup>th</sup> largest number from the input set (i.e. the MSB of the output number may be set to zero (block 302), then this means that the MSB of the output number may be set to zero (block 307). Additionally, in response to determining that the sum of the MSBs is greater than or equal to i ('Yes' in block 302), the min\_flag is set for all those numbers with an MSB=0 (block 304) and in response to determining that the sum of the MSBs is not greater than or equal to i ('No' in block 302), the max\_flag is set for all those numbers with an MSB=1 (block 306).

[0088] The second iteration (r=2, j=m-2) starts by taking the next bit from each of the numbers and modifying the bits using the flag values (block 308). In particular, the value of the bits may be altered where either the min\_flag or the max\_flag is set for the number, as shown in FIG. 3C. If the max\_flag for the number is set ('Yes' in block 310), then the bit from that number (i.e. the second most significant bit from the number for the second iteration) is set to one (block 312) irrespective of whether the bit value is actually a one or a zero. Similarly, if the min\_flag for the number is set ('Yes' in block 314), then the bit is set to zero (block 316) irrespective of whether the bit value is actually a one or a zero. According to the methods described herein, a number cannot have both the max\_flag and the min\_flag set. If neither flag is set ('No' in blocks 310 and 314) then the value of the bit is left unchanged (block 318).

[0089] The alteration of the bits (in block 308, as shown in detail in FIG. 3C) can also be described by the following logic equation:

$$z_k[j] = x_k[j] \cdot \overline{min_k[j+1]} + max_k[j+1]$$

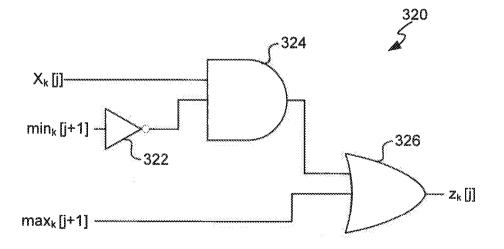

where · represents a logical AND operation and + represents a logical OR operation. The corresponding hardware arrangement 320, which may be replicated n-times (one for each number in the set 200) is shown in FIG. 3D and comprises a NOT gate 322, an AND gate 324 and an OR gate 326. As shown in FIG. 3D, the current bit is combined with an inverted version of the current minimum flag (as set in the previous iteration) in an AND gate 324 and then the output of the AND gate 324 is combined with the current maximum flag (as set in the previous iteration) in an OR gate 326. The truth table for the reachable states of the hardware arrangement 320 is shown in FIG. 3E.

[0090] The altered bits (as generated in block 308) are then summed and if the sum is greater than or equal to i ('Yes' in block 302) then this means that the next bit of the i<sup>th</sup> largest number from the input set (i.e. the next bit of the output number) is a one and the next bit of the output bit may be set to one (block 305); however, if the sum is less than i ('No' in block 302), then this means that the next bit of the i<sup>th</sup> largest number from the input set (i.e. the next bit of the output number) is a zero and the next bit of the output number may be set to zero (block 307). In this way the method builds the output number (in blocks 305 and 307), one bit at a time and one bit per iteration. In response to determining that the sum is greater than or equal to i ('Yes' in block 302), the min\_flag is set for all those numbers with an altered bit equal to i ('No' in block 302), the max\_flag is set for all those numbers with an altered bit equal to one (block 306).

[0091] The summing of the bits (in block 302) can also be described by the following logic equation:

$$sum_j = \sum_{k=0}^{n-1} z_k[j]$$

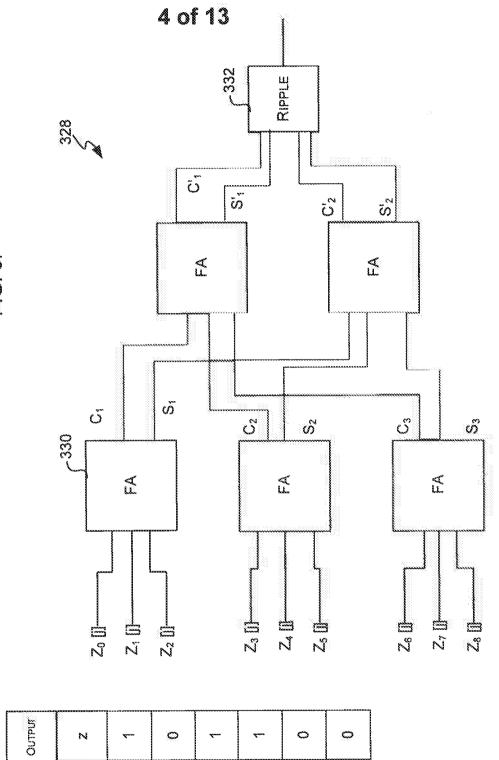

The corresponding hardware arrangement 328 comprises a plurality of adders (e.g. a plurality of full adders 330 which each add together three bits, i.e. for three different values of k, followed by one or more ripple carry adders 332). An example hardware arrangement is shown in FIG. 3F; however the summation may be implemented in hardware in other ways.

[0092] The updating of the minimum flag (in block 304) and maximum flag (in block 306) can also be described by the following logic equations:

$$y[j] = (sum_j \ge i)? 1:0$$

$$min_k[j] = min_k[j+1] + (y[j] \cdot \overline{x_k[j]} \cdot \overline{max_k[j+1]})$$

$$max_k[j] = max_k[j+1] + (\overline{y[j]} \cdot x_k[j] \cdot \overline{min_k[j+1]})$$

In these last two equations, the first terms refer to the flag values from the previous iteration and are used to ensure that the flag is not changed if it has already been set by an earlier bit within a number. The same two last equations may also be used when referring to the altered bits  $(z_k[j])$  by simply replacing  $x_k[j]$  by  $z_k[j]$ , as  $x_k[j] = z_k[j]$  when both flags are 0 and if either of the flags are 1 then the value of  $x_k[j]$  is irrelevant in the equations above, however the hardware implementation using the altered bits may be larger (in terms of area of hardware logic) than using the original bits. The corresponding hardware arrangements 336, 338 are shown in FIGs. 3G and 3H and comprise a combination of NOT, AND and OR gates (or other logic blocks which implement the same functionality as the NOT, AND and OR gates and which may be referred to as NOT, AND and OR logic blocks).

[0093] The method of FIG. 3A may then be repeated for all m bits in the input numbers to build up the output number or, in various examples, there may be additional logic that identifies when a result has been obtained before all m iterations are complete (i.e. when there is only one distinct value in the set of numbers 200 that has neither the max\_flag nor the min\_flag set) and outputs the result at that stage. In various examples, the additional logic may additionally, or instead, be used to limit the number of iterations that are performed (i.e. to provide a maximum value of r,  $r_{max}$ ) and then output the result at that stage. In such examples, only a part of the output number has been built up and so the remaining bits, or the entire output number, may be obtained by selecting one of the numbers from the set of input numbers based on the flag values, or alternatively, other data that identifies the output number (e.g. the number index, k) may be output. Although if the set of input numbers may include duplicate values (i.e. if it is not guaranteed that all the n numbers in the input set are unique), such that there may be more than one input number that is the i<sup>th</sup> largest number in the input set of n m-bit numbers, then this adds complexity to the additional logic and so the benefit of having the additional logic may be reduced or lost. This additional logic may be referred to as an early exit logic unit.

[0094] Performing a bitwise OR on the  $min_k[j]$  and  $max_k[j]$  signals and then negating the result yields a signal which has a 1 in the k<sup>th</sup> bit if, and only if, bits m-1 to j of the output number matches bits m-1 to j in the number  $N_k$ .

[0095] The method of FIG. 3A can be described with reference to the example shown in FIG. 4, where n=5 and i=3. In the first iteration 402, the MSBs of each number are summed and the result is 3. As the sum is equal to i ('Yes' in block 302), the MSB of the output number 403 is set to one (block 305) and the min\_flag is set for those numbers where the MSB is zero (block 304). In the example shown, the min\_flag is set for numbers N<sub>1</sub> and N<sub>4</sub>.

[0096] In the second iteration, the next bits in each of the 5 numbers are first modified based on the flag values (block 308) to get the  $z_k[m-2]$  values and in this example, as only the flags for numbers N<sub>1</sub> and N<sub>4</sub> are set, only these bits are modified from a one to a zero. The modified bits 404 are then summed and the result is 1. As the sum is less than i ('No' in block 302), the next bit of the output number is set to zero (block 307) and the max\_flag is set for those numbers where the modified bit is one (block 306). In the example shown, the max\_flag is set for number N<sub>2</sub>.

[0097] The third iteration again starts by modifying the next bits in each of the 5 numbers based on the flag values (block 308) to get the  $z_k[m-3]$  values and in this example, as the flags for numbers N<sub>1</sub>, N<sub>2</sub> and N<sub>4</sub> are set, only these bits are affected, although as shown in FIG. 4, whilst the values of the 3<sup>rd</sup> bits of numbers N<sub>2</sub> and N<sub>4</sub> are flipped (from a 0 to a 1 for number N<sub>2</sub> because of the max\_flag and from a 1 to a 0 for number N<sub>4</sub> because of the min\_flag) the 3<sup>rd</sup> bit of number N<sub>1</sub> is not modified as it is already a zero and it is the min\_flag that is set. As before the modified bits 406 are summed and in this case the result is 2. As the sum is less than i ('No' in block 302), the next bit of the output number is set to zero (block 307) and the max\_flag is set for those numbers where the modified bit is one (block 306). In the example shown, the max\_flag is set for number N<sub>0</sub>. At this point there is only one number, i.e. the i<sup>th</sup> largest number from the input set. The method may stop at this point (e.g. if logic is provided to assess the flags and determine when only one number does not have a flag set) or the method may continue until all bits have been assessed.

[0098] It can be appreciated that if m=8 in the example of FIG. 4 and the five input values (N<sub>0</sub>-N<sub>4</sub>) are 101xxxxx, 010xxxxx, 110xxxxx, 100xxxxx and 011xxxxx (where each x can represent either 0 or 1) then as shown in FIG. 4, the third largest number is determined to be 100xxxxx, and this can be determined just by analysing the first three bits of the inputs values in this example. As described above, following the third iteration, only the three most significant bits of the output number 403 (bits 100) have been built up and the remaining five bits may be determined either by continuing with the remaining five iterations of the method or by selecting N<sub>3</sub> based on the flag values and either adding the 5 LSBs to the already generated output number 403 or outputting N<sub>3</sub> and discarding the three bits that have already been built up. Alternatively, instead of outputting the output number itself, data identifying that output number (e.g. the index k=3) may be output.

[0099] Whilst FIG. 3A shows a first example method of calculating (or identifying) the ith largest number from the input set of n m-bit numbers, a very similar method may be used to calculate (or identify) the p<sup>th</sup> smallest number from the input set of n m-bit numbers and one example is shown in FIG. 3B. In the method of FIG. 3B, the only differences compared to the method of FIG. 3A, are that the summation is compared to the value of (n-p) and the comparison switches from 'greater than or equal' (in block 302 of FIG. 3A) to 'strictly greater than' (in block 303 of FIG. 3B). Alternatively, the comparison performed in block 303 of FIG. 3B may be whether the sum is greater than or equal to (n+1-p). If the sum of MSBs (or altered bits for subsequent iterations) is greater than (n-p) ('Yes' in block 303), the MSB of the output number is set to one (block 305) and the min\_flag is set for all those numbers with an MSB or altered bit equal to zero (block 304). If, however, the sum is not greater than (n-p) ('No' in block 303), the MSB of the output number is set to zero (block 307) and the max\_flag is set for all those numbers with an MSB or altered bit equal to one (block 306). As before, the method is then repeated for subsequent bits in each of the numbers in the input set to build up the output number. The method may terminate either after m iterations or, where the additional hardware is provided, in response to determining that there is only a single number in the input set that does not have any flags set.

[0100] In another example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers, all the input numbers N<sub>k</sub> may be bitwise inverted  $(N_k \rightarrow \overline{N_k})$  and then the method of FIG. 3A may be used with i=p, so long as the final output is inverted back to its original form prior to being output.

[0101] FIG. 5 is a flow diagram of a second example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers. Like the first method, as described above and shown in FIG. 3A, the second method is also iterative; however, it does not use flags. Instead, based on the result of the summation (in block 302), the values of the numbers themselves are updated (blocks 504 and 506). In response to determining that the sum of the MSBs is greater than or equal to i ('Yes' in block 302), the MSB of the output number is set to one (block 305) and all the bits in those numbers with an MSB=0 are set to zero (block 504) and in response to determining that the sum of the MSBs is not greater than or equal to i ('No' in block 302), the MSB of the output number is set to zero (block 302), the MSB of the output number is not greater than or equal to i ('No' in block 302), the MSB of the output number is set to zero (block 302), the MSB of the output number is not greater than or equal to i ('No' in block 302), the MSB of the output number is set to zero (block 307) and the all the bits in those numbers with an MSB=1 are set to one (block 506).

[0102] The second iteration (j=m-2) starts by taking the next bit from each of the numbers (block 508), where some of these numbers may be the original numbers and others are the numbers that were modified in the first iteration (e.g. in block 504 or 506). The bits are summed and dependent upon the whether the sum is greater than or equal to i (in block 302), one or more of the remaining, original numbers may be set to all zeros (in block 504) or all ones (in block 506) and a further bit is added to the output number (in block 305 or 307).

[0103] The updating of the numbers (in blocks 504 and 506) can also be described by the following logic equations:

$$z_k[h] = y[j] \cdot (x_k[j] \cdot x_k[h]) + \overline{y[j]} \cdot (x_k[j] + x_k[h])$$

for h = 0, 1, ..., m-1.

[0104] The method of FIG. 5 may then be repeated for all m bits in the input numbers or, in various examples, there may be additional logic that identifies when a result has been obtained earlier (i.e. when there is only one distinct value left among the updated numbers  $N_k$  which are not all ones or all zeros) and outputs the result at that stage (as described above). As noted above, this becomes more complex if there may be more than one number that is the i<sup>th</sup> biggest.

[0105] The method of FIG. 5 can be described with reference to the example shown in FIG. 6, where n=5 and i=3. In the first iteration 602, the MSBs of each number are summed and the result is 3. As the sum is equal to i ('Yes' in block 302), the MSB of the output number 603 is set to one (block 305) and those numbers where the MSB is zero are modified so that all their bits are equal to zero (block 504) and in the example shown numbers N<sub>1</sub> and N<sub>4</sub> are modified in this way.

[0106] In the second iteration 604, the next bits in each of the 5 numbers (original numbers  $N_0$ ,  $N_2$ ,  $N_3$  and modified numbers  $N_1$  and  $N_4$ ) are summed and the result is 1. As the sum is less than i ('No' in block 302), the next most significant bit of the output number 603 is set to zero (block 307) and those numbers where the bit is one are modified so that all their bits are equal to one (block 506) and in the example shown number  $N_2$  is modified in this way.

[0107] In the third iteration 606, the next bits in each of the 5 numbers (original numbers  $N_0$  and  $N_3$  and modified numbers  $N_1 N_2$  and  $N_4$ ) are summed and in this case the result is 2. As the sum is less than i ('No' in block 302), the next bit of the output number 603 is set to one (block 307) and those numbers where the bit is one have all their bits set equal to one (block 506) and in the example shown number  $N_0$  is modified in this way. At this point there is only one original number in the set (i.e. one number that is not all ones or all zeros), number  $N_3$ , and this is

therefore the output number, i.e. the i<sup>th</sup> largest number from the input set. The method may stop at this point (e.g. if logic is provided to assess the flags and determine when only one original, unmodified number remains in the set) or the method may continue until all bits have been assessed and all bits of the output number generated (one bit per iteration).

[0108] Whilst FIG. 5 shows a first example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers, a very similar method may be used to calculate (or identify) the p<sup>th</sup> smallest number from the input set of n m-bit numbers. Like in the method of FIG. 3B, this involves changing the method of FIG. 5 only such that the summation is compared to the value of (n-p) or (n+1-p) rather than i (in block 302). Where (n-p) is used, if the sum of bits is strictly greater than (n-p), then the next bit in the output number is set to one and those numbers with a bit equal to zero are modified so that all the bits are equal to zero (block 504) and in response to determining that the sum is not greater than (n-p), the next bit in the output number is set to zero and those numbers with a bit equal to one (block 506). Alternatively, where (n+1-p) is used, if the sum of bits is greater than or equal to (n+1-p) then the next bit in the output number is set to one (block 305) and those numbers with a bit equal to zero are modified so that all the bits are equal to zero (block 305) and those numbers with a bit equal to zero are modified so that all the bits are equal to zero (block 305) and those numbers with a bit equal to zero are modified so that all the bits are equal to zero (block 305) and those numbers with a bit equal to zero are modified so that all the bits are equal to zero (block 307) and those numbers with a bit equal to one are modified so that all the bits are equal to one (block 307) and those numbers with a bit equal to one (block 506).

[0109] In another example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers, all the input numbers N<sub>k</sub> may be bitwise inverted  $(N_k \rightarrow \overline{N_k})$  and then the method of FIG. 5 may be used with i=p, so long as the final output is inverted back to its original form prior to being output.

[0110] FIG. 7A is a flow diagram of a third example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers. Like the first and second methods, as described above and shown in FIGs. 3A and 5, the third method is also iterative. Like the second method (shown in FIG. 5), the third method modifies numbers instead of using flags; however, instead of modifying some numbers to all zeros and others to all ones, all numbers are modified to be the same value (e.g. all zeros or all ones) and in the examples shown, all numbers are modified to be all zeros. In response to determining that the sum of the MSBs is greater than or equal to i ('Yes' in block 302), the next bit in the output number is set to one (block 305) and all the bits in those numbers with an MSB=0 are set to zero (block 504). In response to determining that the sum of the MSBs is not greater than or equal to i ('No' in block 302), the next bit in the output to i ('No' in block 302), the next bit in the output number is set to zero (block 307) and all the bits in those numbers is set to zero (block 307) and all the bits in those numbers with an MSB=1 are set to zero (block 706) and then, in order that the next iteration performs a correct comparison (in block 302), the value of i is then decremented by the total of the summation in that iteration (block 707).

[0111] The second iteration (j=m-2) starts by taking the next bit from each of the numbers (block 508), where some of these numbers may be the original numbers and others are the numbers that were modified (e.g. to be all zeros) in the first iteration. The bits are summed and dependent upon the whether the sum is greater than or equal to i (in block 302), the next bit in the output integer is set (in block 305 or 307) and different numbers from the remaining, original numbers may be set to all zeros (in block 504 or 706). Only if the sum was less than i ('No' in

block 302), is the value of i is further decremented by the total of the summation in that iteration (block 707). The method of FIG. 7A may then be repeated for all m bits in the input numbers or, as described above, the method may be terminated when all except for one of the numbers in the input set have been modified (e.g. to all zeros) and this remaining number is then the output number.

[0112] The updating of the numbers (in blocks 504 and 706) can also be described by the following logic equations:

$$z_k[h] = \overline{\left(\left(y[j] \cdot \overline{x_k[j]}\right) + \left(\overline{y[j]} \cdot x_k[j]\right)\right)} \cdot x_k[h]$$

for h = 0, 1, ..., m-1.

[0113] The method of FIG. 7A can be described with reference to the example shown in FIG. 8, where n=5 and i=3. In the first iteration 802, the MSBs of each number are summed and the result is 3. As the sum is equal to i ('Yes' in block 302), the MSB of the output number 803 is set to one (block 305) and those numbers where the MSB is zero are modified so that all their bits are equal to zero (block 504) and in the example shown numbers N<sub>1</sub> and N<sub>4</sub> are modified in this way.

[0114] In the second iteration 804, the next bits in each of the 5 numbers (original numbers  $N_0$ ,  $N_2$ ,  $N_3$  and modified numbers  $N_1$  and  $N_4$ ) are summed and the result is 1. As the sum is less than i ('No' in block 302), the next bit in the output number is set to zero (block 307) and those numbers where the bit is one are modified so that all their bits are equal to zero (block 706) and in the example shown number  $N_2$  is modified in this way. The value of i is then decremented by the result of the summation (i.e. by one) so that for the next iteration i=2.

[0115] In the third iteration 806, the next bits in each of the 5 numbers (original numbers  $N_0$  and  $N_3$  and modified numbers  $N_1 N_2$  and  $N_4$ ) are summed and in this case the result is 1. As the sum is less than i ('No' in block 302), the next bit in the output number is set to zero (block 307) and those numbers where the bit is one are modified so that all their bits are equal to zero (block 706) and in the example shown number  $N_0$  is modified in this way. The value of i may be decremented again by the result of the summation (i.e. by one) so that i=1. At this point there is only one original number in the set, number  $N_3$ , and this is therefore the output number, i.e. the i<sup>th</sup> largest number from the input set. The method may stop at this point (e.g. if logic is provided to assess the flags and determine when only one original, unmodified number remains in the set) or the method may continue until all bits have been assessed.

[0116] Whilst FIG. 7A shows a first example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers, a very similar method may be used to calculate (or identify) the p<sup>th</sup> smallest number from the input set of n m-bit numbers, as shown in FIG. 7B. As with FIG. 3B, whilst FIG. 7B shows a comparison, in block 303, of whether the sum is strictly greater than (n-p), in other examples the comparison may be whether the sum is greater than or equal to (n+1-p). In another example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers, all the input numbers N<sub>k</sub> may be bitwise inverted ( $N_k \rightarrow \overline{N_k}$ ) and then the method of FIG. 7A may be used with i=p, so long as the final output is inverted back to its original form prior to being output.

[0117] FIG. 9 is a flow diagram of a fourth example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers. Like the first, second and third methods, as described above and shown in FIGs. 3A, 5 and 7A, the fourth method is also iterative. Like the first method (shown in FIG. 3A), the fourth method uses a flag; however, only a single flag is used. In response to determining that the sum of the MSBs is greater than or equal to i ('Yes' in block 302), the MSB of the output number is set to one (block 305) and the flag is set for those numbers with an MSB=0 (block 904). In response to determining that the sum of the output number is set to zero (block 307) and the flag is set for those numbers with an MSB=1 (block 906) and then, in order that the next iteration performs a correct comparison (in block 302), the value of i is then decremented by the total of the summation in that iteration (block 707).

[0118] The second iteration (j=m-2) starts by taking the next bit from each of the numbers and modifying the bits using the flag values (block 908). If the flag is set for a number, then the bit is set to a predefined value, e.g. zero, irrespective of whether the bit value is actually a one or a zero. If the flag is not set, then the value of the bit is left unchanged.

[0119] The alteration of the bits (in block 908) can also be described by the following logic equation:

$$z_k[j] = x_k[j] \cdot \overline{f \log_k[j+1]}$$

The corresponding hardware arrangement 340, which may be replicated n-times (one for each number in the set 200) is shown in FIG. 3I and comprises a NOT gate 342 and an AND gate 344, i.e. the current bit is combined with an inverted version of the current flag (as set in the previous iteration) in an AND gate.

[0120] The altered bits (as generated in block 908) are then summed and dependent upon the whether the sum is greater than or equal to i (in block 302), one or more further flags may be set (in block 904 or 906). If the predefined value is zero and the sum was less than i ('No' in block 302), the value of i is updated by decrementing the threshold value by the total of the summation in that iteration (block 707). Letting  $i_j$  denote the threshold value, *i*, used in the comparison of the *j*<sup>th</sup> bits, this updating can be described by:

$$i_j = \begin{cases} i_{j+1} & \text{if } sum_{j+1} \ge i_{j+1} \\ i_{j+1} - sum_j & \text{if } sum_{j+1} < i_{j+1} \end{cases}$$

In a variation of that shown in FIG. 9, if the predefined value is one (instead of zero) and the sum was greater than or equal to i ('Yes' in block 302), the value of i is updated by incrementing the threshold value by the number of rows which are changed this iteration, this will be the total number of inputs minus the total of the summation in that iteration (block 707) this updating can be described by:

$$i_j = \begin{cases} i_{j+1} & \text{if } sum_{j+1} < i_{j+1} \\ i_{j+1} + (n - sum_{j+1}) & \text{if } sum_{j+1} \ge i_{j+1} \end{cases}$$

The method of FIG. 9 (or the variation of that method) may then be repeated for all m bits in the input numbers.

[0121] Whilst FIG. 9 shows a first example method of calculating (or identifying) the i<sup>th</sup> largest number from the input set of n m-bit numbers, a very similar method may be used to calculate

(or identify) the p<sup>th</sup> smallest number from the input set of n m-bit numbers by changing the comparison performed (e.g. from block 302 to block 303 or to the modified version of block 303 described above, where the sum is compared to (n+1-p)) and the way in which the threshold is updated (e.g. from block 707 to block 717). In another example method of calculating the p<sup>th</sup> smallest number from the input set of n m-bit numbers, all the input numbers N<sub>k</sub> may be inverted  $(N_k \rightarrow \overline{N_k})$  and then the method of FIG. 9 may be used with i=p, so long as the final output is inverted back to its original form.

[0122] In yet further variations, instead of using flags or updating the bits within the numbers, bits in a mask may be set in response to the comparison (e.g. in block 302) and then for subsequent iterations, the bits in the numbers may be combined (e.g. using AND gates) with the mask values. This has the same effect as the updating of the numbers (in the examples described above).

[0123] Synthesis experiments suggest that the use of two flags (as in the methods of FIGs. 3A and 3B) is more efficient in some circumstances than the other methods described herein in the sense that it requires smaller area of hardware logic to implement. In other circumstances the other methods described herein may be more efficient (e.g. the method of FIG. 5 may be more efficient if the cost of a register to store flags is more than the additional logic to update the bits in the input numbers and/or the methods of FIGs. 7A, 7B and 9 may be more efficient in circumstances where the logic that performs the updating of i or p can be made small).