US 20140312297A1

# (19) United States (12) Patent Application Publication CLARK

# (10) Pub. No.: US 2014/0312297 A1 (43) Pub. Date: Oct. 23, 2014

### (54) DEVICE STRUCTURE FOR A RRAM AND METHOD

- (71) Applicant: Crossbar, Inc., Santa Clara, CA (US)

- (72) Inventor: Mark Harold CLARK, Santa Clara, CA (US)

- (21) Appl. No.: 14/310,113

- (22) Filed: Jun. 20, 2014

# **Related U.S. Application Data**

(62) Division of application No. 13/598,550, filed on Aug. 29, 2012, now Pat. No. 8,796,102.

#### Publication Classification

(51) Int. Cl. *H01L 45/00* (2006.01)

### (52) U.S. Cl.

# (57) ABSTRACT

A method of forming a resistive device includes forming a first wiring layer overlying a first dielectric on top of a substrate, forming a junction material, patterning the first wiring layer and junction material to expose a portion of the first dielectric, forming a second dielectric over the patterned first wiring layer, forming an opening in the second dielectric to expose a portion of the junction material, forming a resistive switching material over the portion of the junction material in the opening, the resistive switching material having an intrinsic semiconductor characteristic, forming a conductive material over the resistive switching material, etching the conductive material and the resistive switching material to expose respective sidewalls of the resistive switching material and the conductive material, and the second dielectric, and forming a second wiring layer over the conductive material in contact with the respective sidewalls and the second dielectric.

Fig. 4

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 13

#### DEVICE STRUCTURE FOR A RRAM AND METHOD

**[0001]** This application claims priority to and is a divisional of U.S. application Ser. No. 13/598,550 filed Aug. 29, 2012, which is hereby incorporated by reference for all purposes.

### BACKGROUND

**[0002]** The inventor of the present invention has recognized the success of semiconductor devices has been mainly driven by an intensive transistor down-scaling process. However, as field effect transistors (FETs) approach sizes less than 100 nm, physical problems such as short channel effect begin to hinder proper device operation. For transistor based memories, such as those commonly known as Flash memories, other performance degradations or problems may occur as device sizes shrink. With Flash memories, a high voltage is usually required for programming of such memories, however, as device sizes shrink, the high programming voltage can result in dielectric breakdown and other problems. Similar problems can occur with other types of non-volatile memory devices other than Flash memories.

**[0003]** The inventor of the present invention recognizes that many other types of non-volatile random access memory (RAM) devices have been explored as next generation memory devices, such as: ferroelectric RAM (Fe RAM); magneto-resistive RAM (MRAM); organic RAM (ORAM); phase change RAM (PCRAM); and others.

**[0004]** A common drawback with these memory devices include that they often require new materials that are incompatible with typical CMOS manufacturing. As an example of this, Organic RAM or ORAM requires organic chemicals that are currently incompatible with large volume silicon-based fabrication techniques and foundries. As another example of this, Fe-RAM and MRAM devices typically require materials using a high temperature anneal step, and thus such devices cannot be normally be incorporated with large volume silicon-based fabrication techniques.

**[0005]** Additional drawbacks with these devices include that such memory cells often lack one or more key attributes required of non-volatile memories. As an example of this, Fe-RAM and MRAM devices typically have fast switching (e.g. "0" to "1") characteristics and good programming endurance, however, such memory cells are difficult to scale to small sizes. In another example of this, for ORAM devices reliability of such memories is often poor. As yet another example of this, switching of PCRAM devices typically includes Joules heating and undesirably require high power consumption.

**[0006]** From the above, improved semiconductor memory devices that can scale to smaller dimensions with reduced drawbacks are therefore desirable.

#### BRIEF SUMMARY OF THE PRESENT INVENTION

**[0007]** The present invention is directed to resistive switching devices. More particularly, embodiments according to the present invention provide device structures and methods for resistive switching devices. Embodiments of resistive switching devices can be applied in non-volatile memory devices, but it should be recognized that embodiments can be applied to a much broader range of memories, processors, devices, or the like. **[0008]** In a specific embodiment, a method of forming a resistive device for a non-volatile memory device is provided. The method includes providing a substrate having a surface region and forming a first dielectric material overlying the surface region of the substrate. A first wiring material is formed overlying the first dielectric material and a junction material comprising a p+ polycrystalline silicon material or p-doped silicon germanium material is formed overlying the first wiring material. In a specific embodiment, the method subjects the first wiring material and the junction material to a first pattern and etch process to form one or more bottom wiring structures and to expose a portion of the first dielectric material. The one or more bottom wiring structures includes the first wiring material and the junction material.

**[0009]** Embodiments also include forming a second dielectric material overlying the one or more bottom wiring structure, and then forming an opening structure in a portion of the second dielectric material to expose a portion of the junction material. A resistive switching material is formed overlying at least the junction material in the opening structure. The resistive switching material can include an amorphous silicon material having an intrinsic semiconductor characteristic in certain embodiments.

**[0010]** In specific embodiments, the method includes forming a conductive material overlying and adjacent to the resistive switching material (in physical and electric contact therewith). In a specific embodiment, the method includes removing concurrently a portion of the conductive material and the resistive switching material to expose a portion of second dielectric material surface while maintaining the conductive material and the resistive switching material in the opening structure in physical contact and electric contact with the junction material.

**[0011]** In some embodiments, a second wiring structure is formed overlying the conductive material in the first opening structure and overlying the exposed second dielectric material. The conductive material, the resistive switching material and the junction material form a resistive switching device in some specific embodiments.

**[0012]** In a specific embodiment, a resistive switching device for a non-volatile memory device is provided. The device includes a top electrode, a bottom electrode and a resistive switching material configured in an intersection region of the top electrode and the bottom electrode. In a specific embodiment, the top electrode has a portion that includes an active metal material in physical and electric contact with the resistive switching material. The bottom electrode includes a junction material formed from a p+ silicon material (for example, a p+ polycrystalline silicon material, or a combination).

**[0013]** In various embodiments, the resistive switching material includes a silicon material having an intrinsic semiconductor characteristic. Depending on the embodiment, the resistive switching material can be an amorphous silicon material or a polycrystalline silicon material, each having an intrinsic semiconductor characteristic.

**[0014]** In operation, the active metal material is configured to form a metal region including a filament structure in a portion of the resistive switching material upon application of an electric field to cause an electric resistance change of the resistive switching material. For example, a positive voltage applied to the top electrode with respect to the bottom electrode would cause the resistive switching device to be in a low

resistance state or a high bit state upon programming. A negative voltage applied to the top electrode after programming would cause the resistive switching device to be in a high resistance state or having a low bit value.

[0015] According to one aspect of the invention, a method of forming a resistive device for a non-volatile memory device is disclosed. One method includes providing a substrate having a surface region, forming a first dielectric material overlying the surface region of the substrate, and forming a first wiring material overlying the first dielectric material. A technique includes forming a junction material comprising a p-doped silicon-bearing material overlying the first wiring material, subjecting the first wiring material and the junction material to a first pattern and etch process to form one or more bottom wiring structures and expose a portion of the first dielectric material, the one or more bottom wiring structures comprising the first wiring material and the junction material, and forming a second dielectric material overlying the one or more bottom wiring structure. A process includes forming an opening structure in a portion of the second dielectric material to expose a portion of the junction material, forming a resistive switching material comprising an amorphous silicon-bearing material overlying at least the portion of the junction material in the opening structure, the amorphous silicon-bearing material having an intrinsic semiconductor characteristic, and forming a conductive material overlying the resistive switching material, the conductive material being in physical contact and electric contact with the resistive switching material. A method includes removing concurrently a portion of the conductive material and a portion of the resistive switching material to expose a portion of second dielectric material, sidewalls of the conductive material and sidewalls of the resistive switching material, while maintaining conductive material and resistive switching material in the opening structure in physical contact and electric contact with the junction material, and forming a second wiring structure overlying the conductive material in the opening structure and overlying the portion of the second dielectric material.

[0016] According to another aspect of the invention, a resistive switching device for a non-volatile memory device is disclosed. A device includes a substrate having a surface region, a first dielectric material overlying the surface region of the substrate, and a first wiring material overlying the first dielectric material. A memory includes a junction material comprising a p-doped silicon-bearing material overlying the first wiring material, one or more bottom wiring structures comprising the first wiring material and the junction material, and a second dielectric material overlying the one or more bottom wiring structures. A device includes a plurality of stacks of material comprising a conductive material and a resistive switching material disposed within an opening structure of the second dielectric material, wherein the resistive switching material is in contact with a portion of the junction material, wherein the resistive switching material comprises an amorphous silicon-bearing material having an intrinsic semiconductor characteristic, and wherein the conductive material and the resistive switching material include respective sidewalls, and a second wiring material overlying the plurality of stacks of material and the second dielectric material, wherein the second wiring material contacts the sidewalls of the conductive material, the sidewalls of the resistive switching material and the second dielectric material.

**[0017]** Many benefits can be achieved by ways of the present invention over conventional techniques. Some embodiments according to the present invention provide a method to form a resistive switching device free from contamination or with reduced contamination that cause undesirable electric connection between electrodes (or shorts). Additionally, various embodiments can be carried out using conventional processing equipment without modification. Depending on the embodiments, one or more of these benefits may be achieved. One skilled in the art would recognize other variations, modifications, and alternatives.

#### SUMMARY OF THE DRAWINGS

**[0018]** In order to more fully understand the present invention, reference is made to the accompanying drawings. Understanding that these drawings are not to be considered limitations in the scope of the invention, the presently described embodiments and the presently understood best mode of the invention are described with additional detail through use of the accompanying drawings in which:

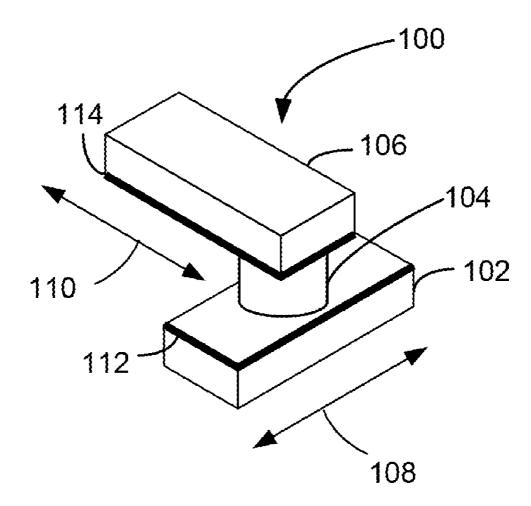

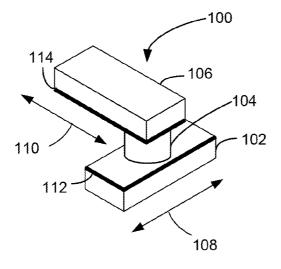

**[0019]** FIG. **1** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

**[0020]** FIG. **2** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

**[0021]** FIG. **3** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

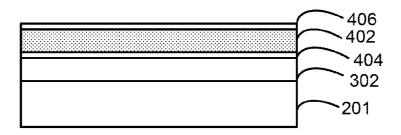

**[0022]** FIG. **4** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

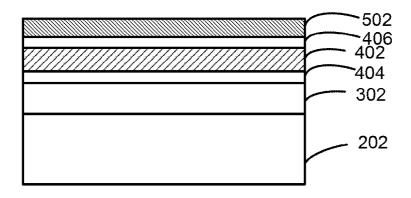

**[0023]** FIG. **5** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

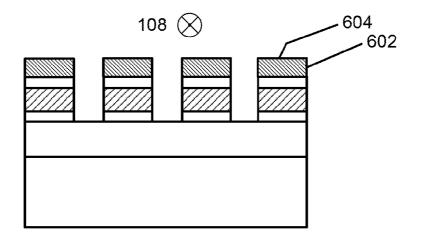

**[0024]** FIG. **6** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

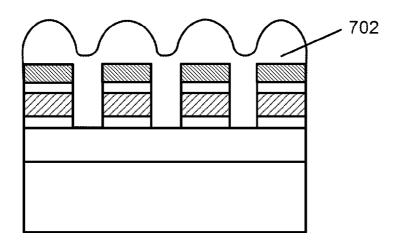

**[0025]** FIG. **7** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

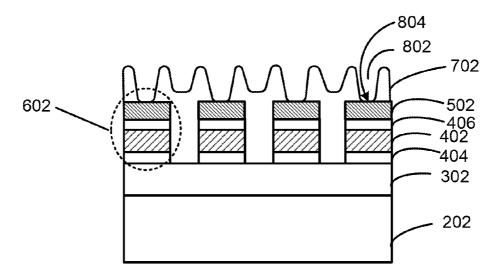

**[0026]** FIG. **8** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

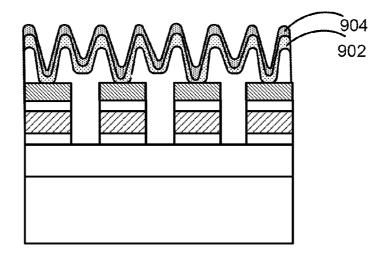

**[0027]** FIG. **9** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

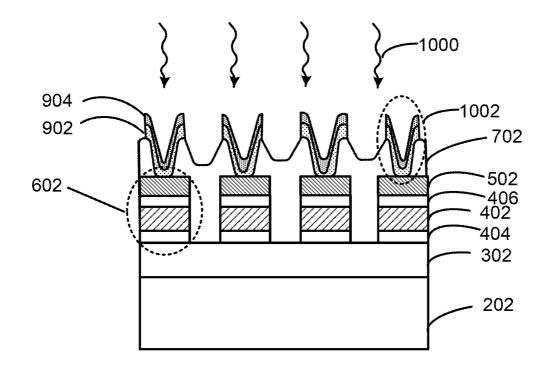

**[0028]** FIG. **10** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

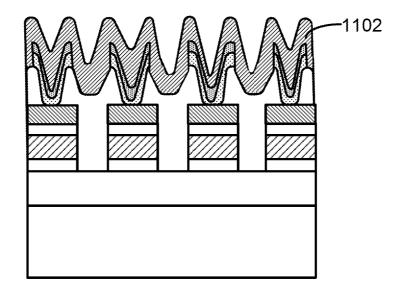

**[0029]** FIG. **11** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention;

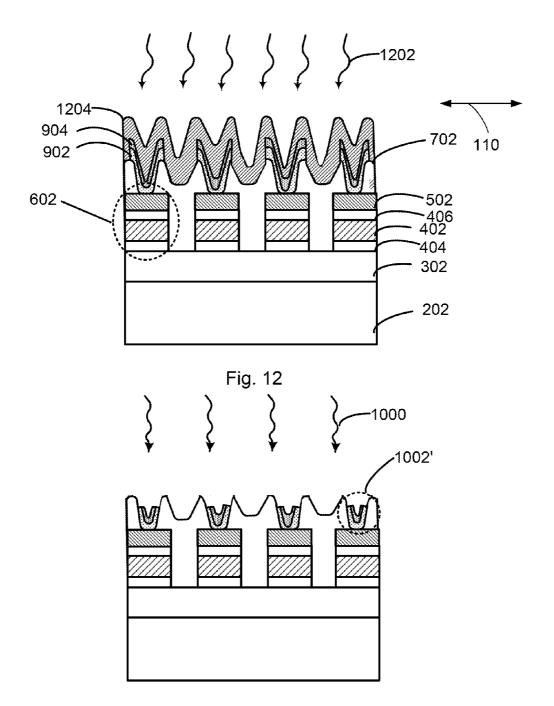

**[0030]** FIG. **12** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention; and

**[0031]** FIG. **13** is a simplified diagram illustrating a resistive switching device according to an embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE PRESENT INVENTION

**[0032]** The present invention is directed to resistive switching device. More particularly, embodiments according to the present invention provide a device structure and a method to form a resistive switching device. The resistive switching device has been applied in non-volatile memory device. But it should be recognized that embodiment according to the present invention can have a much broader range of applicability.

[0033] Switching devices is generally based on a state change characteristic of a non-conducting material in the presence of an electric field. Silicon based switching devices have a material compatibility advantage over other switching devices using materials such as metal oxides in fabrication. However, conventional metal/Si/metal (M/Si/M) type devices require a high operating voltage (usually greater than about 10V) which is not fully controllable and thus reduces the device yield and endurance. Such devices may not be able to further scale down to nanometer scale as required by present application in consumer electronics. Moreover, contaminations and process complexity adversely affect yield and performance of the device. Embodiments according to the present invention provide a method and a resulting device structure for a resistive switching device having a desirable switching characteristic and device reliability.

**[0034]** The terms "top" and "bottom" are for purpose of illustration only, and should not be construed to be limiting.

**[0035]** The present invention is generally related to resistive switching devices. More particularly, embodiments according to the present invention provide a device structure and a method to improve device performance of a resistive switching device The present invention can be applied to improving data retention characteristic of non-volatile memory devices, but it should be recognized that embodiments according to the present invention can have a much broader range of applicability.

[0036] Some embodiments of a resistive switching device include a two terminal device including a top electrode, a bottom electrode and a resistive switching material disposed between the top electrode and the bottom electrode. The resistive switching material is characterized by a resistance dependent on an electric field upon an application of a suitable voltage to one of the electrodes. The electric field causes a conductor path to form in the resistive switching material. Depending on the electrode material and the resistive switching material used, the conductor path can be formed from the electrode material or defect path in the presence of the electric field. The conductor path determines the resistance of the resistive switching material. For example, for a metal oxide material as the switching material, the conductor path can form from oxygen deficient sites in the metal oxide. For a silicon material as the switching material, the conductor path can be formed from the electrode material, which comprises an active metal material. The resistive switching material is in a high conductance state. The conductor path is broken or retracts when a reverse bias voltage is applied and causes the resistive switching material to be in a low conductance state. The resistance of the resistive switching material has a resistance depending on the voltage and provide for a multi-level or multi-bit device. Therefore the conductor path structure needs to be stable under selected voltage, forward bias voltage, or reverse bias voltage for proper data retention.

**[0037]** Embodiments according to the present invention provide a device structure and a method for a resistive switching device characterized by a stable conductive path when a pre-determined voltage is applied and a reliable data retention characteristic for the device.

**[0038]** FIG. 1 is a simplified diagram illustrating a resistive switching device 100 according to an embodiment of the present invention. The resistive switching device includes a first electrode 102, a second electrode 106, and a resistive switching material 104 sandwiched between the first electrode and the second electrode.

**[0039]** In various embodiments, resistive switching device **100** is formed upon a semiconductor substrate (not shown). In certain embodiments, the semiconductor substrate can have one or more MOS devices formed thereon. The one or more MOS devices can be controlling circuitry for the resistive memory devices in specific embodiments. In other embodiments, the one or more MOS devices may include other functionality, such as a processor, logic, or the like.

[0040] In various embodiments, a processor, or the like, may include resistive memory memories as described herein. Because the resistive state-change memories are relatively non-volatile, the states of devices, such as processors, or the like may be maintained while power is not supplied to the processors. To a user, such capability would greatly enhance the power-on power-off performance of devices including such processors. Additionally, such capability would greatly reduce the power consumption of devices including such processors. In particular, because such resistive memories are non-volatile, the processor need not draw power to refresh the memory states, as is common with CMOS type memories. Accordingly, embodiments of the present invention are directed towards processors or other logic incorporating these memory devices, as described herein, devices (e.g. smart phones, network devices) incorporating such memory devices, and the like.

[0041] In some embodiments, the first electrode 102 can be a first conductor material. The first electrode 102 can include a first conductor material such as a first metal material and a doped semiconductor material 112. In a specific embodiment, the first metal material 102 can be tungsten, aluminum, copper or other suitable metal that are compatible with CMOS fabrication techniques. In additional embodiments, a doped semiconductor material 112 may be p-doped polysilicon, p-doped silicon germanium, or the like. In a specific embodiment, the first electrode is elongated in shape and configured to extend in a first direction 108.

**[0042]** The resistive switching material **104** can include a suitable insulator material having a resistance that can be altered upon application of an electric field to the insulator material. In a specific embodiment, the resistive switching material **104** can include a silicon material. For example, the silicon material can be an amorphous silicon material, a microcrystalline silicon material, a macro crystalline silicon material, a silicon germanium material including any combination of these. In some embodiments, the silicon material includes an amorphous silicon material, a silicon oxide, or the like.

**[0043]** The resistive switching material **104** is characterized by a state, for example, a resistance state dependent on an electric field in the switching material. In a specific embodiment, the switching material is an amorphous silicon material. The amorphous silicon material has essentially intrinsic semiconductor characteristic and is not intentionally doped in a specific embodiment. In various embodiments, the amorphous silicon is also referred to as non-crystalline silicon (nc-Si). nc-Si non-volatile resistive switching devices may be fabricated using existing CMOS technologies. In an exemplary process, a mixture of silane (SiH4) (45 sccm) and Helium (He) (500 sccm) is used to form an a-Si layer with a deposition rate of 80 nm per minute (T=260° C., P=600 mTorr) during PECVD. In another exemplary process, a mixture of silane (SiH4) (190 sccm) and Helium (He) (100 sccm) is used to form an a-Si layer with a deposition rate of 2.8 A per second (T=380° C., P=2.2 Torr) during PECVD. In another exemplary process, silane (SiH4 80 sccm) or disilane is used to form an a-Si layer with a deposition rate of 2.8 nm per minute (T=585° C., P=100 mTorr) during LPCVD. Portions of poly-silicon grains may form during the LPCVD process and result in an amorphous-poly silicon film. In various embodiments, no p-type, n-type, or metallic impurities are intentionally added to the deposition chamber while forming the amorphous silicon material. Accordingly, when deposited, the amorphous silicon material is substantially free of any p-type, n-type or metallic dopants, i.e. the amorphous silicon material is undoped.

[0044] In yet another embodiment, the resistive switching material/amorphous silicon material 104 may be formed from an upper region of a p+ polycrystalline silicon or p+ silicon germanium bearing layer (e.g. 112) using an Argon, Silicon, Oxygen plasma etch, or the like. For instance, a plasma etch may use a bias power within a range of approximately 30 watts to approximately 120 watts to convert an upper region of the polysilicon or silicon germanium material into a non-conductive amorphous silicon having p-type impurities (from the original polycrystalline silicon or silicon germanium bearing layer 112).

**[0045]** The second electrode **106** can be a second conductor material and can have a portion that includes a second metal material. The second metal material can be selected from aluminum, nickel, silver, gold, palladium, platinum, and others. The second metal material may have a suitable diffusivity in the switching material in a specific embodiment. In a specific embodiment, the second electrode is elongated in shape and configured to extend in a second direction **110** orthogonal to the first direction **108**. In a specific embodiment, the second metal material includes a silver material.

[0046] As mentioned above, in certain embodiments, the resistive switching device 100 can include a contact material (112) disposed between the metal material of the first electrode 102 and the amorphous silicon material 104. In some embodiments, the contact material 112 provides a suitable interfacial defect characteristic for desirable switching behavior for the switching device 100. For amorphous silicon material as the switching material 104, the contact material 112 can be p+ polysilicon or p+ silicon germanium material. In certain embodiments, the contact material 112 can be optional.

[0047] In some embodiments, additional interposing layer (s) 114 may be disposed between resistive switching material 104 and second electrode 106. The additional layer 114 may include a material that has non-noble metal properties, e.g. the material oxidizes in the presence of oxygen. In some examples, the additional layer 114 may be titanium, titanium nitride, tungsten, tungsten nitride, or the like. In various embodiments, additional layer 114 may serve as an adhesion and/or barrier layer between resistive switching material 104 and second electrode 106.

**[0048]** In various embodiments, multiple resistive switching devices **100** can be disposed in an N by M crossbar array to form a high density interconnected array of non-volatile memory cells.

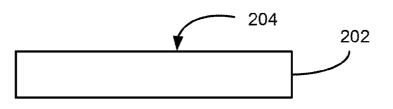

**[0049]** FIGS. **2-13** illustrate a method of forming a resistive switching device for a memory device according to various embodiments of the present invention. As shown in FIG. **1**, a semiconductor substrate **202** having a surface region **204** is provided. Semiconductor substrate **202** can be a single crystal silicon wafer, a silicon germanium material, a silicon on insulator (commonly called SOI) depending on the embodiment. In certain embodiments, semiconductor substrate **202** can have one or more MOS devices formed thereon or therein. The one or more MOS devices can be controlling circuitry for the resistive switching device, or the like in some embodiments.

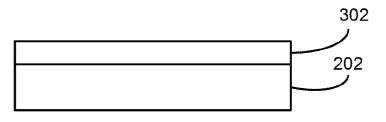

**[0050]** As illustrated in FIG. **3**, embodiments of the method include depositing a first dielectric material **302** overlying the semiconductor substrate **202**. First dielectric material **302** can be silicon oxide, silicon nitride, a dielectric stack of alternating layers of silicon oxide and silicon nitride (for example, an ONO stack), a low K dielectric, a high K dielectric, or a combination, and others, depending on the application. First dielectric material **302** can be deposited using techniques such as chemical vapor deposition, including low pressure chemical vapor deposition, plasma enhanced chemical vapor deposition, atomic layer deposition (ALD), physical vapor deposition, including any combination of these, and others.

**[0051]** Referring to FIG. **4**, embodiments of the method include depositing a first wiring material **402** overlying the first dielectric material. First wiring material **402** can be a suitable metal material including alloy materials, or a semiconductor material having a suitable conductivity characteristic. In some embodiments, the metal material can be tungsten, aluminum, copper or silver, and others. In some embodiments, the first wiring material may be a combination of conductive materials. In various embodiments, these metal materials may be deposited using a physical vapor deposition process, chemical vapor deposition process, electroplating, or electrodeless deposition process, a combinations of these, and others. In some embodiments, the semiconductor material can be, for example, a p-type doped silicon material, a conductive polysilicon, or the like.

[0052] In certain embodiments, a first adhesion material 404 is first formed overlying the first dielectric material 402 before deposition of the first wiring material 402 to promote adhesion of the first wiring material 402 to the first dielectric material 302. A diffusion barrier material 406 may also be formed overlying the first wiring material 402 to prevent, for example, the conductive material, the metal material, gasses, oxygen, or the like to contaminate other portions of the device in a specific embodiment.

**[0053]** Referring to FIG. 5, the method includes forming a junction material **502** overlying at least the first wiring material **402** (or first diffusion barrier material **406**, if used). First junction material **502** can be a p-doped silicon-bearing material (e.g. p++ polysilicon, p-doped silicon-germanium, or the like) in a specific embodiment. The p++ polysilicon material can be formed by using a deposition process such as a low pressure chemical vapor deposition process a plasma enhanced chemical vapor deposition process using silane  $(SiH_4)$  or disilane  $(Si_2H_6)$ , or a suitable chlorosilane depending on the application. Alternatively, the first silicon material

can be deposited using a physical vapor deposition process from a suitable silicon target. Deposition temperature can range from about 380 Degree Celsius to about 450 Degree Celsius, and preferably not higher than 440 Degree Celsius. In a specific embodiment, the p++ polysilicon material is deposited using a low pressure chemical vapor deposition process using disilane at a deposition temperature ranging from about 400 Degree Celsius to about 460 Degree Celsius. [0054] In FIG. 6, an embodiment of the method subjects first wiring material 402 (and junction material 502 to a first pattern and etch process to form a bottom wiring structure 602. The bottom wiring structure 602 includes a plurality of first elongated structures configured to extend in first direction 108 in a specific embodiment.

[0055] Next, as illustrated in FIG. 7, an embodiment deposits a second dielectric material 702 overlying the bottom wiring structure 602. In some embodiments, second dielectric material 702 contacts first dielectric material 302.

**[0056]** The second dielectric material **702** can be silicon oxide, silicon nitride, a dielectric stack of alternating layers of silicon oxide and silicon nitride (for example, an ONO stack), a low K dielectric, a high K dielectric, or a combination, and others, depending on the application.

**[0057]** In some embodiments, second dielectric material **702** may be subjected to a planarizing process form a planarized surface. The planarizing process can be a chemical mechanical polishing process or an etch back process, a combination thereof, and others depending on the application. In certain implementations, the planarizing steps may be omitted, as illustrated in FIG. **8**.

[0058] Referring to FIG. 8, second dielectric material 702 (not planarized) is subjected to a second pattern and etch process to form a first opening structure 802 in a portion of second dielectric material 702. In various embodiments, junction material 502 serves as an etch stop. As shown in FIG. 8, first opening structure 802 exposes a top surface region 804 of dielectric material 702 in the bottom wiring structure 602, as shown.

**[0059]** As shown in FIG. 9, various embodiments include depositing a resistive switching material 902 overlying the second dielectric material 702 and substantially conformal overlying the first opening structure 802. In a specific embodiment, the resistive switching material 902 is an amorphous silicon material having an intrinsic semiconductor characteristic.

[0060] In various embodiments, the resistive switching material 902 is characterized by a state, for example, a resistance state dependent on an electric field in the switching material. In a specific embodiment, the resistive switching material 902 is an amorphous silicon material. The amorphous silicon material has essentially intrinsic semiconductor characteristic and is not intentionally doped in a specific embodiment. In various embodiments, the amorphous silicon is also referred to as non-crystalline silicon (nc-Si). nc-Si non-volatile resistive switching devices may be fabricated using existing CMOS technologies. In an exemplary process, a mixture of silane (SiH4) (45 sccm) and Helium (He) (500 sccm) is used to form an a-Si layer with a deposition rate of 80 nm per minute (T=260° C., P=600 mTorr) during PECVD. In another exemplary process, a mixture of silane (SiH4) (190 sccm) and Helium (He) (100 sccm) is used to form an a-Si layer with a deposition rate of 2.8 A per second (T=380° C., P=2.2 Torr) during PECVD. In another exemplary process, silane (SiH4 80 sccm) or disilane is used to form an a-Si layer with a deposition rate of 2.8 nm per minute (T=585° C., P=100 mTorr) during LPCVD. Portions of poly-silicon grains may form during the LPCVD process and result in an amorphous-poly silicon film. In various embodiments, no p-type, n-type, or metallic impurities are intentionally added to the deposition chamber while forming the amorphous silicon material. Accordingly, when deposited, the amorphous silicon material is substantially free of any p-type, n-type or metallic dopants, i.e. the amorphous silicon material is undoped. In some embodiments, a thickness of the amorphous silicon-bearing material may be on the order of about 5 nm, within the range of about 3 nm to about 8 nm, within the range of about 10 nm, or the like.

[0061] In yet another embodiment, the resistive switching material 902 (e.g. amorphous silicon material) may be formed from an upper region of junction material 502, via top surface region 804. In some examples, junction material 501 includes a p-doped silicon bearing material (e.g. polysilicon, silicon-germanium) that is amorphized by an Argon, Silicon, Oxygen plasma etch, or the like. For instance, a plasma etch may use a bias power within a range of approximately 30 watts to approximately 120 watts to convert an upper region of junction material 502 into a non-conductive amorphous silicon. Although this layer may have having p-type impurities (from the original polycrystalline silicon bearing layer), in the amorphized state, the impurities are not active, and the amorphized layer is intrinsic. Typical thickness ranges for such an amorphized layer is from about 2 nm to about 10 nm thick.

[0062] Referring again to FIG. 9, in various embodiments, the method includes depositing an active metal material 904 overlying the resistive switching material. For amorphous silicon material as the resistive switching material 902, active metal material 904 can be selected from silver, gold, palladium, platinum, aluminum, chromium, vanadium, and others. The active metal material 904 is selected to have a desirable diffusivity characteristic in the resistive switching material 902 in a presence of a suitable electric field.

[0063] In certain embodiments, the active metal material 904 is silver. In some embodiments, silver is deposited at a temperature no greater than about 250 Degree Celsius to inhibit mass diffusion of silver into the resistive switching material 902. In a specific embodiment, in operation of the fabricated device, when a positive voltage greater than a threshold voltage applied to the active metal material 904 with respect to the bottom wiring structure 602, the active metal material 904 (e.g. silver) migrates into a portion of the amorphous silicon material 902. This causes the amorphous silicon material 902 to be in a low resistance state (or on state) and causes an on-state current flow.

[0064] Referring now to FIG. 10. Resistive switching material 902 and active metal material 904 are subjected concurrently to a pattern and etch process 1000 to remove a first portion of the resistive switching material 904 and the active metal 902 from a surface region of the second dielectric material while a second portion 1002 of the resistive switching material and the active metal material are maintained in physical and electric contact with the first junction material 502. As illustrated in FIG. 10, by etching resistive switching material 904 and active metal 902 with the same etch process, and etching deeply into second dielectric material 702, pigtails, or other types of contaminants that may cause sidewall shorts are reduced from the exposed sidewalls of resistive switching material 904 and active metal 902. **[0065]** In some embodiments, the resistive switching material in second portion **1002** provides a resistive switching region for a resistive switching device. The pattern and etch process **1000** can be a sputter etch using argon as an etchant material. Alternatively, a reactive ion etch may be used. In some embodiments, the second dielectric material **702** may have a thickness thick enough to maintain a certain thickness after etching process **1000** to electrically isolate each of the resistive switching devices, as illustrated.

[0066] In some embodiments, the method includes forming a second wiring material 1102 overlying the active metal material 904 in the first opening structure and the exposed surface region of the second dielectric material 702 as illustrated in FIG. 11. The second wiring material 1102 can be copper, tungsten, or aluminum depending on the application. Depending on the implementation, the active metal material 1002 (for example, silver) may be used as the top wiring material. The second wiring material 1102 can further include one or more diffusion barrier layer and/or adhesion material disposed between second wiring material 1102 and active metal material 904 and/or disposed above second wiring material 1102. In various embodiments, an adhesion material promotes adhesion of the second wiring material to the second dielectric material and the active metal material; and one or more diffusion barrier material inhibits unintentional diffusion of the active metal material and/or inhibits oxygen from diffusing into other layers of the device. Depending on the implementation, the one or more diffusion barrier material can include titanium, titanium nitride, tungsten, titanium tungsten, or a combination thereof, and others.

[0067] In the embodiments illustrated in FIG. 12, second wiring material 1102 including the one or more diffusion barrier material is subjected to a pattern and etch process 1202 to form a top wiring structure 1204 for the resistive switching device. In some embodiments, pattern and etch process 1202 is performed at temperatures no greater than about 250 Degree Celsius to inhibit mass diffusion of active conductive material (for example silver material) to diffuse into the resistive switching material (for example amorphous silicon material) due to thermal effect.

**[0068]** The second wiring structure **1204** is configured to be elongated in shape and extend to form wiring structures that extend in a second direction **110**, perpendicular to the first direction **108** in a specific embodiment. The resistive switching material **902** is sandwiched in an intersection region formed the top wiring structure **1204** and the bottom wiring structure **602** providing for a high density interconnected device.

**[0069]** Depending on the application, second wiring material **1102** can be a semiconductor material having a suitable conductance. For example, the semiconductor material can include a suitably doped polysilicon material in a specific embodiment.

**[0070]** In some alternative embodiments, as illustrated in FIG. **13**, pattern and etching process **1000** can remove substantially all the resistive switching material **902** and the active metal material **904** from the surface region of the second dielectric material **702** and partially from the first opening region while a second portion **1002**' remains in the first opening structure.

[0071] In some embodiments, the second portion including the resistive switching material 902 and the active metal material 904 maintains a physical and electrical contact with the junction material 502 in a specific embodiment. By merely changing a critical dimension (CD) of patterning and etching process **1000**, either structure **1002** or **1002'** may be achieved. The embodiments in FIGS. **11** and **13** provide for a resistive switching material side wall free from contamination from patterning and etching of the conductive material or wiring materials during fabrication.

**[0072]** As the resistive switching material **902** is formed in the first opening structure before pattern and etch, contamination due to etching may be formed on sidewall of the resistive switching material **902** and undesirable electrical connection between the bottom wiring structure **602** and the top wiring structure **1204** is thus inhibited. Device yield and device performance are thus enhanced.

[0073] In a specific embodiment, a resistive switching device structure for a non-volatile memory device is provided. The resistive switching device includes a substrate having a surface region and a first dielectric material overlying the surface region of the substrate. The substrate can be a single crystal silicon material, a silicon on insulator substrate (commonly known as SOI), or a silicon germanium material, and others, depending on the embodiment. In a specific embodiment, the substrate can have one or more transistor device formed thereon. The one or more transistor device can be controlling circuitry for the resistive switching device in a specific embodiment. The resistive switching device includes a first wiring material overlying the first dielectric material and a junction material comprising a p+ polycrystalline silicon material overlying the first wiring material. In a specific embodiment, the device structure includes one or more bottom wiring structures comprising the first wiring material and the junction material. The bottom wiring structure is elongated in shape and configured to extend in a first direction. The bottom wiring structures are isolated using a second dielectric material overlying the one or more bottom wiring structures. The resistive switching device includes a stack of material configured in an opening in a portion of the second dielectric material overlying the junction material in a specific embodiment. The stack of material includes a resistive switching material overlying a conductive material in a specific embodiment. The resistive switching material includes an amorphous silicon material having an intrinsic semiconductor characteristic in various implementations. The resistive switching device includes a second wiring structure overlying at least the conductive material in the first opening structure and overlying an exposed second dielectric material. The second wiring structure is configured to extend in a second direction at an angle to the first direction. In certain implementation, the angle is right angle.

**[0074]** Though the present invention has been exemplified in various embodiments, it is to be understood that the examples and embodiment described herein are for illustrative purpose only purposes only and that various modifications or alternatives in light thereof will be suggested to persons skilled in the art and are to be included within the spirit and purview of this application and scope of the appended claims.

What is claimed is:

1. A resistive switching device for a non-memory device, comprising:

- a substrate having a surface region;

- a first dielectric material overlying the surface region of the substrate;

- a first wiring material overlying the first dielectric material;

- a junction material comprising a p-doped silicon-bearing material overlying the first wiring material;

- one or more bottom wiring structures comprising the first wiring material and the junction material;

- a second dielectric material overlying the one or more bottom wiring structures;

- a plurality of stacks of material comprising a conductive material and a resistive switching material disposed within an opening structure of the second dielectric material, wherein the resistive switching material is in contact with a portion of the junction material, wherein the resistive switching material comprises an amorphous silicon-bearing material having an intrinsic semiconductor characteristic, and wherein the conductive material and the resistive switching material include respective sidewalls;

- a second wiring material overlying the plurality of stacks of material and the second dielectric material, wherein the second wiring material contacts the sidewalls of the conductive material, the sidewalls of the resistive switching material and the second dielectric material.

2. The device of claim 1 wherein the substrate comprises one or more transistor device formed thereon, the one or more transistor device comprising a controlling circuitry for the non-volatile memory device.

**3**. The device of claim **1** wherein the conductive material is selected from a group consisting of: silver, tungsten, aluminum, copper, gold, palladium, aluminum, platinum, copper, zinc, nickel, or combination thereof.

4. The device of claim 1 wherein the second wiring material further comprises a diffusion barrier layer material or an adhesion material.

5. The device of claim 1 wherein junction material is selected from a group consisting of: a p-doped polycrystalline silicon material, and a p-doped silicon germanium material.

6. The device of claim 1 wherein the amorphous siliconbearing material having an intrinsic semiconductor characteristic is selected from a group consisting of a non-intentionally doped amorphous silicon material, a silicon oxide.

7. The device of claim 6 wherein the amorphous siliconbearing material has a thickness selected from a range of about 3 nm to about 8 nm.

**8**. The device of claim **1** wherein the junction material comprises an etch stop.

**9**. The method of claim **1** wherein the sidewalls of the resistive switching material are substantially free from side wall contamination derived from the conductive material.

10. The method of claim 1 further comprising:

- one or more top wiring structures comprising the second wiring material, wherein the one or more top wiring structures extend in a first direction;

- wherein the one or more bottom wiring structures extend in a second direction; and

- wherein the first direction and the second direction are substantially orthogonal.

\* \* \* \* \*