US011893676B2

# (12) United States Patent Seiler

# (10) Patent No.: US 11,893,676 B2

# (45) **Date of Patent:** Feb. 6, 2024

## (54) PARALLEL TEXTURE SAMPLING

# (71) Applicant: META PLATFORMS

TECHNOLOGIES, LLC, Menlo Park,

CA (US)

(72) Inventor: Larry Seiler, Redmond, WA (US)

(73) Assignee: Meta Platforms Technologies, LLC,

Menlo Park, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 108 days.

(21) Appl. No.: 17/562,723

(22) Filed: Dec. 27, 2021

## (65) Prior Publication Data

US 2022/0180590 A1 Jun. 9, 2022

## Related U.S. Application Data

- (63) Continuation of application No. 16/591,520, filed on Oct. 2, 2019, now Pat. No. 11,244,492.

- (60) Provisional application No. 62/755,281, filed on Nov. 2, 2018.

- (51) Int. Cl. *G06T 15/04* (2011.01) *G06T 15/08* (2011.01)

- (52) U.S. Cl. CPC ...... *G06T 15/04* (2013.01); *G06T 15/08* (2013.01)

# (58) Field of Classification Search

None

See application file for complete search history.

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 6,563,507    | B1* | 5/2003  | Ito G06T 15/005       |

|--------------|-----|---------|-----------------------|

|              |     |         | 345/569               |

| 2003/0169265 | A1* | 9/2003  | Emberling G06T 15/04  |

|              |     |         | 345/582               |

| 2003/0174136 | A1* | 9/2003  | Emberling G06T 11/40  |

|              |     |         | 345/531               |

| 2006/0125834 | A1* | 6/2006  | Chung G06T 1/60       |

|              |     |         | 345/552               |

| 2006/0164429 | A1* | 7/2006  | Mantor G06T 1/60      |

|              |     |         | 345/582               |

| 2006/0290707 | A1* | 12/2006 | Pallister G06T 15/005 |

|              |     |         | 345/582               |

| 2009/0289949 | A1* | 11/2009 | Buchner G06T 11/001   |

|              |     |         | 345/582               |

|              |     |         | 5 15/502              |

(Continued)

## FOREIGN PATENT DOCUMENTS

JP 2015200915 A 11/2015

Primary Examiner — Andrew G Yang

(74) Attachment Agent on Firm Pelcer Potts

(74) Attorney, Agent, or Firm — Baker Botts L.L.P.

## (57) ABSTRACT

In one embodiment, a computing system may store, by first buffer blocks, texels organized into a texel array including a number of N×N texel sub-arrays. Each texel may fall within a corresponding N×N texel sub-array and may be associated with a two-dimensional sub-array coordinate indicating a position of that texel within the corresponding N×N texel sub-array. Each first buffer block of may be assigned a particular two-dimensional sub-array coordinate and stores a texel subset having the particular two-dimensional sub-array coordinate. The system may receive, by filter blocks, texels from the first buffer blocks. Each filter block may receive a texel from each first buffer block to form a corresponding N×N texel sub-array. The system may perform, by filter blocks, sampling operations parallelly on their respective N×N texel sub-arrays.

# 20 Claims, 26 Drawing Sheets

# **US 11,893,676 B2**Page 2

#### (56) **References Cited**

# U.S. PATENT DOCUMENTS

| 2012/0281915 A1* | 11/2012 | Strom | H04N 19/182                       |

|------------------|---------|-------|-----------------------------------|

| 2016/0078666 A1* | 3/2016  | Park  | 382/233<br>G06T 15/005<br>345/426 |

<sup>\*</sup> cited by examiner

FIG. 1B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 84

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Quad Buffer Block A $(0,0)$ $\bigcap$ Quad Buffer Block B $(1,0)$ Quad Buffer Block C $(0,1)$ Quad Buffer Block D $(1,1)$ 1102 | A2 A3 A4 B1 B2 B3 B4 C1 C2 C3 C4 D1 D2 D3 D4 | A6         A7         A8         B5         B6         B7         B8         C5         C6         C7         C8         D5         D6         D7         D8 | A10         A11         A12         B9         B10         B11         B12         C9         C10         C11         C12         D9         D10         D11         D12 | A14 A15 A16 B13 B14 B15 B16 C13 C14 C15 C16 D13 D14 D15 D16 | <b>→</b> | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Texel Buffer Block $(0, 1)$ Block | Block (1, 1) B6 B8 Texel Buffer C6 C8 Texel Buffer D6 D8 Block (1, 1) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|--------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | iffer Blc<br>1102                                                                                                              | <b></b>                                      | <del> </del>                                                                                                                                                 |                                                                                                                                                                          | 15 A10                                                      |          | Texel  <br>Block<br>112                                | Texel<br>Block<br>112                                  | Texel<br>Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Texel<br>Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ıad Bu                                                                                                                         |                                              |                                                                                                                                                              |                                                                                                                                                                          | 14 A                                                        | -        |                                                        | $\subseteq$                                            | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A13 A5 A A10 A10 A A13 A | n<br>On                                                                                                                        | A1 A                                         | A5 A(                                                                                                                                                        | A9 A1                                                                                                                                                                    | A13 A1                                                      |          | A3                                                     |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A6 A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

FIG. 8F

FIG. 10

0 0 0 0 0 × Alpha4Lo Alpha4Hi Alpha4 Index4 7 2 0  $\alpha$ Data Formats in Buffer Memory  $\alpha$  $\mathfrak{C}$  $\mathfrak{C}$  $\mathfrak{C}$  $\alpha$ Color10 4 4 4 4 4 Alpha8 S S S S 5 Distance6 Color6Lo Color6Hi Color6 9 9 9 9 9 \_  $\infty$  $\infty$  $\infty$  $\infty$  $\infty$ 6 6 6 6 6 10 10 10 10 10 Mode Mode Mode Mode  $\bowtie$ 11 11 Texel Format Texel Format Texel Format Texel Format Texel Format 1210 1212 1214 1211

FIG. 12B

FIG. 12C

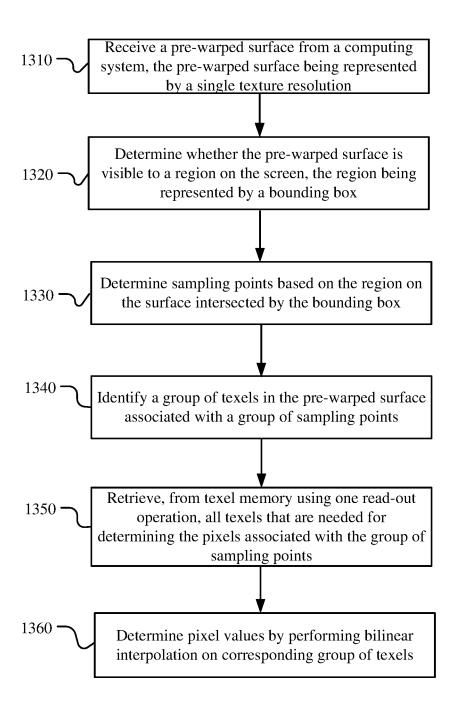

# **1300**

FIG. 13

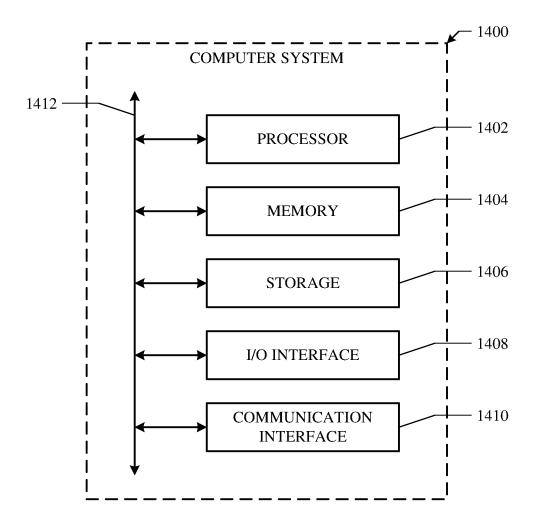

FIG. 14

# PARALLEL TEXTURE SAMPLING

#### **PRIORITY**

This application is a continuation under 35 U.S.C. § 120 <sup>5</sup> of U.S. patent application Ser. No. 16/591,520, filed 2 Oct. 2019, which claims the benefit under 35 U.S.C. § 119(e) of U.S. Provisional Patent Application No. 62/755,281, filed 2 Nov. 2018, which is incorporated herein by reference.

### TECHNICAL FIELD

This disclosure generally relates to artificial reality, such as virtual reality and augmented reality.

# BACKGROUND

Artificial reality is a form of reality that has been adjusted in some manner before presentation to a user, which may include, e.g., a virtual reality (VR), an augmented reality (AR), a mixed reality (MR), a hybrid reality, or some combination and/or derivatives thereof. Artificial reality content may include completely generated content or generated content combined with captured content (e.g., real-25 world photographs). The artificial reality content may include video, audio, haptic feedback, or some combination thereof, and any of which may be presented in a single channel or in multiple channels (such as stereo video that produces a three-dimensional effect to the viewer). Artificial 30 reality may be associated with applications, products, accessories, services, or some combination thereof, that are, e.g., used to create content in an artificial reality and/or used in (e.g., perform activities in) an artificial reality. The artificial reality system that provides the artificial reality content may 35 be implemented on various platforms, including a headmounted display (HMD) connected to a host computer system, a standalone HMD, a mobile device or computing system, or any other hardware platform capable of providing artificial reality content to one or more viewers.

# SUMMARY OF PARTICULAR EMBODIMENTS

Particular embodiments described herein relate to a method of rendering artificial reality objects using pre- 45 warped surfaces as the rendering primitives, and parallelly retrieving all the texels that are needed to determine the properties (e.g., colors or distance fields) of a set of pixel samples (e.g., a 2×2 set of pixels) within a tile (e.g., a collection of pixels, such as 16×16 pixels, defined by its four 50 corners) in one operation. The system may generate prewarped surfaces on one or more CPUs/GPUs associated with a computing system (e.g., a body wearable computing system, such as a mobile phone, or a laptop, desktop, etc.). The pre-warped surfaces may be generated based on the 55 rendering results of the CPU(s)/GPU(s), such as a 2D image that visually take into account the 3D contour of the underlying object. The pre-warped surfaces may be generated with particular shape, size, orientation based on a viewpoint (e.g., view distance, view angle) of a viewer. The 2D image 60 may be stored as the texture data of the surface. The surface may be considered as a flat planar canvas for the 2D texture and is positioned in 3D view space facing the viewer (e.g., with a normal vector substantially pointing towards the viewer). As a result, the pre-warped texture data of the 65 surface may be represented by a single mipmap level instead of multiple texture mipmap levels.

2

A headset system may receive the pre-warped surfaces from the body wearable computing system and render the surfaces on a head mounted display by transforming the pre-warped surfaces. Visibility of pre-warped surfaces may be tested by projecting rays from a viewer's screen. In particular embodiments, the rays may be cast from a number of tiles (e.g., an aligned block of 16×16 pixels), each of which may be defined by its four corner positions in screen space. Once it is determined that a particular surface is visible from a tile, colors for pixels within the tile may be sampled from the texture of the surface. In particular embodiments, pixel sampling may be performed concurrently for four aligned 2×2 pixels. The system may restrict minification by zooming out operations to be within a 15 two-time range. With this constraint, the 2×2 sampling points may always fall within a 4×4 texels region. In particular embodiments, the system may use a multi-level memory architecture including 16 independent texel buffer blocks for texel buffer. The system may use a pre-determined texel storage pattern to store 4×4 texels regions in the 16 independent quad buffer blocks that can be addressed separately and can be readout parallelly (e.g., in one operation). Therefore, the system may access the 4x4 texels region in one read operation and parallelly sample all the texels that are needed to determine the four pixels values (rather than sequentially access four quads). Since the prewarped surfaces are generated based on one texture mipmap level, the headset system may only need to access single texture mipmap and use bilinear interpolation instead of trilinear interpolation, which would require reading another set of texel data from a different mipmap level, to determine the pixels values.

In an embodiment, a method may comprise, by a computing system:

receiving a plurality of texels organized into a texel array comprising a plurality of sub-arrays;

determining a plurality of texel subsets, wherein the texels in each subset have a same position within their respective sub-arrays;

storing the plurality of texel subsets into a plurality of buffer blocks, respectively, wherein each buffer block stores one texel subset of the plurality of texel subsets; and

retrieving a sampling texel array from the plurality of buffer blocks for parallelly determining pixel values of a plurality of sampling points, wherein each texel of the sampling texel array is retrieved from a different buffer block of the plurality of buffer blocks.

The plurality of sub-arrays may form a repeated pattern within the texel array.

Each of the plurality of buffer blocks may be addressed separately and accessed parallelly.

The plurality of buffer blocks may be grouped into a plurality of groups, and each texel used for determining a pixel value of a sampling point may be retrieved from a different group of the plurality of groups.

In one embodiment, the plurality of texel subsets may be determined by:

determining a reference texel having a first coordinate (u, v) indicating a position of the reference texel within the texel array;

determining a plurality of intermediate texel groups comprising texels having least significant bits of binary representations of first coordinates (u, v) equal to (0, 0), (1, 0), (0, 1), and (1, 1), respectively;

determining a second coordinate (x, y) for each texel of each intermediate texel group; and

determining the plurality of texel subsets each comprising texels having least significant bits of binary representations of second coordinates (x, y) equal to (0, 0), (1, 0), (0, 1), and (1, 1) with respect to a corresponding intermediate texel group.

The plurality of texel subsets may comprise 16 texel subsets, and the plurality of buffer blocks may comprise 16 buffer blocks.

The 16 texel subsets may be organized into four texel groups. The plurality of sampling points may comprise four 10 sampling points, and the four texel groups may be used for parallelly determining the pixels values of the four sampling points, respectively.

Each pixel value may be determined based on a 2×2 texel sub-array of the sampling texel array, and each texel of the 15 2×2 texel sub-array may be selected from one of the four texel groups.

The plurality of sampling points may be associated with an intersection area of a display region to a two-dimensional representation of a portion of a scene.

The two-dimensional representation may comprise threedimensional information of the portion of the scene, and the two-dimensional representation of the portion of the scene may be visible in the display region.

The two-dimensional representation of the portion of the 25 scene may be represented with a single texture resolution, and the texel array may comprise texels having the single texture resolution.

The sampling texel array may be associated with an aligned texel region or an unaligned texel region.

In one embodiment, one or more computer-readable nontransitory storage media may embody software that is operable when executed to:

receive a plurality of texels organized into a texel array comprising a plurality of sub-arrays;

determine a plurality of texel subsets, wherein the texels in each subset have a same position within their respective sub-arrays:

store the plurality of texel subsets into a plurality of buffer blocks, respectively, wherein each buffer block stores 40 one texel subset of the plurality of texel subsets; and

retrieve a sampling texel array from the plurality of buffer blocks for parallelly determining pixel values of a plurality of sampling points, wherein each texel of the sampling texel array is retrieved from a different buffer 45 block of the plurality of buffer blocks.

The plurality of sub-arrays may form a repeated pattern within the texel array.

Each of the plurality of buffer blocks is addressed separately and accessed parallelly.

The plurality of buffer blocks may be grouped into a plurality of groups, and each texel used for determining a pixel value of a sampling point may be retrieved from a different group of the plurality of groups.

In one embodiment, a system may comprise: one or more 55 processors; and one or more computer-readable non-transitory storage media coupled to one or more of the processors and comprising instructions operable when executed by one or more of the processors to cause the system to:

receive a plurality of texels organized into a texel array 60 comprising a plurality of sub-arrays;

determine a plurality of texel subsets, wherein the texels in each subset have a same position within their respective sub-arrays;

store the plurality of texel subsets into a plurality of buffer 65 blocks, respectively, wherein each buffer block stores one texel subset of the plurality of texel subsets; and

4

retrieve a sampling texel array from the plurality of buffer blocks for parallelly determining pixel values of a plurality of sampling points, wherein each texel of the sampling texel array is retrieved from a different buffer block of the plurality of buffer blocks.

The plurality of sub-arrays may form a repeated pattern within the texel array.

Each of the plurality of buffer blocks may be addressed separately and accessed parallelly.

The plurality of buffer blocks may be grouped into a plurality of groups, and each texel used for determining a pixel value of a sampling point may be retrieved from a different group of the plurality of groups.

In an embodiment, one or more computer-readable nontransitory storage media may embody software that is operable when executed to perform a method according to or within any of the above mentioned embodiments.

In an embodiment, a system may comprise: one or more processors; and at least one memory coupled to the processors and comprising instructions executable by the processors, the processors operable when executing the instructions to perform a method according to or within any of the above mentioned embodiments.

In an embodiment, a computer program product, preferably comprising a computer-readable non-transitory storage media, may be operable when executed on a data processing system to perform a method according to or within any of the above mentioned embodiments

The embodiments disclosed herein are only examples, and the scope of this disclosure is not limited to them. Particular embodiments may include all, some, or none of the components, elements, features, functions, operations, or steps of the embodiments disclosed above. Embodiments according to the invention are in particular disclosed in the attached claims directed to a method, a storage medium, a system and a computer program product, wherein any feature mentioned in one claim category, e.g. method, can be claimed in another claim category, e.g. system, as well. The dependencies or references back in the attached claims are chosen for formal reasons only. However, any subject matter resulting from a deliberate reference back to any previous claims (in particular multiple dependencies) can be claimed as well, so that any combination of claims and the features thereof are disclosed and can be claimed regardless of the dependencies chosen in the attached claims. The subjectmatter which can be claimed comprises not only the combinations of features as set out in the attached claims but also any other combination of features in the claims, wherein each feature mentioned in the claims can be combined with any other feature or combination of other features in the claims. Furthermore, any of the embodiments and features described or depicted herein can be claimed in a separate claim and/or in any combination with any embodiment or feature described or depicted herein or with any of the features of the attached claims.

## BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1A illustrates an example artificial reality system.

FIG. 1B illustrates an example eye display system of the headset system.

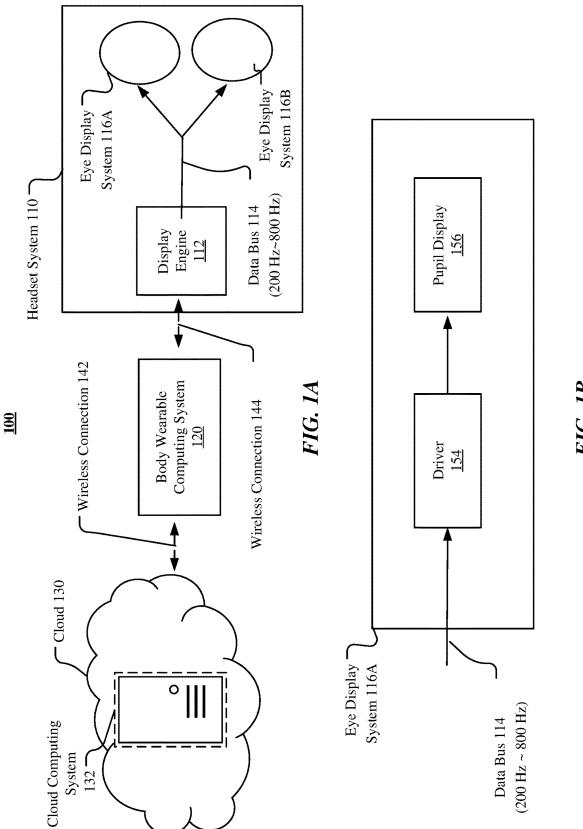

FIG. 2 illustrates an example 3D object.

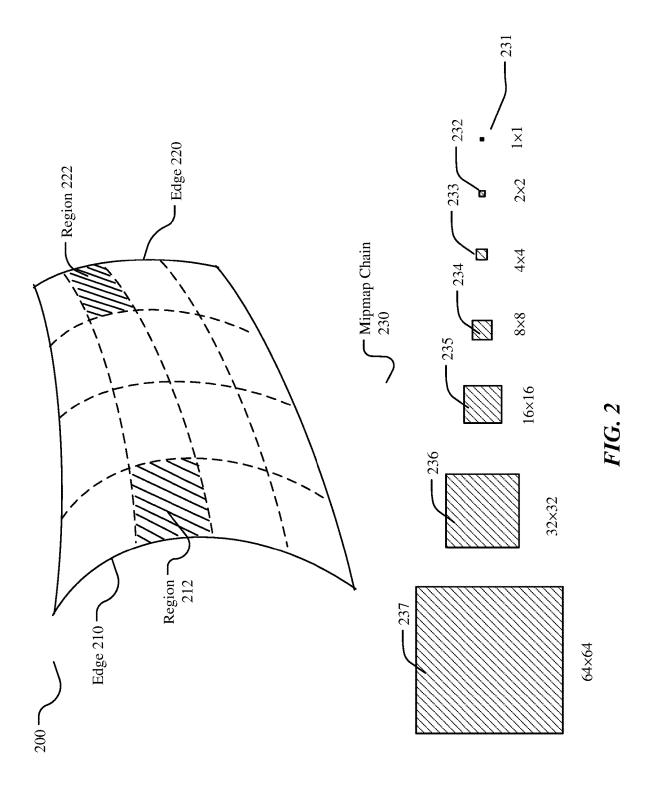

FIG. 3 illustrates an example pre-warped surface generated on a body wearable computing system.

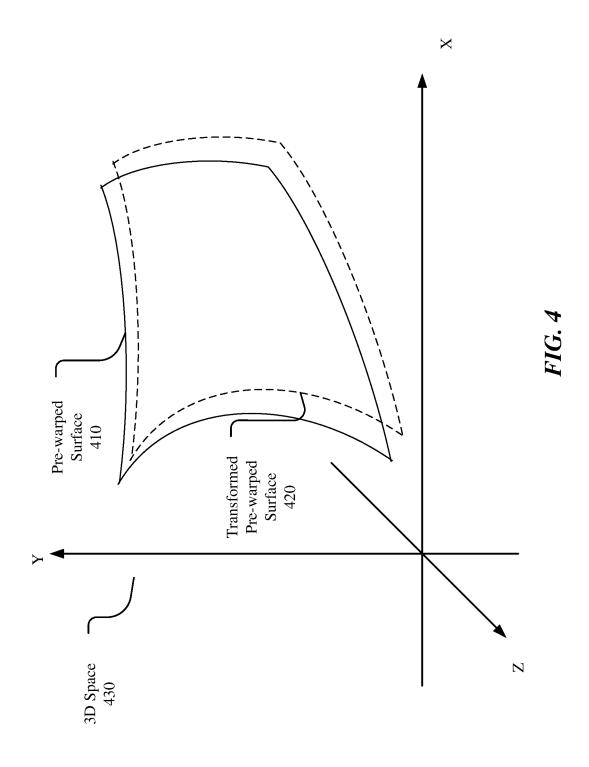

FIG. 4 illustrates an example pre-warped surface which appears transformed by the headset system for rendering on eye display systems.

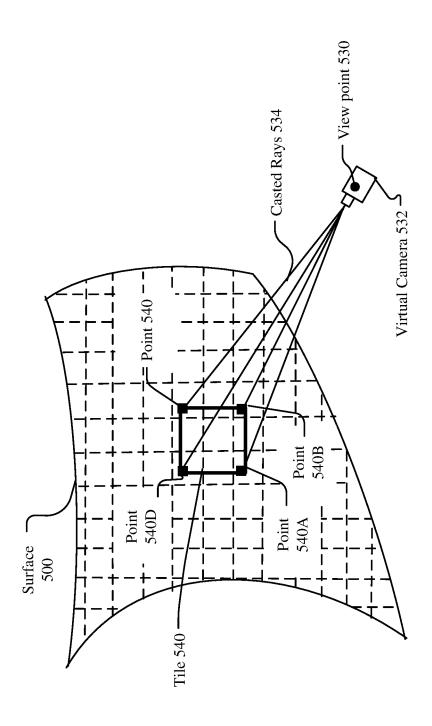

FIG. 5 illustrates an example pre-warped surface that is visible through an example tile.

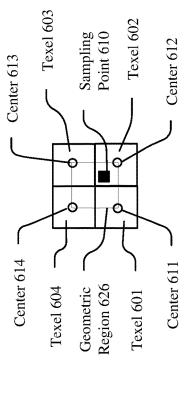

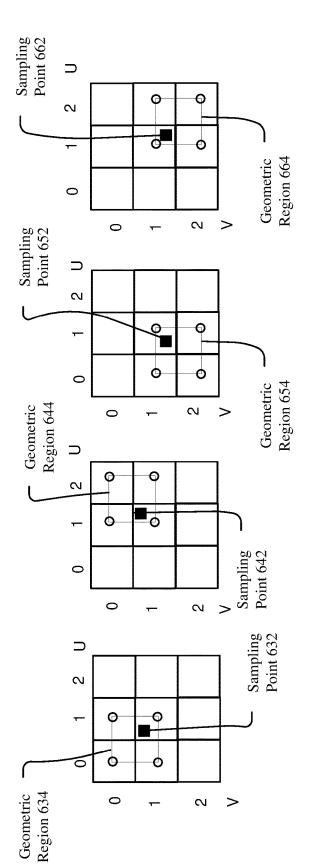

FIGS. 6A-B illustrate an example process for determining the texels that are needed for determining the color or distance field of a sampling point.

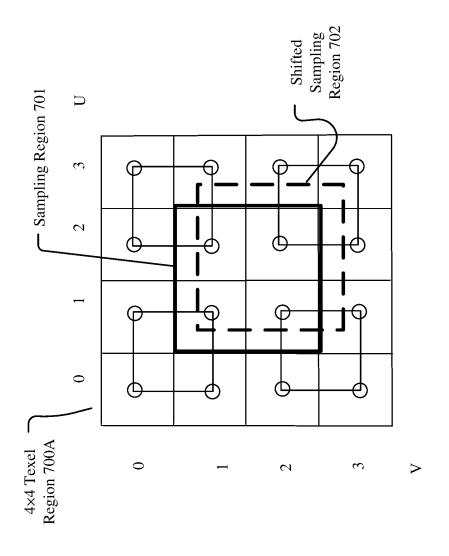

FIG. 7A illustrates an example 4×4 texel region and an example sampling region that represents a set of 2×2 orthogonal sampling points located at the four corners of the sampling region.

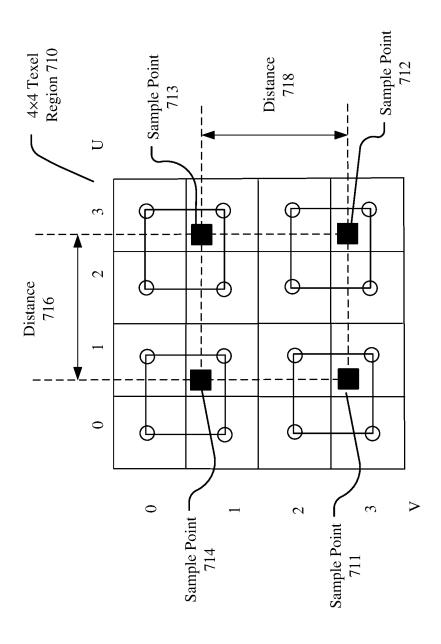

FIG. 7B illustrates example 2×2 orthogonal sampling 10 points within an aligned 4×4 texel region.

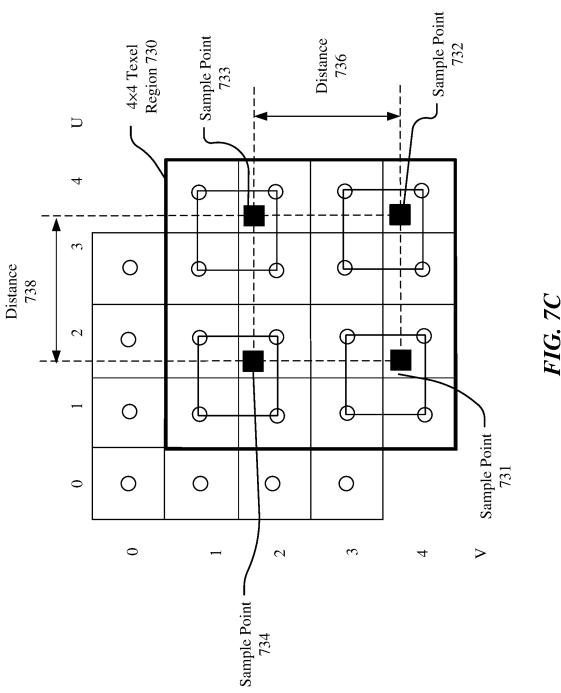

FIG. 7C illustrates example 2×2 orthogonal sampling points within an unaligned 4×4 texel region.

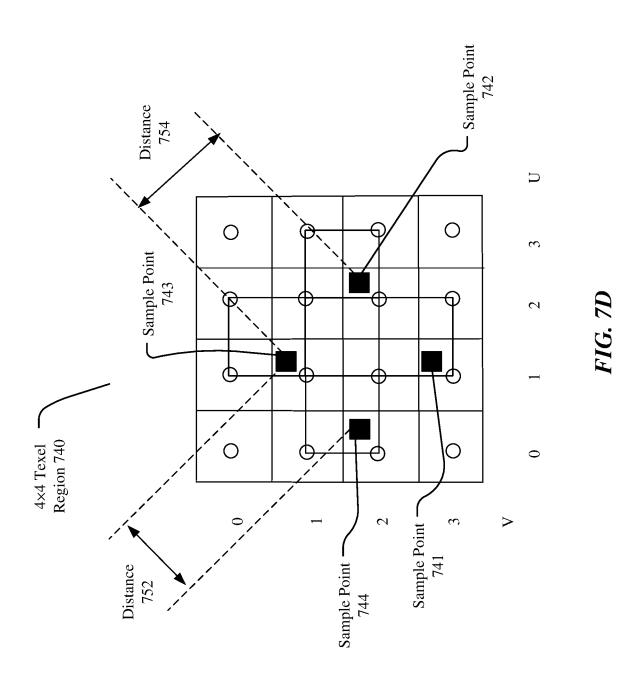

FIG. 7D illustrates example 2×2 non-orthogonal sampling points within a 4×4 texel region.

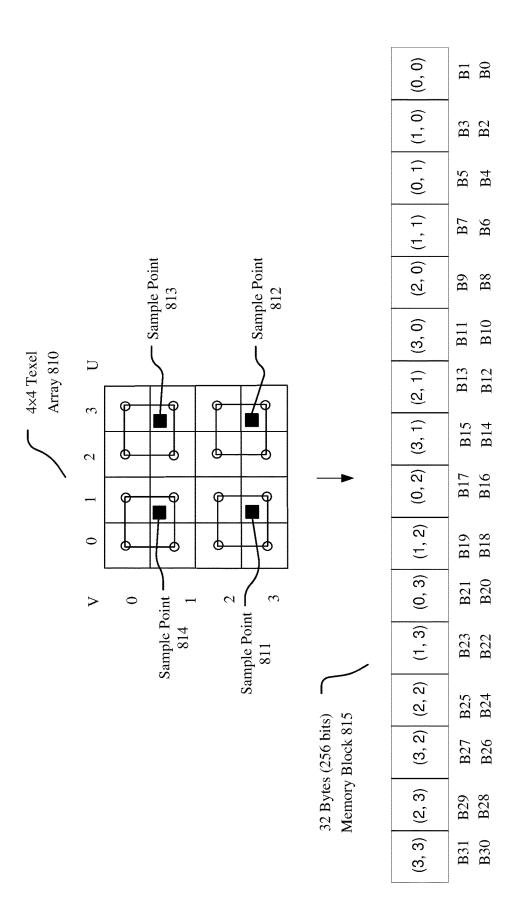

FIG. 8A illustrates an example 4×4 texel array stored in a 32 bytes texel memory of control block with an interleaved pattern.

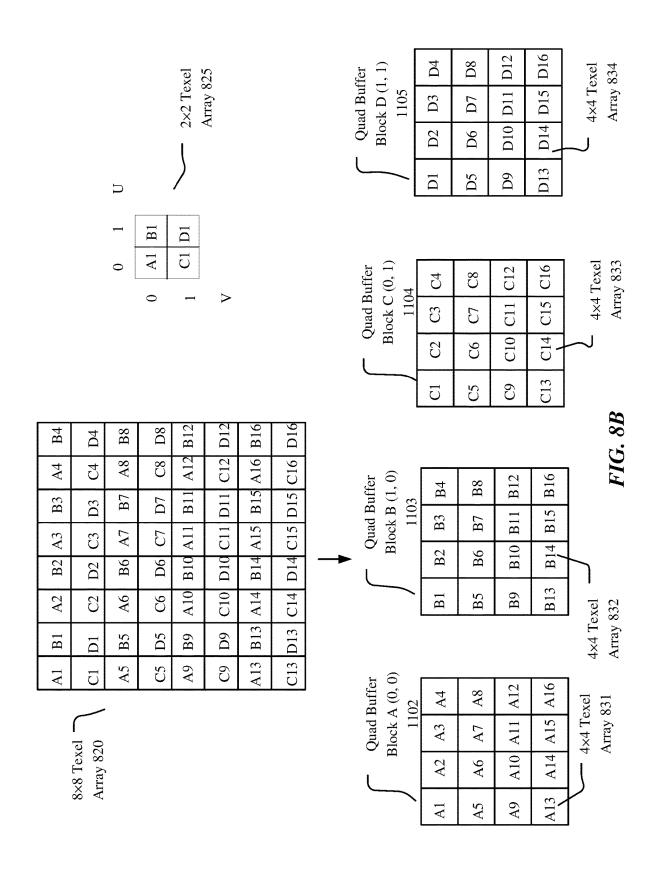

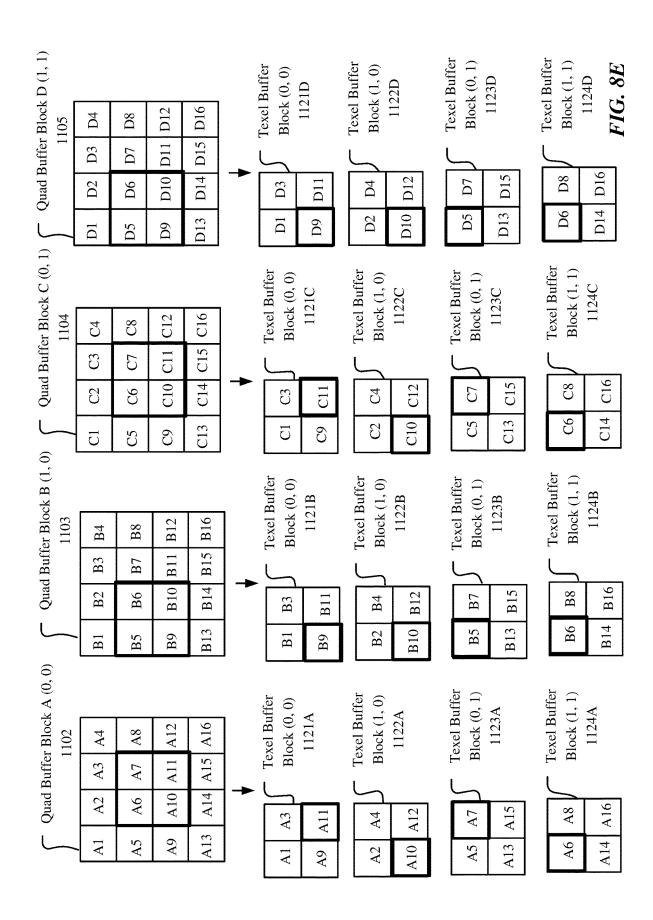

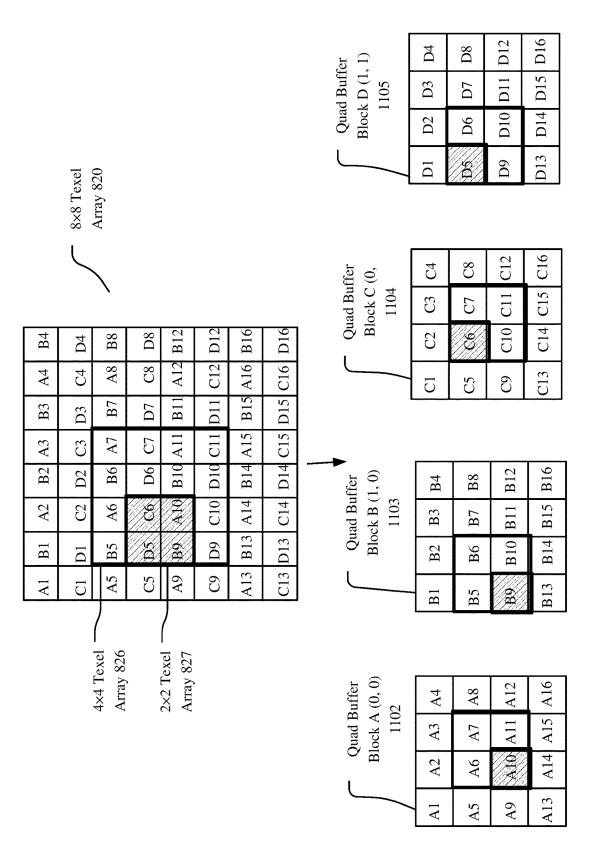

FIGS. **8**B-C illustrate an example 8×8 texel array stored in 16 independent texel buffer blocks to allow any 4×4 texel <sup>20</sup> array to be read in one read operation.

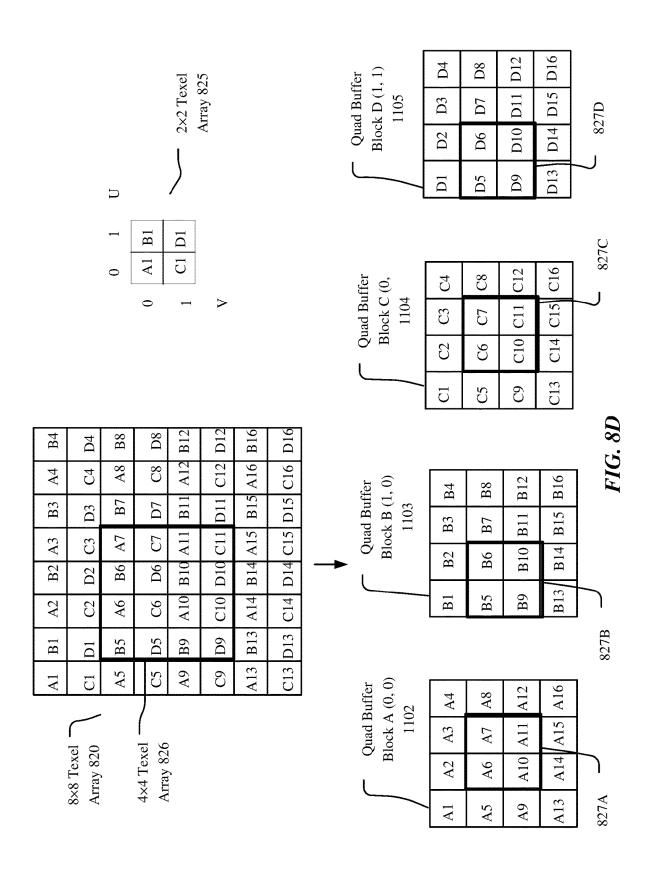

FIGS. **8**D-E illustrate an example 4×4 texel array selected from an 8×8 texel array stored in 16 independent texel buffer blocks.

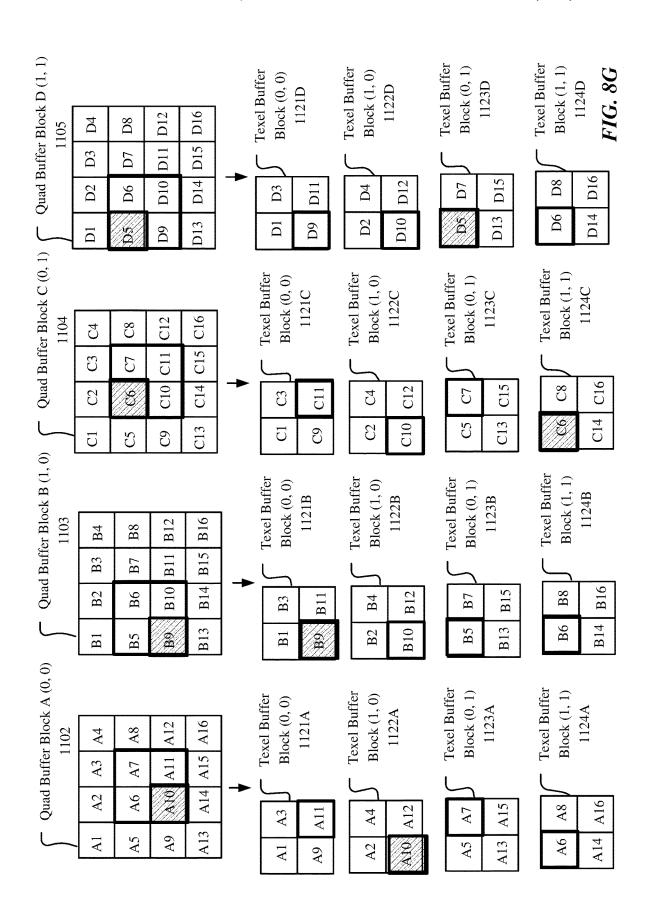

FIGS. **8**F-G illustrate an example 2×2 texel array which <sup>25</sup> is selected from an 8×8 texel array stored in 16 independent texel buffer blocks and can be read from the texel buffer with reduced multiplexing operations.

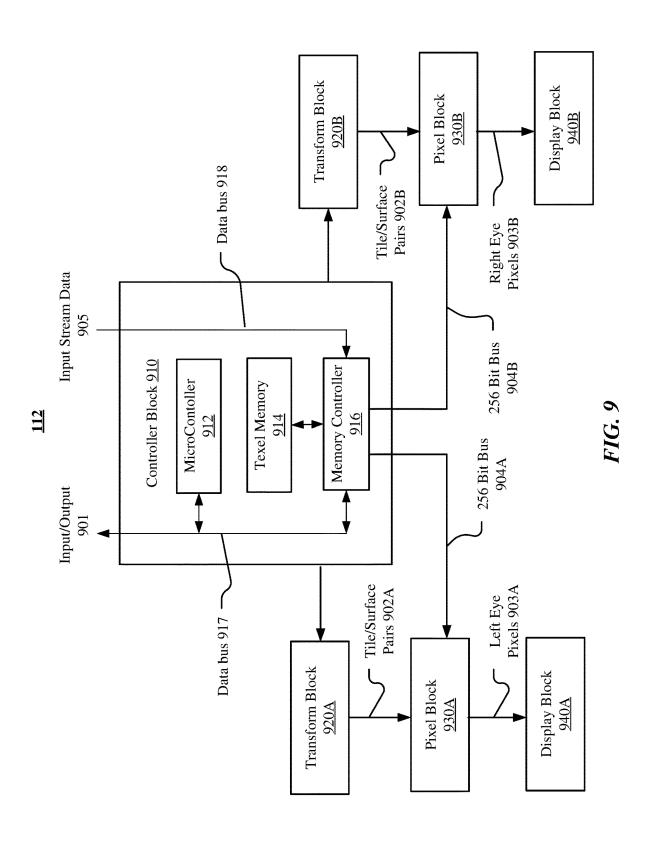

FIG. 9 illustrates a system diagram for a display engine.

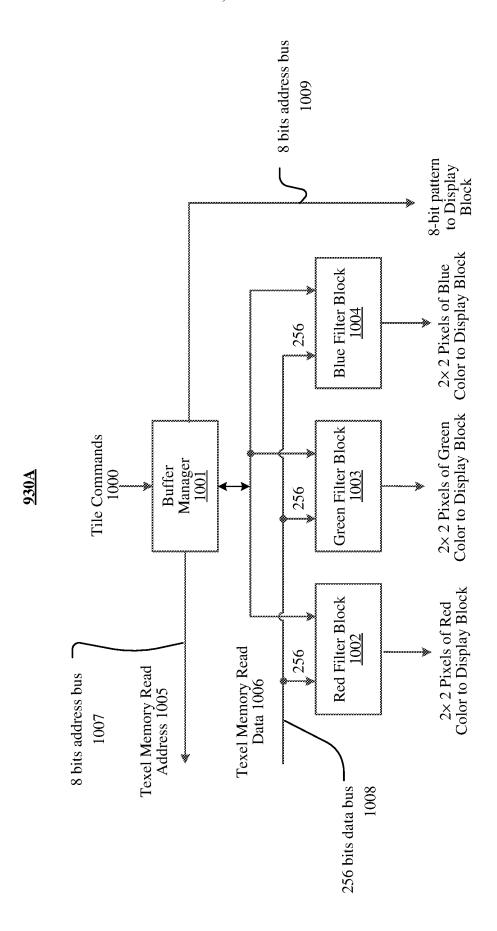

FIG. 10 illustrates an example diagram for pixel block.

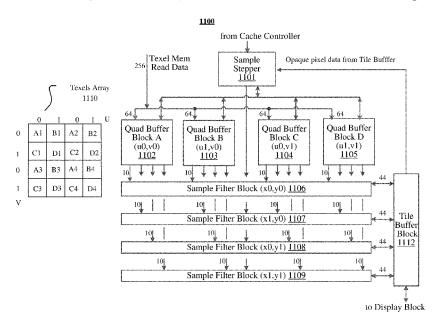

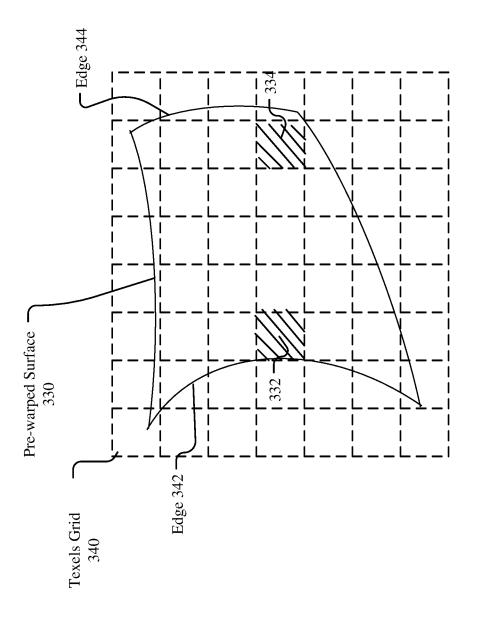

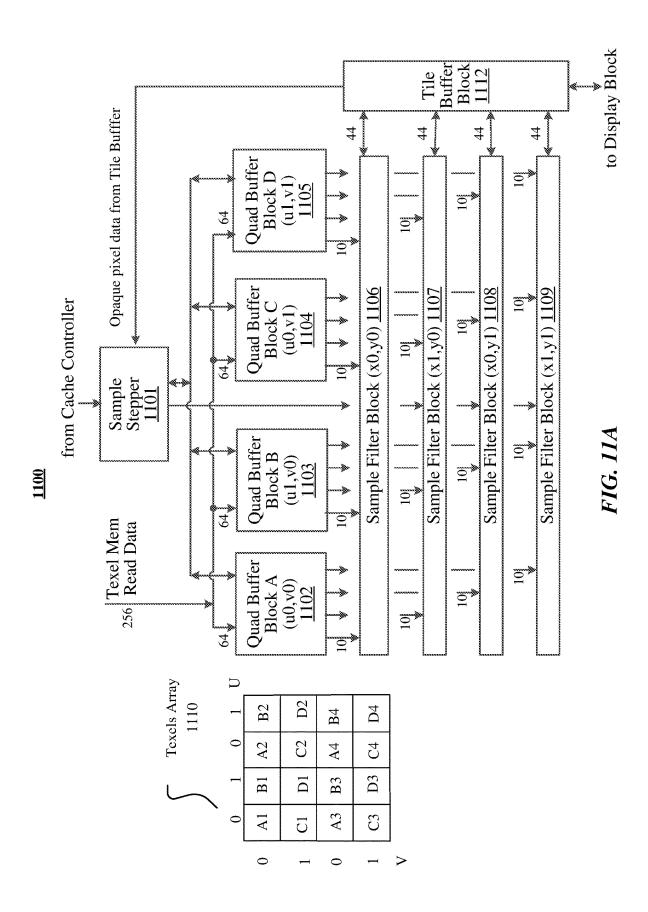

FIG. 11A illustrates an example diagram for filter block including four quad buffer blocks.

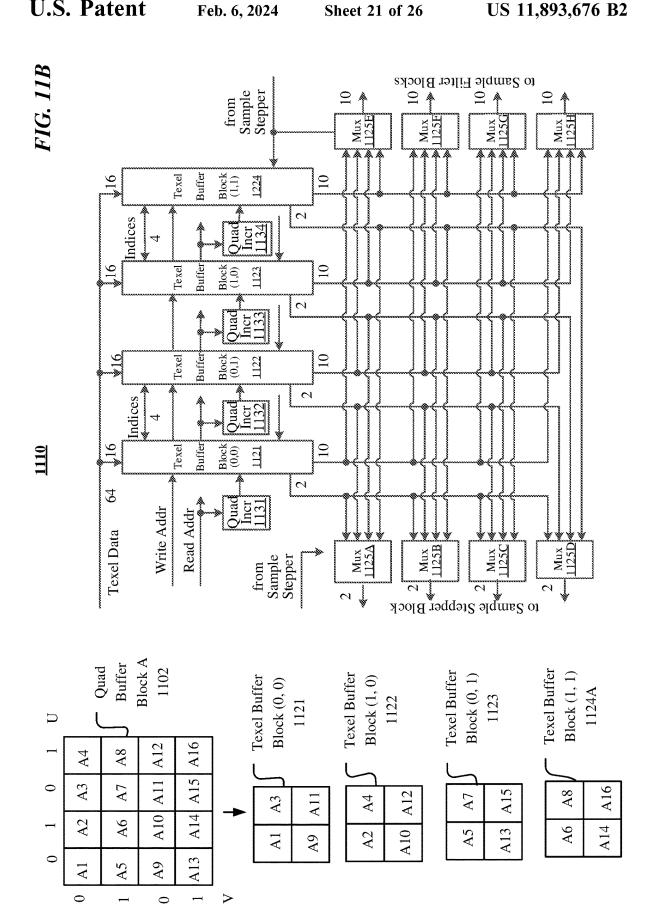

FIG. 11B illustrates an example diagram for quad buffer block including four texel buffer blocks.

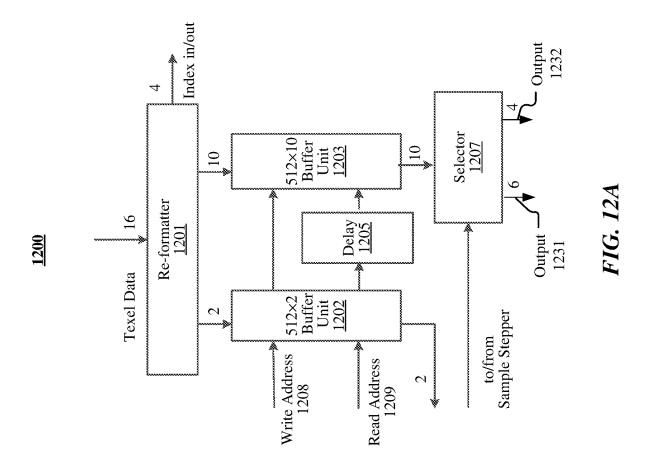

FIG. 12A illustrates an example diagram for texel buffer <sup>35</sup> block.

FIG. 12B illustrates example data formats for texel data stored in texel buffer blocks.

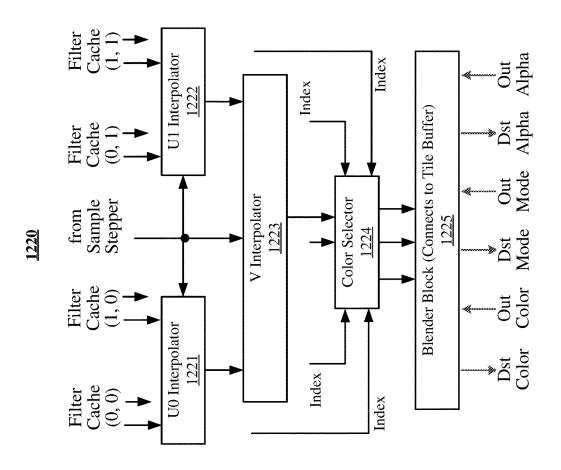

FIG.  $12\mathrm{C}$  illustrates an example diagram for sample filter block.

FIG. 13 illustrates an example method of parallelly sampling multiple groups of texels to determine multiple pixel values using bilinear interpolation.

FIG. 14 illustrates an example computer system.

## DESCRIPTION OF EXAMPLE EMBODIMENTS

Traditional graphics rendering systems may need to perform separate read operations to obtain the necessary texel data from a texture to determine the color (for images) or 50 distance field (for labels, such as fonts, characters, glyphs, etc.) for a single pixel. During a sampling process, traditional rendering pipelines implemented on traditional GPUs access texel buffer memory in quads when performing bilinear interpolation to determine the pixel value (e.g., 55 color/distance field). For example, traditional GPUs may need to perform four separate read operations to retrieve the four closest texels, relative to the sample location, that are needed to perform filtering (e.g., via bilinear interpolation). Such memory-access operations are slow and consume more 60 power. In addition, if multiple pixel samples are being filtered concurrently, different sampling locations may require texels from different texture mipmap levels, further adding to memory-access time. For example, if a virtual box is drastically slanted relative to the viewer, the portion of the 65 box that is closer to the viewer may use a high-resolution mipmap texture than the portion of the box that is farer away

6

from the viewer. Similarly, if the viewer zooms out from the box, more texels may need to be retrieved or the system may need to switch to a coarser mipmap level. Such operations, especially when performed in large volume, significantly adds to the overall rendering time, power consumption, and complexity of the system.

The problems described above may be largely eliminated by particular embodiments of a display engine that is designed to process or adjust pre-warped surfaces. These surfaces may be the primitives on which the display engine operates, rather than 3D model polygons from which traditional computer graphics are rendered. A "surface" may comprise 2D texture data, made up of texels, and 3D position data (e.g., distance, angle, or/and coordinates as specified in the viewer's view-space coordinates). In particular embodiments, a surface may be represented as a flat, planar canvas, placed in a viewer's view space, on which the texture is mapped. Visibility of a surface may be computed using the 3D position data of the surface, and color or distance field determination for each pixel may be sampled from the texture data of the surface. The texture of a surface may be generated based on the 2D image rendered by a GPU (e.g., from a 3D model defined by polygons). As such, even if a surface appears to show a 3D object, the surface is, in fact, a flat surface. A surface, therefore, can be considered as having been pre-warped based on the viewer's viewpoint when the surface is generated. Moreover, the normal vector of the surface may substantially point towards the viewer, even if the viewer moved slightly since the time when the surface was generated (e.g., the viewer is unlikely to have moved significantly between frames or 1/60 of a second). Since a surface is pre-warped and facing the viewer, when the surface is being processed by the display engine to make inter-frame adjustments, the surface can be sampled using a single texture mipmap level (e.g., instead of multiple texture mipmap levels). In addition, particular embodiments of the system may restrict minification caused by zoom-out operations to be within a two-time range, which allows the four sampling points to always fall within a 4×4 texel region. Particular embodiments of the system may take advantage of this feature and configure a texel storage pattern in the texel buffer memory (e.g., quad buffer blocks including texel buffer blocks) to allow the 4×4 texel region to be stored in 45 a manner so that it can be read out in one read operation. Particular embodiments of the system may use a memory structure including a pre-determined number of memory blocks, which can be accessed parallelly with reduced multiplexing and bandwidth requirements.

Particular embodiments of the system provide faster and fewer memory reading to retrieve the texels that are need for determining pixel values, and reduce power consumption and operation logic that are needed to retrieve texels from texel buffer memory (e.g., quad buffer blocks including texel buffer blocks). Particular embodiments of the system reduce the amount of computation by the headset system for adjusting or transforming (e.g., conceptually, adjustments in position, orientation, and/or scale) a pre-warped surface to accommodate a viewer's changing viewpoints between frames. Particular embodiments of the system reduce the amount of computation and power consumption that are needed for reading the texels needed for filtering multiple pixel samples (e.g., 2×2 pixels), since the system confines any such group of samples to fall within a 4×4 texel region. Particular embodiments of the system provide a texel buffer hardware structure and texel data storage pattern that reduce the multiplexing operations on the headset system and

reduce the bandwidth usage on data bus when accessing the texel buffer memory (e.g., quad buffer blocks including texel

FIG. 1A illustrates an example artificial reality system **100**. In particular embodiments, the artificial reality system 5 100 may include a headset system 110, a body wearable computing system 120, a cloud computing system 132 in a cloud 130, etc. In particular embodiments, the headset system 110 may include a display engine 112 which is connected to two eye display systems 116A and 116B through a data bus 114. The headset system 110 may be a system including a head-mounted display (HMD) which may be mounted on a user's head to provide artificial reality to the user. The headset system 110 may have limited amount of power available in its power sources (e.g., bat- 15 teries). The display engine 112 may provide display data to the eye display systems 116A and 116B though the data bus 114 with relative high data rates (e.g., 200 Hz-800 Hz). As will be discussed later, the display engine 112 may include one or more controller blocks, texel memories, transform 20 blocks, pixel blocks, etc. The texels stored in the texel memories may be accessed by pixel blocks and may be provided to the eye display systems 116A and 116B for display.

system 120 may be worn on the body of a user. In particular embodiments, the body wearable computing system 120 may be a computing system (e.g., a laptop, a desktop, a mobile computing system) that is not worn on a user body. The body wearable computing system 120 may include one 30 or more GPUs, one or more smart video decoders, memories, processors, and other modules. The body wearable computing system 120 may have more computational resources than the display engine 112 but may still have limited amount power in its power sources (e.g., batteries). 35 The body wearable computing system 120 may be coupled with the headset system 110 through a wireless connection 144. The cloud computing system 132 may be high performance computers (e.g., servers) and may communicate with the body wearable computing system 120 through a wireless 40 connection 142. FIG. 1B illustrates an example eye display system (e.g., 116A or 116B) of the headset system 110. In particular embodiments, the eye display system 116A may include a driver 154, a pupil display 156, etc. The display engine 112 may provide display data to the pupil display 156 45 the data bus 114 and the driver 154 at high data rates (e.g., 200 Hz-800 Hz).

In traditional graphics-rendering systems, depending on how a 3D object(s) is oriented relative to a viewer, certain regions of the 3D objects would be closer to the viewer than 50 others. The distance discrepancy may lead to pixel sampling locations in different regions to require different mipmap levels for texture sampling. As an example, FIG. 2 illustrates an example 3D object 200. The object 200 may be oriented in a slanted orientation relative to the viewer, with edge 210 55 of the object 200 being relatively closer to the viewer than edge 220. As a result, sampling the color of a pixel that falls in the region 212 on the edge 210 may require a finer texture mipmap level relative to the coarser mipmap level that may be used to sample a pixel that falls in region 222 on the edge 60 220. For example, if the GPUs has access to multiple texture levels 231, 232, 233, 234, 235, 236, 237 in a mipmap chain 230, the GPU may use mipmap level 237 for pixels falling within region 212 and mipmap level 236 for pixels falling within region 222.

In addition, mipmap levels may need to change due to minification caused by zoom-out operations. In general, if a

zoom-out operation results in more than two-time zoom out on an object, the mipmap used for sampling may need to change in order to render a new scene. For example, if the viewer were to zoom out, resulting in the size of each texel in those mipmap levels 237, 236 to become smaller relative to the pixel sample size, the GPU may change the mipmap levels used. For example, after zooming out, the GPU may use mipmap level 236 for pixel samples falling in region 212 and mipmap level 235 for pixel samples falling in region 222

Unfortunately, reading texture data out of texel buffer memory takes time and power. As such, the aforementioned scenarios where mipmap switching can be costly and unsuitable in applications where frames are expected to be output at a very high rate, such as 200-800 frames per second. In particular embodiments where a display engine resides on an AR/VR headset system, computational resources and available power (e.g., powered by one or more batteries) may be especially limited. These limitations on computational resources and available power may become prohibitive for a headset system to meet the demands of the application (e.g., rendering AR/VR scenes that are responsive to user movements).

Particular embodiments of the system address the afore-In particular embodiments, the body wearable computing 25 mentioned problems by generating (e.g., at 60 hertz frame rate) pre-warped surfaces on the GPUs of body wearable computing system and allow the headset system to postwarp or re-sample the pre-warped surfaces (e.g., at 200 or more hertz) to adjust for changes in the viewer's perspective between frames. In addition to generating pre-warped surfaces, particular embodiments may further limit zoom-out operations to no more than 2x zoom out. As will be explained in further detail below, doing so would ensure that the texels needed for sampling four 2×2 pixels are confined to a 4×4 texel region. This enables the display engine to configure how texels are written and read so that a 4×4 texel region can be access using a single read operation.

> FIG. 3 illustrates an example pre-warped surface 330 generated on a body wearable computing system. In particular embodiments, the body wearable computing system may include one or more GPUs or/and smart video decoders. In particular embodiments, the pre-warped surfaces may be generated one or more GPUs on the body wearable computing system. In particular embodiments, the pre-warped surfaces may be generated by one or more video decoders on the body wearable computing system. For example, the GPUs on the body wearable computing system may render a 2D view of the 3D object 200 shown in FIG. 2. The 2D object 200 may be defined using a large number of polygons or triangles (e.g., hundreds or thousands of polygons), and the body wearable computing system may render the 2D view using a traditional graphics-rendering pipeline (e.g., using ray tracing and shading). Although this rendering process could be very expensive computationally, the body wearable computing system may have more computational resources (e.g., more powerful processors, more memory space) and more available power (e.g., larger battery capacity, direct plugin to a power outlet, etc.) than the headset system. As such, the 2D view of the 3D object 200 may be rendered at the rate of, for example, 30-60 hertz.

> In particular embodiments, the 2D view of the 3D object 200 may be used to generate the pre-warped surface 330. Although the pre-warped surface 330 is represented in 2D, it may appear 3D from the viewpoint of the viewer when the 2D view of rendered. For example, the edge 342 of the surface 330 may appear closer to the viewpoint, and the edge 344 may appear to be farer from the viewpoint. Despite its

3D appearance, the texture of the pre-warped surface 330 is 2D, as if the surface is a flat canvas on which the 2D image is mapped. The pre-warped surface 330 may have a defined position within 3D view space relative to a viewpoint. Different regions of the pre-warped surface 330 may be 5 substantially equal distance from the viewpoint. For example, the regions corresponding to texels 332 and 334 may be substantially equal distance from the viewpoint in 3D view space, yet the corresponding regions 212 and 222 on the 3D model 200 are different distances away from the 10 viewpoint when the 2D view of the 3D object 200 was rendered.

In particular embodiments, the 2D appearance of the pre-warped surface 330 may be stored as a texture with a uniform texel grid 340. Unlike the corresponding 3D model 15 200, the pre-warped surface 330 is substantially equal distance from the viewpoint, even though the relative depth of regions such as 332 and 334 may appear to be different. As such, any pixel sampling on the pre-warped surface 330 may be performed using the same mipmap level texture, rather 20 than different mipmap levels for different portions of the surface. For example, although the edge 342 may appear closer to the viewer than the edge 344, the texels corresponding to regions 332 and 334 may correspond to the same texture level or texture resolution.

The headset system may receive the pre-warped surface from the body wearable computing system through a wireless or wired communication connection. In particular embodiments, the headset system may receive the prewarped surface at the start of a frame. Between then and the 30 next frame (e.g., in 1/60 second intervals), the headset system may warp or re-sample the pre-warped surface based on the current head position or eye gaze of the user (as determined based on the inertial measurement unit and/or eye tracking device of the headset) at a much higher frame rate (e.g., 200 35 or more hertz). In this manner, the headset system may avoid the expensive computation that is needed in generating the pre-warped surfaces from the 3D model defined using polygons, and instead be tasked with providing dynamic, real-time updates to the pre-warped surface, which may be 40 significantly fewer in number than the polygons.

FIG. 4 illustrates an example pre-warped surface 410 which appears transformed by the headset system for rendering on eye display systems. In particular embodiments, the headset system may receive pre-warped surfaces from 45 the body wearable computing system. The per-warped surface may be generated based on the rendering results on the GPUs associated with the body wearable computing system and may visually take into account the 3D contour of the underlying object. In particular embodiments, the surface 50 may include texture data as well as position data within the viewer's view space. Based on changes in the viewer's current perspective (e.g., head orientation and/or eye gaze), the display engine of the headset system may perform visibility tests (e.g., using ray casting) from the updated 55 viewpoint of the viewer. For example, the display engine may cast rays from each tile in screen space, positioned and oriented in accordance with the viewer's current perspective, and see if the rays intersect any surfaces in view space. may then re-sample the appropriate color information for each pixel using the texture data of the surfaces that intersect the projected rays. The result of this post-warping process may be an updated 2D frame after the body computing system rendered the initial 2D frame (which was used to 65 generate the pre-warped surface). The updated 2D frame may appear as if the headset system generated a transformed

10

pre-warped surface 420 by moving and/or warping the initial pre-warped surface 410 along one or more dimensions in the 3D space 430. As another example, the headset system may rotate the pre-warped surface 410 along one or more axis in the 3D space 430. As another example, the headset system may increase or reduce the size of the pre-warped surface 410 for zoom in or out operations. As another example, the headset system may combine one or more transformations or adjustments as described above to transform or adjust the received pre-warped surface into a new surface (e.g., 420) for rendering on eye display systems.

In particular embodiments, the headset system may transform or adjust the received pre-warped surfaces according to one or more conditions of the viewers. In particular embodiment, the headset system may transform or adjust the received pre-warped surfaces according to one or more conditions which cause the pre-warped surface to change its position (e.g., distance, orientation, angle) with respect to the viewer in relative high speed but within relative small ranges. For example, the headset system may adjust the orientation or position of the pre-warped surface 410 based on a viewpoint change (e.g., head motion, eye motion) of the viewer. As another example, the headset system may adjust the size, orientation, or/and position of the pre-warped surface 410 based on a zooming operation (e.g., zoom in or out) of the viewer. In particular embodiments, the conditions of the viewers (e.g., viewpoint change, view distance change, user operations) may be determined based on one or more sensors or sensing systems associated with the artificial reality system, for example, accelerometers, vergence tracking systems, eye tracking systems, head motion sensors, body motion sensors, controllers, etc. In particular embodiments, the headset system may transform or adjust the received pre-warped surfaces according to one or more conditions including, for example, but not limited to, a view point, a view distance, a view angle, a moving speed, a moving direction, an acceleration metric, a head motion, an eve motion, an head posture, an eye status, an user zooming operation, a gazing point, a gazing distance, a vergence distance, an user input, a controller status, etc.

In particular embodiments, the system may limit the minification effect of zoom out operations to be within a two-time zoom out range. The two-time zoom-out limitation may ensure that the changes in texel size relative to sample pixel size, as caused by the user's zooming operations, will be within an acceptable range for using the current texture mipmap level. Furthermore, as will be discussed later, the two-time zoom-out constraint may allow the four sampling points associated with one tile to fall within an aligned or unaligned 4×4 texel region, and therefore allow the system to parallelly retrieve all the texels that are needed to determine the colors or distance fields of the sampling points with higher speed and better computational efficiency. In addition, by bounding the number of texels that are needed for a block of 2×2 sampling positions, this limitation simplifies the logic of the display engine while allowing the headset system to provide updated frames faster with improved efficiency.

FIG. 5 illustrates an example pre-warped surface 500 that Based on the visibility determination, the display engine 60 is visible through an example tile 540. In particular embodiments, the system may use a ray casting algorithm to determine whether a pre-warped surface 500 is visible through a region on a screen. In particular embodiments, the region on the screen may be represented by a tile (e.g., a block of pixels, such as 16×16 pixels). The ray casting algorithm may firstly determine the viewpoint 530 of the viewer (e.g., a center point of the viewer's eye). Then, the ray casting algorithm may position a conceptual or virtual camera 532 at the viewer's viewpoint and cast a number of rays 534 from the virtual camera 532. In particular embodiments, four rays may be cast from the four corners of a tile positioned within the screen of the virtual camera 532. The group of four casted rays 534 may intersect with the prewarped surface 500 at four respective intersecting points (e.g., 540A, 540B, 540C, 540D). The sampling points 540A, 540B, 540C, and 540D may form and be associated with a tile 540, which is paired with the surface 500. In particular 10 embodiments, the system may generate a number of tile/ surface pairs in this manner.

Once the display engine determines that a tile intersects with a surface, it may then sample each pixel within the tile using the texture data of the surface. In particular embodiments, if a tile contains 16×16 pixels, the display engine (e.g., its pixel block) may use interpolation to determine the texture coordinates (e.g., in (U, V)) of each of the pixel sample locations using the four texture coordinates of the four corners of the projected tile (after the points of intersection in 3D view space have been converted into texture coordinates). Then, the display engine may compute (e.g., using bilinear or bicubic interpolation) the color or distance field properties of each sampling point using the four closest texels.

FIGS. **6**A-B illustrate an example process for determining the texels that are needed for determining the color or distance field of a sampling point. FIG. 6A illustrate an example sampling point 610 and the corresponding texels (e.g., **601**, **602**, **603**, **604**) that are needed to determine the 30 pixel value at the sampling point **610**. In particular embodiments, the system may determine a pixel value using interpolation based on the four closest texels. For example, the pixel value corresponding to the sampling point 610 may be determined by interpolating the four closets texels of 601, 35 602, 603, and 604. To help visualize the texels used for determining the pixel value for the sampling point 610, the figures shown illustrate a geometric region 626 formed by connecting the respective center points 611, 612, 613, 614 of the texels 601, 602, 603, 604. The pixel value of the 40 sampling point 610 is determined by the texels 601, 602, 603, and 604 forming the surrounding the geometric region 626.

FIG. 6B illustrates example sampling points (e.g., 632, 642, 652, 662) and the associated texels for determining the 45 corresponding pixels values. The sampling point 632, 642, 652, 662 may all fall into the same texel as indicated by (U. V) coordinate of (1,1), but may be associated with different groups of texels based on the relative position of the sampling points with respect to the texel (1,1) and its 50 neighboring texels. For example, the sampling point 632 may be within the geometric region 634 determined by the center points of the texels (0, 0), (1, 0), (0, 1), and (1, 1), and therefore the texels (0, 0), (1, 0), (0, 1), and (1, 1) may be identified as the texels needed for the interpolation to 55 determine the pixel value corresponding to the sampling point 632. As another example, the sampling point 642 may be within the geometric region 644 determined by the center points of the texels (1, 0), (2, 0), (1, 1), and (2, 1), and therefore the texels (1, 0), (2, 0), (1, 1), and (2, 1) may be 60 identified as the texels needed for the interpolation to determine the pixel value corresponding to the sampling point 642. As another example, the sampling point 652 may be within the geometric region 654 determined by the center points of the texels (0, 1), (1, 1), (0, 2), and (1, 2), and therefore the texels (0, 1), (1, 1), (0, 2), and (1, 2) may be identified as the texels needed for the interpolation to

determine the pixel value corresponding to the sampling point **652**. As another example, the sampling point **662** may be within the geometric region **664** determined by the center points of the texels (1, 1), (2, 1), (1, 2), and (2, 2), and therefore the texels (1, 1), (2, 1), (1, 2), and (2, 2) may be identified as the texels needed for the interpolation to determine the pixel value corresponding to the sampling point **662**.

In particular embodiments, the system may sample the surface using sampling points that correspond to pixel positions (e.g., each point represents the center of a pixel) to determine the color values of the pixels. In particular embodiments, the pixel size of a sampling point may be substantial the same as the size of the texel. When the viewer zooms out, a surface associated with a rendered object may become smaller in size because of the minification effect. When the minified surface is sampled without changing the texture resolution (i.e., using the same mipmap level), the same pixel size would now be larger than the size of a tile and, consequently, a pixel may cover multiple texels on the minified surface. Therefore, the display engine may need to access and interpolate more texels (e.g., beyond 4×4 texels) in order to determine the colors of 2×2 sampling points. Therefore, sampling a minified surface by zooming out beyond a two-times range introduces uncertainty in terms of the amount and range of texels that may be needed. In particular embodiments, the system may restrict the minification effect of zoom-out operations to be within a twotime range, thereby ensuring that the four sampling points always fall within a 4×4 texel region which could be readout in one read operation and could be sampled parallelly.

In particular embodiments, the 2×2 sampling points would fall within a 4×4 texel region as long as the positions of the adjacent sampling points are no more than 2 texels apart. In particular embodiments, the distance between two sampling points may be measured by Manhattan distance. For example, the constraint may be described by satisfying both of the following two equations:

$$\left| \frac{du}{dx} \right| + \left| \frac{dv}{dx} \right| \le 2 \tag{1}$$

$$\left| \frac{du}{dy} \right| + \left| \frac{dv}{dy} \right| \le 2 \tag{2}$$

where the u and v correspond to sampling point coordinates in the (U, V) coordinate space for the texels; x and y correspond to the two-dimensional (X, Y) coordinate space for display pixels. In particular embodiments, the distance between two sampling points may be measured by geometric distance rather than Manhattan distance. In particular embodiments, the size of a texel may be defined by the length of an edge of the texel square.

As previously described, in particular embodiments, texture sampling may be concurrently performed for 2×2 pixels sampling points. FIG. 7A illustrates an example 4×4 texel region 700A and an example sampling region 701 that represents a set of 2×2 orthogonal sampling points located at the four corners of the sampling region 701. The size of each side of the sampling region 701 may be less than or equal to two times of texel size. The sampling region 701 in FIG. 7A is aligned with the texels along the two dimensions in the 2D space of the texels. When the sampling region 701 is projected on the texels, the associated texels that are needed for interpolation to determine the pixel values at each sampling point (i.e., each of the four corners of the sampling

region 701) may be determined using the method as described in FIGS. 6A-B. Each group of four texel centers connected by thin lines represents the four closest texel centers that would be used to filter the sampling point (e.g., a corner of the sampling region 701) located within the 5 thin-line box. For the sampling region 701, the texels that are needed for filtering the four 2×2 sampling points fall within the  $4\times4$  texel region 701. When the sampling region 701 is moved along one or more dimensions of the 2D space, the texels that are needed to filter the four sampling points 10 would always fall within a 4×4 texel region. For example, if the sampling region 701 is shifted to the position shown by sampling region 702, the associated texels for determine the four sampling points (the four corners of the sampling region 702) will continue to fall within the same aligned 4×4 texel region 700A. As another example, when the sampling region 702 is shifted for a larger distance (e.g., more than a half-texel size along one or two dimensions of the 2D space) with respect to the sampling region 701, the sampling region 702 may have its associated texels to fall within an 20 unaligned 4×4 texel region.

FIG. 7B illustrates example 2×2 orthogonal sampling points within an aligned 4x4 texel region. The sampling points 711, 712, 713, and 714 may be the four corner points of a sampling region which is aligned with texels along the 25 two dimensions of the 2D texels space. When the distance 716 between the sampling point 714 and 713 is less than or equal to 2 texels, the corresponding 8 texels that are needed to determine the pixels 714 and 713 may fall within a 2×4 texel region including texels (0, 0), (1, 0), (2, 0), (3, 0), (0, 30)1), (1, 1), (2, 1), and (3, 1). When the distance **718** between the sampling points 712 and 713 is less than or equal to 2 texels, the corresponding 8 texels of that are needed to determine the pixels for 714 and 713 may fall within a 4×2 texel region. Similarly, when the distance 716 between the 35 sampling point 711 and 712 is less than or equal to 2 texels, the corresponding 8 texels of that are needed to determine the pixels for 711 and 712 may fall within a 2×4 texel region. When the distance 718 between the sampling point 711 and 714 is less than or equal to 2 texels, the corresponding 8 40 texels of that are needed to determine the pixels for 711 and 714 may fall within a 4×2 texel region. Therefore, when the distances between any two neighboring sampling points are less than or equal to two times of a texel edge length, all the texels that are needed for the interpolation to determine the 45 four pixels values corresponding to the four corners may always be included in a 4×4 texel region regardless how where the sampling region is positioned.

FIG. 7C illustrates example 2×2 orthogonal sampling points within an unaligned 4×4 texel region 730. As discussed above, as along as the distances between any two sampling points are less than or equal to two times of a texel edge length, the texels that are needed to determine the four pixels values may always fit within a 4×4 texel region no matter how the 2×2 sampling points are positioned. However, when the sampling points are shifted by more than half the texel size, the four sample points may fall within a different, unaligned texel region, but the dimensions of that texel region would continue to be 4×4. For example, the sampling points of 731, 732, 733, 734 may fall within an unaligned texel regions 730 when the sampling points positions are changed from the position as illustrated in FIG. 7B to the positions as illustrated in FIG. 7C.