US011682464B2

## (12) United States Patent

Tokutomi et al.

#### (54) METHOD OF CONTROLLING A SEMICONDUCTOR MEMORY INCLUDING MEMORY CELLS AND A WORD LINE

(71) Applicant: KIOXIA CORPORATION, Tokyo (JP)

(72) Inventors: **Tsukasa Tokutomi**, Kamakura (JP); **Masanobu Shirakawa**, Chigasaki (JP)

(73) Assignee: KIOXIA CORPORATION, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 17/696,339

(22) Filed: Mar. 16, 2022

(65) Prior Publication Data

US 2022/0208282 A1 Jun. 30, 2022

### Related U.S. Application Data

(63) Continuation of application No. 16/892,817, filed on Jun. 4, 2020, now Pat. No. 11,315,643, which is a (Continued)

#### (30) Foreign Application Priority Data

Sep. 18, 2018 (JP) ...... JP2018-174175

(51) Int. Cl. G11C 16/04 (2006.01) G11C 16/34 (2006.01) (Continued) (10) Patent No.: US 11,682,464 B2

(45) **Date of Patent:**

\*Jun. 20, 2023

(52) U.S. Cl.

CPC ....... *G11C 16/34* (2013.01); *G06F 11/1068* (2013.01); *G11C 11/5628* (2013.01);

(Continued)

(58) Field of Classification Search

CPC . G11C 16/34; G11C 11/5628; G11C 11/5642;

G11C 16/10; G11C 16/26;

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

7,805,660 B2\* 9/2010 Hazama ...... G11C 7/16 714/778

7,859,932 B2 12/2010 Mokhlesi (Continued)

#### FOREIGN PATENT DOCUMENTS

2007-323731 A 12/2007

2013-122804 6/2013

(Continued)

Primary Examiner — Tha-O H Bui

(74) Attorney, Agent, or Firm — Oblon, McClelland,

Maier & Neustadt, L.L.P.

JP

JP

#### (57) ABSTRACT

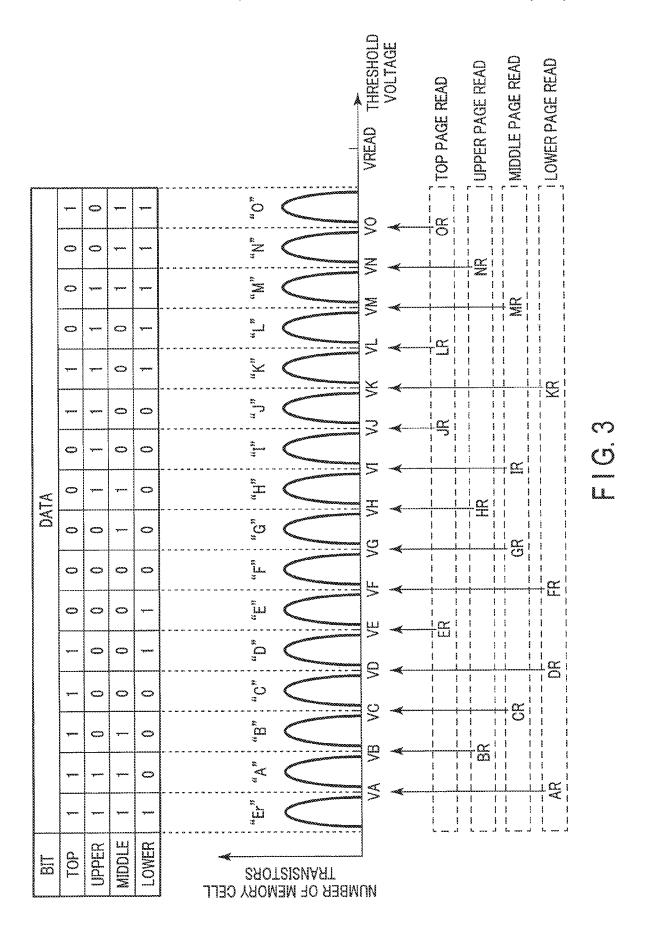

According to one embodiment, a controller is configured to write four-bit data in each of memory cells, and read first data item from the memory cells through application of a first voltage to a word line. The controller is configured to read second data items by repeating a first operation of reading data including data of respective first bits of the memory cells through application of two voltages to the word line at different timings while changing the two voltages in each first operation. The controller is configured to mask part of each of the second data items using the first data.

#### 9 Claims, 37 Drawing Sheets

# **US 11,682,464 B2**Page 2

|      | Related U.S. Application Data continuation of application No. 16/291,281, filed on                                                                               | USPC                                                                                                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|      | Mar. 4, 2019, now Pat. No. 10,714,192.                                                                                                                           | (56) References Cited                                                                                                                |

| (51) | Int. Cl. <i>G11C 11/56</i> (2006.01)                                                                                                                             | U.S. PATENT DOCUMENTS                                                                                                                |

|      | G11C 16/26 (2006.01)<br>G06F 11/10 (2006.01)<br>G11C 29/52 (2006.01)<br>G11C 16/10 (2006.01)                                                                     | 8,848,453 B2 9/2014 Shen et al.<br>9,111,626 B2 8/2015 Kim et al.<br>10,714,192 B2 7/2020 Tokutomi<br>2011/0007565 A1* 1/2011 Hazama |

| (52) | U.S. Cl. CPC <i>G11C 11/5642</i> (2013.01); <i>G11C 16/10</i> (2013.01); <i>G11C 16/26</i> (2013.01); <i>G11C 29/52</i> (2013.01); <i>G11C 16/0483</i> (2013.01) | 2013/0148436 A1 6/2013 Kurosawa<br>2018/0138241 A1* 5/2018 Pellizzer H01L 45/141<br>FOREIGN PATENT DOCUMENTS                         |

| (58) | Field of Classification Search CPC                                                                                                                               | JP 2014-086128 5/2014<br>JP 5638537 12/2014<br>JP 5992623 9/2016<br>JP 2018-110043 A 7/2018<br>* cited by examiner                   |

C C

F | G. 2

F I G. 4

FIG.6

FIG.7

FIG.8

FIG. 9

C C L

FIG. 20

FIG. 24

FIG. 25

Jun. 20, 2023

FIG. 28

ウL

FIG. 33

FIG. 34

| WORD LINE GROUP | B READ SHIFT<br>AMOUNT | E READ SHIFT<br>AMOUNT | H READ SHIFT<br>AMOUNT |

|-----------------|------------------------|------------------------|------------------------|

| WLG0            | ∆VBg0                  | ∆VEg0                  | ∆VHg0                  |

| WLG1            | ΔVBg1                  | ΔVEg1                  | ∆VHg1                  |

| WLG2            | ∆ VBg2                 | ΔVEg2                  | ∆VHg2                  |

| WLG3            | ∆ VBg3                 | ∆VEg3                  | ∆VHg3                  |

FIG. 35

\$ \_\_\_\_\_

E E E

# METHOD OF CONTROLLING A SEMICONDUCTOR MEMORY INCLUDING MEMORY CELLS AND A WORD LINE

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. No. 16/892,817 filed Jun. 4, 2020, which is a continuation of U.S. application Ser. No. 16/291,281, filed Mar. 4, 2019, and is based upon and claims the benefit of priority from Japanese Patent Application No. 2018-174175, filed Sep. 18, 2018; the entire contents of each of which are incorporated herein by reference.

#### **FIELD**

Embodiments described herein relate generally to a memory system.

#### BACKGROUND

A memory system including a semiconductor memory and a controller that controls the semiconductor memory is known.

# BRIEF DESCRIPTION OF THE VIEWS OF THE DRAWINGS

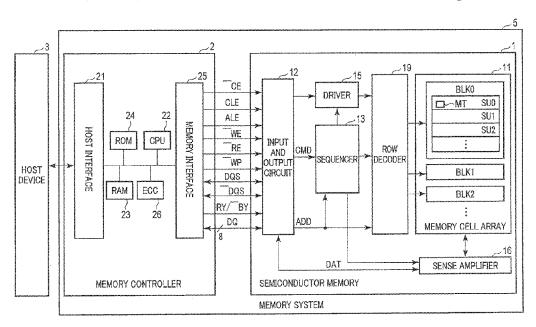

- FIG. 1 shows components and connections in a memory 30 system according to a first embodiment and associated components;

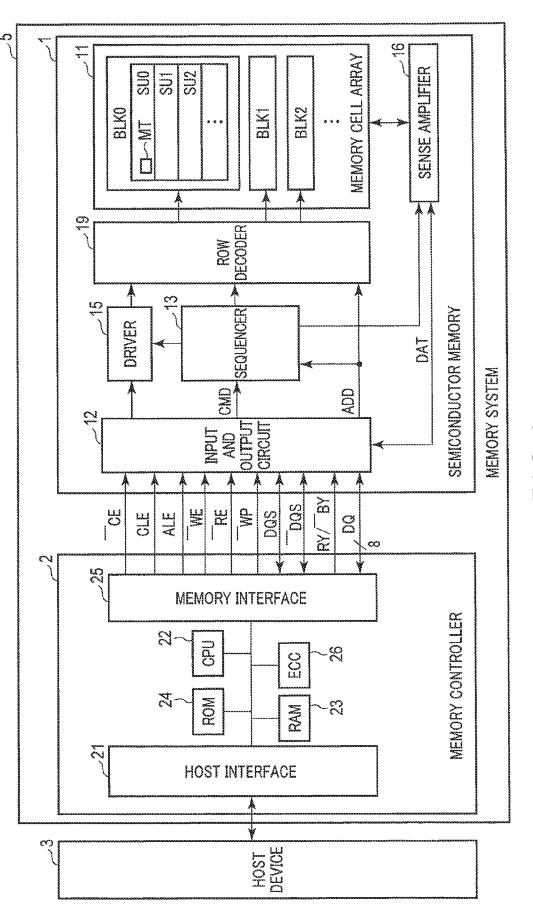

- FIG. 2 shows an example of several components and connections in a memory cell array according to the first embodiment;

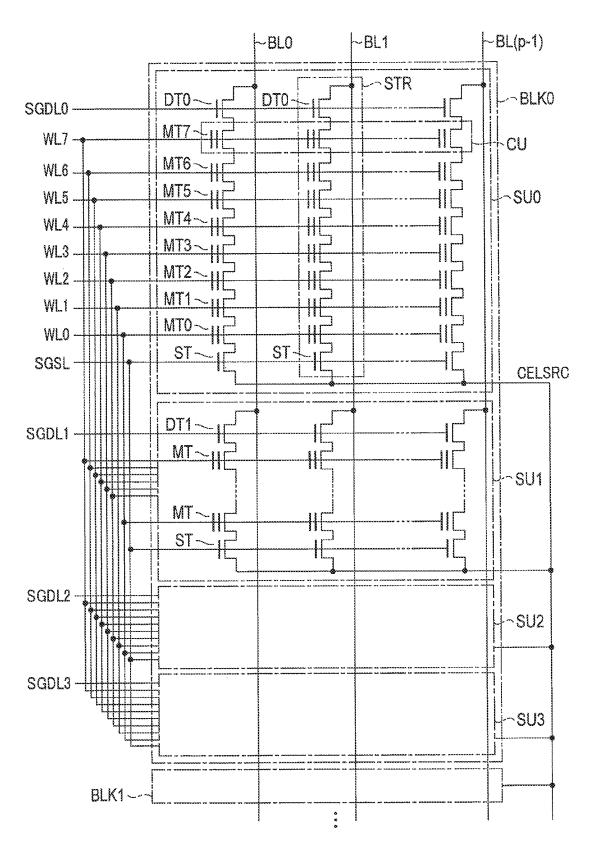

- FIG. 3 shows the distribution of the threshold voltages of memory cell transistors each configured to store four-bit data according to the first embodiment;

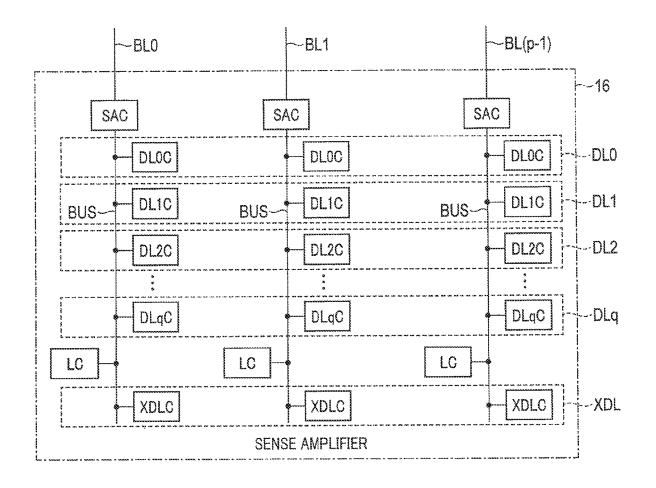

- FIG. 4 shows components and connections in a sense amplifier according to the first embodiment;

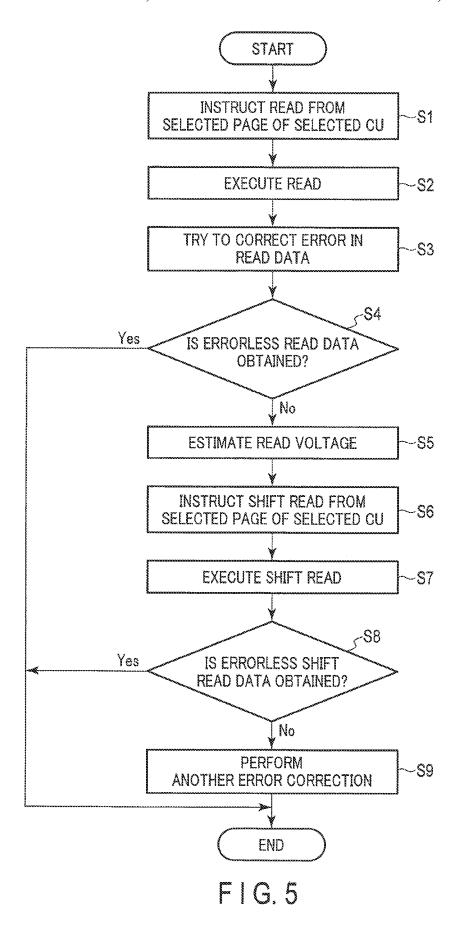

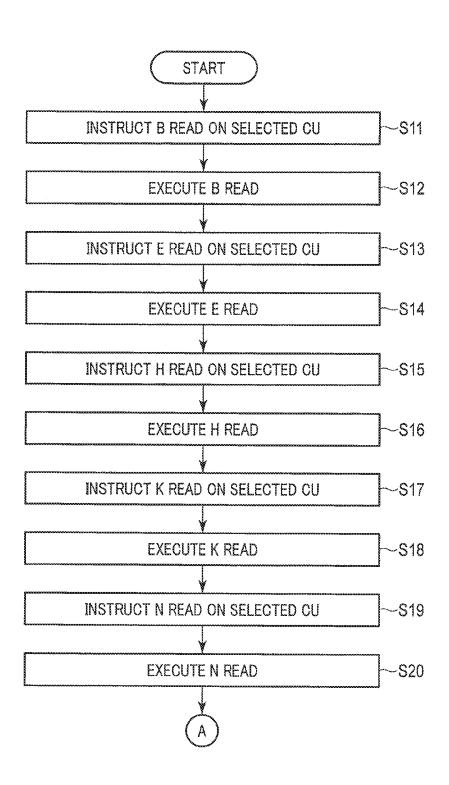

- FIG. 5 is a flowchart showing an operation according to the first embodiment;

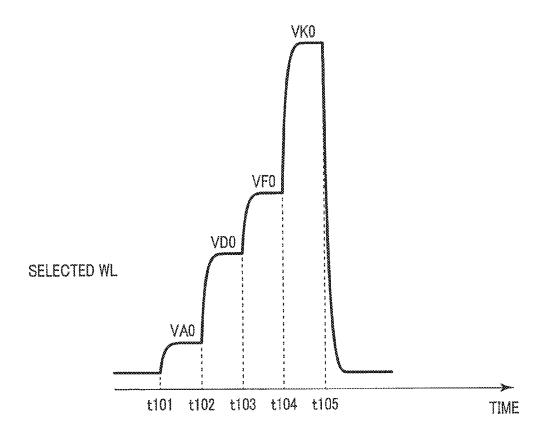

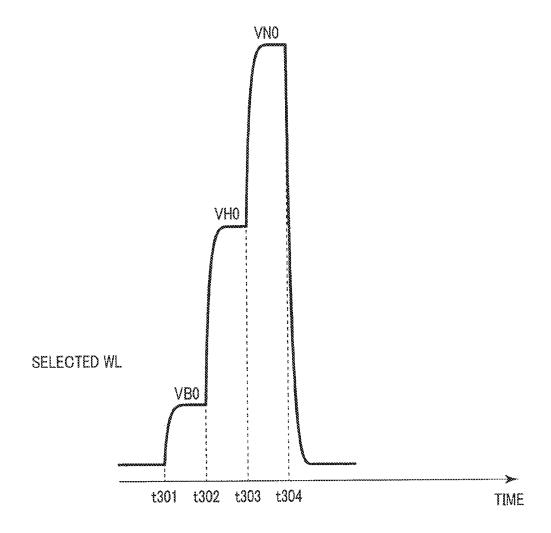

- FIG. 6 shows voltages applied to a selected word line along the time when a lower page is selected according to the first embodiment;

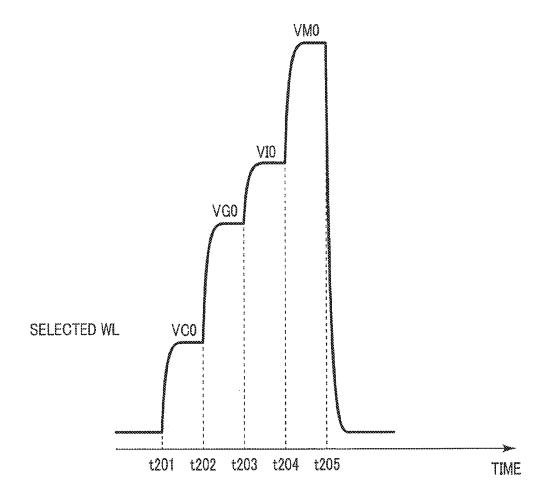

- FIG. 7 shows voltages applied to a selected word line along the time when a middle page is selected according to the first embodiment;

- FIG. 8 shows voltages applied to a selected word line along the time when an upper page is selected according to 50 the first embodiment;

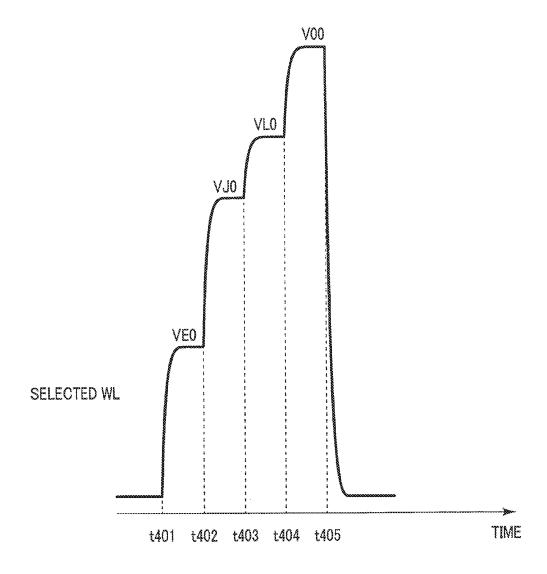

- FIG. 9 shows voltages applied to a selected word line along the time when a top page is selected according to the first embodiment;

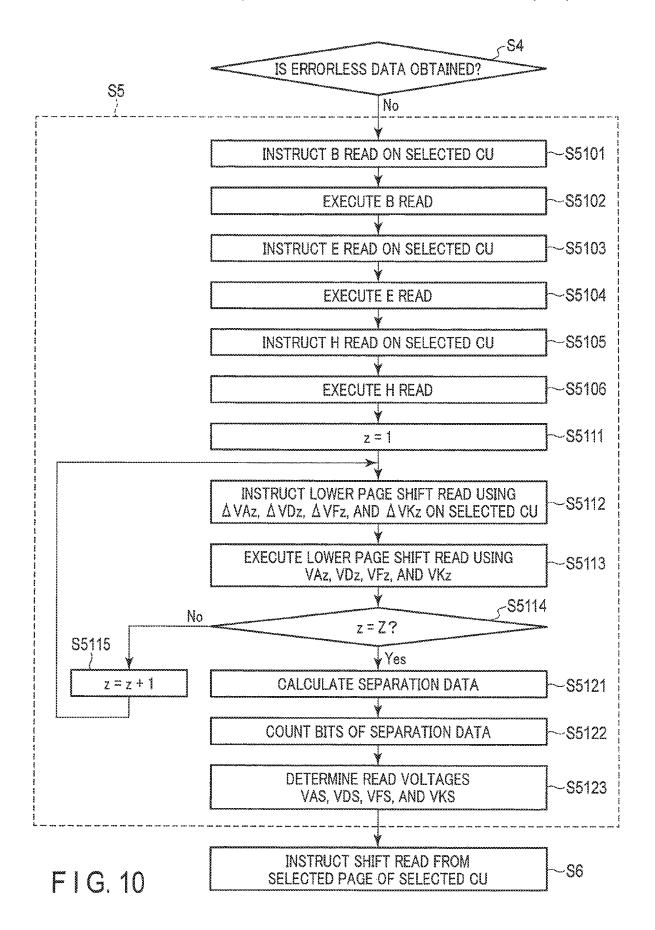

- FIG. 10 is a sub-flowchart when a lower page is selected 55 according to the first embodiment;

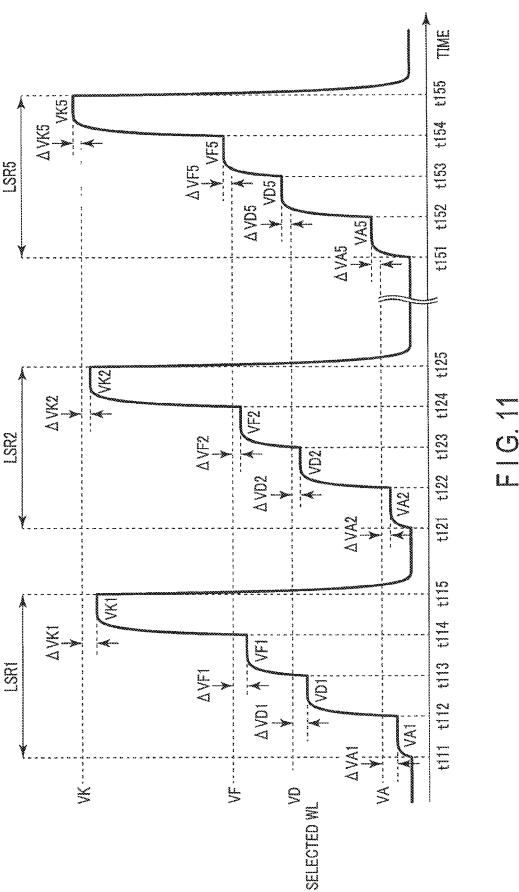

- FIG. 11 shows voltages applied to a selected word line along the time during shift read from a lower page according to the first embodiment;

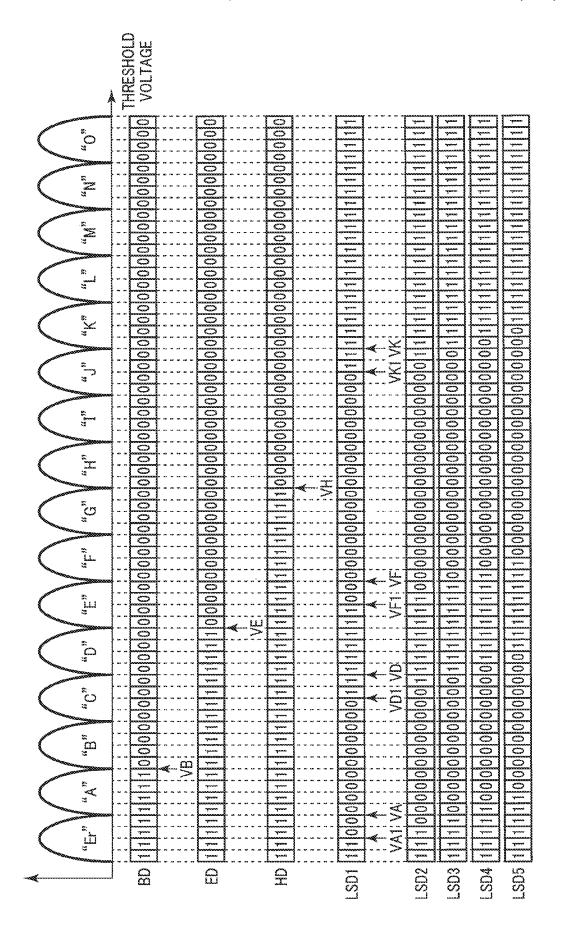

- FIG. 12 shows an example of various data obtained by 60 reads according to the first embodiment;

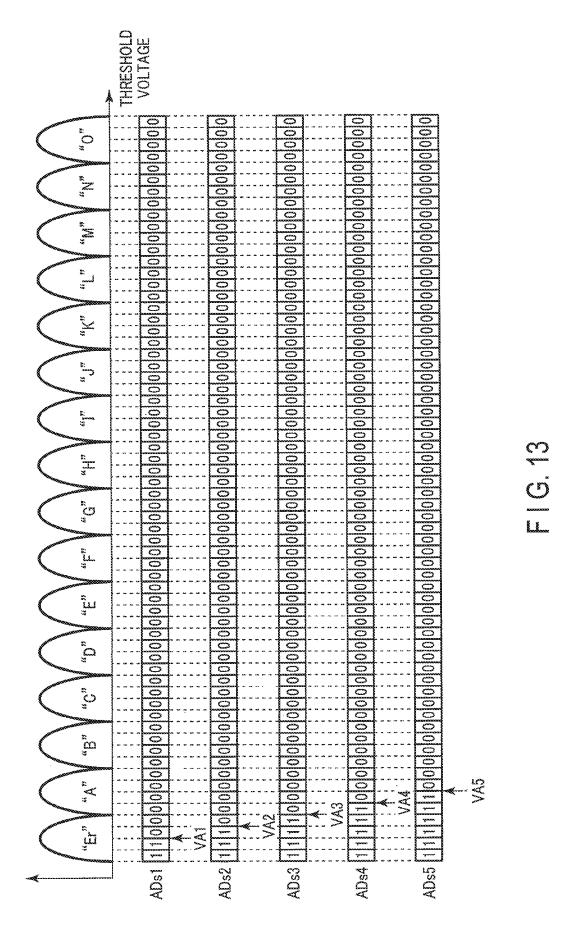

- FIG. 13 shows an example of separation data obtained according to the first embodiment;

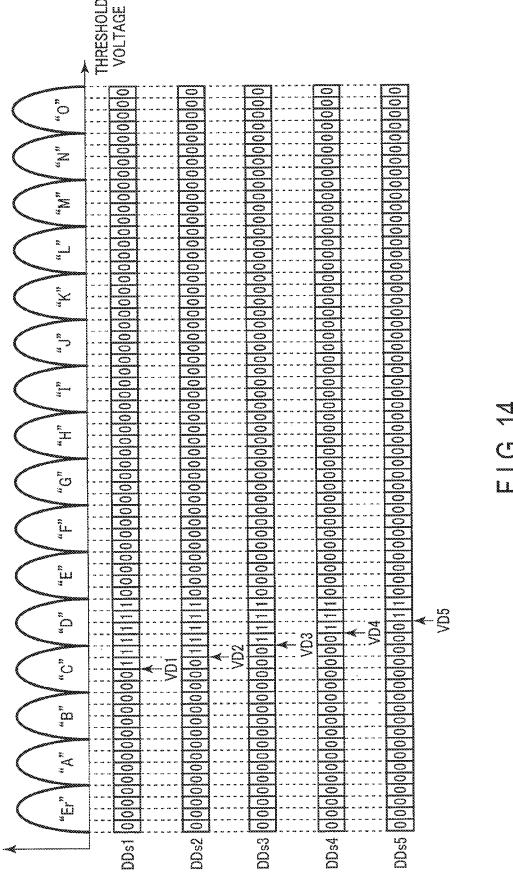

- FIG. 14 shows an example of separation data obtained according to the first embodiment;

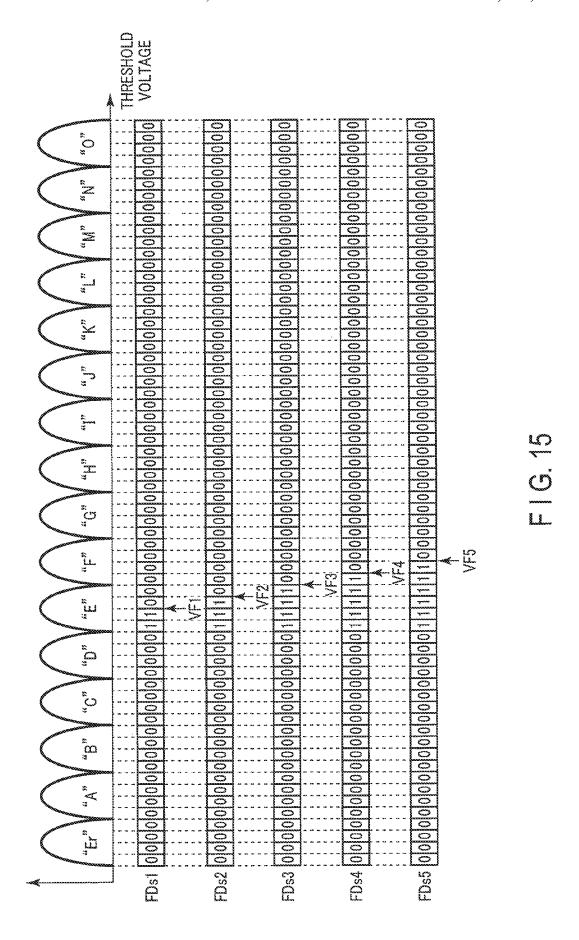

- FIG. 15 shows an example of separation data obtained according to the first embodiment;

2

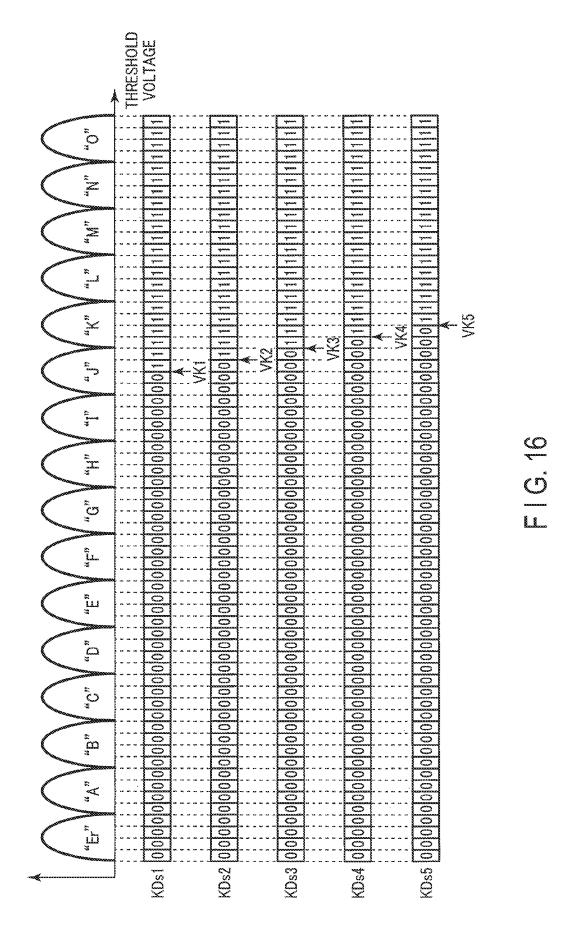

- FIG. 16 shows an example of separation data obtained according to the first embodiment;

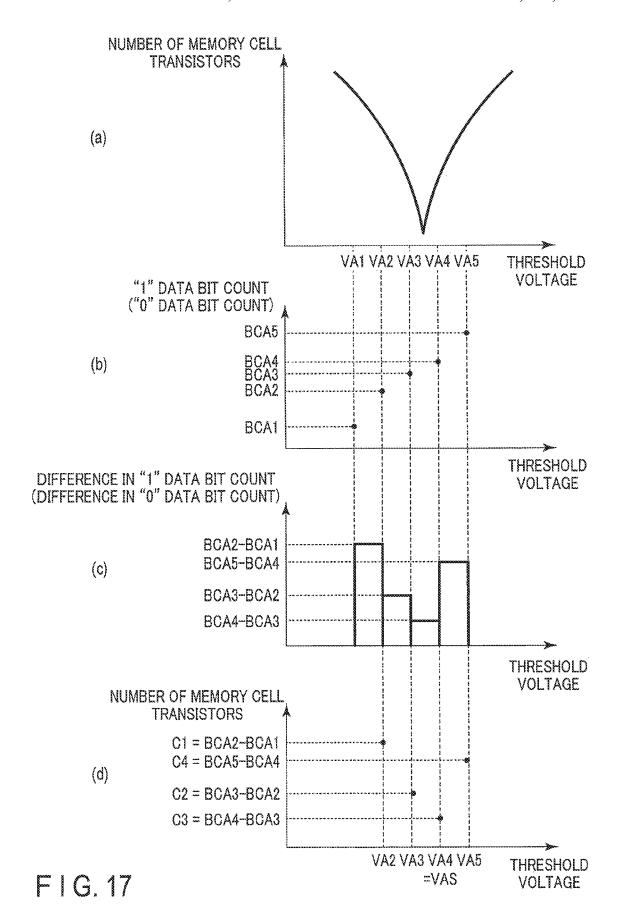

- FIG. 17 shows processing according to the first embodiment:

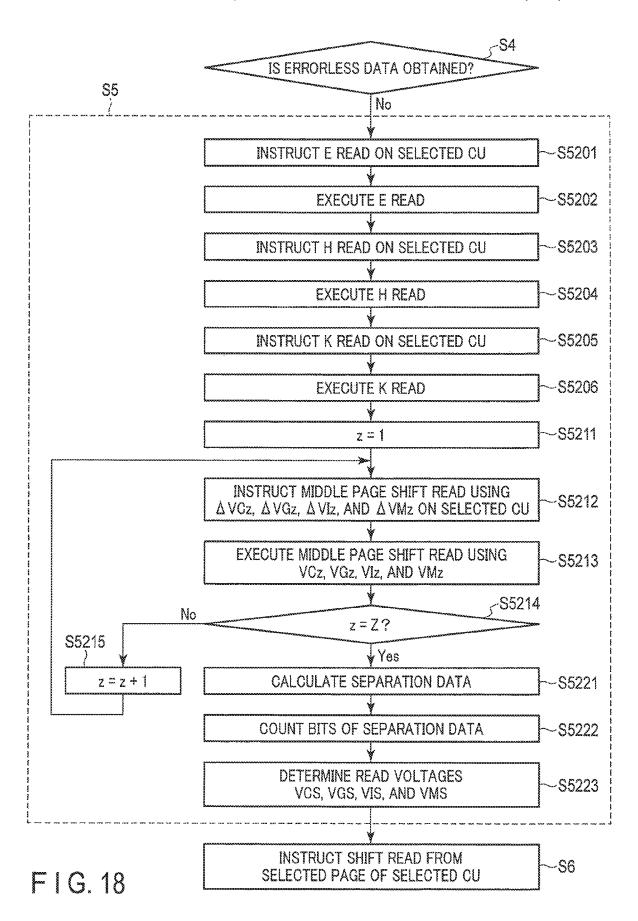

- FIG. **18** is a sub-flowchart when a middle page is selected according to the first embodiment;

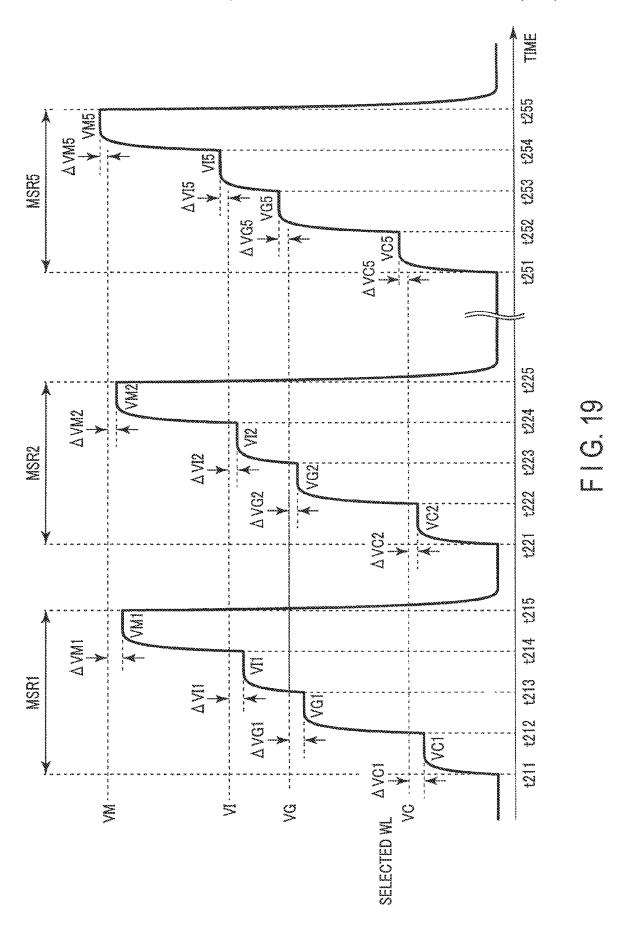

- FIG. 19 shows voltages applied to a selected word along the time during shift read from a middle page according to the first embodiment;

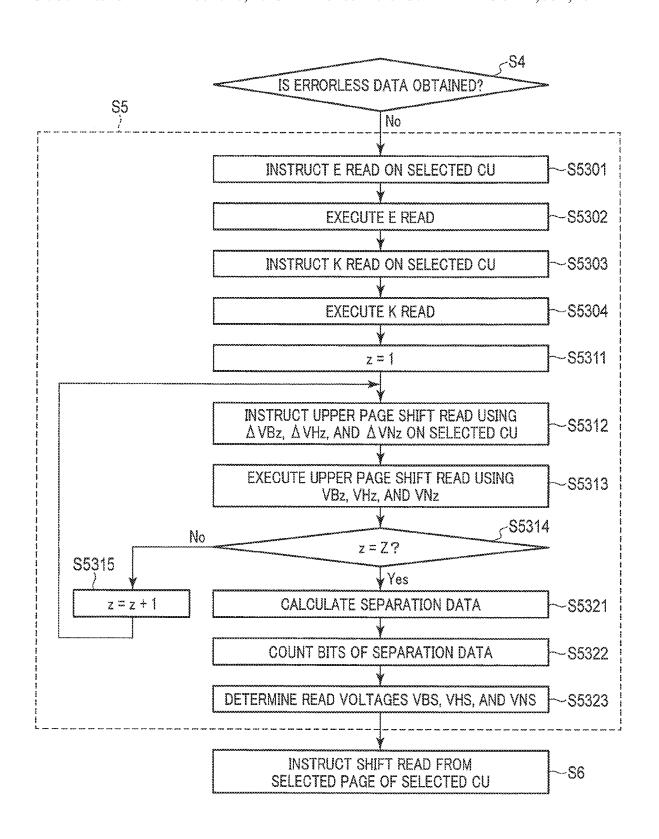

- FIG. 20 is a sub-flowchart when an upper page is selected according to the first embodiment;

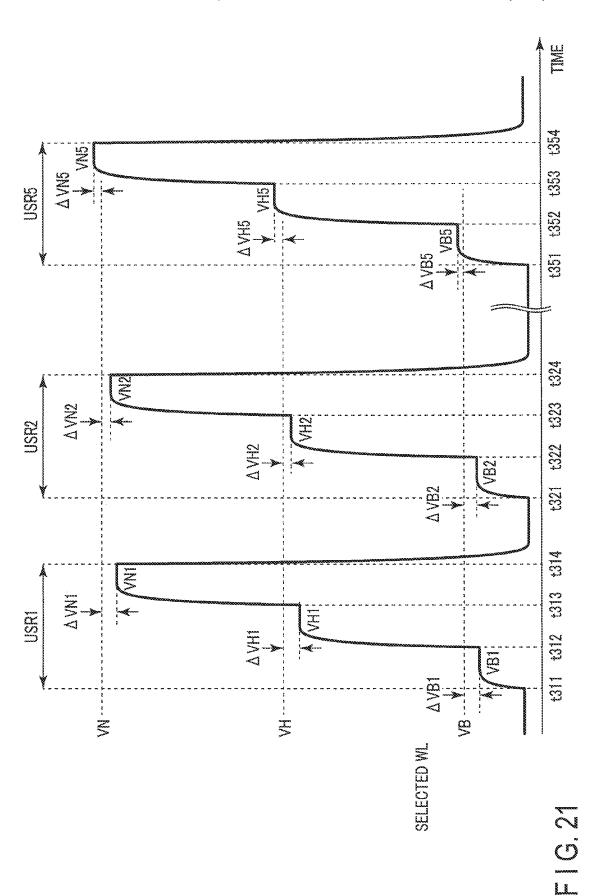

- FIG. 21 shows voltages applied to a selected word line along the time during shift read from an upper page according to the first embodiment;

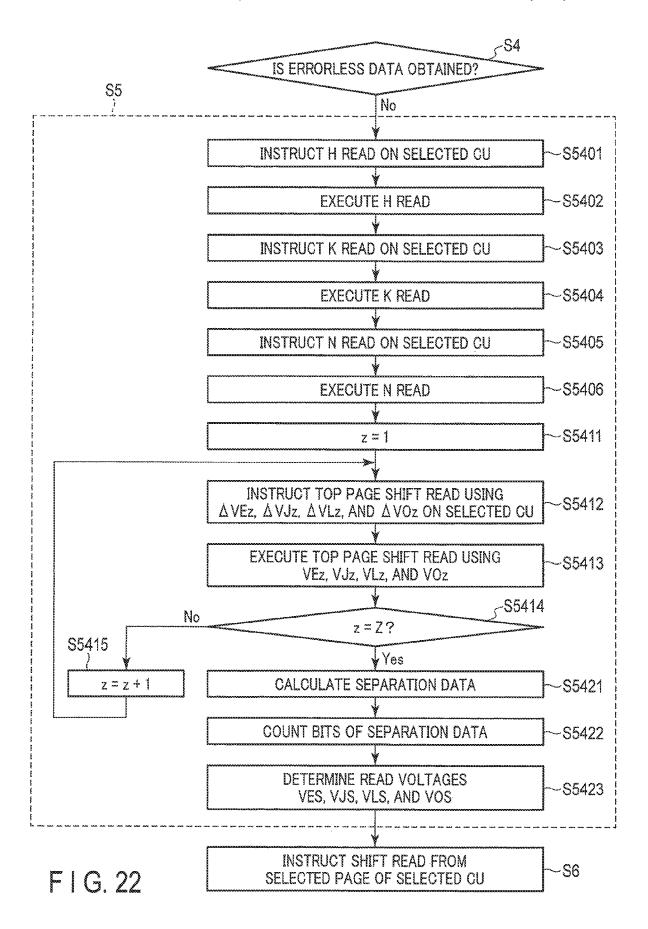

- FIG. 22 is a sub-flowchart when a top page is selected according to the first embodiment;

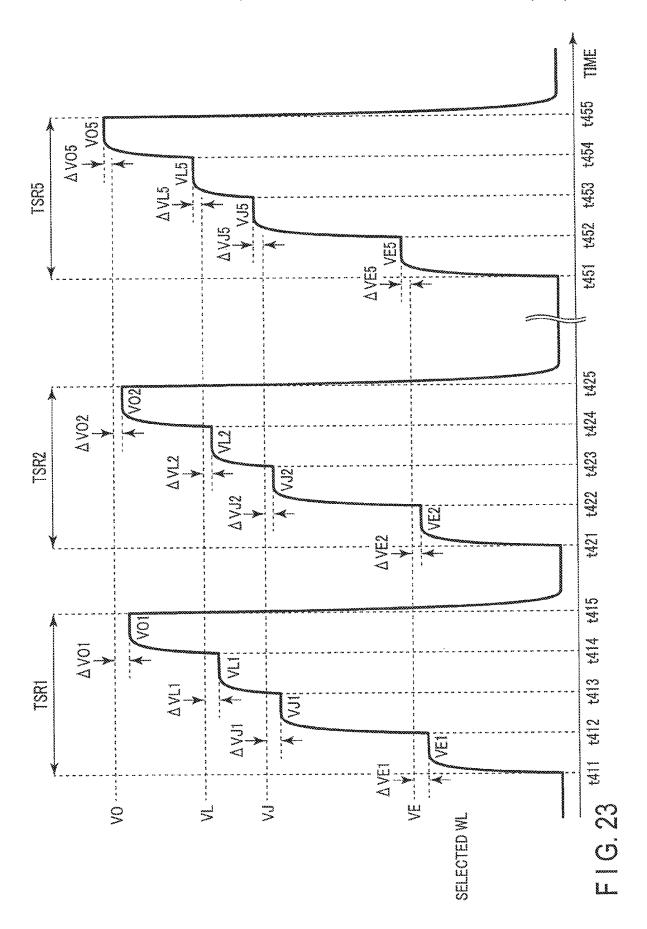

- FIG.  $\overline{23}$  shows voltages applied to a selected word line along the time during shift read from a top page according to the first embodiment;

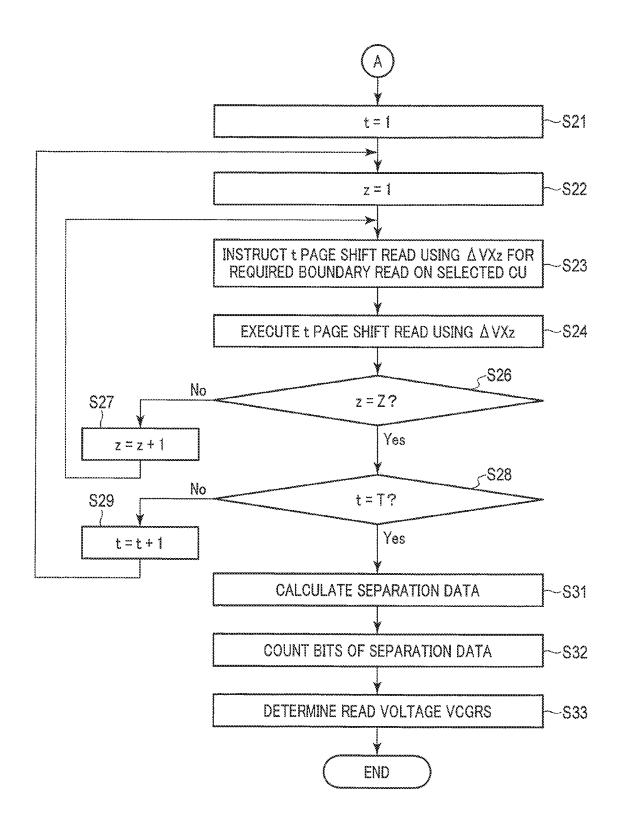

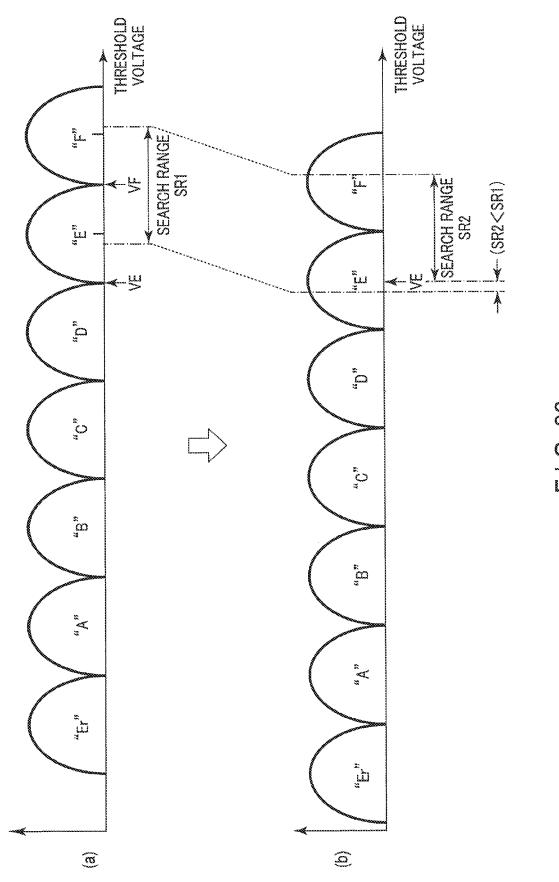

- FIG. **24** is a flowchart showing an operation according to the second embodiment:

- FIG. 25 is a flowchart showing an operation according to the second embodiment;

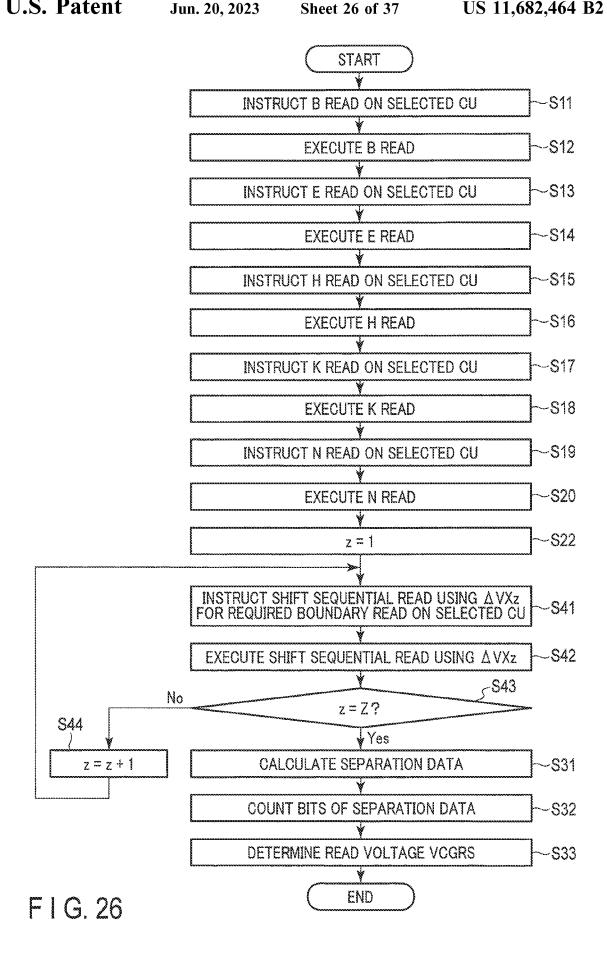

- FIG. **26** is a flowchart showing an operation according to <sup>25</sup> the third embodiment;

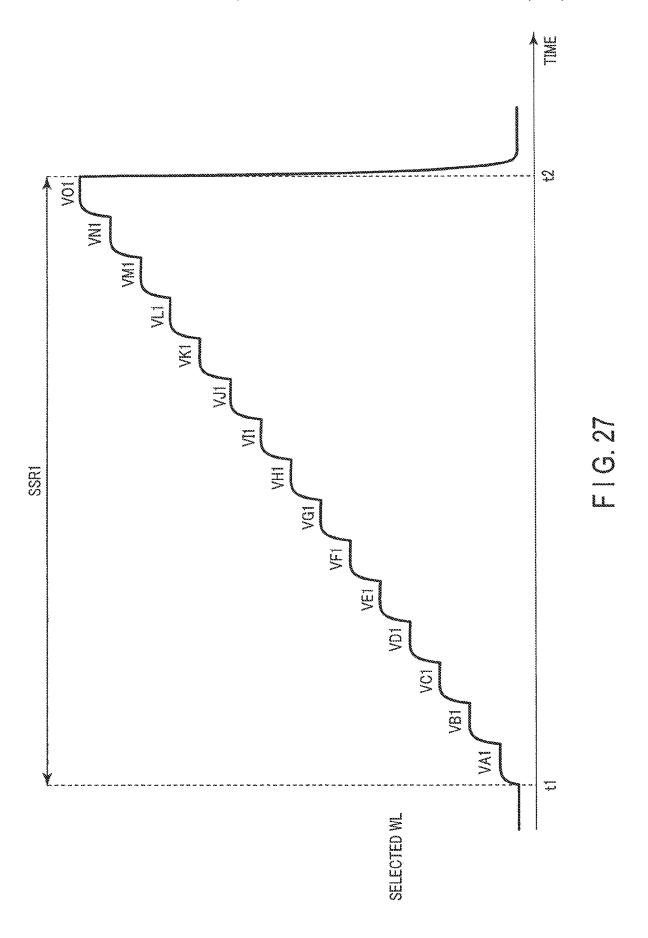

- FIG. 27 shows voltages applied to a selected word line along the time during an operation according to the third embodiment;

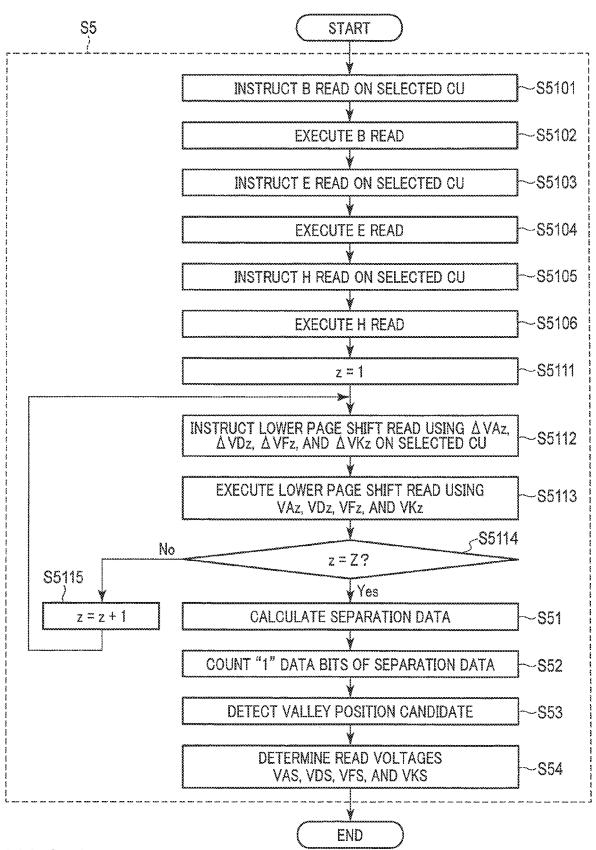

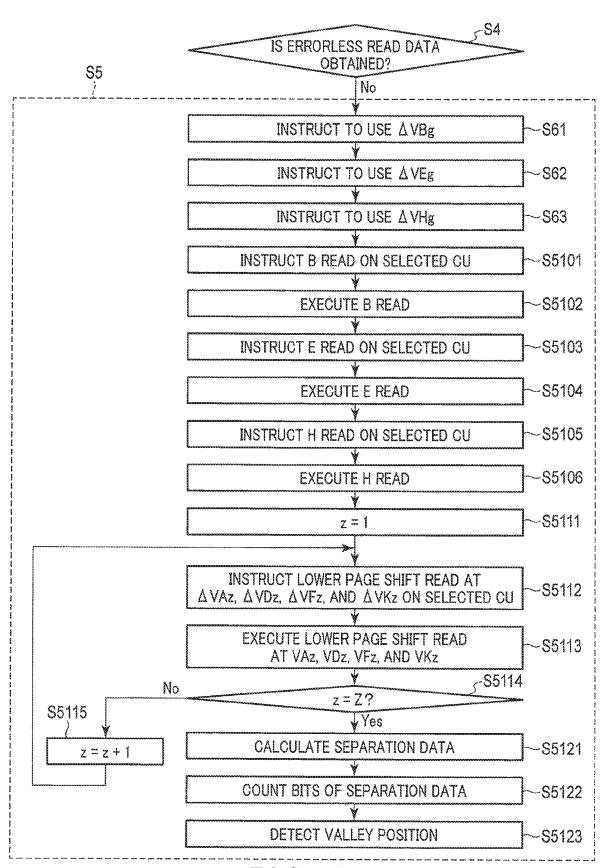

- FIG. 28 is a flowchart showing an operation according to the fourth embodiment;

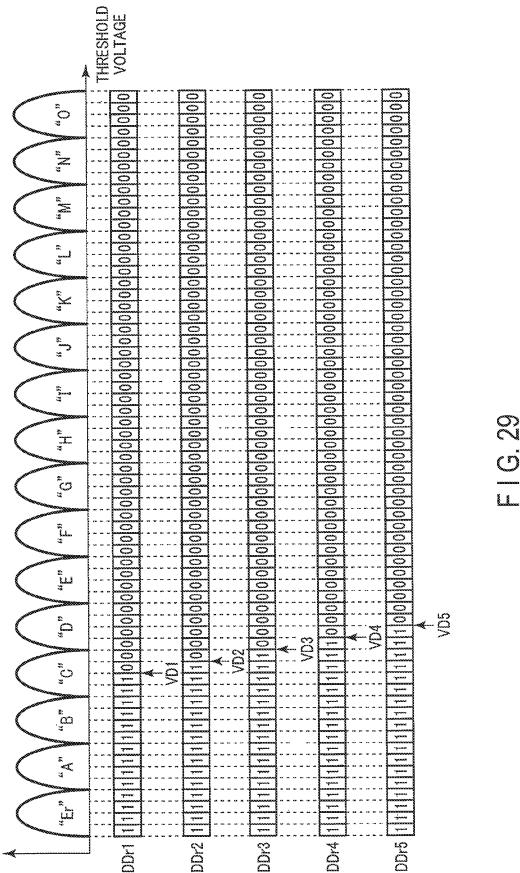

- FIG. 29 shows an example of separation data obtained according to the fourth embodiment;

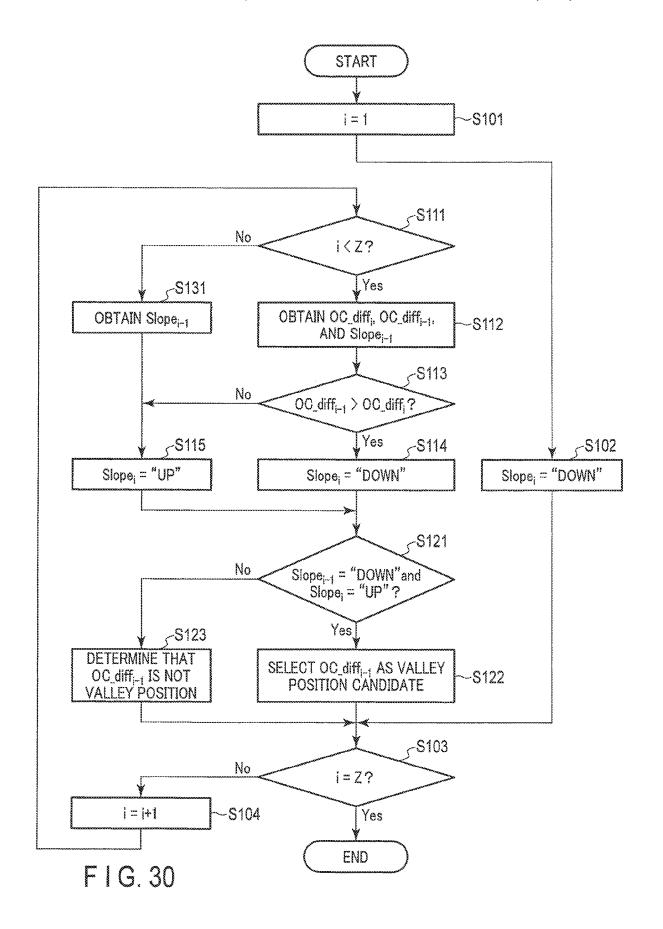

- FIG. 30 is a sub-flowchart showing an operation of a memory system according to the fourth embodiment;

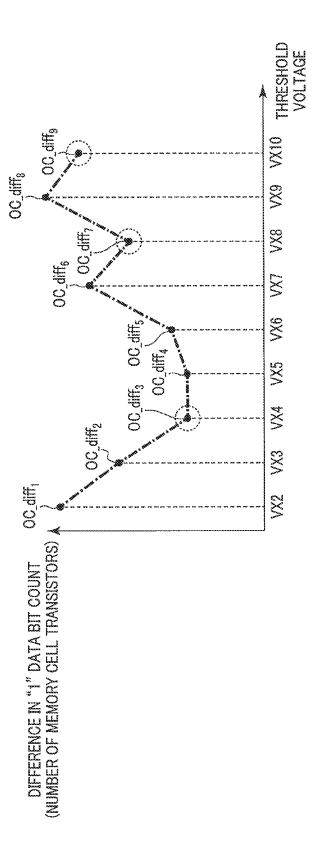

- FIG. 31 shows a relationship between differences in "1" data bit count and threshold voltages obtained according to the fourth embodiment;

- FIG. 32 shows a concept of a method of determining a valley position according to the fourth embodiment;

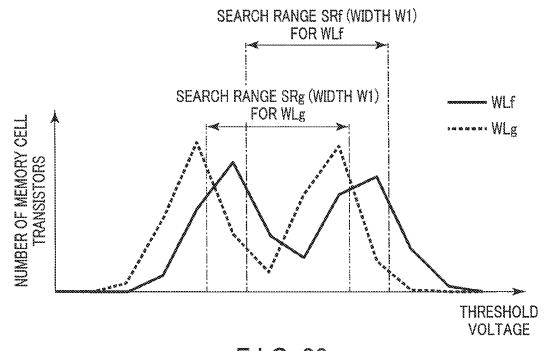

- FIG. 33 shows a distribution of threshold voltages concerning two adjacent states according to a fifth embodiment;

- FIG. 34 shows a flowchart for an operation according to the fifth embodiment;

- FIG. 35 shows data used in the fifth embodiment;

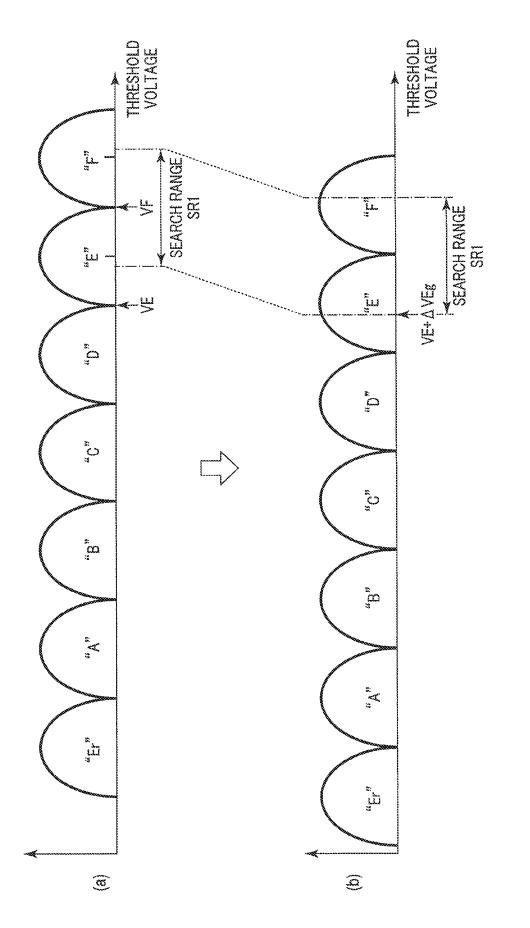

- FIG. 36 shows search ranges for reference; and

- FIG. 37 shows search ranges according to the fifth embodiment.

#### DETAILED DESCRIPTION

According to one embodiment, a memory system includes a semiconductor memory and a controller. The semiconductor memory includes memory cells and a word line coupled to the memory cells. The controller is configured to write four-bit data in each of the memory cells, and read first data item from the memory cells through application of a first voltage to the word line. The controller is further configured to read a plurality of second data items by repeating a first operation of reading data including data of respective first bits of the memory cells through application of two voltages to the word line at different timings while changing the two voltages in each first operation from the two voltages in another first operation. The controller is further configured to mask part of each of the second data items using the first data.

Embodiments will now be described with reference to the figures. In the following description, components with sub-

stantially the same functionalities and configurations will be referred to with the same reference numerals, and repeated descriptions may be omitted. The entire description for a particular embodiment also applies to another embodiment unless it is explicitly mentioned otherwise or obviously 5 eliminated.

Each functional block can be implemented as hardware, computer software, or combination of the both. For this reason, in order to clearly illustrate that each block can be any of hardware, software or combination, descriptions will be made in terms of their functionalities in general. It is not necessary that functional blocks are distinguished as in the following examples. For example, some of the functions may be implemented by functional blocks different from those illustrated below. Furthermore, an illustrated functional block may be divided into functional sub-blocks.

Moreover, any step in a flow of a method of an embodiment is not limited to any illustrated order, and can occur in an order different from an illustrated order and/or can occur concurrently with another step.

In the specification and the claims, a phrase of a particular first component being "coupled" to another second component includes the first component being coupled to the second component either directly or via one or more components which are always or selectively conductive.

#### First Embodiment

#### <1.1. Structure (Configuration)>

FIG. 1 shows components and connections in a memory 30 system according to the first embodiment and associated components. As shown in FIG. 1, a memory system 5 is controlled by a host device 3 and includes a semiconductor memory 1 and a memory controller 2 which are. The memory system 5 can be, for example, an solid state drive 35 (SSD) or SD<sup>TM</sup> card.

The memory controller 2 controls the semiconductor memory 1. The memory controller 2 receives instructions from the host device 3, and controls the semiconductor memory 1 based on the received instructions.

## <1.1.1. Memory Controller>

The memory controller 2 includes a host interface 21, a central processing unit (CPU) 22, a random access memory (RAM) 23, a read only memory (ROM) 24, a memory interface 25, and an error correction code (ECC) circuit 26. 45 The memory controller 2 executes various operations and some of the functions of the host interface 21 and the memory interface 25 by causing the CPU 22 to execute firmware (or, programs) stored in the ROM 24 and loaded in the RAM 23. The RAM 23 further temporarily stores data 50 and functions as a buffer memory and a cash memory.

The host interface 21 is connected to the host device 3 via a bus and controls communications between the memory controller 2 and the host device 3. The memory interface 25 is connected to the semiconductor memory 1 and controls 55 communications between the memory controller 2 and the semiconductor memory 1.

The ECC circuit 26 performs processing required to detect and correct errors in data written in the semiconductor memory 1 and data read from the semiconductor memory 1. 60 More specifically, the ECC circuit 26 generates redundant data for correcting an error in data to be written in the semiconductor memory 1 (or, substantial write data). The generated redundant data and the substantial write data are then written in the semiconductor memory 1. The ECC 65 circuit 26 detects an error in data read from the semiconductor memory 1, and tries to correct an error if any.

4

#### <1.1.2. Semiconductor Memory>

The semiconductor memory 1 includes components such as a memory cell array 11, an input and output circuit 12, a sequencer 13, a driver 15, a sense amplifier 16, and a row decoder 19.

The memory cell array 11 includes memory blocks BLK such as BLK0, BLK1 . . . . Each block BLK is a set of string units SU such as SU0, SU1, . . . . Each string unit SU is a set of NAND strings STR such as STR0, STR1, . . . (not shown). The string STR includes memory cell transistors MT

The input and output circuit 12 is connected to the memory controller 2 via a NAND bus. The NAND bus transmits control signals and a signal DQ having a width of eight bits. The control signals include signals —CE, CLE, ALE, —WE, —RE, and —WP and data strobe signals DQS and —DQS. The symbol "—" indicates inverted logic. The input and output circuit 12 receives and receives the signal DQ. The input and output circuit 12 receives some control signals from the memory controller 2 and fetches and outputs the signal DQ based on the received control signals. The signal DQ includes a command (CMD), write or read data (DAT), address (ADD), and status (STA).

The sequencer 13 receives the command CMD and the address ADD from the input and output circuit 12, and controls driver 15, the sense amplifier 16, and the row decoder 19 based on the received command CMD and the address ADD.

The driver 15 supplies a selected one of potentials to the row decoder 19. The row decoder 19 receives various potentials from the driver 15 and the address ADD from the input and output circuit 12, and transfers the potential from the driver 15 to one block BLK selected based on the received address ADD.

The sense amplifier 16 senses a state of memory cell transistors MT, generates read data based on the sensed state, and transfers write data to the memory cell transistors MT. <1.1.3. Memory Cell Array>

FIG. 2 shows an example of several components and connections in the memory cell array 11 according to the first embodiment, and shows components and connections in one block BLK0 and associated components. A plurality of blocks BLK, for example, all blocks BLK, each include the components and the connections shown in FIG. 2.

One block BLK includes a plurality of (for example, four) string units SU0 to SU3.

In each block BLK, each of p (where p is a natural number) bit lines BL0 to BL(p-1) is connected to one string STR from each of the string units SU0 to SU3.

Each string STR includes one select gate transistor ST, a plurality of, for example, eight memory cell transistors MT such as MT0 to MT7, and one select gate transistor DT such as DT0, DT1, DT2, or DT3. The transistors ST, MT, and DT are coupled in series in this order between a source line CELSRC and one bit line BL. A memory cell transistor MT includes a control gate electrode (word line WL) and a charge storage layer insulated from the surroundings, and can store data in a nonvolatile manner based on the amount of charge in the charge storage layer.

The strings STR respectively coupled to different bit lines BL constitute one string unit SU. In each string unit SU, the control gate electrodes of the memory cell transistors MT0 to MT7 are respectively coupled to word lines WL0 to WL7. In addition, in each block BLK, word lines WL with the same address in different string units SU are coupled to each other. A set of memory cell transistors MT sharing a word line WL in one string unit SU is referred to as a cell unit CU.

Transistors DT0 to DT3 respectively belong to the string units SU0 to SU3. In each case with  $\alpha$ =0 to 3, the gates of respective transistors DT $\alpha$  of respective strings STR of a string unit SU $\alpha$  is coupled to a select gate line SGDL $\alpha$ . The gates of the transistors ST are coupled to a select gate line 5 SGSL.

#### <1.1.4. Cell Transistors>

The memory cell transistors MT will be described with reference to FIG. 3. The semiconductor memory 1 can store data of two bits or more in one memory cell transistor MT. FIG. 3 shows a distribution of the threshold voltages of the memory cell transistors MT each storing four-bit data as a result of data write in the memory system 5 according to the first embodiment. The threshold voltage of each memory cell transistor MT has a value corresponding to the stored 15 data. When storing four-bit data per memory cell transistor MT, each memory cell transistor MT can have one of  $2^4=16$ threshold voltages. The 16 threshold voltages respectively correspond to states of storing "1111" data, "1110" data, "1010" data, "1000" data, "1001" data, "0001" data, "0000" 20 data, "0010" data, "0110" data, "0100" data, "1100" data, "1101" data, "0101" data, "0111" data, "0011" data, and "1011" data. The memory cell transistors MT respectively storing "1111" data, "1110" data, "1010" data, "1000" data, "1001" data, "0001" data, "0000" data, "0010" data, "0110" data, "0100" data, "1100" data, "1101" data, "0101" data, "0111" data, "0011" data, and "1011" data are referred to as being in Er, A, B, C, D, E, F G, H, I, J, K, L, M, N, and O states. The memory cell transistors MT in Er, A, B, C, D, E, F G, H, I, J, K, L, M, N, and O states respectively have 30 higher threshold voltages in this order.

Even a plurality of memory cell transistors MT that store identical four-bit data can have different threshold voltages due to variations in the characteristics of the memory cell transistors MT. Referring to FIG. 3 and subsequent drawings, although the distribution of threshold voltages is indicated by a continuous curve, the numbers of memory cell transistors MT are discrete.

In order to determine the data stored in a memory cell transistor MT as a read target, the state of the memory cell 40 transistor MT is determined. The state determination is performed by using read voltages VA, VB, VC, VD, VE, VF, VG, VH, VI, VJ, VK, VL, VM, VN, and VO. A voltage having a magnitude to be applied to the memory cell transistor MT as a read target to determine the state of the 45 memory cell transistor MT, including read voltages VA, VB, VC, VD, VE, VF, VG, VH, VI, VI, VK, VL, VM, VN, and VO may be referred as a read voltage VCGR hereinafter.

The read voltage VA is higher than the highest threshold voltage of the memory cell transistor MT in Er state, and is 50 lower than the lowest threshold voltage of the memory cell transistor MT in A state immediately after the write.

The read voltage VB is higher than the highest threshold voltage of the memory cell transistor MT in A state immediately after the write, and is lower than the lowest threshold 55 voltage of the memory cell transistor MT in B state immediately after the write.

The read voltage VC is higher than the highest threshold voltage of the memory cell transistor MT in B state immediately after the write, and is lower than the lowest threshold ovltage of the memory cell transistor MT in C state immediately after the write.

The read voltage VD is higher than the highest threshold voltage of the memory cell transistor MT in C state immediately after the write, and is lower than the lowest threshold 65 voltage of the memory cell transistor MT in D state immediately after the write.

6

The read voltage VE is higher than the highest threshold voltage of the memory cell transistor MT in D state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in E state immediately after the write.

The read voltage VF is higher than the highest threshold voltage of the memory cell transistor MT in E state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in F state immediately after the write.

The read voltage VG is higher than the highest threshold voltage of the memory cell transistor MT in F state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in G state immediately after the write.

The read voltage VH is higher than the highest threshold voltage of the memory cell transistor MT in G state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in H state immediately after the write.

The read voltage VI is higher than the highest threshold voltage of the memory cell transistor MT in H state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in I state immediately after the write.

The read voltage VJ is higher than the highest threshold voltage of the memory cell transistor MT in I state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in J state immediately after the write.

The read voltage VK is higher than the highest threshold voltage of the memory cell transistor MT in J state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in K state immediately after the write

The read voltage VL is higher than the highest threshold voltage of the memory cell transistor MT in K state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in L state immediately after the write.

The read voltage VM is higher than the highest threshold voltage of the memory cell transistor MT in  $\rm L$  state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in M state immediately after the write.

The read voltage VN is higher than the highest threshold voltage of the memory cell transistor MT in M state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in N state immediately after the write.

The read voltage VO is higher than the highest threshold voltage of the memory cell transistor MT in N state immediately after the write, and is lower than the lowest threshold voltage of the memory cell transistor MT in O state immediately after the write.

The read voltages VA, VB, VC, VD, VE, VF, VG, VH, VI, VJ, VK, VL, VM, VN, and VO are, for example, default voltages. Read using the read voltage VX (where X is A, B, C, D, E, F, G, H, I, J, K, L, M, N, or O) is referred to as X read (XR).

A state of the memory cell transistor MT as a read target (selected memory cell transistor) is determined by determining in which range the threshold voltage of the memory cell transistor MT falls. In order to determine a range in which the threshold voltage of the selected memory cell transistor MT falls, it is determined whether the threshold voltage exceeds a read voltage VCGR. The memory cell transistor

MT having a threshold voltage equal to or higher than the read voltage VCGR maintains an OFF state even while receiving the read voltage VCGR at its control gate electrode. In contrast to this, the memory cell transistor MT having a threshold voltage lower than the read voltage 5 VCGR is turned on while receiving the read voltage VCGR at its control gate electrode. A voltage VREAD is applied to the word line WL of memory cell transistors MT of cell units CU as a non-read target, and is higher than the threshold voltages of the memory cell transistors MT in any states.

A set of data of bits at the same position (digit) of the memory cell transistors MT of one cell unit CU constitutes one page. A set of data of bits at the most significant (first digit) position of the memory cell transistors MT of each cell unit CU is referred to as a top page. A set of data of bits at 15 the second digit from the most significant digit of the memory cell transistors MT of each cell unit CU is referred to as an upper page. A set of data of bits at the third digit from the most significant digit of the memory cell transistors MT of each cell unit CU is referred to as a middle page. A 20 set of data of bits at the least significant (fourth digit) position of the memory cell transistors MT of each cell unit CU is referred to as a lower page.

The data of each page is determined by read using a plurality of read voltages VCGR with different magnitudes. 25 The following is an example. Data obtained by X read is referred to as X read data XD.

Each bit of a lower page is determined as "1" data when it is determined that the threshold voltage of the selected memory cell transistor MT storing the data of that bit falls 30 within the range of lower than the read voltage VA, the range of the read voltage VD or higher and lower than the read voltage VF, or the range of the read voltage VK or higher. Each bit of a lower page is determined as "0" data when it is determined that the threshold voltage of the selected 35 memory cell transistor MT storing the data of the bit falls within the range of the read voltage VA or higher and lower than the read voltage VD, or the range of the read voltage VF or higher and lower than the read voltage VK. In order to MT, the read voltage VCGR at the boundary between a state determined as "0" data and a state determined as "1" data is used. Lower page read uses, for example, A read, D read, F read, and K read. The state of the selected memory cell transistor MT can be determined by the logical operation of 45 A read data AD, D read data DD, F read data FD, and K read data KD.

The same applies to other pages. Middle page data is determined by using, for example, C read, G read, I read, and M read. Upper page data is determined by using, for 50 BLK. example, B read, H read, and N read. Top page data is determined by using, for example, E read, J read, L read, and

A plurality of reads required to identify the data stored in a page, such as a set of A read, D read, F read, and K read 55 and controls the ECC circuit 26 to try to correct an error in in the case of low page read, are referred to as boundary reads required for the page.

The threshold voltage of the memory cell transistor MT can change due to factors such as disturbances from immediately after the write and/or a lapse of time. The threshold 60 voltage of a memory cell transistor MT can be erroneously determined as being in a state different from a state intended at the time of write depending on how the threshold voltage changes.

## <1.1.5. Sense Amplifier>

FIG. 4 shows components and connections in the sense amplifier 16 according to the first embodiment. The sense

amplifier 16 includes p sense amplification circuits SAC, data latches DL, such as DL0, DL1, DL2, ..., DLq (where q is a natural number), p arithmetic circuits LC, and one data latch XDL. In each case in which  $\beta$  is between 0 and q, a data latch DLβ includes p data latch circuits DLβC. The data latch XDL includes p data latch circuits XDLC. The data latch circuits DLβC and XDLC temporarily store data.

Each bit line BL is coupled to one sense amplification circuits SAC, q+1 data latch circuits DL0C, DL1C, DL2C, ..., DLqC, one arithmetic circuit LC, and one data latch circuit XDLC.

Each sense amplification circuit SAC is electrically coupled to one selected memory cell transistor MT via one bit line BL coupled to the sense amplification circuit SAC during data read. Each sense amplification circuit SAC senses a voltage of a magnitude determined based on the threshold voltage of the selected memory cell transistor MT on a node in the sense amplification circuit SAC, and determines, based on the sense result, to which one of two states the memory cell transistor MT electrically coupled to the sense amplification circuit SAC belongs. The two states of the memory cell transistor MT are respectively expressed by "0" data and "1" data. Each sense amplification circuit SAC stores information indicating that read data is "0" data or "1" data in a data latch circuit DLC coupled to the sense amplification circuit SAC.

The arithmetic circuit LC can perform a logical operation for data in the data latch circuits DLC and XDLC coupled to the arithmetic circuit LC. Logical operations include a NOT operation, a logical OR operation, a logical AND operation, an exclusive XOR operation, and an exclusive NOR operation.

<1.2. Operation>

FIG. 5 shows a flowchart for an operation of the memory system according to the first embodiment. FIG. 5, in particular, shows a flowchart concerning data read from a page in a cell unit CU of a string unit SU of a block BLK. Some of the steps will be described in detail later.

As shown in FIG. 5, in step S1, the memory controller 2 determine the state of the selected memory cell transistor 40 instructs the semiconductor memory 1 to perform read from a page in a cell unit CU., the memory controller 2 transmits a command set for read to the semiconductor memory 1. The read command set specifies the cell unit CU as a read target and a page as a read target. A read target cell unit CU and a read target page are respectively referred to as a selected cell unit CU and a selected page. In addition, the string unit SU including the selected cell unit CU is referred to as a selected string unit SU, and the block BLK including the selected string unit SU is referred to as a selected block

> In step S2, upon receiving the read command set, the semiconductor memory 1 reads data from the selected page, and transmits the read data to the memory controller 2.

> In step S3, the memory controller 2 receives the read data, the received read data.

> If no error is included or error correction has succeeded (YES branch of step S4), the data written in the selected page is obtained. Written data, i.e., data including no error or having undergone error correction, will be referred to as errorless data hereinafter. When errorless data is obtained, the flowchart in FIG. 5 comes to an end.

> When the error correction fails in step S4 (NO branch of step S4), the process goes to step S5. In step S5, the memory controller 2 determines, by estimation, the read voltage VCGR to be used next. The read voltage VCGR is estimated with an expectation to acquire errorless data from the data

9

read from the selected page by using the read voltage VCGR. The details of step S5 will be described later. For a case of storing four-bit data per memory cell transistor MT, in order to read data from one page, three or four read voltages (boundary read voltages) VCGR for three or four 5 boundary reads are required. For this reason, step S5 includes estimating three or four boundary read voltages VCGR.

In step S6, the memory controller 2 instructs the semiconductor memory 1 to perform shift read using the read 10 voltages VCGR estimated in step S5. Shift read is read using a read voltages VCGR differing in magnitude from a standard (for example, default) read voltage VCGR while specifying an adjustment for the standard read voltage VCGR. The read voltages VCGR used for shift read are referred to 15 as shift read voltages VCGRS. In order to perform shift read, the memory controller 2 transmits a command set for shift read to the semiconductor memory 1. A shift read command set specifies the selected cell unit CU, a selected page, and differences  $\Delta V$  between the standard read voltages VCGR 20 and the shift read voltages VCGRS. In storing four-bit data per memory cell transistor MT, a shift read command set specifies three or four differences  $\Delta V$  for three or four boundary read voltages.

In step S7, upon receiving the shift read command set, the 25 semiconductor memory 1 reads data from the selected page by using the shift read voltages VCGRS, i.e., performs shift read with respect to the selected page, and transmits the read data to the memory controller 2. The read data obtained by shift read is referred to as shift read data.

In step S8, the memory controller 2 receives shift read data and controls the ECC circuit 26 to try to correct an error in the received data. When shift read data including no error (errorless shift read data) is obtained (YES branch of step S8), the flowchart in FIG. 5 comes to an end. When error 35 correction fails (NO branch of step S8), the process goes to step S9.

In step S9, the memory controller 2 tries to correct an error in the data from the selected page by using another method. Upon completion of step S9, the flowchart in FIG. 40 5 comes to an end.

# <1.2.1. Details of Step S2 (Read)>

The read in step S2 varies depending on whether a lower page, middle page, upper page, or top page is selected. Each of four cases will be described below.

## <1.2.1.1. Details of Read from Lower Page>

FIG. 6 shows voltages applied to the word line (selected word line) WL coupled to the selected cell unit CU in step S2 along the time when a lower page is selected according to the first embodiment.

In the period shown in FIG. 6, the voltages required to perform read from a selected page of the selected cell unit CU are applied to associated components. For example, a voltage VSG is applied to a select gate line SGDL coupled to the selected string unit SU of the selected block BLK over 55 the period from time t101 to time t105. The voltage VSG has a magnitude that turns on the selected gate transistor DT. In addition, the voltage VREAD is applied to unselected word lines WL among the word lines WL over the period from time t101 to time t105. With the application of such voltages, 60 the strings STR of the selected string unit SU are electrically coupled between respective bit lines BL and the cell source line CELSRC.

As shown in FIG. 6, a read voltage VA0 is applied to the selected word line WL over the period from time t101 to 65 time t102. Read voltages VAw, with w (where w is 0 or a natural number) representing different values, have different

10

magnitudes. The read voltage VAw may have the same magnitude as that of a read voltage VA, or a magnitude different from that of the read voltage VA. For example, when the read voltage VA as a default voltage is used for read in step S2, the magnitude of the read voltage VA0 is the same as that of the read voltage VA.

As a result of application of the read voltage VA0, when a selected memory cell transistor MT is turned on, a current flows from the corresponding bit line BL to the source line CELSRC, and when it remains off, no such a current flows. The sense amplifier 16 determines whether this current flows. Based on this determination, it is determined whether the threshold voltage of the selected memory cell transistor MT is lower than the read voltage VA0, or equal to or higher than the read voltage VA0.

Read using a read voltage VXw is referred to as Xw read. The data obtained by A0 read is stored in a first data latch DL of the data latches DL0 to DLq. "0" data is obtained from the selected memory cell transistor MT having a threshold voltage equal to or higher than the read voltage VA0, and "1" data is obtained from the memory cell transistor MT having a threshold voltage lower than the read voltage VA0. The data obtained from each selected memory cell transistor MT is stored in the data latch circuit DLC coupled to the bit line BL coupled to the memory cell transistor MT in the first data latch DL.

A read voltage VD0 is applied to the selected word line WL over the period from time t102 to time t103 to perform D0 read and obtain D0 read data. A read voltage VF0 is applied to the selected word line WL over the period from time t103 to time t104 to perform F0 read and obtain F0 read data. A read voltage VK0 is applied to the selected word line WL over the period from time t104 to time t105 to perform K0 read and obtain K0 read data. The A0 read data, the D0 read data, the F0 read data, and the K0 read data are respectively stored in the different ones of the data latches DL0 to DLa.

Subsequently, the data of the lower page of the selected cell unit CU is obtained based on the A0 read data, the D0 read data, the F0 read data, and the K0 read data. The data read from the lower page by using the read voltages VAw, VDw, VFw, and VKw is referred to as lower page read data LDw.

## <1.2.1.2. Details of Read from Middle Page>

FIG. 7 shows voltages applied to the selected word line WL along the time in step S2 when a middle page is selected according to the first embodiment.

In the period shown in FIG. 7, the voltages required to perform read from a selected page of the selected cell unit CU are applied to associated components as described with reference to FIG. 6.

As shown in FIG. 7, a read voltage VC0 is applied to the selected word line WL over the period from time t201 to time t202 to perform C0 read and obtain C0 read data. A read voltage VG0 is applied to the selected word line WL over the period from time t202 to time t203 to perform G0 read and obtain G0 read data. A read voltage VI0 is applied to the selected word line WL over the period from time t203 to time t204 to perform I0 read and obtain I0 read data. A read voltage VM0 is applied to the selected word line WL over the period from time t204 to time t205 to perform M0 read and obtain M0 read data.

Subsequently, the data of the middle page of the selected cell unit CU is obtained based on the C0 read data, the G0 read data, the I0 read data, and the M0 read data. The data

read from the middle page by using read voltages VCw, VGw, VIw, and VMw is referred to as middle page read data MDw  $\,$

<1.2.1.3. Details of Read from Upper Page>

FIG. **8** shows voltages applied to the selected word line <sup>5</sup> WL along the time in step S**2** when an upper page is selected according to the first embodiment.

In the period shown in FIG. **8**, the voltages required to perform read from a selected page of the selected cell unit CU are applied to associated components as described with reference to FIG. **6**.

As shown in FIG. **8**, a read voltage VB**0** is applied to the selected word line WL over the period from time t**301** to time t**302** to perform B**0** read and obtain B**0** read data. A read voltage VH**0** is applied to the selected word line WL over the period from time t**302** to time t**303** to perform H**0** read and obtain H**0** read data. A read voltage VN**0** is applied to the selected word line WL over the period from time t**303** to time t**304** to perform N**0** read and obtain N**0** read data.

Subsequently, the data of the upper page of the selected cell unit CU is obtained based on the B0 read data, the H0 read data, and the N0 read data. The data read from the upper page by using read voltages VBw, VHw, and VNw is referred to as upper page read data UDw.

<1.2.1.4. Details of Read from Top Page>

FIG. 9 shows voltages applied to the selected word line WL along the time in step S2 when a top page is selected according to the first embodiment.

In the period shown in FIG. 9, the voltages required to 30 perform read from a selected page of the selected cell unit CU are applied to associated components as described with reference to FIG. 6.

As shown in FIG. 9, a read voltage VE0 is applied to the selected word line WL over the period from time t401 to 35 1. time t402 to perform E0 read and obtain E0 read data. A read voltage VJ0 is applied to the selected word line WL over the period from time t402 to time t403 to perform J0 read and obtain J0 read data. A read voltage VL0 is applied to the selected word line WL over the period from time t403 to 40 m time t404 to perform L0 read and obtain L0 read data. A read voltage VO0 is applied to the selected word line WL over the period from time t404 to time t405 to perform O0 read and obtain O0 read data.

Subsequently, the data of the top page of the selected cell  $\,^{45}$  unit CU is obtained based on the EQ read data, the J0 read data, the L0 read data, and the O0 read data. The data read from the top page by using read voltages VE0, VJ0, VL0, and VO0 is referred to as top page read data TD0.

<1.2.2. Details of Step S5 (Read Voltage Estimation)>

The read voltage estimation in step S5 differs depending on which one of a lower page, a middle page, an upper page, and a top page is selected. Each of the four cases will be described below.

<1.2.2.1. When Selected Page is Lower Page>

FIG. 10 is a sub-flowchart for step S5 when a lower page is selected according to the first embodiment. As shown in FIG. 10, the NO branch of step S4 goes to step S5101.

The memory controller **2** performs single state read several times on the selected page through several steps 60 from step S**5101**. Single state read indicates the operation of obtaining X read data XD from the semiconductor memory **1** unlike data read from a page.

In step S5101, the memory controller 2 instructs B read on the selected cell unit CU. To this end, the memory controller 2 transmits, to the semiconductor memory 1, a command to instruct B read on the selected cell unit CU.

12

In step S5102, upon receiving the B read command, the semiconductor memory 1 performs B read on the selected cell unit CU to obtain B read data BD, and transmits the B read data BD to the memory controller 2. The memory controller 2 stores the B read data BD in the RAM 23.

In step S5103, the memory controller 2 transmits, to the semiconductor memory 1, a command to instruct  $\rm E$  read on the selected cell unit CU.

In step S5104, upon receiving the E read command, the semiconductor memory 1 performs E read on the selected cell unit CU to obtain E read data ED, and transmits the E read data ED to the memory controller 2. The memory controller 2 stores the E read data ED in the RAM 23.

In step S5105, the memory controller 2 transmits, to the semiconductor memory 1, a command to instruct H read on the selected cell unit CU.

In step S5106, upon receiving the H read command, the semiconductor memory 1 performs H read on the selected cell unit CU to obtain H read data HD, and transmits the H read data HD to the memory controller 2. The memory controller 2 stores the H read data HD in the RAM 23.

Step S5106 continues at step S5111. The memory controller 2 performs shift read Z (where Z is a natural number) times from step S5111 to step S5115. For example, Z is 5. The following description is based on this example. In each shift read, the memory controller 2 specifies shift amounts  $\Delta VA$ ,  $\Delta VD$ ,  $\Delta VF$ , and  $\Delta VK$ . Shift amounts  $\Delta VA$ ,  $\Delta VD$ ,  $\Delta VF$ , and  $\Delta VK$  in each shift read are different from shift amounts  $\Delta VA$ ,  $\Delta VD$ ,  $\Delta VF$ , and  $\Delta VK$  in another shift read. The following is an example of executing each shift read with the shift amounts  $\Delta VA$ ,  $\Delta VD$ ,  $\Delta VF$ , and  $\Delta VK$  which are different from those in another shift read.

In step S5111, the memory controller 2 sets a parameter z (where z is a natural number equal to or lower than Z) to

In step S5112, the memory controller 2 instructs lower page read (lower page shift read) LSRz using shift read voltages in the zth loop on the selected cell unit CU. For the lower page shift read LSRz, the memory controller 2 transmits a shift read command set to the semiconductor memory 1. The shift read command set specifies a selected page and shift amounts  $\Delta VAz$ ,  $\Delta VDz$ ,  $\Delta VFz$ , and  $\Delta VKz$ . The shift amounts  $\Delta VAz$ ,  $\Delta VDz$ ,  $\Delta VFz$ , and  $\Delta VKz$  are respectively added to standard read voltages VA, VD, VF, and VK in lower page shift read LSRz.

In step S5113, the semiconductor memory 1 performs lower page shift read LSRz on the selected cell unit CU with the shift amounts ΔVAz, ΔVDz, ΔVFz, and ΔVKz. That is, the semiconductor memory 1 performs lower page read with shift read voltages VAz, VDz, VFz, and VKz instead of the read voltages VA, VD, VF, and VK. The shift read voltage VAZ is VA+ΔVAz. The shift read voltage VDz is VD+ΔVDz. The shift read voltage VFz is VF+ΔVFz. The shift read voltage VKz is VK+ΔVKz. The data obtained by lower page shift read LSRz is referred to as lower page shift read data LSDz. The semiconductor memory 1 transmits the lower page shift read data LSDz to the memory controller 2.

In step S5114, the memory controller 2 determines whether 2 is Z. When  $z\neq Z$  (NO branch of step S5114), the memory controller 2 sets Z=z+1 in step S5115. The process returns to step S5112. When z=Z (YES branch of step S5114), the process goes to step S5121. When the process goes to step S5121, the memory controller 2 should store lower page shift read data LSD1, LSD2, LSD3, LSD4, and LSD5.

In step S5121, the memory controller 2 masks particular bits of the lower page shift read data LSD1 to SLD5 with the

B read data BD, the E read data ED, and the H read data HD. To this end, the memory controller 2 performs logical operations using the B read data BD, the E read data ED, the H read data HD, and the lower page shift read data LSD1 to LSD5. Performing the logical operations will produce separation data ADs such as ADs1, ADs2, ADs3, ADs4, and ADs5, separation data DDs such as DDs1, DDs2, DDs3, DDs4, and DDs5, separation data FDs such as FDs1, FDs2, FDs3, FDs4, and FDs5, and separation data KDs such as KDs1, KDs2, KDs3, KDs4, and KDs5. Separation data 10 ADsz, DDsz, FDsz, and KDsz each are formed from part of the lower page shift read data LSDz. A method of obtaining the separation data ADs, DDs, FDs, and KDs will be described later. The memory controller 2 stores the obtained separation data ADs, DDs, FDs, and KDs in the RAM 23. 15

In step S5122, the memory controller 2 calculates bit counts BCA1, BCA2, BCA3, BCA4, BCA5, BCD1, BCD2, BCD3, BCD4, BCD5, BCF1, BCF2, BCF3, BCF4, BCF5, BCK1, BCK2, BCK3, BCF4, and BCK5 with the separation data ADs, DDs, FDs, and KDs. The method for the calcu- 20 S5102, S5104, S5106, and S5113. Each square in FIG. 12 lation will be described later.

In step S5123, the memory controller 2 determines boundary read voltages VAS, VDS, VFS, and VKS with the bit counts BCA1, BCA2, BCA3, BCA4, BCA5, BCD1, BCD2, BCD3, BCD4, BCD5, BCF1, BCF2, BCF3, BCF4, 25 BCF5, BCK1, BCK2, BCK3, BCF4, and BCK5. The method for the determination will be described later.

The memory controller 2 then calculates shift amounts  $\Delta VAS$ ,  $\Delta VDS$ ,  $\Delta VFS$ , and  $\Delta VKS$ . The shift amount  $\Delta VAS$ is VAS-VA. The shift amount  $\Delta$ VDS is VDS-VD. The shift 30 amount  $\Delta VFS$  is VFS-VF. The shift amount  $\Delta VKS$  is VKS-VK.

Step S5123 continues at step S6. When step S6 follows step S5123, the memory controller 2 specifies the shift amounts  $\Delta VAS$ ,  $\Delta VDS$ ,  $\Delta VFS$ , and  $\Delta VKS$  in step S6.

In step S6, the shifted boundary read voltages VAS, VDS, VFS, and VKS are used. A boundary read voltage VXS that is shifted is referred to as shifted boundary read voltage

The set of steps S5101 and S5102, the set of steps S5103 40 and S5104, and the set of steps S5105 and S5106 can be performed in any order differently from the order described with reference to FIG. 10.

The set of steps S5111, S5112, S5113, S5114, and S5115 may be performed before the set of steps S5101, S5102, 45 S5103, S5104, S5105, and S5106. In this case, the NO branch of step S4 continues at step S5111, YES branch of step S5114 continues at step S5101, and step S5106 continues at step S5121.

<1.2.2.1.1. Shift Read>

FIG. 11 shows voltages applied to the selected word line WL along the time in step S5113 according to the first

As described with reference to FIG. 6, while the voltage is applied to the selected word line WL, for example, the 55 voltage VSG is applied to the select gate line SGDL coupled to the selected string unit SU of the selected block BLK, and the voltage VREAD is applied to the unselected word lines

As shown in FIG. 11, voltage application for lower page 60 shift read LSR1 is performed in the period from time t111 to time t115, and voltage application for lower page shift read LSR2 is performed in the subsequent period from time t121 to time t125. Subsequently, voltage application for lower page shift read LSR3 is performed in the period from time 65 t131 to time t135 (not shown), and voltage application for lower page shift read LSR4 is performed in the period from

14

time t141 to time t145 (not shown). Voltage application for lower page shift read LSR5 is then performed in the period from time t151 to time t155.

In the example in FIG. 11, in each of cases in which z=1, 2, and 3, the shift amounts  $\Delta VAz$ ,  $\Delta VDz$ ,  $\Delta VF$ , and  $\Delta VK$ have negative magnitudes.

In each of cases in which y is natural numbers from 1 to 5, a read voltage VAy is applied to the selected word line WL over the period from time t1y1 to time t1y2 to perform Ay read. A read voltage VDy is applied to the selected word line WL over the period from time  $t1\gamma2$  to time  $t1\gamma3$  to perform Dy read. A read voltage VPy is applied to the selected word line WL over the period from time t1y3 to time t1y4 to perform Fy read. A read voltage VKy is applied to the selected word line WL over the period from time t1y4 to time t1y5 to perform Ky read.

<1.2.2.1.2. Data Read from Semiconductor Memory>

FIG. 12 shows an example of data obtained by steps indicates 1-bit data read from a selected memory cell transistor MT having a threshold voltage in the range corresponding to the square.

As shown in FIG. 12, the B read data BD has "1" data in each bit read from a memory cell transistor MT having a threshold voltage lower than the read voltage VB, and has "0" data in each bit read from a memory cell transistor MT having a threshold voltage equal to or higher than the read voltage VB.

The E read data ED has "1" data in each bit read from a memory cell transistor MT having a threshold voltage lower than the read voltage VE, and has "0" data in each bit read from a memory cell transistor MT having a threshold voltage equal to or higher than the read voltage VE.

The H read data HD has "1" data in each bit read from a memory cell transistor MT having a threshold voltage lower than the read voltage VH, and has "0" data in each bit read from a memory cell transistor MT having a threshold voltage equal to or higher than the read voltage VH.

The lower page shift read LSR1 uses read voltages VA1, VD1, VF1, and VK1 different from the read voltages VA, VD, VF, and VK. In performing read from a memory cell transistor MT having a threshold voltage, when different read voltages are used, bits obtained by the read can have different values. For this reason, the boundary (to be referred to as the boundary voltage hereinafter) between the threshold voltage of the memory cell transistor MT that reads out "1" data and the threshold voltage of the memory cell transistor MT that reads out "0" data in the lower page shift 50 read data LSD1 is different from the boundary voltage in lower page read data LD0. More specifically, the boundary voltage in the lower page shift read data LSD1 is lower than that in the lower page read data LD0.

Likewise, the boundary voltages in the lower page shift read data LSD2, LSD3, LSD4, and LSD5 are different from those in the lower page shift read data LSD1. For example, the lower page shift read data LSD1, LSD2, LSD3, LSD4, and LSD5 have higher threshold voltages in the order named.

<1.2.2.1.3. Separation Data Operation>

FIGS. 13, 14, 15, and 16 each show an example of data obtained by step S5121 according to the first embodiment. FIGS. 13, 14, 15, and 16 respectively show examples of the separation data ADs, DDs, FDs, and KDs.

The memory controller 2 performs, for example, the following logical operations in the RAM 23 to generate the separation data ADs, DDs, FDs, and KDs.

<1.2.2.1.3.1. Separation Data ADs Calculation> The separation data ADs can be obtained by equation (1).

$$ADs = LSD & BD$$

(1)

The operator "&" indicates an AND operation on two operands on both sides. In each of cases in which γ is natural numbers from 1 to 5, the memory controller **2** obtains <sup>10</sup> separation data ADsγ by calculating ADsγ=LSDγ & BD.

As shown in FIG. 13, the separation data ADs1, ADs2, ADs3, ADs4, and ADs5 respectively have different numbers of "1" data bits. When the numbers of "1" data bits differ, the numbers of "O" data bits also differ. In particular, the 15 separation data ADs1, ADs2, ADs3, ADs4, and ADs5 differ in the number of "1" data bits read from the memory cell transistors MT having threshold voltages between the read voltage VA1 and the read voltage VA5. The separation data ADs1, ADs2, ADs3, ADs4, and ADs5 in each of the remaining bits have the same value.

The separation data ADs1 has no "1" data in bits read from memory cell transistors MT having threshold voltages between the read voltage VA1 and the read voltage VA5.

The separation data ADs2 has "1" data in a bit read from 25 a memory cell transistor MT having a threshold voltage between the read voltage VA1 and the read voltage VA2.

The separation data ADs3 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VA1 and the read voltage VA3.

The separation data ADs4 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VA1 and the read voltage VA4.

The separation data ADs5 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage <sup>35</sup> between the read voltage VA1 and the read voltage VA5.

The number of "1" data bits in the bits read from the memory cell transistors MT having threshold voltages between the read voltage VA1 and the read voltage VA5 increases in the order of the separation data ADs1, ADs2, 40 ADs3, ADs4, and ADs5. This makes it possible to use the separation data ADs1 to ADs5 to estimate the number of memory cell transistors MT having threshold voltages with the same magnitudes as those of the read voltages VA2 to VA5 in the selected cell unit CU.

<1.2.2.1.3.2. Separation Data DDs Calculation> The separation data DDs can be obtained by equation (2).

$$DDs = (LSD \& ^{-}BD) \& ED$$

(2)

The memory controller **2** obtains separation data DDs $\gamma$  by calculating DDs $\gamma$ =(LSD $\gamma$  & —BD) & ED in each of cases in which  $\gamma$  is natural numbers from 1 to 5.

As shown in FIG. 14, the separation data DDs1, DDs2, DDs3, DDs4, and DDs5 respectively have different numbers of "1" data bits. In particular, the separation data DDs1, DDs2, DDs3, DDs4, and DDs5 differ in the number of "0" data bits read from the memory cell transistors MT having 60 threshold voltages between the read voltage VD1 and the read voltage VD5. The separation data DDs1, DDs2, DDs3, DDs4, and DDs5 in each of the remaining bits have the same value.

The separation data DDs1 has no "0" data in bits read 65 from memory cell transistors MT having threshold voltages between the read voltage VD1 and the read voltage VD5.

16

The separation data DDs2 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VD1 and the read voltage VD2.

The separation data DDs3 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VD1 and the read voltage VD3.

The separation data DDs4 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VD1 and the read voltage VD4.

The separation data DDs5 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VD1 and the read voltage VD5.

The number of "0" data bits in the bits read from the memory cell transistors MT having threshold voltages between the read voltage VD1 and the read voltage VD5 increases in the order of the separation data DDs1, DDs2, DDs3, DDs4, and DDs5. This makes it possible to use the separation data DDs1 to DDs5 to estimate the number of memory cell transistors MT having threshold voltages with the same magnitudes as those of the read voltages VD2 to VD5 in the selected cell unit CU.

<1.2.2.1.3.3. Separation Data FDs Calculation>

The separation data FDs can be obtained by equation (3).

$$FDs = (LSD \& ^-ED) \& HD$$

(3)

The memory controller **2** obtains separation data FDs $\gamma$  by calculating FDs $\gamma$ =(LSD $\gamma$  & —ED) & HD in each of cases in which  $\gamma$  is natural numbers from 1 to 5.

As shown in FIG. 15, the separation data FDs1, FDs2, FDs3, FDs4, and FDs5 respectively have different numbers of "1" data bits. In particular, the separation data FDs1, FDs2, FDs3, FDs4, and FDs5 differ in the number of "1" data bits read from the memory cell transistors MT having threshold voltages between the read voltage VF1 and the read voltage VF5. The separation data FDs1, FDs2, FDs3, FDs4, and FDs5 in each of the remaining bits have the same value.

The separation data FDs1 has no "1" data in bits read from memory cell transistors MT having threshold voltages between the read voltage VF1 and the read voltage VF5.

The separation data FDs2 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VF1 and the read voltage VF2.

The separation data FDs3 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VF1 and the read voltage VF3.

The separation data FDs4 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VF1 and the read voltage VF4.

The separation data FDs5 has "1" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VF1 and the read voltage VF5.

The number of "1" data bits in the bits read from the memory cell transistors MT having threshold voltages between the read voltage VF1 and the read voltage VF5 increases in the order of the separation data FDs1, FDs2, FDs3, FDs4, and FDs5. This makes it possible to use the separation data FDs1 to FDs5 to estimate the number of memory cell transistors MT having threshold voltages with the same magnitudes as those of the read voltages VF2 to VF5 in the selected cell unit CU.

<1.2.2.1.3.4. Separation Data KDs Calculation> The separation data KDs can be obtained by equation (4).

$$KDs = LSD \& ^-HD$$

(4)

The memory controller 2 obtains separation data KDs $\gamma$  by calculating KDs $\gamma$ =LSD $\gamma$  & —HD in each of cases in which  $\gamma$  is natural numbers from 1 to 5.

As shown in FIG. 16, the separation data KDs1, KDs2, KDs3, KDs4, and KDs5 respectively have different numbers of "0" data bits. In particular, the separation data KDs1, KDs2, KDs3, KDs4, and KDs5 differ in the number of "0" data bits read from the memory cell transistors MT having 15 threshold voltages between the read voltage VK1 and the read voltage VK5. The separation data KDs1, KDs2, KDs3, KDs4, and KDs5 in each of the remaining bits have the same value.

The separation data KDs1 has no "0" data in bits read 20 from memory cell transistors MT having threshold voltages between the read voltage VK1 and the read voltage VK5.

The separation data KDs2 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VK1 and the read voltage VK2. 25

The separation data KDs3 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VK1 and the read voltage VK3.

The separation data KDs4 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage 30 between the read voltage VK1 and the read voltage VK4.

The separation data KDs5 has "0" data in a bit read from a memory cell transistor MT having a threshold voltage between the read voltage VK1 and the read voltage VK5.

The number of "0" data bits in the bits read from the 35 memory cell transistors MT having threshold voltages between the read voltage VK1 and the read voltage VK5 increases in the order of the separation data KDs1, KDs2, KDs3, KDs4, and KDs5. This makes it possible to use the separation data KDs1 to KDs5 to estimate the number of 40 memory cell transistors MT having threshold voltages with the same magnitudes as those of the read voltages VK2 to VK5 in the selected cell unit CU.

<1.2.2.1. Four-Bit Count and Shifted Boundary Read Voltage Estimation>

FIG. 17 is a view for describing processing in steps S5122 and S5123 according to the first embodiment. FIG. 17 shows the processing for estimating shifted boundary read voltages VAS in steps S5122 and S5123.

Part (a) shows a range including a boundary between the 50 distribution of the threshold voltages of the memory cell transistors MT which are written as Er state and the distribution of the threshold voltages of the memory cell transistors MT which are written as A state. Note, however, that the memory controller 2 does not know a distribution shown in 55 part (a).

The memory controller 2 counts "0" data bits or "1" data bits in each of the separation data ADs1 to ADs5. The memory controller 2 can count, for example, the number of "0" data bits or the number of "1" data bits which increases 60 in ascending order of the separation data ADs1 to ADs5. When counting in the separation data ADs1 to ADs5, the memory controller 2 can count "1" data in each of the separation data ADs1 to ADs5.

Part (b) shows an example of the counts. The bit count 65 BCA1 is the number of "1" data bits in the separation data based on VA1 read data, i.e., the separation ADs1. The bit

18

count BCA2 is the number of "1" data bits in the separation data ADs2. The bit count BCA3 is the number of "1" data bits in the separation data ADs3. The bit count BCA4 is the number of "1" data bits in the separation data ADs4. The bit count BCA5 is the number of "1" data bits in the separation data ADs5.

The memory controller 2 then calculates the differences between specific pairs of the bit counts BCA1, BCA2, BCA3, BCA4, and BCA5. More specifically, the memory controller 2 calculates BCA2–BCA1, BCA3–BCA2, BCA4–BCA3, and BCA5–BCA4. Part (c) shows an example of the calculation result.

Each difference represents the number of memory cell transistors MT that are turned on first at corresponding threshold voltages. For example, BCA2-BCA1 represents the number of memory cell transistors MT that are not turned on at the read voltage VA1 but turned on at the read voltage VA2. Based on this, the memory controller 2 regards each difference as the number of corresponding memory cell transistors MT. For example, BCA2-BCA1 is regarded as the number of memory cell transistors MT having a threshold voltage with the same magnitude as that of the read voltage VA2. The relationships between such differences and threshold voltages equivalently represent the numbers of memory cell transistors MT respectively having threshold voltages with the same magnitudes as those of the read voltages VA2, VA3, VA4, and VA5. Part (d) shows these relationships.

The number of memory cell transistors MT having a threshold voltage with the same magnitude as that of the read voltage VA2 is BCA2–BCA1=C1. Likewise, the number of memory cell transistors MT having a threshold voltage with the same magnitude as that of the read voltage VA3 is BCA3–BCA2=C2. The number of memory cell transistors MT having a threshold voltage with the same magnitude as that of the read voltage VA4 is BCA4–BCA3=C3. The number of memory cell transistors MT having a threshold voltage with the same magnitude as that of the read voltage VA5 is BCA5–BCA4=C4.

The memory controller 2 then detects the smallest one of the counts C1 to C4 as a valley position (a local minimum position), and determines to use a threshold voltage corresponding to the valley position as the shifted boundary read voltage VAS.

The processing described with reference to FIG. 17 is performed on a set of the separation data DDs1 to DDs5, a set of the separation data FDs1 to FDs5, and a set of the separation data KDs1 to KDs5. As a result, the shifted boundary read voltages VDS, VFS, and VKS can be determined in the same manner of determining the shifted boundary read voltage VAS.

<1.2.2.2. When Selected Page is Middle Page>

FIG. 18 is a sub-flowchart for step S5 when a middle page is selected according to the first embodiment. As shown in FIG. 18, the NO branch of step S4 goes to step S5201. A procedure for determining shifted boundary read voltages when a middle page is selected is almost the same as the procedure for determining the shifted boundary read voltages when the lower page is selected. Accordingly, differences from the processing shown in FIG. 10 will be mainly described below.

The memory controller 2 obtains the E read data ED, the H read data HD, and the K read data KD in steps S5201 to S5206. Steps S5201, S5202, S5203, and S5204 are respectively the same as steps S5103, S5104, S5105, and S5106 in FIG. 10. In step S5205, the memory controller 2 instructs K read instead of E read in step S5201. In step S5206, the

memory controller 2 executes K read and transmits the K read data KD instead of executing E read and transmitting the E read data ED in step S5202.

The memory controller 2 performs shift read Z times in steps S5211 to 35215 as in steps S5111 to S5115 in FIG. 10. Shift amounts  $\Delta VC, \Delta VG, \Delta VI,$  and  $\Delta VM$  in each shift read are different from shift amounts  $\Delta VC, \Delta VG, \Delta VI,$  and  $\Delta VM$  in another shift read.

In step S5211, the memory controller 2 sets z to 1 as in step S5111 in FIG. 10.

Step S5212 is similar to step S5112 in FIG. 10. In step S5212, the memory controller 2 instructs middle page read (middle page shift read) MSRz using shift read voltages in the zth loop on the selected cell unit CU. In middle page shift read MSRz, the memory controller 2 specifies shift amounts  $\Delta VCz$ ,  $\Delta VGz$ ,  $\Delta VIz$ , and  $\Delta VMz$ .

Step S5213 is similar to step S5113 in FIG. 10. In step S5213, the semiconductor memory 1 performs middle page shift read MSRz on the selected cell unit CU with the shift amounts  $\Delta VCz$ ,  $\Delta VGz$ ,  $\Delta VIz$ , and  $\Delta VMz$ . That is, the semiconductor memory 1 performs middle page shift read with shift read voltages  $\Delta VCz$ ,  $\Delta VGz$ ,  $\Delta VIz$ , and  $\Delta VMz$  instead of the read voltages VC, VG, VI, and VM. The shift read voltage VCz is VC+ $\Delta VCz$ . The shift read voltage VGz 25 is VG+ $\Delta VGz$ . The shift read voltage VMz is VM+ $\Delta VMz$ . The data obtained by middle page shift read MSRz is referred to as middle page shift read data MSDz.

Steps 35214 and S5215 are the same as steps S5114 and 30 S5115 in FIG. 10. When z≠Z (NO branch of step S5214), the memory controller 2 sets z=z+1 in step S5215. The process then returns to step S5212. When z=Z (YES branch of step S5214), the process goes to step S5221. When the process goes to step S5221, the memory controller 2 should store 35 middle page shift read data MSD1, MSD2, MSD3, MSD4, and MSD5.

Step S5221 is similar to step S5121 in FIG. 10. In step S5221, the memory controller 2 masks particular bits of the middle page shift read data MSD1 to MSD5 with the E read 40 data ED, the H read data HD, and the K read data KD as in step S5121. To this end, the memory controller 2 performs logical operations using the E read data ED, the H read data HD, the K read data KD, and the middle page shift read data MSD1 to MSD5. Performing the logical operations will 45 produce separation data CDs such as CDs1, CDs2, CDs3, CDs4, and CDs5, GDs such as GDs1, GDs2, GDs3, GDs4, and GDs5, IDs such as IDs1, IDs2, IDs3, IDs4, and IDs5, and MDs such as MDs1, MDs2, MDs3, MDs4, and MDs5. Separation data CDsz, GDsz, IDsz, and MDsz each are 50 formed from part of the middle page shift read data MSDz. A method of obtaining the separation data CDs, GDs, IDs, and MDs will be described later. The memory controller 2 stores the obtained separation data CDs, GDs, IDs, and MDs in the RAM 23.

Step S5222 is similar to step S5122 in FIG. 10. In step S5222, the memory controller 2 calculates bit counts BCC1, BCC2, BCC3, BCC4, BCC5, BCG1, BCG2, BCG3, BCG4, BCG5, BCI1, BCI2, BCI3, BCI4, BCI5, BCM1, BCM2, BCM3, BCM4, and BCM5 with the separation data CDs, 60 GDs, IDs, and MDs as in step S5122.

Step S5223 is similar to step S5123 in FIG. 10. In step S5223, the memory controller 2 determines shifted boundary read voltages VCS, VGS, VIS and VMS with the bit counts BCC1, BCC2, BCC3, BCC4, BCC5, BCG1, BCG2, 65 BCG3, BCG4, BCG5, BCI1, BCI2, BCI3, BCI4, BCI5, BCM1, BCM2, BCM3, BCM4, and BCM5 as in step S5123.

The memory controller 2 then calculates shift amounts  $\Delta VCS$ ,  $\Delta VGS$ ,  $\Delta VIS$ , and  $\Delta VMS$ . The shift amount  $\Delta VCS$  is VCS-VC. The shift amount  $\Delta VGS$  is VGS-VG. The shift amount  $\Delta VIS$  is VIS-VI. The shift amount  $\Delta VMS$  is VMS-VM.

Step S5223 continues at step S6. When step S6 follows step S5223, the memory controller 2 specifies the shift amounts  $\Delta$ VCS,  $\Delta$ VGS,  $\Delta$ VIS, and  $\Delta$ VMS in step S6.

The set of steps S5201 and S5202, the set of steps S5203 and S5204, and the set of steps S5205 and S5206 can be performed in any order differently from the order described with reference to FIG. 18.

The set of steps S5211, S5212, S5213, S5214, and S5215 may be performed before the set of steps S5201, S5202, S5203, S5204, S5205, and S5206. In this case, NO branch of step S4 continues at step S5211, YES branch of step S5214 continues at step S5201, and step S5206 continues at step S5221.

<1.2.2.2.1. Shift Read>

FIG. 19 shows voltages applied to the selected word line WL along the time in step S5213 according to the first embodiment.

As described with reference to FIG. 6, while the voltage is applied to the selected word line WL, for example, the voltage VSG is applied to the select gate line SGDL coupled to the selected string unit SU of the selected block BLK, and the voltage VREAD is applied to the unselected word lines WL.

As shown in FIG. 19, voltage application for middle page shift read MSR1 is performed in the period from time t211 to time t215, and voltage application for middle page shift read MSR2 is performed in the subsequent period from time t221 to time t225. Subsequently, voltage application for middle page shift read MSR3 is performed in the period from time t231 to time t235 (not shown), and voltage application for middle page shift read MSR4 is performed in the period from time t241 to time t245 (not shown). Voltage application for middle page shift read MSR5 is then performed in the period from time t251 to time t255.

In the example in FIG. 19, in each of cases in which z=1, 2, and 3, the shift amounts  $\Delta VCz$ ,  $\Delta VGz$ ,  $\Delta VI$ , and  $\Delta VM$  have negative magnitudes.

Likewise, in each of cases in which  $\gamma$  is natural numbers from 1 to 5 (inclusive), a read voltage VC $\gamma$  is applied to the selected word line WL over the period from time t2 $\gamma$ 1 to time t2 $\gamma$ 2 to perform C $\gamma$  read. A read voltage VG $\gamma$  is applied to the selected word line WL over the period from time t2 $\gamma$ 2 to time t2 $\gamma$ 3 to perform G $\gamma$  read. A read voltage VI $\gamma$ 1 is applied to the selected word line WL over the period from time t2 $\gamma$ 3 to time t2 $\gamma$ 4 to perform I $\gamma$  read. A read voltage VM $\gamma$ 1 is applied to the selected word line WL over the period from time t2 $\gamma$ 4 to time t2 $\gamma$ 5 to perform My read.

<1.2.2.2. Separation Data Calculation>

In step S**5221**, the memory controller **2** performs, for example, the following logical operations in the RAM **23** to generate the separation data CDs, GDs, IDs, and MDs.

The separation data CDs can be obtained by equation (5).

$$CDs\gamma = MSD \& ED$$

(5)

The memory controller **2** obtains separation data CDsγ by calculating CDsγ=MSDγ & ED in each of cases in which γ is natural numbers from 1 to 5. The separation data CDs**1**, CDs**2**, CDs**3**, CDs**4**, and CDs**5** have different numbers of "1" data (and "0" data) bits.

The separation data GDs can be obtained by equation (6).

$$GDs = (MSD \& ^-ED) \& HD$$

(6)

The memory controller **2** obtains separation data GDs $\gamma$  by calculating GDs $\gamma$ =(MSD $\gamma$  & —ED) & HD in each of cases in which  $\gamma$  is natural numbers from 1 to 5. The separation data GDs**1**, GDs**2**, GDs**3**, GDs**4**, and GDs**5** have different 10 numbers of "1" data (and "0" data) bits.

The separation data IDs can be obtained by equation (7).

$$IDs = (MSD \& ^-HD) \& KD$$

(7)

The memory controller **2** obtains separation data IDsγ by calculating IDsγ=(MSDγ & —HD) &KD in each of cases in which γ is natural numbers from 1 to 5. The separation data <sup>20</sup> IDs**1**, IDs**2**, IDs**3**, IDs**4**, and IDs**5** have different numbers of "1" data (and "0" data) bits.

The separation data MDs can be obtained by equation (8).

$$MDs = MSD \quad \& \quad ^-KD \tag{8}$$

The memory controller **2** obtains separation data MDsγ by calculating MDsγ=MSDγ & —KD in each of cases in which 30 γ is natural numbers from 1 to 5. The separation data MDs**1**, MDs**2**, MDs**3**, MDs**4**, and MDs**5** have different numbers of "1" data (and "0" data) bits.

In each of cases in which  $\delta$  is C, G, I, and M, the numbers of "1" data (or "0" data) bits read from memory cell 35 transistors MT having threshold voltages between a read voltage VS1 and a read voltage V55 increase in the order of separation data  $\delta Ds1$ ,  $\delta Ds2$ ,  $\delta Ds3$ ,  $\delta Ds4$ , and  $\delta Ds5$ . Accordingly, the separation data  $\delta Ds1$  to  $\delta Ds5$  can be used to estimate the numbers of memory cell transistors MT having 40 threshold voltages with the same magnitudes as those of read voltages V $\delta 2$  to V $\delta 5$  in the selected cell unit CU.

<1.2.2.2.3. Identification of Bit Counts and Shifted Boundary Read Voltages>

The memory controller **2** performs the processing 45 described with reference to FIG. **17** on a set of the separation data CDs**1** to CDs**5**, a set of the separation data GDs**1** to GDs**5**, a set of the separation data IDs**1** to IDs**5**, and a set of the separation data MDs**1** to MDs**5**. As a result, the shifted boundary read voltages VCS, VGS, VIS, and VMS can be 50 determined in the same manner as determining the shifted boundary read voltage VAS.

<1.2.2.3. When Selected Page is Upper Page>

FIG. 20 is a sub-flowchart for step S5 when an upper page is selected according to the first embodiment. As shown in 55 FIG. 20, the NO branch of step S4 goes to step S5301. A procedure for determining shifted boundary read voltages when an upper page is selected is almost the same as the procedure for determining the shifted boundary read voltages when the lower page is selected. Accordingly, differences from the processing shown in FIG. 10 will be mainly described below.

The memory controller 2 obtains the E read data ED and the K read data KD in steps S5301 to S5304. Steps S5301 and S5302 are respectively the same as steps S5103 and 65 S5104 in FIG. 10. In step S5303, the memory controller 2 instructs K read instead of E read in step S5301. In step

22

S5304, the memory controller 2 executes K read and transmits the K read data KD instead of executing E read and transmitting the E read data ED in step S5302.