### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2023/0386544 A1 GODO et al.

#### Nov. 30, 2023 (43) **Pub. Date:**

#### (54) SEMICONDUCTOR DEVICE AND **ELECTRONIC DEVICE**

#### (71) Applicant: SEMICONDUCTOR ENERGY LABORATORY CO., LTD.,

Atsugi-shi, Kanagawa-ken (JP)

(72) Inventors: Hiromichi GODO, Isehara, Kanagawa

(JP); Yoshiyuki KUROKAWA, Sagamihara, Kanagawa (JP); Kazuki TSUDA, Atsugi, Kanagawa (JP); Satoru OHSHITA, Hadano, Kanagawa

(21) Appl. No.: 18/245,098

(22) PCT Filed: Sep. 7, 2021

(86) PCT No.: PCT/IB2021/058112

§ 371 (c)(1),

(2) Date: Mar. 13, 2023

#### Foreign Application Priority Data (30)

| Sep. 18, 2020 | (JP) | 2020-157570 |

|---------------|------|-------------|

| Sep. 18, 2020 | (JP) | 2020-157607 |

| Sep. 18, 2020 | (JP) | 2020-157610 |

#### **Publication Classification**

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | G11C 11/22 | (2006.01) |

|      | H10B 53/30 | (2006.01) |

|      | H10B 51/30 | (2006.01) |

|      | H01L 21/28 | (2006.01) |

|      | H01L 29/78 | (2006.01) |

(52) U.S. Cl.

CPC ...... G11C 11/223 (2013.01); G11C 11/221 (2013.01); G11C 11/2297 (2013.01); H10B *53/30* (2023.02); *H10B 51/30* (2023.02); H01L 29/40111 (2019.08); H01L 29/78391 (2014.09)

#### (57)ABSTRACT

A semiconductor device with low power consumption is provided. The semiconductor device includes a first transistor, a second transistor, and a capacitor. The first transistor includes a first gate and a first back gate, and the second transistor includes a second gate and a second back gate. A gate insulating layer for the first back gate has ferroelectricity. The first transistor has a function of, when being in an off state, retaining a first potential corresponding to first data. The second transistor has a function of making an output current flow between a source and a drain of the second transistor.

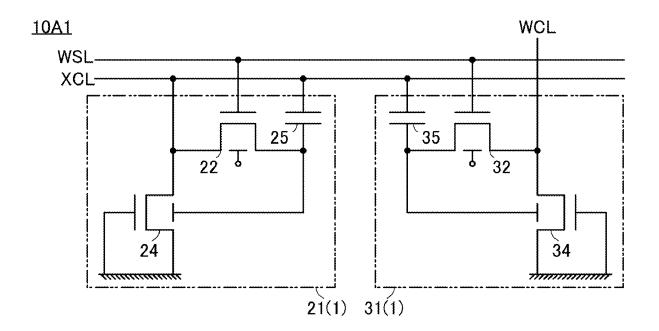

FIG. 1A

FIG. 1B

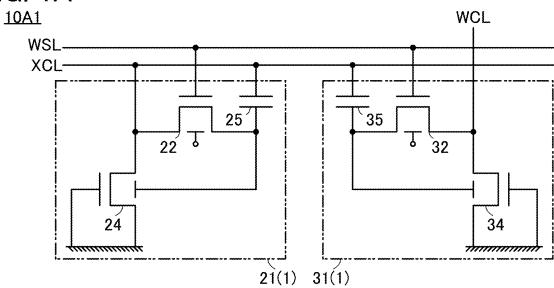

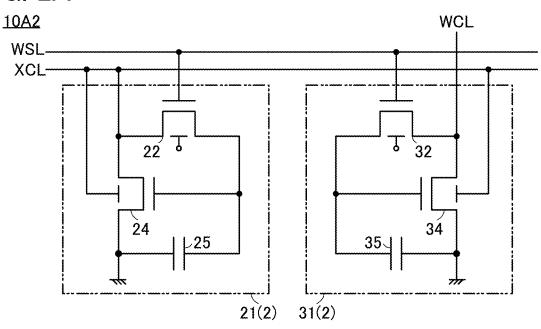

FIG. 2A

FIG. 2B

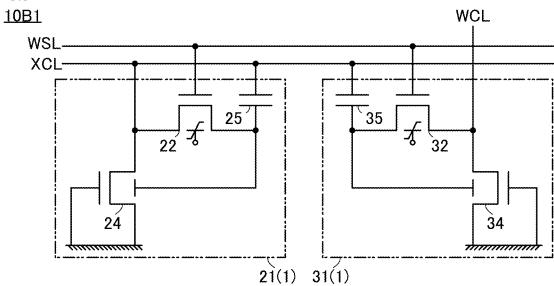

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B WCL 10C1 WSL XCL-25 35 32 22 24 34 21(1) 31(1) M2--HC **NBG** VGL-M1 VCL C1 N2 FEC1 N1 VIL

FIG. 7B  $WCL_1(V_d)$  $WCL_n(V_d)$ 31 21 XCL\_1  $I_{X1}$ C<sub>P</sub> T<sub>W</sub> 21\_1 XCL\_2  $I_{X2}$ 31\_2,1 Ir21 31\_2,n Ir2n 21\_2 XCL\_m  $I_{Xm}$  $\boxed{31\_m,1} \stackrel{I_{rm1}}{}$ 21\_m 31\_m,n 20 30

FIG. 8A

FIG. 8B

FIG. 11A

FIG. 11B

FIG. 12A

FIG. 12B

FIG. 13

FIG. 14

FIG. 15

FIG. 16

# FIG. 17A

## FIG. 17B

FIG. 17C

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 18D

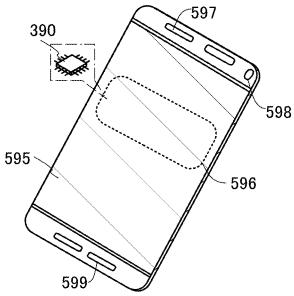

FIG. 19A

FIG. 19B

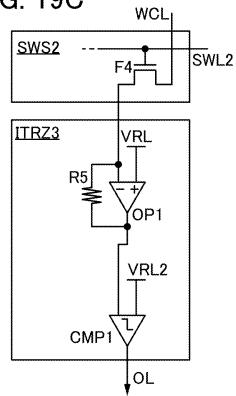

FIG. 19C

FIG. 20

FIG. 21A

<u>100</u>

FIG. 21B

FIG. 22A

FIG. 24

FIG. 26A

Intermediate state New crystalline phase

| Amorphous                | Crystalline                                              | Crystal                          |  |

|--------------------------|----------------------------------------------------------|----------------------------------|--|

| •completely<br>amorphous | •CAAC •nc •CAC excluding single crystal and poly crystal | ∙single crystal<br>•poly crystal |  |

FIG. 26B

FIG. 26C

5nm<sup>-1</sup>

FIG. 27

FIG. 28A

FIG. 28B

FIG. 29A

FIG. 29B

# FIG. 30A

FIG. 30B

FIG. 30C

### SEMICONDUCTOR DEVICE AND ELECTRONIC DEVICE

#### TECHNICAL FIELD

[0001] In this specification, a semiconductor device and the like will be described.

[0002] Note that one embodiment of the present invention is not limited to the above technical field. Examples of the technical field of one embodiment of the present invention disclosed in this specification and the like include a semiconductor device, an imaging device, a display device, a light-emitting device, a power storage device, a memory device, a display system, an electronic device, a lighting device, an input device, an input/output device, a driving method thereof, and a manufacturing method thereof.

#### BACKGROUND ART

[0003] Integrated circuits that imitate the mechanism of the human brain are currently under active development. The integrated circuits incorporate electronic circuits as the brain mechanism and include circuits corresponding to "neurons" and "synapses" of the human brain. Such integrated circuits may therefore be called "neuromorphic", "brain-morphic", or "brain-inspired" circuits. The integrated circuits have a non-von Neumann architecture and are expected to be able to perform parallel processing with extremely low power consumption as compared with a von Neumann architecture, in which power consumption increases with increasing processing speed.

[0004] An information processing model that imitates a biological neural network including "neurons" and "synapses" is called an artificial neural network (ANN). By using an artificial neural network, inference with an accuracy as high as or higher than that of a human can be carried out. In an artificial neural network, the main arithmetic operation is the weighted sum operation of outputs from neurons, i.e., the product-sum operation.

[0005] Non-Patent Document 1 proposes a product-sum operation circuit including a nonvolatile memory cell. Each memory cell of the product-sum operation circuit outputs a current corresponding to a product of data corresponding to a multiplier stored in each memory cell and input data corresponding to a multiplicand by using operation in a subthreshold region of a transistor containing silicon in its channel formation region. With the sum of currents output from the memory cells in each column, data corresponding to product-sum operation is obtained. The product-sum operation circuit includes memory cells therein, and thus does not need to read and write data from and to an external memory when carrying out multiplication and addition. This can decrease the number of times of data transfer for reading, writing, and the like; thus, the power consumption should be reduced.

#### REFERENCE

### Non-Patent Document

[0006] [Non-Patent Document 1] X. Guo et al., "Fast, Energy-Efficient, Robust, and Reproducible Mixed-Signal Neuromorphic Classifier Based on Embedded NOR Flash Memory Technology" IEDM2017, pp. 151-154.

#### SUMMARY OF THE INVENTION

#### Problems to be Solved by the Invention

[0007] An object of one embodiment of the present invention is to provide a semiconductor device with low power consumption. Another object of one embodiment of the present invention is to provide a semiconductor device capable of retaining data for along time. Another object of one embodiment of the present invention is to provide a highly reliable semiconductor device. Another object of one embodiment of the present invention is to provide a novel semiconductor device and the like.

[0008] One embodiment of the present invention does not necessarily achieve all the above objects and only needs to achieve at least one of the objects. The descriptions of the above objects do not preclude the existence of other objects. Objects other than these objects will be apparent from the descriptions of the specification, the claims, the drawings, and the like, and objects other than these objects can be derived from the descriptions of the specification, the claims, the drawings, and the like.

#### Means for Solving the Problems

[0009] One embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, and a capacitor. The first transistor includes a first gate and a first back gate. The second transistor includes a second gate and a second back gate. A gate insulating layer for the first back gate has ferroelectricity. The first transistor has a function of, when being in an off state, retaining a first potential corresponding to first data supplied to the second back gate through the first transistor. The capacitor has a function of changing the first potential retained in the second back gate to a second potential in accordance with a potential change caused by supply of second data to one electrode of the capacitor. The second transistor has a function of making an output current corresponding to a potential of the second back gate flow between a source and a drain of the second transistor. The output current is a current flowing when the second transistor operates in a subthreshold region. A constant potential is supplied to the second gate.

[0010] Another embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, and a capacitor. The first transistor includes a first gate and a first back gate. The second transistor includes a second gate and a second back gate. A gate insulating layer for the first back gate has ferroelectricity. One electrode of the capacitor is electrically connected to the second gate. A constant potential is supplied to the other electrode of the capacitor. The first transistor has a function of, when being in an off state, retaining a first potential corresponding to first data supplied to the second gate through the first transistor. The second transistor has a function of making an output current corresponding to a potential of the second gate flow between a source and a drain of the second transistor. The output current is a current flowing when the second transistor operates in a subthreshold region.

[0011] Another embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, and a capacitor. The first transistor includes a first gate and a first back gate. The second transistor includes a second gate and a second back gate. A gate insulating layer for the first back gate has ferroelectricity. One electrode of

the capacitor is electrically connected to the second back gate. A constant potential is supplied to the other electrode of the capacitor. The first transistor has a function of, when being in an off state, retaining a first potential corresponding to first data supplied to the second back gate through the first transistor. The second transistor has a function of making an output current corresponding to a potential of the second back gate flow between a source and a drain of the second transistor. The output current is a current flowing when the second transistor operates in a subthreshold region.

[0012] In the above embodiment, the semiconductor device may include a circuit, the circuit may be electrically connected to the first gate, and the circuit may have a function of generating a signal controlling on and off of the first transistor.

[0013] In the above embodiment, the gate insulating layer for the first back gate may include an oxide containing one or both of hafnium and zirconium.

[0014] Another embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, a fourth transistor, a first capacitor, a second capacitor, and a ferroelectric capacitor. The first to third transistors each include a gate and a back gate. One of a source and a drain of the first transistor is electrically connected to one of a source and a drain of the second transistor and one electrode of the first capacitor. The other of the source and the drain of the first transistor is electrically connected to the back gate of the second transistor and the other electrode of the first capacitor. The back gate of the first transistor is electrically connected to one of a source and a drain of the third transistor, the back gate of the third transistor, and one of a source and a drain of the fourth transistor. The gate of the third transistor is electrically connected to one electrode of the ferroelectric capacitor. The other of the source and the drain of the fourth transistor is electrically connected to the other electrode of the ferroelectric capacitor and one electrode of the second capacitor. [0015] In the above embodiment, a constant potential may be supplied to the gate of the second transistor.

[0016] Another embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, a fourth transistor, a first capacitor, a second capacitor, and a ferroelectric capacitor. The first to third transistors each include a gate and a back gate. One of a source and a drain of the first transistor is electrically connected to one of a source and a drain of the second transistor. The other of the source and the drain of the first transistor is electrically connected to the gate of the second transistor and one electrode of the first capacitor. The back gate of the first transistor is electrically connected to one of a source and a drain of the third transistor, the back gate of the third transistor, and one of a source and a drain of the fourth transistor. The gate of the third transistor is electrically connected to one electrode of the ferroelectric capacitor. The other of the source and the drain of the fourth transistor is electrically connected to the other electrode of the ferroelectric capacitor and one electrode of the second capacitor.

[0017] Another embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, a fourth transistor, a first capacitor, a second capacitor, and a ferroelectric capacitor. The first to third transistors each include a gate and a back gate. One of a source and a drain of the first transistor is electrically

connected to one of a source and a drain of the second transistor. The other of the source and the drain of the first transistor is electrically connected to the back gate of the second transistor and one electrode of the first capacitor. The back gate of the first transistor is electrically connected to one of a source and a drain of the third transistor, the back gate of the third transistor, and one of a source and a drain of the fourth transistor. The gate of the third transistor is electrically connected to one electrode of the ferroelectric capacitor. The other of the source and the drain of the fourth transistor is electrically connected to the other electrode of the ferroelectric capacitor and one electrode of the second capacitor.

[0018] In the above embodiment, a constant potential may be supplied to the other electrode of the first capacitor.

[0019] In the above embodiment, the semiconductor device may include a circuit, the circuit may be electrically connected to the gate of the first transistor, and the circuit may have a function of generating a signal controlling on and off of the first transistor.

[0020] In the above embodiment, the ferroelectric capacitor may include a dielectric layer, and the dielectric layer may include an oxide containing one or both of hafnium and zirconium.

[0021] In the above embodiment, the first transistor may include a semiconductor layer including a metal oxide in a channel formation region.

[0022] In the above embodiment, the metal oxide may contain In, Ga, and Zn.

[0023] In the above embodiment, the second transistor may include a semiconductor layer containing silicon in a channel formation region.

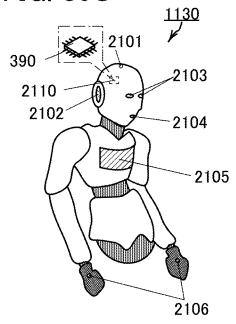

[0024] An electronic device including the semiconductor device of one embodiment of the present invention and a housing, in which arithmetic operation of a neural network is performed by the semiconductor device, is also one embodiment of the present invention.

[0025] Note that other embodiments of the present invention will be shown in the description of the following embodiments and the drawings.

#### Effect of the Invention

[0026] According to one embodiment of the present invention, a semiconductor device with low power consumption can be provided. According to another embodiment of the present invention, a semiconductor device capable of retaining data for a long time can be provided. According to another embodiment of the present invention, a highly reliable semiconductor device can be provided. According to one embodiment of the present invention, a novel semiconductor device and the like can be provided.

**[0027]** The description of a plurality of effects does not preclude the existence of other effects. In addition, one embodiment of the present invention does not necessarily achieve all the effects described as examples. In one embodiment of the present invention, other objects, effects, and novel features are apparent from the description of this specification and the drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0028] FIG. 1A and FIG. 1B are diagrams illustrating structure examples of semiconductor devices.

[0029] FIG. 2A and FIG. 2B are diagrams illustrating structure examples of semiconductor devices.

[0030] FIG. 3A and FIG. 3B are diagrams illustrating structure examples of semiconductor devices.

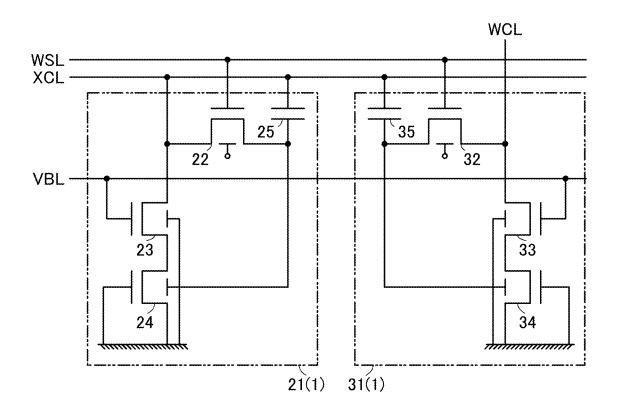

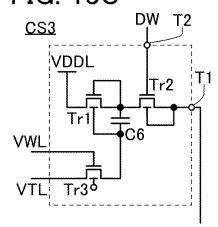

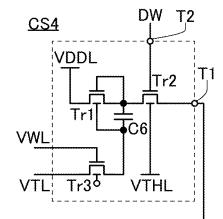

[0031] FIG. 4A and FIG. 4B are diagrams illustrating structure examples of a semiconductor device.

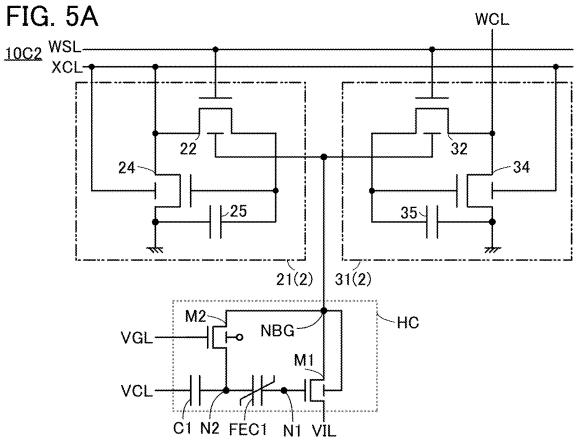

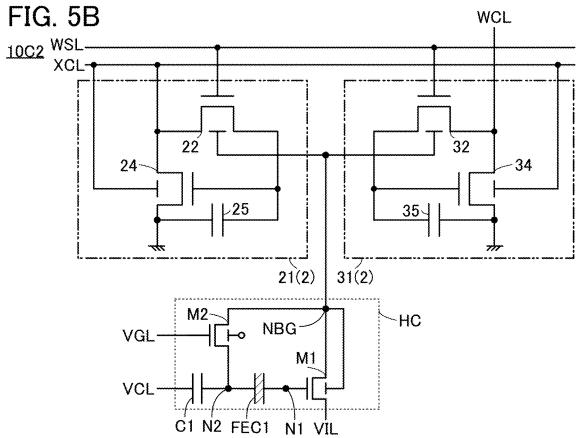

[0032] FIG. 5A and FIG. 5B are diagrams illustrating structure examples of a semiconductor device.

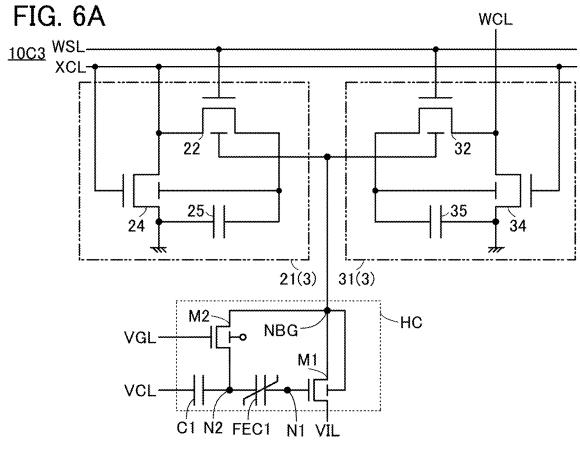

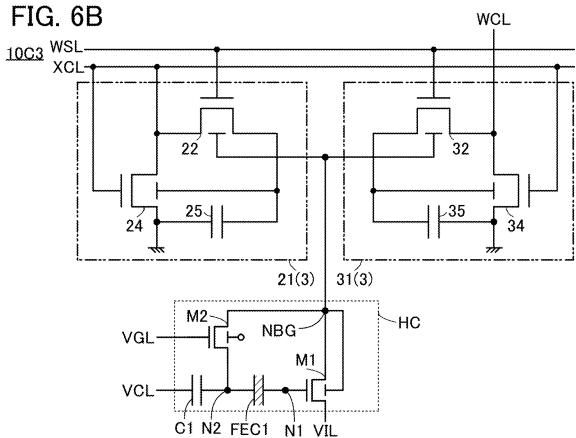

[0033] FIG. 6A and FIG. 6B are diagrams illustrating structure examples of a semiconductor device.

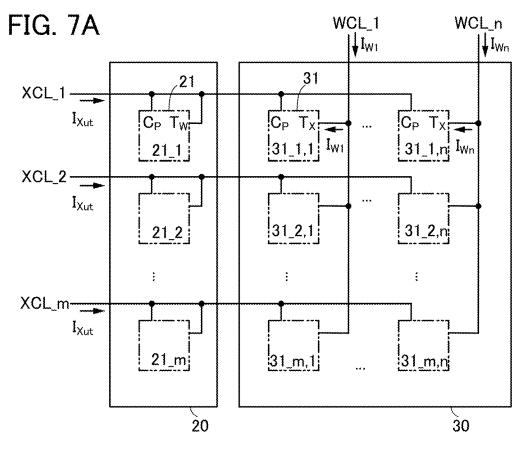

[0034] FIG. 7A and FIG. 7B are diagrams illustrating structure examples of a semiconductor device.

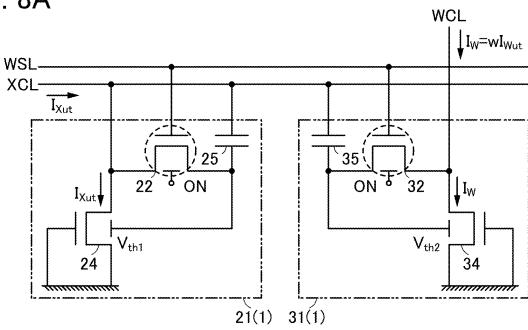

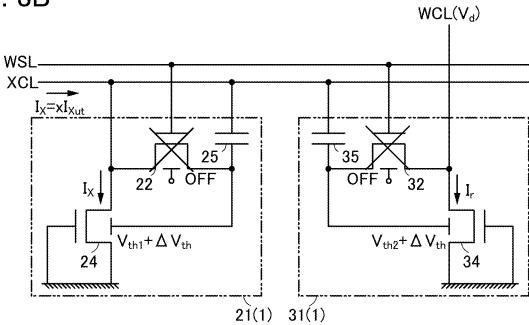

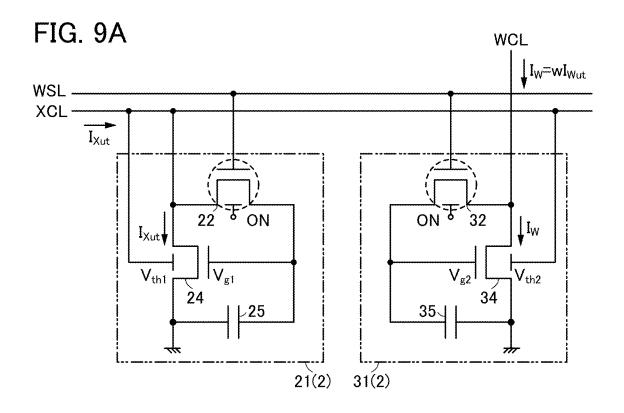

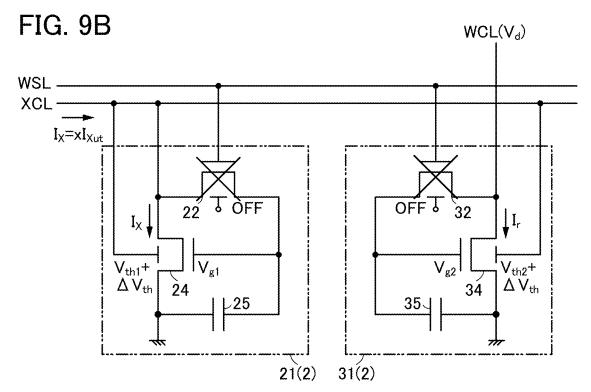

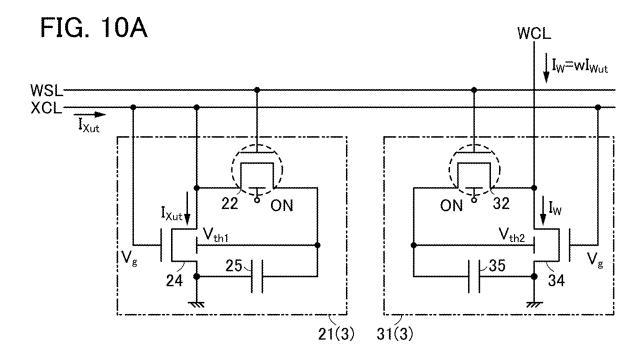

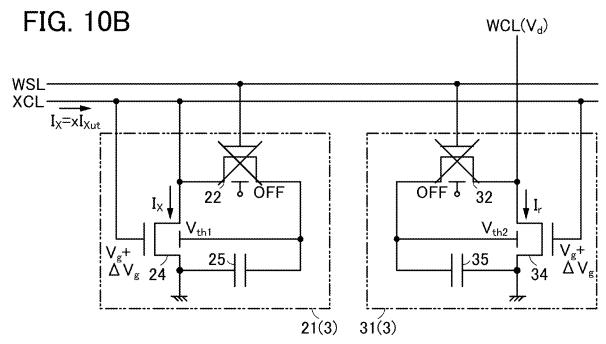

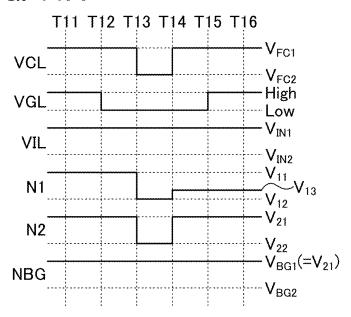

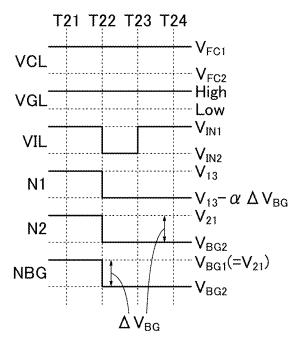

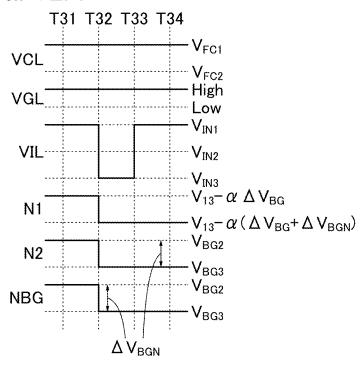

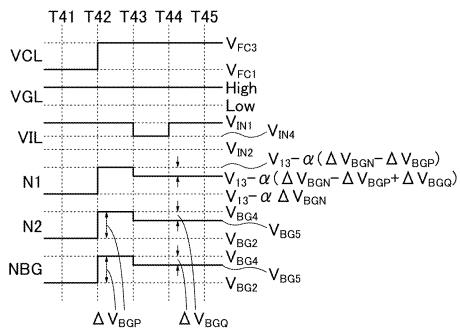

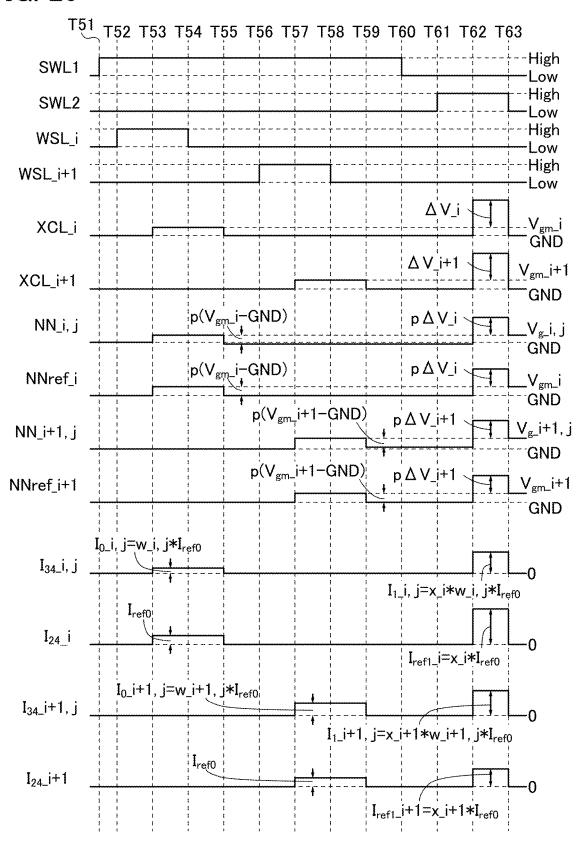

[0035] FIG. 8A and FIG. 8B are diagrams illustrating examples of a method for operating a semiconductor device. [0036] FIG. 9A and FIG. 9B are diagrams illustrating examples of a method for operating a semiconductor device. [0037] FIG. 10A and FIG. 10B are diagrams illustrating examples of a method for operating a semiconductor device. [0038] FIG. 11A and FIG. 11B are diagrams showing examples of a method for operating a semiconductor device. [0039] FIG. 12A and FIG. 12B are diagrams showing examples of a method for operating a semiconductor device. [0040] FIG. 13 is a diagram illustrating a structure example of a semiconductor device.

[0041] FIG. 14 is a diagram illustrating a structure example of a semiconductor device.

[0042] FIG. 15 is a diagram illustrating a structure example of a semiconductor device.

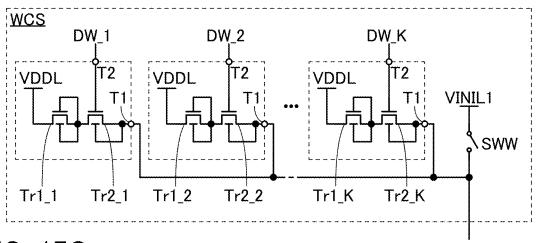

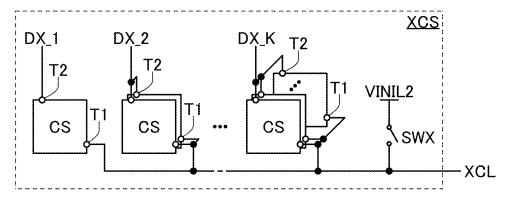

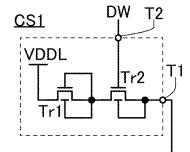

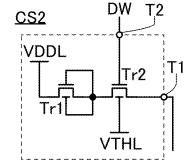

[0043] FIG. 16 is a diagram illustrating a structure example of an arithmetic circuit.

[0044] FIG. 17A, FIG. 17B, and FIG. 17C are diagrams illustrating structure examples of an arithmetic circuit.

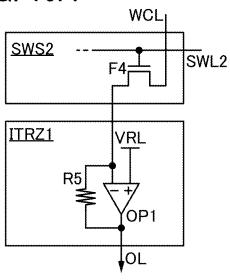

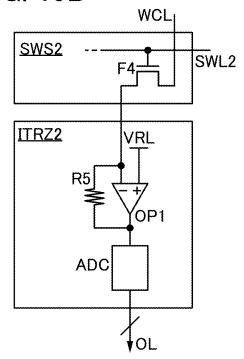

[0045] FIG. 18A, FIG. 18B, FIG. 18C, and FIG. 18D are diagrams illustrating structure examples of arithmetic circuits.

[0046] FIG. 19A, FIG. 19B, and FIG. 19C are diagrams illustrating structure examples of arithmetic circuits.

[0047] FIG. 20 is a diagram illustrating a structure example of an arithmetic circuit.

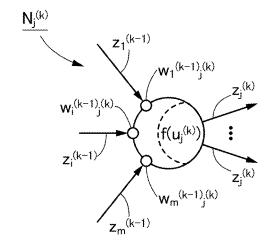

$[0048]\;$  FIG. 21, FIG. 21A, and FIG. 21B are diagrams illustrating a neural network.

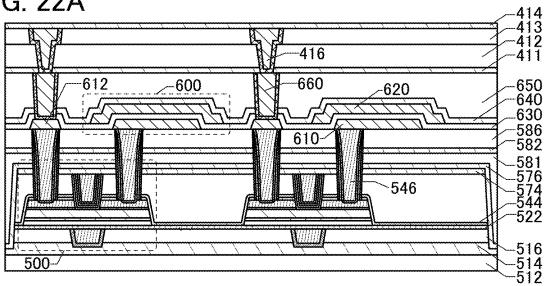

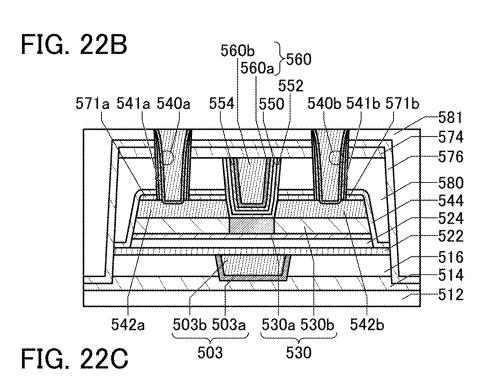

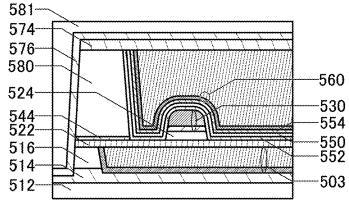

[0049] FIG. 22A is a diagram illustrating a structure example of a semiconductor device. FIG. 22B and FIG. 22C are diagrams illustrating structure examples of transistors.

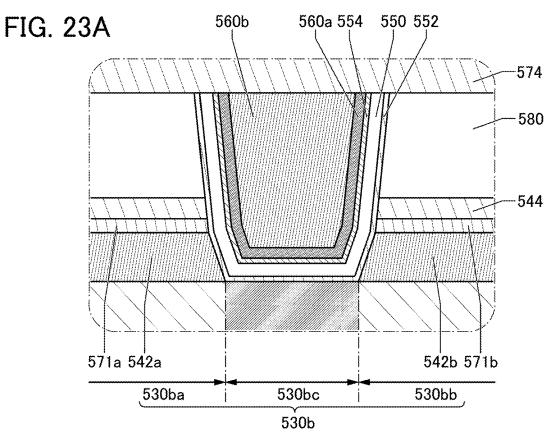

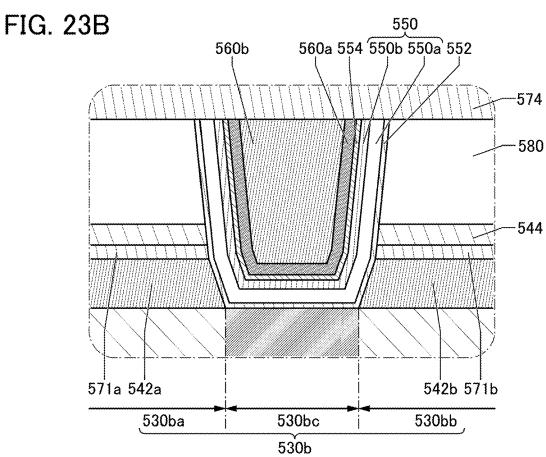

$[0050]~{\rm FIG.~23A}$  and FIG. 23B are diagrams illustrating structure examples of a transistor.

[0051] FIG. 24 is a diagram illustrating a structure example of a transistor.

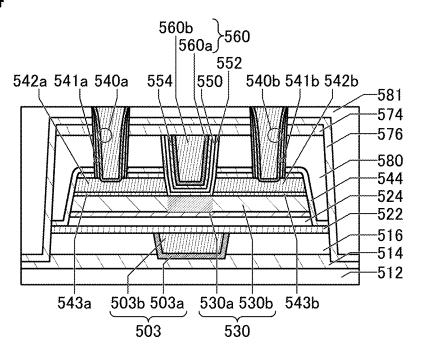

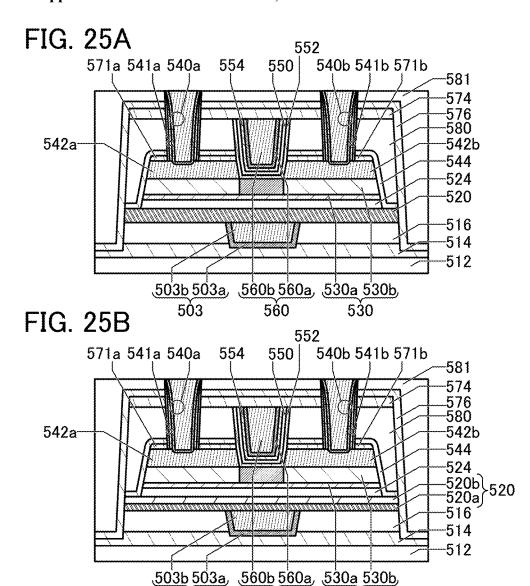

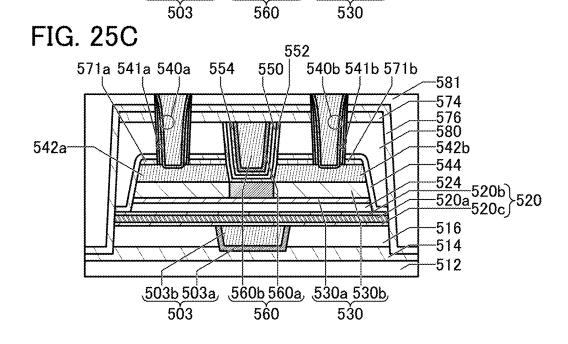

[0052] FIG. 25A to FIG. 25C are diagrams illustrating structure examples of a transistor.

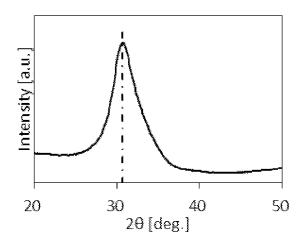

[0053] FIG. 26A is a diagram showing a classification of crystal structures of IGZO. FIG. 26B is a diagram showing an XRD spectrum of crystalline IGZO. FIG. 26C is a diagram showing a nanobeam electron diffraction pattern of crystalline IGZO.

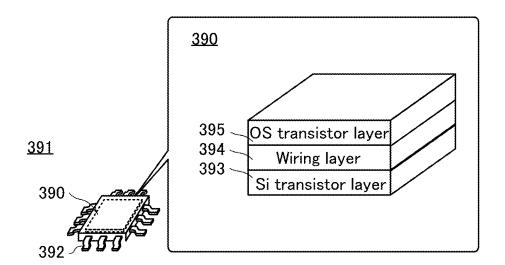

[0054] FIG. 27 is a diagram illustrating a structure example of an integrated circuit.

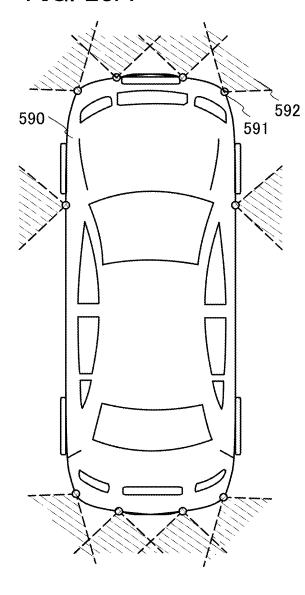

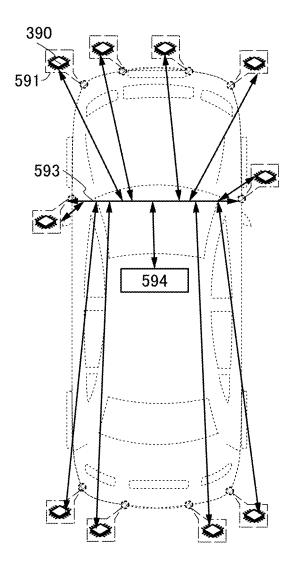

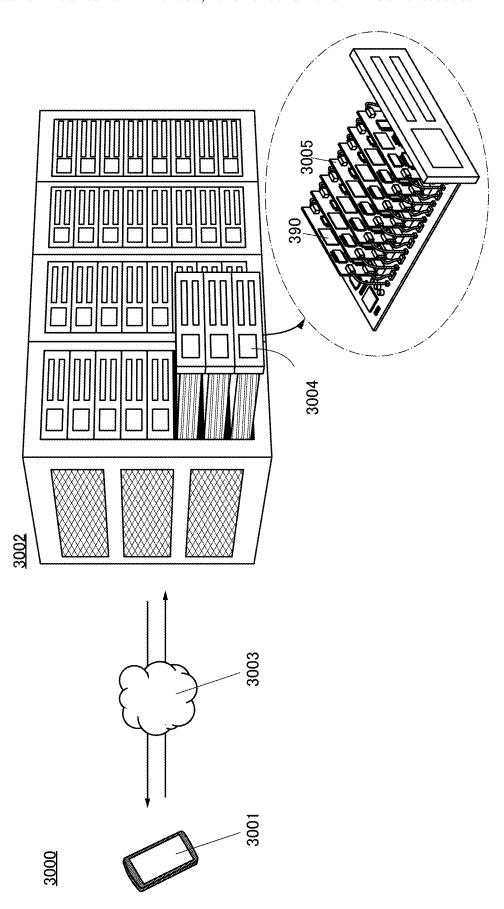

[0055] FIG. 28A and FIG. 28B are diagrams illustrating an application example of an integrated circuit.

[0056] FIG. 29A and FIG. 29B are diagrams illustrating an application example of an integrated circuit.

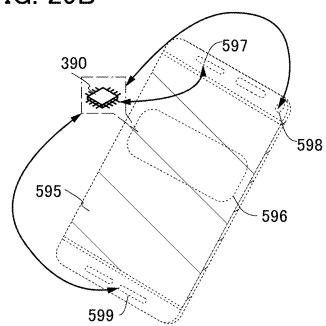

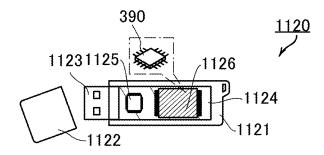

[0057] FIG. 30A, FIG. 30B, and FIG. 30C are diagrams illustrating application examples of an integrated circuit.

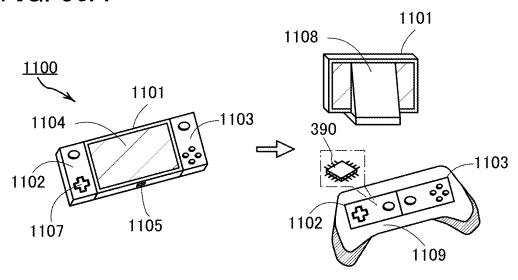

[0058] FIG. 31 is a diagram illustrating an application example of an integrated circuit.

#### MODE FOR CARRYING OUT THE INVENTION

[0059] Embodiments of the present invention will be described below. Note that one embodiment of the present invention is not limited to the following description, and it will be readily understood by those skilled in the art that modes and details of the present invention can be modified in various ways without departing from the spirit and scope of the present invention.

[0060] One embodiment of the present invention therefore should not be construed as being limited to the following description of the embodiments.

[0061] Note that ordinal numbers such as "first", "second", and "third" in this specification and the like are used in order to avoid confusion among components. Thus, the terms do not limit the number of components. Furthermore, the terms do not limit the order of components. In this specification and the like, for example, a "first" component in one embodiment can be referred to as a "second" component in other embodiments or claims. For another example, a "first" component in one embodiment in this specification and the like can be omitted in other embodiments or claims.

[0062] The same components, components having similar functions, components made of the same material, components formed at the same time, and the like in the drawings are denoted by the same reference numerals, and repeated description thereof is omitted in some cases.

[0063] In this specification, for example, a power supply potential VDD may be abbreviated to a potential VDD, VDD, or the like. The same applies to other components (e.g., a signal, a voltage, a circuit, an element, an electrode, and a wiring).

[0064] In the case where a plurality of components are denoted by the same reference numerals, and, particularly when they need to be distinguished from each other, an identification sign such as "\_1", "\_2", "\_n", or "\_m,n" is sometimes added to the reference numerals.

#### Embodiment 1

[0065] The structure, operation, and the like of a semiconductor device of one embodiment of the present invention will be described.

[0066] Note that in this specification and the like, a semiconductor device generally means a device that can function by utilizing semiconductor characteristics. A semiconductor element such as a transistor, a semiconductor circuit, an arithmetic device, and a memory device are each one embodiment of a semiconductor device. It can be sometimes said that a display device (a liquid crystal display device, a light-emitting display device, and the like), a projection device, a lighting device, an electro-optical device, a power storage device, a memory device, a semiconductor circuit, an imaging device, an electronic device, and the like include a semiconductor device.

[0067] FIG. 1A is a diagram illustrating a semiconductor device 10A1 of one embodiment of the present invention.

[0068] The semiconductor device 10A1 includes a reference cell 21(1) and an arithmetic cell 31(1). The reference cell 21(1) includes a transistor 22, a transistor 24, and a capacitor 25. The arithmetic cell 31(1) includes a transistor

32, a transistor 34, and a capacitor 35. The transistor 22, the transistor 24, the transistor 32, and the transistor 34 each include a gate and a back gate.

[0069] In this specification and the like, in the case where a transistor having a function of a switch includes a gate and a back gate, on/off of the transistor can be controlled by controlling a potential of the gate. In addition, the threshold voltage of the transistor can be controlled by controlling a potential of the back gate.

[0070] The transistors and the capacitors included in the reference cell 21(1) and the arithmetic cell 31(1) are connected to at least one of a wiring WSL, a wiring XCL, a wiring WCL, and a wiring supplying a ground potential, as illustrated in FIG. 1.

[0071] The reference cell 21(1) has a function of making a set current flow therein at the time of data writing and the time of data reading to make the arithmetic cell 31(1) execute arithmetic operation. Specifically, the reference cell 21(1) has a function of making a reference current flow therein at the time of data writing to retain a reference potential, and making a current corresponding to input data (X) to be supplied to the arithmetic cell 31(1) flow to the reference cell 21(1) at the time of data reading to control a current flowing in the arithmetic cell 31(1). Note that the reference cell 21(1) is simply referred to as a cell in some

[0072] Next, connection relations in the reference cell 21(1) will be described.

[0073] A gate of the transistor 22 is electrically connected to the wiring WSL. One of a source and a drain of the transistor 22 is electrically connected to one of a source and a drain of the transistor 24, and is electrically connected to one electrode of the capacitor 25 through the wiring XCL. The other of the source and the drain of the transistor 22 is electrically connected to the back gate of the transistor 24 and the other electrode of the capacitor 25. The transistor 22 is brought into an on state at the time of data writing so that a reference potential can be written to a retention node (the back gate of the transistor 24) in the reference cell 21(1), and is brought into an off state so that the reference potential can be retained in the reference cell 21(1). Note that a node to which the back gate of the transistor 24, the other of the source and the drain of the transistor 22, and the other electrode of the capacitor 25 are connected is also referred to as a retention node. The retention node can be set at a potential corresponding to a current flowing in the transistor 24.

[0074] Here, the threshold voltage of the transistor 22 can be controlled by controlling the back gate potential of the transistor 22. Specifically, when the back gate potential of the transistor 22 is increased, the threshold voltage of the transistor 22 can be decreased. Meanwhile, when the back gate potential of the transistor 22 is decreased, the threshold voltage of the transistor 22 can be increased. Thus, the on-state current of the transistor 22 can be increased when the back gate potential of the transistor 22 is increased while the transistor 22 is in an on state, and the off-state current of the transistor 22 can be decreased when the back gate potential of the transistor 22 is decreased while the transistor 22 is in an off state.

[0075] A gate of the transistor 24 and the other of the source and the drain of the transistor 24 are connected to a wiring supplying a constant current such as a low power supply potential (e.g., a ground potential). The wiring sup-

plying a ground potential functions as a wiring for supplying a current between the source and the drain of the transistor **24**.

[0076] The capacitor 25 changes the potential of the other electrode in accordance with a change in potential supplied to the one electrode when the other electrode is in an electrically floating state.

[0077] The arithmetic cell 31(1) has a function of making a current corresponding to weight data (W) to be retained in the arithmetic cell 31(1) flow therein at the time of data writing to retain a voltage corresponding to the current inside. The arithmetic cell 31(1) also has a function of supplying a current corresponding to arithmetic operation of the weight data and the input data at the time of data reading as a result of boosting of the voltage retained at the time of data writing in accordance with a current flowing in the reference cell 21(1). The weight data is referred to as first data, and the input data is referred to as second data, in some cases. Note that the arithmetic cell 31(1) is simply referred to as a cell in some cases. Note that the weight data is data (weight data) corresponding to a weight parameter used for product-sum operation of an artificial neural network, for example.

[0078] Next, connection relations in the arithmetic cell 31(1) will be described.

[0079] A gate of the transistor 32 is electrically connected to the wiring WSL. One of a source and a drain of the transistor 32 is electrically connected to one of a source and a drain of the transistor 34 and the wiring WCL. One electrode of the capacitor 35 is electrically connected to the wiring XCL. The other of the source and the drain of the transistor 32 is electrically connected to the back gate of the transistor 34 and the other electrode of the capacitor 35. The transistor 32 is brought into an on state at the time of data writing so that a voltage corresponding to the weight data can be written to the arithmetic cell 31(1), and is brought into an off state so that the voltage corresponding to the weight data can be retained in the arithmetic cell 31(1). Note that a node to which the back gate of the transistor 34, the other of the source and the drain of the transistor 32, and the other electrode of the capacitor 35 are connected is also referred to as a retention node.

[0080] Here, the threshold voltage of the transistor 32 can be controlled by controlling the back gate potential of the transistor 32. Specifically, when the back gate potential of the transistor 32 is increased, the threshold voltage of the transistor 32 can be decreased. Meanwhile, when the back gate potential of the transistor 32 is decreased, the threshold voltage of the transistor 32 can be increased. Thus, the on-state current of the transistor 32 can be increased when the back gate potential of the transistor 32 is increased while the transistor 32 is in an on state, and the off-state current of the transistor 32 can be decreased when the back gate potential of the transistor 32 is decreased while the transistor 32 is in an off state.

[0081] A gate of the transistor 34 and the other of the source and the drain of the transistor 34 are connected to a wiring supplying a constant potential such as a low power supply potential (e.g., aground potential). The wiring supplying a ground potential functions as a wiring for supplying a current between the source and the drain of the transistor 34

[0082] The capacitor 35 changes the potential of the other electrode in accordance with a change in potential supplied to the one electrode when the other electrode is in an electrically floating state.

[0083] Next, the transistors included in the reference cell 21(1) and the arithmetic cell 31(1) will be described.

[0084] The transistor 24 and the transistor 34 operate in a subthreshold region, unless otherwise specified. A drain current Id of a transistor that operates in a subthreshold region can be represented by Equation (1).

[Formula 1]

$$I_d = I_0 \exp\left(\frac{q(V_g - V_{th})}{\eta k_B T}\right) \tag{1}$$

[0085] In Equation (1),  $I_0$  represents a drain current when  $V_g=V_{th}$ , q represents elementary charge,  $V_g$  represents a gate voltage,  $V_{th}$  represents a threshold voltage,  $\eta$  represents a coefficient determined by a device structure or the like,  $k_B$  represents the Boltzmann constant, and T represents temperature. As shown in Equation (1), the drain current Id of the transistor that operates in a subthreshold region does not depend on the drain voltage. Currents flowing in the transistor 24 and the transistor 34 are the amounts of currents flowing when the transistors operate in a subthreshold region. The currents in the transistor 24 and the transistor 34 in a subthreshold region can reduce the influence of variation in drain voltage. Accordingly, the accuracy of data obtained by arithmetic operation can be increased.

[0086] Note that in this specification and the like, a subthreshold region refers to a region where a gate voltage is lower than threshold voltage in a graph showing gate voltage (Vg)-drain current (Id) characteristics of a transistor. Alternatively, the subthreshold region refers to a region where a current flows due to carrier diffusion, which is out of gradual channel approximation (a model in which only a drift current is considered). Alternatively, the subthreshold region refers to a region where a drain current is increased exponentially with respect to an increase in gate voltage. Alternatively, the subthreshold region includes a region that can be regarded as any region of the above description.

[0087] A drain current when the transistor operates in the subthreshold region is referred to as a subthreshold current. The subthreshold current is increased exponentially with respect to the gate voltage, without depending on the drain voltage. The circuit operation using the subthreshold current can reduce the influence of variation in drain voltage.

[0088] The transistor 22 and the transistor 32 have functions of retaining the potentials of the back gate of the transistor 24 and the back gate of the transistor 34 by being brought into an off state. Specifically, with the function, a reference potential supplied to the back gate of the transistor 24 through the transistor 22 is retained. In addition, with the function, a potential corresponding to data supplied to the back gate of the transistor 34 through the transistor 32 is retained. The transistor 22 and the transistor 32 are each preferably a transistor including a metal oxide in a channel formation region (also referred to as OS transistor), for example. It is further preferable that the channel formation regions of the transistor 22 and the transistor 32 be each an oxide containing at least one of indium, gallium, and zinc, for example. Instead of the oxide, an oxide containing at

least one of indium, an element M(as the element M, for example, one kind or a plurality of kinds selected from aluminum, gallium, yttrium, copper, vanadium, beryllium, boron, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium, and the like can be given), and zinc may be used.

[0089] A current flowing between a source and a drain in an off state, that is, a leakage current, is extremely low in an OS transistor. Thus, with the use of an OS transistor as the transistor 22 and/or the transistor 32, the leakage current of the transistor 22 and/or the transistor 32 can be suppressed, so that the power consumption of the semiconductor device **10**A1 can be reduced. Specifically, a change in the potential retained in each of the back gate of the transistor 24 and the back gate of the transistor 34 can be extremely small, so that the frequency of refresh operations for the potential can be reduced. The reduction in the frequency of refresh operations can reduce the power consumption of the semiconductor device 10A1. An extremely low leakage current from the retention node to the wiring WCL or the wiring XCL allows the cell to retain the potential of the retention node for a long time.

[0090] Furthermore, an extremely low current, such as a current lower than  $1\times10^{-20}$  A, lower than  $1\times10^{-22}$  A, or lower than  $1\times10^{-24}$  A, can flow in an OS transistor as a drain current per micrometer of channel width when the gate voltage is lower than the threshold voltage of the transistor. In addition, a drain current per micrometer of channel width of lower than or equal to  $1.0 \times 10^{-8}$  A, lower than or equal to  $1.0 \times 10^{-12}$  A, or lower than or equal to  $1.0 \times 10^{-15}$  A can flow in an OS transistor when the gate voltage is equal to the threshold voltage of the transistor. Thus, subthreshold currents with different magnitudes can flow in an OS transistor in a range of the gate voltage in which the transistor operates in a subthreshold region. That is, an OS transistor can have a wide range of the gate voltage where the transistor operates in a subthreshold region. Specifically, when the threshold voltage of an OS transistor is  $V_{th}$ , a circuit operation using the gate voltage in the voltage range of  $(V_{th}-1.0 \text{ V})$  to  $V_{th}$ inclusive, or  $(V_{th}-0.5 \text{ V})$  to  $V_{th}$  inclusive is possible in the subthreshold region.

[0091] A metal oxide functioning as an oxide semiconductor has a band gap of 2.5 eV or wider; thus, an OS transistor has an extremely low off-state current. For example, the off-state current per micrometer in channel width at a source-drain voltage of 3.5 V and room temperature (25° C.) can be lower than  $1\times10^{-20}$  A, lower than  $1\times10^{-22}$  A, or lower than  $1\times10^{-24}$  A. Therefore, in an OS memory, the amount of electric charge that leaks from a retention node through the OS transistor is extremely small.

[0092] A metal oxide used for an OS transistor is a Zn oxide, a Zn—Sn oxide, a Ga—Sn oxide, an In—Ga oxide, an In—Zn oxide, an In—Zn oxide, an In-M-Zn oxide (M is Ti, Ga, Y, Zr, La, Ce, Nd, Sn, or Hf), or the like. The use of a metal oxide containing Ga as M for the OS transistor is particularly preferable because the electrical characteristics such as field-effect mobility of the transistor can be made excellent by adjusting a ratio of elements. In addition, an oxide containing indium and zinc may contain one or more kinds selected from aluminum, gallium, yttrium, copper, vanadium, beryllium, boron, silicon, titanium, iron, nickel, ger-

manium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, magnesium, and the like.

[0093] In order to improve the reliability and electrical characteristics of the OS transistor, it is preferable that the metal oxide used in the semiconductor layer is a metal oxide having a crystal portion, such as CAAC-OS, CAC-OS, or nc-OS. CAAC-OS is an abbreviation for c-axis-aligned crystalline oxide semiconductor. CAC-OS is an abbreviation for Cloud-Aligned Composite oxide semiconductor. In addition, nc-OS is an abbreviation for nanocrystalline oxide semiconductor.

[0094] The CAAC-OS has c-axis alignment, a plurality of nanocrystals are connected in the a-b plane direction, and its crystal structure has distortion. Note that the distortion refers to a portion where the direction of a lattice arrangement changes between a region with a regular lattice arrangement and another region with a regular lattice arrangement in a region where the plurality of nanocrystals are connected.

[0095] The CAC-OS has a function of allowing electrons (or holes) serving as carriers to flow and a function of not allowing electrons serving as carriers to flow. The function of allowing electrons to flow and the function of not allowing electrons to flow are separated, whereby both functions can be heightened to the maximum. In other words, when CAC-OS is used for a channel formation region of an OS transistor, a high on-state current and an extremely low off-state current can be both achieved.

[0096] An OS transistor is an accumulation transistor in which electrons are majority carriers. Therefore, drain-induced barrier lowering (DIBL), which is one of short-channel effects, affects an OS transistor less than an inversion transistor having a pn junction. In other words, an OS transistor has higher resistance against short channel effects than a Si transistor.

[0097] The use of OS transistors also as the transistor 24 and the transistor 34 enables an operation with a range of current in the subthreshold regions, leading to a reduction in the current consumption. With the use of OS transistors also as the transistor 24 and the transistor 34, the transistors can be manufactured concurrently with the transistor 22 and the transistor 32; thus, the manufacturing process of the arithmetic circuit can sometimes be shortened.

[0098] Note that the transistor 22, the transistor 24, the transistor 32, and the transistor 34 are not necessarily OS transistors. For example, the transistor 22, the transistor 24, the transistor 32, and the transistor 34 can be Si transistors. As the silicon, amorphous silicon (sometimes referred to as hydrogenated amorphous silicon), microcrystalline silicon, polycrystalline silicon, single crystal silicon, or the like can be used, for example.

[0099] The transistor 22, the transistor 24, the transistor 32, and the transistor 34 illustrated in FIG. 1 are n-channel transistors; however, the semiconductor device of one embodiment of the present invention is not limited thereto. For example, some or all of the transistor 22, the transistor 24, the transistor 32, and the transistor 34 may be replaced with p-channel transistors.

[0100] In the case where some or all of the transistor 22, the transistor 24, the transistor 32, and the transistor 34 are replaced with p-channel transistors, a voltage supplied by wirings, for example, may be changed as necessary such that the transistor 22, the transistor 24, the transistor 32, and the transistor 34 each perform a desired operation.

[0101] Note that the above variation examples of the structure, polarity, or the like of a transistor are applied to not only the transistor 22, the transistor 24, the transistor 32, and the transistor 34. For example, the structure, the polarity, or the like of a transistor described in other parts of the specification or a transistor illustrated in other drawings may also be changed.

[0102] Next, the wiring WSL, the wiring XCL, and the wiring WCL connected to the reference cell 21(1) and the arithmetic cell 31(1) will be described.

[0103] A signal for controlling on/off of the transistor 22 and the transistor 32 functioning as switches is supplied to the wiring WSL. The wiring WSL functions as a write word line for writing data to the reference cell 21(1) and the arithmetic cell 31(1). Here, when a current corresponding to desired data is supplied to the wiring XCL or the wiring WCL, data is written to the reference cell 21(1) or the arithmetic cell 31(1). When a potential corresponding to desired data is supplied to the wiring XCL or the wiring WCL, data is written to the reference cell 21(1) or the arithmetic cell 31(1). Data is written to the reference cell 21(1) when the transistor 22 is turned on, and written to the arithmetic cell 31(1) when the transistor 32 is turned on. The transistor 22 and the transistor 32 can be turned on by setting the wiring WSL at an H level (a high-level potential). Data is retained in the reference cell 21(1) when the transistor 22 is turned off, and data is retained in the arithmetic cell 31(1) when the transistor 32 is turned off. The transistor 22 and the transistor 32 can be turned off by setting the wiring WSL at an L level (a low-level potential).

[0104] The wiring WCL has a function of supplying a current (a weight current or a current  $I_{Wut}$ ) in an amount corresponding to the weight data (also referred to as first data or first input data) to the arithmetic cell 31(1), or a function of supplying a constant potential for supplying a current in accordance with the potential retained in the arithmetic cell 31(1).

**[0105]** The wiring XCL has a function of supplying a current (a reference current or a current  $I_{Xul}$ ) in an amount corresponding to reference data or a current (an input current or a current  $I_X$ ) in an amount corresponding to the input data (also referred to as second data or second input data) to the reference cell **21(1)** and the arithmetic cell **31(1)**.

[0106] FIG. 1B is a diagram illustrating a semiconductor device 10B1 of one embodiment of the present invention. In the semiconductor device 10B1, agate insulating layer for the back gate of the transistor 22 and a gate insulating layer for the back gate of the transistor 32 included in the semiconductor device 10A1 each contain a material that can have ferroelectricity.

[0107] In circuit diagrams in this specification and the like, a back gate to which a diagonal line is added indicates that a gate insulating layer for the back gate of the transistor contain a material that can have ferroelectricity.

[0108] In this specification and the like, ferroelectricity means a property that a polarization state is maintained even when voltage application is stopped after polarization is caused by the voltage application. Paraelectricity means a property that a polarization state is not maintained and disappears when voltage application is stopped after polarization is caused by the voltage application.

[0109] Examples of the material that can have ferroelectricity include hafnium oxide, zirconium oxide,  $HfZrO_X$  (X is a real number greater than 0), a material obtained by

adding an element J1 (the element J1 here is zirconium (Zr), silicon (Si), aluminum (Al), gadolinium (Gd), yttrium (Y), lanthanum (La), strontium (Sr), or the like) to hafnium oxide, and a material obtained by adding an element J2 (the element J2 here is hafnium (Hf), silicon (Si), aluminum (Al), gadolinium (Gd), yttrium (Y), lanthanum (La), strontium (Sr), or the like) to zirconium oxide. As the material that can have ferroelectricity, piezoelectric ceramic having a perovskite structure, such as PbTiO<sub>X</sub>, barium strontium titanate (BST), strontium titanate, lead zirconate titanate (PZT), strontium bismuth tantalate (SBT), bismuth ferrite (BFO), or barium titanate may be used. The material that can have ferroelectricity can be, for example, a plurality of materials selected from the above-listed materials or a stacked-layer structure of a plurality of materials selected from the abovelisted materials. Note that each of hafnium oxide, zirconium oxide, HfZrO<sub>x</sub>, the material obtained by adding the element J1 to hafnium oxide, and the like possibly changes its crystal structure (characteristics) depending not only on the deposition condition but also on a variety of processes or the like, and thus is referred to as a material that can have ferroelectricity in this specification and the like.

[0110] As the material that can have ferroelectricity, hafnium oxide or a material containing hafnium oxide and zirconium oxide is particularly preferable because it can have ferroelectricity even when being processed into a thin film of several nanometers.

[0111] The thickness of the material that can have ferroelectricity can be less than or equal to 100 nm, preferably less than or equal to 50 nm, further preferably less than or equal to 20 nm, still further preferably less than or equal to 10 nm (typically, greater than or equal to 2 nm and less than or equal to 9 nm). In the case where  $\mathrm{HfZrO}_X$  is used as the material that can have ferroelectricity, deposition is preferably performed by an atomic layer deposition (ALD) method, particularly a thermal ALD method.

[0112] In the case where the material that can have ferroelectricity is deposited by a thermal ALD method, a material not containing hydrocarbon (also referred to as Hydro Carbon or HC) is suitably used as a precursor. In the case where the material that can have ferroelectricity contains one or both of hydrogen and carbon, crystallization of the material that can have ferroelectricity is hindered in some cases. Thus, the concentration of one or both of hydrogen and carbon in the material that can have ferroelectricity is preferably reduced by using a precursor not containing hydrocarbon, as described above. Examples of the precursor not containing hydrocarbon include chlorine-based materials. In the case where a material containing hafnium oxide and zirconium oxide (HfZrOx) is used as the material that can have ferroelectricity, HfCl<sub>4</sub> and/or ZrCl<sub>4</sub> can be used as a precursor.

[0113] In the case where the material that can have ferroelectricity is deposited by a thermal ALD method,  $\rm H_2O$  or  $\rm O_3$  can be used as an oxidizer. Note that an oxidizer for a thermal ALD method is not limited to this. For example, an oxidizer for a thermal ALD method may contain one or more selected from  $\rm O_2$ ,  $\rm O_3$ ,  $\rm N_2O$ ,  $\rm NO_2$ ,  $\rm H_2O$ , and  $\rm H_2O_2$ .

[0114] In addition, there is no particular limitation on the crystal structure of the material that can have ferroelectricity. For example, the material that can have ferroelectricity has one or more crystal structures selected from cubic, tetragonal, orthorhombic, and monoclinic crystal structures. It is particularly preferable that the material that can have ferro-

electricity have an orthorhombic crystal structure, in which case ferroelectricity appears. Alternatively, the material that can have ferroelectricity may have a composite structure including an amorphous structure and a crystal structure.

[0115] As the material that can have ferroelectricity, it is possible to use silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, silicon oxide to which fluorine is added, silicon oxide to which carbon is added, silicon oxide to which carbon and nitrogen are added, porous silicon oxide, or the like. In particular, silicon oxide and silicon oxynitride, which have thermal stability, are preferable.

[0116] In the semiconductor device 10B1, the polarization state of a gate insulating layer for the back gate can be controlled by controlling the back gate potential of the transistor 22. Thus, the threshold voltage of the transistor 22 can be controlled. Similarly, the polarization state of a gate insulating layer for the back gate can be controlled by controlling the back gate potential of the transistor 32, and thus the threshold voltage of the transistor 32 can be controlled.

[0117] In the semiconductor device 10B1, even when polarization is caused in the gate insulating layer for the back gate of the transistor 22 or the transistor 32 and then potential supply to the back gate is stopped, the gate insulating layer can maintain the polarization state. Thus, it does not need to continue supplying a potential to the back gates of the transistor 22 and the transistor 32. Therefore, the semiconductor device 10B1 can be a semiconductor device with low power consumption.

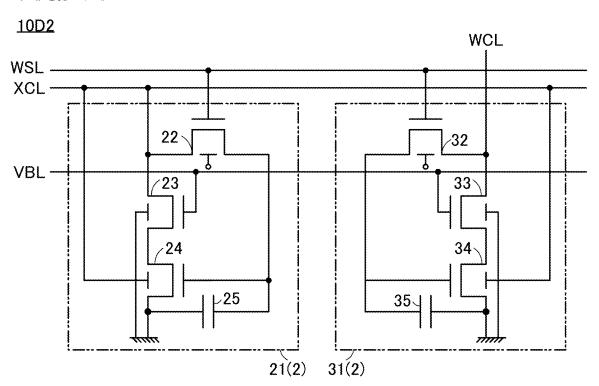

[0118] FIG. 2A is a diagram illustrating a semiconductor device 10A2 of one embodiment of the present invention. Note that in the following description of the semiconductor device 10A2, components and the like similar to those of the semiconductor device 10A1 are not described in some cases.

[0119] The semiconductor device 10A2 includes a reference cell 21(2) and an arithmetic cell 31(2). The reference cell 21(2) includes the transistor 22, the transistor 24, and the capacitor 25, like the reference cell 21(1). The arithmetic cell 31(2) includes the transistor 32, the transistor 34, and the capacitor 35, like the arithmetic cell 31(1).

[0120] The gate of the transistor 22 is electrically connected to the wiring WSL. One of the source and the drain of the transistor 22 is electrically connected to one of the source and the drain of the transistor 24 and the wiring XCL. The other of the source and the drain of the transistor 22 is electrically connected to the gate of the transistor 24 and one electrode of the capacitor 25. The transistor 22 is brought into an on state at the time of data writing so that a reference voltage can be written to a retention node (the gate of the transistor 24) in the reference cell 21(2), and is brought into an off state so that the reference voltage can be retained in the reference cell 21(2). Note that a node to which the gate of the transistor 24, the other of the source and the drain of the transistor 22, and the one electrode of the capacitor 25 are connected is also referred to as a retention node. The retention node can be set at a potential corresponding to a current flowing in the transistor 24.

[0121] The other of the source and the drain of the transistor 24 and the other electrode of the capacitor 25 are connected to a wiring supplying a constant potential such as a low power supply potential (e.g., aground potential). The wiring supplying aground potential functions as a wiring for supplying a current between the source and the drain of the

transistor **24**. In addition, the back gate of the transistor **24** is electrically connected to the wiring XCL.

[0122] Next, connection relations in the arithmetic cell 31(2) will be described.

[0123] The gate of the transistor 32 is electrically connected to the wiring WSL. One of the source and the drain of the transistor 32 is electrically connected to one of the source and the drain of the transistor 34 and the wiring WCL. The other of the source and the drain of the transistor 32 is electrically connected to the gate of the transistor 34 and one electrode of the capacitor 35. The transistor 32 is brought into an on state at the time of data writing so that a voltage corresponding to the weight data can be written to the arithmetic cell 31(2), and is brought into an off state so that the voltage corresponding to the weight data can be retained in the arithmetic cell 31(2). Note that a node to which the gate of the transistor 34, the other of the source and the drain of the transistor 32, and the one electrode of the capacitor 35 are connected is also referred to as a retention node.

[0124] The other of the source and the drain of the transistor 34 is connected to a wiring supplying a constant potential such as a low power supply potential (e.g., a ground potential). The wiring supplying a ground potential functions as a wiring for supplying a current between the source and the drain of the transistor 34. In addition, the back gate of the transistor 34 is electrically connected to the wiring XCL.

[0125] Next, the transistors included in the reference cell 21(2) and the arithmetic cell 31(2) will be described.

[0126] The transistor 22 and the transistor 32 have functions of retaining the potentials of the gate of the transistor 24 and the gate of the transistor 34 by being brought into an off state. Specifically, with the function, a reference potential supplied to the gate of the transistor 24 through the transistor 22 can be retained. In addition, with the function, a potential corresponding to data supplied to the gate of the transistor 34 through the transistor 32 can be retained.

[0127] A current flowing between a source and a drain in an off state, that is, a leakage current, is extremely low in an OS transistor. Thus, with the use of an OS transistor as the transistor 22 and/or the transistor 32, the leakage current of the transistor 22 and/or the transistor 32 can be suppressed, so that the power consumption of the semiconductor device 10A2 can be reduced. Specifically, a change in the potential retained in each of the gate of the transistor 24 and the gate of the transistor 34 can be extremely small, so that the frequency of refresh operations for the potential can be reduced. The reduction in the frequency of refresh operations can reduce the power consumption of the semiconductor device 10A2. An extremely low leakage current from the retention node to the wiring WCL or the wiring XCL allows the cell to retain the potential of the retention node for a long time.

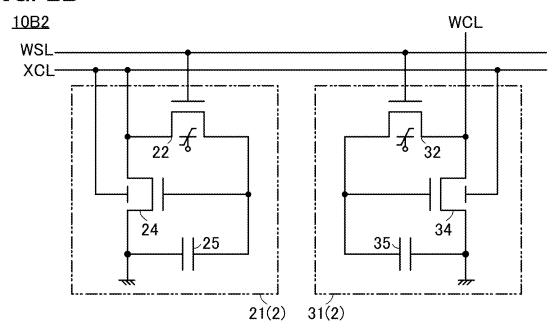

[0128] FIG. 2B is a diagram illustrating a semiconductor device 10B2 of one embodiment of the present invention. In the semiconductor device 10B2, agate insulating layer for the back gate of the transistor 22 and a gate insulating layer for the back gate of the transistor 32 included in the semiconductor device 10A2 each contain a material that can have ferroelectricity.

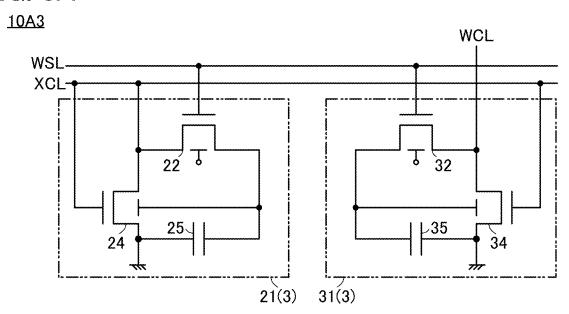

[0129] FIG. 3A is a diagram illustrating a semiconductor device 10A3 of one embodiment of the present invention. Note that in the following description of the semiconductor

device 10A3, components and the like similar to those of the semiconductor device 10A1 are not described in some cases.

[0130] The semiconductor device 10A3 includes a reference cell 21(3) and an arithmetic cell 31(3). The reference cell 21(3) includes the transistor 22, the transistor 24, and the capacitor 25, like the reference cell 21(1). The arithmetic cell 31(3) includes the transistor 32, the transistor 34, and the capacitor 35, like the arithmetic cell 31(1). The transistor 22, the transistor 24, the transistor 32, and the transistor 34 each include a gate and a back gate.

[0131] The gate of the transistor 22 is electrically connected to the wiring WSL. One of the source and the drain of the transistor 22 is electrically connected to one of the source and the drain of the transistor 24 and the wiring XCL. The other of the source and the drain of the transistor 22 is electrically connected to the gate of the transistor 24 and one electrode of the capacitor 25. The transistor 22 is brought into an on state at the time of data writing so that a reference potential can be written to a retention node (the back gate of the transistor 24) in the reference cell 21(3), and is brought into an off state so that the reference potential can be retained in the reference cell 21(3). Note that a node to which the back gate of the transistor 24, the other of the source and the drain of the transistor 22, and the one electrode of the capacitor 25 are connected is also referred to as a retention node. The retention node can be set at a potential corresponding to a current flowing in the transistor 24.

[0132] The other of the source and the drain of the transistor 24 and the other electrode of the capacitor 25 are connected to a wiring supplying a constant potential such as a low power supply potential (e.g., aground potential). The wiring supplying aground potential functions as a wiring for supplying a current between the source and the drain of the transistor 24. The gate of the transistor 24 is electrically connected to the wiring XCL.

[0133] Next, connection relations in the arithmetic cell 31(3) will be described.

[0134] The gate of the transistor 32 is electrically connected to the wiring WSL. One of the source and the drain of the transistor 32 is electrically connected to one of the source and the drain of the transistor 34 and the wiring WCL. The other of the source and the drain of the transistor 32 is electrically connected to the back gate of the transistor 34 and one electrode of the capacitor 35. The transistor 32 is brought into an on state at the time of data writing so that a voltage corresponding to the weight data can be written to the arithmetic cell 31(3), and is brought into an off state so that the voltage corresponding to the weight data can be retained in the arithmetic cell 31(3). Note that a node to which the back gate of the transistor 34, the other of the source and the drain of the transistor 32, and the one electrode of the capacitor 35 are connected is also referred to as a retention node.

[0135] The other of the source and the drain of the transistor 34 is connected to a wiring supplying a constant potential such as a low power supply potential (e.g., a ground potential). The wiring supplying a ground potential functions as a wiring for supplying a current between the source and the drain of the transistor 34. The gate of the transistor 34 is electrically connected to the wiring XCL.

[0136] Next, the transistors included in the reference cell 21(3) and the arithmetic cell 31(3) will be described.

[0137] The transistor 22 and the transistor 32 have functions of retaining the potentials of the back gate of the transistor 24 and the back gate of the transistor 34 by being brought into an off state. Specifically, with the function, a reference potential supplied to the back gate of the transistor 24 through the transistor 22 can be retained. In addition, with the function, a potential corresponding to data supplied to the back gate of the transistor 32 can be retained.

[0138] As described above, a current flowing between a source and a drain in an off state, that is, a leakage current, is extremely low in an OS transistor. Thus, with the use of an OS transistor as the transistor 22 and/or the transistor 32, the leakage current of the transistor 22 and/or the transistor 32 can be suppressed, so that the power consumption of the semiconductor device 10A3 can be reduced. Specifically, a change in the potential retained in each of the back gate of the transistor 24 and the back gate of the transistor 34 can be extremely small, so that the frequency of refresh operations for the potential can be reduced. The reduction in the frequency of refresh operations can reduce the power consumption of the semiconductor device 10A3. An extremely low leakage current from the retention node to the wiring WCL or the wiring XCL allows the cell to retain the potential of the retention node for a long time.

[0139] FIG. 3B is a diagram illustrating a semiconductor device 10B3 of one embodiment of the present invention. In the semiconductor device 10B3, agate insulating layer for the back gate of the transistor 22 and a gate insulating layer for the back gate of the transistor 32 included in the semiconductor device 10A3 each contain a material that can have ferroelectricity.

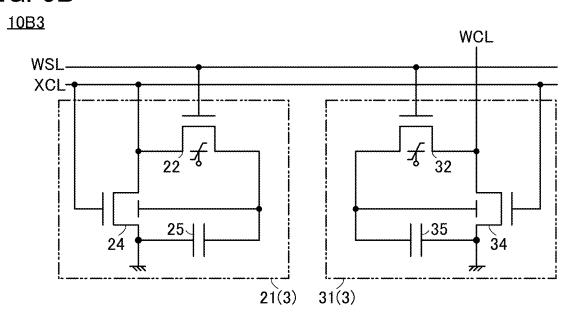

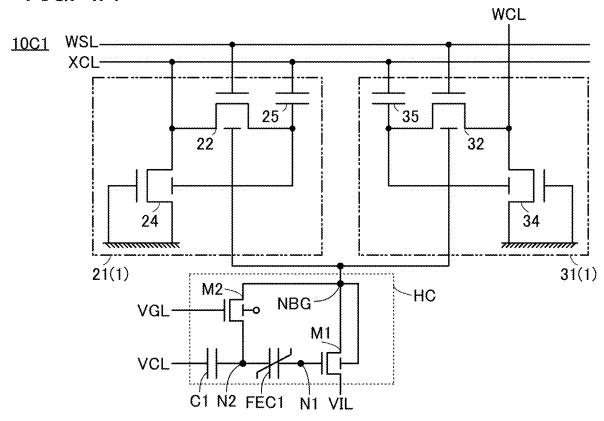

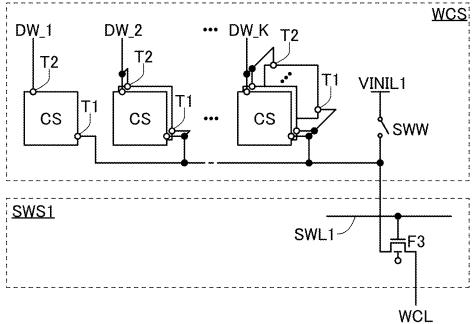

[0140] FIG. 4A is a diagram illustrating a semiconductor device 10C1 of one embodiment of the present invention, FIG. 5A is a diagram illustrating a semiconductor device 10C2 of one embodiment of the present invention, and FIG. 6A is a diagram illustrating a semiconductor device 10C3 of one embodiment of the present invention. In the semiconductor device 10C1, the back gate of the transistor 22 and the back gate of the transistor 32 included in the semiconductor device 10A1 are electrically connected to a circuit HC. In the semiconductor device 10C2, the back gate of the transistor 22 and the back gate of the transistor 32 included in the semiconductor device 10A2 are electrically connected to the circuit HC. In the semiconductor device 10C3, the back gate of the transistor 22 and the back gate of the transistor 32 included in the semiconductor device 10A3 are electrically connected to the circuit HC.

[0141] The circuit HC has a function of a retention circuit for retaining the back gate potential of the transistor 22 and the back gate potential of the transistor 32. The circuit HC includes a transistor M1, a transistor M2, a capacitor C1, and a capacitor FEC1. The transistor M1 and the transistor M2 each include a gate and a back gate.

[0142] The transistor M1 and the transistor M2 are each preferably an OS transistor. As described above, an OS transistor has an extremely low off-state current. Thus, with the use of an OS transistor as the transistor M1 and the transistor M2, the back gate potential of the transistor 22 and the back gate potential of the transistor 32 can be retained for a long time.

[0143] The capacitor FEC1 is a capacitor containing a material that can have ferroelectricity as a dielectric. In this

specification and the like, a capacitor containing a material that can have ferroelectricity as a dielectric is referred to as a ferroelectric capacitor.

[0144] Note that in this specification and the like, a circuit symbol of a ferroelectric capacitor (e.g., the capacitor FEC1) is a circuit symbol of a capacitor to which a diagonal line is added, as illustrated in FIG. 4A, FIG. 5A, and FIG. 6A. As another circuit symbol, a circuit symbol of a capacitor including a plurality of diagonal lines between two parallel lines as illustrated in FIG. 4B, FIG. 5B, and FIG. 6B may be used.

[0145] The circuit HC is electrically connected to the reference cell 21 and the arithmetic cell 31. Specifically, the back gate of the transistor 22 and the back gate of the transistor 32 are electrically connected to one of a source and a drain of the transistor M1, the back gate of the transistor M1, and one of a source and a drain of the transistor M2. The other of the source and the drain of the transistor M1 is electrically connected to a wiring VIL. The gate of the transistor M1 is electrically connected to one electrode of the capacitor FEC1. The other of the source and the drain of the transistor M2 is electrically connected to the other electrode of the capacitor C1. The gate of the transistor M2 is electrically connected to a wiring VGL. The other electrode of the capacitor C1 is electrically connected to a wiring VGL.

[0146] In this specification and the like, a point to which the gate of the transistor M1 and the other electrode of the capacitor FEC1 are electrically connected is referred to as a node N1. In addition, a point to which the other electrode of the capacitor FEC1, the one electrode of the capacitor C1, and the other of the source and drain of the transistor M2 are electrically connected is referred to as a node N2. Furthermore, a point to which the one of the source and the drain of the transistor M1, and the one of the source and the drain of the transistor M2 are electrically connected is referred to as a node NBG. That is, a potential of the node NBG can be a potential to be supplied to the back gate of the transistor 22 and the back gate of the transistor 32.

[0147] Since the node N1 is not electrically connected to a circuit element, a terminal, a wiring, or the like other than the gate of the transistor M1 and the one electrode of the capacitor FEC1, no voltage is directly input from a voltage source or the like to the node N1. Thus, the node N1 is in a floating state. An initial potential of the node N1 can be determined at the time of manufacturing a semiconductor device (specifically, at the time of forming the circuit HC, for example).

[0148] The wiring VIL functions as a wiring supplying a constant potential. In the case where the threshold voltages of the transistor 22 and the transistor 32 are shifted to the positive direction, for example, the constant potential can be a low-level potential, a ground potential, a negative potential, or the like. In the case where the threshold voltages of the transistor 22 and the transistor 32 are shifted to the negative direction, for example, the constant potential can be a high-level potential, a positive potential, or the like.

**[0149]** The wiring VCL functions as a wiring for supplying a potential for causing polarization in the material that can have ferroelectricity and is contained in the capacitor FEC1. For example, in the case where the direction of an electric field generated in the material by the polarization of the material is from the one electrode toward the other

electrode of the capacitor FEC1, the potential can be a positive potential or the like. As another example, in the case where the direction of an electric field generated in the material by the polarization of the material is from the other electrode toward the one electrode of the capacitor FEC1, the potential can be a negative potential or the like. In addition, a potential not causing polarization in the material that can have ferroelectricity and is contained in the capacitor FEC1 may be supplied to the wiring VCL.

[0150] The wiring VGL functions as a wiring supplying a signal potential for controlling switching between an on state and an off state of the transistor M2. For example, the transistor M2 can be brought into an on state when the potential of the wiring VGL is set to a high-level potential, and the transistor M2 can be brought into an off state when the potential of the wiring VGL is set to a low-level potential.

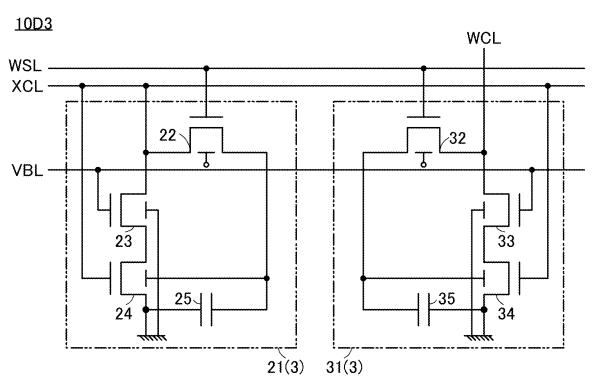

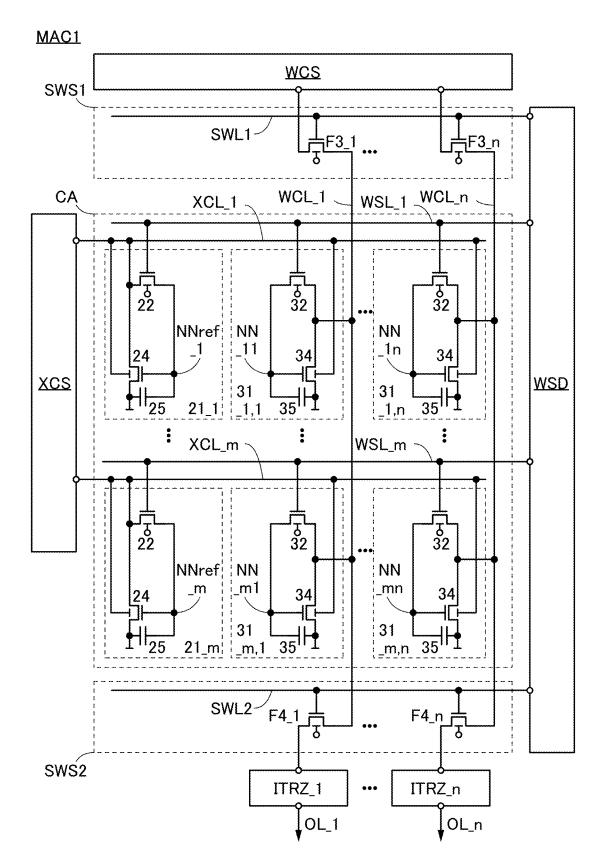

[0151] Next, a structure including a plurality of the reference cells 21 and the arithmetic cells 31 will be described with reference to FIG. 7A and FIG. 7B. FIG. 7A illustrates a schematic operation at the time of data writing and FIG. 7B illustrates a schematic operation at the time of data reading. [0152] In FIG. 7A and FIG. 7B, a reference cell portion 20 provided with a plurality of reference cells 21\_1 to 21\_m (each of which corresponds to the reference cell 21 in FIG. TA and the like), and an arithmetic cell portion 30 provided with a plurality of arithmetic cells  $31_1$ , to  $31_m$ , (each of which corresponds to the arithmetic cell 31 in FIG. TA and the like) are provided. FIG. 7A and FIG. 7B illustrate a plurality of wirings XCL as wirings XCL\_1 to XCL\_m. Furthermore, FIG. 7A and FIG. 7B illustrate a plurality of wirings WCL as wirings WCL\_1 to WCL\_n. Note that m and n are each an integer of 1 or more.

[0153] In FIG. 7A and FIG. 7B, the cells included in the reference cell portion 20 and the arithmetic cell portion 30 are arranged in a matrix including n+1 cells in the row direction and m cells in the column direction. Any structure is acceptable as long as the cells included in the reference cell portion 20 and the arithmetic cell portion 30 are arranged in a matrix including two or more cells in the row direction and one or more cells in the column direction.

[0154] FIG. 7A and FIG. 7B illustrate the reference cell 21 and the arithmetic cell 31 in a simplified manner for the description. A terminal  $C_P$  of the reference cell 21 in the reference cell portion 20 corresponds to the one electrode of the capacitor 25 in FIG. TA and the like, the back gate of the transistor 24 in FIG. 2A and the like, or the gate of the transistor 24 in FIG. 3A and the like. A terminal  $T_W$  of the reference cell 21 in the reference cell portion 20 corresponds to a terminal to which the one of the source and the drain of the transistor 22 and the one of the source and the drain of the transistor 24 are connected in FIG. TA, FIG. 2A, FIG. 3A, and the like. The terminal  $C_P$  of the arithmetic cell 31 in the arithmetic cell portion 30 corresponds to the one electrode of the capacitor 35 in FIG. TA and the like, the back gate of the transistor 34 in FIG. 2A and the like, or the gate of the transistor 34 in FIG. 3A and the like. A terminal Tx of the arithmetic cell 31 in the arithmetic cell portion 30 corresponds to a terminal to which the one of the source and the drain of the transistor 32 and the one of the source and the drain of the transistor 34 are connected in FIG. TA, FIG. 2A, FIG. 3A, and the like.

[0155] In a data writing operation illustrated in FIG. 7A, the current  $I_{Xut}$  is supplied to the reference cell 21 in each

row. The current supplied to each row is the current  $I_{Xut}$  which is normalized, and is equivalent for each row. The amount of the current  $I_{Xut}$  corresponds to that of a current corresponding to reference data (reference current). The current does not flow in the arithmetic cells 31 in each row because the arithmetic cells 31 are connected through the capacitors. The reference cell 21 operates such that a voltage corresponding to the current flowing therein is retained.

**[0156]** Furthermore, in the data writing operation illustrated in FIG. 7A, currents  $I_{W1}$  to  $I_{Wn}$  ( $I_{W}$ ) are supplied to arithmetic cells in the respective columns. Each of the currents supplied to the respective columns corresponds to the amount of current obtained by multiplying the normalized current  $I_{Wu}$  by weight data w ( $I_{W}$ =w $I_{Wu}$ ). The currents  $I_{W1}$  to  $I_{Wn}$  may be different for each column.

[0157] In a data reading operation illustrated in FIG. 7B, currents  $I_{X1}$  to  $I_{Xm}$  ( $I_X$ ) are supplied to the reference cells 21 in the respective rows. Each of the currents  $I_{X1}$  to  $I_{Xm}$  supplied to the respective rows corresponds to the amount of current obtained by multiplying the normalized current  $I_{Xu}$  by input data x ( $I_X=xI_{Xu}I$ ). The currents  $I_{X1}$  to  $I_{Xm}$  may be different for each row. Note that the current  $I_{Xu}$  is preferably equivalent to the current  $I_{Wu}$ .

[0158] In the data reading operation illustrated in FIG. 7B, the voltages retained in the reference cells 21 are boosted by the currents  $I_{X1}$  to  $I_{Xm}$ . In accordance with the boosting, the voltages of the wirings XCL\_1 to XCL\_m are also boosted; thus, voltages retained in the arithmetic cells 31 are boosted by capacitive coupling of the capacitors 35. Then, the potentials of the wirings WCL\_1 to WCL\_n are set to a voltage Vd. At this time, a current  $I_r$ , flowing in the transistor 34 corresponds to the product of the current value  $(I_w)$  retained in the arithmetic cell 31 at the time of data writing and the current value  $(I_x)$  supplied to the reference cell 21 at the time of data reading (currents  $I_{r11}$  to  $I_{rmn}$ ). Estimation of the sum of the currents  $I_{r11}$  to  $I_{rmn}$  flowing in each column can result in output of data corresponding to the result of the product-sum operation of the input data and the weight data.

[0159] Note that the transistor 22 and the transistor 24 included in each of the cells in the reference cell portion 20 preferably have the same size (e.g., channel length, channel width, and transistor structure). Furthermore, the transistor 32 and the transistor 34 included in each of the cells in the arithmetic cell portion 30 preferably have the same size. Furthermore, the transistor 22 and the transistor 32 preferably have the same size. Furthermore, the transistor 24 and the transistor 34 preferably have the same size.

[0160] By making the transistors have the same size, the transistors can have substantially the same electrical characteristics. Thus, by making the transistors 22 included in the reference cell  $21_1,1$  to the reference cell  $21_m,n$  have the same size and the transistors 24 included in the reference cell 21 1.1 to the reference cell 21 m,n have the same size, the reference cell  $21_1$ , to the reference cell  $21_m$ , n can perform almost the same operation under the same conditions. The same conditions here mean, for example, that the input potential to the source, drain, gate, or the like of the transistor 22, the input potential to the source, drain, gate, or the like of the transistor 24, and voltages retained in the reference cell  $21_1$ ,1 to the reference cell  $21_m$ , n are the same. By making the transistors 32 included in the arithmetic cell  $31_1$  to the arithmetic cell  $31_m$  have the same size and making the transistors 34 included in the arithmetic cell 31\_1 to the arithmetic cell 31\_m have the same size, the arithmetic cell  $31\_n$  to the arithmetic cell  $31\_m$  can perform substantially the same operation and can have substantially the same operation results. The arithmetic cell  $31\_n$  to the arithmetic cell  $31\_m$  can perform substantially the same operation under the same conditions. The same conditions here mean, for example, that the input potential to the source, drain, gate, or the like of the transistor 32, the input potential to the source, drain, gate, or the like of the transistor 34, and voltages retained in the arithmetic cell 31 m are the same.

[0161] The operation of the reference cell 21(1) and the arithmetic cell 31(1) at the time of data writing will be described with reference to FIG. 8A.

[0162] The wiring WSL is set to an H level so that the transistor 22 and the transistor 32 are brought into an on state (ON). The current  $I_{Xut}$  corresponding to the reference current is supplied to the wiring XCL. Furthermore, the current  $I_W$  is supplied to the wiring WCL. The current  $I_W$  corresponds to a current obtained by multiplying the weight data w by the normalized current  $I_{Wut}$  ( $I_W$ =w $I_{Wut}$  in the drawing).

[0163] In the reference cell 21(1), the transistor 22 is brought into an on state. A potential of the retention node to which the back gate of the transistor 24 is electrically connected becomes a potential that makes the threshold voltage of the transistor 24 be  $V_{m1}$ . Accordingly, the transistor 24 allows the current of the current  $I_{Xut}$  to flow between the source and the drain of the transistor 24 can be set such that a current flowing between the source and the drain of the transistor 24 becomes  $I_{Xut}$ . In this specification and the like, such an operation is expressed as, for example, "setting (programming) the current flowing between the source and the drain of the transistor 24 in the reference cell 21(1) to  $I_{Xut}$ " in some cases.

[0164] In the arithmetic cell 31(1), the transistor 32 is brought into an on state. The potential of the retention node to which the back gate of the transistor 34 is electrically connected becomes a potential that makes the threshold voltage of the transistor 34 be  $V_{th2}$ . Accordingly, a current flowing between the source and the drain of the transistor 34 in the arithmetic cell 31(1) is set to  $I_W$ . Specifically, the threshold voltage of the transistor 34 is set such that a current flowing between the source and the drain of the transistor 34 becomes  $I_W$ .

[0165] The current  $I_{Xut}$  supplied to the reference cell 21(1) through the wiring XCL at the time of data writing can be represented by Equation (2). Here, a ground potential is supplied to the gate of the transistor 24 and the other of the source and the drain of the transistor 24.

[Formula 2]

$$I_{Xut} = I_0 \exp\left(\frac{-V_{th1}}{\eta k_B T/q}\right) \tag{2}$$

[0166] The current  $I_W$  supplied to the arithmetic cell 31(1) through the wiring WCL at the time of data writing can be represented by Equation (3). Here, a ground potential is supplied to the gate of the transistor 34 and the other of the source and the drain of the transistor 34.

[Formula 3]

$$I_{W} = I_{0} \exp \left( \frac{-V_{th2}}{\eta k_{B} T/q} \right) = w I_{Wut}$$

(3)

[0167] As shown in Equation (3), the current  $I_w$  can be expressed as the product of the weight data w and the normalized current  $I_{ww}$ .

[0168] The operation of the reference cell 21(1) and the arithmetic cell 31(1) at the time of data reading is described with reference to FIG. 8B. Note that a period in which the set current is retained can be provided in a period between data writing and data reading. In the period in which the set current is retained, the transistor 22 and the transistor 32 are brought into an off state (OFF). When OS transistors are used as the transistor 22 and the transistor 32, each of them can keep retaining the potential of the retention node corresponding to the set current.

[0169] In the reference cell 21(1), the wiring WSL is set to an L level so that the transistor 22 is brought into an off state (OFF). The current  $I_X$  corresponding to the input current is supplied to the wiring XCL. The current  $I_X$  corresponds to a current obtained by multiplying the input data x by the normalized current  $I_{Xu}$  ( $I_X$ =x $I_{Xu}$  in the drawing). When the current  $I_X$  flows in the transistor 24, the potential of the retention node to which the back gate of the transistor 24 is electrically connected changes due to capacitive coupling through the capacitor 25, and thus the threshold voltage of the transistor 24 changes to  $V_{th1}$ + $\Delta V_{th}$ . Accordingly, the potential of the wiring XCL also changes.