US 20140268458A1

# (19) United States

# (12) Patent Application Publication Luciani et al.

(10) **Pub. No.: US 2014/0268458 A1**(43) **Pub. Date:** Sep. 18, 2014

### (54) SYSTEMS AND METHODS FOR DETECTING AND DETERMINING SOURCES OF POWER DISTURBANCES IN CONNECTION WITH EFFECTIVE REMEDIATION

(52) **U.S. CI.**CPC ...... *H02H 9/02* (2013.01); *H02H 3/207* (2013.01); *H02H 3/10* (2013.01)

(71) Applicant: Innovolt, Inc., Atlanta, GA (US)

(72) Inventors: Vincent P. Luciani, Charlotte, NC (US); Eugene Bright, Boca Raton, FL (US)

(57) ABSTRACT

(73) Assignee: Innovolt, Inc., Atlanta, GA (US)

(21) Appl. No.: **14/213,838**

(22) Filed: Mar. 14, 2014

Related U.S. Application Data

(60) Provisional application No. 61/783,567, filed on Mar. 14, 2013.

# **Publication Classification**

(51) Int. Cl. H02H 9/02 (2006.01) H02H 3/10 (2006.01) H02H 3/20 (2006.01) Apparatus and methods for selective protection of an electrical load from disturbances on an input power line. A power protection circuit includes a selectively variable inrush current limiting circuit and a switch for disconnecting the input power line from the load. A control circuit determines that the electrical load is in a first operational state, such as a standby mode or normal operation, or a second operational state, such as full operation at rated current. The power protection circuit provides variable inrush current limiting to the electrical load in response to a first category of disturbances when the electrical load is in the first operational state. The power protection circuit inhibits disconnecting the electrical load in response to a second category of disturbances when the electrical load is in the second operational state. Species of selectively variable current limiting circuits are also described.

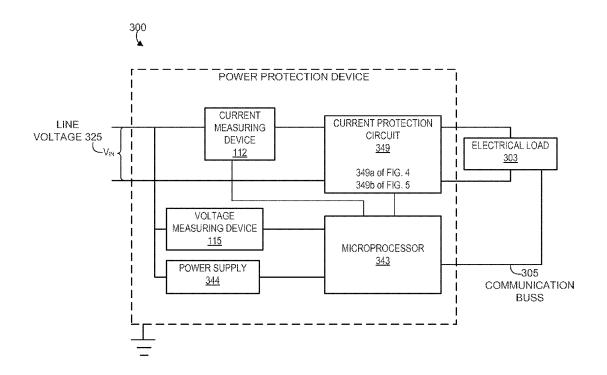

FIG. 1 — EXEMPLARY BLOCK DIAGRAM OF A POWER PROTECTION DEVICE ENVIRONMENT

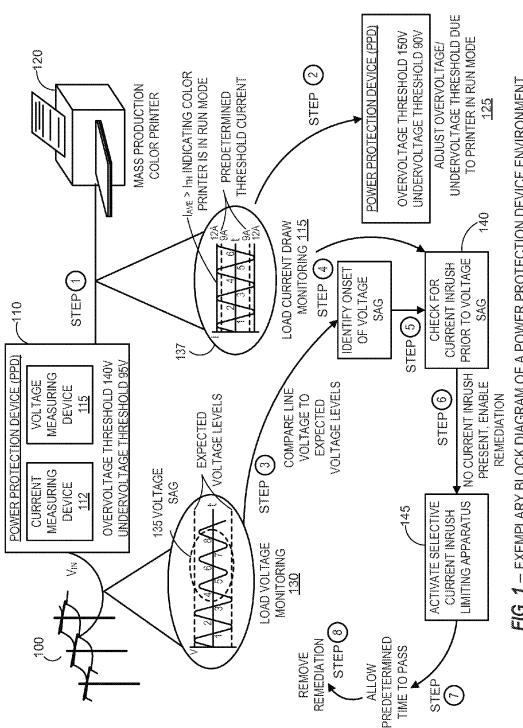

FIG. 2 - EXEMPLARY CURRENT VERSUS VOLTAGE WAVEFORM COMPARISON

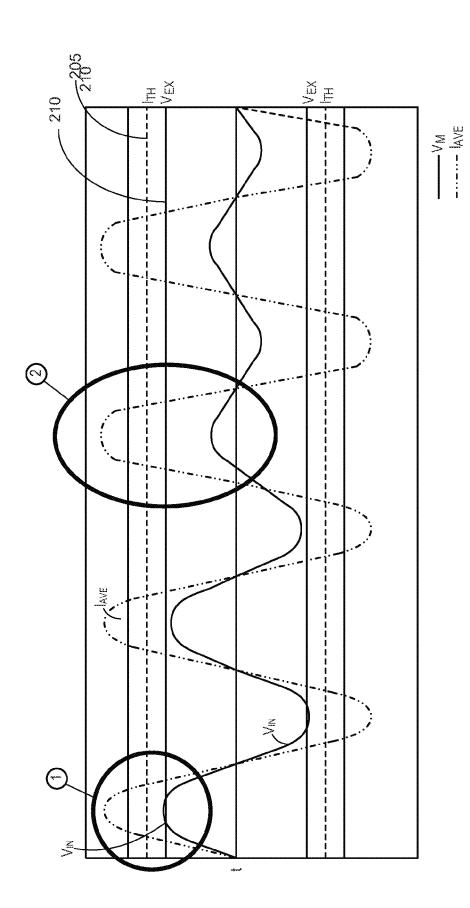

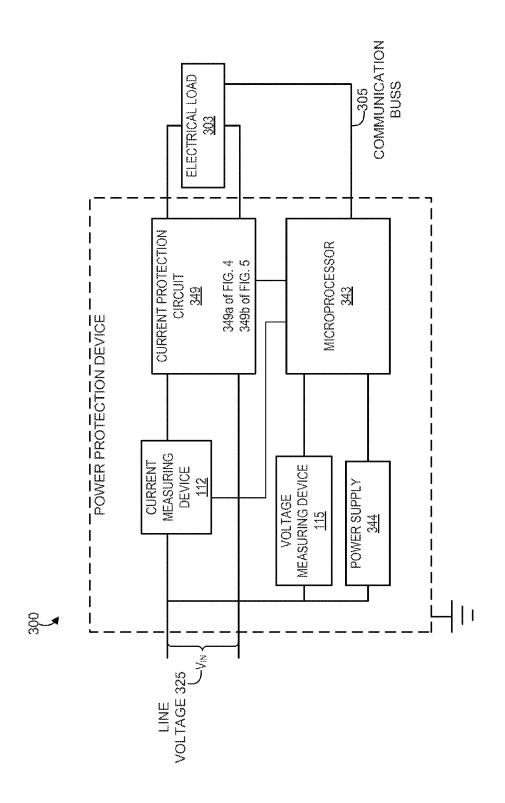

FIG. 3 – POWER PROTECTION DEVICE ARCHITECTURE

FIG. 4 - EXEMPLARY SELECTIVE CURRENT LIMITING PROTECTION CIRCUIT

FIG. 5 - EXEMPLARY SELECTIVE CURRENT LIMITING PROTECTION CIRCUIT

FIG. 6A1 — EXEMPLARY VOLTAGE MEASURING PROCESS

FIG. 6A2 - EXEMPLARY VOLTAGE MEASURING PROCESS

FIG. 6B - EXEMPLARY CURRENT MEASURING PROCESS

FIG. 6C - PROCESS FOR DETERMING POWER DISTURBANCE REMEDIATION OR INHIBITION

FIG. 7A - SELECTIVE CURRENT LIMITING PROCESS

FIG. 7B - TEMPERATURE MODULATED SELECTIVE CURRENT LIMITING PROCESS

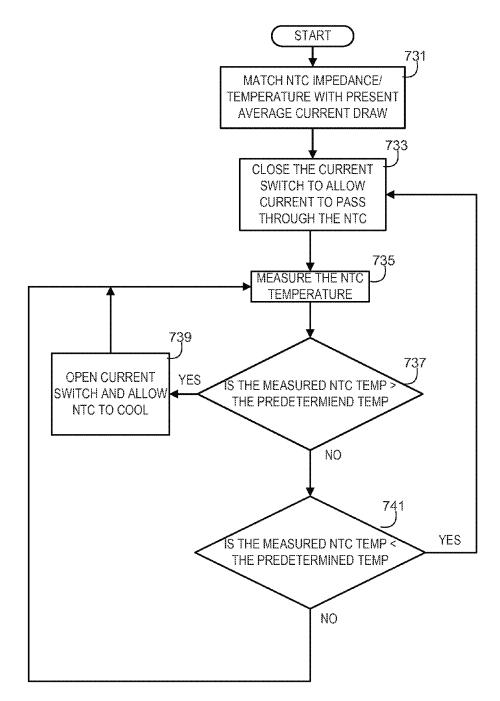

FIG. 7C - EXEMPLARY NTC TEMPERATURE MODULATION PROCESS

FIG. 8 - EXEMPLARY IN RUSH CURRENT SCENARIO

F16. 9 - EXEMPLARY VOLTAGE VS. CURRENT CHARACTERISTIC COMPARISON IN CONNECTION WITH CURRENT INRUSH SCENARIO

# SYSTEMS AND METHODS FOR DETECTING AND DETERMINING SOURCES OF POWER DISTURBANCES IN CONNECTION WITH EFFECTIVE REMEDIATION

# CROSS REFERENCE TO RELATED APPLICATION

[0001] This application claims benefit under 35 U.S.C. §119(e) of U.S. Provisional Patent Application No. 61/783, 567, filed Mar. 14, 2013, and entitled "Systems and Methods for Selective Current Limiting and Voltage Sag Discrimination", which is incorporated herein by reference as if set forth herein in its entirety.

#### TECHNICAL FIELD

[0002] The present systems and methods relate generally to detection of power disturbances and appropriate remediation, and more particularly to the determination of power disturbances due to a load on a branch circuit or a power grid anomaly. Further, the present systems and methods relate generally to selective power disturbance remediation due to voltage and current parameters.

#### BACKGROUND

[0003] Power disturbances on a power grid system are not limited solely to lighting-induced voltage surges as previously thought. Voltage disturbances on power grid systems may embody other common forms such as voltage sags, momentary interruptions, overvoltages, undervoltages, and power outages. Voltage sags on the power grid may occur when short circuits occur somewhere on the grid, a large load is connected to the grid, a sudden load change, etc.

[0004] Voltage sags may account for 90-95% of power disturbance events, particularly in commercial and industrial facilities. Voltage sags are voltage reductions in the nominal line voltage that persist for a particular time period. Typically, voltage sags are characterized by drops of between 10%-90% of nominal (system) line voltages. The drops in voltage typically last from a cycle (16.6 millisecond) to a second or so, or tens of milliseconds to hundreds of milliseconds.

[0005] Certain method and apparatus for correcting certain types and forms of voltage sags are known. One example is U.S. patent application Ser. No. 13/449,870, by Deepakraj Divan, filed Apr. 18, 2012, entitled "Voltage Sag Corrector Using a Variable Duty Cycle Boost Converter," assigned to the same assignee as the present application. This patent application and its contents are incorporated by reference herein as if made a part hereof. While voltage sag correction is one method of addressing power disturbances having certain properties, such voltage sag correctors may not be suitable for many industrial applications.

[0006] Certain methods and apparatus for reducing inrush current to electrical loads due to voltage sags are also known. For example, U.S. Pat. No. 8,039,994, of Deepakraj Divan, entitled Reduction of Inrush Current Due to Voltage Sags, owned by Georgia Tech Research Corporation and licensed to the assignee of this application, and its associated patent family, is one such example. This patent and its contents are incorporated by reference herein as if made a part hereof.

[0007] Other examples include U.S. Pat. No. 8,035,938, Active Current Surge Limiters, of Deepakraj Divan, also owned by Georgia Tech Research Corporation and licensed to the assignee hereof, and its associated patent family. This

patent and its contents are also incorporated by reference herein as if made a part hereof.

[0008] Another example includes U.S. Pat. No. 8,411,403, Voltage Surge and Overvoltage Protection with Current Surge Protection, also of Deepakraj Divan, also owned by Georgia Tech Research Corporation and licensed to the assignee hereof, and its associated patent family. This patent and its contents are also incorporated by reference herein as if made a part hereof.

[0009] The need to identify the causes of different voltage disturbances and protect electrical loads have influenced the advent of intelligent power protection devices that monitor input line voltages for fluctuations and implement various forms of remediation or protection from resultant phenomena such as inrush currents. Some known power protection devices reside near a source voltage and some are located closer to a load, and attempt to monitor the voltage as it is supplied to the electrical load. Some intelligent power protection devices attempt to reduce "nuisance trips" (i.e., unwanted disconnections of the connected electrical load from the power source) by implementing delays or averaging techniques of the incoming supply voltage.

[0010] Most buildings, structures, or facilities have an input power feed from a main power distribution line that feeds a central connection point (e.g., fuse panel, breaker panel, distribution panel, etc.). A branch circuit is the power feeder circuit that leaves the central connection point and provides electrical power for at least one electrical load. As will be generally understood, more than one electrical load may be present on a single branch circuit, wherein multiple electrical loads are connected in parallel. Voltage drops or voltage sags are known to occur between the central connection point and the entry point of the load. There are multiple causes for a branch circuit-based voltage sag, such as incorrect feeder wire size, wherein the improper wire impedance being inserted into the circuit can cause a greater than necessary voltage drop. Additionally, when an electrical load starts, specifically an inductive electrical load, the voltage on the branch circuit will decrease. Further, if there is more than one electrical load on the branch, the reduced voltage is also seen by the each electrical load on the branch.

[0011] However, some of the remediation techniques do not incorporate the working state of the load device into consideration prior to remediation of the voltage disturbance. For example, with some mission-critical electrical load devices such as production printers or manufacturing equipment, it may be desirable to either inhibit remediation or relax the disturbance detection parameters based on the working state of the protected electrical load in order to allow the protected electrical load device to complete its required task. Further, allowing relaxed parameters may not disturb the load equipment if conditions momentarily fall below less than desirable conditions. As is generally understood, inserting a current limiting device before voltage recovery reduces the current inrush. Furthermore, if the electrical load is causing a branch circuit-based sag, additional current limitation is not necessary as it further starves the electrical load of needed voltage, which may cause an unintentional nuisance trip.

[0012] Grid-based voltage sags have a tendency to starve electrical loads of voltage, which generally discharges the internal capacitance of the load device. At the recovery point from a brief voltage sag, power interruption, or power outage, electrical loads pull a large current inrush in order to reenergize internal components. The current inrush is usually

2

unabated, as the internal current limiting component commonly used by the electrical device to limit the current at turn-on does not have time to reset during these brief voltage sags or power outages. One form of power disturbance remediation is to insert an electrical impedance following a voltage sag, power disturbance, etc. The electrical impedance can be a standard resistor, a negative temperature coefficient resistor (NTC or thermistor), or any other resistive or reactive component inserted in to the circuit to reduce the amount of current inrush that occurs during the recovery of a power disturbance.

[0013] Some current limiting circuits utilize a single impedance source to compensate the onset of a current inrush to a load or circuit. This single impedance may not contain the most appropriate value to limit the amount of current drawn due to the nature of the particular power disturbance occurrence. Regardless the cause of the current inrush (recovery from voltage sag, recovery from power outage, recovery from a undervoltage, reconnect after an overvoltage, etc.), the value of the single impedance source inserted to reduce the current surge can cause the voltage presented to the electrical load to momentarily reduce due to the voltage drop across the inserted resistive element. This reduction in voltage can sometimes cause the connected electrical load to unintentionally turn off (e.g., nuisance trip) due to the voltage presented to the electrical load to drop below the required level for operation. An unintentional loss of power to critical load systems may potentially be severely damaging and costly to

[0014] Therefore, the applicant believes there is a long-felt but unresolved need for a system or method that monitors various input line voltages and effectuates various remediation techniques more flexibly. Moreover, it is believed there is a need for a system or method to effectively recognize potential causes for nuisance trips and adjust detection parameters to enable efficient remediation measures. Further, it is believed there is a need for a system and method that can appropriately modulate inserted impedance values of power-disturbance remediation circuits.

# BRIEF SUMMARY OF THE DISCLOSURE

[0015] Briefly described, and according to one embodiment, aspects of the present disclosure generally relate to systems and methods for efficiently remediating an undesirable input power voltage due to a power disturbance. According to one embodiment, a power protection device (PPD) determines the operational state of an electrical load device being protected by a power protection device in order to make a determination if remediation as a response to a power disturbance should be provided or inhibited.

[0016] In one embodiment, the operational state of an electrical load device is determined by use of a current sensing or measuring device that monitors the current draw of the electric load. In one embodiment, the PPD may relax the disturbance detection parameters or inhibit remediation according to predetermined load state to ensure that the load maintains proper functionality. In another embodiment, the PPD may remediate a power disturbance according to a load state and/or line voltage condition. Further and according to another aspect, the PPD may remediate a power disturbance according to a load current anomaly and/or line voltage conditions. In further embodiments, aspects of the PPD generally enable the system to determine whether the source of the voltage disturbance is due to load operations or if the source of the

voltage disturbance is from the power grid. Generally, the source of a voltage disturbance will dictate the execution and/or inhibition of remediation.

[0017] In one embodiment, the PPD comprises a selectively variable current inrush limiting apparatus, wherein various impedance mechanisms are inserted into the voltage and current path to the load according to the current draw of an electrical load device operation as measured by current measuring device. In one aspect, multiple impedance paths are connected in parallel to allow control circuit, such as a microprocessor, to choose the proper current limiting impedance value based on the current draw of the electrical load device prior to the onset of a voltage sag or other power interruption that can cause a current inrush at the point of voltage recovery.

[0018] These and other aspects, features, and benefits of the claimed invention(s) will become apparent from the following detailed written description of the preferred embodiments and aspects taken in conjunction with the following drawings, although variations and modifications thereto may be effected without departing from the spirit and scope of the novel concepts of the disclosure.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0019] The accompanying drawings illustrate one or more embodiments and/or aspects of the disclosure and, together with the written description, serve to explain the principles of the disclosure. Wherever possible, the same reference numbers are used throughout the drawings to refer to the same or like elements of an embodiment, and wherein:

[0020] FIG. 1 is an exemplary block diagram of a power protection device environment, according to one embodiment of the present disclosure.

[0021] FIG. 2 illustrates an exemplary current versus voltage waveform characteristic comparison of amplitude versus time, according to one embodiment of the present disclosure.

[0022] FIG. 3 illustrates a power protection device architecture, according to one embodiment of the present disclosure.

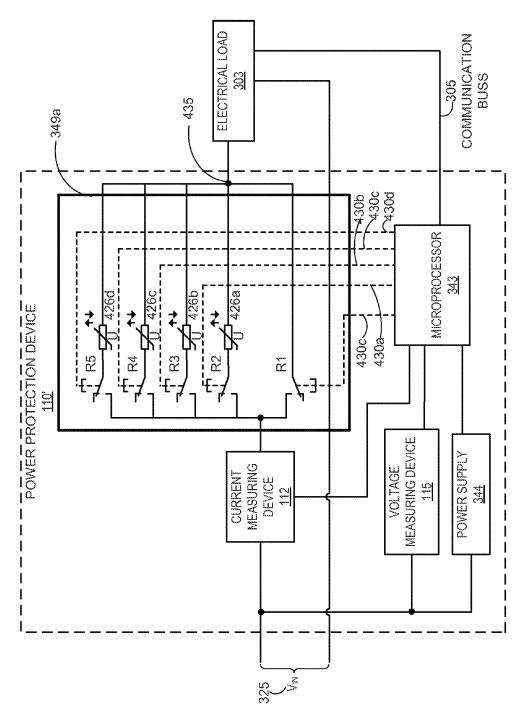

[0023] FIG. 4 illustrates an embodiment of a selective current inrush limiting protection circuit, according to one embodiment of the present disclosure.

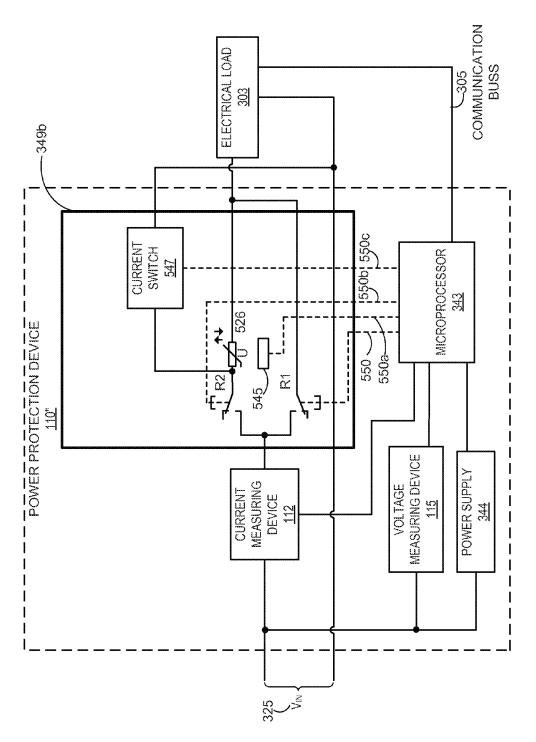

[0024] FIG. 5 illustrates an alternate embodiment of a selective current inrush limiting protection circuit, according to one embodiment of the present disclosure.

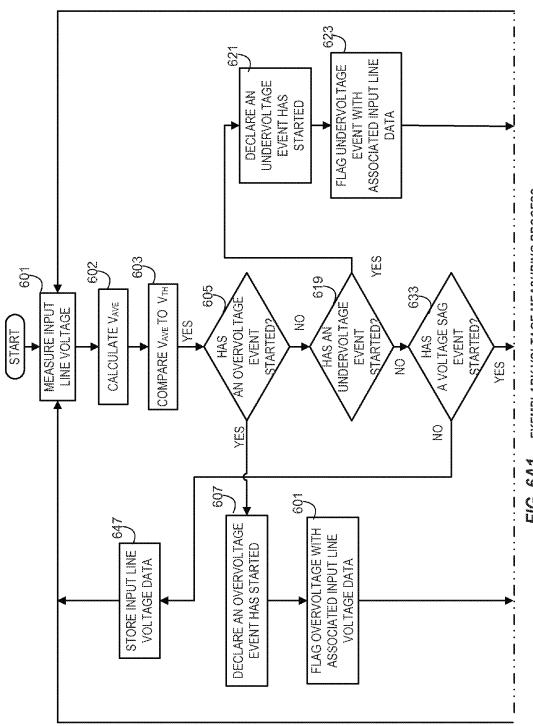

[0025] FIG. 6A1 is flow chart describing a first portion of a process for determining various voltage disturbances, according to one embodiment of the present disclosure.

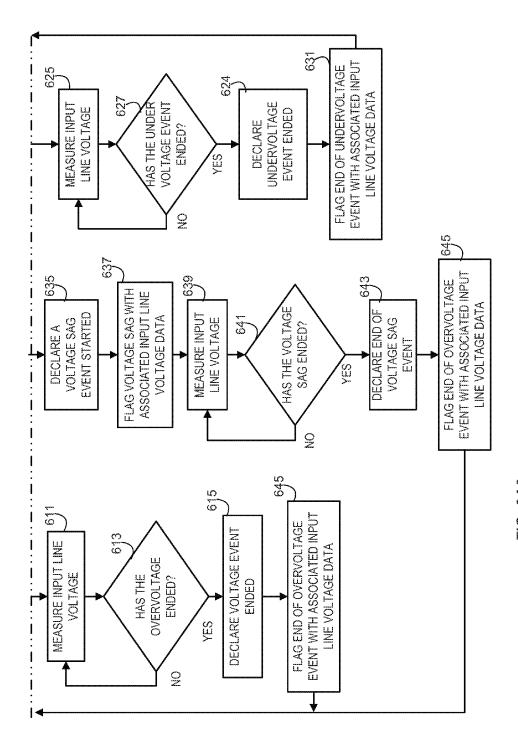

[0026] FIG. 6A2 is flow chart describing a second portion of a process for determining various voltage disturbances, according to one embodiment of the present disclosure.

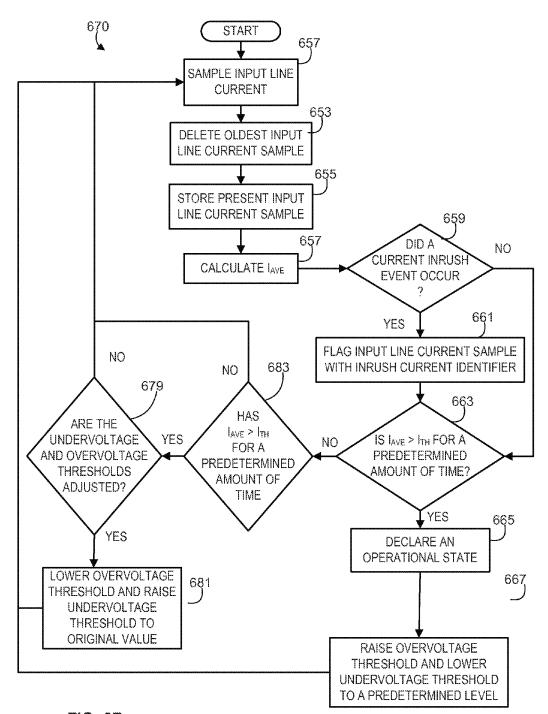

[0027] FIG. 6B is a flow chart describing a process for determining a current measuring process, according to one embodiment of the present disclosure.

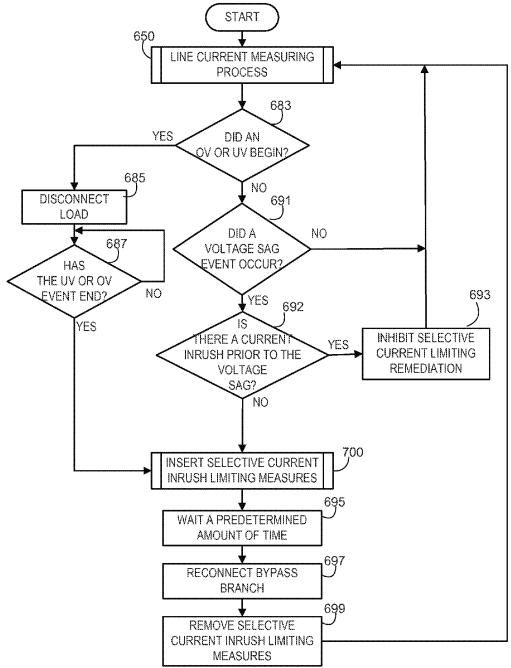

[0028] FIG. 6C is a flow chart describing a process for determining power protection device remediation or inhibition, according to one embodiment of the present disclosure.

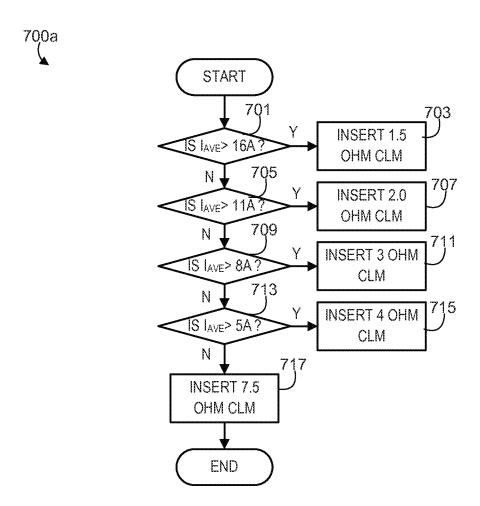

[0029] FIG. 7A is a flow chart illustrating a process of selective current limiting based on the average load current, according to one embodiment of the present disclosure.

[0030] FIG. 7B is a flow chart illustrating a process of selective current limiting based on the average load current, according to one embodiment of the present disclosure.

[0031] FIG. 7C is a flow chart illustrating a process of NTC temperature modulation based on the average load current, according to one embodiment of the present disclosure.

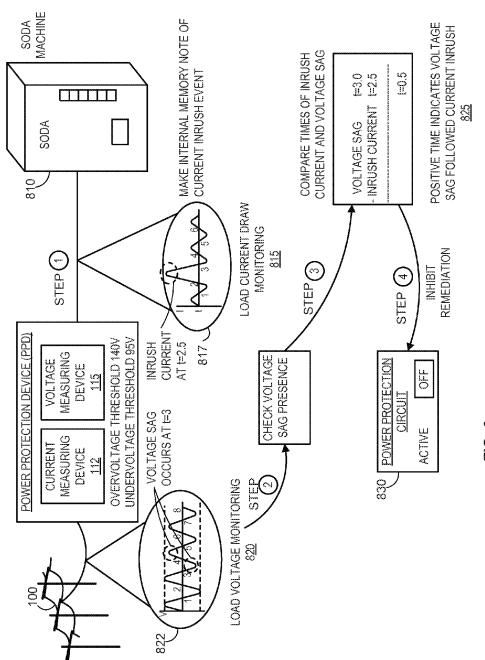

[0032] FIG. 8 is an exemplary block diagram of a power protection device environment, according to one embodiment of the present disclosure.

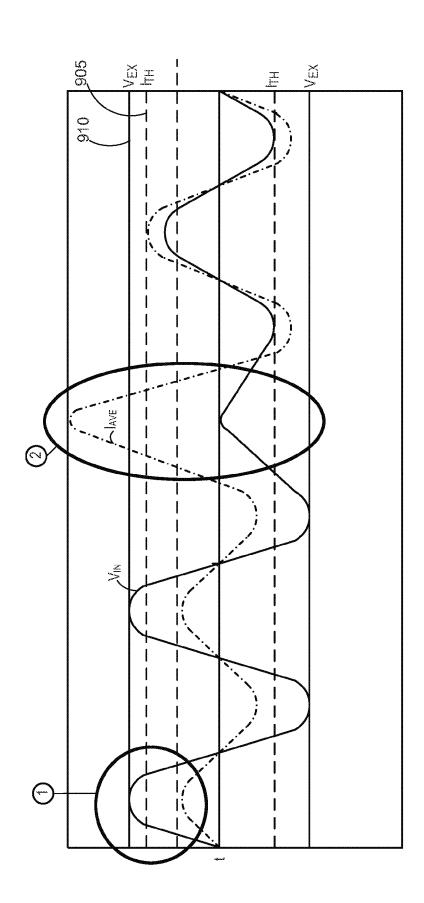

[0033] FIG. 9 illustrates an exemplary current versus voltage waveform characteristic comparison of amplitude versus time, according to one embodiment of the present disclosure.

#### DETAILED DESCRIPTION

#### Overview

[0034] For the purpose of promoting an understanding of the principles of the present disclosure, reference will now be made to the embodiments illustrated in the drawings and specific language will be used to describe the same. It will, nevertheless, be understood that no limitation of the scope of the disclosure is thereby intended; any alterations and further modifications of the described or illustrated embodiments, and any further applications of the principles of the disclosure as illustrated therein are contemplated as would normally occur to one skilled in the art to which the disclosure relates. All limitations of scope should be determined in accordance with and as expressed in the claims.

[0035] Aspects of the present disclosure generally relate to systems and methods for efficiently remediating an undesirable input power voltage due to a power disturbance. According to one embodiment, a power protection device (PPD) determines the operational state of an electrical load device being protected by a power protection device in order to make a determination if remediation as a response to a power disturbance should be inhibited. In one embodiment, the operational state of the electrical load device is determined by use of a current sensing mechanism that monitors the current draw of the electric load. In one embodiment, the PPD may relax the disturbance detection parameters or inhibit remediation according to predetermined load state to ensure that the load maintains proper functionality. In another embodiment, the PPD may remediate a power disturbance according to a load state and/or line voltage condition. Further and according to another aspect, the PPD may remediate a power disturbance according to a load current anomaly and/or line voltage conditions. In further embodiments, aspects of the PPD generally enable the system to determine whether the source of the voltage disturbance is due to load operations or if the source of the voltage disturbance is from the power grid. Generally, the source of a voltage disturbance will dictate the execution and/or inhibition of remediation.

[0036] In one embodiment, the PPD comprises a selectively variable current inrush limiting apparatus, wherein various impedance mechanisms are inserted into the voltage and current path to the load according to the current draw of an electrical load device operation as measured by current measuring device. In one aspect, multiple impedance paths are connected in parallel to allow a microprocessor to choose the proper current limiting impedance value based on the current draw of the electrical load device prior to the onset of a voltage sag or other power interruption that can cause a current inrush at the point of voltage recovery.

# **Exemplary Embodiment**

[0037] Referring now to the figures, FIG. 1 illustrates an embodiment of a power protection device (PPD) 110 in an

exemplary environment, constructed and operated in accordance with various aspects of the present disclosure. In general, FIG. 1 illustrates a scenario involving the determination of an operative state of an exemplary load (e.g., a mass production color printer 120) corresponding to power disturbance source identification and appropriate related remediation of the associated power disturbance.

[0038] More specifically, FIG. 1 illustrates an exemplary load in a running state, the detection of a power disturbance, namely a voltage sag, within the input power voltage, and a decision to inhibit voltage disturbance remediation. Assume that the mass production color printer 120 is a load system significant to an operating companies business, whereby stopping a printing process may be detrimental to the printer's business operations. It is known that many production color printers 120 can tolerate a range of operating voltages without undue risk of damage or fault. For example, some production color printers can safely tolerate an input power voltage variation of +30V and -30V. In this exemplary scenario, a power protection device 110, coupled to a mass production color printer 120, is coupled to an input AC power source (e.g. a power line 100, a distributed power system, etc.). Further, an input AC power source maybe referred to herein as a supply voltage, an input power voltage, an input line voltage, etc.

[0039] Assume that the protection settings of the PPD 110 has an overvoltage threshold of 140V and an undervoltage threshold of 95V, wherein some form of remediation will be invoked if the power voltage falls outside of the range of the thresholds. In one aspect, the PPD 110 continuously measures and stores the average current draw of the load during its operation and identifies a plurality of predetermined currentrelated events (e.g., current inrush, over threshold current draws, and current anomalies) according to the characteristics of the measured average current draw. Typically, the window of time for the stored current measurements may comprise a duration of anywhere between 60 cycles of data to hours of data according to the demand of the system. In certain instances, the PPD may adjust the overvoltage or undervoltage thresholds according to various parameters indicative of a load's operating state. For example, the load may be in a running state, comprise a critical system that should not be interrupted unless there is significant risk of damage or disruption to the job, and therefore, the overvoltage and undervoltage thresholds may adjust to enable a larger tolerance for various power disturbances such that the operation of the load will not be interrupted for minor occurrences that do not present undue risk.

[0040] The PPD 110 also measures and averages voltages supplied to the load to identify various predetermined events (e.g., voltage sag, momentary power outage, power disruption, undervoltage, overvoltage, etc.) and analyzes the relationship between the supply voltage and the stored average current draw of the current to determine the source of the occasion or power disturbance. Accordingly, the PPD 110 stores a plurality of voltage samples as an average input line voltage measurement  $V_{AVE}$  to determine the input line voltage trends. Further, the PPD 110 detects various power disturbances that are typically identified as an average input line voltage measurement  $V_{AVE}$  magnitude, which has remained at a certain magnitude for a predetermined amount of time (as will be described further herein).

[0041] As will be understood, typically, voltage sags are characterized by drops of between 10%-90% of nominal (sys-

tem) input line voltages. The drops in voltage typically last from a cycle (16.6 millisecond) to a second or so, or tens of milliseconds to hundreds of milliseconds. Similarly, an undervoltage is characterized by drops of similar nature of the nominal (system) input line voltage, but the drops in an undervoltage condition typically of a longer duration than a voltage sag. The required duration utilized to determine an undervoltage may comprise any number of cycles, seconds, milliseconds, minutes, hours, etc., but typically a duration of an undervoltage is approximately 2 seconds. Further, the PPD 110 determines whether to remediate the power disturbance or to inhibit remediation because the power disturbance is not significant to the operation of the load or remediation may impact operation of the load.

[0042] Still referring to FIG. 1, a particular sequence of events in this exemplary scenario is illustrated sequentially as numbered circles, each of which is associated with a step of a process as herein described. Starting at step 1, a power protection device (PPD) 110 comprising a current measuring device 112 is coupled to an electrical load and an input voltage source (e.g., a power line 100). In this specific exemplary scenario, assume that the electrical load comprises a mass production color printer 120. As will be generally understood by one of ordinary skill in the art, any electrical load current variations detected by the current measuring may be due to differing connected equipment, but also may be due to different modes of operation within the same piece of equipment. On some industrial equipment, current inrushes can reach levels up to 50-500 times that of the rated steady-state line current.

[0043] Assume that the current measuring device 112 of the PPD is real-time monitoring the average current draw  $I_{AVE}$  of the load 117 with an expected threshold current,  $I_{TH}$ , of 9 amperes (A). Assume that the current draw when the printer is in an operational state of standby mode is 9 A. Therefore, in the scenario of FIG. 1, the expected threshold current  $I_{TH}$  is set according to the current draw of the electrical load in standby mode. The PPD 110 keeps a running average of the current draw within a window of time where the oldest current measurement sample value is deleted from the average calculation each time a new load current measurement sample is taken.

[0044] In the example of FIG. 1, the  $I_{AVE}$  is presently shown at 12 A, which indicates that the present  $I_{AVE}$  is greater than the expected threshold current  $I_{TH}$ . In this scenario, assume that when the mass production printer 120 is actively printing (at say, full capacity), the current draw will be greater than when it is in standby mode. Assume that the current draw when the printer is in an operation state of standby mode is 9 A; therefore, the current threshold,  $I_{TH}$ , is determined to be 9 A. Similarly, the printer may be in an off mode, wherein the current draw is close to OA. Accordingly, in the scenario shown in FIG. 1,  $I_{AVE}$  is greater than  $I_{TH}$ , indicating that the printer is in an active printing state. As previously described, the mass production color printer 120 is considered an important device to an operative entity, which as at the discretion of the operational entity utilizing the mass production color printer.

[0045] Hence, at step 2, the PPD adjusts the overvoltage and undervoltage thresholds to 150V and 90V 125, respectively, to ensure that operation of the mass production color printer 120 does not cease in the event of a power disturbance occurs presenting an input power voltage outside of the previously non-adjusted voltage threshold range. The PPD deter-

mines that the mass color printer is in a run mode due to measuring the average current draw  $I_{AVE}$  (e.g. 12 A) and identifying the average current draw is  $I_{\mathit{AVE}}$  higher than the expected current threshold  $I_{TH}$  (e.g. 9 A) for a predetermined number of cycles. For example, the predetermined number of cycles may be 4 cycles, but as will be generally understood any number of cycles may be used to determine the operational run state of a load. At step 3, the PPD continuously monitors the line voltage 130 for various predetermined occurrences such as power or voltage disturbances. Assume that occurrences generally comprise various power disturbances such as a voltage sag, a momentary power outage, a power disruption, an undervoltage, an overvoltage, etc. As shown in step 3, during the monitoring process the PPD 110 compares the line voltage to a predetermined expected line voltage within the nominal range of satisfactory operation.

[0046] Assume at step 3 that a voltage sag occurs near t=4 for the line voltage supplied to the mass production color printer 120. At step 4, the PPD 110 identifies the onset of a voltage sag 135 near t=4, wherein the measured line voltage is lower than the expected or nominal line voltage. As will be generally understood, the PPD comprises a time stamping component, wherein a time may be associated with various actions/events (e.g., a power disturbance, a current inrush, an input line voltage sample, an input line current sample, etc.). Accordingly, the PPD 110 determines whether the source of the voltage sag is from the branch circuit (e.g. due to the steady state current draw of the mass color printer 120) or whether the voltage sag is from a power-grid power disturbance

[0047] At step 5, the PPD determines the source of the voltage sag, wherein the PPD checks the stored average current draw  $I_{AVE}$  to determine if a current inrush is present near the voltage sag in the time domain. As previously mentioned, a current inrush event typically comprises a time stamp dictating when the current inrush event occurred. Likewise, a power disturbance typically comprises a time stamp indicating when the event occurred. Therefore, in one embodiment, the PPD will compare the times of the two events to determine which occurred first, the difference between the events, and any other relationship between them. If a current inrush precedes the onset of the voltage sag, this more likely indicates that the load caused the voltage sag on the particular circuit branch. Alternatively, if a voltage sag occurs prior to a current inrush, or when there is no current inrush near the time of the voltage sag, generally the voltage sag is more likely due to an external source such as a power disturbance on a local branch circuit or on the power grid.

[0048] At step 6, the PPD 110 determines there is not a current inrush near the time of the onset of the voltage sag, indicating the voltage sag is due to power disturbance on the grid, and remediation is warranted. As known to those skilled in the art, during a voltage sag or other similar power disturbance, the capacitance within the certain types of loads will discharge its stored energy as the stored energy compensates for the lower input power voltage. Subsequently, when the voltage sag recovers, the capacitance within the electrical load generally draws a large amount of current to replenish the energy that was depleted, creating a large current inrush and a need for remediation. Assume that the power protection device 110 is specifically configured according to the typical current draw of the mass production printer 120. In this example, the protection circuit within the power protection device activates a 2 ohm current inrush limiting mechanism

**145**, according to predetermined parameters, for example, as shown in Table 1 and the description of Table 1.

[0049] After remediation has been effected, the PPD 110 generally has a wait period or built-in timing function, wherein the remediation stays active until a predetermined period of time has passed for the disturbance to end and power to be restored to within the nominal operating range. At step 7, the PPD waits the allotted predetermined period of time before removing the current inrush remediation measures, as shown in step 8. Accordingly, after the current remediation measures are removed the circuit is returned to the operating state as previously described in connection with step 2 with adjusted overvoltage and undervoltage thresholds.

[0050] It will be appreciated that the current remediation measures according to this disclosure may be overridden and insertion of the current remediation measures in to the current path will be inhibited (as will be described in greater detail in connection with the scenarios shown in FIG. 8). It will further be appreciated that the PPD detects a power disturbance within the branch circuit of the electrical load and determine current remediation measures according to the identification of a branch circuit-based voltage sag. It will still be further appreciated that the branch circuit-based voltage sag may be due to a particular electrical load on the branch circuit, wherein each electrical load on the branch circuit will receive a lower amplitude input power voltage due to the branch circuit-based voltage sag.

[0051] FIG. 2 illustrates the voltage and current characteristic comparison 140 (step 5 in FIG. 1) in connection with the discussion example of FIG. 1. As discussed, in step 5 of FIG. 1, the PPD 110 compares the presence of current inrush prior to the onset of the power disturbance (e.g. voltage sag) within the time domain. Accordingly, FIG. 2 is an illustrative representation of the voltage and current waveform characteristic relationship to identify the presence of a current event (e.g., current inrush, increase in current draw, etc.), wherein the presence of the current inrush or increase in current draw may determine that the power disturbance was caused by an electrical load fed from the branch circuit. If a current anomaly is present, the PPD further determines where the current inrush resides within the time domain in comparison with a power disturbance such as an undervoltage, overvoltage, voltage sag, etc.

[0052] As shown at numbered circle 1 of FIG. 2, the current  $I_{A\!V\!E}$  and voltage  $V_M$  are typical sine waves. Assume and as illustrated, the average current,  $I_{AVE}$  is trending over the indicated threshold current, I<sub>TH</sub>, 205, correlating with step 1 of FIG. 1. Accordingly and as previously described, an  $I_{AVE}$ trending over the predetermined current threshold indicates that the load device, e.g. the mass production color printer, is in a running state and is still considered an important load to the operational entity and should not be disconnected from power unless there is a significant power disturbance that presents risk of damage to the equipment. Further, at numbered circle 1 of FIG. 2, the measured voltage  $V_M$  is near the expected voltage  $V_{EX}$  threshold 210, indicating a generally normal steady state of the mass production color printer 120. [0053] The numbered circle 2 of FIG. 2 identifies an onset of a voltage sag, wherein the measured voltage  $V_M$  level is trending lower than the expected voltage  $V_{EX}$  threshold 210. Further, the  $I_{AVE}$  is consistently trending above the current threshold 205 without a current inrush occurrence, which indicates a steady state running condition of the load, e.g. the mass production color printer 120. According to various embodiments of the present disclosure, the PPD 110 compares the voltage and current characteristics in the time domain to determine various predetermined conditions. For example and as illustrated in FIG. 2 and described in connection with FIG. 1, a voltage sag without an increase in measured current  $I_{AVE}$  or a current inrush in the near present time prior to the voltage sag typically indicates a power disturbance originating in the power grid and generally necessitates power disturbance remediation.

[0054] FIG. 3 illustrates a power protection device (PPD) 110, which is generally connected at an interface between an input line voltage 325 and an electrical load 303 according to one embodiment of the present disclosure. In one aspect, the PPD 110 comprises a current measuring device 112 for measuring the current drawn by the electrical load 303. The amount of current drawn by the electrical load 303 may be used as an indicator of the electrical load's operational state. For example, when an electrical load is running, it typically draws more current than when the electrical load is in a standby mode. In another aspect, the current measuring device 112 is used not only to measure average current draw prior to any possible disturbance, but also senses the current inrushes such as those due to inductive electrical loads.

[0055] In one embodiment, the current draw is measured in real-time by the current measuring device 112. The current draw information is sent to the microprocessor 343 for further analysis. According to various embodiments, the current measuring device 112 comprises any type of current sensing circuit. For example and in one embodiment, the current measuring device 112 may comprise a stand-alone current measuring integrated circuit, which passes measurements to the microprocessor 343. In another embodiment, the current measuring device 112 may comprises a current transformer connected either to an external integrated circuit or to analog and/or digital ports within the central processing circuit 343. In another embodiment, the current measuring device 343 comprises a series resistor connected either to an external integrated circuit or to analog to digital ports within the central processing circuit 343.

[0056] According to one aspect, the PPD 110 keeps a running average of the current draw within a window of time where the oldest current measurement sample value is deleted from the average calculation each time a new load current measurement sample is taken. As previously described, the window of time could be of any length from 1 cycle to hours of data, but a window of between 240 and 480 electrical cycles or 4 to 8 seconds is generally utilized. In addition, instantaneous current inrushes are monitored by comparing the current sample to the previous sample and looking for a large differentiation in amplitude. Accordingly, if the differentiation amount continually increases and the amplitude is above a threshold considerably higher than the average current draw of the electrical load 303, then a marker in memory is set within the power protection device 110 indicating that a current inrush has just occurred. As will be generally understood by one of ordinary skill in the art, the process of comparing a current sample to a previous sample is mathematically equivalent to taking the first derivative of the current signal.

[0057] Still referring to FIG. 3, in one embodiment, the PPD 110 further comprises a voltage measuring device 115 for sensing and measuring voltages connected to the PPD. According to one aspect, the voltage measuring device 115

ensures the line voltage  $V_{IN}$  325 is within an acceptable predetermined nominal operating range prior to the connection of the load to prevent damage to the load by supplying an input power voltage outside of an acceptable range of the load. Line voltage 325 is generally measured in real-time by the voltage measuring device 115. This information is also sent to the microprocessor 343.

[0058] Generally, after the line voltage 325 is determined to be satisfactory for powering the attached electrical load 303, the PPD connects the electrical load 303 to the power source. In certain embodiments, the voltage measuring device 115 can be any type of circuit providing either an isolated or a non-isolated interface between the voltage being monitored and the microprocessor 343. In another embodiment, the voltage measuring device 115 could also be a stand-alone voltage measurement device 112 that reads the voltage and passes the value to the microprocessor 343.

[0059] According to one aspect of the embodiment of FIG. 3, the PPD 110 further comprises a microprocessor 343 that is operative for executing an algorithm for detecting and remediating power grid disturbances, as well as to making remediation-inhibiting decisions based on current and voltage measurements received from the current measuring device 112 and the voltage measuring device 115. In one aspect, the microprocessor 343 with the use of voltage measuring device 115 continually monitors the input line voltage 325 to detect voltage anomalies, voltage signatures, etc. In one aspect, some of the various voltage signatures being monitored comprise voltage sags, momentary power disruptions, overvoltage scenarios, undervoltage scenarios, etc. In various embodiments, the microprocessor 343 may comprise any type of central processing unit or state machine such as a microprocessor, microcontroller, field programmable gate array (FPGA), or any other device that can execute algorithms for detecting and remediating power disturbances. In other embodiments, the microprocessor 343 may comprise peripheral functionality such as an analog-to-digital converter, serial communication ports (e.g., I2C, SPI port, etc.) or other circuitry to communicate with other circuits or integrated circuits.

[0060] In one aspect, the microprocessor 343 operates in a monitoring mode where it continually samples the line voltage 325 to detect power disturbances such as, but not limited to voltage sags, overvoltages, undervoltages, momentary power interruptions, and power outages. In the discussion in FIG. 1, the power disturbance comprised a voltage sag due to a power grid anomaly, wherein the measured voltage started trending at a level lower than the expected value. In another aspect, a sample-by-sample comparison between the incoming line voltage and a predetermined expected voltage at the same point of the correct line voltage may be used to determine a line voltage disturbance in less than a ½ or ¼ cycle. According to various aspects, measured values are compared to predetermined thresholds for each disturbance type in order to determine if remediation is required or should be inhibited. In one aspect, prior to and during the detection of voltage disturbances, the microprocessor 343 determines whether to change the parameters for voltage disturbance detection or to inhibit remediation for a detected power disturbance.

[0061] In one exemplary aspect, the determination is made by measuring the average current draw  $I_{AVE}$  of the electrical load 303, detecting current inrushes and/or anomalies, storing the average current draw data, and comparing to the detection

of voltage disturbances via the microprocessor **343**. Further, in another aspect, as mentioned in connection with FIG. **1**, the microprocessor typically comprises a time stamping mechanism that can associate a time with a particular event, action, data, etc.

[0062] In one aspect, by detecting current inrushes that occur prior to voltage disturbances, the microprocessor 343 can evaluate whether or not to remediate against the current inrush. Generally, voltage sags or momentary power interruptions to an electrical load can cause current inrushes when the input line voltage returns to the nominal voltage. Therefore, as a voltage sag or power interruption is experienced at an electrical load 303, the charge on the capacitors internal to an electrical load reduce because energy stored in the capacitor is dissipated by other circuitry within the electrical load. When the voltage sag or momentary power outage recovers, the now-discharged capacitors draw a relatively unabated current impulse or current inrush because the electrical load's own current inrush limiting component, if present, may not have had enough time to reset. Typical reset times for current inrush limiting devices, such as negative temperature coefficient thermistors found in some internal protective circuits within electrical loads, vary based on their chemical characteristic and temperature but it is usually approximately 30 seconds to 2 minutes. However, time between onset and recovery for grid-based and branch circuit-based voltage sags can be as quick as 2 AC cycles (32 mS).

[0063] According to one embodiment, the microprocessor 343 further comprises a timer mechanism for determining the time remediation recovery and reset of the current inrush limiting components, wherein a predetermined period is generally utilized before the current inrush limiting components are removed from the circuit. In one embodiment, the microprocessor 343 continuously monitors the line voltage 325 until the power disturbance and recovery has completed. Accordingly, the microprocessor waits a predetermined amount of time afterwards before restoring the protection circuit 349 back to a non-remediation state.

[0064] Still referring to FIG. 3 and in one embodiment, the PPD 110 comprises a power supply 344 for providing DC voltage to power the PPD circuit. According to one aspect, the power supply 344 provides power to the microprocessor 343 and the microprocessor provides power to the other elements in the PPD 110. In another aspect, the power supply 344 directly provides power to the other elements in the PPD 110. [0065] As further shown in the FIG. 3 embodiment, a protection circuit 349 is generally controlled by a control circuit, such as a microprocessor 343. According to one aspect, the protection circuit 349 performs various power disturbance remediation tasks including but not limited to isolating the electrical load 303 with the use of a switching component from the input line voltage 325. In another aspect, the protection circuit 349 provides current inrush limiting protection measures, which certain embodiments will be discussed in greater detail below.

[0066] In one embodiment, a communications buss 305 may be utilized to provide a "load functioning" signal to indicate to the power protection device 110 that the electrical load 303 is in use. Such a load functioning signal may be utilized to determine the operational state of the load, either independently or in conjunction with monitoring the average current draw of the electrical load 303. In one aspect, the communications buss 305 transmits the load functioning signal to the microprocessor 343 to inform the microprocessor

the operational state of the electrical load 303. The operational state of the electrical load may comprise a running state, a level of a running state (e.g., 50% full capacity), standby state (e.g., not running, but powered on and ready to run), etc. For example, the operational load may transmit a signal via the communications buss 305 to inform the microprocessor 343 that the electrical load 303 is running and to start measuring the average current draw of the electrical load. Further, the communications buss 305 may transmit the level of the running state of the electrical load 303 to the microprocessor 343, such that the microprocessor 343 can determine the appropriate level of remediation according to the level of the running state.

[0067] Accordingly and in one aspect, the communications buss 305 could be as simple as a dry relay contact located within the electrical load 303 that changes state when the electrical load 303 is in use. In another aspect, the communications buss 305 could be a higher-level two-way communications buss such as an I2C, USB, SPI, RS232, etc. and the power protection device 110 would then adjust its disturbance detection parameters as described above. In one aspect, the load functioning signal may comprise a binary information signal, wherein one value represents a running state, and the opposite value represents a standby or off state. In another aspect, the load functioning signal may comprise a dynamic signal correlating to various levels of the running state of the electrical load (e.g. proportional to its running capacity on a 1-100% scale).

[0068] FIG. 4 illustrates an embodiment of an exemplary power protection device 110' comprising a selective current inrush limiting circuit protection circuit. According to one embodiment, the selective current inrush limiting circuit (SCILC) 349a is connected at an interface between an input line voltage 325 and an electrical load 303. According to one aspect and similar to the FIG. 3 embodiment, the SCILC 349a comprises a voltage measuring device 115, a power supply 344, a current measuring device 340, a microprocessor 343 and an electrical load 303. As will be generally understood, the aforementioned components typically execute the same functions as described for similar components in connection with FIG. 3.

[0069] In one embodiment, the SCILC 349a comprises relays R1, R2, R3, R4, and R5 connected in series with selective current inrush limiting components 426a, 426b, **426**c, and **426**d, respectively. According to one aspect, R1 provides a bypass path around the current inrush limiting components, wherein the impedance in the current path is a predetermined non-current limiting impedance of the PPD 110'. In another aspect, R2, R3, R4, and R5 are arranged in parallel to a node 435 and provide individually or combinatorial selectable current paths containing different values of current inrush limiting component, specifically in this embodiment in the form of negative temperature coefficient thermistors (NTC). In certain embodiments, R1, R2, R3, R4, and R5 may be mechanical relays, solid state relays, siliconcontrolled rectifiers (SCRs), or any other switching element. Further, the relays are typically controlled by the microprocessor 343 via control signals through the relay's associated control line 430a, 430b, 430c, 430d, and 430e.

[0070] In one embodiment, the SCILC 349a comprises selectively-enabled resistive elements 426a, 426b, 426c, and 426d for reducing the current inrush that an electrical load may draw from a power source. According to one aspect, insertion of the resistive elements into the circuit will gener-

ally provide a voltage drop and thereby reduce the amount of current within a circuit path. In one embodiment, the resistive elements **426***a*, **426***b*, **426***c*, and **426***d* are placed in parallel within the SCILC **349***a*. In another embodiment, the resistive elements may be placed in series. In yet another embodiment, the resistive elements may be placed in a combination of series and parallel. In one embodiment, the resistive elements **426***a*, **426***b*, **426***c*, and **426***d* comprise negative temperature coefficient thermistors (NTC).

[0071] As will be generally understood by one of ordinary skill in the art, placing the resistive elements in other configurations will still provide various current inrush limiting effects and the disclosed embodiment is not intended to limit the spirit or scope of the present disclosure. Further and in certain embodiments, resistive elements 126 may comprise any resistive element such as a resistor, inductor, or any other device providing real or complex impedance with any resistive value.

[0072] According to one embodiment, the SCILC 349a comprises a microprocessor 343 for running a computerimplemented process for detecting and remediating power grid disturbances as well as selecting the value of current inrush limiting component(s). In one embodiment, the microprocessor 343 runs in monitoring mode, in which the microprocessor continually samples the line voltage 325  $V_{IN}$  to detect power disturbances such as but not limited to voltage sags, overvoltages, undervoltages, momentary power interruptions, and power outages. Further, and in one aspect, monitoring mode also continuously samples the current draw of an electrical load, stores a predetermined number of cycles of the current draw, and flags detected current events (e.g., current inrushes, current draw increases, etc.). In one aspect, a monitoring mode of the microprocessor 343 may be achieved by comparing a measured value using an RMS or other averaging method of the line voltage  $V_{in}$  325 over half of a sinusoidal voltage cycle to an expected value of the correct line voltage. Alternately and in another aspect, a sample-bysample comparison between the incoming line voltage and an expected value at the same point of the correct line voltage may determine a line voltage disturbance in less than half or quarter of a sinusoidal voltage cycle. As will be generally understood, the sample-by-sample comparison of the incoming line voltage and the expected voltage value may determine a line voltage disturbance within any portion of a sinusoidal voltage cycle.

[0073] As will be generally understood, measured current and voltage values are compared to predetermined thresholds for each disturbance type and the extent of the disturbance in order to determine if remediation is required. In one embodiment, during the line voltage monitoring process, the microprocessor 343 also measures the average current draw of the electrical load, as described in the FIG. 1 discussion example. Accordingly, the SCILC 349a identifies current values for a predetermined period of time prior to any possible detected power disturbance. This is generally accomplished by keeping a running average of the current draw within a window of time where the oldest current measurement sample value is deleted from the average calculation each time a new load current measurement sample is taken. In certain embodiments, the stored current values are stored locally on the PPD 110', the microprocessor 343, on a hard drive, transmitted to a database, etc. As will be generally understood by one of ordinary skill in the art, the window could be of any length but a window of between 240 and 480 electrical cycles or 4 to 8

seconds is generally utilized. Furthermore and in certain embodiments, processes may be implemented that look at load current trends over normal use to predict the actual load current at the time of remediation if the load current varies regularly over time.

[0074] In one embodiment, the microprocessor 343 inserts selectively variable current inrush limiting circuitry as remediation as a result of a detected voltage sag or power disturbance. Generally, during a voltage sag, capacitance within the electrical load 303 discharges as a result of providing makeup power after the supply power is in sag or interruption. At the point of recovery from a voltage sag or momentary interruption, discharged capacitors typically pull an inordinately large amount of current or current inrush, as the load's internal current limiting NTC (if present) has not had sufficient time to cool and therefore regain its current limiting characteristics.

[0075] In one embodiment, the value of the NTC within the SCILC is determined by the amount of current the load generally draws during steady state operation. In one aspect, the NTC is placed in series with a switching device to allow it to be inserted in series at or near the onset of a voltage sag and remain in the circuit until after the voltage sag or interruption recovers. In another embodiment, instead of a single NTC, multiple NTCs are switched in series with the load using a plurality of switching devices R2, R3, R4 and R5 shown in FIG. 4. As will be generally understood by one of ordinary skill in the art, although the FIG. 4 embodiment utilizes four NTCs with corresponding switching mechanism, any number and/or combination of NTCs and switching devices may be used and the present embodiment is not meant to limit the spirit or scope of the present disclosure.

[0076] According to one aspect, before connecting a line voltage 325 to the power protection device (PPD) 110', all relays R1, R2, R3, R4, and R5 in FIG. 4 are generally open and there is typically no line voltage presented to the electrical load 303. Upon connection of line voltage 325 to the PPD 110', the microprocessor 343 executes an algorithm that checks the line voltage 325 by use of an analog-to-digital converter either residing within the microprocessor itself, or as a part of the voltage measuring device 115 circuit 342. In any case, after the line voltage 325 is determined to be satisfactory for powering the electrical load 303, microprocessor 343 switches R1 closed to connect the line voltage 325 to the electrical load 303. In another aspect, the powering on of the electrical load 303 may be performed by asserting at least one other relay or any combination of relays R2, R3, R4, and/or R5 to provide current inrush limiting upon power up in the event that the electrical load's 303 own internal current inrush limiting device is determined by the selective current inrush limiting circuit 349a to be inoperative due to recently being in the on state and not having sufficient time for the electrical load's 303 internal current inrush limiting component to properly reset. In one aspect, after a predetermined period of time, R1 then closes and all other switching devices are opened. In another aspect, R1 typically remains closed connecting the line voltage 325 to the electrical load 303 bypassing all current inrush limiting components.

[0077] Accordingly and in one aspect, the communications buss 305 could be as simple as a dry relay contact located within the electrical load 303 that changes state when the electrical load 303 is in use. In another aspect, the communications buss 305 could be a higher-level two-way communications buss such as an I2C, USB, SPI, RS232, etc. and the

power protection device 110 would then adjust its disturbance detection parameters as described above. In one aspect, the load functioning signal may comprise a binary information signal, wherein one value represents a running state, and the opposite value represents a standby or off state. In another aspect, the load functioning signal may comprise a dynamic signal correlating to various levels of the running state of the electrical load.

[0078] According to one embodiment and as shown in Table 1, various values of current limiting impedances for selective insertion may be calculated based on a historical current draw of the electrical load in order to keep the resulting voltage seen by the load above 90V. As will be generally understood by one of ordinary skill in the art, many 120V electrical loads can work properly for a period of time if the input voltage is at least above 90V. As shown, the current limiting impedances are inversely varying according to the current draw of the load prior to a voltage disturbance such that after inserting the current limiting impedance, the resultant voltage seen by the load remains above 90V. Further, when a voltage disturbance is detected, remediation is effected. Remediation could be different depending on the disturbance type.

TABLE 1

| Current Draw<br>by the Load | Inserted Current<br>Limiting Impedance | Resultant Voltage<br>seen by the Load |

|-----------------------------|----------------------------------------|---------------------------------------|

| 20                          | 1.5                                    | 90                                    |

| 19                          | 1.5                                    | 91.5                                  |

| 18                          | 1.5                                    | 93                                    |

| 17                          | 1.5                                    | 94.5                                  |

| 16                          | 1.5                                    | 96                                    |

| 15                          | 2                                      | 90                                    |

| 14                          | 2                                      | 92                                    |

| 13                          | 2                                      | 94                                    |

| 12                          | 2                                      | 96                                    |

| 11                          | 2                                      | 98                                    |

| 10                          | 3                                      | 90                                    |

| 9                           | 3                                      | 93                                    |

| 8                           | 3                                      | 96                                    |

| 7                           | 4                                      | 92                                    |

| 6                           | 4                                      | 96                                    |

| 5                           | 4                                      | 100                                   |

| 4                           | 7.5                                    | 90                                    |

| 3                           | 7.5                                    | 97.5                                  |

| 2                           | 7.5                                    | 105                                   |

| 1                           | 7.5                                    | 112.5                                 |

[0079] As will be generally understood, the current drawn by the electrical load 303 generally varies according to the type of load. In one aspect, the resistive element values 426a, 426b, 426c, 426d are generally chosen according to the current draw of the load such that when current inrush remediation is active, the resultant voltage seen by the load remains above 90V. In one aspect illustrated in Table 1, exemplary current draw and resistive element values have been chosen and a voltage seen by the load has been calculated to demonstrate the current inrush limiting process. Accordingly, as the current measuring device 340 monitors the real time current draw of the electrical load 303, the microprocessor 343 selects the appropriate resistive element to insert into the circuit to ensure the voltage seen by the load remains above 90V and current inrush is abated. Further discussion in connection with the process of selecting the proper resistive element will be described in greater detail in connection with FIG. 7.

**[0080]** As will be generally understood, once a current limiting impedance is inserted, the resulting voltage as seen by the load drops due to a voltage drop across the inserted current limiting component following  $V_{drop} = I_{load} *R$ . In one aspect, the voltage drop varies depending on the current draw of the load. For example, if the current draw prior to a disturbance was 10 amperes and a resistive current limiting device of 7.5 ohms was inserted, the voltage drop across the current limiting device is 75V (10 A\*7.5 ohms) resulting in the voltage seen by the load to be 45V (120V–75 V). As previously discussed, for most 120V electrical loads, this results in the load being unintentionally cut off due to an excessive reduction in input voltage.

[0081] FIG. 5 illustrates an alternate embodiment of a PPD 110" that utilizes a variable current limiting impedance for remediation of power disturbances in accordance with various systems and methods of the present disclosure. Similar to the embodiment presented in FIGS. 3 and 4, the exemplary embodiment shown in FIG. 5 comprises a current measuring device 112, a voltage measuring device 115, a power supply 344, a microprocessor 343, and an electrical load 303 that generally perform the same functions as the example for FIGS. 3 and 4. The embodiment illustrated in FIG. 5 further comprises a temperature modulated selective current limiting circuit (TMSCILC) 349b.

[0082] Additionally and in one aspect, the current limiting impedance 349b comprises an NTC thermistor 526 in series with a switching device R2. In one aspect, the TMSCILC comprises a temperature sensor 545, which is physically positioned adjacent to the NTC thermistor 526 and measures the temperature of the NTC. Further and according to one aspect, the TMSCILC 349b further comprises a current switch 547 that is controlled by the microprocessor 343. In one aspect, the current switch 547 is used to bypass the NTC thermistor **526**, such that the NTC thermistor can reduce its temperature by eliminating the current flow through the NTC thermistor. [0083] In one embodiment, the power protection device 110" is a least in part a process executed by the microprocessor 343, wherein the microprocessor is in a monitoring mode where it monitors the input line voltage in order to detect disturbances including, but not limited to voltage sags, overvoltages, undervoltages, momentary interruptions, power outages, etc. Further and according to another aspect, the monitoring mode process also measures the average current draw of the electrical load 303. After initial startup, the switch R1 is closed, connecting the electrical load 303 to input line voltage V<sub>IV</sub>.

[0084] According to one aspect, switch R2 of the TMSCILC **349***b* is open, removing NTC **526** from the circuit. During the monitoring process, once the average current draw of the electrical load 303,  $I_{AVE}$ , is calculated, the determined value of current limiting resistance, as determined in accordance with the average current draw of the electrical load 303, for the NTC 526 is adjusted by closing current switch 547 and pulling current through NTC 526. As will be generally understood by one of ordinary skill in the art, the NTC thermistor's resistance varies with heat, wherein generally as the NTC heats up it becomes less resistive than at room temperatures or colder temperatures. Accordingly, this characteristic may be exploited by measuring its temperature in order to determine the NTC's resistance. In one aspect, the current switch 547 is manipulated by being steadily turned on or by being pulsed on with an appropriate duty cycle such that the current flows through the NTC 526. Then the NTC is allowed to cool by opening the current switch 547 as to maintain the proper temperature and the corresponding impedance value. Accordingly, pulsing the current switch 547 allows the NTC to heat and cool, which effectively maintains a steady or consistent impedance value. As previously described, the resistance value of NTC 526 is monitored by monitoring the temperature sensor 545. Accordingly, the microprocessor 343 executes program code to provide a process for determining the impedance of the NTC by analyzing the temperature data received from the temperature sensor 545.

[0085] According to one aspect, generally, R1 is initially closed allowing the electrical load 303 to be connected to input line voltage 325. The current measuring device 112 340 is read by microprocessor 343 and a target NTC temperature value is determined according to the average current draw of the electrical load 303 and an impedance, which the impedance is determined by the amplitude of the average current draw and heating the NTC 526 to a temperature that will provide the desired impedance. In one aspect, the microprocessor 343 then pulses current switch 547 and pulls current from the input line voltage 325 through switch R1 and NTC 526 to neutral. At the same time, microprocessor 343 monitors the NTC's 526 temperature via a temperature information signal from transmitted from the temperature sensor 545. In one embodiment, using a table stored in microprocessor 343, similar to that of Table 1, the desired resistance value is attained by pulsing current through NTC 526 by pulsing current switch 547 until the desired temperature as read by the microprocessor 343 using temperature sensor 545 is reached. [0086] For example, at room temperature, an NTC 526 suitable for use in an exemplary embodiment may have a value of 10 ohms. During normal operation, the average current drawn by the electrical load 303 is measured at 5 amperes. For the purpose of this exemplary discussion, normal operation typically comprises running without a current limiting impedance mechanism inserted into the supply current path to the electrical load 303. During normal operation, the microprocessor manipulates (e.g., closes and/or opens) the current switch 547 in order to pull current through NTC **526** and then to the load while monitoring the temperature information signal coming from the temperature sensor 545 to the microprocessor 343 in order to set the NTC 526 resistance to 4 ohms. Further, once the NTC reaches the appropriate temperature as determined by the temperature information signal, the microprocessor further manipulates the current switch to maintain the desired temperature correlating to the determined impedance.

[0087] Note that while the example presented in FIG. 5 uses a negative temperature coefficient (NTC) thermistor, a positive temperature coefficient thermistor (PTC) may also be used, which as will be understood requires a modification to the process, where in heating there the positive coefficient thermistor (PTC) increases the impedance of the PTC. Therefore, the operative algorithm of the microprocessor would inverse its logic and heat the PTC to increase the impedance. [0088] In one embodiment, the microprocessor 343 controls the operation of the current switch 547, the relays R1 and R2, and receives a temperature information signal form the temperature sensor 545 via communication/control lines 550c, 550, 550b, and 550a respectively. In one aspect, the communications buss 305 could be as simple as a dry relay contact located within the electrical load 303 that changes state when the electrical load 303 is in use. In another aspect, the communications buss 305 could be a higher-level twoway communications buss such as an I2C, USB, SPI, RS232, etc. and the power protection device **110** would then adjust its disturbance detection parameters as described above. In one aspect, the load functioning signal may comprise a binary information signal, wherein one value represents a running state, and the opposite value represents a standby or off state. In another aspect, the load functioning signal may comprise a dynamic signal correlating to various levels of the running state of the electrical load.

[0089] FIGS. 6A1 and 6A2 is a flow chart illustrating an exemplary voltage measuring and power disturbance detection process, according to one embodiment of the present disclosure. As previously described in connection with FIG. 3, the voltage measurement device 115 continues to sample and measure the input line voltage  $V_{IN}$  for detecting the presence/onset of a power disturbance (e.g., voltage sags, momentary interruptions, overvoltages, undervoltages, and power outages, etc.) and transmits the input line voltage measurements to the microprocessor 343, starting at 601. Further and according to one aspect, typically after the microprocessor identifies the presence of a power disturbance, the microprocessor 343 determines an appropriate remediation (as will be discussed further in connection with FIG. 6C).

At step 602, the microprocessor 343 preferably calculates the average measured voltage,  $V_{\mathit{A\!V\!E}}$  and uses  $V_{\mathit{A\!V\!E}}$  to determine the presence of various predetermined power disturbances. Alternatively, instantaneous voltage values could be used for some applications. Accordingly, at step 603, the microprocessor determines the presence/onset of various predetermined power disturbances by comparing the magnitude of  $V_{AVE}$  (or instantaneous voltage value if chosen) to the magnitude of an expected overvoltage threshold  $V_{THOV}$ . Subsequently, the microprocessor 343 determines the presence/ onset of an overvoltage by determining if the comparison result at step 603 comprises a  $V_{\mathit{AVE}}$  magnitude greater than the OV threshold voltage  $V_{THOV}$  magnitude and the greater magnitude of the V<sub>AVE</sub> has remained relatively consistent for a predetermined amount of time. In one aspect, the predetermined amount of time may comprise any period of time as directed and intended by the PPD 102. For example, the predetermined period may be \( \frac{1}{4} \) of a cycle, many cycles, second, or hours, but typically, a 2 second period is utilized. [0091] If the microprocessor 343 determines an overvoltage event has started, a declaration is made that an overvoltage event has started, as shown in step 607. Accordingly, at step 609, the microprocessor 343 sets a flag corresponding to the overvoltage event data. In one aspect, the flagged overvoltage event data may comprise the last amplitude of the measured input line voltage  $V_m$ , the amplitude of average measured voltage  $V_{\mathit{AVE}}$ , the time associated with the start of the overvoltage event, etc.

[0092] In one aspect, the microprocessor 343 starts a programmed routine to determine the end of the overvoltage event; hence, the microprocessor continues measuring the input line voltage  $V_m$  and calculating the measured average voltage  $V_{AVE}$ , as shown in step 611. Accordingly, at step 613, the microprocessor determines if the overvoltage has ceased, wherein the microprocessor compares the measured average voltage  $V_{AVE}$  to the OV threshold voltage  $V_{THOV}$ , and determines whether the input line voltage is equal to or below the OV threshold voltage  $V_{THOV}$ . If the measured average voltage  $V_{AVE}$  is equal to or lower than the OV threshold voltage  $V_{THOV}$ , the microprocessor declares the overvoltage event has ended, as shown in step 615. Alternatively, if the mea-

sured average voltage  $V_{AVE}$  is not equal to or lower than the threshold voltage  $V_{TH}$ , the microprocessor continues to measure the input line voltage  $V_m$  and calculate the measured average voltage  $V_{AVE}$ , as shown in step 611 and compares to the OV threshold voltage  $V_{THOV}$ , as shown in step 613.

[0093] Referring back to step 615, after the microprocessor 343 declares the overvoltage event has ended, the microprocessor clears the overvoltage flag with the associated input line voltage data. Subsequently, the microprocessor returns to the measuring input line voltages  $V_m$  as shown in step 601.

[0094] Refer back to step 605 in FIG. 6A1, wherein the microprocessor 343 determines if the presence/onset of an overvoltage has occurred. If the microprocessor determines that an overvoltage has not occurred, the microprocessor determines if the presence/onset of an undervoltage has occurred by comparing the magnitude of  $V_{\mathit{AVE}}$  to the magnitude of the expected undervoltage (UV) voltage threshold  $V_{THUV}$ . Subsequently, the microprocessor 343 determines the presence/onset of an undervoltage by determining if the comparison result at step 603 comprises a  $V_{AVE}$  magnitude less than the UV threshold voltage  $V_{\mathit{THUV}}$  magnitude and the lesser magnitude of the  $V_{\mathit{AVE}}$  has remained relatively consistent for a predetermined amount of time. In one aspect, as previously descried in connection with determination of an overvoltage, the predetermined amount of time may comprise any period of time as directed and intended by the execution of the PPD 102. For example, the predetermined period may be ½ of a cycle, many cycles, second, or hours, but typically, a 2 second period is utilized.

[0095] If the microprocessor 343 determines that an undervoltage event has started, the microprocessor makes a declaration that an undervoltage event has started, as shown in step 621. Accordingly, at step 623, the microprocessor 343 sets a flag corresponding to the undervoltage event data. In one aspect, the flagged undervoltage event data may comprise the last amplitude of the measured input line voltage  $V_m$ , the amplitude of average measured voltage  $V_{AVE}$ , the time associated with the start of the undervoltage event, etc.

[0096] In one aspect, the microprocessor 343 starts a programmed routine to determine the end of the undervoltage event; therefore, the microprocessor continues measuring the input line voltage  $V_m$  and calculate the measured average voltage  $V_{AVE}$ , as shown in step 625. Accordingly, at step 627, the microprocessor determines if the undervoltage has ceased, wherein the microprocessor compares the measured average voltage  $\mathbf{V}_{\mathit{AVE}}$  to the UV threshold voltage  $\mathbf{V}_{\mathit{THUV}},$  and determines whether the measured average voltage  $V_{\mathit{AVE}}$  is equal to or relatively close the UV threshold voltage  $\mathbf{V}_{\mathit{THUV}}$ If the measured average voltage  $V_{\mathit{AVE}}$  is equal to or relatively close to the UV threshold voltage  $V_{\mathit{THUV}}$ , the microprocessor declares the undervoltage event has ended, as shown in step 629. Alternatively, if the measured average voltage  $V_{AVE}$  is not equal to or lower by a predetermined amount than the UV threshold voltage  $\mathbf{V}_{\mathit{THUV}}\!,$  the microprocessor continues to measure the input line voltage  $V_m$  and calculate the measured average voltage  $V_{\mbox{\tiny AVE}},$  as shown in step  ${\bf 625}$  and compares  $V_{\mathit{AVE}}$  to the UV threshold voltage  $V_{\mathit{THUV}}$ , as shown in step 627. Referring back to step 629, after the microprocessor 343 declares the undervoltage event has ended, the microprocessor clears the undervoltage flag with the associated input line voltage data. Subsequently, the microprocessor returns to measuring input line voltages  $V_m$ , as shown in step 601.

[0097] Referring back to step 619, wherein the microprocessor 343 determines if the presence/onset of an undervolt-

age has occurred. If the microprocessor determines that an undervoltage has not occurred, the microprocessor determines if there is the presence/onset of a voltage sag, as shown in step 633 by comparing the magnitude of  $V_{\mathit{AVE}}$  to the magnitude of the expected voltage sag (VS) threshold  $V_{THVS}$ . Subsequently, the microprocessor 343 determines the presence/onset of a voltage sag by determining if the comparison result at step 603 comprises a  $V_{\mathit{AVE}}$  magnitude lower than the  $\operatorname{VS}$  threshold voltage  $\operatorname{V}_{\mathit{THVS}}$  magnitude and the lower magnitude of the  $V_{\mathit{AVE}}$  has remained for a predetermined amount of time. In one aspect, the predetermined amount of time may comprise any period of time as directed and intended by the execution of the PPD 102, typically for detection of a voltage sag, the predetermined amount of time is shorter than the predetermined amount of time for an undervoltage. As previously described, voltage sags are characterized by drops of between 10%-90% of nominal (system) input line voltages. The drops in voltage typically last from a cycle (16.6 millisecond) to a second or so, or tens of milliseconds to hundreds of milliseconds.