US011839086B2

## (12) United States Patent Petti et al.

#### (54) 3-DIMENSIONAL MEMORY STRING ARRAY OF THIN-FILM FERROELECTRIC TRANSISTORS

(71) Applicant: SUNRISE MEMORY

CORPORATION, San Jose, CA (US)

(72) Inventors: Christopher J. Petti, Mountain View,

CA (US); Vinod Purayath, Sedona, AZ (US); George Samachisa, Atherton, CA (US); Wu-Yi Henry Chien, San Jose, CA (US); Eli Harari, Saratoga, CA

(US)

(73) Assignee: SUNRISE MEMORY

CORPORATION, San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/812,375

(22) Filed: Jul. 13, 2022

(65) **Prior Publication Data**

US 2023/0027837 A1 Jan. 26, 2023

### Related U.S. Application Data

- (60) Provisional application No. 63/222,926, filed on Jul. 16, 2021.

- (51) Int. Cl. H10B 51/30 (2023.01) G11C 11/22 (2006.01) H10B 51/20 (2023.01)

- (52) U.S. Cl.

### (10) Patent No.: US 11,839,086 B2

(45) **Date of Patent:**

Dec. 5, 2023

#### (58) Field of Classification Search

CPC ....... H10B 51/30; H10B 51/20; H10B 51/50; H10B 51/10; G11C 11/223;

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,213,139 A 7/1980 Rao 4,984,153 A 1/1991 Kregness et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 111799263 A \* 10/2020 JP 1998-269789 A2 10/1998 (Continued)

#### OTHER PUBLICATIONS

"PCT Search Report and Written Opinion, PCT/US2022/039473", dated Dec. 6, 2022, 14 pages.

(Continued)

Primary Examiner — Fernando Hidalgo

#### (57) ABSTRACT

Thin-film Ferroelectric field-effect transistor (FeFET) may be organized as 3-dimensional NOR memory string arrays. Each 3-dimensional NOR memory string array includes a row of active stack each including a predetermined number of active strips each provided one on top of another and each being spaced apart from another by an isolation layer. Each active strip may include a shared source layer and a shared drain layer shared by the FeFETs provided along the active strip. Data storage in the active strip is provided by ferroelectric elements that can individually electrically set into one of two polarization states. FeFETs on separate active strips may be configured for read, programming or erase operations in parallel.

#### 66 Claims, 49 Drawing Sheets

# US 11,839,086 B2 Page 2

| (50) E |                    | 1e 41             | 6 1                                                   | 0.210.225                | D2   | 12/2015          | Wanda akal                           |

|--------|--------------------|-------------------|-------------------------------------------------------|--------------------------|------|------------------|--------------------------------------|

| · /    |                    | ssification       |                                                       | 9,219,225<br>9,230,985   |      |                  | Karda et al.<br>Wu et al.            |

| CPG    | ~ ·······          |                   | 1/2273; G11C 11/2275; G11C /2259; H01L 29/78391; H01L | 9,231,206                |      |                  | Tao et al.                           |

|        |                    | 11                |                                                       | 9,263,577                |      |                  | Ramaswamy et al.                     |

| TIO    | 20                 |                   | 29/40111; H01L 29/516                                 | 9,281,044                | B2 * |                  | Ramaswamy H01L 29/78391              |

|        |                    |                   |                                                       | 9,299,580                |      |                  | Kong et al.                          |

| See    | applicati          | on file to        | r complete search history.                            | 9,337,210<br>9,362,487   |      |                  | Karda et al.<br>Inumiya et al.       |

| (50)   |                    | D. C              | C' I                                                  | 9,391,084                |      | 7/2016           |                                      |

| (56)   |                    | Referen           | ces Cited                                             | 9,412,752                |      |                  | Yeh et al.                           |

|        | II S               | DATENT            | DOCUMENTS                                             | 9,455,268                | B2   |                  | Oh et al.                            |

|        | 0.5.               | 17111111          | DOCOMENTS                                             | 9,472,560                |      |                  | Ramaswamy et al.                     |

| 5,388  | ,246 A             | 2/1995            | Kasai                                                 | 9,530,794<br>9,558,804   |      |                  | Ramaswamy et al.                     |

|        | ,808 A             |                   | Brahmbhatt                                            | 9,538,804                |      | 1/2017<br>4/2017 | Liang et al.                         |

| 5,646  | ,886 A             |                   | Brahmbhatt                                            | 9,633,944                |      | 4/2017           |                                      |

|        | ,842 A             |                   | Iwamatsu                                              | 9,698,152                | B2   | 7/2017           | Peri                                 |

|        | ,192 A<br>,776 A   | 6/1998<br>8/1998  | Ancaster et al.                                       | 9,711,529                |      |                  | Hu et al.                            |

|        | ,993 A             |                   | Kramer et al.                                         | 9,748,172                | B2   | 8/2017           | Takaki<br>Ramaswamy et al.           |

|        | ,167 A             | 6/1999            | Leedy                                                 | 9,786,684<br>9,799,761   |      |                  | Or-Bach et al.                       |

|        | ,605 A             |                   | Sano et al.                                           | 9,818,468                |      | 11/2017          |                                      |

|        | ,497 A             | 4/2000            |                                                       | 9,818,848                | B2   |                  | Sun et al.                           |

|        | ,862 A<br>,133 A   |                   | Margulis<br>Furukawa et al.                           | 9,830,969                |      |                  | Slesazeck et al.                     |

|        | ,171 A             |                   | Davies et al.                                         | 9,842,651                |      | 12/2017          | Harari                               |

|        | ,838 A             |                   | Kim et al.                                            | 9,865,680<br>9,875,784   |      |                  | Okumura et al.<br>Li et al.          |

| 6,313  | ,518 B1            |                   | Ahn et al.                                            | 9,876,018                |      |                  | Chavan et al.                        |

|        | ,046 B1            |                   | Kamiya et al.                                         | 9,892,800                |      | 2/2018           |                                      |

|        | ,508 B1            | 3/2002<br>5/2002  | Rasovaky et al.                                       | 9,911,497                |      | 3/2018           |                                      |

|        | ,744 B1<br>,053 B1 |                   | Fujiwara                                              | 9,941,299                |      |                  | Chen et al.                          |

|        | ,124 B1            |                   | Cleeves et al.                                        | 10,014,317<br>10,038,092 |      | 7/2018           | Chen et al.                          |

|        | ,365 B1            |                   | Salling                                               | 10,033,557               |      |                  | Slesazeck et al.                     |

|        | ,503 B2            | 9/2003            |                                                       | 10,056,393               |      |                  | Schroeder et al.                     |

|        | ,094 B2<br>,105 B1 | 6/2004<br>6/2004  | Chang et al.                                          | 10,074,667               |      |                  | Higashi                              |

|        | ,458 B2            |                   | Fricke et al.                                         | 10,090,036<br>10,096,364 |      | 10/2018          | Van Houdt                            |

| 6,873  | ,004 B1            |                   | Han et al.                                            | 10,030,364               |      |                  | Harari et al.                        |

|        | ,994 B2            |                   | Lee et al.                                            | 10,157,780               |      |                  | Wu et al.                            |

|        | ,703 B2<br>,350 B2 |                   | Ryu et al.<br>Walker et al.                           | 10,211,223               |      |                  | Van Houdt et al.                     |

|        | ,977 B2            |                   | Chen et al.                                           | 10,211,312               |      |                  | Van Houdt et al.                     |

|        | ,653 B2            |                   | Cheng et al.                                          | 10,217,667<br>10,249,370 |      | 4/2019           | Or-Bach et al.                       |

|        | ,308 B2            | 12/2007           |                                                       | 10,254,968               |      |                  | Gazit et al.                         |

|        | ,141 B2            |                   | Takeuchi                                              | 10,283,493               |      | 5/2019           | Nishida                              |

|        | ,980 B2<br>,002 B2 |                   | Arimoto et al.<br>Forbes et al.                       | 10,319,696               |      |                  | Nakano                               |

|        | ,963 B2            |                   | Edahiro et al.                                        | 10,355,121               |      | 2/2019           | Or-Bach et al.<br>Gupta et al.       |

|        | ,012 B2            | 3/2009            | Kuo                                                   | 10,373,956<br>10,381,370 |      |                  | Shin et al.                          |

|        | ,725 B2            | 4/2009            |                                                       | 10,381,378               |      | 8/2019           |                                      |

|        | ,348 B1            | 6/2009<br>11/2009 |                                                       | 10,395,737               | B2   | 8/2019           |                                      |

|        | ,411 B2<br>,359 B2 |                   | Boes et al.                                           | 10,403,627               |      |                  | Van Houdt et al.                     |

|        | ,145 B2            |                   | Shimizu et al.                                        | 10,418,377<br>10,424,379 |      |                  | Van Houdt et al.<br>Slesazeck et al. |

|        | ,295 B2            |                   | Park et al.                                           | 10,424,579               |      |                  | Herner et al.                        |

|        | ,614 B2            |                   | Kang et al.                                           | 10,438,645               |      |                  | Muell et al.                         |

|        | ,009 B2<br>,521 B1 |                   | Wilson et al.                                         | 10,460,788               |      | 10/2019          |                                      |

|        | ,321 B1<br>,418 B2 |                   | Or-Bach et al.<br>Carman                              | 10,475,812               |      | 11/2019          |                                      |

|        | ,396 B2            |                   | Sinha et al.                                          | 10,510,773<br>10,600,808 |      |                  | Ramaswamy et al.<br>Schröder et al.  |

| 8,237  | ,213 B2            | 8/2012            | Liu                                                   | 10,608,008               |      |                  | Harari et al.                        |

|        | ,504 B2            | 8/2012            |                                                       | 10,608,011               |      |                  | Harari et al.                        |

|        | ,183 B2<br>,823 B2 | 10/2012           | Lerner<br>Boescke                                     | 10,622,051               |      |                  | Mueller et al.                       |

|        | ,823 B2<br>,482 B2 |                   | Kim et al.                                            | 10,622,377<br>10,636,471 |      |                  | Harari et al.                        |

| 8,395  | ,942 B2            |                   | Samachisa et al.                                      | 10,650,892               |      | 5/2020           | Ramaswamy et al.                     |

|        | ,618 B2            |                   | Cooney et al.                                         | 10,651,153               |      |                  | Fastow et al.                        |

|        | ,114 B2<br>,612 B2 | 1/2014            | Lue<br>Choi et al.                                    | 10,651,182               | B2   | 5/2020           | Morris et al.                        |

|        | ,612 B2<br>,436 B2 |                   | Scalia et al.                                         | 10,651,196               |      |                  | Sharangpani et al.                   |

|        | ,473 B2            |                   | Shim et al.                                           | 10,692,837               |      |                  | Nguyen et al.                        |

| 8,848  | ,425 B2            | 9/2014            | Schloss                                               | 10,692,874<br>10,700,093 |      |                  | Harari et al.<br>Kalitsov et al.     |

|        | ,278 B2            |                   | Alsmeier et al.                                       | 10,700,093               |      | 7/2020           |                                      |

|        | ,801 B2<br>,802 B2 |                   | Sandhu et al.<br>Mueller                              | 10,720,437               |      | 11/2020          |                                      |

|        | ,802 B2<br>,310 B2 |                   | Li et al.                                             | 10,872,905               | B2   | 12/2020          | Muel                                 |

| 9,158  | ,622 B2            | 10/2015           | Lee et al.                                            | 10,879,269               |      |                  | Zhang et al.                         |

|        | ,293 B2            |                   | Wang et al.                                           | 10,896,711               |      |                  | Lee et al.                           |

| 9,202  | ,694 B2            | 12/2015           | Konevecki et al.                                      | 10,937,482               | B2   | 5/2021           | Sharma et al.                        |

# US 11,839,086 B2 Page 3

| (56)                         | Referen | ces Cited         | 2013/0031325                          |                              |    | Nakamoto et al.  |                                        |

|------------------------------|---------|-------------------|---------------------------------------|------------------------------|----|------------------|----------------------------------------|

|                              | TTO 1   | DATENT            | DOCUMENTS                             | 2013/0126957<br>2013/0256780 |    |                  | Higashitani et al.                     |

|                              | U.S.    | PATENT            | DOCUMENTS                             | 2014/0015036                 |    |                  | Kai et al.<br>Fursin et al.            |

| 10,950,616                   | B2      | 3/2021            | Harari et al.                         | 2014/0040698                 |    |                  | Loh et al.                             |

| 11,043,280                   |         |                   | Prakash et al.                        | 2014/0070289                 | A1 | 3/2014           | Tanaka et al.                          |

| 11,171,157                   |         |                   | Lai et al.                            | 2014/0070290                 |    |                  | Inumiya et al.                         |

| 11,411,025                   |         |                   | Lai et al.                            | 2014/0075135                 |    |                  | Choi et al.<br>Dunga et al.            |

| 2001/0030340                 |         |                   | Fujiwara                              | 2014/0112075<br>2014/0117366 |    | 5/2014           |                                        |

| 2001/0053092<br>2002/0012271 |         | 1/2001            | Kosaka et al.                         | 2014/0151774                 |    | 6/2014           |                                        |

| 2002/0012271                 |         |                   | Lee et al.                            | 2014/0173017                 |    |                  | Takagi et al.                          |

| 2002/0051378                 |         |                   | Ohsawa                                | 2014/0213032                 |    |                  | Kai et al.                             |

| 2002/0193484                 |         | 12/2002           |                                       | 2014/0229131                 |    |                  | Cohen et al.<br>Karda et al.           |

| 2003/0038318                 |         | 2/2003            |                                       | 2014/0247674<br>2014/0328128 |    |                  | Louie et al.                           |

| 2004/0214387<br>2004/0246807 |         | 10/2004           | Madurawe et al.                       | 2014/0340952                 |    |                  | Ramaswamy et al.                       |

| 2004/0262681                 |         |                   | Masuoka et al.                        | 2014/0355328                 |    |                  | Muller et al.                          |

| 2004/0262772                 | A1      | 12/2004           | Ramanathan et al.                     | 2015/0054507                 |    |                  | Gulaka et al.                          |

| 2004/0264247                 |         | 12/2004           |                                       | 2015/0098272<br>2015/0113214 |    |                  | Kasolra et al.<br>Sutardja             |

| 2005/0128815                 |         |                   | Ishikawa et al.                       | 2015/0155876                 |    |                  | Jayasena et al.                        |

| 2005/0236625<br>2005/0280061 |         | 10/2005           | Schuele et al.                        | 2015/0194440                 |    |                  | Noh et al.                             |

| 2006/0001083                 |         |                   | Bhattacharyya                         | 2015/0220463                 |    |                  | Fluman et al.                          |

| 2006/0080457                 |         |                   | Hiramatsu et al.                      | 2015/0249143                 |    | 9/2015           |                                        |

| 2006/0155921                 |         |                   | Gorobets et al.                       | 2015/0263005<br>2015/0340371 |    | 9/2015           | Zhao et al.                            |

| 2006/0212651                 |         | 9/2006<br>11/2006 | Ashmore                               | 2015/0340371                 |    |                  | Chen et al.                            |

| 2006/0261404<br>2007/0012987 |         |                   | McTeer                                | 2016/0013156                 |    |                  | Zhai et al.                            |

| 2007/0023817                 |         | 2/2007            |                                       | 2016/0019951                 | Al | 1/2016           | Park et al.                            |

| 2007/0045711                 |         |                   | Bhattacharyya                         | 2016/0035711                 |    | 2/2016           |                                        |

| 2007/0134876                 |         |                   | Lai et al.                            | 2016/0086970                 |    | 3/2016           |                                        |

| 2007/0192518                 |         |                   | Rupanagunta et al.                    | 2016/0118404<br>2016/0141294 |    | 4/2016<br>5/2016 | Peri et al.                            |

| 2008/0022026<br>2008/0054346 |         |                   | Yang et al.<br>Saitoh et al.          | 2016/0225860                 |    |                  | Karda et al.                           |

| 2008/0034340                 |         |                   | Lee et al.                            | 2016/0276360                 |    |                  | Doda et al.                            |

| 2008/0173930                 |         |                   | Watanabe                              | 2016/0300724                 |    |                  | Levy et al.                            |

| 2008/0178794                 |         |                   | Cho et al.                            | 2016/0314042                 |    | 10/2016          |                                        |

| 2008/0212358                 | A1*     | 9/2008            | Mitsui H01L 21/76849                  | 2016/0321002<br>2016/0358934 |    |                  | Jung et al.<br>Lin et al.              |

| 2009/0220912                 | A 1     | 10/2009           | Maafumi et al                         | 2017/0053906                 |    |                  | Or-Bach et al.                         |

| 2008/0239812<br>2008/0266960 |         | 10/2008           | Naofumi et al.                        | 2017/0062456                 |    |                  | Sugino et al.                          |

| 2008/0291723                 |         |                   | Wang et al.                           | 2017/0092370                 |    | 3/2017           |                                        |

| 2008/0301359                 |         | 12/2008           |                                       | 2017/0092371                 |    | 3/2017           |                                        |

| 2009/0057722                 |         |                   | Masuoka et al.                        | 2017/0140807<br>2017/0148517 |    | 5/2017           | Sun et al.                             |

| 2009/0140318                 |         | 6/2009            | e e e e e e e e e e e e e e e e e e e | 2017/0148810                 |    |                  | Kai et al.                             |

| 2009/0157946<br>2009/0237996 |         | 6/2009<br>9/2009  | Kirsch et al.                         | 2017/0194341                 | A1 |                  | Yamada                                 |

| 2009/0268519                 |         | 10/2009           |                                       | 2017/0213731                 |    |                  | Yoon et al.                            |

| 2009/0279360                 | A1      | 11/2009           | Peter et al.                          | 2017/0213821<br>2017/0358594 |    |                  | Or-Bach et al.<br>Lu et al.            |

| 2009/0290442                 |         | 11/2009           |                                       | 2018/0006044                 |    |                  | Chavan et al.                          |

| 2009/0316487                 |         |                   | Lee et al.                            | 2018/0095127                 |    |                  | Pappu et al.                           |

| 2010/0013001<br>2010/0121994 |         |                   | Cho et al.<br>Kim et al.              | 2018/0108416                 |    | 4/2018           | Harari                                 |

| 2010/0124116                 |         |                   | Takashi et al.                        | 2018/0151419                 | A1 |                  | Wu et al.                              |

| 2010/0128509                 | A1      |                   | Kim et al.                            | 2018/0261613                 |    |                  | Ariyoshi et al.                        |

| 2010/0148215                 |         |                   | Schulze et al.                        | 2018/0269229<br>2018/0286918 |    |                  | Or-Bach et al.<br>Bandyopadhyay et al. |

| 2010/0207185                 |         |                   | Lee et al.<br>Awaya et al.            | 2018/0330791                 |    |                  | Li et al.                              |

| 2010/0219392<br>2010/0254191 |         |                   | Son et al.                            | 2018/0331042                 |    |                  | Manusharow et al.                      |

| 2010/0327413                 |         |                   | Lee et al.                            | 2018/0342455                 |    |                  | Nosho et al.                           |

| 2011/0003418                 | A1      |                   | Sakata et al.                         | 2018/0342544<br>2018/0366471 |    |                  | Lee et al.<br>Harari et al.            |

| 2011/0044113                 |         | 2/2011            |                                       | 2018/0366485                 |    | 12/2018          |                                        |

| 2011/0047325<br>2011/0115011 |         |                   | Mishima<br>Masuoka et al.             | 2018/0366489                 |    |                  | Harari et al.                          |

| 2011/0113011                 |         |                   | Jones et al.                          | 2018/0374929                 | A1 | 12/2018          | Yoo                                    |

| 2011/0143519                 |         | 6/2011            |                                       | 2019/0006009                 |    | 1/2019           |                                        |

| 2011/0170266                 |         |                   | Haensh et al.                         | 2019/0006015<br>2019/0019564 |    |                  | Norman et al.<br>Li et al.             |

| 2011/0208905                 |         |                   | Shaeffer et al.                       | 2019/0019304                 |    |                  | Herner et al.                          |

| 2011/0298013<br>2011/0310683 |         |                   | Hwang et al.<br>Gorobets              | 2019/0007327                 |    |                  | Or-Bach et al.                         |

| 2011/0310083                 |         | 3/2012            |                                       | 2019/0157296                 |    |                  | Harari et al.                          |

| 2012/0146126                 |         |                   | Lai et al.                            | 2019/0180821                 | A1 | 6/2019           | Harari                                 |

| 2012/0182801                 | A1      | 7/2012            | Lue                                   | 2019/0206890                 |    |                  | Harari et al.                          |

| 2012/0208347                 |         |                   | Hiwang et al.                         | 2019/0214077                 |    |                  | Oh et al.                              |

| 2012/0223380                 |         |                   | Lee et al.                            | 2019/0237470                 |    |                  | Mine et al.                            |

| 2012/0243314<br>2012/0307568 |         |                   | Takashi<br>Banna et al.               | 2019/0238134<br>2019/0244971 |    | 8/2019<br>8/2019 | Lee et al.                             |

| 2012/0307308                 |         | 12/2012           |                                       | 2019/0259769                 |    |                  | Karda et al.                           |

| 2012/052//17                 |         | 12,2012           |                                       | 2017, 0207 107               |    | 5, 2017          |                                        |

#### (56)References Cited U.S. PATENT DOCUMENTS 2019/0303042 A1 10/2019 Kim et al 2019/0304988 A1 10/2019 Dong et al. pp. 235-248. 2019/0325945 A1 10/2019 Linus 2019/0325964 A1 10/2019 Harari 2019/0319044 A1 11/2019 Harari 2019/0348424 A1 11/2019 Karda et al. 2019/0355747 A1 11/2019 Herner et al. 2019/0370117 A1 12/2019 Fruchtman et al. 2020/0020718 A1 1/2020 Harari et al. 2020/0051990 A1 2/2020 Harari et al. 2020/0063263 A1 2/2020 Technology, Jun. 2021, 2 p. Yang et al. 2020/0065647 A1 2/2020 Mulaosmanovic et al. 2020/0075631 A1 3/2020 Dong 2020/0098738 A1 3/2020 Herner et al. 2020/0098779 A1 3/2020 Cernea et al. 3060589., Apr. 2021, pp. 617-620. 2020/0098881 A1\* 3/2020 Vellianitis ....... H01L 29/66628 2020/0176468 A1 6/2020 Herner et al. 2020/0201718 A1 6/2020 Richter et al. 2020/0203378 A1 6/2020 Harari et al. 2020/0219572 A1 7/2020 Harari Papers, 2010, pp. 131-132. 2020/0243486 A1 7/2020 Ouader et al. 2020/0258897 A1 8/2020 Yan et al. Hoffmann ...... H10B 53/30 2020/0350324 A1\* 11/2020 2020/0357453 A1 11/2020 Slesazeck et al. 2020/0357455 A1 11/2020 Noack et al. 2020/0357470 A1 11/2020 Noack 2020/0357822 A1\* 11/2020 Chen ...... G11C 11/223 2020/0365609 A1 11/2020 Harari 2020/0388313 A1 12/2020 Cho et al. 2020/0388711 A1 12/2020 Doyle et al. 2020/0403002 A1 12/2020 Harari 2020/0411533 A1 12/2020 Alsmeier et al. 2021/0005238 A1 Mueller 1/2021 pages. 2021/0013224 A1 1/2021 Purayath et al. 2021/0020659 A1 1/2021 Chen 2021/0066502 A1 3/2021 Karda et al. 2021/0074725 A1 3/2021 Lue 2021/0074726 A1 3/2021 Lue 2021/0111179 A1 4/2021 Shivaraman et al. 2021/0175251 A1 6/2021 Zhang et al. pages 2021/0247910 A1 8/2021 Kim et al. 2021/0248094 A1 8/2021 Norman et al. 2021/0265308 A1 8/2021 Norman et al. 2021/0375933 A1\* 12/2021 Lu ...... H01L 29/40111 (2015), Feb. 21, 2015, pp. N29-N35. 2022/0028876 A1 1/2022 Purayath et al. 2022/0028886 A1 1/2022 Pur et al. 2022/0139933 A1\* 5/2022 Noack ...... G11C 11/221 2022/0231049 A1\* $7/2022 \quad Lin \quad .... \qquad H10B \; 51/20$ 10.8.1-10.8.4. 2022/0246777 A1\* 8/2022 Kim ...... B32B 17/10 2022/0254390 A1\* 8/2022 Gans ...... G11C 5/04 2022/0351776 A1\* 11/2022 Nam ...... G11C 11/223 2022/0384459 A1 12/2022 Lu et al. 2022/0393031 A1\* Ando ...... H01L 29/66484 12/2022 4199-4205. 2023/0052477 A1\* 2/2023 Ha ...... H01L 29/0847 FOREIGN PATENT DOCUMENTS 2000-243972 A2 9/2000 JP JP 2000339978 A 12/2000 2004079606 A 3/2004 JP JP 2006099827 A1 4/2006 2009206451 A1 9/2009 JР 2010108522 A1 5/2010 JΡ 2010251572 A 11/2010 JР 2011028540 A1 2/2011

JΡ

KR

KR

KR

WO

WO

WO

2012-150876 A2

20120085591 A

20120085591 A1

2015025357 A1

2018236937 A1

2019066948 A1

20120085603 A

8/2012

8/2012

8/2012

8/2012

2/2015

12/2018

4/2019

#### OTHER PUBLICATIONS

Lee, Sang Yeol, "Comprehensive Review on Amorphous Oxide Semiconductor Thin Film Transistor", Trans. Electr. Electron. Mater. 21, https://doi.org/10.1007/s42341-020-00197-w, Mar. 28, 2020,

Lee, Chea-Young, et al., "Etching Characteristics and Changes in Surface Properties of IGZO Thin Films by O2 Addition in CF4/Ar Plasma", Coatings. 2021, 11(8):906. https://doi.org/10.3390/ coatings11080906, Jul. 29, 2021.

Liao, P.J., et al., "Characterization of Fatigue and Its Recovery Behavior in Ferroelectric HfZrO", 2021 Symposium on VLSI

Liao, C.Y., et al., "Multibit Ferroelectric FET Based on Nonidentical Double HfZrO2 for High-Density Nonvolatile Memory", IEEE Electron Device Letters, vol. 42, No. 4, doi: 10.1109/LED.2021.

Lue, H.T., et al., "A Highly Scalable 8-Layer 3D Vertical-gate  $\{VG)$ TFT NANO Flash Using Junction-Free Buried Channel BE-SONOS Device", Symposium on VLSI: Tech. Dig. Of Technical

Materano, Monica, et al., "Interplay between oxygen defects and dopants: effect on structure and performance of HfO2-based ferroelectrics", Inorg. Chem. Front. (8), Apr. 9, 2021, pp. 2650-2672. Mo, Fei, et al., "Experimental Demonstration of Ferroelectric HfO2 FET with Ultrathin-body IGZO for High-Density and Low-Power Memory Application", 2019 Symposium on VLSI Technology, 3, doi: 10.23919/VLSIT.2019.8776553., 2019, pp. T42-T4.

Mo, Fei, et al., "Experimental Demonstration of Ferroelectric HfO2 FET with Ultrathin-body IGZO for High-Density and Low-Power Memory Application", Symposium on VLSI Technology, 2019, pp. T42-T43, doi: 10.23919/VLSIT.2019.8776553., Jul. 13, 2020, 7

Mo, Fei, et al., "Low-Voltage Operating Ferroelectric FET with Ultrathin IGZO Channel for High-Density Memory Application", IEEE Journal of the Electron Devices Society, vol. 8, doi: 10.1109/ JEDS.2020.3008789., Jul. 13, 2020, pp. 717-723.

Mueller, S., et al., "Development Status of Gate-First FeFET Technology", 2021 Symposium on VLSI Technology, Jun. 2021, 2

Mueller, J., et al., "Ferroelectric Hafnium Oxide Based Materials and Devices: Assessment of Current Status and Future Prospects", ECS Journal of Solid State Science and Technology, 4 (5) N30-N35

Mueller, J., et al., "Ferroelectric hafnium oxide: A CMOScompatible and highly scalable approach to future ferroelectric memories", IEEE International Electron Devices Meeting, Washington, DC, USA, doi: 10.1109/IEDM.2013.6724605., 2013, pp.

Mueller, Stephen, et al., "From MFM Capacitors Toward Ferroelectric Transistors: Endurance and Disturb Characteristics of HfO2-Based FeFET Devices", IEEE Transactions on Electron Devices, vol. 60, No. 12, doi: 10.1109/TED.2013.2283465., Dec. 2013, pp.

Müller, J., et al., "Ferroelectric hafnium oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories", 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, doi: 10.1109/IEDM.2013.6724605., 2013, pp. 10.8.1-10.

Nguyen, Manh-Cuong, et al., "Wakeup-Free and Endurance-Robust Ferroelectric Field-Effect Transistor Memory Using High Pressure Annealing", IEEE Electron Device Letters, vol. 42, No. 9, doi: 10.1109/LED.2021.3096248., Sep. 2021, pp. 1295-1298.

On, Nuri, et al., "Boosting carrier mobility and stability in indiumzinc-tin oxide thin-film transistors through controlled crystallization", Sci Rep 10, 18868, https://doi.org/10.1038/s41598-020-76046w, 2020, 16 pages.

Onuki, Tatsuya, et al., "Embedded memory and ARM Cortex-MO core using 60-nm C-axis aligned crystalline indium-gallium-zinc oxide FET integrated with 65-nm Si CMOS", IEEE Journal of Solid-State Circuits, vol. 52, No. 4,, Apr. 2017, pp. 925-932.

#### (56) References Cited

#### OTHER PUBLICATIONS

Park, Goon-Ho, et al., "Electrical Characteristics of SiO2/High-k Dielectric Stacked Tunnel Barriers for Nonvolatile Memory Applications", Journal of the Korean Physical Society, vol. 55, No. 1, Jul. 2009, pp. 116-119.

Park, Min Hyuk, et al., "Review of defect chemistry in fluorite-structure ferroelectrics for future electronic devices", J. Mater. Chem. C, vol. 8, No. 31 10526-10550, Jun. 9, 2020., Aug. 21, 2020, pp. 10526-10550.

Rios, Rafael, et al., "A Physically Based Compact Model for IGZO Transistors", IEEE Transactions on Electron Devices, vol. 68, No. 4, doi: 10.1109/TED.2021.3059387., Apr. 2021, pp. 1664-1669. Rzehak, Volker, "Low-Power FRAM Microcontrollers and Their Applications", Texas Instruments White Paper, SLAA502, Jul.

2019, 7 pages.

Saitoh, Masumi, et al., "HfO2-based FeFET and FTJ for Ferroelectric-Memory Centric 3D LSI towards Low-Power and High-Density Storage and AI Applications", 2020 IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553.2020. 9372106., 2020, pp. 18.1.1-18.1.4.

Saitoh, Masumi, et al., "HfO2-based FeFET and FTJ for Ferroelectric-Memory Centric 3D LSI towards Low-Power and High-Density Storage and AI Applications", IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553.2020.9372106., 2020, pp. 18.1.1-18.1.4.

Salahuddin, Sayeef, et al., "FeFETs for Near-Memory and In-Memory Compute", 2021 IEEE International Electron Devices Meeting (IEDM), Department of Electrical Engineering and Computer Sciences, Dec. 2021, 4 pages.

Sharma, Abhishek A., et al., "High Speed Memory Operation in Channel-Last, Back-gated Ferroelectric Transistors", IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553. 2020.9371940., 2020, pp. 18.5.1-18.5.4.

Sheng, Jiazhen, et al., "Review Article: Atomic layer deposition for oxide semiconductor thin film transistors: Advances in research and development", J. Vac. Sci. Technol. A 36, 060801, https://doi.org/10.1116/1.5047237., Nov. 2, 2018, 14 pages.

Si, Mengwei, et al., "Why In2O3 Can Make 0.7 nm Atomic Layer Thin Transistors?", https://arxiv.org/ftp/arxiv/papers/2012/2012. 12433.pdf., 2012, 26 pages.

Si, Mengwei, et al., "Why In2O3 Can Make 0.7 nm Atomic Layer Thin Transistors?", available at https://arxiv.org/ftp/arxiv/papers/2012/2012.12433.pdf, School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907, United States, 2012, pp. 1-26.

Su, Nai-Chao, et al., "A Nonvolatile InGaZnO Charge-Trapping-Engineered Flash Memory With Good Retention Characteristics", IEEE Electron Device Letters, vol. 31, No. 3, Mar. 2010, pp. 201-203.

Sun, Chen, "First Demonstration of BEOL-Compatible Ferroelectric TCAM Featuring a-IGZO Fe-TFTs with Large Memory Window of 2.9 V, Scaled Channel Length of 40 nm, and High Endurance of 108 Cycles", 2021 Symposium on VLSI Technology Digest of Technical Papers, Kyoto, doi: 978-4-86348-779-6., Jun. 2021, 2 pages.

Tan, Ava J., et al., "A Nitrided Interfacial Oxide for Interface State Improvement in Hafnium Zirconium Oxide-Based Ferroelectric Transistor Technology", IEEE Electron Device Letters, vol. 39, No. 1, doi: 10.1109/LED.2017.2772791., Jan. 2018, pp. 95-98.

Tan, Ava J., et al., "Experimental Demonstration of a Ferroelectric HfO2-Based Content Addressable Memory Cell", IEEE Electron Device Letters, vol. 41, No. 2, doi: 10.1109/LED.2019.2963300., Feb. 2020, pp. 240-243.

Tan, Ava Jiang, et al., "Ferroelectric HfO2 Memory Transistors with High-κ Interfacial Layer and Write Endurance Exceeding 1010 Cycles", arXiv:2103.08806 [physics.app-ph], available at https://arxiv.org/abs/2103.08806., Mar. 16, 2021.

Tan, Ava J., et al., "Hot Electrons as the Dominant Source of Degradation for Sub-5nm HZO FeFETs", IEEE Symposium on

VLSI Technology, Honolulu, HI, USA, doi: 10.1109/VLSITechnology18217.2020.9265067., 2020, pp. 1-2.

Tan, Yan-Ny, et al., "Over-Erase Phenomenon in SONOS-Type Flash Memory and its Minimization Using a Hafnium Oxide Charge Storage Layer", IEEE Transactions on Electron Devices, vol. 51, No. 7, Jul. 2004, pp. 1143-1147.

Tanaka, T., et al., "A 768 GB 3b/cell 3D-Floaling-Gate NANO

Tanaka, T., et al., "A 768 GB 3b/cell 3D-Floaling-Gate NANO Flash Memory", Digest of Technical Papers, the 2016 EEE International Solid-Slate Circuits Conference, 2016, pp. 142-144.

Van Houdt, Jan, "The 3D FeFET: contender for 3D-NAND Flash memory and machine learning", available at https://www.imec-int.com/en/imec-magazine/imec-magazine-october-2017/the-vertical-ferroelectric-fet-a-new-contender-for-3d-nand-flash-memory-and-machine-learning, Sep. 30, 2019, 8 pages.

Wann, H.C., et al., "High-Endurance Ultra-Thin Tunnel Oxide in Monos Device Structure for Dynamic Memory Application", IEEE Electron Device letters, vol. 16, No. 11, Nov. 1995, pp. 491-493. Yang, Jin, et al., "Highly Optimized Complementary Inverters Based on p-SnO and n-InGaZnO With High Uniformity", IEEE Electron Device Letters, vol. 39, No. 4, doi: 10.1109/LED.2018. 2809796., Apr. 2018, pp. 516-519.

Wu, Jixuan, et al., "A Monolithic 3D Integration of RRAM Array with Oxide Semiconductor FET for In-Memory Computing in Quantized Neural Network AI Applications", 2020 IEEE Symposium on VLSI Technology Digest of Technical Papers, Honolulu, HI, USA, Jun. 2020, 4 pages.

"EP Extended Search Report EP168690149.3", dated Oct. 18, 2019. "European Search Report, EP 16852238.1", dated Mar. 28, 2019. "European Search Report, EP17844550.8", dated Aug. 12, 2020, 11 pages.

"Imec Demonstrates Capacitor-less IGZO-Based DRAM Cell With >400s Retention Time", IMEC, Press release, available at https://www.imec-int.com/en/press/imec-demonstrates-capacitor-less-igzo-based-dram-cell-400s-retention-time, Dec. 15, 2020, 15 pages.

"Invitation to Pay Additional Fees (PCT/ISA/206), PCT/US2020/015710", dated Mar. 20, 2020, 2 pages.

"Invitation to Pay Additional Fees, PCT/US2019/065256", dated Feb. 13, 2020, 2 pages.

"Notification of Reasons for Refusal, Japanese Patent Application 2018-527740", (English translation), dated Nov. 4, 2020, 8 pages. "Partial European Search Report EP 16869049.3", dated Jul. 1, 2019, pp. 1-12.

"PCT Search Report and Written Opinion, PCT/US2018/038373", dated Sep. 10, 2018.

"PCT Search Report and Written Opinion, PCT/US2018/067338", dated May 8, 2019.

"PCT Search Report and Written Opinion, PCT/US2019/014319", dated Apr. 15, 2019.

"PCT Search Report and Written Opinion, PCT/US2019/041678", dated Oct. 9, 2019.

"PCT Search Report and Written Opinion, PCT/US2019/052164", dated Feb. 27, 2020.

"PCT Search Report and Written Opinion, PCT/US2019/052446", dated Dec. 11, 2019.

"PCT Search Report and Written Opinion, PCT/US2019/065256", dated Apr. 14, 2020.

"PCT Search Report and Written Opinion, PCT/US2020/015710", dated Jun. 9, 2020.

"PCT Search Report and Written Opinion, PCT/US2020/017494", dated Jul. 20, 2020, 13 pages.

"PCT Search Report and Written Opinion, PCT/US2020/065374", dated Mar. 15, 2021, 17 pages.

"PCT Search Report and Written Opinion, PCT/US2020/065670", dated Apr. 5, 2021, 12 pages.

"PCT Search Report and Written Opinion, PCT/US2021/016964", dated Jun. 15, 2021, 19 pages.

"PCT Search Report and Written Opinion, PCT/US2021/025722", dated Jun. 15, 2021, 10 pages.

"PCT Search Report and Written Opinion, PCT/US2021/042607", dated Nov. 4, 2021, 17 pages.

"PCT Search Report and Written Opinion, PCT/US2021/064844", dated Mar. 8, 2022, 15 paged.

#### (56) References Cited

#### OTHER PUBLICATIONS

"PCT Search Report and Written Opinion, PCT/US2021/42620", dated Oct. 28, 2021, 18 pages.

"PCT Search Report and Written Opinion, PCT/US2022/016729", Applicant: SunRise Memory Corporation, dated May 17, 2022, 20 pages.

Ahn, Min-Ju, et al., "Transparent multi-level-cell nonvolatile memory with dual-gate amorphous indiumgallium-zinc oxide thin-film transistors", Appl. Phys. Lett. 109, 252106; doi: 10.1063/1. 4972961., 2016, 6 pages.

Alessandri, Cristobal, et al., "Monte Carlo Simulation of Switching Dynamics in Polycrystalline Ferroelectric Capacitors", IEEE Transactions on Electron Devices, vol. 66, No. 8, doi: 10.1109/TED. 2019.2922268., Aug. 2019, pp. 3527-3534.

Ali, T., et al., "A Multilevel FeFET Memory Device based on Laminated HSO and HZO Ferroelectric Layers for High-Density Storage", IEEE International Electron Devices Meeting (IEDM), 2019, doi: 10.1109/ EDM19573.2019.8993642., Dec. 2019, pp. 28.7.1-28.7.4.

Ali, T., et al., "High Endurance Ferroelectric Hafnium Oxide-Based FeFET Memory Without Retention Penalty,", IEEE Transactions on Electron Devices, vol. 65, No. 9, doi: 10.1109/TED.2018.2856818.—paper cited in Bae (Berkeley) paper, Sep. 2018, pp. 3769-3774. Bae, Jong-Ho, et al., "Highly Scaled, High Endurance, Q-Gate,

Nanowire Ferroelectric FET Memory Transistors", IEEE Electron Device Letters, vol. 41, No. 11, doi: 10.1109/LED.2020.3028339.— Sayeef-Berkeley paper on FeFET memory, Nov. 2020, pp. 1637-1640.

Beyer, Sven, et al., "FeFET: A versatile CMOS compatible device with game-changing potential", IEEE International Memory Workshop (IMW), doi: 10.1109/IMW48823.2020.9108150., 2020, pp. 1-4.

Böscke, T.S., et al., "Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors", 2011 International Electron Devices Meeting, Washington, DC, USA, doi: 10.1109/IEDM.2011.6131606., 2011, pp. 24.5.1-24.5.4.

Chang, Sou-Chi, et al., "Anti-ferroelectric HfxZr1-xO2 Capacitors for High-density 3-D Embedded-DRAM", IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553.2020. 9372011., 2020, pp. 28.1.1-28.1.4.

Cho, Min Hoe, et al., "Achieving a Low-Voltage, High-Mobility IGZO Transistor through an ALD-Derived Bilayer Channel and a Hafnia-Based Gate Dielectric Stack", ACS Applied Materials & Interfaces, Apr. 1, 2021, 13 (14), DOI: 10.1021/acsami.0c22677, 2021, pp. 16628-16640.

Cho, Min Hoe, et al., "Comparative Study on Performance of IGZO Transistors With Sputtered and Atomic Layer Deposited Channel Layer", IEEE Transactions on Electron Devices, vol. 66, No. 4, doi: 10.1109/TED.2019.2899586., Apr. 2019, pp. 1783-1788.

Choi, Seonjun, et al., "A novel three-dimensional NAND flash structure for improving the erase performance", IEICE Electronics Express, 2019 vol. 16 Issue 3, 2019, 6 pages.

De, Sourav, et al., "Ultra-Low Power Robust 3bit/cell Hf0.5Zr0. 5O2 Ferroelectric FinFET with High Endurance for Advanced Computing-In-Memory Technology", 2021 Symposium on VLSI Technology, Kyoto, Japan, Jun. 13-19, 2021, Jun. 2021, 2 pages. Dünkel, "A FeFET based super-low-power ultra-fast embedded NVM technology for 22nm FDSOI and beyond", IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2017, doi: 10.1109/IEDM.2017.8268425., 2017, pp. 19.7.1-19.7.4. Dutta, Sourav, et al., "Logic Compatible High-Performance Ferroelectric Transistor Memory", available at https://arxiv.org/abs/2105.11078, Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, USA, May 24, 2021, 28 pages. Florent, K., "First demonstration of vertically stacked ferroelectric AI doped HfO2 devices for NAND applications", Symposium on VLSI Technology, doi: 10.23919/VLSIT.2017.7998162., 2017, pp.

Florent, K., et al., "Vertical Ferroelectric HfO2 FET based on 3-D NAND Architecture: Towards Dense Low-Power Memory", IEEE

International Electron Devices Meeting (IEDM), San Francisco, CA, 2018, doi: 10.1109/IEDM.2018.8614710., 2018, pp. 2.5.1-2.5.

Hendy, Ian , "The Role of Increased Semiconductor Mobility—an IGZO Case Study", Display Daily, available at https://www.displaydaily.com/article/display-daily/the-role-of-increased-semiconductor-mobility-an-igzo-case-study, Apr. 2021, 11 pages. Hou, S. Y., et al., "Wafer-Leval Integration of an Advanced Logic-Memory System Through the Second-Generation CoWoS Technology", IEEE Transactions on Electron Devices, vol. 64, No. 10, Oct. 2017, 4071-4077.

Hsain, Hanan Alexandra, et al., "Many routes to ferroelectric HfO2: A review of current deposition methods", J. Vac. Sci. Technol. A 40, 010803 (2022), published Dec. 1, 2021., Dec. 1, 2021, pp. 010803-1-010803-36.

Jeewandara, Thamarasee , et al., "High-speed 3-D memory with ferroelectric NAND flash memory", available at https://techxplore.com/news/2021-01-high-speed-d-memoryferroelectric-nand.html, Jan. 26, 2021, 5 pages.

Kawai, H., et al., "Design Principle of Channel Material for Oxide-Semiconductor Field-Effect Transistor with High Thermal Stability and High On-current by Fluorine Doping", IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553. 2020.9372121., 2020, pp. 22.2.1-22.2.4.

Kim, Min-Kyu, et al., "CMOS-compatible ferroelectric NAND flash memory for high-density, low-power, and high-speed three-dimensional memory", Science Advances, vol. 7, No. 3, eabe 1341, DOI: 10.1126/sciadv.abe1341. (Replacement of polysilicon channel material—use IZO for channel), Jan. 13, 2021, 10.

Kim, Taeho, et al., "Effects of high pressure nitrogen annealing on ferroelectric Hf0.5Zr0.5O2 films", Appl. Phys. Lett. 112, 092906 https://doi.org/10.1063/1.5003369, Mar. 2, 2018, 5 pages.

Kim, N., et al., "Multi-layered Vertical gate NANO Flash Overcoming Stacking Limit for Terabit Density Storage", Symposium on VLSI Tech. Dig. of Technical Papers, 2009, pp. 188-189.

Kunitake, Hitoshi, et al., "High-temperature Electrical Characteristics of 60nm CAAC-IGZO FET: Comparison with Si FET", International Conference on Solid State Devices and Materials, https://doi.org/10.7567/SSDM.2018.N-3-04, Sep. 2018, pp. 787-788

Chen, Chi-Yu, et al., "FeFET Memory Featuring Large Memory Window and Robust Endurance of Long-Pulse Cycling by Interface Engineering using High-k AION", 2020 IEEE Symposium on VLSI Technology, doi: 10.1109/VLSITechnology18217.2020.9265103., 2020, pp. 1-2.

Kim, Hyungwoo, et al., "Two-step deposition of TiN capping electrodes to prevent degradation of ferroelectric properties in an in-situ crystallized TiN/Hf0.5Zr0.5O2/TIN device", Nano Express 3 015004., 2022, 12 pages.

McBriarty, Martin E., et al., "Crystal Phase Distribution and Ferroelectricity in Ultrathin HfO2—ZrO2 Bilayers", Phys. Status Solidi B, 257: 1900285. https://doi.org/10.1002/pssb.201900285, Aug. 21, 2019, pp. 1-25.

Mittmann, T., et al., "Impact of Oxygen Vacancy Content in Ferroelectric HZO films on the Device Performance", 2020 IEEE International Electron Devices Meeting (IEDM), doi: 10.1109/IEDM13553.2020.9372097., 2020, pp. 18.4.1-18.4.4.

Onaya, Takashi, et al., "Improvement in ferroelectricity of HfxZr1—xO2 thin films using top- and bottom-ZrO2 nucleation layers", APL Materials 7, 061107; https://doi.org/10.1063/1.5096626, 2019, pp. 1.8

Sato, Yuta, et al., "Source/Drain Contact Engineering of InGaZnO Channel BEOL Transistor for Low Contact Resistance and Suppressing Channel Shortening Effect,", 20th International Workshop on Junction Technology (IWJT), doi: 10.23919/IWJT52818.2021. 9609366., 2021, 3 pages.

Wang, Chin-I, et al., "Atomic layer deposited TIN capping layer for sub-10 nm ferroelectric Hf0.5Zr0.5O2 with large remnant polarization and low thermal budget", Applied Surface Science, vol. 570, 2021, 151152, ISSN 0169-4332, https://doi.org/10.1016/j.apsusc. 2021.151152., Aug. 9, 2021, pp. 1-8.

\* cited by examiner

114 Y 100 Y 101

FIG. 1a-2

FIG. 2b-4

FIG. 2b-5

FIG. 2f(ii)

FIG. 2g(ii)

FIG. 2h(ii)

FIG. 2i(ii)

FIG. 2j(ii)

FIG. 2k(ii)

FIG. 21

FIGURE 3a

S S C L

FIG. 6c

FIG. 7a

FIG. 7b

FIG. 7c

FIG. 9A

FIG. 9b

FIG. 9c

## 3-DIMENSIONAL MEMORY STRING ARRAY OF THIN-FILM FERROELECTRIC TRANSISTORS

# CROSS REFERENCE TO RELATED APPLICATIONS

The present application claims priority to U.S. provisional application ("Parent Application"), Ser. No. 63/222,926, entitled "3-Dimensional Memory String Array of Thin-Film 10 Ferroelectric Transistors," filed on Jul. 16, 2021.

The present application is related to U.S. patent application ("Non-Provisional Application I"), Ser. No. 17/674,137, entitled "Thin-film Storage Transistor With Ferroelectric Storage Layer," filed on Feb. 17, 2022, which claims priority 15 to (i) U.S. provisional application ("Provisional Application I"), Ser. No. 63/152,266, entitled "Thin-Film Storage Transistor With Ferroelectric Storage Layer," filed on Feb. 22, 2021, and (ii) U.S. provisional application ("Provisional Application II"), Ser. No. 63/153,273, entitled "Thin-Film 20 strings"). Storage Transistor With Ferroelectric Storage Layer," filed on Feb. 24, 2021.

The present application is related to U.S. patent application ("Non-Provisional Application II"), Ser. No. 17/382, Memory Structure Of NOR Memory Strings," filed on Jul. 221, 2021, which claims priority to U.S. provisional application ("Provisional Application III"), Ser. No. 63/054,743, entitled "Methods For Fabricating A 3-Dimensional Memory Structure Of NOR Memory Strings," filed on Jul. 30 21, 2020. The present application is also related to U.S. provisional application ("Provisional Application IV"), Ser. No. 63/054,750, entitled "Methods for Fabricating A 3-Dimensional Memory Structure of NOR Memory Strings, filed on Jul. 21, 2020, now U.S. patent application Ser. No. 35 17/382,126, filed Jul. 21, 2021; U.S. provisional application ("Provisional Application V"), Ser. No. 63/139,435, entitled "Vertical NOR Thin-film Transistor Strings and Fabrication Thereof," filed on Jan. 20, 2021, now U.S. patent application sional application ("Provisional Application VI"), Ser. No. 63/114,958, entitled "Methods for Reducing Disturb Errors by Refreshing Data Alongside Programming or Erase Operations," filed on Nov. 17, 2020, now U.S. patent application Ser. No. 17/525,712, filed Nov. 12, 2021.

The present application is also related to U.S. nonprovisional patent application ("Related Application"), Ser. No. 16/894,596, entitled "Capacitive-Coupled Non-Volatile Thin-Film Transistor Strings in Three Dimensional Arrays," filed on Jun. 5, 2020, which is a continuation of U.S. patent 50 application Ser. No. 16/107,118, entitled "Capacitive-Coupled Non-Volatile Thin-Film Transistor Strings in Three Dimensional Arrays," filed on Aug. 21, 2018, which is a divisional application of U.S. non-provisional patent application Ser. No. 15/248,420, entitled "Capacitive-Coupled 55 Non-Volatile Thin-Film Transistor Strings in Three Dimensional Arrays," filed on Aug. 26, 2016, which is related to and claims priority of (i) U.S. provisional application Ser. No. 62/235,322, entitled "Multi-gate NOR Flash Thin-film Transistor Strings Arranged in Stacked Horizontal Active 60 Strips With Vertical Control Gates," filed on Sep. 30, 2015; (ii) U.S. provisional patent application Ser. No. 62/260,137, entitled "Three-dimensional Vertical NOR Flash Thin-film Transistor Strings," filed on Nov. 25, 2015; (iii) U.S. nonprovisional patent application Ser. No. 15/220,375, "Multi- 65 Gate NOR Flash Thin-film Transistor Strings Arranged in Stacked Horizontal Active Strips With Vertical Control

2

Gates," filed on Jul. 26, 2016; and (vi) U.S. provisional patent application Ser. No. 62/363,189, entitled "Capacitive Coupled Non-Volatile Thin-film Transistor Strings," filed Jul. 15, 2016.

The disclosures of Parent Application, Related Application, Non-Provisional Applications I and II, and Provisional Applications I, II, III, IV, V, and VI are hereby incorporated by reference in their entireties.

## BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates to high-density memory structures. In particular, the present invention relates to high-density, low read-latency memory structures formed by interconnected thin-film storage elements (e.g., 3-dimensional array of thin-film storage transistors), including those organized as NOR-type memory strings ("NOR memory

## 2. Discussion of the Related Art

The memory circuit structures of this detailed description 064, entitled "Methods For Fabricating A 3-Dimensional 25 may be fabricated above the planar surfaces of one or more semiconductor substrates (e.g., silicon wafers) using conventional fabrication processes. In this description, "vertical" refers to a direction substantially normal to a planar surface of a semiconductor substrate, and "horizontal" refers to any direction that is orthogonal to "vertical." A Cartesian coordinate system may therefore be adopted, in which "horizontal" refers to any direction substantially parallel to the planar surface of semiconductor substrate, which is a surface spanning any two non-colinear horizontal directions X and Y (also referred to as the "X-Y plane"). Similarly, with respect to that Cartesian coordinate system, "vertical" refers to a normal direction (also referred to as the "Z-direction") to the planar surface.

A NOR-type memory string includes storage transistors Ser. No. 17/559,101, filed Dec. 22, 2021; and U.S. provi- 40 that share a common source region and a common drain region, while allowing each storage transistor to be individually addressed and accessed. The Related Application discloses 3-dimensional arrays of NOR memory strings ("NOR memory strings") of charge storage transistors. The Related Application discloses, for example, a NOR memory string that includes (i) a common source region and a common drain region both running lengthwise along a horizontal direction and (i) the gate electrodes for the charge storage transistors each running along a vertical direction.

Advances in electrically polarizable materials ("ferroelectric materials"), especially those used in electronic circuits, suggest new potential applications in ferroelectric memory circuits. For example, the article "Ferroelectricity in Hafnium Oxide: CMOS compatible Ferroelectric Field Effect Transistors," by T. S. Böscke et al., published in 2011 International Electron Devices Meeting (IEDM), pp. 24.5.1-24.5.4 (doi: 10.1109/IEDM.2011.6131606), discloses a ferroelectric field effect transistor ("FeFET") that uses hafnium oxide as a gate dielectric material. By controlling polarization in a ferroelectric gate dielectric layer, the FeFET may be programmed to have one of two or more selectable threshold voltages. Each threshold voltage of the FeFET constitutes a state (e.g., a "programmed" state, an "erased" state, or any other state that represents a designated binary value). Such an FeFET has application in high-density memory circuits. For example, U.S. patent application Ser. No. 13/897,037, entitled "Apparatuses having a ferroelectric field-effect tran-

sistor memory array and related method," by D. V. Nirmal Ramaswamy et al., filed on May 17, 2013, now U.S. Pat. No. 9,281,044, discloses a 3-dimensional array of FeFETs.

The FeFETs of the prior art, however, suffer from low endurance. For example, the article "Vertical Ferroelectric 5 HfO<sub>2</sub> FET based on 3-D NAND Architecture: Towards Dense Low-Power Memory," by K. Florent et. al., published in 2018 IEEE International Electron Devices Meeting pp. 2.5.1-2.5.4 2018, (doi: IEDM.2018.8614710), discloses an endurance of merely  $10^4$  10 cycles. Such low endurance renders the memory circuits practically unsuitable for many memory applications. It is highly desirable to have a memory circuit that can serve as a building a block of a main memory system. Current building blocks of main memory systems (e.g., dynamic 15 random-access memory (DRAM)) have low retention time and low memory density.

## **SUMMARY**

According to one embodiment of the present invention, an array of memory cells includes FeFETs formed in stacks of horizontal active strips, with vertical control gate electrodes (also referred to as "local word lines") provided along one or both sidewalls of the active strips, the control gate 25 electrodes being separated from their associated active strips by one or more polarizable or ferroelectric elements (also referred to as "ferroelectric or polarization layers"). Polarization of the polarizable element in an FeFET changes the threshold voltage the FeFET. Each active strip may include 30 a channel layer formed adjacent both a common source region and a common drain region. In one embodiment, in a given stack of active strips (also referred to as an "active stack"), the polarizable or ferroelectric elements associated with the FeFETs of each active strip are separated from the 35 polarizable or ferroelectric elements associated with the FeFETs of other active strips. The FeFETs of each active strip may be organized as one or more NOR memory strings. Further, independently addressable FeFETs may be formed along opposite sides of an active strip to achieve twice the 40 memory density than if the FeFETs are formed as a single file along the length of the common bit line. Furthermore, by forming channel regions of the FeFETs along the vertical sidewalls of each active strip (i.e., between the common drain region and the common source region), a memory 45 density that is substantially higher than is achieved in the prior art is possible because the volume of the channel region, even with a large extent along the Z-direction, has an insignificant footprint in the X-Y plane.

In one embodiment, only the common drain region (also 50 referred to as a "common bit line") of the FeFETs in a NOR memory string is electrically and selectively connected by one or more conductors to one of several voltage sources. In one embodiment, the common source region may be precharged to a predetermined voltage prior to a read, program 55 (sometimes also referred to as "write"), or erase operation, and is held to that predetermined voltage by the parasitic capacitance associated with the common source region during the read, program (sometimes also referred to as "write"), or erase operation. In one embodiment, one or 60 more arrays of NOR memory strings may be organized and formed as an independently addressable modular memory circuit (also referred herein as a "tile"). A group of tiles may be formed above the same substrate but are configured to each be independently controlled and operated, thereby 65 allowing massively parallel read, program or erase operations to be carried out concurrently on the tiles. The NOR

4

memory strings within each tile may also be organized in groups that are configured to each be independently controlled and operated.

In one embodiment, in a 3-dimensional array of NOR memory strings, FeFETs are formed on both side edges along the lengths of each active strip, with vertical local word lines being provided along both side edges. High density is achieved by sharing the local word lines between their adjacent active stacks, each local word line serving as a common gate electrode to vertically aligned FeFETs in the active strips of both active stacks. The vertical local word lines may be contacted by interconnection conductors (also referred to as "global word lines") provided above or below the 3-dimensional array of NOR memory strings. The global word lines may run along a direction transverse to the lengths of the contacted active strips.

Organizing the FeFETs as 3-dimensional arrays of NOR memory strings—rather than as NAND memory strings, for example—results in (i) reduced read-latencies approaching those of dynamic random access memory (DRAM) arrays, (ii) reduced sensitivities to read-disturb and program-disturb conditions, (iii) reduced power dissipation and a lower cost-per-bit metric relative to planar NAND or DRAM memory arrays, and (iv) the ability to read, write or erase FeFETs on multiple active strips concurrently, thereby significantly increasing data throughput.

According to one embodiment of the present invention, undesirable effects on a memory operation due to variations among FeFETs within an array of NOR memory strings may be overcome by processing the memory operation in conjunction with FeFETs in a designated reference NOR memory string within the same array. For example, effects on a read operation of an FeFET of a NOR memory string due to a background leakage current present in NOR memory strings can be substantially mitigated by comparing the sensed result of a concurrently read FeFET within a reference NOR memory string. In some embodiments, the ferroelectric or polarizable elements may have a data retention time that requires refreshing to meet data stability requirements in some applications. Relative to storage transistors in conventional non-volatile memory circuits (e.g., non-volatile NAND memory strings), which do not require refreshing in those applications, the FeFETs may be considered "quasi-volatile" (QV) storage transistors. The FeFETs are considered quasi-volatile because, as compared to conventional volatile memory circuits (e.g., DRAM circuits), the FeFETs require refreshing significantly less frequently. For example, FeFETs in high density arrays need only be refreshed, restored, or replaced, once every few minutes, hours or every few days, and may be accomplished by accessing the FeFETs individually or accessed concurrently as one or more groups. Such refresh operations ensure long term stable and reliable operations. The refresh operations may also be performed in the background, without interfering regular user read, erase or write operations.

The present invention is better understood upon consideration of the detailed description below, in conjunction with the accompanying drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

Various embodiments of the invention are disclosed in the following detailed description and the accompanying drawings. Although the drawings depict various examples of the invention, the invention is not limited by the depicted examples. It is to be understood that, in the drawings, like

reference numerals designate like structural elements. Also, it is understood that the depictions in the FIGS. are not necessarily to scale.

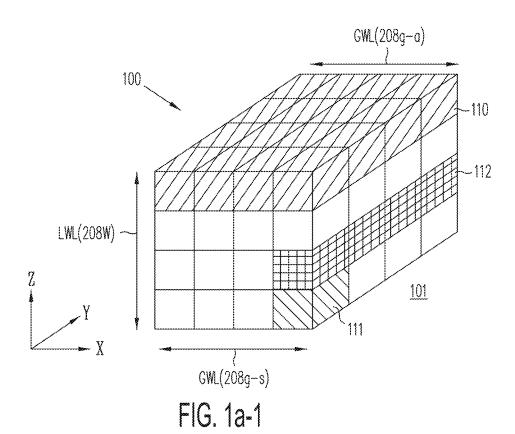

FIG. 1, which includes FIGS. 1a-1 and 1a-2, show conceptualized memory structure 100, which illustrates an 5 organization of ferroelectric field-effect transistors (FeFETs) in an array of NOR memory strings, according to one embodiment of the present invention.

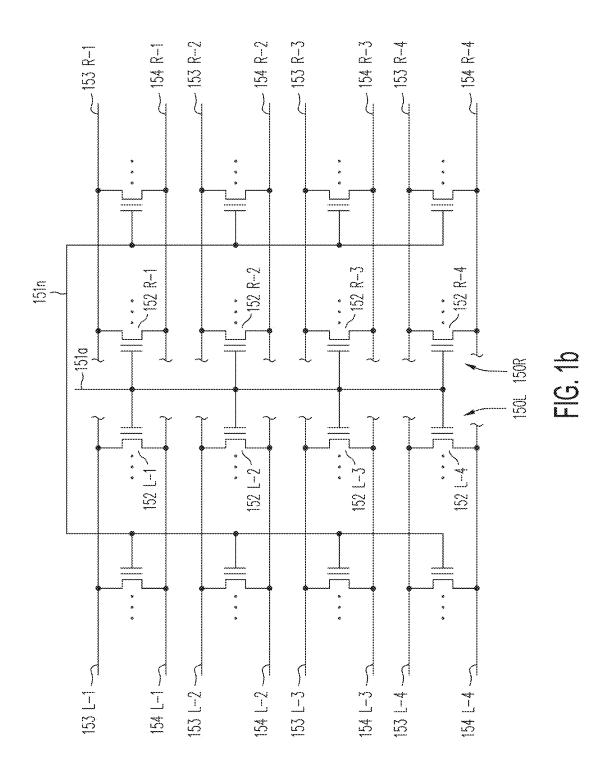

FIG. 1b shows a basic circuit representation of four NOR memory string-pairs, each NOR memory string-pair including two NOR memory strings provided on the same plane (i.e., one of planes 159-1, 159-2, 159-3 and 159-4), according to one embodiment of the present invention.

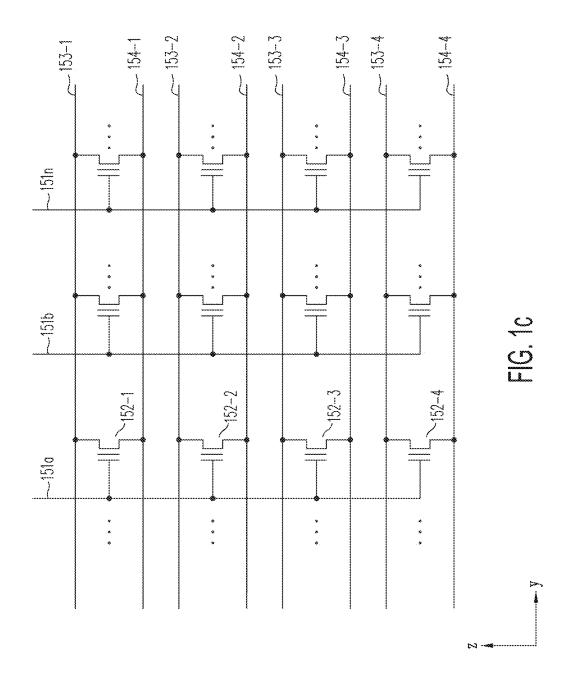

FIG. 1c shows a basic circuit representation of four NOR memory strings, each NOR memory string being provided 15 on a respective one of planes 159-1, 159-2, 159-3 and 159-4, according to one embodiment of the present invention.

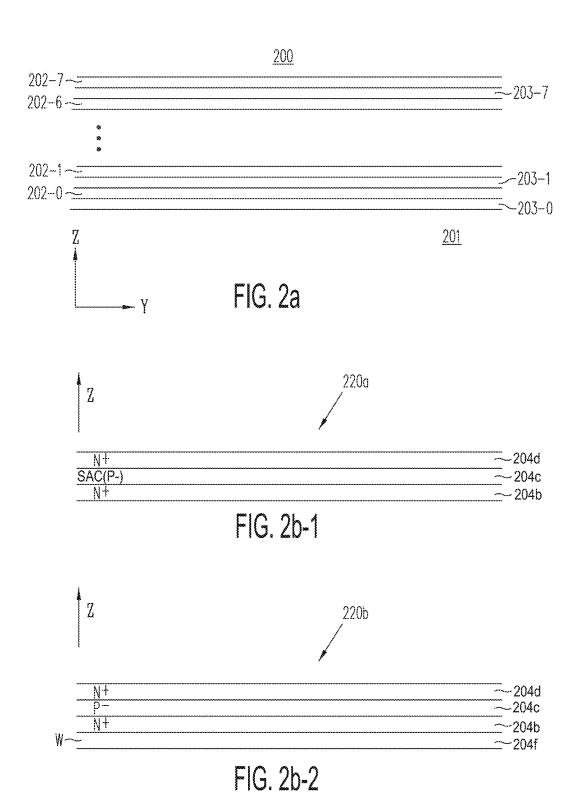

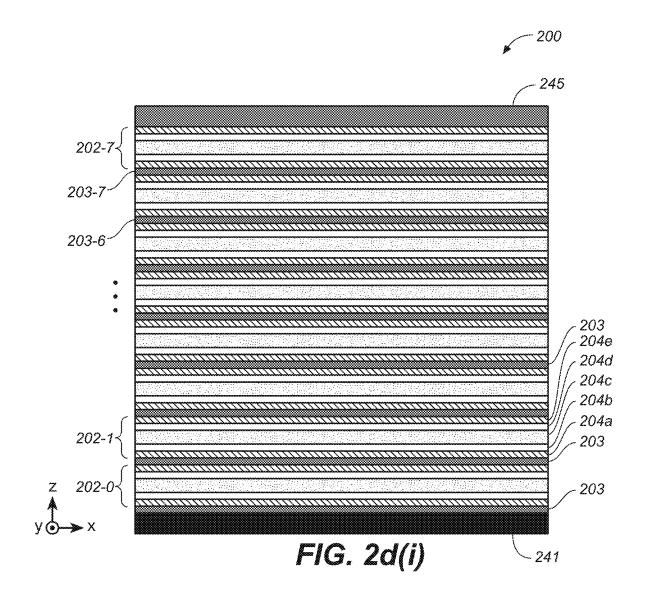

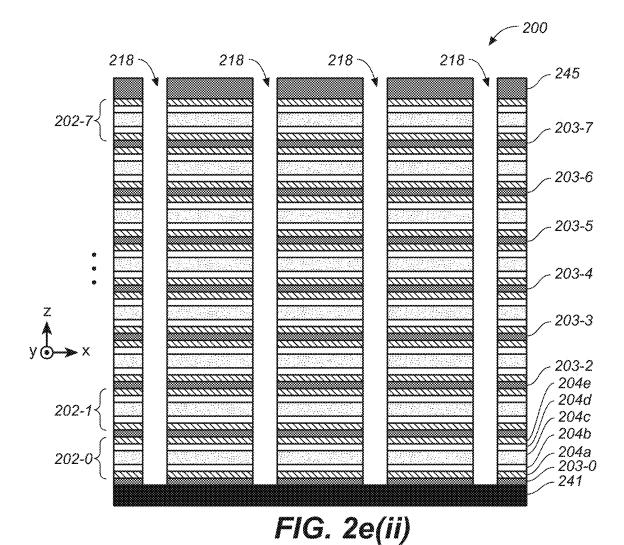

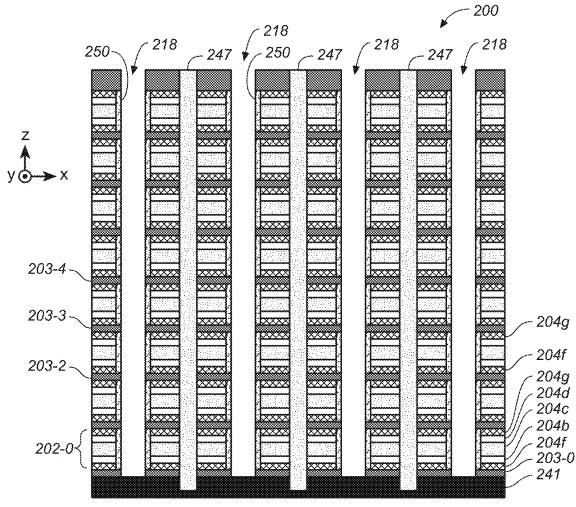

FIG. 2a shows a cross section in a Y-Z plane of semiconductor structure 200, after active layers 202-0 to 202-7 (each separated from the next active layer by one of isolation 20 layers 203-0 to 203-7) have been formed on semiconductor substrate 201, but prior to formation of individual active strips, in accordance with one embodiment of the present invention.

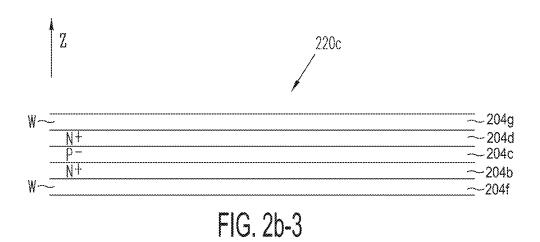

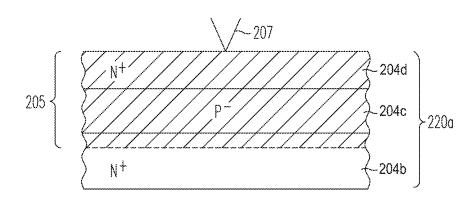

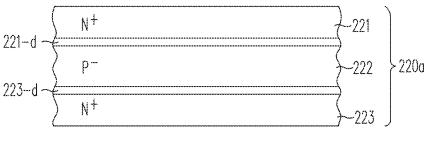

FIGS. 2b-1, 2b-2, 2b-3, 2b-4 and 2b-5 show various 25 examples of active layer 220a, according to one embodiment of the present invention.

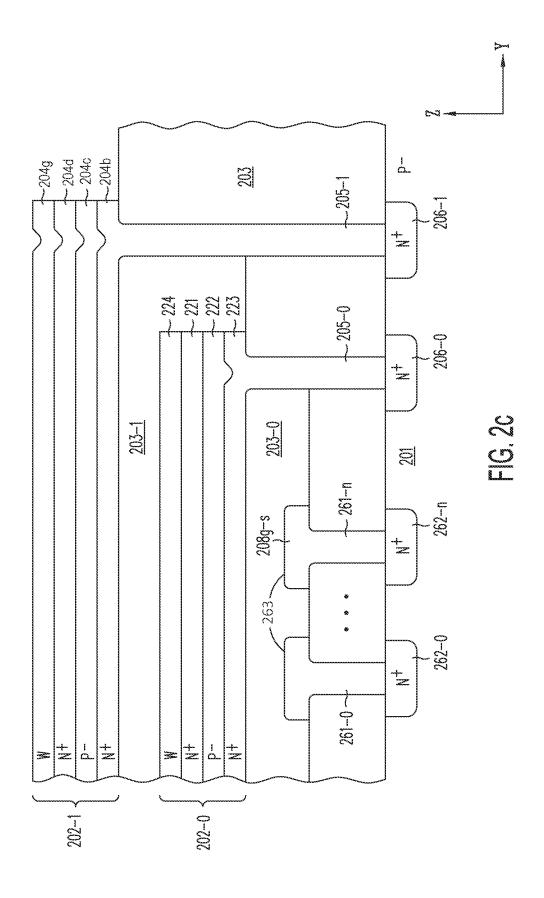

FIG. 2c shows cross section in a Y-Z plane of structure 200 of FIG. 2a through buried contacts 205-0 and 205-1, which connect  $n^+$  silicon layers 204b of active layers 202-0 30 and 202-1 to circuitry 206-0 and 206-1 in semiconductor substrate 201.

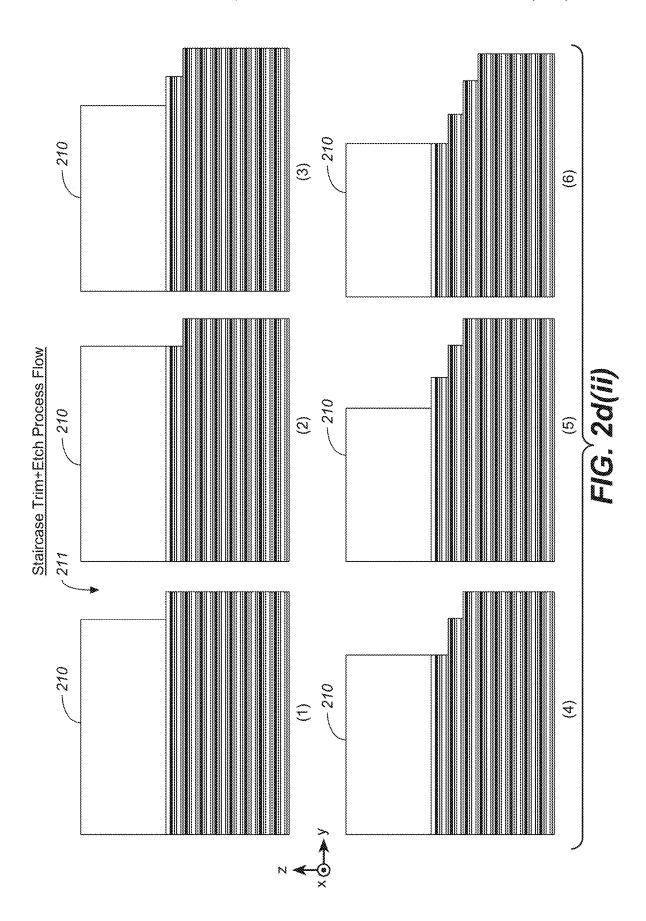

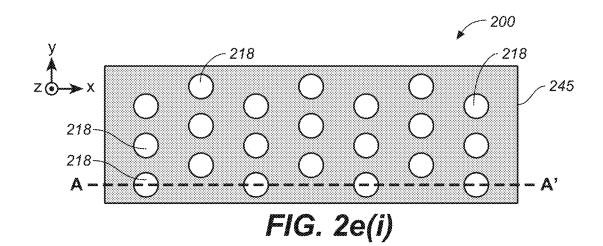

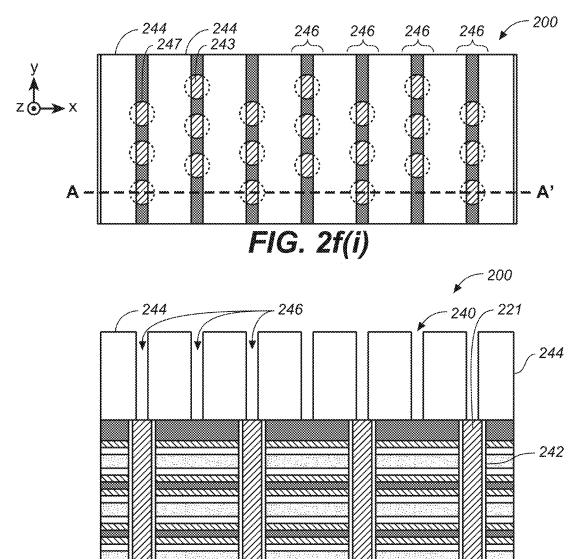

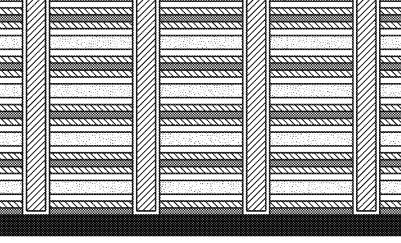

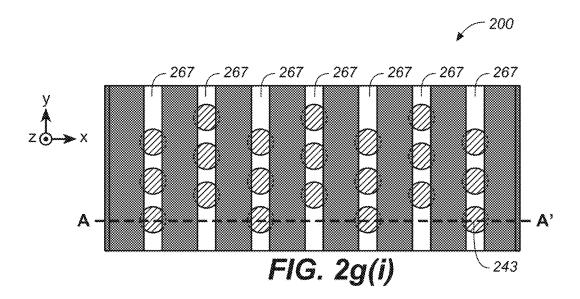

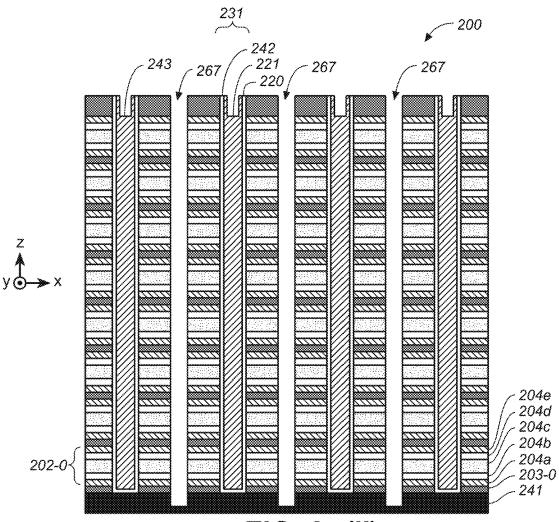

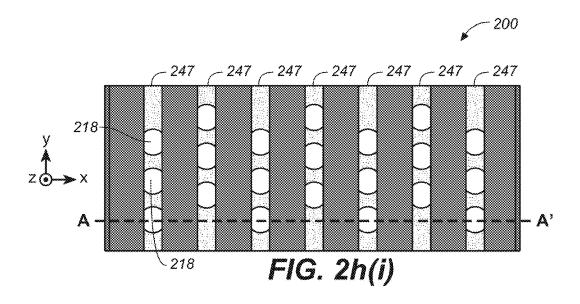

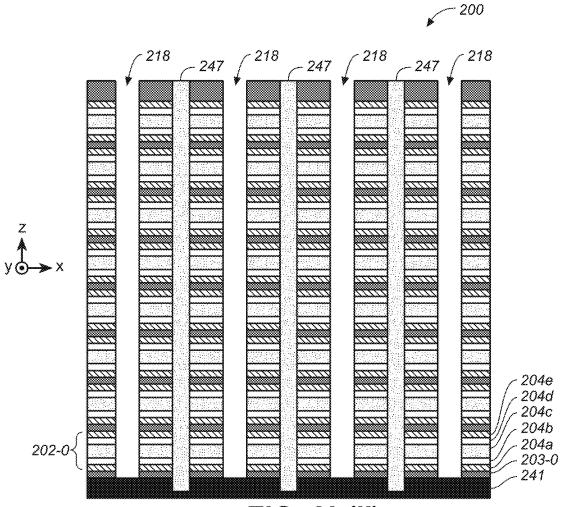

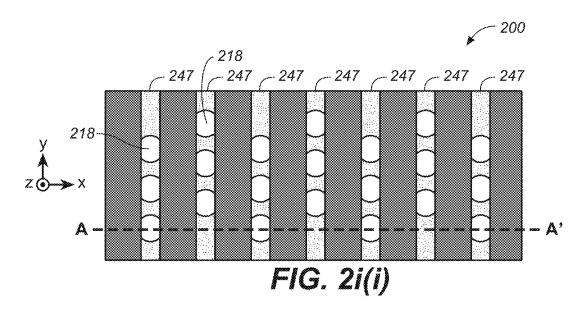

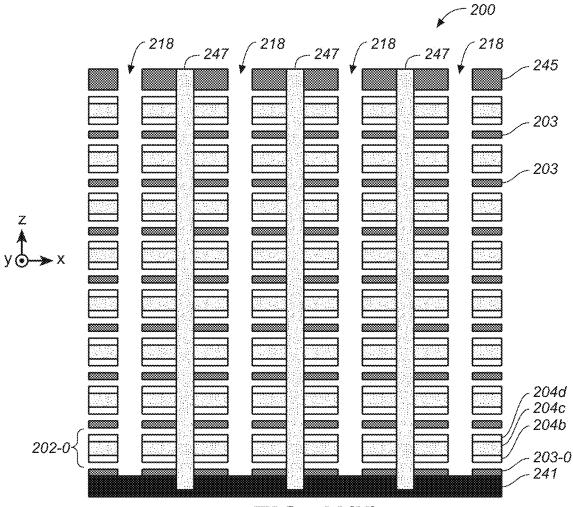

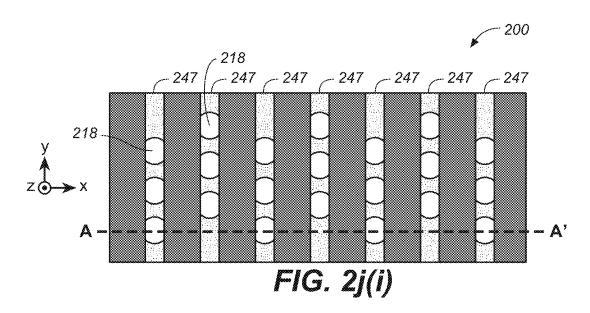

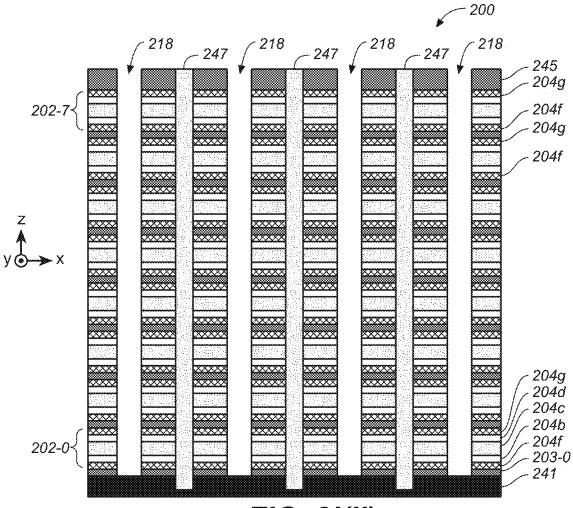

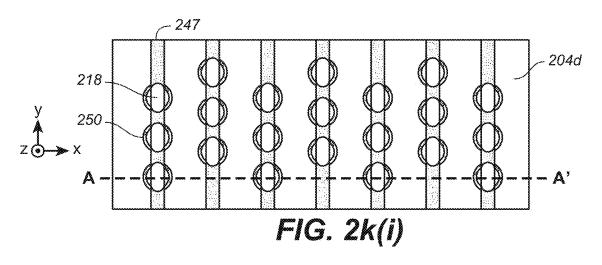

FIGS. 2d(i), 2d(ii), 2e(i), 2e(ii), 2f(i), 2f(ii), 2g(i), 2g(ii), 2h(ii), 2h(ii), 2i(i), 2i(ii), 2j(i), 2j(ii), 2h(i) and 2h(ii) illustrate steps of an exemplary process for forming a modular circuit 35 or tile that includes an array of NOR memory strings, including an array portion (i.e., memory structure 200), according to one embodiment of the present invention; in particular, FIG. 2h illustrates, preceding steps that form the gate stacks of the FeFETs, a step for providing a channel 40 region for each FeFET; the channel region may be provided by any one group of the groups of process steps described in conjunction with FIGS. 3a to 3b, FIGS. 4a to 4c and FIGS. 5a to 5f, respectively.

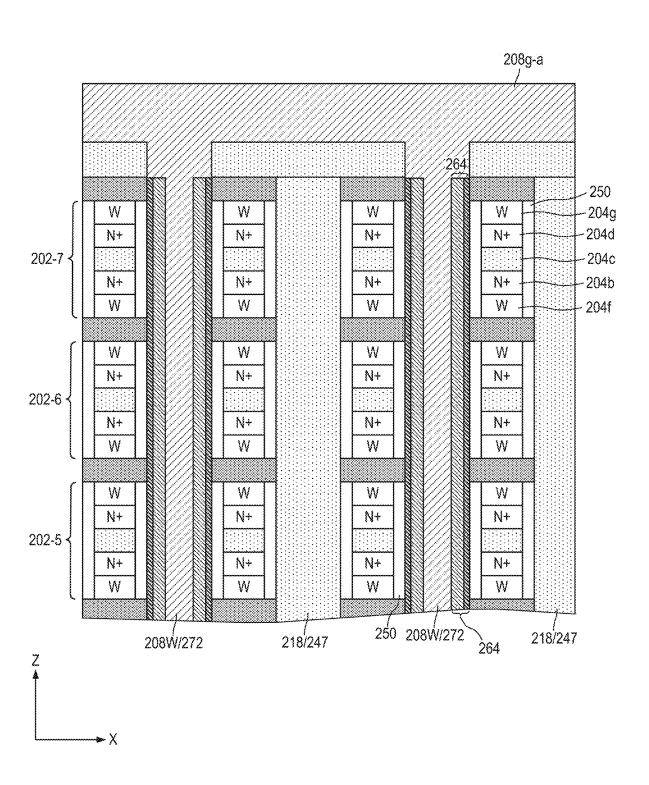

FIG. 2*l* shows an X-Z plane cross section through a row 45 of local word lines 208*g-a*, showing active strips formed out of active layers 202-7 and 202-6, according to one embodiment of the present invention.

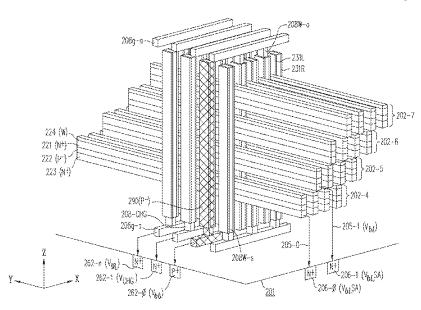

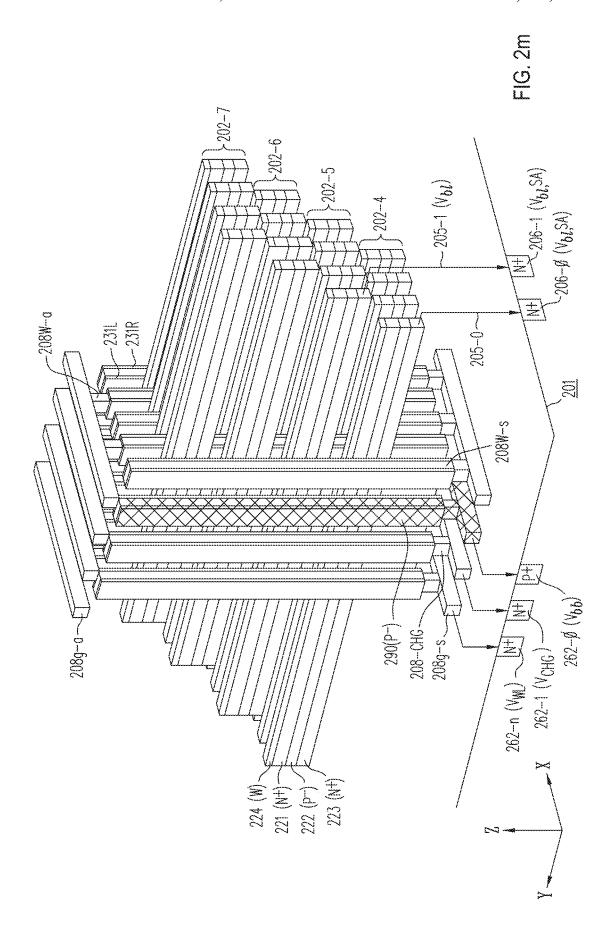

FIG. 2m shows a 3-dimensional view of horizontal active layers 202-4 to 202-7 in the embodiment of FIG. 2k, with 50 local word lines or local pre-charge word lines connected to global word lines 208g-s and global word lines 208g-a, and showing each active strip as having its N<sup>+</sup> layer 204d (acting as a drain region) connected through select circuits to any of voltage supplies (e.g.,  $V_{ss}$ ,  $V_{bl}$ ,  $V_{pgm}$ ,  $V_{inhibit}$  and  $V_{erase}$ ), 55 decoding, sensing and other circuits arranged either adjacent or directly underneath the memory arrays.

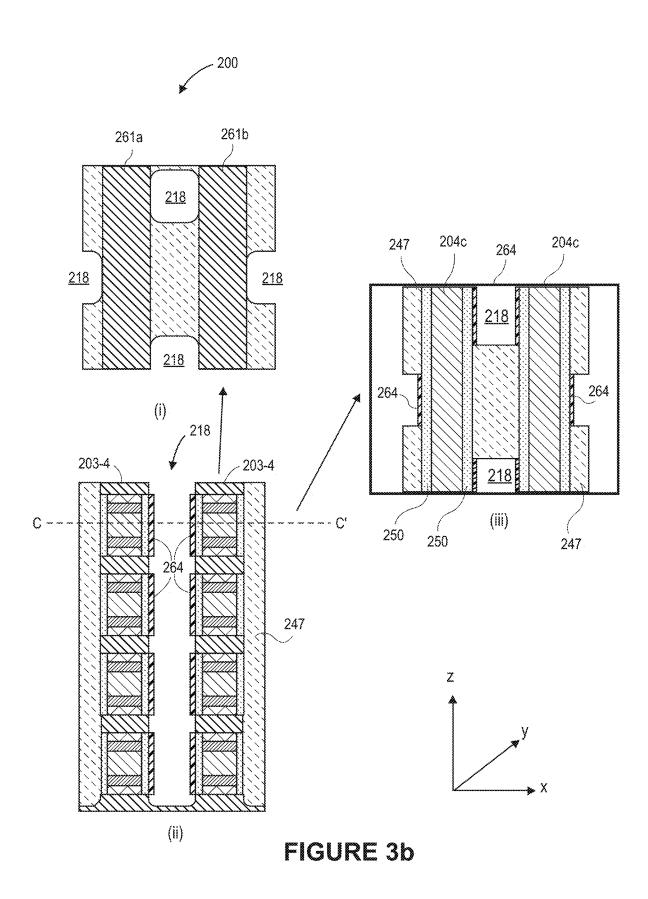

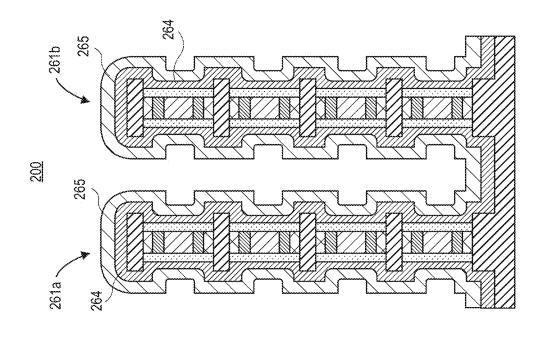

FIGS. 3a and 3b illustrate a first group of process steps for forming the gate stacks in the FeFETs of an array of NOR memory strings, according to one embodiment of the present 60 invention.

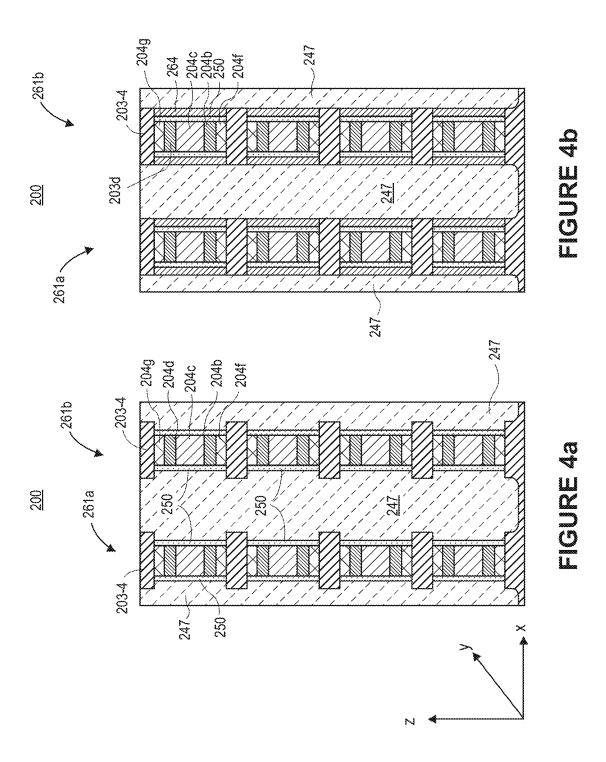

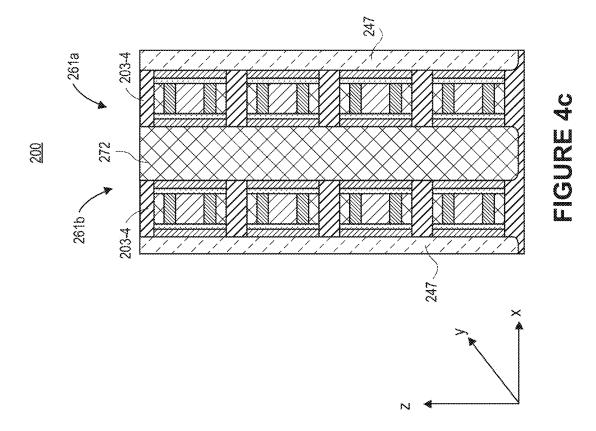

FIGS. 4a, 4b and 4c illustrate a second group of process steps for forming the gate stacks in the FeFETs in an array of NOR memory strings, according to one embodiment of the present invention.

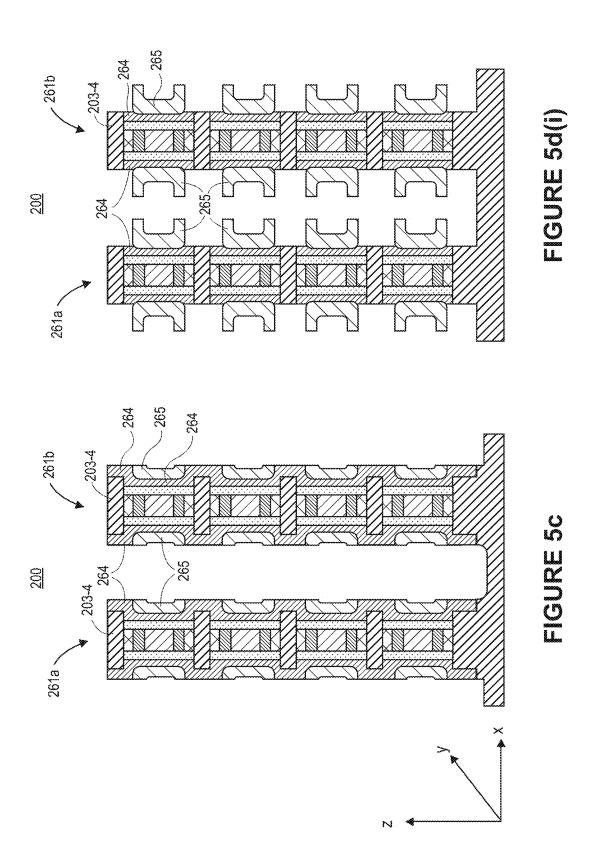

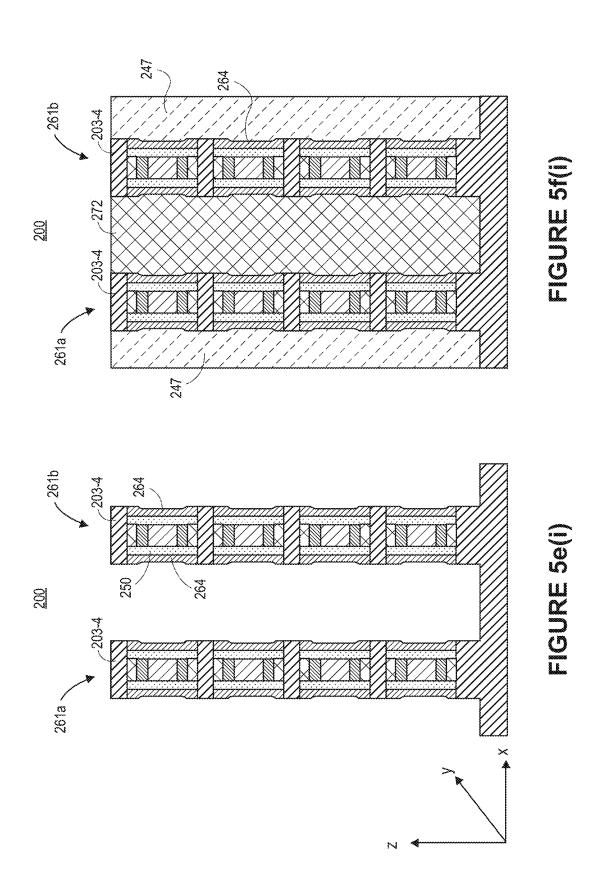

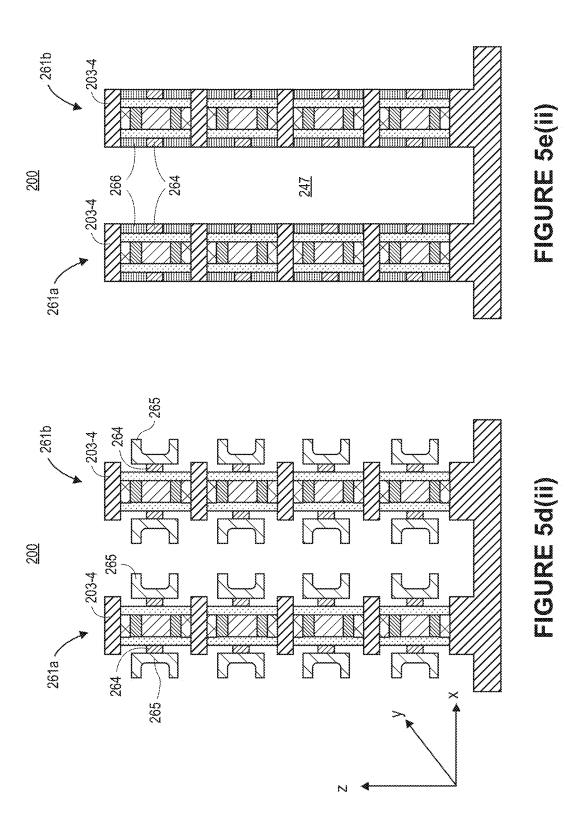

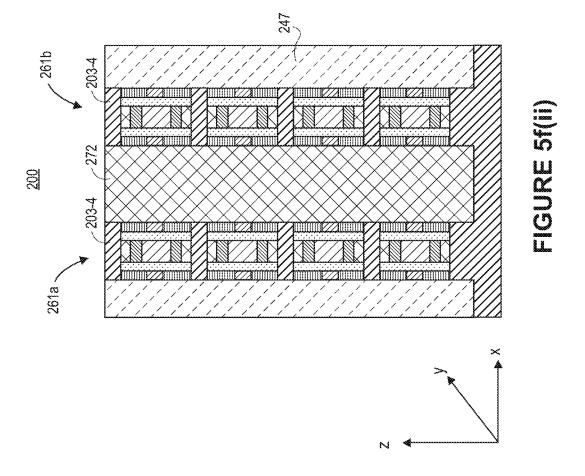

FIGS. 5a, 5b, 5c, 5d(i), 5d(ii), 5e(i), 5e(i), 5f(i) and 5f(ii) illustrate a third group of process steps for forming the gate

6

stacks in the FeFETs of an array of NOR memory strings, according to one embodiment of the present invention.

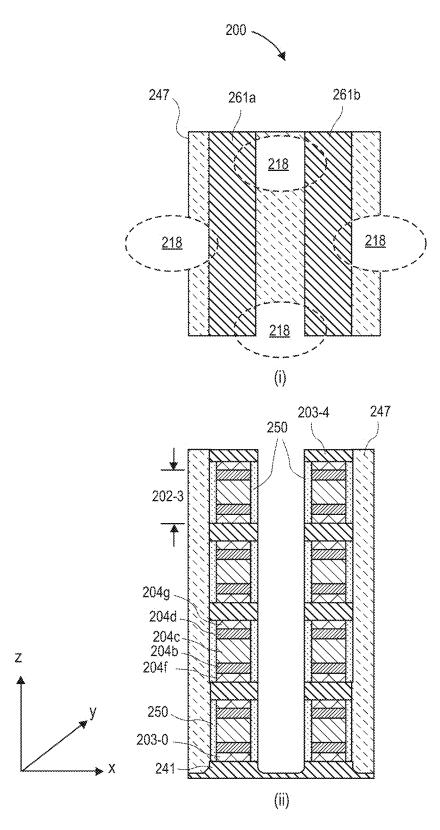

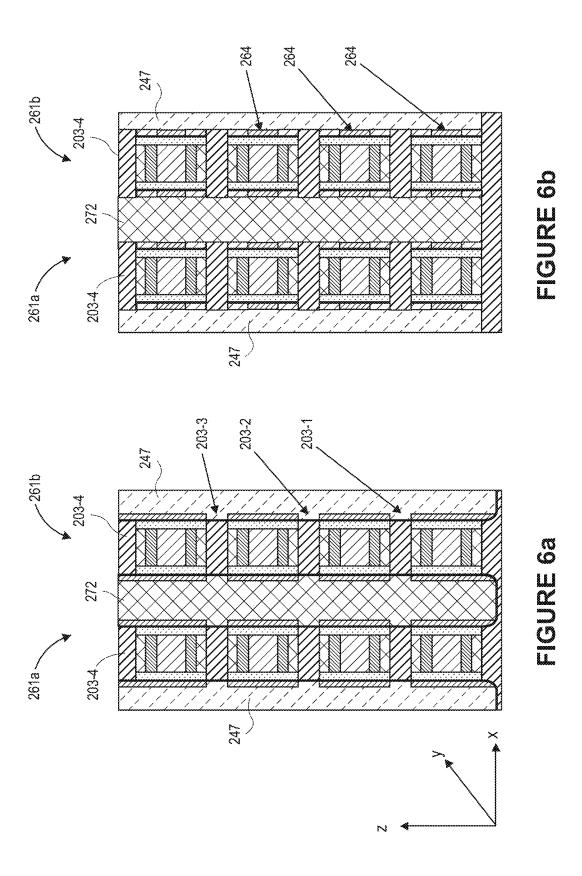

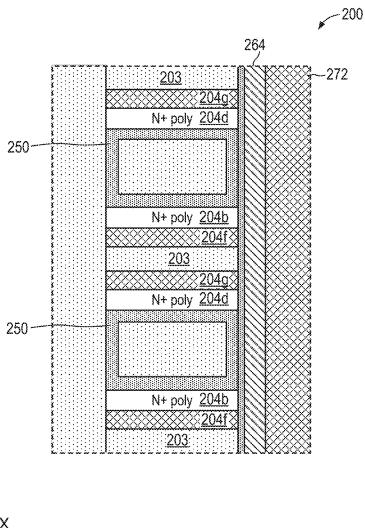

FIG. 6a shows an X-Z cross sectional view of memory structure 200, which represents active stacks 261a and 261b fabricated under any group of process steps illustrated by FIG. 3a-3b, FIGS. 4a to 4c and FIGS. 5a to 5f(i), in accordance with one embodiment of the present invention.

FIG. 6b shows an X-Z cross sectional view of memory structure 200, which represents active stacks 261a and 261b fabricated under the group of process steps illustrated by FIGS. 5a-5f(ii), in accordance with one embodiment of the present invention.

FIG. 6c shows an X-Z cross sectional view of memory structure 200, fabricated under a channel-last fabrication process, in accordance with one embodiment of the present invention.

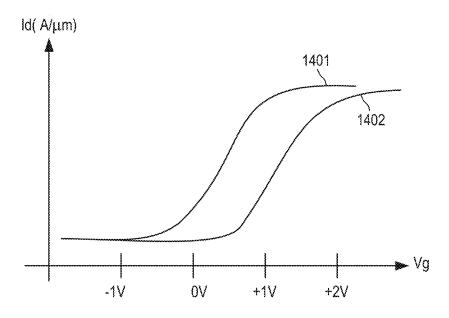

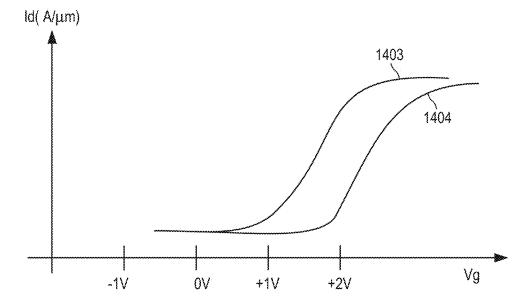

FIG. 7a shows hysteresis in the drain current  $(I_d)$  in response to an applied gate voltage  $(V_g)$  in a conventional FeFET.

FIG. 7b shows a desirable hysteresis in the drain current  $(I_d)$  response to an applied gate voltage  $(V_g)$  in a thin-film FeFET in a NOR memory array, according to one embodiment of the present invention.

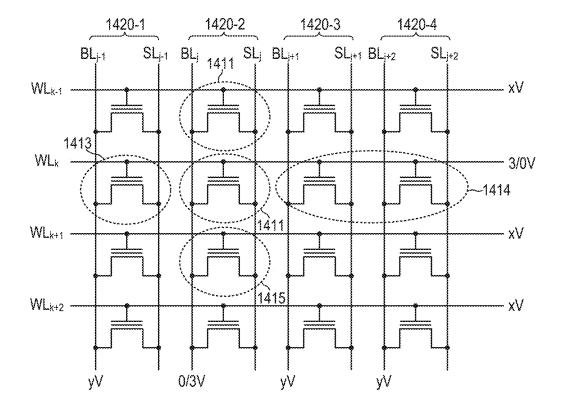

FIG. 7c shows a circuit schematic diagram of FeFETs in NOR memory strings **1420-1** to **1420-4**, according to one embodiment of the present invention.

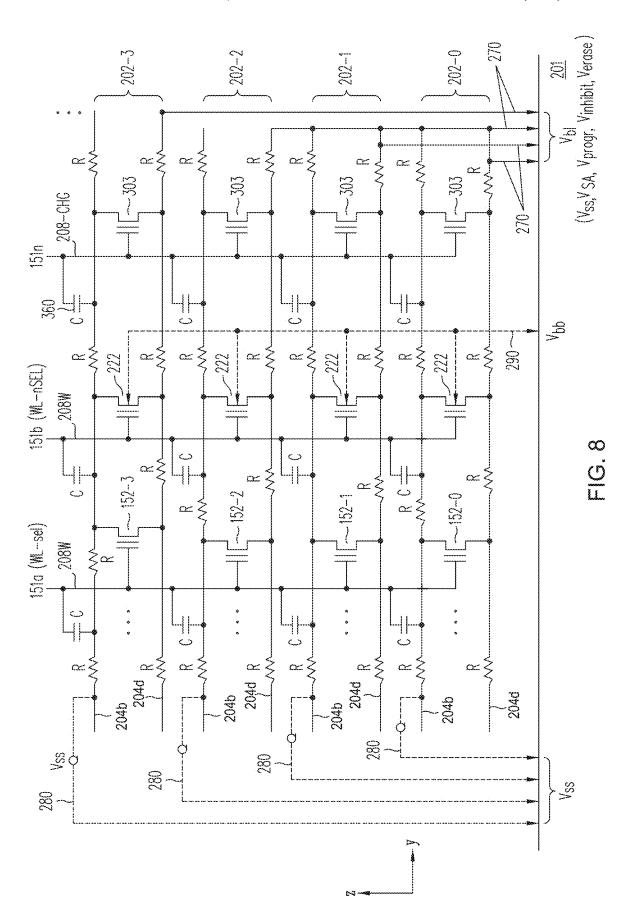

FIG. 8 illustrates the methods and circuit elements used for setting source voltage  $V_{ss}$  in  $n^+$  silicon layers **204***d*; specifically, source voltage  $V_{ss}$  may be set through hard-wire decoded source line connections **280** (dashed line) or alternatively, by activating pre-charge FeFETs **303** and decoded bit line connections **270**, to any one of voltage sources for bit line voltages  $V_{ss}$ ,  $V_{bl}$ ,  $V_{pgm}$ ,  $V_{inhibit}$  and  $V_{erase}$ .

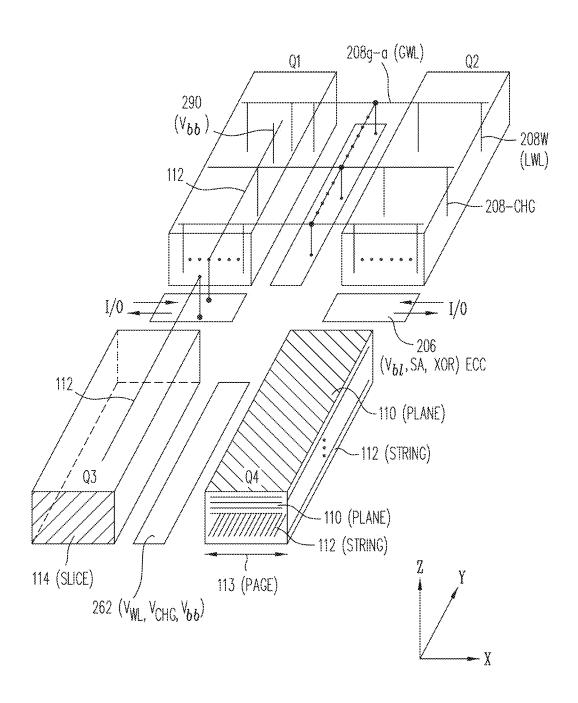

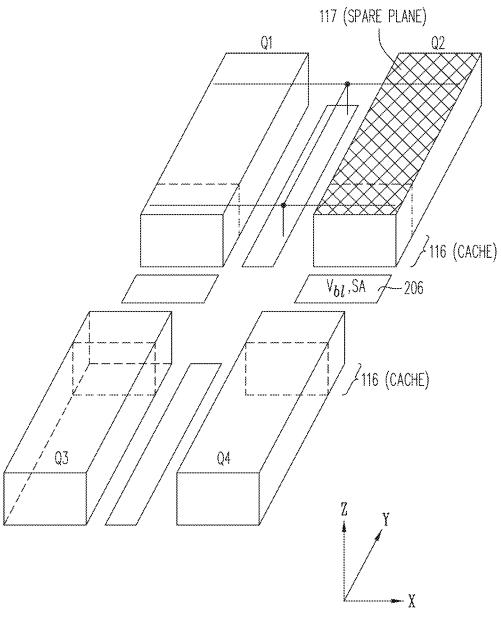

FIG. 9a shows semiconductor structure 600, which is a three-dimensional representation of an array of NOR memory strings organized into quadrants Q1-Q4; in each quadrant, (i) numerous NOR memory strings are each formed in an active strip extended along the Y-direction (e.g., NOR memory string 112), (ii) pages extending along the X-direction (e.g., page 113), each bit in the page corresponds to an FeFET from each NOR memory string at a corresponding Y-position, the NOR memory strings in the page being of the same corresponding Z-position (i.e., of the same active layer); (iii) slices extending in both the X- and Z-directions (e.g., slice 114), with the bits in each slice provided by the pages of the same corresponding Y-position, one page from each of the planes, and (iv) planes extending along both the X- and Y-directions (e.g., plane 110), the bits in each plane being provided by all pages at a given Z-position (i.e., formed out of the same active layer).

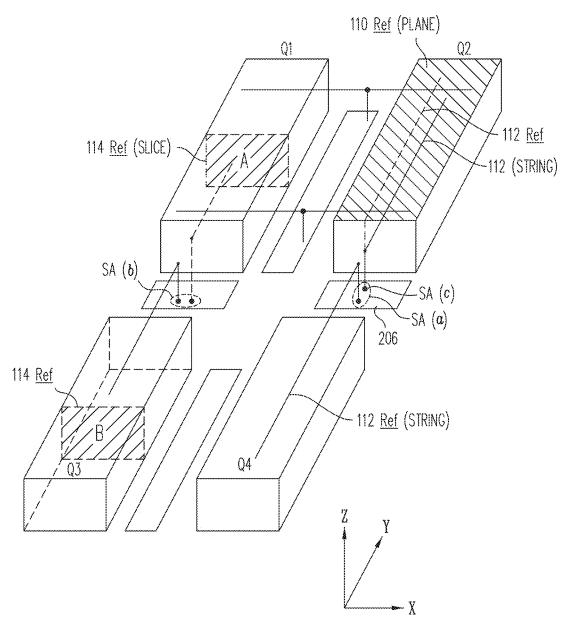

FIG. 9b shows structure 600 of FIG. 9a, showing FeFETs in programmable reference string 112-Ref in quadrant Q4 and FeFETs in NOR memory string 112 in quadrant Q2 coupled to sense amplifiers SA(a), Q2 and Q4 being "mirror image quadrants"; FIG. 9b also shows (i) programmable reference slice 114-Ref (indicated by area A) in quadrant Q3 similarly providing corresponding reference FeFETs for slice 114 in mirror image quadrant Q1, sharing sense amplifiers SA(b), and (ii) programmable reference plane 110-Ref in quadrant Q2 providing corresponding reference FeFETs to plane 110 in mirror image quadrant Q1, sharing sense amplifiers SA(c), and also providing corresponding reference FeFETs for NOR memory strings in the same quadrant (e.g., NOR memory string 112).

FIG. 9c shows structure 600 of FIG. 9a, showing slices 116 being used as a high speed cache because of their close proximity to their sense amplifiers and voltage sources 206;

FIG. 9c also show spare planes 117, which may be used to provide replacement or substitution NOR memory strings or pages in quadrant O2.

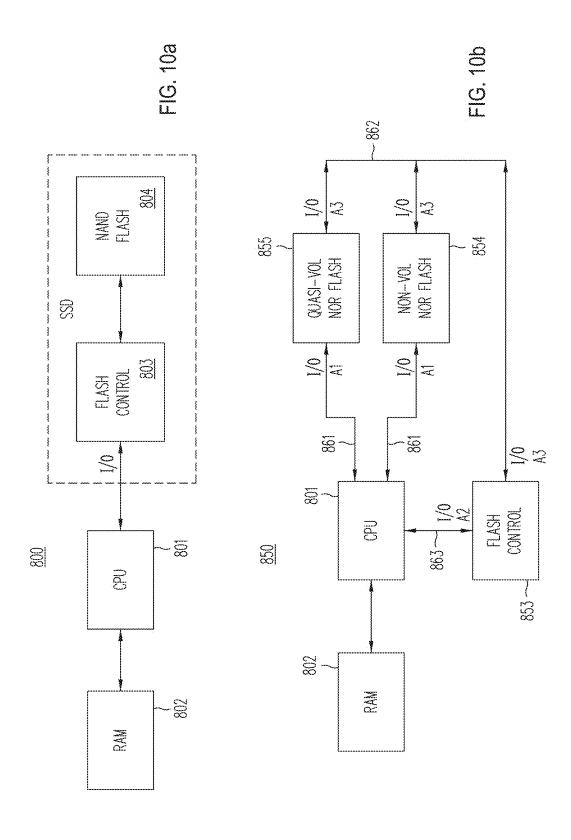

FIG. 10a shows in simplified form prior art storage system 800 in which microprocessor (CPU) 801 communicates with system controller 803 in a flash solid state drive (SSD) that employs NAND flash chips 804; the SSD emulates a hard disk drive and NAND flash chips 804 do not communicate directly with CPU 801 and have relatively long read latency.

FIG. 10b shows in simplified form system architecture 850 using the memory devices of the present invention, in which FeFETs of NOR memory string arrays 854 and 855 communicate directly with CPU 801 through one or more input and output (I/O) ports 861, and indirectly through 15 controller 863.

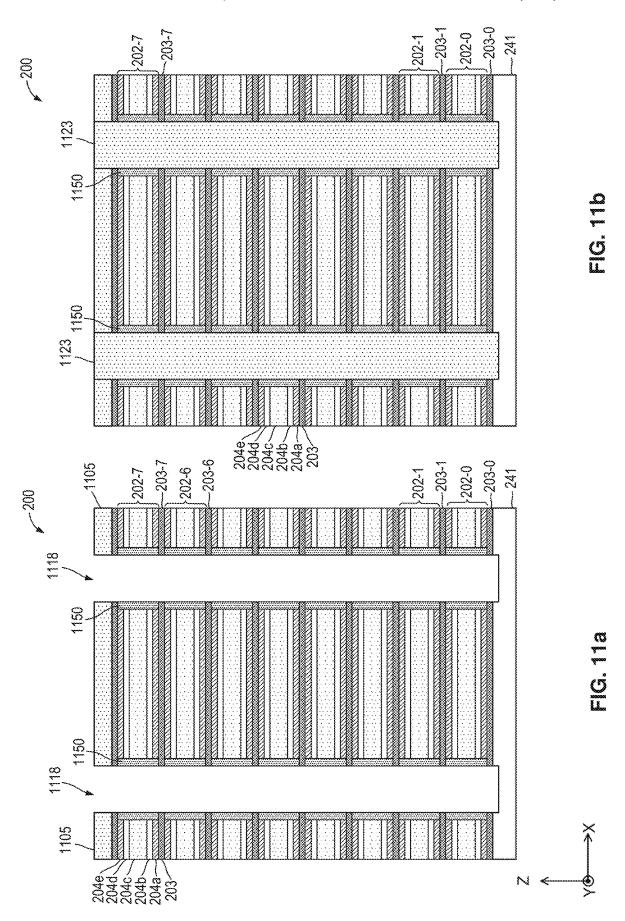

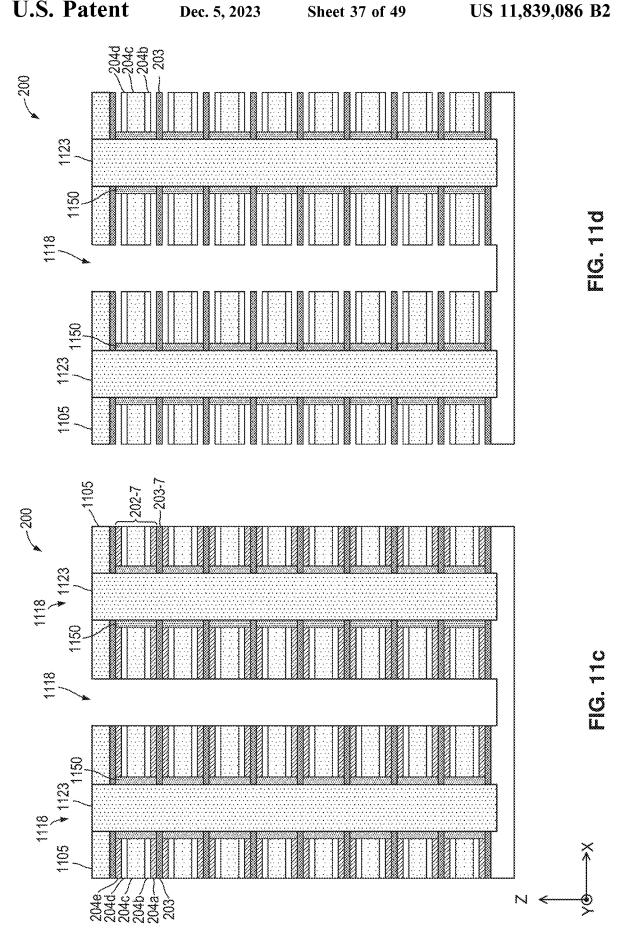

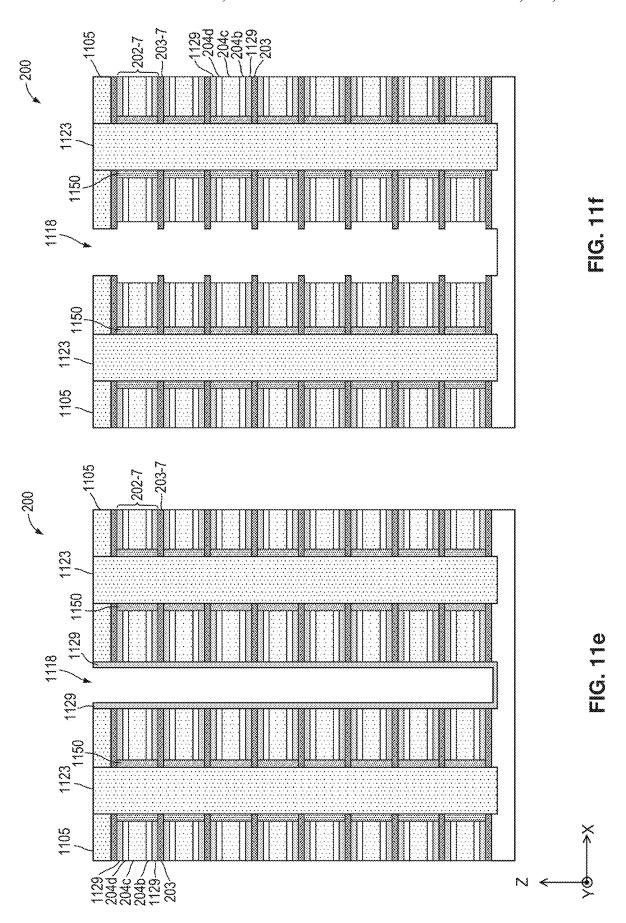

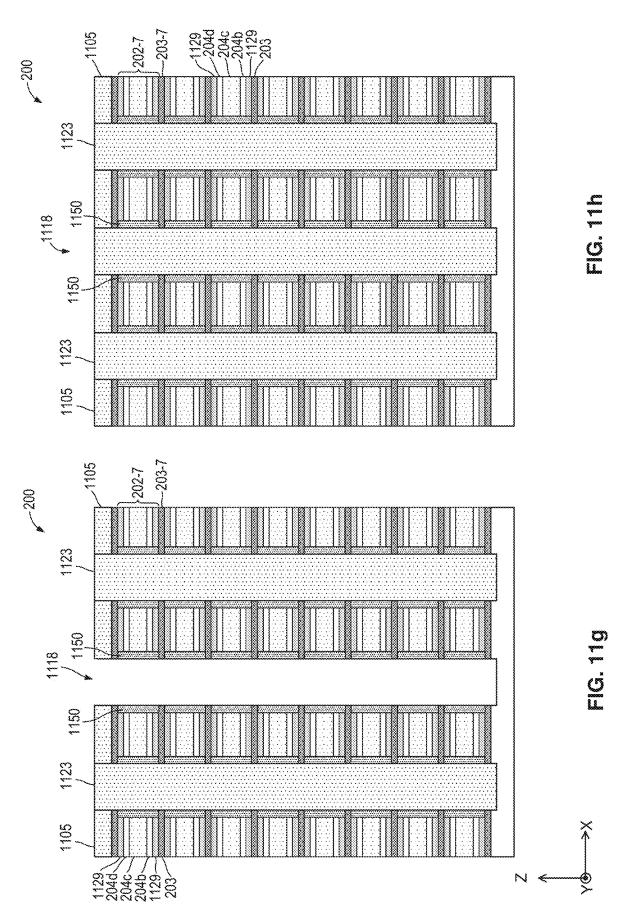

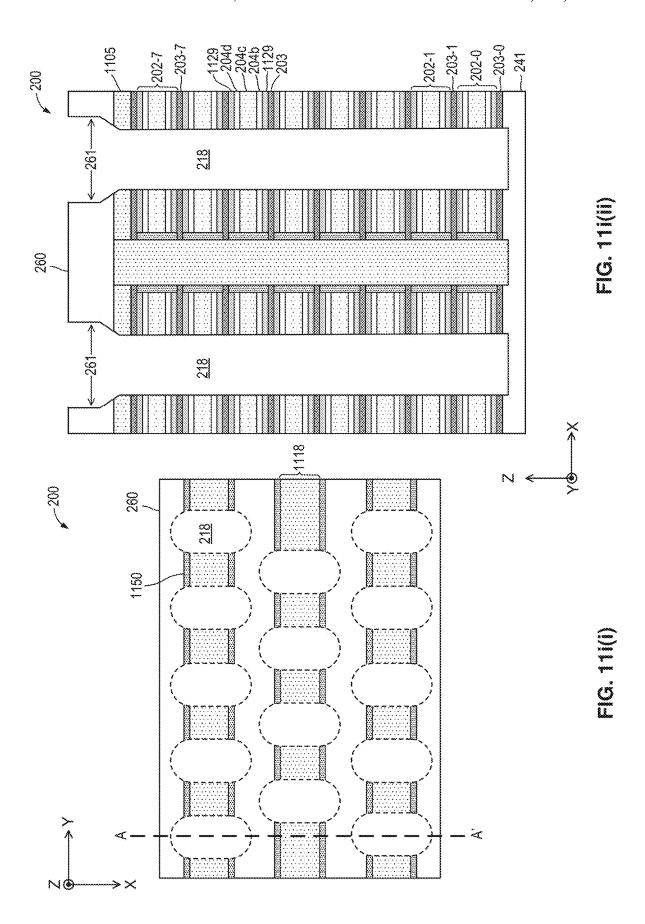

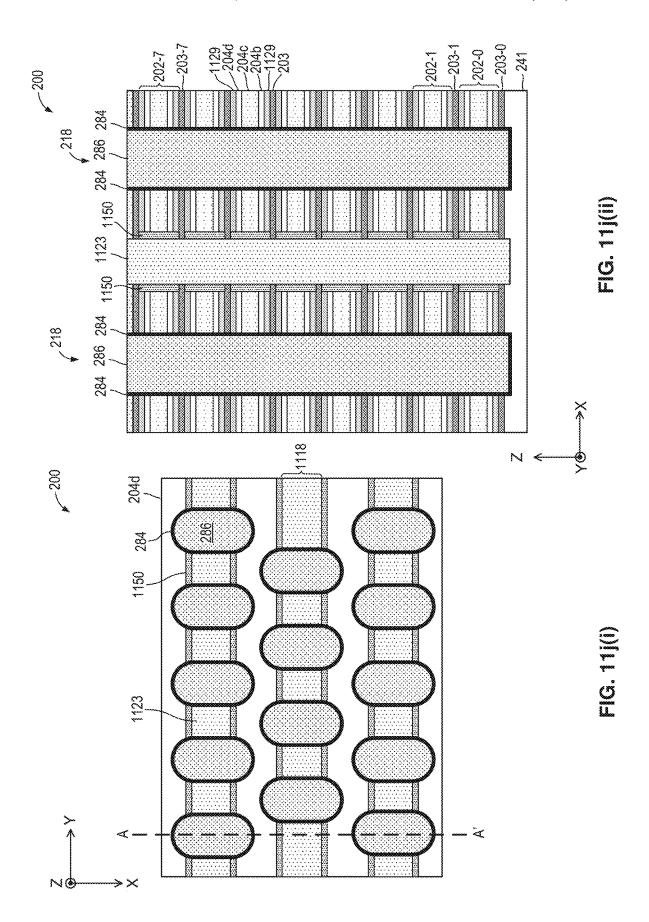

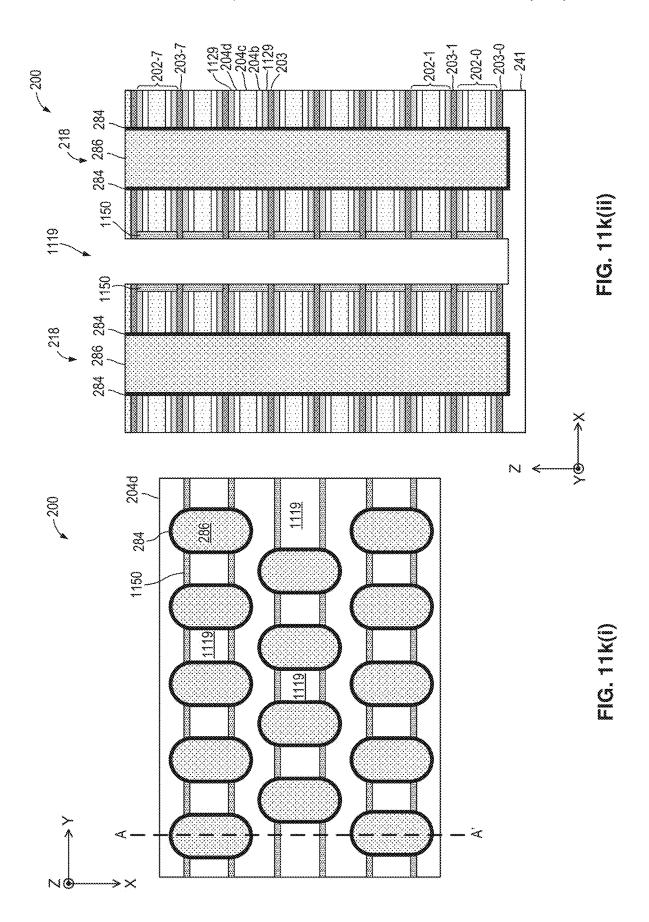

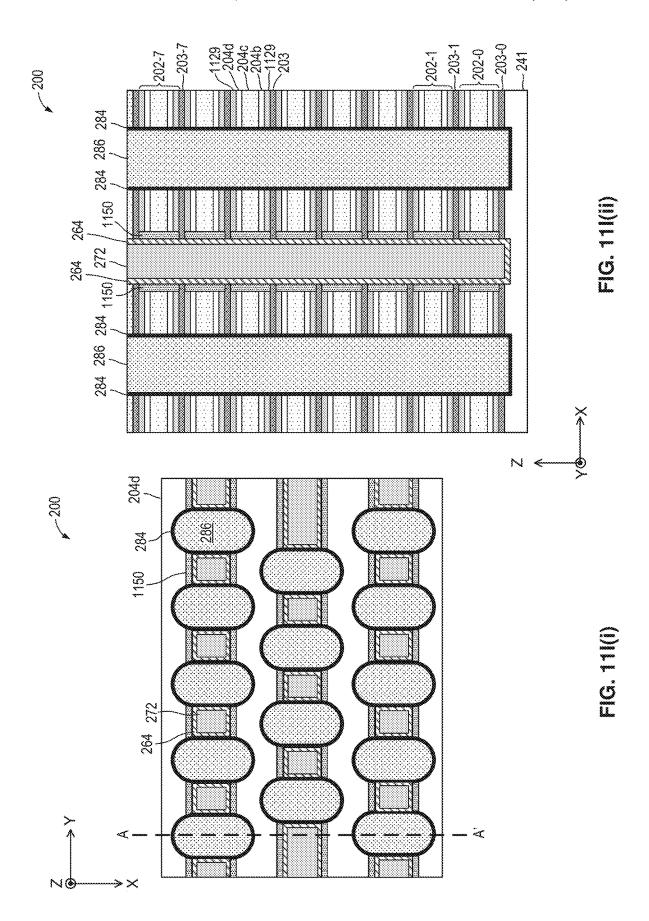

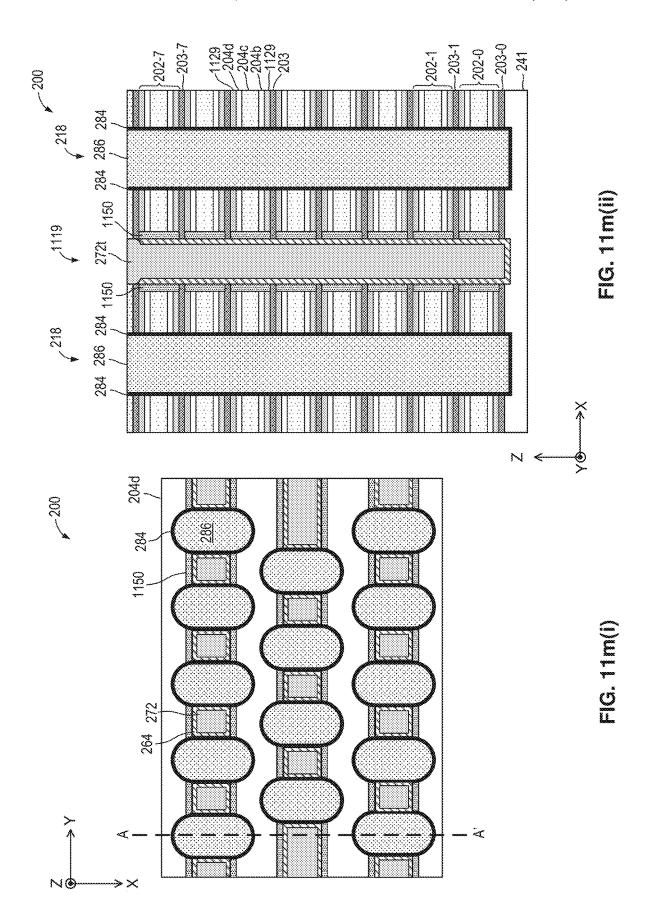

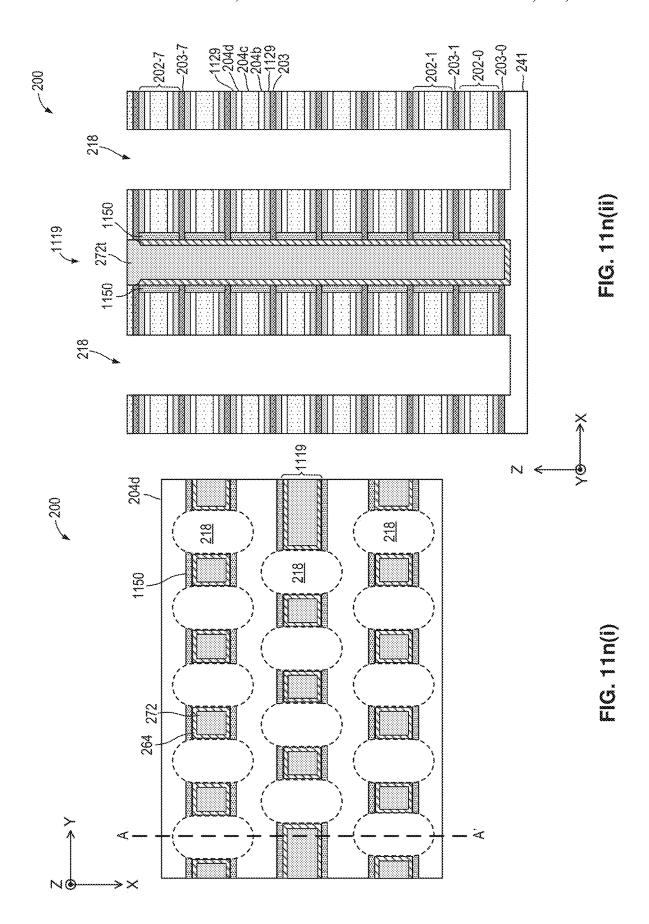

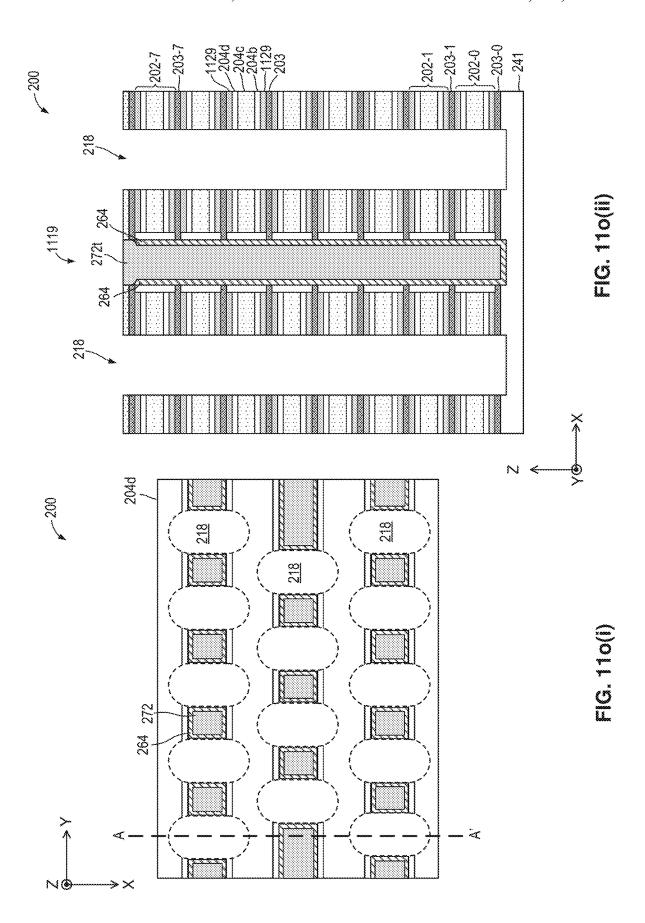

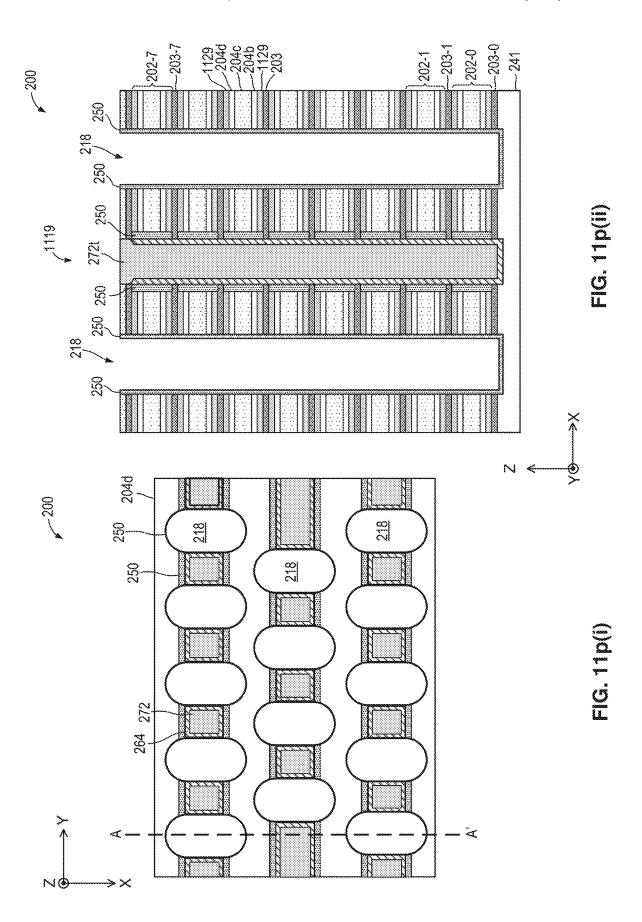

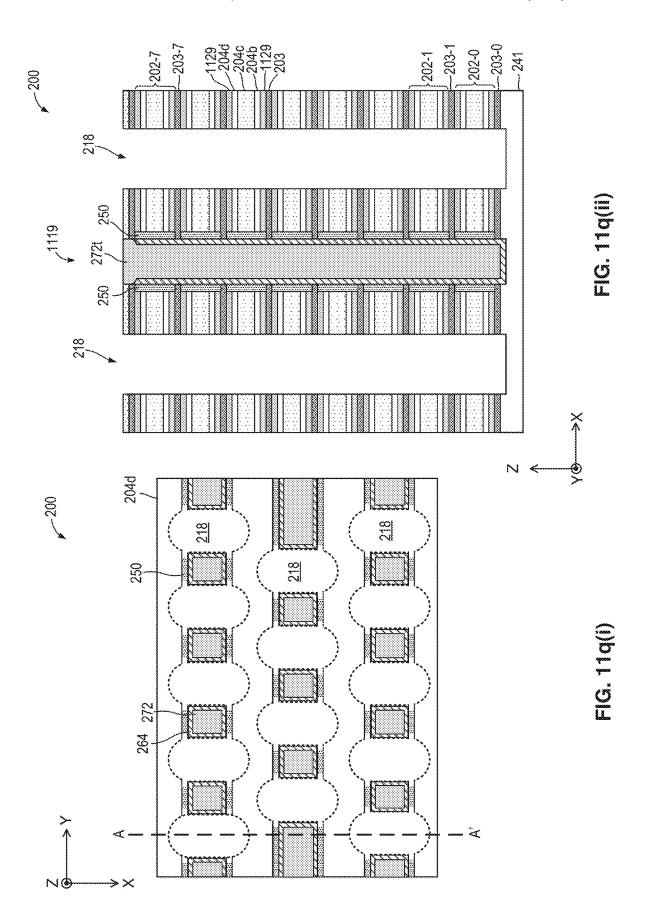

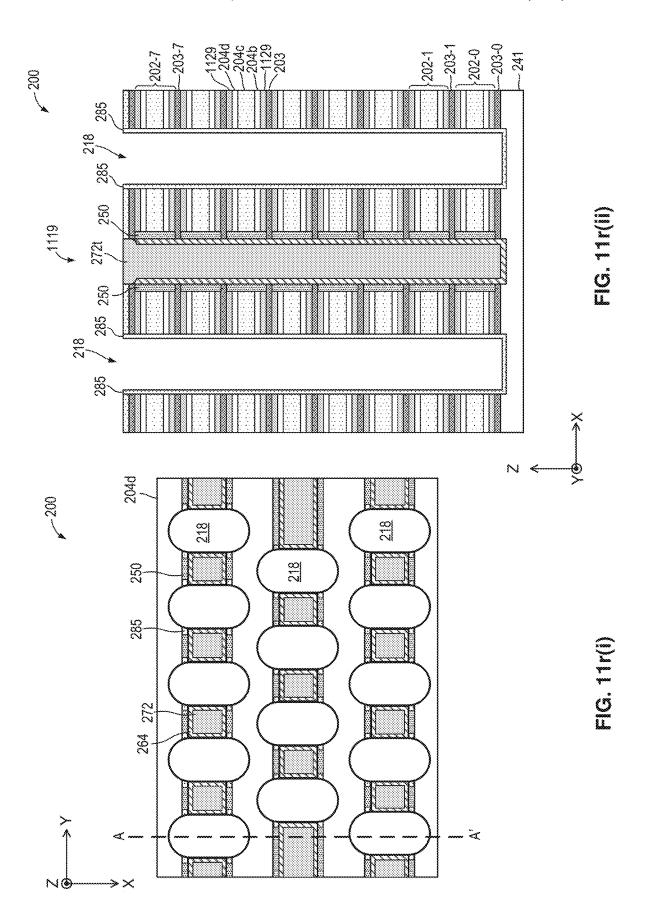

FIGS. 11a, 11b, 11c, 11d, 11e, 11f, 11g, 11h, 11i(i), 11i(ii), 11j(i), 11j(ii), 11k(i), 11k(ii), 11l(i), 11l(ii), 11m(i), 11m(ii), 11n(ii), 11o(i), 11o(ii), 11p(i), 11p(ii), 11q(i), 11q(ii), 11r(i), and 11r(ii) illustrate an additional process in which, 20 subsequent to forming ferroelectric layers, the channel regions for the FeFETs of an array of NOR memory strings are formed by replacing an earlier-formed sacrificial layer, according to one embodiment of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

In this detailed description, process steps described for one embodiment may be used in a different embodiment, 30 even if the process steps are not expressly described in the different embodiment. When reference is made herein to a method including two or more defined steps, the defined steps can be carried out in any order or simultaneously, except where the context dictates or specific instruction 35 otherwise are provided herein. Further, unless the context dictates or express instructions otherwise are provided, the method can also include one or more other steps carried out before any of the defined steps, between two of the defined steps, or after all the defined steps

The present inventors realize that certain polarizable materials (also referred to as "ferroelectric materials") may be used to form storage elements in memory applications. Such ferroelectric materials include, for example, hafnium oxide, which have been used in forming charge-trapping 45 layers in non-volatile or quasi-volatile memory circuits. According to one embodiment of the present invention, high-density data storage may be achieved using ferroelectric field-effect transistors ("FeFETs") as the storage transistors of a 3-dimensional memory array (e.g., an array of 50 NOR memory strings). The present invention, as illustrated herein, provides high endurance, long data retention, and relatively low voltage operations for both erase (under 7.0 volts) and programming (e.g., under -7.0 volts) operations. By combining their ferroelectric or polarization character- 55 istics with the 3-dimensional organization (e.g., as thin-film NOR memory strings described herein), memory arrays formed out of the FeFETs of the present invention achieve the additional benefits of high-density, low-cost, high-speed randomly accessed memory circuits (e.g., low read latency). 60

FIGS. 1a-1 and 1a-2 show conceptualized memory structure 100, which illustrates an organization of ferroelectric field-effect transistors (FeFETs) in an array of NOR memory strings, according to one embodiment of the present invention. This detailed description is facilitated by adopting as 65 reference a Cartesian coordinate system, as indicated in FIGS. 1a-1 and 1a-2. Conceptualized memory structure 100,

8

provided herein as an abstraction of certain salient characteristics of a memory structure of the present invention, represents an array of NOR memory strings fabricated over a surface of substrate 101. Conceptualized memory structure 100, being an abstraction, is not drawn to scale along any of the X-, Y-, and Z-directions. Substrate 101 may be, for example, a conventional silicon wafer having a top layer with a planar surface for fabricating integrated circuits, as is familiar to those of ordinary skill in the art. Thus, under this adopted Cartesian coordinate system, the term "horizontal" refers to any direction parallel to the planar surface of substrate 101, which is a surface of an X-Y plane. Similarly, the term "vertical" refers to the Z-direction or a normal to the planar surface.